# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

### **General Description**

The MAX20067 IC is a complete TFT bias solution for automotive applications. It includes a current-mode boost converter and two push-pull charge-pump drivers.

The IC also includes a gate-shading push-pull level shifter that can be used to improve display uniformity (when needed), and a DAC and VCOM buffer. All blocks on the IC can be used in stand-alone mode or through the I<sup>2</sup>C interface.

Comprehensive control functions are included using the built-in  $I^2C$  interface, as well as diagnostics and monitoring.

The IC is intended to operate with 2.7V to 5.5V supplies.

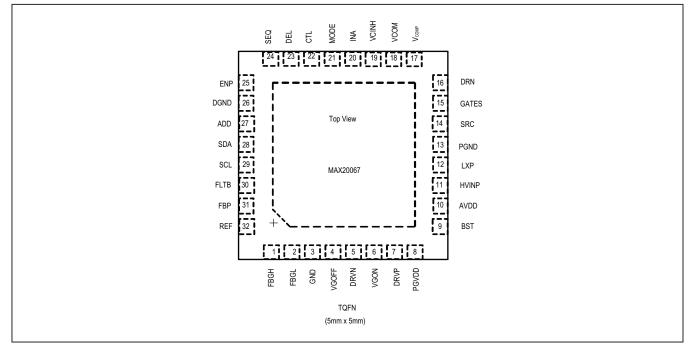

The MAX20067 is available in a 32-pin TQFN package and operates in the -40°C to +105°C temperature range.

### **Applications**

- Infotainment Displays

- Central Information Displays

- Instrument Clusters

Ordering Information appears at end of data sheet.

### **Benefits and Features**

- Versatile TFT Display Power Section

- Integrated Synchronous Boost Converter with Output Voltages Up to 18V

- Integrated Charge-Pump Drivers for the VGON (+36V, max) and VGOFF (-24V, min) Outputs

- Low EMI Operation

- Programmable Switching Frequencies of 440kHz or 2.2MHz

- Programmable Spread Spectrum

- Full Sequencing Flexibility Through I<sup>2</sup>C, Along with Preset Sequences Using SEQ Pin

- Extended Diagnostics Using I<sup>2</sup>C Interface

- Undervoltage/Overvoltage on HVINP, VGON, and VGOFF

- Overcurrent on AVDD

- Temperature Warning

- Built-In Gate-Shading Circuit Controlled by CTL Input

- 8-Bit DAC-Controlled VCOM Buffer

- Robust

- -40°C to +105°C Operating Temperature Range

- Internal Temperature Shutdown

- · AEC-Q100 Qualified

- Compact 32-Pin (5mm x 5mm) TQFN Package

# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

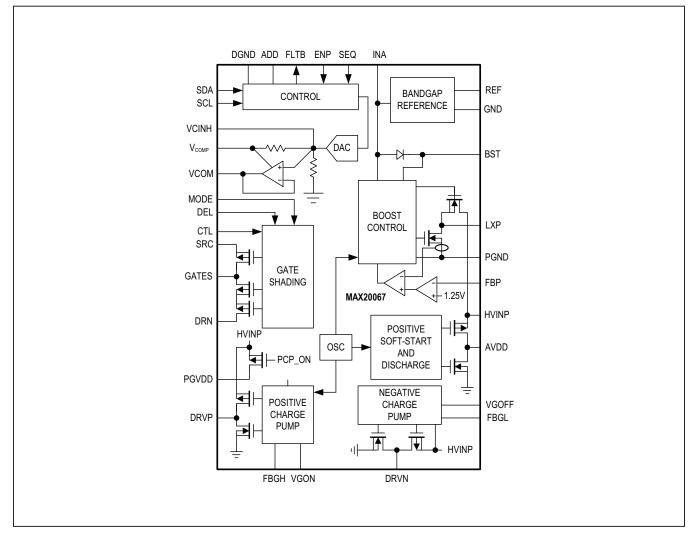

## Simplified Block Diagram

# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

## **Absolute Maximum Ratings**

| INA, SDA, SCL, ENP, FLTB, CTL to GN | ID0.3V to +6V                    |

|-------------------------------------|----------------------------------|

| DEL, REF, FBP, FBGH, FBGL, SEQ,     |                                  |

| MODE, ADD to GND                    | 0.3V to INA + 0.3V               |

| LXP, BST to GND                     | 0.3V to +26V                     |

| BST to LXP                          | 0.3V to +6V                      |

| HVINP, V <sub>COMP</sub> to GND     | 0.3V to +26V                     |

| VCINH, VCOM to GND                  | 0.3V to V <sub>COMP</sub> + 0.3V |

| VCINH to VCOM                       | +1V                              |

| AVDD, PGVDD to HVINP                | 0.3V to HVINP + 0.3V             |

| VGON, SRC, DRN to GND               | 0.3V to +38V                     |

| DRN to GATES                        | 38V to +38V                      |

| GATES to GND                        | 0.3V to SRC + 0.3V               |

| VGOFF to GND                        | 26V to +0.3V                     |

|                                     |                                  |

| DRVP, DRVN to PGND                     | 0.3V to HVINP + 0.3V               |

|----------------------------------------|------------------------------------|

| GND to PGND                            | 0.3V to +0.3V                      |

| GND to DGND                            | 0.3V to +0.3V                      |

| LXP Continuous Current                 | 2.4A                               |

| Continuous Power Dissipation (Multilay | er Board) (T <sub>A</sub> = +70°C) |

| W to 2.758W                            |                                    |

| Package Thermal Resistance             | 1.7°C/W                            |

| ESDHB                                  | 2kV to +2kV                        |

| ESDMM                                  | 200V to +200V                      |

| Operating Temperature                  | 40°C to 105°C                      |

| Junction Temperature                   | 40°C to +150°C                     |

| Storage Temperature Range              | 65°C to +150°C                     |

| Lead Temperature Range                 | +300°C                             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

### 32-Pin TQFN

| PACKAGE CODE                            | T3255+4C       |  |  |  |

|-----------------------------------------|----------------|--|--|--|

| Outline Number                          | <u>21-0140</u> |  |  |  |

| Land Pattern Number                     | <u>90-0012</u> |  |  |  |

| Thermal Resistance, Single-Layer Board: |                |  |  |  |

| Junction to Ambient ( $\theta_{JA}$ )   | 47             |  |  |  |

| Junction to Case $(\theta_{JC})$        | 1.7            |  |  |  |

| Thermal Resistance, Four-Layer Board:   |                |  |  |  |

| Junction to Ambient ( $\theta_{JA}$ )   | 29             |  |  |  |

| Junction to Case $(\theta_{JC})$        | 1.7            |  |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

## **Electrical Characteristics**

| PARAMETER                                           | SYMBOL             | CONDITIONS                                            | MIN                     | TYP  | MAX   | UNITS |

|-----------------------------------------------------|--------------------|-------------------------------------------------------|-------------------------|------|-------|-------|

| INA POWER INPUT                                     |                    | 1                                                     |                         |      |       |       |

| INA Supply Voltage Range                            | V <sub>INA</sub>   |                                                       | 2.7                     |      | 5.5   | V     |

| INA Undervoltage-Lockout<br>Threshold, Rising       | UVLO <sub>R</sub>  |                                                       | 2.45                    | 2.55 | 2.65  | V     |

| INA Undervoltage-Lockout<br>Threshold, Falling      | UVLO <sub>F</sub>  |                                                       |                         | 2.45 |       | V     |

| Supply Current                                      | I <sub>INA</sub>   | ENP = 1 or ENP bit = 1, no switching                  |                         | 1.8  | 3     | mA    |

| Shutdown Current                                    | I <sub>SD</sub>    | ENP = 0 and ENP bit = 0,<br>total current INA + HVINP |                         | 7    | 15    | μA    |

| OSCILLATOR                                          |                    |                                                       |                         |      |       |       |

| Boost Converter Switching<br>Frequency              | f <sub>SW0</sub>   | SWFREQ bit = 0                                        | 1.98                    | 2.2  | 2.42  | MHz   |

| Boost Converter Switching<br>Frequency, Low Setting | f <sub>SW1</sub>   | SWFREQ bit = 1                                        | 390                     | 440  | 490   | kHz   |

| Frequency Dither                                    |                    | SSOFF bit = 1                                         | -4                      |      | +4    | %     |

| REFERENCE                                           |                    |                                                       |                         |      |       |       |

| REF Output Voltage                                  | V <sub>REF</sub>   |                                                       | 1.238                   | 1.25 | 1.262 | V     |

| REF Load Regulation                                 |                    | I <sub>REF</sub> from 0µA to 100µA                    |                         | 10   | 20    | mV    |

| REF Line Regulation                                 |                    | 2.7V < V <sub>INA</sub> < 5.5V, no load               |                         |      | 5     | mV    |

| BOOST CONVERTER                                     |                    |                                                       |                         |      |       |       |

| AVDD Output Voltage Range                           | V <sub>AVDD</sub>  |                                                       | V <sub>INA</sub><br>+ 1 |      | 18    | V     |

| LXP Current Limit                                   |                    |                                                       | 2.1                     | 2.5  | 2.9   | A     |

| Low-Side Switch<br>On-Resistance                    | R <sub>LXP</sub>   |                                                       |                         | 0.2  | 0.4   | Ω     |

| LXP Leakage Current                                 | I <sub>LXP</sub>   | V <sub>LXP</sub> = 18V, T <sub>A</sub> = +25°C        |                         |      | 5     | μA    |

| Synchronous Rectifier<br>On-Resistance              | R <sub>SYNC</sub>  |                                                       |                         | 0.25 | 0.5   | Ω     |

| Synchronous Rectifier<br>Zero-Crossing Threshold    | I <sub>SYNCZ</sub> | 2.2MHz                                                |                         | 140  |       | mA    |

| Maximum Duty Cycle                                  | DCMAX              |                                                       | 90                      | 94   | 98    | %     |

| Current-Limit Ramp Time at Startup                  | t <sub>RAMP</sub>  |                                                       |                         | 12.5 |       | ms    |

| FBP Regulation Voltage                              | V <sub>FPB</sub>   |                                                       | 1.225                   | 1.25 | 1.275 | V     |

| FBP Load Regulation                                 |                    | 1mA < I <sub>AVDD</sub> < 200mA                       |                         | -1   |       | %     |

| FBP Line Regulation                                 |                    | V <sub>INA</sub> = 2.7V to 5.5V                       | -0.4                    |      | +0.4  | %     |

# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

## **Electrical Characteristics (continued)**

| PARAMETER                                   | SYMBOL                | CONDITIONS                            | MIN        | TYP  | MAX   | UNITS |

|---------------------------------------------|-----------------------|---------------------------------------|------------|------|-------|-------|

| FBP Undervoltage-Fault<br>Threshold         | V <sub>FBPUV</sub>    |                                       | 75         | 80   | 85    | %     |

| FBP Overvoltage-Fault<br>Threshold          | V <sub>FBPOV</sub>    |                                       | 110        | 115  | 120   | %     |

| FBP Input Bias Current                      | I <sub>FBP</sub>      |                                       |            |      | 200   | nA    |

| HVINP-AVDD Switch<br>On-Resistance          | R <sub>HA</sub>       |                                       |            | 0.5  | 1     | Ω     |

| AVDD Discharge Resistance                   | R <sub>AVDD</sub>     |                                       | 1          | 1.5  | 2     | kΩ    |

| HVINP-AVDD Switch Current<br>Limit          | I <sub>LIMHA</sub>    | After soft-start<br>During soft-start | 240<br>120 |      |       | mA    |

| POSITIVE CHARGE-PUMP R                      | EGULATOR              |                                       | J          |      |       | 1     |

| PGVDD Operating Voltage<br>Range            | V <sub>PGVDD</sub>    |                                       | 6          |      | 18    | V     |

| VGON Output Voltage<br>Range                | V <sub>VGON</sub>     |                                       |            |      | 36    | V     |

| DRVP Current Limit                          | I <sub>LIM_P</sub>    |                                       | 40         |      |       | mA    |

| Positive Charge-Pump<br>Switching Frequency |                       |                                       |            | 440  |       | kHz   |

| FBGH Regulation Voltage                     | V <sub>FBGH</sub>     |                                       | 1.225      | 1.25 | 1.275 | V     |

| FBGH Undervoltage-Fault<br>Threshold        | V <sub>FBGHUV</sub>   |                                       | 75         | 80   | 85    | %     |

| FBGH Overvoltage-Fault<br>Threshold         | V <sub>FBGHOV</sub>   |                                       | 110        | 115  | 120   | %     |

| DRVP On-Resistance High                     | R <sub>ONH_DRVP</sub> |                                       |            |      | 60    | Ω     |

| DRVP On-Resistance Low                      | R <sub>ONL_DRVP</sub> |                                       |            |      | 30    | Ω     |

| HVINP-PGVDD Switch<br>On-Resistance         | R <sub>HP</sub>       |                                       |            | 30   | 60    | Ω     |

| HVINP-PGVDD Current Limit                   |                       |                                       | 40         |      |       | mA    |

| VGON Discharge Resistance                   |                       |                                       | 8          | 12   | 16    | kΩ    |

| NEGATIVE CHARGE-PUMP                        | REGULATOR             |                                       |            |      |       |       |

| VGOFF Output Voltage<br>Range               |                       |                                       | -24        |      | -6    | V     |

| DRVN Current Limit                          | I <sub>LIMN</sub>     |                                       | 15         |      |       | mA    |

| Negative Charge-Pump<br>Switching Frequency |                       |                                       |            | 440  |       | kHz   |

| FBGL Regulation Voltage                     | V <sub>FBGL</sub>     | V <sub>REF</sub> - V <sub>FBGL</sub>  | 0.98       | 1    | 1.02  | V     |

| FBGL Undervoltage-Fault<br>Threshold        | V <sub>FBGLUV</sub>   | Rising                                | 400        | 450  | 500   | mV    |

# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

## **Electrical Characteristics (continued)**

| PARAMETER                                     | SYMBOL                      | CONDITIONS                                        | MIN   | TYP                           | MAX                         | UNITS |

|-----------------------------------------------|-----------------------------|---------------------------------------------------|-------|-------------------------------|-----------------------------|-------|

| FBGL Overvoltage-Fault<br>Threshold           | V <sub>FBGLOV</sub>         | Falling                                           | 20    | 50                            | 100                         | mV    |

| DRVN On-Resistance High                       | R <sub>ONH_DRVN</sub>       |                                                   |       |                               | 60                          | Ω     |

| DRVN On-Resistance Low                        |                             |                                                   |       |                               | 30                          | Ω     |

| VGOFF Discharge<br>Resistance                 |                             |                                                   | 8     | 12                            | 16                          | kΩ    |

| GATE-SHADING CIRCUIT                          |                             |                                                   |       |                               |                             |       |

| SRC Input Voltage Range                       | V <sub>SRC</sub>            |                                                   |       |                               | 36                          | V     |

| SRC-to-GATES Switch<br>On-Resistance          | R <sub>SRC</sub><br>GATES   |                                                   |       | 10                            | 20                          | Ω     |

| DRN-to-GATES Switch<br>On-Resistance          | R <sub>DRN</sub> _<br>GATES |                                                   |       | 10                            | 20                          | Ω     |

| DEL Pullup Current                            |                             |                                                   | 4     | 5                             | 6                           | μA    |

| DEL Enable Threshold                          |                             |                                                   |       | 1.25                          |                             | V     |

| CTL-to-GATES Delay                            |                             | C <sub>GATES</sub> = 1nF                          |       | 150                           |                             | ns    |

| MODE Switch<br>On-Resistance                  |                             |                                                   |       | 1250                          |                             | Ω     |

| MODE Voltage Threshold                        |                             | MODE rising                                       | 2     |                               |                             | V     |

| MODE Pullup Current                           |                             |                                                   | 80    | 100                           | 120                         | μA    |

| MODE Current-Source<br>Stop Threshold         |                             |                                                   |       | 1.7                           |                             | V     |

| VCOM BUFFER                                   | 1                           | L                                                 | I     |                               |                             |       |

| V <sub>COMP</sub> Voltage Range               |                             |                                                   | 5     |                               | 18                          | V     |

| V <sub>COMP</sub> Quiescent Supply<br>Current |                             | I <sub>VCOMP</sub> = 0mA, V <sub>COMP</sub> = 12V |       | 1.8                           |                             | mA    |

| VCINH Input Impedance                         |                             |                                                   |       | 500                           |                             | kΩ    |

| VCINH/V <sub>COMP</sub> Division<br>Ratio     |                             |                                                   |       | 0.5                           |                             | V/V   |

| VCOM Output Current Limit                     |                             |                                                   | 130   |                               |                             | mA    |

| VCOM Offset Voltage                           |                             |                                                   | -8    |                               | +8                          | mV    |

| VCOM Output Voltage<br>Range                  |                             |                                                   | 1.5   |                               | V <sub>COMP</sub><br>- 1.5V | V     |

| VCOM DAC Step Size                            |                             |                                                   |       | 19.5                          |                             | mV    |

| VCOM DAC Voltage Range                        |                             |                                                   |       | V <sub>COMP</sub> /2<br>+2.5V |                             | V     |

| VCOM Undervoltage-<br>Detection Threshold     |                             | VCINH - VCOM, falling                             | -0.55 | -0.35                         | -0.15                       | V     |

| VCOM Overvoltage-<br>Detection Threshold      |                             | VCINH - VCOM, rising                              | 0.04  | 0.25                          | 0.41                        | V     |

# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

## **Electrical Characteristics (continued)**

| PARAMETER                                      | SYMBOL                | CONDITIONS                                  | MIN  | ТҮР  | MAX  | UNITS |

|------------------------------------------------|-----------------------|---------------------------------------------|------|------|------|-------|

| VCOM Fault Detection<br>Filter Time            |                       | tfault[1:0] = 01                            |      | 60   |      | ms    |

| VCOM Discharge Resistance                      |                       |                                             | 6    | 13   | 20   | kΩ    |

| TFT FAULT PROTECTION                           |                       | 1                                           |      |      |      |       |

| Fault Timeout                                  |                       | tfault[1:0] = 01                            |      | 60   |      | ms    |

| Fault Retry Time                               |                       |                                             |      | 2.4  |      | s     |

| FLTB Output Frequency                          |                       | Stand-alone mode only                       | 0.88 | 1    | 1.12 | kHz   |

| FLTB Output Duty Cycle,<br>VGON or VGOFF Fault |                       |                                             |      | 75   |      | %     |

| FLTB Output Duty Cycle,<br>HVINP Fault         |                       |                                             |      | 50   |      | %     |

| FLTB Output Duty Cycle,<br>AVDD Fault          |                       |                                             |      | 25   |      | %     |

| AVDD Undervoltage-Fault<br>Threshold           |                       | Relative measurement between HVINP and AVDD | 70   | 75   | 80   | %     |

| FBP Short-Circuit Fault<br>Threshold           |                       |                                             | 30   | 40   | 50   | %     |

| FBGH Short-Circuit Fault<br>Threshold          |                       |                                             | 30   | 40   | 50   | %     |

| FBGL Short-Circuit Fault<br>Threshold          |                       |                                             | 0.8  | 0.85 | 0.9  | V     |

| Short-Circuit and Overload<br>Fault Delay      |                       |                                             |      | 10   |      | μs    |

| THERMAL PROTECTION                             |                       |                                             |      |      |      |       |

| Thermal Shutdown                               | T <sub>SHDN</sub>     |                                             |      | 165  |      | °C    |

| Thermal-Shutdown<br>Hysteresis                 | T <sub>SHDN_HYS</sub> |                                             |      | 15   |      | °C    |

| LOGIC INPUT AND OUTPUT                         | S                     |                                             |      |      |      |       |

| FLTB, DEL Low Output<br>Voltage                | V <sub>OL</sub>       | I <sub>SINK</sub> = 5mA                     |      |      | 0.4  | V     |

| FLTB, DEL, SDA Leakage<br>Current              | IILEAK                |                                             | -1   |      | +1   | μA    |

| SDA Output Voltage Low                         | V <sub>OLSDA</sub>    |                                             |      |      | 0.8  | V     |

| ENP Pulldown Resistor<br>Value                 | R <sub>ENPPD</sub>    |                                             | 50   | 75   |      | kΩ    |

| ENP Glitch Filter Time                         | t <sub>ENP</sub>      |                                             |      | 10   |      | μs    |

| ENP, CTL, SCL, SDA, ADD<br>Input Voltage Low   | V <sub>IL</sub>       |                                             |      |      | 0.8  | V     |

| ENP, CTL, SCL, SDA, ADD<br>Input Voltage High  | V <sub>IH</sub>       |                                             | 2    |      |      | V     |

# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

## **Electrical Characteristics (continued)**

| PARAMETER                          | SYMBOL              | CONDITIONS | MIN | ТҮР | MAX | UNITS |

|------------------------------------|---------------------|------------|-----|-----|-----|-------|

| I2C INTERFACE                      |                     |            |     |     |     |       |

| Clock Frequency                    | f <sub>SCL</sub>    |            |     |     | 400 | kHz   |

| Setup Time (Repeated)<br>START     | <sup>t</sup> SU:STA |            | 260 |     |     | ns    |

| Hold Time (Repeated)<br>START      | <sup>t</sup> HD:STA |            | 260 |     |     | ns    |

| SCL Low Time                       | t <sub>LOW</sub>    |            | 350 |     |     | ns    |

| SCL High Time                      | <sup>t</sup> HIGH   |            | 260 |     |     | ns    |

| Data Setup Time                    | <sup>t</sup> SU:DAT |            | 50  |     |     | ns    |

| Data Hold Time                     | t <sub>HD:DAT</sub> |            | 0   |     |     | ns    |

| Setup Time for STOP Condi-<br>tion | t <sub>SU:STO</sub> |            | 260 |     |     | ns    |

| Spike Suppression                  |                     |            |     | 50  |     | ns    |

# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

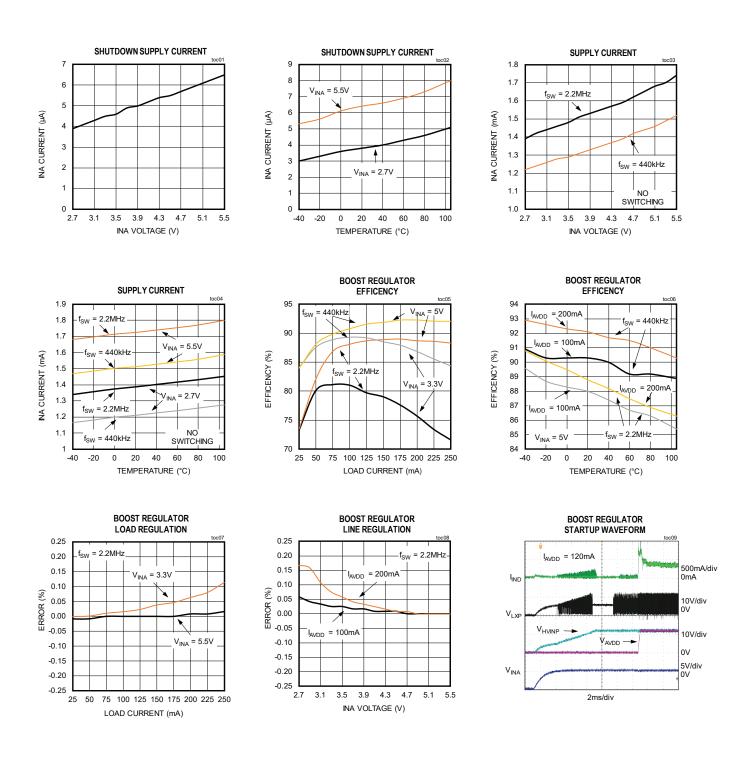

## **Typical Operating Characteristics**

(V<sub>INA</sub> = 3.3V,  $f_{SW}$  = 2.2MHz,  $C_{VCOM}$  = 1µF,  $T_A$  = +25°C, unless otherwise noted.)

# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

(V<sub>INA</sub> = 3.3V,  $f_{SW}$  = 2.2MHz,  $C_{VCOM}$  = 1µF,  $T_A$  = +25°C, unless otherwise noted.)

# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

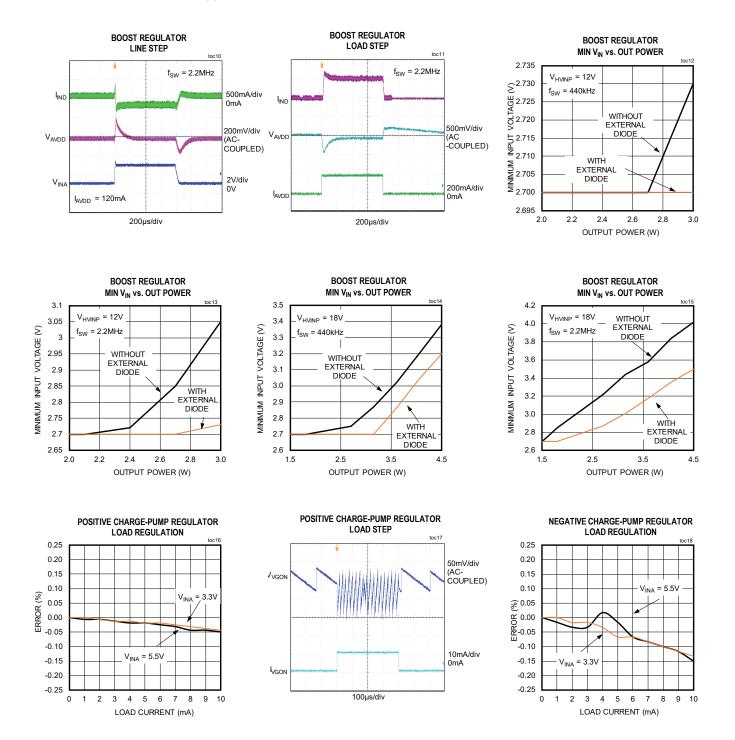

## **Typical Operating Characteristics (continued)**

$(V_{INA} = 3.3V, f_{SW} = 2.2MHz, C_{VCOM} = 1\mu F, T_A = +25^{\circ}C, unless otherwise noted.)$

# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

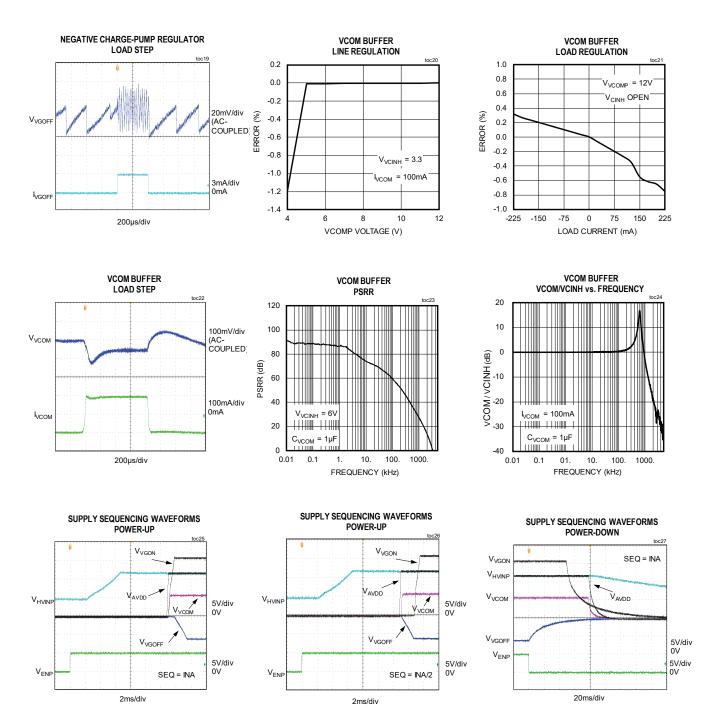

## **Typical Operating Characteristics (continued)**

(V<sub>INA</sub> = 3.3V,  $f_{SW}$  = 2.2MHz,  $C_{VCOM}$  = 1µF,  $T_A$  = +25°C, unless otherwise noted.)

# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

## **Pin Configuration**

## **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                                                    |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | FBGH  | Positive Charge-Pump Feedback Connection. FBGH is regulated to 1.25V. Connect a resistor-<br>divider from VGON to GND with its midpoint connected to FBGH.                                                  |

| 2   | FBGL  | Negative Charge-Pump Feedback Connection. FBGL is regulated to 0.25V. Connect a resistor-<br>divider from REF to VGOFF with its midpoint connected to FBGL.                                                 |

| 3   | GND   | Ground Connection                                                                                                                                                                                           |

| 4   | VGOFF | Output of Negative Charge-Pump Block.                                                                                                                                                                       |

| 5   | DRVN  | Negative Charge-Pump Push-Pull Drive Output                                                                                                                                                                 |

| 6   | VGON  | Output of Positive Charge-Pump Block                                                                                                                                                                        |

| 7   | DRVP  | Positive Charge-Pump Push-Pull Drive Output                                                                                                                                                                 |

| 8   | PGVDD | Supply voltage for positive charge-pump. PGVDD is connected to HVINP by means of an internal switch when the positive charge-pump is enabled. Bypass PGVDD with a ceramic capacitor of at least 1µF to GND. |

| 9   | BST   | Bootstrap Capacitor Connection for Synchronous Rectifier Driver. Connect a 0.1µF ceramic capacitor between BST and LXP.                                                                                     |

| 10  | AVDD  | Switched Output of Boost Converter. Connect a bypass capacitor of at least $4.7\mu$ F from AVDD to PGND.                                                                                                    |

| 11  | HVINP | Boost Output and Input to Positive and Negative Charge Pumps. Bypass HVINP with the boost-converter output capacitor placed close to the pin.                                                               |

| 12  | LXP   | Switching Node of Boost Converter. Connect the boost inductor between LXP and INA.                                                                                                                          |

| 13  | PGND  | Ground Connection for Boost Switching Device and VCOM Buffer. Connect to GND using a low-impedance trace.                                                                                                   |

# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

## **Pin Description (continued)**

| PIN | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                     |

|-----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14  | SRC               | Source of Internal High-Side Switch in Gate-Shading Circuit. SRC is usually connected to VGON. Bypass SRC with a 0.1µF capacitor placed close to the pin.                                                                                                                                                                                                                    |

| 15  | GATES             | Switched Output of Gate-Shading Circuit                                                                                                                                                                                                                                                                                                                                      |

| 16  | DRN               | Lower Input of Gate-Shading Circuit. Connect to an external source or GND through a discharge resistor.                                                                                                                                                                                                                                                                      |

| 17  | V <sub>COMP</sub> | Supply Voltage for VCOM Buffer. Normally connected to AVDD. Bypass $V_{COMP}$ with a 0.1µF ceramic capacitor placed close to the pin.                                                                                                                                                                                                                                        |

| 18  | VCOM              | Output of VCOM Amplifier. Bypass VCOM to GND with a 1µF ceramic capacitor.                                                                                                                                                                                                                                                                                                   |

| 19  | VCINH             | Noninverting Input of VCOM Amplifier. In stand-alone mode, drive VCINH to set the VCOM output voltage. VCINH is prebiased to 50% of $V_{COMP}$ with an internal resistor-divider comprising two 1M $\Omega$ resistors.                                                                                                                                                       |

| 20  | INA               | Supply Connection for Display Bias Circuitry. Bypass INA with a local 0.1µF capacitor.                                                                                                                                                                                                                                                                                       |

| 21  | MODE              | Mode Configuration Pin for Gate-Shading Level Shifter. MODE is used to adjust the timing of the gate-shading output. MODE is high impedance when connected to INA, and internally pulled down during UVLO or in shutdown.                                                                                                                                                    |

| 22  | CTL               | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                      |

| 23  | DEL               | Gate-Shading Circuit Delay Input. Connect a capacitor from DEL to GND to set the turn-on delay.                                                                                                                                                                                                                                                                              |

| 24  | SEQ               | Logic-Level Sequencing Input Pin. The voltage level on SEQ determines whether the IC is serially controlled, or one of the predetermined sequences is used. Connect SEQ to INA or a resistive divider between INA and GND to set one of the preset stand-alone sequences (see Table 3). For serial control, connect SEQ to GND.                                              |

| 25  | ENP               | Active-High Enable Input for Boost Converter. ENP also enables the VGON and VGOFF regulators in the set sequence. ENP has an internal pulldown resistor. When serial control is used, connect ENP low.                                                                                                                                                                       |

| 26  | DGND              | Digital Ground. Connect directly to the exposed pad of the package.                                                                                                                                                                                                                                                                                                          |

| 27  | ADD               | I <sup>2</sup> C Address-Selection Pin. Connect to GND for a base address of 0x20, or to INA for a base address of 0x28.                                                                                                                                                                                                                                                     |

| 28  | SDA               | Bidirectional I <sup>2</sup> C Data Pin                                                                                                                                                                                                                                                                                                                                      |

| 29  | SCL               | Serial-Clock Input                                                                                                                                                                                                                                                                                                                                                           |

| 30  | FLTB              | Open-Drain, Active-Low Fault Output. Connect a pullup resistor from FLTB to a logic supply ≤ 5V. In stand-alone mode, the duty cycle of the FLTB pin indicates an error condition, if present (see <u>Table 4</u> ). When the serial interface is used, FLTB is either a 0 (indicating data to be read from the internal registers) or a 1. It does not output a PWM signal. |

| 31  | FBP               | Boost Feedback Connection. FBP is regulated to 1.25V. Connect a resistor-divider from HVINP to GND with its midpoint connected to FBP.                                                                                                                                                                                                                                       |

| 32  | REF               | Internal 1.25V Reference Output. Connect a 0.22µF capacitor from REF to GND.                                                                                                                                                                                                                                                                                                 |

|     | EP                | Exposed Pad. Connect EP to GND.                                                                                                                                                                                                                                                                                                                                              |

# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

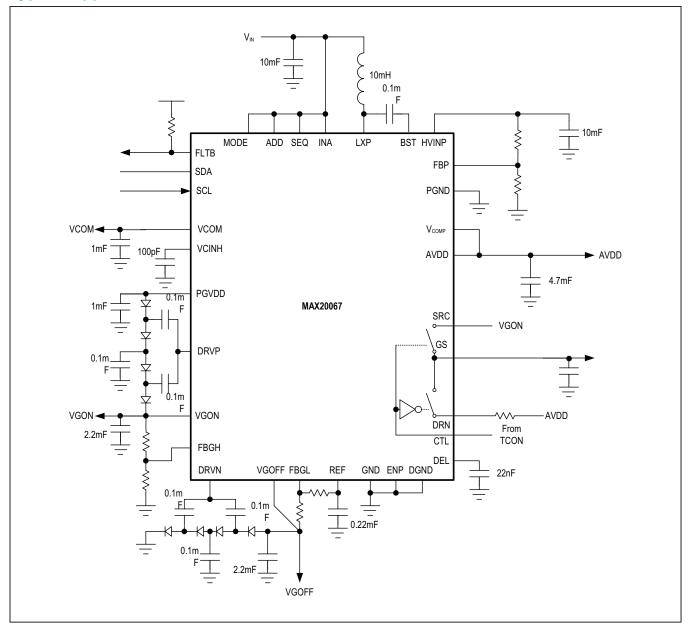

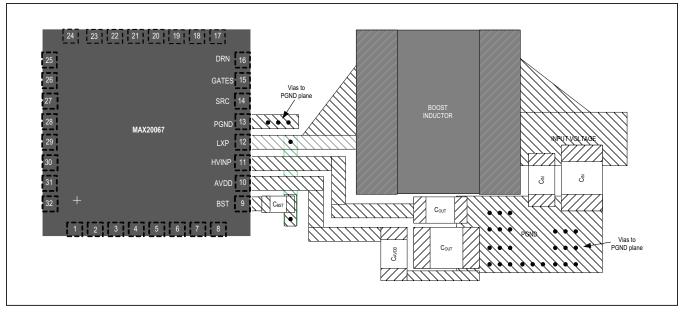

## **Typical Application Circuit**

## Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

### **Detailed Description**

The MAX20067 is a highly integrated power-supply IC for automotive TFT-LCD applications. The IC integrates one boost converter, two gate-driver supplies, a high-voltage "gate-shading" level shifter, and a high-current VCOM buffer.

The main power-supply section, comprising the boost converter and gate-driver supplies, operates from a 2.7V to 5.5V supply. The boost converter operates at 440kHz or 2.2MHz and has built-in spread spectrum that can be disabled using the serial interface for reducing EMI.

The boost converter provides an output voltage adjustable up to 18V, with up to 200mA output current and has two internal MOSFET switching elements.

The IC provides gate-driver supplies using positive and negative charge-pump regulators, with a current capability of 10mA for the positive charge pump (using a doubler charge pump) and 3mA for the negative charge pump (assuming a 2-stage charge pump). Output voltage is adjustable with a +36V (max) output on the positive charge pump and -22V on the negative charge pump.

The startup and shutdown sequences for all power domains, controlled using one of the preset modes, are selected using the SEQ pin. Sequencing can also be controlled through the serial interface when the SEQ pin is grounded.

#### **TFT Power Section**

#### **Source-Driver Power Supplies**

The source-driver power supply consists of a boost converter that generates +18V (max) and can deliver up to +200mA. The source-driver power supply's regulation voltage (HVINP) is set by a resistor-divider on FBP. The source driver uses constant-frequency peak-current-mode control, with internal fixed-slope compensation. Internal compensation stabilizes the control loop. At low output power, the converter enters skip mode.

The TFT boost converter has an internal error amplifier with a  $g_m$  of 13µS that has FBP and REF = 1.25V as inputs. There is an internal compensation network at the output of the error amplifier as follows:

#### $C_C$ = 140pF, $R_C$ = 500k $\Omega$

For the current loop, there is internal current sensing using a transresistance of  $R_T = 0.21V/A$ . The currentsense voltage ( $V_{CS} = I_{inductor} \times R_T$ ) is added to the slope compensation. The slope-compensation signal has a slope of 1250mV per microsecond. The resulting  $V_{SUM}$ =  $V_{CS} + V_{SLOPE}$  is compared to  $V_{COMP}$  (output of the error amplifier) at the input of the PWM comparator to regulate the LXP duty cycle.

#### **Gate-Driver Power Supplies**

The positive gate-driver charge pump (VGON) generates +36V (max) and the negative gate-driver charge pump (VGOFF) generates -24V (max). The gate-driver supplies have a current capability of 10mA for the positive charge pump (using a doubler charge pump) and 3mA for the negative charge pump (assuming a 2-stage charge pump). The VGON and VGOFF regulation voltages are both set using the external resistor networks, as shown in the *Typical Application Circuit*. Both charge-pump regulators use a 440kHz switching frequency. The charge pumps regulate the output voltages by controlling the current that flows into the flying capacitors.

#### **Operation of the Positive Charge Pump**

The positive charge-pump regulator is typically used to generate the positive supply rail for the TFT-LCD gatedriver ICs.

The output voltage is set with an external resistive voltage-divider from its output to GND, with the midpoint connected to FBGH. The number of charge-pump stages and the setting of the feedback-divider determine the output voltage of the positive charge-pump regulator. The charge pump push-pull output consists of a high-side p-channel MOSFET (P1) and a low-side n-channel MOSFET (N1) to control the power transfer.

The positive charge pump uses a simple skipping control scheme. The feedback signal (FBGH) is compared with a 1.25V internal reference. The result of this comparison is sampled on every clock cycle. If the feedback signal is below 1.25V, a DRVP cycle is initiated. In the first half period, the rising edge of the clock turns on N1 and turns off P1, allowing the flying capacitors to charge, while during the second half period, the falling edge of the clock turns off N1 allowing charge transfer to the output. During both phases, N1 and P1 act as current-limited switches with a current limit of at least 40mA.

Alternatively, if the feedback signal is above 1.25V at the clock rising edge, the regulator ignores the clock period and N1 and P1 remain off.

The charge-pump regulator also includes a discharge switch from VGON to ground, turned off to discharge the output capacitors during the sequential turn-off of the output voltages, as programmed by the SEQ pin or through I<sup>2</sup>C. The PGVDD node is internally connected through a switch to the HVINP voltage. See <u>Table 3</u> for stand-alone sequencing options.

## Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

#### **Operation of the Negative Charge Pump**

The negative charge-pump regulator is typically used to generate the negative supply rail for the TFT-LCD gatedriver ICs. The output voltage is set with an external resistive voltage-divider from its output to REF, with the midpoint connected to FBGL. The number of charge-pump stages and the setting of the feedback-divider determine the output of the negative charge-pump regulator. The charge-pump controller includes a high-side p-channel MOSFET (P1) and a low-side n-channel MOSFET (N1) to control the power transfer.

The feedback signal (FBGL) is compared with a 0.25V internal reference obtained by partitioning the main 1.25V reference. The result of this comparison is sampled on every clock cycle. If (REF - FBGL) is less than 1.25V - 0.25V or 1V, a DRVN cycle is initiated. In the first half period, the rising edge of the clock turns on P1 and turns off N1, allowing the flying capacitors to charge, while during the second half period, the falling edge of the clock turns on N1 and turns off P1 allowing charge transfer to the output. During both phases, N1 and P1 act as current-limited switches with a current limit of at least 15mA.

Alternatively, if (REF - FBGL) is less than 1V at the clock rising edge, the regulator ignores the clock period and N1 and P1 remain off.

For sequencing of the output voltages at turn-off, a discharge switch is connected from VGOFF to ground. The desired sequence is programmable using the SEQ pin or through  $I^2C$ . See <u>Table 3</u> for the stand-alone sequencing options.

#### Fault Protection on the TFT Section

The IC has robust fault and overload protection. If any of the source-driver or gate-driver supplies fall below 80% (typ) or above 115% of the programmed regulation voltage for more than 60ms (typ, default), all the outputs turn off and a fault condition is set. If a short condition occurs on any of the source-driver supplies for more than 10µs,

all the outputs turn off and a fault condition is set. A short condition is detected when the output voltage falls below 40% of the intended regulation voltage. The output with the fault turns off immediately, while the other outputs follow the turn-off sequence programmed by the SEQ pin or through I<sup>2</sup>C. The fault condition is cleared when the ENP pin or INA supply is cycled or after the retry timer (2.4s typ, default) times out, if enabled. If needed, the retry time can be adjusted or this function disabled using the serial interface. In the case of a thermal fault, the IC turns off immediately and remains off until the chip temperature drops by 15°C (typ).

#### **Output Control**

The sequencing of the IC's source-driver and gate-driver outputs (AVDD, VGON, and VGOFF) is determined by the setting of the SEQ pin or through  $I^2C$ . All outputs are brought up with soft-start control to limit the inrush current. Table 3 lists the sequencing options using the SEQ pin.

The outputs are also turned off in sequence, with the boost converter the last block to be disabled. Active pulldowns are provided on all outputs to facilitate a controlled discharge. The pulldowns remain active for 512ms after the boost has been disabled, at which point the IC enters shutdown mode, if applicable.

#### Power-Up/Power-Down Sequencing and Timing

The IC allows for flexible power-up/power-down sequencing and timing of the source-driver and gate-driver power supplies (AVDD, VGON, and VGOFF). Toggling the ENP pin from low to high initiates an adjustable preset powerup sequence. Alternatively, power-up sequencing can be controlled through I<sup>2</sup>C. Toggling the ENP pin from high to low initiates the power-down sequence. The ENP pin has an internal deglitching filter of 10µs (typ). **Note:** A glitch in the ENP signal with a period less than 10µs is ignored by the internal enable circuitry.

## Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

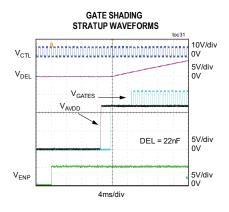

#### **Gate-Shading Level Shifter**

The gate-shading level shifter is enabled when the softstart of all regulators is completed and the DEL pin exceeds its enable threshold. A capacitor on the DEL pin can be used to adjust the startup-delay time together with the internal  $5\mu$ A current source. The delay can be calculated using the following equation:

$$\text{DELAY} = \frac{\left(1.25 V \times C_{\text{DEL}}\right)}{5 \mu A}$$

When the IC is disabled, GATES is discharged to GND. After the IC is enabled, the GATES switches are off and GATES is high impedance until the complete power sequence is finished (without a fault occurring) and DEL exceeds 1.25V. When DEL exceeds 1.25V, the level shifter is activated and its state controlled by the CTL and MODE inputs according to <u>Table 1</u>. An external resistor and capacitor are used to produce the desired waveform where the rise of the output signal is fast, but the fall is an exponential decay controlled by the external values of the resistor and capacitor. In addition, a capacitor on the MODE pin can be used to delay the fall of the GATES output.

Connect MODE to INA when the  $V_{GGS}$  delay is not needed. Connect a capacitor from MODE to GND to set the delay according to the following equation:

$$C_{\text{MODE}} = \frac{(100 \mu A \times t_{\text{DMODE}})}{1.75 V}$$

where  $t_{\mbox{DMODE}}$  is the desired delay if the level shifter is not used to connect CTL to GND.

#### **VCOM Buffer**

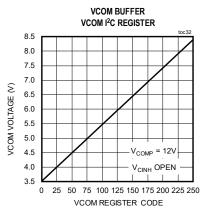

The VCOM buffer is enabled when AVDD crosses its power-good threshold. The VCOM positive supply is  $V_{COMP}$ , which is normally externally connected to the AVDD output, while its negative supply is ground. The output voltage is set by default to half of  $V_{COMP}$  through two 1000k $\Omega$  internal resistors. The VCOM buffer can be controlled either by driving the VCINH pin or using the internal DAC that is written to through the serial interface. When driving the VCINH pin, the source impedance or the resistance of the external resistor-divider should be much lower than 500k $\Omega$ . In DAC mode, an 8-bit value is written through I<sup>2</sup>C, which sets the VCOM output voltage in a nominal range of ±2.5V around AVDD/2. Table 2 shows

the correspondence between the DAC value written and the VCOM output voltage. The VCOM output can source or sink a current up to a peak of 130mA. The LCD backplane consists of a distributed series capacitance and resistance, a load that can be easily driven by the buffer. In a short-circuit condition, the power dissipation of the VCOM buffer can lead to complete thermal shutdown of the IC.

The VCOM buffer should be used with an external  $1\mu F$  ceramic capacitor connected from its output to GND.

A VCOM buffer fault is detected if the voltage difference between VCINH and the VCOM output pin is greater than 250mV. The VCOM fault detection is filtered internally and a VCOM buffer fault is latched. To clear a fault, write a 0 to the corresponding fault bit. In stand-alone mode, toggle the ENP pin or power down the device and then power it on again.

| CTL  | MODE | GATES OUTPUT                               | CMODE<br>DISCHARGE |

|------|------|--------------------------------------------|--------------------|

| Low  | High | GATES shorted to DRN using internal device | _                  |

| High | High | GATES shorted to SRC using internal device |                    |

| Low  | Low  | GATES shorted to DRN using internal device | Off                |

| High | Low  | GATES shorted to SRC using internal device | On                 |

### **Table 1. Gate-Shading Operating Modes**

#### Table 2. VCOM DAC Values

| DAC VALUE | NOMINAL VCOM OUTPUT<br>VOLTAGE WITH V <sub>AVDD</sub> = 12V |

|-----------|-------------------------------------------------------------|

| 0xFF      | 8.5V                                                        |

| 0xFE      | 8.5V                                                        |

|           |                                                             |

| 0x80      | 6.02V                                                       |

| 0x7F      | 6V                                                          |

| 0x7E      | 5.98V                                                       |

|           |                                                             |

| 0x01      | 3.52V                                                       |

| 0x00      | 3.5V                                                        |

## Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

### **FLTB Output**

The FLTB output pin is an active-low, open-drain output that can be used to signal various device faults (for operation in stand-alone mode, see the Stand-Alone Mode section). When the I<sup>2</sup>C interface is used, the FLTB output can flag any or all of the following conditions:

- Overtemperature fault

- Overcurrent on AVDD •

- Undervoltage on HVINP, VGON, or VGOFF

- Overvoltage on HVINP, VGON, or VGOFF •

- VCOM overvoltage or undervoltage

Some of the above conditions can be masked from causing FLTB to go low by using the corresponding mask bit in the Fault Mask 1 (0x08) and Fault Mask 2 (0x09) registers.

#### **Stand-Alone Mode**

The IC can be used either in stand-alone mode (when there is no local microcontroller), or in I<sup>2</sup>C mode. In standalone mode, the SEQ pin sets the sequence according to Table 3.

The ENP pin (active high) is used to turn on or off the complete device. In stand-alone mode, the open-drain FLTB output is high when there is no detected fault. When a fault is detected, the FLTB pin outputs a signal with a duty cycle that indicates what type of fault has been detected. This is summarized in Table 4.

### I<sup>2</sup>C Serial Interface

The IC contains an I<sup>2</sup>C serial interface and acts as a slave device. The basic unit of data transfer is 8 bits. To select I<sup>2</sup>C mode, connect the SEQ pin to GND. The state of the SEQ pin is sampled when the INA voltage exceeds approximately 2V and the status is latched.

Control of the power-up sequence through I<sup>2</sup>C can be performed in two ways, manual or automatic. In manual mode, the I<sup>2</sup>C host enables the outputs individually using the bits in the Regulator Control register (0x02). If a fault is detected in manual mode, the faulty output is disabled after the corresponding deglitch time and no other action is performed. Retry is disabled in manual mode.

The bits in Fault registers 0x0A and 0x0B can be cleared by writing a 0 to the corresponding position in the register. If the values of the other bits are retained, a 1 should be written to them. (e.g., if the vgon ov bit is cleared in register 0x0A, 0x77 should be written to the register). In this manner, only bit 3 is cleared, and the other bits are left unchanged.

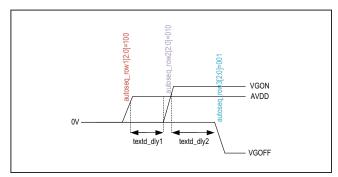

In automatic mode, the sequence is preset using the autoseq\_row1-autoseq\_row3 and textd\_dly1, textd\_dly2 bits, and executed using the autoseq ctrl bit. See the Autosequencing Mode section for further details.

2nd

VGOFF

VGON

#### **POWER-ON SEQUENCING POWER-OFF SEQUENCING** NOMINAL SEQ **PIN VOLTAGE** 1st 2nd 3rd 1st GND 12C CONTROL

VGOFF

VGON

# Table 4. FLTB Output Duty Cycle

AVDD

AVDD

Table 3. Output Sequencing

INA/2

INA

| FLTB DUTY CYCLE   | ERROR CONDITION     |  |  |  |  |

|-------------------|---------------------|--|--|--|--|

| Continuously high | No error            |  |  |  |  |

| 75%               | VGON or VGOFF fault |  |  |  |  |

| 50%               | HVINP fault         |  |  |  |  |

| 25%               | AVDD fault          |  |  |  |  |

| 1.5%              | Thermal shutdown    |  |  |  |  |

VGON

VGOFF

VGON

VGOFF

3rd

AVDD

AVDD

# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

### I<sup>2</sup>C Protocol

The IC's Slave ID is chosen by connecting the ADD pin to either GND or INA (see <u>Table 5</u>). A master device communicates with the IC by transmitting the correct Slave ID followed by the register address and data word. Each transmit sequence is framed by a START (S) or Repeated START (Sr) condition and a STOP (P) condition. Each word transmitted over the bus is 8 bits long and is always followed by an acknowledge clock pulse.

The IC's SDA line operates as both an input and an open-drain output. A pullup resistor greater than  $500\Omega$  is required on the SDA bus, or the resistor has to be selected as a function of bus capacitance, such that the rise time on the bus is not greater than 120ns per the I<sup>2</sup>C bus specification. The IC's SCL line operates as an input only. A pullup resistor greater than  $500\Omega$  is required on SCL if there are multiple masters on the bus, or if the master in a single-master system has an open-drain SCL output. In general, for the SCL line resistor selection, the same recommendations as the SDA line apply. Series resistors in line with SDA and SCL are optional. The SCL and SDA inputs suppress noise spikes to ensure proper device operation even on a noisy bus.

#### Individual Output Control Through I<sup>2</sup>C

Using the bits in the Regulator Control register (0x02), all outputs can be controlled individually by the local host microcontroller. When using this mode of operation, a fault on any output is signaled by the FLTB output pin (if not masked) and the fault bits. The output with the fault remains active until the microcontroller intervenes.

When using the individual control bits, the boost converter must always be enabled first and disabled last in the sequence.

#### Autosequencing Mode

In autosequencing mode, a complete sequence is configured using the autoseq\_row1-3[2:0] and textd\_dly1-2 bits and then executed by setting the autoseq\_ctrl bit. To use autosequencing, set the en\_autoseq bit in the Configurations register (0x01) to 1 and then configure the desired sequence using the autoseq\_row1-autoseq\_row3 bits in the Auto Sequencing ctrl1 (0x04) and Auto Sequencing ctrl2 (0x05) registers. The 3 bits of autoseq\_row1 correspond to the AVDD output and each bit represents one of three time slots. To enable AVDD during the first time slot, set autoseq\_row1 to 100. To enable AVDD during the second time slot, set autoseq\_row1 to 010, etc. In an analogous fashion, autoseq\_row2 sets the VGON time slot and autoseq\_row3 sets the VGOFF time slot.

The delays between each of the time slots are configured using the textd\_dly1 and textd\_dly2 settings.

When the complete configuration is set, the sequence is executed automatically by setting autoseq\_ctrl in the Regulator Control register (0x02) to 1. The corresponding power-off uence can be performed by setting autoseq\_ctrl to 0. If a fault occurs in automatic mode, the faulty output is turned off and the other outputs are turned off in the set order. If retry is enabled, a retry is attempted after the appropriate delay.

**Note:** If the manual control bits have been used to enable one or more of the outputs, automatic sequencing behaves differently: it starts immediately when the en\_autoseq bit is set.

Figure 1. Sample Sequence

| ADD PIN    |    |    | DEV | WRITE | READ |    |    |         |         |

|------------|----|----|-----|-------|------|----|----|---------|---------|

| CONNECTION | A6 | A5 | A4  | A3    | A2   | A1 | A0 | ADDRESS | ADDRESS |

| GND        | 0  | 1  | 0   | 0     | 0    | 0  | 0  | 0x40    | 0x41    |

| INA        | 0  | 1  | 0   | 1     | 0    | 0  | 0  | 0x50    | 0x51    |

### Table 5. I<sup>2</sup>C Slave Addresses

# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

## **Register Map**

| ADDRESS | NAME                                           | MSB (7)             | 6                       | 5                 | 4                | 3                | 2                      | 1                 | LSB (0)           |  |

|---------|------------------------------------------------|---------------------|-------------------------|-------------------|------------------|------------------|------------------------|-------------------|-------------------|--|

| bank 0  |                                                |                     |                         |                   |                  |                  | •                      |                   |                   |  |

| 0x00    | Device Id[7:0]                                 |                     | rev_id                  | [7:4]             |                  | dev_id[3:0]      |                        |                   |                   |  |

| 0x01    | Configurations[7:0]                            | fault_<br>latch_dis | en_auto-<br>seq         | tretry            | /[5:4]           | tfaul            | t[3:2]                 | dis_ss            | swfrq             |  |

| 0x02    | Regulator control[7:0]                         | _                   | auto-<br>seq_ctrl       | dis_vcom          | dis_gs           | en_vgoff         | en_vgon                | en_avdd           | en_bst            |  |

| 0x03    | Regulator power<br>status[7:0]                 | —                   |                         | vcom_on           | gs_on            | vgoff_on         | vgon_on                | avdd_on           | bst_on            |  |

| 0x04    | Auto sequencing<br>ctrl1[7:0]                  | —                   | _                       | autoseq_row2[5:3] |                  |                  | aut                    | autoseq_row1[2:0] |                   |  |

| 0x05    | Auto sequencing<br>ctrl2[7:0]                  | —                   | textd_dly2[6:5] textd_d |                   |                  | lly1[4:3] a      |                        | toseq_row3[2:0]   |                   |  |

| 0x06    | VCOM voltage[7:0]                              |                     |                         |                   | vcom_d           | ac[7:0]          |                        |                   |                   |  |

| 0x07    | UNUSED - do not write<br>to this register[7:0] | _                   | _                       | _                 | _                | _                | _                      | _                 | _                 |  |

| 0x08    | Fault mask 1[7:0]                              | _                   | vgoff_uv_<br>mask       | vgoff_<br>ov_mask | vgon_<br>uv_mask | vgon_<br>ov_mask | avdd_<br>ovld_<br>mask | hvinp_<br>uv_mask | hvinp_<br>ov_mask |  |

| 0x09    | Fault mask 2[7:0]                              | _                   | _                       |                   |                  | vcom_<br>ov_mask |                        |                   | _                 |  |

| 0x0A    | Fault register 1[7:0]                          | _                   | vgoff_uv                | vgoff_ov          | vgon_uv          | vgon_ov          | avdd_<br>ovld          | hvinp_uv          | hvinp_ov          |  |

| 0x0B    | Fault register 2[7:0]                          | —                   | —                       | —                 | vcom_uv          | vcom_ov          | —                      | th_shdn           | hw_rst            |  |

### Device Id (0x00)

Register to identify the device type and the revision number.

| BIT         | 7 | 6     | 5      | 4 | 3           | 2    | 1    | 0 |  |

|-------------|---|-------|--------|---|-------------|------|------|---|--|

| Field       |   | rev_i | d[7:4] |   | dev_id[3:0] |      |      |   |  |

| Reset       |   | 0)    | <0     |   | 0x9         |      |      |   |  |

| Access Type |   | Read  | Only   |   |             | Read | Only |   |  |

| BITFIELD | BITS | DESCRIPTION                       |  |  |  |  |

|----------|------|-----------------------------------|--|--|--|--|

| rev_id   | 7:4  | Revision ID. 0 = revision 1, etc. |  |  |  |  |

| dev_id   | 3:0  | Device ID. Reads 0x9.             |  |  |  |  |

# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

### Configurations (0x01)

Miscellaneous configurations needed for part operations.

| BIT         | 7                   | 6           | 5           | 4           | 3           | 2           | 1      | 0           |

|-------------|---------------------|-------------|-------------|-------------|-------------|-------------|--------|-------------|

| Field       | fault_latch_<br>dis | en_autoseq  | tretry[5:4] |             | tfault[3:2] |             | dis_ss | swfrq       |

| Reset       | 0x0                 | 0x0         | 0x2         |             | 0x1         |             | 0x0    | 0x0         |

| Access Type | Write, Read         | Write, Read | Write,      | Write, Read |             | Write, Read |        | Write, Read |

| BITFIELD            | BITS | DESCRIPTION                                                                                                                                                           | DECODE                                                                                                                                                               |  |  |

|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| fault_latch_<br>dis | 7    | Fault register control. When set to 0, the fault register bits are latched.                                                                                           | 0x0: Fault register bits are latched fault flags<br>0x1: Fault register bits are fault status bits (no<br>latching)                                                  |  |  |

| en_autoseq          | 6    | When set to 1, this bit enables the automatic sequencing feature.                                                                                                     | 0x0: Automatic sequencing is disabled<br>0x1: Automatic sequencing is enabled                                                                                        |  |  |

| tretry              | 5:4  | If retry is enabled (set to any value other than 0x0), then this is the time that elapses before a new power-on is attempted after turn-off due to a regulator fault. | 0x0: Retry is disabled<br>0x1: Retry to power on regulator after 0.95s<br>0x2: Retry to power on regulator after 1.9s<br>0x3: Retry to power on regulator after 3.8s |  |  |

| tfault              | 3:2  | Fault-deglitch duration. This is the time that a regulator fault must be continuously present before the fault is considered valid.                                   | 0x0: 30ms<br>0x1: 60ms<br>0x2: 120ms<br>0x3: 250ms                                                                                                                   |  |  |

| dis_ss              | 1    | Boost spread-spectrum-disable control bit.                                                                                                                            | 0x0: Boost spread spectrum enabled<br>0x1: Boost spread spectrum disabled                                                                                            |  |  |

| swfrq               | 0    | Boost converter switching-frequency selection.                                                                                                                        | 0x0: 2.2MHz boost switching frequency<br>0x1: 440kHz boost switching frequency                                                                                       |  |  |

# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

### **Regulator control (0x02)**

Direct control of regulators enable. This register can be used on  $I^2C$  variant when "en\_autoseq = 0" to control the manual sequencing of regulators (i.e. regulators' sequencing is completely controlled by host software). Note that some controls are implemented in this register. As an example, the enable of any regulator is not allowed unless "en\_bst" has been enabled and ready (bst\_on = 1).

| BIT         | 7 | 6            | 5           | 4           | 3           | 2           | 1           | 0           |

|-------------|---|--------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Field       | — | autoseq_ctrl | dis_vcom    | dis_gs      | en_vgoff    | en_vgon     | en_avdd     | en_bst      |

| Reset       | _ | 0x0          | 0x0         | 0x0         | 0x0         | 0x0         | 0x0         | 0x0         |

| Access Type | _ | Write, Read  | Write, Read | Write, Read | Write, Read | Write, Read | Write, Read | Write, Read |

| BITFIELD     | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DECODE                                                                                                                                                                                                                                        |  |  |

|--------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| autoseq_ctrl | 6    | Controls the automatic sequencer. If the auto-<br>matic sequencer is enabled, setting this bit to 1<br>starts the power-on sequence as programmed.<br>Deasserting this bit to 0 starts the power-down<br>sequence. Note that the sequence program-<br>ming cannot be altered while the sequence<br>is ongoing. Once the current sequence is<br>completed, sequence programming is again<br>enabled. If the en_autoseq bit is set to 0, this<br>bit has no effect. | 0x0: If regulators are off, keep them as they are. If<br>regulators are on, start the power off sequence and<br>keep them off<br>0x1: If regulators are off start the power on se-<br>quence and keep them on. Else keep them as they<br>are. |  |  |

| dis_vcom     | 5    | VCOM buffer disable. By default, the VCOM buffer is enabled when the AVDD crosses its power-good threshold.                                                                                                                                                                                                                                                                                                                                                       | 0x0: VCOM buffer is enabled<br>0x1: VCOM buffer has been disabled                                                                                                                                                                             |  |  |

| dis_gs       | 4    | Gate-shading disable. By default, the gate-<br>shading block is enabled when soft-start for all<br>regulators is completed and when the DEL pin<br>exceeds its enable threshold.                                                                                                                                                                                                                                                                                  | 0x0: Gate shading is enabled<br>0x1: Gate shading has been disabled                                                                                                                                                                           |  |  |

| en_vgoff     | 3    | Negative charge-pump enable.                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x0: Negative charge pump is disabled<br>0x1: Negative charge pump has been enabled                                                                                                                                                           |  |  |

| en_vgon      | 2    | Positive charge-pump enable.                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x0: Positive charge pump is disabled<br>0x1: Positive charge pump has been enabled                                                                                                                                                           |  |  |

| en_avdd      | 1    | Control bit for the switch between HVINP and AVDD. Note that any attempt to set this bit to 1 fails if the field "bst_ok" is 0.                                                                                                                                                                                                                                                                                                                                   | 0x0: Switch beween HVINP and AVDD is open<br>0x1: Switch beween HVINP and AVDD is closed                                                                                                                                                      |  |  |

| en_bst       | 0    | Boost converter enable.                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x0: Buck is disabled<br>0x1: Buck is enabled                                                                                                                                                                                                 |  |  |

# Automotive 3-Channel Display Bias IC with VCOM Buffer, Level Shifter, and I<sup>2</sup>C Interface

### Regulator power status (0x03)

Status of the regulators. Each bit set to 1 means that related regulator is powered on (i.e. it has been enabled, the transient has completed and it's active ready).