# Capacitance-Digital-Converter LSI for Electrostatic Capacitive Touch Sensors

The LC717A30UJ is a high performance, low cost, and highly usable capacitance converter for electrostatic capacitive touch and proximity sensors.

8 capacitance-sensing input channels ideal for use in any end products that needs an array of switches. The LC717A30UJ facilitates a short system development time through its automatic calibration function and minimal external components. The detection result (ON/OFF) for each sensor is read out by the serial interface (I<sup>2</sup>C or SPI).

#### **Features**

- Differential Capacitive Detection Using Mutual Capacitance

- Operates with Small to Large Capacitance Sensor Input Pads

- Capacitance Detection Down to Femto-Farad Level

- Measurement Time 16 ms for 8 Sensors

- Minimal External Components

- Selectable Interface: I<sup>2</sup>C or SPI

- Current Consumption: 0.8 mA (V<sub>DD</sub> = 5.5 V)

- Supply Voltage: 2.6 V to 5.5 V

- AEC-Q100 Qualified and PPAP Capable

#### **Typical Applications**

- Automotive: Smart Key, Control Switches, Car Audio, Proximity

- Consumer: Home Appliance, White Goods, Induction Cooking

- Industrial: Security Lock

- Computing: PC Peripherals, Audio Visual Equipment

- Lighting: Remote Control Switches

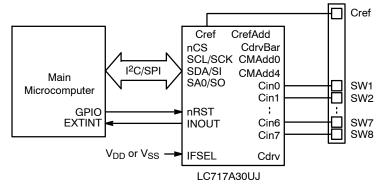

Figure 1. Application Schematic 1

# ON Semiconductor®

www.onsemi.com

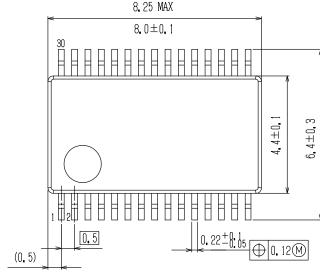

SSOP30 (225 mil) CASE 565AZ

# **MARKING DIAGRAM**

XXXXX = Specific Device Code

Y = Year M = Month

DDD = Additional Traceability Data

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 9 of this data sheet.

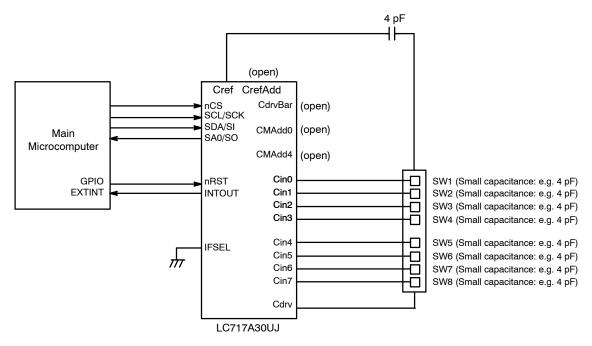

8 small capacitance sensors channels and 4-wire SPI interface.

Figure 2. Application Schematic 2

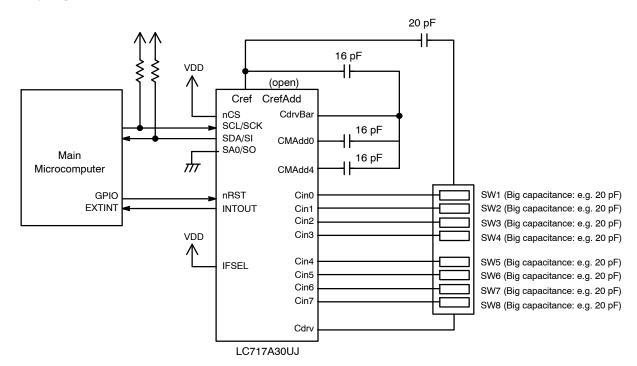

8 Large capacitance sensors and I<sup>2</sup>C interface.

Figure 3. Application Schematic 3

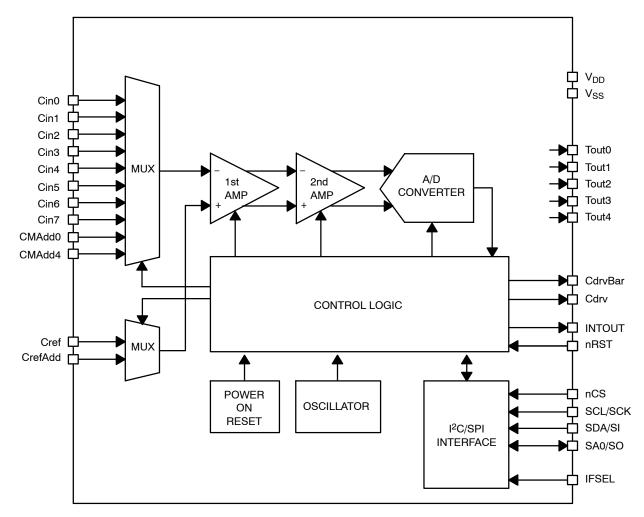

# **BLOCK DIAGRAM**

The LC717A30UJ is a capacitance-digital converter LSI that can detect capacitance at the femto farad level. It consists a multiplexer that selects the input channels, a two-stage amplifier that detects the changes in the

capacitance and outputs analog-amplitude values, an A/D converter, a system clock, a power-on reset circuit, control logic and interface, I<sup>2</sup>C bus or SPI.

Figure 4. Simplified Block Diagram

# **PIN ASSIGNMENT**

Figure 5. Pin Assignment (Top View)

**Table 1. PIN ASSIGNMENT**

| Pin No. | Pin Name        | I/O   | Description                                                                                                                                                                                                           |

|---------|-----------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | $V_{DD}$        | Power | Power supply (+2.6 V to +5.5 V) (Note 1)                                                                                                                                                                              |

| 2       | V <sub>SS</sub> | Power | Ground (Notes 1, 2)                                                                                                                                                                                                   |

| 3       | Non Connect     | _     | Connect to Ground                                                                                                                                                                                                     |

| 27      | Cin0            | I/O   | Sensor inputs.                                                                                                                                                                                                        |

| 28      | Cin1            | I/O   | Cin0 to Cin7 are connected to the inverting input of the 1st amplifier through the multiplexer.                                                                                                                       |

| 4       | Cin2            | I/O   | All unused input pins must remain open.                                                                                                                                                                               |

| 5       | Cin3            | I/O   | Cdrv and Cin printed circuit board patterns should be close to each other as they are capacitively coupled.                                                                                                           |

| 8       | Cin4            | I/O   | capacitively coupled.                                                                                                                                                                                                 |

| 9       | Cin5            | I/O   |                                                                                                                                                                                                                       |

| 12      | Cin6            | I/O   |                                                                                                                                                                                                                       |

| 13      | Cin7            | I/O   |                                                                                                                                                                                                                       |

| 6       | Tout0           | 0     | Test pin, must remain open                                                                                                                                                                                            |

| 7       | Tout1           | 0     | Test pin, must remain open                                                                                                                                                                                            |

| 10      | CMAdd4          | I/O   | Offset capacitance input pin for the sensor inputs 4 to 7.  When using large sensor pads with high capacitance, additional capacitance is added between CMAdd4 and CdrvBar. See Figure 3.  Remain open if not in use. |

| 11      | CMAdd0          | I/O   | Offset capacitance input pin for the sensor inputs 0 to 3.  When using large sensor pads with high capacitance, additional capacitance is added between CMAdd4 and CdrvBar. See Figure 3.  Remain open if not in use. |

| 14      | Tout2           | 0     | Test pin, must remain open                                                                                                                                                                                            |

| 15      | Cref            | I/O   | Reference capacitance input pins. See Figures 2 and 3.  When using large sensor pads with high capacitance, additional capacitance maybe                                                                              |

| 17      | CrefAdd         | I/O   | added for Cref. See Figure 3.  Remain open if not in use.                                                                                                                                                             |

Table 1. PIN ASSIGNMENT (continued)

| Pin No. | Pin Name    | I/O | Description                                                                                                                                                                                                              |

|---------|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16      | CdrvBar     | 0   | Capacitance sensors drive signal inversion output.  When using large sensor pads with high capacitance, additional capacitance is added between CMAdd0 and CMAdd4 and CdrvBar. See Figure 3.  Remain open if not in use. |

| 18      | Cdrv        | 0   | Capacitance sensors drive output.  Cdrv and Cin printed circuit board patterns should be close to each other as they are capacitively coupled.                                                                           |

| 19      | INTOUT      | 0   | Interrupt output pin. (Active high)<br>Remain open if not in use                                                                                                                                                         |

| 20      | IFSEL       | I   | Interface Select. IFSEL = "Low" (V <sub>SS</sub> ): SPI mode IFSEL = "High" (V <sub>DD</sub> ): I <sup>2</sup> C mode                                                                                                    |

| 21      | SCL/SCK     | I   | I <sup>2</sup> C = SCL clock input<br>SPI = SCK clock input                                                                                                                                                              |

| 22      | SDA/SI      | I/O | I <sup>2</sup> C = SDA data input/output<br>SPI = SI data input                                                                                                                                                          |

| 23      | SA0/SO      | I/O | I <sup>2</sup> C = SA0 slave address selection input<br>SPI = SO data output                                                                                                                                             |

| 24      | nCS         | I   | I <sup>2</sup> C = "High" (V <sub>DD</sub> )<br>SPI = nCS chip select inversion input                                                                                                                                    |

| 25      | nRST        | I   | Reset signal inversion input pin. nRST = "Low" (V <sub>SS</sub> ), in reset state Cin0 to Cin7, CMAdd0, CMAdd4, Cref, CrefAdd, CdrvBar and Tout0 to Tout4 are "Hi–Z"                                                     |

| 26      | Non Connect | =   | Connect to Ground                                                                                                                                                                                                        |

| 29      | Tout3       | 0   | Test pin, must remain open                                                                                                                                                                                               |

| 30      | Tout4       | 0   | Test pin, must remain open                                                                                                                                                                                               |

$<sup>1. \ \</sup> For noise de-coupling place a high-valued capacitor and a low-valued capacitor in parallel between V_{DD} and V_{SS}. \ The small-valued capacitor,$ at least 0.1 µF, should be mounted near the LSI.

2. When V<sub>SS</sub> terminal is not grounded, in battery-powered mobile equipment, detection sensitivity may be degraded.

# **Table 2. PIN FUNCTIONS**

| Pin No. | Pin Name        | I/O   | Pin Functions                                                        | Pin Type                 |

|---------|-----------------|-------|----------------------------------------------------------------------|--------------------------|

| 1       | V <sub>DD</sub> | Power | Power supply (+2.6 V to +5.5 V)                                      |                          |

| 2       | V <sub>SS</sub> | Power | Ground                                                               |                          |

| 27      | Cin0            | I/O   | Capacitance sensor input 0                                           |                          |

| 28      | Cin1            | I/O   | Capacitance sensor input 1                                           | V <sub>DD</sub> A        |

| 4       | Cin2            | I/O   | Capacitance sensor input 2                                           | AMP                      |

| 5       | Cin3            | I/O   | Capacitance sensor input 3                                           | 1_ T R 🖟 📐               |

| 8       | Cin4            | I/O   | Capacitance sensor input 4                                           |                          |

| 9       | Cin5            | I/O   | Capacitance sensor input 5                                           | 1 🛊 💹 –                  |

| 12      | Cin6            | I/O   | Capacitance sensor input 6                                           | V <sub>SS</sub> # Buffer |

| 13      | Cin7            | I/O   | Capacitance sensor input 7                                           | 1                        |

| 10      | CMAdd4          | I/O   | Additional offset capacitance input pin for the sensor inputs 4 to 7 | 1                        |

| 11      | CMAdd0          | I/O   | Additional offset capacitance input pin for the sensor inputs 0 to 3 | 1                        |

| 15      | Cref            | I/O   | Reference capacitance input                                          | 1                        |

| 17      | CrefAdd         | I/O   | Additional Reference capacitance input                               | 1                        |

Table 2. PIN FUNCTIONS (continued)

| Pin No. | Pin Name | I/O | Pin Functions                                                      | Pin Type                            |

|---------|----------|-----|--------------------------------------------------------------------|-------------------------------------|

| 6       | Tout0    | 0   | Output for tests                                                   |                                     |

| 7       | Tout1    | 0   | Output for tests                                                   | - V <sub>DD</sub> ∆                 |

| 14      | Tout2    | 0   | Output for tests                                                   | 1 🛦                                 |

| 29      | Tout3    | 0   | Output for tests                                                   |                                     |

| 30      | Tout4    | 0   | Output for tests                                                   | Buffer                              |

| 16      | CdrvBar  | 0   | Capacitance sensors drive signal inversion output                  | V <sub>ss</sub> "                   |

| 18      | Cdrv     | 0   | Capacitance sensors drive output                                   |                                     |

| 19      | INTOUT   | 0   | Interrupt output                                                   | V <sub>DD</sub> A Buffer            |

| 20      | IFSEL    | I   | Switching control input of the serial data communication interface | V <sub>SS</sub> //                  |

| 21      | SCL/SCK  | 1   | SCL clock input (I <sup>2</sup> C)                                 | <del> </del>                        |

| 21      | Jozack   |     |                                                                    | Schmitt R                           |

|         |          | Ι   | SCK clock input (SPI)                                              |                                     |

| 24      | nCS      | Ι   | nCS chip select inversion input (SPI)                              | <b> </b> ★                          |

| 25      | nRST     | I   | External reset signal inversion input                              | V <sub>SS</sub> m                   |

| 22      | SDA/SI   | I/O | SDA data input/output (I <sup>2</sup> C)                           | V <sub>DD</sub> $\triangle$ Schmitt |

|         |          | I   | SI data input (SPI)                                                | O.D.                                |

| 23      | SA0/SO   | I   | SA0 slave address selection input (I <sup>2</sup> C)               | V <sub>DD</sub> A Schmitt R         |

|         |          | 0   | SO data output (SPI)                                               | V <sub>SS</sub> Buffer              |

#### ABSOLUTE MAXIMUM RATINGS (V<sub>SS</sub> = 0 V, T<sub>A</sub> = +25°C)

| Symbol            | Parameter                              | Value                        | Unit |

|-------------------|----------------------------------------|------------------------------|------|

| V <sub>DD</sub>   | Supply Voltage Range                   | -0.3 to +6.5                 | V    |

| V <sub>IN</sub>   | Input Voltage Range (Note 3)           | -0.3 to V <sub>DD</sub> +0.3 | V    |

| V <sub>OUT</sub>  | Output Voltage Range (Note 4)          | -0.3 to V <sub>DD</sub> +0.3 | V    |

| I <sub>OP</sub>   | Peak Output Current Range (Notes 4, 5) | -8.0 to +8.0                 | mA   |

| I <sub>OA</sub>   | Total Outputs Current Range (Note 6)   | -40 to +40                   | mA   |

| P <sub>dmax</sub> | Maximum Power Dissipation (Note 7)     | 160                          | mW   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 3. Apply to Cin0 to Cin7, CMAdd0, CMAdd4, Cref, CrefAdd ,SCL/SCK ,SDA/SI ,SA0, nCS, nRST, IFSEL.

- 4. Apply to Cdrv, CdrvBar, SDA, SO, INTOUT, Tout0 to Tout4.

- 5. Total value with duty cycle under 25%.

- 6. Limited to one pin, with duty cycle under 50%.

- 7.  $T_A = 105$ °C, Single-layer glass epoxy board (76.1 × 114.3 × 1.6 mm).

# RECOMMENDED OPERATING CONDITIONS ( $V_{SS} = 0 V$ )

| Symbol          | Parameter                               | Min                 | Max                 | Unit |

|-----------------|-----------------------------------------|---------------------|---------------------|------|

| $V_{DD}$        | Operating Supply Voltage Range (Note 8) | 2.6                 | 5.5                 | V    |

| V <sub>IH</sub> | Input High-level Voltage Range (Note 9) | 0.8 V <sub>DD</sub> | $V_{DD}$            | V    |

| $V_{IL}$        | Input Low-level Voltage Range (Note 9)  | 0                   | 0.2 V <sub>DD</sub> | V    |

| T <sub>A</sub>  | Ambient Temperature Range               | -40                 | 105                 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

9. Apply to SCL/SCK ,SDA/SI ,SA0, nCS, nRST, IFSEL.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 2.6 \text{ to } 5.5 \text{ V}, V_{SS} = 0 \text{ V}, T_{A} = -40 \text{ to } + 105^{\circ}\text{C}, \text{ Unless otherwise specified, the Cdrv drive frequency is } f_{CDRV} = 121 \text{ kHz.})$

| Symbol            | Parameter                                    | Condition                                                                                                | Min                 | Тур  | Max                 | Unit |

|-------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------|------|---------------------|------|

| COMMON            |                                              |                                                                                                          |                     |      |                     |      |

| V <sub>OH1</sub>  | Output High-level Voltage (Note 10)          | $I_O = -1.5 \text{ mA}, V_{DD} = 2.6 \text{ to } 3.6 \text{ V}$                                          | 0.8 V <sub>DD</sub> | _    | -                   | ٧    |

| V <sub>OH2</sub>  | 7                                            | $I_O = -3.0 \text{ mA}, V_{DD} = 3.6 \text{ to } 5.5 \text{ V}$                                          | 0.8 V <sub>DD</sub> | _    | -                   | ٧    |

| V <sub>OL1</sub>  | Output Low-level Voltage (Note 10)           | I <sub>O</sub> = +1.5 mA, V <sub>DD</sub> = 2.6 to 3.6 V                                                 | -                   | -    | 0.2 V <sub>DD</sub> | V    |

| V <sub>OL2</sub>  | 7                                            | I <sub>O</sub> = +3.0 mA, V <sub>DD</sub> = 3.6 to 5.5 V                                                 | -                   | _    | 0.2 V <sub>DD</sub> | ٧    |

| V <sub>OL3</sub>  | Tout0 to Tout4 pins Output Low-level Voltage | I <sub>O</sub> = +1.5 mA                                                                                 | -                   | -    | 0.2 V <sub>DD</sub> | V    |

| V <sub>OL4</sub>  | SDA pin Output Low-level Voltage             | I <sub>O</sub> = +3.0 mA                                                                                 | -                   | _    | 0.4                 | ٧    |

| I <sub>IH</sub>   | Input High-level Current (Note 11)           | $V_I = V_{DD}$                                                                                           | -                   | -    | 1.0                 | μΑ   |

| I <sub>IL</sub>   | Input Low-level Current (Note 11)            | V <sub>I</sub> = V <sub>SS</sub>                                                                         | -1.0                | -    | -                   | μΑ   |

| I <sub>OFF</sub>  | Output Off Leakage Current (Note 12)         | $V_I = V_{DD}$ or $V_I = V_{SS}$                                                                         | -1.0                | -    | 1.0                 | μΑ   |

| I <sub>DD1</sub>  | Current Consumption                          | Initial setting, Long interval operation,<br>Sensor pins are open (Note 13),<br>V <sub>DD</sub> = 5.5 V  | _                   | 0.8  | 2.2                 | mA   |

| I <sub>DD2</sub>  |                                              | Initial setting, Short interval operation,<br>Sensor pins are open (Note 13),<br>V <sub>DD</sub> = 5.5 V | _                   | 3.25 | 6.5                 | mA   |

| I <sub>STBY</sub> |                                              | Sleep mode (Sleep period)<br>Sensor pins are open (Note 13)                                              | -                   | 0.1  | 70                  | μΑ   |

For noise de-coupling place a high-valued capacitor and a low-valued capacitor in parallel between V<sub>DD</sub> and V<sub>SS</sub>. The small-valued capacitor, at least 0.1 μF, should be mounted near the LSI. In addition, it is recommended that the power supply ripple + noise is less than ±40 mV.

| Symbol                         | Parameter                                                     | Condition                                                                                | Min    | Тур    | Max      | Unit     |

|--------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------|--------|--------|----------|----------|

| APACITANC                      | E SENSOR FUNCTION                                             |                                                                                          |        |        |          |          |

| Cin <sub>SENSE</sub>           | Cin Detection Sensitivity                                     | Measurements conducted using the test mode in the LSI, Minimum gain setting              | 0.0476 | 0.068  | 0.0884   | LSB/ff   |

| I <sub>Cin</sub>               | Sensor Pin Leakage Current (Note 14)                          | $V_I = V_{DD}$ or $V_I = V_{SS}$                                                         | -      | ±25    | ±500     | nA       |

| f <sub>CDRV</sub>              | Cdrv Drive Frequency                                          | With 121 kHz setting                                                                     | 84.85  | 121.21 | 157.57   | kHz      |

| OWER-ON R                      | ESET FUNCTION                                                 |                                                                                          |        |        |          |          |

| t <sub>NRST</sub>              | nRST Minimum Pulse Width                                      |                                                                                          | 1.0    | -      | _        | μs       |

| t <sub>POR</sub>               | Power-on Reset Time                                           |                                                                                          | -      | -      | 20       | ms       |

| t <sub>POROP</sub>             | Power-on Reset Operation Condition:<br>Hold Time              |                                                                                          | 10     | -      | -        | ms       |

| V <sub>POROP</sub>             | Power-on Reset Operation Condition:<br>Input Voltage          |                                                                                          | -      | -      | 0.1      | V        |

| t <sub>VDD</sub>               | Power-on Reset Operation Condition:<br>Power Supply Rise Rate | 0 V to V <sub>DD</sub>                                                                   | 1.0    | ı      | =        | V/ms     |

| NTERVAL OP                     | ERATION TIMING                                                |                                                                                          |        |        |          |          |

| T <sub>LIVAL1</sub>            | Long Interval Time                                            | V <sub>DD</sub> = 2.6 to 4.5 V, Long interval mode (Long interval time is set to 101 ms) | 35     | 101    | 145      | ms       |

| T <sub>LIVAL2</sub>            |                                                               | V <sub>DD</sub> = 4.5 to 5.5 V, Long interval mode (Long interval time is set to 101 ms) | 40     | 101    | 125      | ms       |

| T <sub>SIVAL1</sub>            | Short Interval Time                                           | V <sub>DD</sub> = 2.6 to 4.5 V, Short interval mode (Short interval time is set to 5 ms) | 1.7    | 5      | 7.3      | ms       |

| T <sub>SIVAL2</sub>            |                                                               | V <sub>DD</sub> = 4.5 to 5.5 V, Short interval mode (Short interval time is set to 5 ms) | 1.9    | 5      | 6.3      | ms       |

| C COMPATIE                     | BLE BUS INTERFACE TIMING                                      |                                                                                          |        |        |          | •        |

| f <sub>SCL</sub>               | SCL Clock Frequency                                           | SCL                                                                                      | -      | -      | 400      | kHz      |

| t <sub>HD;</sub> sta           | START Condition Hold Time                                     | SCL, SDA                                                                                 | 0.6    | -      | _        | μs       |

| t <sub>LOW</sub>               | SCL Clock Low Period                                          | SCL                                                                                      | 1.3    | -      | _        | μs       |

| t <sub>HIGH</sub>              | SCL Clock High Period                                         | SCL                                                                                      | 0.6    | -      | _        | μs       |

| t <sub>SU; STA</sub>           | Repeated START Condition Setup Time                           | SCL, SDA                                                                                 | 0.6    | -      | -        | μs       |

| t <sub>HD; DAT</sub>           | Data Hold Time                                                | SCL, SDA                                                                                 | 0      | -      | 0.9      | μs       |

| t <sub>SU; DAT</sub>           | Data Setup Time                                               | SCL, SDA                                                                                 | 0.5    | -      | -        | μs       |

| t <sub>r</sub> /t <sub>f</sub> | SDA, SCL Rise/Fall Time                                       | SCL, SDA                                                                                 | -      | -      | 0.3      | μs       |

| t <sub>SU; STO</sub>           | STOP Condition Setup Time                                     | SCL, SDA                                                                                 | 0.6    | -      | _        | μs       |

| t <sub>BUF</sub>               | STOP-to-START Bus Release Time                                | SCL, SDA                                                                                 | 2.5    | -      | _        | μs       |

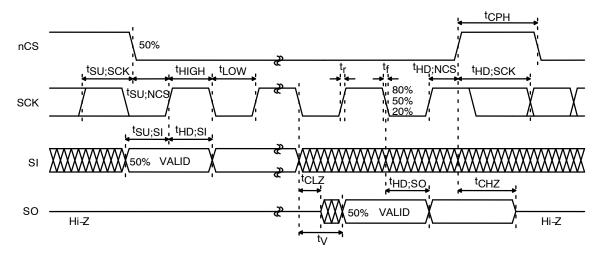

| PI INTERFAC                    | CE TIMING                                                     |                                                                                          |        |        |          |          |

| f <sub>SCK</sub>               | SCK Clock Frequency                                           | SCK                                                                                      | -      | -      | 5.0      | MHz      |

| t <sub>LOW</sub>               | SCK Clock Low Time                                            | SCK                                                                                      | 100    | -      | _        | ns       |

| t <sub>HIGH</sub>              | SCK Clock High Time                                           | SCK                                                                                      | 100    | -      | -        | ns       |

| t <sub>r</sub> /t <sub>f</sub> | Input Signal Rise/Fall Time                                   | nCS, SCK, SI                                                                             | -      | -      | 300      | ns       |

| t <sub>SU; NCS</sub>           | nCS Setup Time                                                | nCS, SCK                                                                                 | 200    | -      | -        | ns       |

| t <sub>SU; SCK</sub>           | SCK Clock Setup Time                                          | nCS, SCK                                                                                 | 100    | -      | -        | ns       |

| t <sub>SU; SI</sub>            | Data Setup Time                                               | SCK, SI                                                                                  | 100    | -      | -        | ns       |

| ,                              | Data Hold Time                                                | SCK, SI                                                                                  | 100    |        | <b>!</b> | <b>.</b> |

# **ELECTRICAL CHARACTERISTICS** (continued)

$(V_{DD} = 2.6 \text{ to } 5.5 \text{ V}, V_{SS} = 0 \text{ V}, T_{A} = -40 \text{ to} + 105^{\circ}\text{C}, \text{ Unless otherwise specified, the Cdrv drive frequency is } f_{CDRV} = 121 \text{ kHz.})$

| Symbol               | Parameter                                | Condition | Min | Тур | Max | Unit |

|----------------------|------------------------------------------|-----------|-----|-----|-----|------|

| SPI INTERFAC         | PI INTERFACE TIMING                      |           |     |     |     |      |

| t <sub>HD; NCS</sub> | nCS Hold Time                            | nCS, SCK  | 200 | -   | _   | ns   |

| t <sub>HD;SCK</sub>  | SCK Clock Hold Time                      | nCS, SCK  | 700 | -   | _   | ns   |

| t <sub>CPH</sub>     | nCS Standby Pulse Width                  | nCS       | 300 | -   | _   | ns   |

| t <sub>CHZ</sub>     | Output High Impedance Time from nCS      | nCS, SO   | -   | -   | 100 | ns   |

| t <sub>V</sub>       | Output Data Determination Time           | SCK, SO   | -   | -   | 100 | ns   |

| t <sub>HD; SO</sub>  | Output Data Hold Time                    | SCK, SO   | 0   | -   | _   | ns   |

| t <sub>CLZ</sub>     | Output Low Impedance Time from SCK Clock | SCK, SO   | 100 | _   | -   | ns   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

#### **Table 3. ORDERING INFORMATION**

| Device        | Package                                      | Shipping (Qty / Packing) <sup>†</sup> |

|---------------|----------------------------------------------|---------------------------------------|

| LC717A30UJ-AH | SSOP30 (225 mil)<br>(Pb-Free / Halogen Free) | 1000 / Tape & Reel                    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

<sup>10.</sup> Apply to Cdrv, CdrvBar, SO, INTOUT. 11. Apply to SCL/SCK, SDA/SI, SA0, nCS, nRST, IFSEL.

<sup>12.</sup> Apply to Cdrv, CdrvBar, SDA, SO.

<sup>13.</sup> Sensor pins (Cin0 to Cin7, CMAdd0, CMAdd4, Cref, CrefAdd) are open condition.

<sup>14.</sup> Apply to Cin0 to Cin7, CMAdd0, CMAdd4, Cref, CrefAdd.

#### **FUNCTIONAL DESCRIPTION**

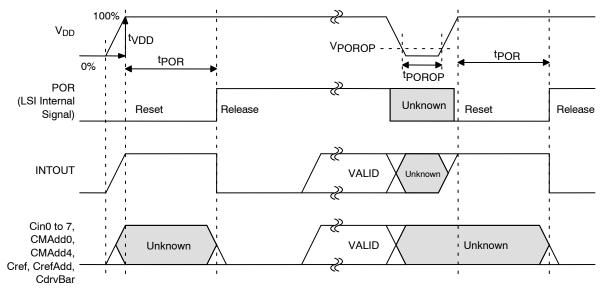

#### Power-on Reset (POR)

When power is turned on, power-on reset is enabled, it is released after power-on reset time,  $t_{POR}$ . Power-on reset operation condition; Power supply rise rate  $t_{VDD}$  must be at least 1.0 V/ms.

Since INTOUT pin changes from "High" to "Low" at the same time as reset release, it is possible to verify the timing of release of reset externally. During power-on reset, Cin0 to Cin7, CMAdd0, CMAdd4, Cref, CrefAdd, and CdrvBar are unknown.

Figure 6. Power-on Sequence by the Power-on Reset

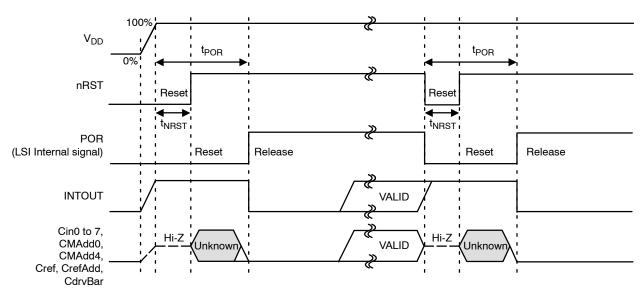

### **External Reset (nRST)**

Reset State nRST = "Low". Pins Cin0 to Cin7, CMAdd0, CMAdd4, Cref, CrefAdd and CdrvBar, are "Hi-Z" during reset state. The reset state is released after tpOR.

Since INTOUT pin changes from "High" to "Low" at the same time as the released of reset, it is possible to verify the timing of release of reset externally.

Figure 7. Power-on Sequence by the External Reset

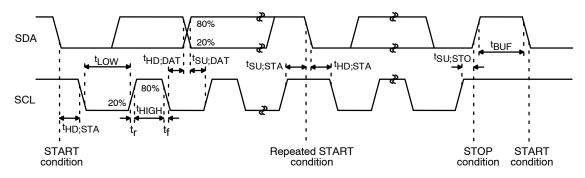

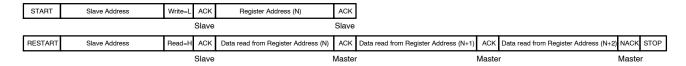

# I<sup>2</sup>C Data Timing

Figure 8. I<sup>2</sup>C Data Timing

#### I<sup>2</sup>C Communication Formats

#### **Write Format**

When using the Write format of I<sup>2</sup>C the data can be written into sequentially incremented addresses.

Figure 9. I<sup>2</sup>C Write Format

# **Read Format**

When using the Read format of I<sup>2</sup>C the data can be read from sequentially incremented addresses.

Figure 10. I<sup>2</sup>C Read Format

# I<sup>2</sup>C Slave Address

SA0 pin is used to select the slave address

Table 4. I<sup>2</sup>C SLAVE ADDRESS

| SA0 Pin Input | 7 bit Slave Address | Binary Notation   | 8 bit Slave Address |

|---------------|---------------------|-------------------|---------------------|

| Low           | 0x16                | 00101100b (Write) | 0x2C                |

|               |                     | 00101101b (Read)  | 0x2D                |

| High          | 0x17                | 00101110b (Write) | 0x2E                |

|               |                     | 00101111b (Read)  | 0x2F                |

# SPI Data Timing (Mode 0/Mode 3)

Figure 11. SPI Data Timing

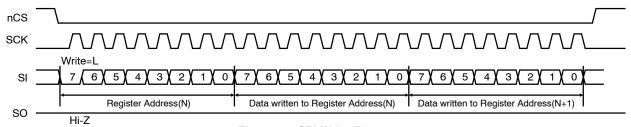

# SPI Write Format (Example of Mode 0)

When using the SPI Write format the data can be written into sequentially incremented addresses with preserving nCS = "L".

Figure 12. SPI Write Format

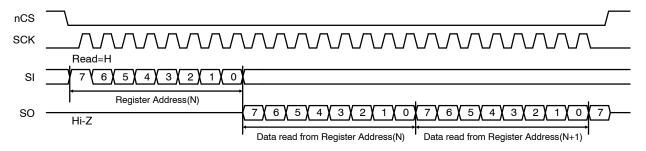

#### **SPI Read Format**

When using the SPI Read format the data can be read from sequentially incremented addresses with preserving nCS = "L".

Figure 13. SPI Read Format

I<sup>2</sup>C Bus is a trademark of Philips Corporation.

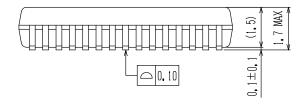

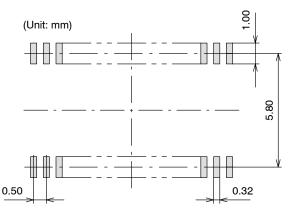

#### SSOP30 (225 mil) CASE 565AZ ISSUE A

**DATE 25 OCT 2013**

#### **SOLDERING FOOTPRINT\***

NOTE: The measurements are not to guarantee but for reference only.

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# GENERIC MARKING DIAGRAM\*

XXXXX = Specific Device Code Y = Year

M = Month

DDD = Additional Traceability Data

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

| DOCUMENT NUMBER: | 98AON80824E      | Electronic versions are uncontrolled except when accessed directly from the Document Repositor Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:     | SSOP30 (225 MIL) |                                                                                                                                                                                | PAGE 1 OF 1 |  |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

ON Semiconductor and (III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability. arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthnoized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com **TECHNICAL SUPPORT**

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910

ON Semiconductor Website: www.onsemi.com

North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

For additional information, please contact your local Sales Representative