# NSD7312 Brushed DC Motor Driver Single H-Bridge

Datasheet (EN) 1.4

### **Product Overview**

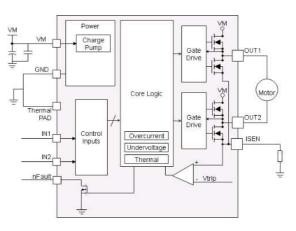

The device NSD7312 is a brushed-DC motor H-bridge driver for Automotive VCU/OBC charger inlet locking, and industrial market including printer, appliance, robotics or other small machines application. Two logic inputs control the H-bridge driver consisted of four N-channel MOSFETs. The device can control motors bidirectionally with up to 3.6A peak current. The input can be PWM modulated to control motor speed using current chopping method. The device enters sleep mode with low quiescent with both inputs IN1, IN2 low.

The device is integrated with current chopping regulation, based on internal reference and the voltage on the ISEN pin, which is proportional to current flowing through motor through an external sense resistor. The current chopping function limit the peak current to a known level can reduce the system power requirements and bulk capacitance required to maintain stable output voltage especially for motor startup and stall condition.

The device is also fully protected from faults and short circuits, including undervoltage, overcurrent and overtemperature. Also, it provides dedicated nFAULT pin to indicate fault status and alert to microcontroller. When fault condition is removed, the device automatically resumes normal operation.

## Applications

- Printers

- Appliances

- Industrial Equipment

- Electrical Lock

- VCU/OBC charger inlet locking

### **Device Information**

| Part Number    | Package | Body Size       |  |  |

|----------------|---------|-----------------|--|--|

| NSD7312-DHSPR  | HSOP8   | 4.90mm × 3.90mm |  |  |

| NSD7312-Q1HSPR | HSOP8   | 4.90mm × 3.90mm |  |  |

### **Key Features**

- Single H-Bridge Motor Driver

- Wide 5-V to 36-V Operating Voltage

- 520mΩ Typical R<sub>DS(ON)</sub> (HS + LS)

- 3.6-A Peak / 1.5-A continuous Current Drive

- PWM Control Interface

- Integrated Current Regulation

- Low-Power Sleep Mode

- Small Package and Footprint

- 8-Pin HSOP 4.9mm X 3.9mm with exposed PAD

- Integrated Protection Features

- VM Undervoltage Lockout (UVLO)

- Overcurrent Protection (OCP)

- Thermal Shutdown (TSD)

- Fault indicating (nFAULT) and Automatic Fault Recovery

- Industrial temperature grade (NSD7312)

- AEC-Q100 Grade 1 Qualified

Automotive temperature grade (NSD7312-Q1)

## **Functional Block Diagrams**

Figure 1. NSD7312 Block Diagram

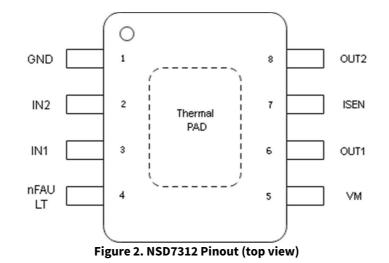

# 1. Pin Configuration and Functions

#### Table 1. NSD7312 Pin Configuration and Description

| SYMBOL         | No | ΤΥΡΕ | DESCRIPTION                                                                                                                                                                                   |

|----------------|----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND            | 1  | PWR  | Logic ground. Connect to board ground                                                                                                                                                         |

| IN1            | 3  | I    | Logic inputs 1. Controls the H-bridge output. Has internal pull downs.                                                                                                                        |

| IN2            | 2  | I    | Logic inputs 2. Controls the H-bridge output. Has internal pull downs.                                                                                                                        |

| ISEN           | 7  | PWR  | High-current ground path. If using current regulation, connect ISEN to a resistor (low-value, high-power-rating) to ground. If not using current regulation, connect ISEN directly to ground. |

| OUT1           | 6  | 0    | H-bridge output1 pin. Connect directly to the motor or other inductive load.                                                                                                                  |

| OUT2           | 8  | 0    | H-bridge output2 pin. Connect directly to the motor or other inductive load.                                                                                                                  |

| VM             | 5  | PWR  | 5V to 36V power supply. Connect a 0.1-μF bypass capacitor to ground, as well as sufficient bulk capacitor needs to guarantee VM pin voltage in maximum range.                                 |

| nFAULT         | 4  | 0    | Open-drain output for fault indication. Pull low when fault (OCP, OT, VUVLO) happens.<br>Connect external pull up resistor, typ. 4.7k/10k                                                     |

| Thermal<br>PAD | _  |      | Thermal pad. Connect to board ground. For good thermal dissipation, use large ground planes on multiple layers, and multiple nearby vias connecting those planes.                             |

## 2. Absolute Maximum Rating

| ITEMS                                          | MIN  | МАХ      | UNIT |

|------------------------------------------------|------|----------|------|

| Power supply voltage (VM)                      | -0.3 | 40       | V    |

| Logic input voltage (IN1, IN2)                 | -0.3 | 6        | V    |

| Fault output pin (nFAULT)                      | -0.3 | 6        | V    |

| Continuous phase node pin voltage (OUT1, OUT2) | -0.7 | VM + 0.7 | V    |

| Current sense input pin voltage (ISEN)         | -0.5 | 0.5      | V    |

## 3. ESD Ratings

| SYMBOL | DESCRIPTION                                                                         | VALUE | UNIT |

|--------|-------------------------------------------------------------------------------------|-------|------|

|        | Human Body Model (HBM) <sup>(1)</sup> , per AEC-Q100-002                            | ±2000 | V    |

| VESD   | Charged device model (CDM) <sup>(1)</sup> , per AEC-Q100-011, all pins              | ±500  | V    |

|        | Charged device model (CDM) <sup>(1)</sup> , per AEC-Q100-011, corner pins (1,4,5,8) | ±750  | V    |

(1) ± 2000v HBM and ± 500v CDM allows safe manufacturing with a standard ESD control process. Pins listed as ± 2000 V HBM & ± 500v CDM may actually have higher performance.

## 4. Recommended Operating Conditions

| SYMBOL          | DESCRIPTION                          | MIN | ТҮР | MAX | UNIT |

|-----------------|--------------------------------------|-----|-----|-----|------|

| VM              | VM Power supply voltage              | 5   |     | 36  | V    |

| V <sub>OD</sub> | nFAULT output voltage range          | 0   |     | 5   | V    |

| I <sub>OD</sub> | nFAULT open drain load current       | 0   |     | 5   | mA   |

| VIN1,<br>VIN2   | Logic input voltage (IN1, IN2)       | 0   |     | 5.5 | V    |

| fpwm            | Logic input PWM frequency (IN1, IN2) | 0   |     | 200 | kHz  |

| Imax            | Max output current <sup>(2)</sup>    | 0   |     | 3.6 | А    |

(2) When the maximum allowable output load current is considered during application scenario, both power dissipation and thermal condition, including ambient temperature, application board thermal condition etc., shall also be evaluated.

## 5. Thermal Information

| SYMBOL | DESCRIPTION                           | MIN | ΤΥΡ | ΜΑΧ | UNIT |

|--------|---------------------------------------|-----|-----|-----|------|

| Та     | Ambient operating ambient temperature | -40 |     | 125 | °C   |

| Тј     | Junction temperature                  | -40 |     | 150 | °C   |

| Tstg   | Storage temperature                   | -65 |     | 150 | °C   |

Copyright © 2023, NOVOSENSE

| Rthjc | Thermal resistance, junction to case                                            | 2.7 | °C/W |

|-------|---------------------------------------------------------------------------------|-----|------|

| Rthja | Thermal resistance, junction to ambient, on 2-layer PCB                         | 62  | °C/W |

|       | Thermal resistance, junction to ambient, on 4-layer PCB based on JEDEC standard | 35  | °C/W |

## 6. Electrical characteristics

Valid for industrial version at  $T_j$  = 25°C, VM=5 to 36V and for automotive version at  $T_j$  = -40 to 150°C, VM=5 to 36V, unless otherwise specified

| SYMBOL               | PARAMETER                   | TEST CONDITIONS                             | MIN | ΤΥΡ | МАХ | UNIT |

|----------------------|-----------------------------|---------------------------------------------|-----|-----|-----|------|

| POWER SU             | PPLY (VM)                   |                                             |     |     |     |      |

| VM                   | VM operating voltage        |                                             | 5   |     | 36  | V    |

| I <sub>VM</sub>      | VM operating supply current | VM = 12 V                                   |     | 2   | 5   | mA   |

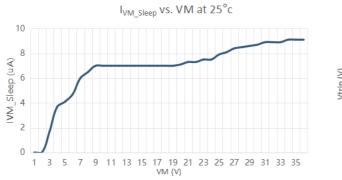

| I <sub>VMSLEEP</sub> | VM sleep current            | VM = 12 V, Ta= 25°c                         |     | 6   | 10  | μA   |

| t <sub>on</sub>      | Turn-on time                | VM > V <sub>UVLO</sub> with IN1 or IN2 high |     | 23  | 50  | μs   |

| Logic Cont           | rol Input (IN1, IN2)        |                                             |     |     |     |      |

| VIL                  | Input logic low voltage     |                                             |     |     | 0.5 | V    |

| V <sub>IH</sub>      | Input logic high voltage    |                                             | 1.8 |     |     | V    |

| V <sub>HYS</sub>     | Input logic hysteresis      |                                             |     | 0.5 |     | V    |

| IIL                  | Input logic low current     | VIN = 0 V                                   | -1  |     | 1   | μA   |

| Ін                   | Input logic high current    | VIN = 3.3 V                                 |     | 33  | 100 | μA   |

| R <sub>PD</sub>      | Pulldown resistance         | to GND                                      |     | 100 |     | kΩ   |

| $t_{\text{PD}}$      | Propagation delay           | INx to OUTx change                          |     | 0.6 | 1   | μs   |

| $\mathbf{t}_{sleep}$ | Time to sleep               | Inputs low to sleep                         |     | 1   | 1.8 | ms   |

| H-BRIDGE             | OUTPUS (OUT1, OUT2)         |                                             |     |     |     |      |

| <b>D</b>             |                             | VM = 12 V, I = 1 A, Ta= 25°c                |     | 285 |     | mΩ   |

| R <sub>DS(ON)</sub>  | High-side FET on resistance | VM = 12 V, I = 1 A, Ta= 125°c               |     |     | 580 | mΩ   |

| _                    |                             | VM = 12 V, I = 1 A, Ta= 25°c                |     | 235 |     | mΩ   |

| R <sub>DS(ON)</sub>  | Low-side FET on resistance  | VM = 12 V, I = 1 A, Ta= 125°c               |     |     | 490 | mΩ   |

| $\mathbf{t}_{DEAD}$  | Output dead time            |                                             |     | 200 |     | ns   |

| V <sub>d</sub>       | Body diode forward voltage  | IOUT = 1 A                                  |     | 0.8 | 1.2 | V    |

| CURRENT I            | REGULATION                  |                                             |     |     |     |      |

| t <sub>OFF</sub>     | PWM off-time                |                                             |     | 25  |     | μs   |

Copyright @ 2023, NOVOSENSE

# Datasheet (EN) 1.4

| t <sub>BLANK</sub>          | PWM blanking time                  |                                   |      | 2    |      | μs |

|-----------------------------|------------------------------------|-----------------------------------|------|------|------|----|

| $t_{deglitch}$              | Current regulation deglitch timing |                                   |      | 0.6  |      | μs |

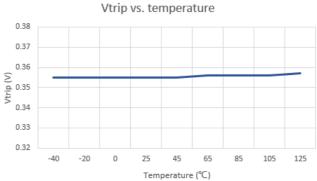

| $V_{\text{TRIP}}$           | ISEN chopping voltage              |                                   | 0.32 | 0.35 | 0.38 | mV |

| PROTECT                     | ION                                |                                   |      |      |      |    |

|                             |                                    | VM falls until UV triggers        | 4.2  | 4.6  |      | V  |

| $V_{\text{UV}}$             | VM undervoltage protection         | VM rises until operation recovers |      | 4.75 | 5.1  | V  |

| $V_{\text{UV}\_\text{HYS}}$ | VM undervoltage hysteresis         |                                   |      | 150  |      | mV |

| $t_{\text{UV}}$             | VM undervoltage deglitch time      |                                   |      | 10   |      | μs |

| I <sub>OCP</sub>            | Overcurrent protection threshold   |                                   | 3.7  | 4.5  | 6.4  | А  |

| t <sub>OCP</sub>            | Overcurrent deglitch time          |                                   |      | 1.5  |      | μs |

| $\mathbf{t}_{\text{RETRY}}$ | Overcurrent retry time             |                                   |      | 3    |      | ms |

| T <sub>SD</sub>             | Thermal shutdown temperature       |                                   | 150  | 165  | 180  | °C |

| T <sub>HYS</sub>            | Thermal shutdown hysteresis        |                                   |      | 20   |      | °C |

| nFAULT O                    | PEN DRAIN OUTPUT                   |                                   |      |      |      |    |

| I <sub>он</sub>             | Output high leakage current        | $V_{OD} = 5V$                     |      |      | 1    | μΑ |

| V <sub>OL</sub>             | Output low voltage                 | Input current 5mA                 |      |      | 0.5  | V  |

## 7. Typical Characteristics

## 8. Functional description

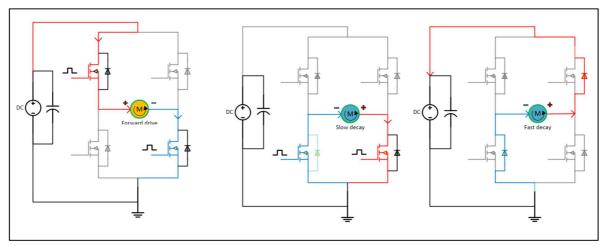

### 8.1. H-bridge operation

The NSD7312 contains two logic input pins IN1 and IN2, the two pins are internally pulled down and able to receive up to max 200kHz PWM signal, for controlling the internal integrated output stage to support motor operation in different states as below table 2.

| IN1 | IN2 | V <sub>ISEN</sub> > V <sub>TRIP</sub> | OUT1     | OUT2     | Description                                                                                                                                      |

|-----|-----|---------------------------------------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 0   | False                                 | HIGH     | LOW      | Normal driving, forward mode                                                                                                                     |

| 0   | 1   | False                                 | LOW      | HIGH     | Normal driving, reverse mode                                                                                                                     |

| 1   | 0   | True                                  | HIGH/LOW | LOW      | Current regulation, forward                                                                                                                      |

| 0   | 1   | True                                  | LOW      | HIGH/LOW | Current regulation, reverse                                                                                                                      |

| 1   | 1   | х                                     | LOW      | LOW      | Slow decay                                                                                                                                       |

| 0   | 0   | x                                     | HIZ      | HIZ      | Fast decay mode.<br>Device move from fast decay to low power<br>sleep mode after both IN1 and IN2 move to 0<br>for 1ms typ (t <sub>sleep</sub> ) |

Table 2. NSD7312 operation state description

Figure 3. High side/low side activation in forward/reverse/slow decay/fast decay

An internal dead-time t<sub>DEAD</sub> is implemented between internal high side and low side switching to avoid cross conduction.

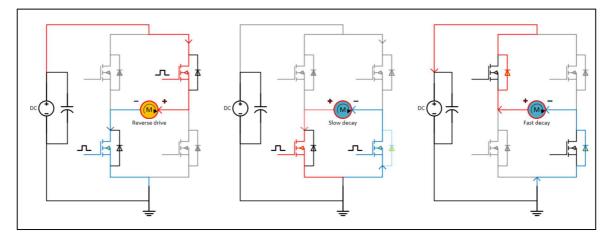

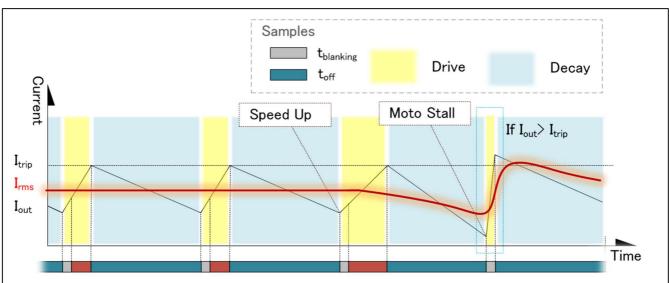

### 8.2. ISEN pin and current regulation

A low value, enough power rating resistor must be placed between ISEN pin and power ground. Together with the internal Voltage reference V<sub>TRIP</sub>, the current regulation level I<sub>TRIP</sub> is set according to the external shunt resistant from ISEN pin to GND, calculation formula as:

$$I_{trip} = \frac{V_{TRIP}}{R_{ISEN}} = \frac{0.35}{R_{ISEN}}$$

The NSD7312 use fixed off-time current regulation. When the load current reaches the setting  $I_{TRIP}$  after the blanking time, the internal controller automatically moves the H-Bridge output to slow decay state by two internal low side MOSFET in ON state, until  $t_{OFF}$  elapses, the H-bridge returns to driving state according to IN1/IN2 pin status starting with blanking time  $t_{BLANK}$  which mask the voltage and current transient during the output switching.

#### Figure 4. Current chopping regulation schemes

#### 8.3. Low power sleep mode

Low power sleep mode in NSD7312 is active when both IN1 and IN2 keeps for low after 1ms (typ.) t<sub>sleep</sub>. It disables most internal circuits, including charge pump and control logic blocks etc., and reduces device current consumption.

When one of IN1 or IN2 pins state moves to high and remains at least 5us, the device exits from low power sleep mode. After 23us (typ.) t<sub>oN</sub> delay timing, OUT1 and OUT2 can be active in normal driving reverse / forward according to IN1 and IN2 inputs.

#### 8.4. Protection function

#### 8.4.1.VM undervoltage protection

When VM power supply pin voltage falls below the undervoltage low threshold ( $V_{UV}$ ) over 10us typ. undervoltage deglitch time, OUT1 and OUT2 becomes HIZ and internal power stage Mosfets are disabled. When VM rise above the  $V_{UV(HIGH)}$ , the device automatically resumes normal operation according to IN1/IN2 pin status.

#### 8.4.2. Overcurrent protection

The device integrates internal current monitor to against output load short, OUT1 / OUT2 pin short to battery or GND. If one of these faults happens and internal sensed current > OCP threshold  $I_{OCP}$  for longer than  $t_{OCP}$ , all H-bridge output MOSFET are disabled.

In the meantime, device provides overcurrent protection recovery function by auto-retry mechanism. After H-bridge output MOSFET disabled for the duration  $t_{RETRY}$ , it automatically re-enables and works according to the state of IN1/IN2 pins. While OCP fault is still present, the protection and auto retry repeats; otherwise, the device moves to normal operation state.

#### 8.4.3. Overtemperature

If the device internal junction temperature over  $T_{SD}$  threshold, the internal MOSFET also automatically disabled. Normal operation will be resumed when internal junction temperature drops below  $T_{SD}$ - $T_{HYS}$

#### 8.4.4. Fault Protection Summary

| Fault            | Condition          | H-Bridge      | nFAULT | <b>Recovery procedure</b>                           |

|------------------|--------------------|---------------|--------|-----------------------------------------------------|

| VM undervoltage  | $VM < V_{UV(LOW)}$ | Disabled, HIZ | LOW    | VM > V <sub>UV (HIGH)</sub>                         |

| ОСР              | >   <sub>OCP</sub> | Disabled, HIZ | LOW    | Auto-retry with $t_{RETRY}$ interval                |

| Over temperature | $T_J > T_{SD}$     | Disabled, HIZ | LOW    | T <sub>J</sub> < T <sub>SD</sub> - T <sub>HYS</sub> |

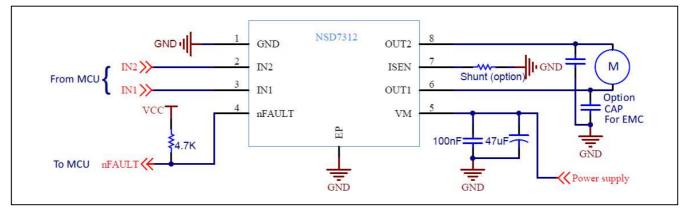

## 9. Application information

### 9.1. Application diagram

#### 9.2. ISEN pin and external shunt resistor selection

To limit the load current during motor start-up and stall condition, a low value shunt resistor is usually placed between ISEN pin and GND. The routing trace shall be short and wide to minimize the IR drop and inductance, which avoids the impact on low-value sensing resistor and ISEN pin.

Because resistor is power rated component, the selection of shunt resistor must meet the enough power rating (I<sup>2</sup>R) and temperature range requirement, while the proper footprint size of resistor shall also be considered.

For example,  $I_{TRIP} = 1.5A$ ,  $R_{ISEN} = 0.35/1.5 = 233$  mohm &  $P = I^2R = 0.524W$ , then  $R_{ISEN}$  can be selected using 250 mohm shunt with SMT 2512 size rating >1W.

#### 9.3. Device power dissipation and continuous driving current

Total device power dissipation ( $P_{TOT}$ ) is consisted of three parts: VM supply current and related dissipation ( $P_{VM}$ ), H-bridge switching loss ( $P_{SW}$ ) and H-bridge MOSFET ON static power dissipation ( $P_{ON}$ ).

$$P_{TOT} = P_{VM} + P_{SW} + P_{ON}$$

$$P_{TOT} = VM * I_{VM} + I_{LOAD} * V_M * (t_{rise} + t_{fall}) * f_{PWM} + I_{LOAD}^2 * (R_{DS(ON)_{HS}} + R_{DS(ON)_{LS}})$$

If the input PWM frequency is used below 20kHz, the switching loss P<sub>sw</sub> is insignificant comparing with P<sub>oN</sub>, therefore, the power loss of NSD7312 under this condition can be quickly estimated by the formula

$$P_{TOT} \approx I_{RMS}^2 \times (R_{DS(ON)_{HS}} + R_{DS(ON)_{LS}})$$

The device junction temperature calculation is defined as  $T_J = T_{amb} + (R_{thja} * P_{TOT})$ , for continuous driving, the device internal temperature must be less than Tj max (150°c) for system operating.

#### 9.4. Layout tips

For optimized thermal performance, the NSD7312 exposed pad must be directly soldered to the PCB surface, also multiple vias should be used to transfer the heat to other PCB layers. In the meanwhile, the PCB is recommended to have higher copper coverage and thick ground plane.

```

Copyright @ 2023, NOVOSENSE \\

```

For robust and reliable electrical usage, the power supply pin VM should be decoupled with a bulk capacitor (47uF or 100uF) and one low value ceramic capacitor (100nF typical). The placement of two capacitors suggests close to VM pin as much as possible.

The generic option capacitor value on OUT1 & OUT2 for EMC is 10nF. The most appropriated value shall be determined during system-level EMC testing. For layout, put the option EMC capacitor close to output connector is suggested.

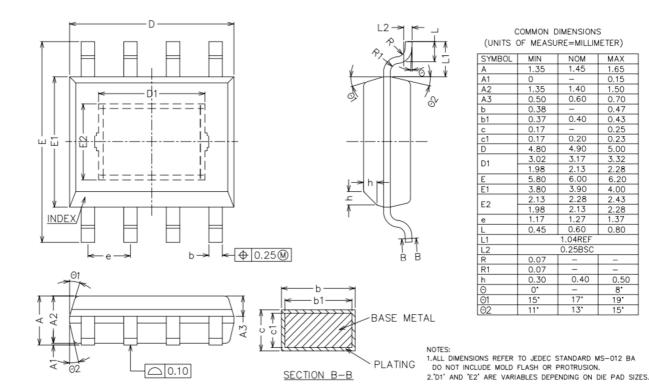

### 10. Package information

### 10.1. HSOP8 package information

Note: Variation A, D1 (MIN 3.02, TYP 3.17, MAX 3.32) & E2 (MIN 2.13, TYP 2.28, MAX 2.43), is used.

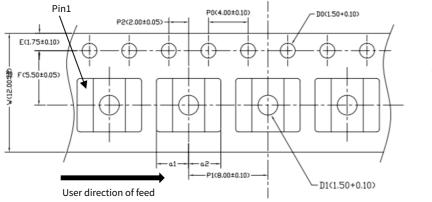

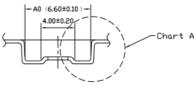

### 10.2. HSOP8 packaging information

NOTES: 1.MATERIAL:Hard polystyrene(PS) 2.ALL DIMS IN MM

## **11. Ordering Information**

| Part Number                                                                                                                                                       | Automotive /<br>Industrial | VREF / VTRIP | NFAULT | IPROBE | Package<br>Type | MSL  | SPQ  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------|--------|--------|-----------------|------|------|--|

| NSD7312-DHSPR                                                                                                                                                     | Industrial                 | Vtrip 0.35v  | YES    | NO     | HSOP8           | MSL3 | 2500 |  |

| NSD7312-Q1HSPR                                                                                                                                                    | Automotive                 | Vtrip 0.35v  | YES    | NO     | HSOP8           | MSL3 | 2500 |  |

| Note: All packages are ROHS compliant with peak reflow temperature of 260°C according to the JEDEC industry standard classifications and peak solder temperature. |                            |              |        |        |                 |      |      |  |

## 12. Revision History

| Revision | Description                                                                | Date       |

|----------|----------------------------------------------------------------------------|------------|

| 1.0      | Initial version                                                            | 2021/11/5  |

| 1.1      | Correct some typo and add application information about power dissipation  | 2022/8/28  |

| 1.2      | Update some datasheet parameters and MSL information                       | 2022/10/14 |

| 1.3      | Add note for thermal pad size variation and MSL                            | 2022/11/25 |

| 1.4      | Revise datasheet parameter maximum values and test condition               | 2023/2/20  |

|          | Revise application diagram and add option output EMC capacitor description |            |

|          | Revise ordering information table and datasheet format                     |            |

## **IMPORTANT NOTICE**

The information given in this document shall in no event be regarded as a guarantee of any warranty or authorization, express or implied, including but not limited to merchantability, fitness for a particular purpose or infringement of any third party's intellectual property rights.

You are solely responsible for your use of Novosense' products and applications. You shall comply with all laws, regulations and requirements related to Novosense's products and applications, although information or support related to any application may still be provided by Novosense.

The resources are intended only for skilled developers designing with Novosense' products. Novosense reserves the rights to make corrections, modifications, enhancements, improvements or other changes to the products and services provided. Novosense authorizes you to use these resources for the development of relevant applications of Novosense's products, other reproduction and display of these recourses is prohibited. Novosense shall not be liable for any claims, damages, costs, losses or liabilities arising out of the use of these resources.

For further information on applications, products and technologies, please contact Novosense (www.novosns.com ).

Suzhou Novosense Microelectronics Co., Ltd