Is Now Part of

# **ON Semiconductor**®

# To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="https://www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to <a href="https://www.onsemi.com">Fairchild\_questions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized applications, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an equif prese

# Single 2A High-Speed, Low-Side IGBT Driver

The FAN3181 is suitable for designed to stand-alone IGBT driver in lowside switching applications by providing high peak current pulses during the switching intervals. The protection functions include Under-Voltage Lockout (UVLO) and Over-Current Protection (OCP), and Desaturation Protection (DESAT) with fault-out function and active miller clamp function. An open-drain fault-out signal is provided to indicate that an over-current, under-voltage, and Desaturation detect has occurred. Soft turn-off feature is used to increase the reliability of an application during short-circuit or over-current periods. This feature works after the desaturation or over-current protection is activated, which provides protection for IGBT against short-circuit and over-current events. With the "Soft" turn-off feature, the gate voltage will be reduced slowly in order to reduce IGBT current.

#### Features

- Operating Supply Voltage 25 V

- Typically 1.5 A/2.0 A Sourcing/Sinking Current-Driving Capability at  $V_{CC}$  = 15 V

- Output In- Phase with Input Signal

- Active Miller Clamp

- Desaturation Protection

- Cycle-by-Cycle Edge-Triggered Shutdown Function

- Fault-Out and Shutdown Function

- Built-in V<sub>CC</sub> UVLO Function

- Built-in Soft Turn-Off Function

- Built-in Over-Current Protection (OCP)

- Operating Junction Temperature Range of -40°C to 125°C

#### **Typical Applications**

- Switch-Mode Power Supplies

- DC DC Converters

- Motor Control for PFC in Air-conditioner Application

#### **ON Semiconductor®**

www.onsemi.com

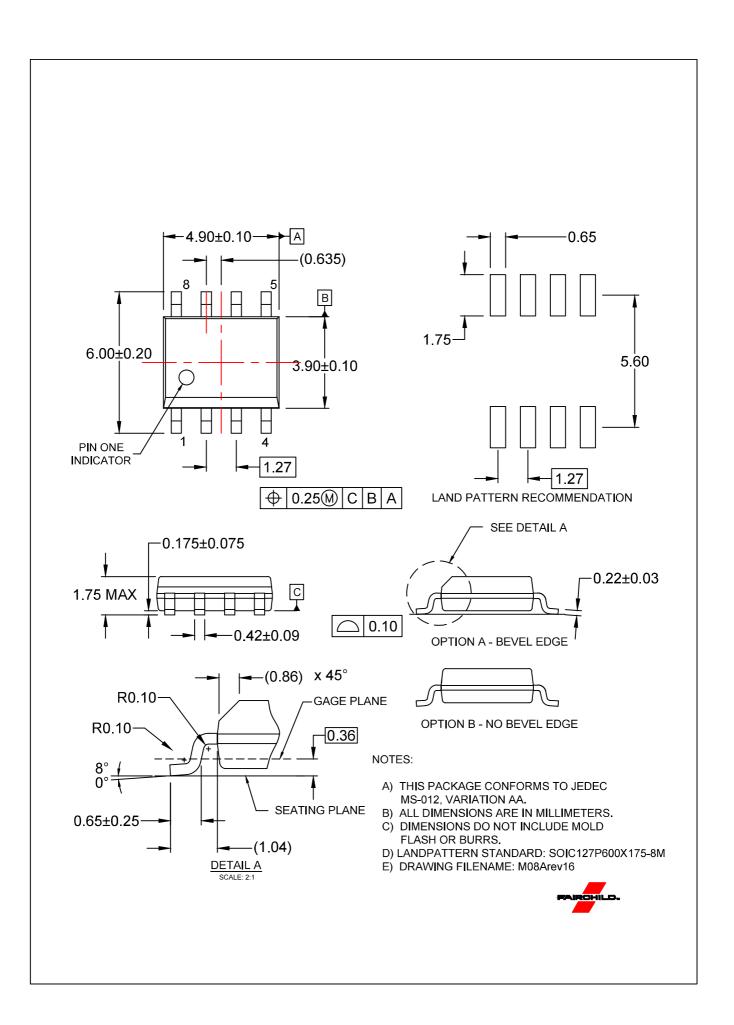

#### PACKAGE PICTURE

8 Lead SOP (Small Outline Package)

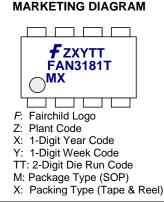

#### ORDERING INFORMATION

| Device                    | Package | Packing<br>Method |  |

|---------------------------|---------|-------------------|--|

| FAN3181TMX <sup>(1)</sup> | SOIC-8  | Tape & Reel       |  |

Note:

1. This device passed wave-soldering test by JESD22A-111

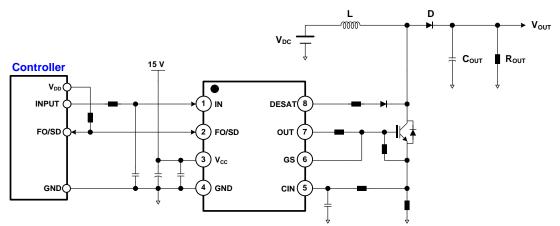

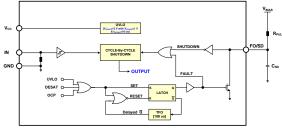

Figure 1 Simplified Application Schematics

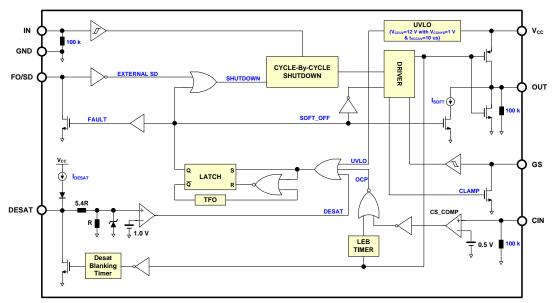

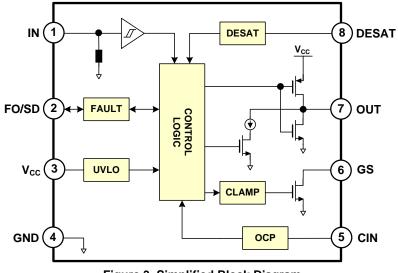

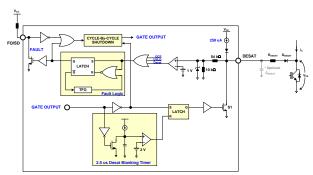

Figure 2. Detailed Block Diagram

Figure 3. Simplified Block Diagram

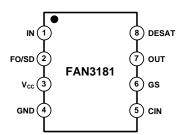

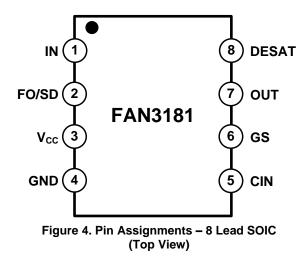

#### **PIN CONNECTIONS**

#### PIN FUNCTION DESCRIPTION

| Pin Name        | Pin No. | I/O/x | Description                                                                                                                                           |

|-----------------|---------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN              | 1       | I     | Input signal to control the output. IN has a pull-down resistor of 100 k $\Omega$ .<br>Output In-Phase with Input Signal (Non-Inverting).             |

| FO/SD           | 2       | 0     | Fault output and shutdown that allows communication to main controller that the drivers has encountered a fault condition and deactivated the output. |

| V <sub>cc</sub> | 3       | x     | Power Supply. The bypass capacitor is required this pin to GND and should be placed as close as possible to the $V_{CC}$ pin.                         |

| GND             | 4       | х     | This pin should connect to the IGBT Emitter or shunt resistor with short trace.                                                                       |

| CIN             | 5       | I     | Analog Input for Over-Current detect                                                                                                                  |

| GS              | 6       | 0     | Provides clamping for the IGBT gate during the off period to protect it from parasitic turn-on due to high collector-to emitter dv/dt induced.        |

| OUT             | 7       | 0     | Driver Output.                                                                                                                                        |

| DESAT           | 8       | I     | Input for detecting the desaturation of IGBT due to fault condition.                                                                                  |

#### MAXIMUM RATINGS (Note 2)

| Rating                                                         |                                     | Symbol             | Min. | Max.                 | Unit |

|----------------------------------------------------------------|-------------------------------------|--------------------|------|----------------------|------|

| Fixed Supply Voltage <sup>(3)</sup>                            |                                     | V <sub>cc</sub>    | -0.3 | 30.0                 | V    |

| Output 1 Voltage                                               |                                     | V <sub>OUT</sub>   | -0.3 | V <sub>cc</sub> +0.3 | V    |

| Output 2 Voltage                                               |                                     | V <sub>GS</sub>    | -0.3 | V <sub>cc</sub> +0.3 | V    |

| IN, FO/SD, DESAT, $V_{\text{CIN}}$ and $V_{\text{FO}}$ Voltage |                                     | V <sub>IN</sub>    | -0.3 | V <sub>cc</sub> +0.3 | V    |

| Operating Junction Temperature                                 |                                     | TJ                 | -55  | 150                  | °C   |

| Storage Temperature Range                                      |                                     | T <sub>STG</sub>   | -55  | 150                  | °C   |

| Electrostatic Discharge<br>Capability                          | Human Body Model <sup>(4)</sup>     | ESD <sub>HBM</sub> |      | 2                    | kV   |

|                                                                | Charged Device Model <sup>(4)</sup> | ESD <sub>CDM</sub> |      | 500                  | V    |

2. Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

3. Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per JESD22-A114

ESD Charged Device Model tested per JESD22-C101

5. All voltage values are given with respect to GND pin.

#### THERMAL CHARACTERISTICS

| Rating                                                                                          | Symbol          | Value | Unit |

|-------------------------------------------------------------------------------------------------|-----------------|-------|------|

| Thermal Characteristics, 8-SOP <sup>(b)</sup><br>Thermal Resistance Junction-Air <sup>(7)</sup> | θ <sub>JA</sub> | 200   | °C/W |

| Power Dissipation <sup>(7)</sup>                                                                | P <sub>D</sub>  | 0.625 | W    |

6. Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

7. JEDEC standard: JESD51-2, JESD51-3. Mounted on 76.2×114.3×1.6mm PCB (FR-4 glass epoxy material).

#### **RECOMMENDED OPERATING CONDITIONS (Note 8)**

| Rating                              | Symbol          | Min. | Max.            | Unit |

|-------------------------------------|-----------------|------|-----------------|------|

| Fixed Supply Voltage                | V <sub>CC</sub> | UVLO | 25              | V    |

| Input Voltage                       | V <sub>IN</sub> | 0    | V <sub>cc</sub> | V    |

| Operating Ambient Temperature Range | T <sub>A</sub>  | -40  | 125             | °C   |

8. Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### ELECTRICAL CHARACTERISTICS

10 11

| Parameter                                                       | n/max values T <sub>A</sub> =-40°C to +125°C, unl<br>Test Conditions | Symbol              | Min. | Тур. | Max. | Unit |

|-----------------------------------------------------------------|----------------------------------------------------------------------|---------------------|------|------|------|------|

| POWER SUPPLY SECTION                                            | -                                                                    |                     |      |      |      |      |

| Quiescent Current for $V_{CC}$                                  | V <sub>IN</sub> = 0 V                                                | I <sub>QCC</sub>    | 600  | 850  | 1050 | μA   |

| Operating Current for V <sub>CC</sub>                           | f <sub>IN</sub> = 20 kHz                                             | Icc                 |      | 1.5  | 2.0  | mA   |

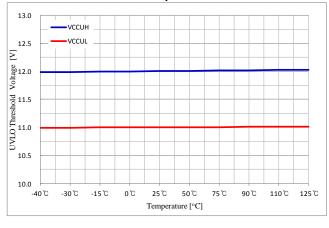

| V <sub>CC</sub> Supply UV Trip Voltage                          |                                                                      | V <sub>CCUV</sub>   | 11.0 | 12.0 | 13.0 | V    |

| V <sub>CC</sub> Supply UV Hysteresis                            |                                                                      | V <sub>CCHYS</sub>  | 0.5  | 1.0  | 1.5  | V    |

| V <sub>CC</sub> Supply UV Filter Time <sup>(9)</sup>            |                                                                      | t <sub>VCCUV</sub>  | 5    | 10   | 15   | μS   |

| INPUT LOGIC SECTION                                             |                                                                      | 1                   |      |      |      |      |

| High Level Input Voltage for IN                                 |                                                                      | VIHT                |      | 1.6  | 2.0  | V    |

| Low Level Input Voltage for IN                                  |                                                                      | VILT                | 0.8  | 1.2  |      | V    |

| Input Logic Hysteresis                                          |                                                                      | VINHYST             |      | 0.4  |      | V    |

| High Level Logic Input Bias Current                             | V <sub>IN</sub> = V <sub>CC</sub>                                    | I <sub>IN+</sub>    | 125  | 150  | 200  | μA   |

| Low Level Logic Input Bias Current                              | V <sub>IN</sub> = 0 V                                                | I <sub>IN-</sub>    |      |      | 1.0  | μA   |

| Logic Input Pull-Down Resistance                                |                                                                      | R <sub>IN</sub>     | 75   | 100  | 120  | kΩ   |

| GATE DRIVER OUTPUT SECTION                                      |                                                                      | 1                   |      | l    | L    |      |

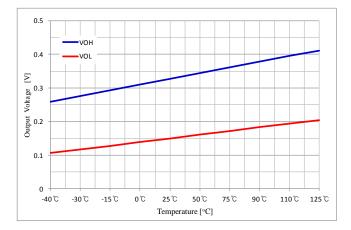

| High Level Output Voltage (V <sub>CC</sub> - V <sub>OUT</sub> ) | I <sub>OUT</sub> =100 mA                                             | V <sub>OH</sub>     |      |      | 0.8  | V    |

| Low Level Output Voltage                                        | I <sub>OUT</sub> =100 mA                                             | V <sub>OL</sub>     |      |      | 0.35 | V    |

| Output HIGH Short-Circuit Pulse Current <sup>(9)</sup>          | $V_0=0$ V, $V_{IN}=5$ V with PW=10 $\mu$ s                           | I <sub>O+</sub>     | 1.0  | 1.5  |      | А    |

| Output LOW Short-Circuit Pulse Current <sup>(9)</sup>           | $V_0=15 \text{ V}, \text{ V}_{IN}=0 \text{ V}$ with PW=10 µs         | I <sub>O-</sub>     | 1.5  | 2.0  |      | А    |

| Soft Turn-Off Sink Current                                      | V <sub>CIN</sub> =1 V, V <sub>O</sub> =V <sub>CC</sub>               | I <sub>SOFT</sub>   | 20   | 30   | 40   | mA   |

| <b>OVER-CURRENT PROTECTION SECTION</b>                          |                                                                      | 1                   |      |      |      |      |

| Over-Current Detect Threshold                                   |                                                                      | V <sub>CINTH</sub>  | 450  | 500  | 550  | mV   |

| Short-Circuit Input Current                                     | V <sub>CIN</sub> =1 V                                                | I <sub>CIN</sub>    | 5    | 10   | 15   | μA   |

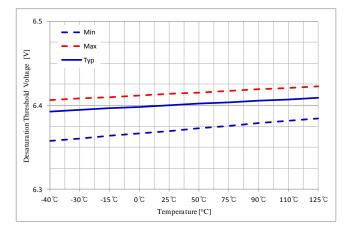

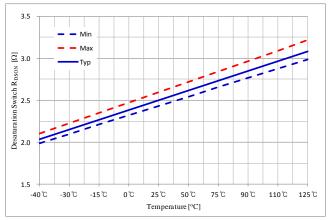

| DESATURATION PROTECTION SECTION                                 |                                                                      |                     |      |      |      |      |

| Desaturation Threshold Voltage                                  |                                                                      | V <sub>DESAT</sub>  | 6.0  | 6.4  | 6.8  | V    |

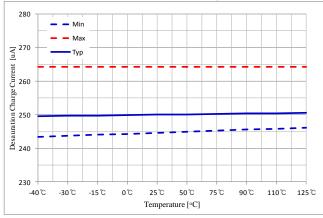

| Current Source                                                  | IN=HIGH                                                              | IDESAT              | 215  | 250  | 285  | μA   |

| Switch On Resistance                                            |                                                                      | RONSAT              |      | 2.5  | 5.0  | Ω    |

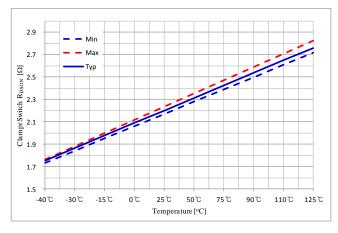

| ACTIVE MILLER CLAMP SECTION                                     |                                                                      |                     |      |      |      |      |

| GS Pin Threshold Voltage                                        |                                                                      | V <sub>GSTH</sub>   | 1.2  | 1.5  | 1.8  | V    |

| GS Pin Low Level Clamp Voltage                                  | I <sub>GS</sub> =50 mA                                               | V <sub>CLAMP</sub>  |      | 110  | 250  | mV   |

| GS Pin Clamp Current <sup>(9)</sup>                             | V <sub>GS</sub> =GND + 2.5 V                                         | IGSCLAMP            | 0.5  | 1.0  |      | А    |

| Clamp Switch Resistance                                         |                                                                      | RONCLAMP            |      | 2.2  | 4.5  | Ω    |

| FAULT-OUTPUT SECTION                                            |                                                                      |                     |      |      |      |      |

| FO/SD High Threshold Voltage                                    |                                                                      | V <sub>FOSDH</sub>  |      | 1.6  | 2.0  | V    |

| FO/SD Low Threshold Voltage                                     |                                                                      | V <sub>FOSDL</sub>  | 0.8  | 1.2  |      | V    |

| Fault Output Leakage Current                                    | V <sub>FOSD</sub> =V <sub>CC</sub>                                   | I <sub>FOSDLK</sub> |      |      | 1.0  | μA   |

| Fault Output Low Level Voltage                                  | $V_{MCU}$ =5 V, R <sub>PULLUP</sub> =20 k $\Omega$                   | V <sub>FOL</sub>    |      |      | 0.1  | V    |

| Fault Output On Resistance                                      | I <sub>FO</sub> =5 mA                                                | R <sub>DSFO</sub>   |      | 250  | 400  | Ω    |

9. This parameter, although guaranteed by design, is not tested in production.

10. Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

11. Performance guaranteed over the indicated operating temperature range by design and/or characterization tested at  $T_J = T_A = 25^{\circ}C$ .

#### DYNAMIC ELECTRICAL CHARACTERISTICS

| Parameter                                                        | Test Conditions                             | Symbol               | Min. | Тур. | Max. | Unit |

|------------------------------------------------------------------|---------------------------------------------|----------------------|------|------|------|------|

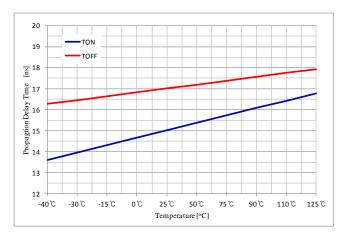

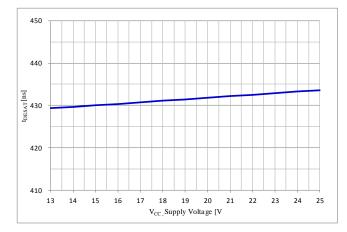

| Turn-On Propagation Delay                                        | V <sub>IN</sub> From 0 V to 5 V             | t <sub>ON</sub>      | 10   | 15   | 20   | ns   |

| Turn-Off Propagation Delay                                       | V <sub>IN</sub> From 5 V to 0 V             | t <sub>OFF</sub>     | 12   | 17   | 22   | ns   |

| Propagation Delay Mismatching I toN-toFF I                       |                                             | MT                   |      |      | 12   | ns   |

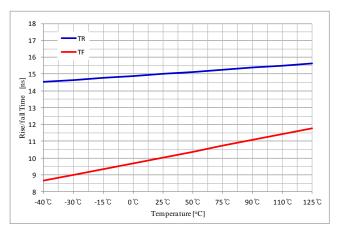

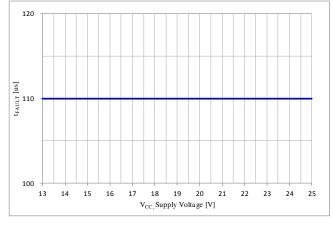

| Turn-On Rise Time                                                |                                             | t <sub>R</sub>       |      | 15   | 20   | ns   |

| Turn-Off Fall Time                                               |                                             | t <sub>F</sub>       |      | 10   | 17   | ns   |

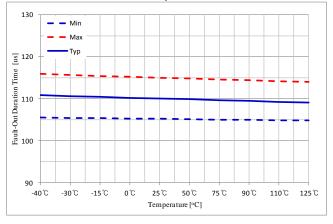

| Fault Output Duration                                            |                                             | t <sub>FAULT</sub>   | 75   | 110  | 145  | μs   |

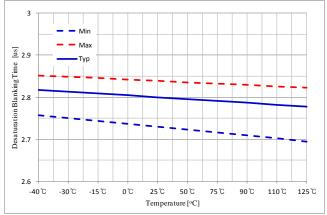

| Desat Blanking Time                                              | V <sub>DESAT</sub> = 6.5 V                  | t <sub>DESABLK</sub> | 1.8  | 2.8  | 3.8  | μs   |

| FO/SD to Output LOW Propagation Delay                            |                                             | t <sub>FOSD</sub>    |      | 17   | 22   | ns   |

| CIN Pin Leading-Edge Blanking Time <sup>(12)</sup>               |                                             | t <sub>CINBLT</sub>  |      | 300  | 400  | ns   |

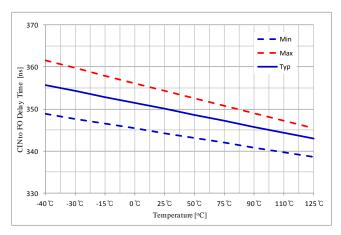

| Time from CIN Triggering to FO                                   | From V <sub>CIN</sub> =1 V to FO Turn-Off   | t <sub>CINFO</sub>   | 250  | 350  | 450  | ns   |

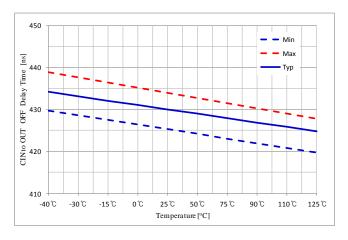

| Time from CIN Triggering to Output Turn-Off                      | From V <sub>CIN</sub> =1 V to Gate Turn-Off | t <sub>CINOFF</sub>  | 330  | 430  | 530  | ns   |

| Time from Clamp Triggering to Output Turn-Off <sup>(12)</sup>    |                                             | t <sub>CLAMP</sub>   |      | 6    | 10   | ns   |

| Time from DESAT Triggering to Output Turn-Off                    |                                             | t <sub>DESAT</sub>   | 330  | 430  | 530  | ns   |

| Minimum Input Pulse Width Response at the Output <sup>(12)</sup> |                                             | t <sub>ONMIN</sub>   | 40   |      |      | ns   |

This parameter, although guaranteed by design, is not tested in production.

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

Performance guaranteed over the indicated operating temperature range by design and/or characterization tested at T<sub>J</sub> = T<sub>A</sub> = 25°C.

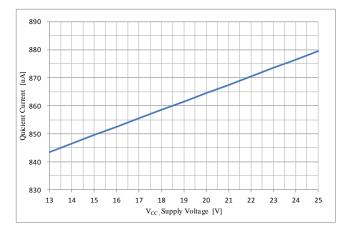

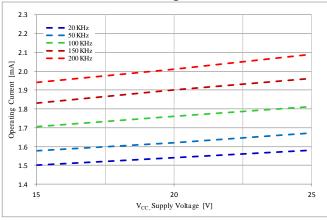

#### TYPICAL CHARACTERISTICS

Figure 5.Quiescent Supply Current vs. V<sub>CC</sub> Supply Voltage

Figure 7. Operating Supply Current vs. V<sub>CC</sub> Supply Voltage

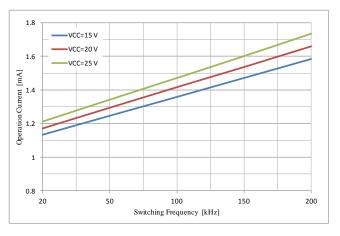

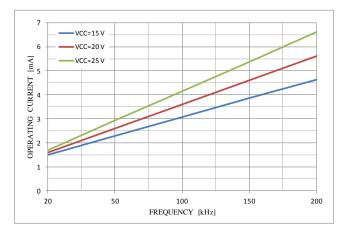

Figure 9.Operating Supply Current vs. Switching Frequency (No Load)

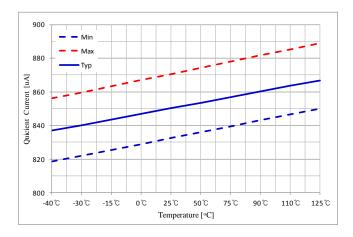

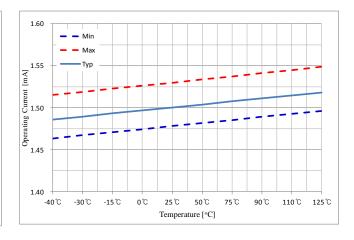

Figure 6.Quiescent Supply Current vs. Temperature

Figure 8. Operating Supply Current vs. Temperature

Figure 10.0perating Supply Current vs. Switching Frequency ( $C_{LOAD} = 1 \text{ nF}$ )

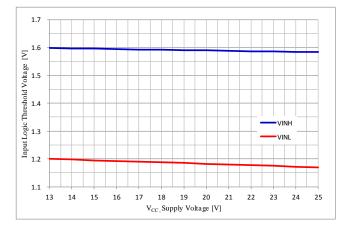

Figure 11. Input Threshold Voltage vs. V<sub>CC</sub> Supply Voltage

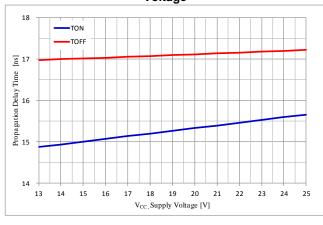

Figure 13.Propagation Delay Time vs. V<sub>CC</sub> Supply Voltage

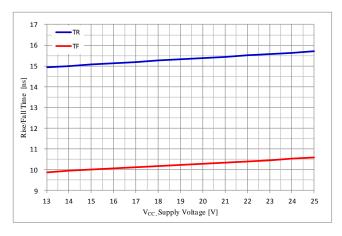

Figure 15.Output Rise/Fall Time vs. V<sub>CC</sub> Supply Voltage

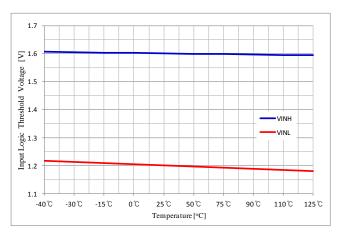

Figure 12. Input Threshold Voltage vs. Temperature

Figure 14. Propagation Delay Time vs. Temperature

Figure 16.Output Rise/Fall Time vs. Temperature

Figure 17. DESAT Triggering to Output OFF Delay Time vs. V<sub>CC</sub> Supply Voltage

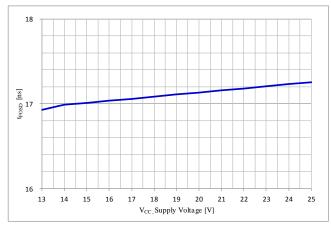

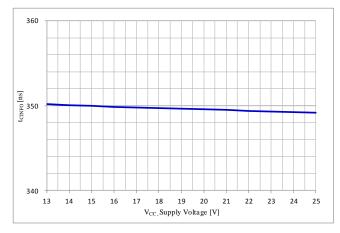

Figure 19. Fault Output Duration vs. V<sub>CC</sub> Supply Voltage

Figure 21. FO/SD to Output LOW Propagation Delay vs. V<sub>CC</sub> Supply Voltage

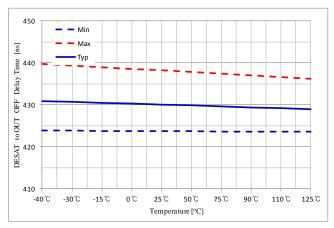

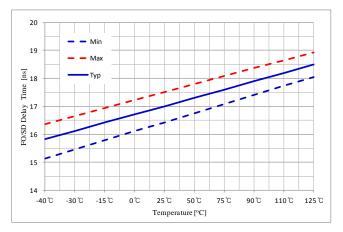

Figure 18. DESAT Triggering to Output OFF Delay Time vs. Temperature

Figure 22. FO/SD to Output LOW Propagation Delay vs. Temperature

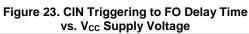

Figure 25. CIN Triggering to Output Low Delay vs. V<sub>CC</sub> Supply Voltage

Figure 27. Desaturation Charge Current vs. Temperature

Figure 24. CIN Triggering to FO Delay vs. Temperature

Figure 26. CIN Triggering to Output Low Delay vs. Temperature

Figure 28. Desaturation Blanking Time vs. Temperature

Figure 29. Desaturation Threshold Voltage vs. Temperature

Figure 31. Vcc UVLO Threshold Voltage vs. Temperature

Figure 33. Clamp Switch RDSON vs. Temperature

Figure 30. Desaturation Blanking Switch R<sub>DSON</sub> vs. Temperature

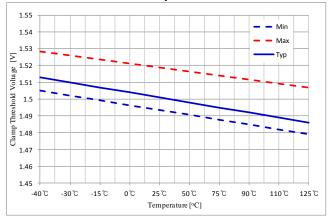

Figure 32. Clamp Threshold Voltage vs. Temperature

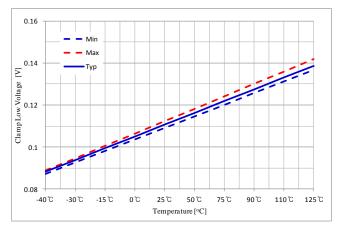

Figure 34. GS Pin Clamp Low Level Voltage at I<sub>GS</sub>=50 mA vs. Temperature

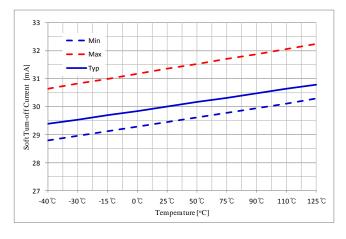

Figure 37. Soft-Off Sink Current vs. Temperature

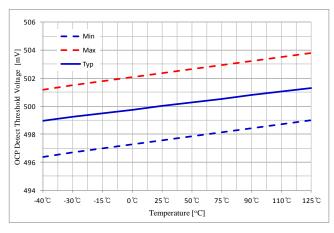

Figure 39. CIN Threshold Voltage vs. Temperature

Figure 36. Fault-Out Switch R<sub>DSON</sub> vs. Temperature

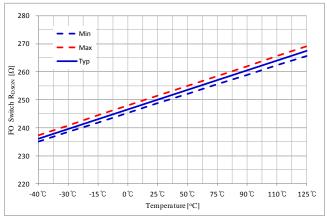

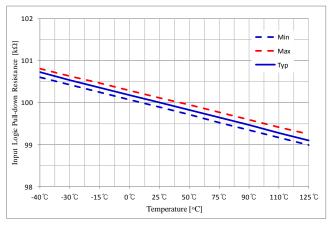

Figure 38. Input Logic Pull-down Resistance vs. Temperature

#### DEFINITIONS

#### Input to Output Switching Time Definitions

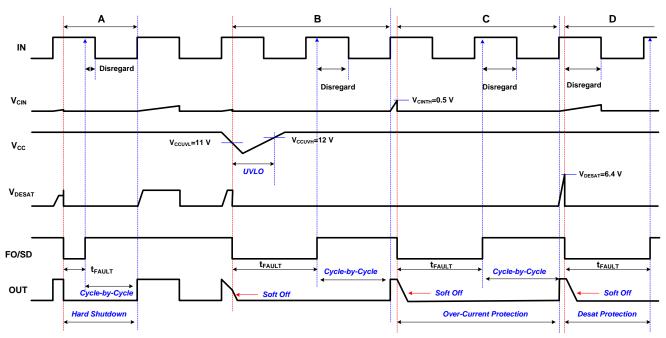

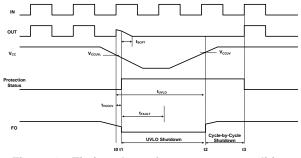

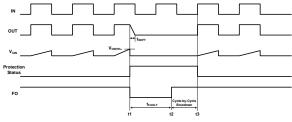

Figure 40 shows an input to output timing diagram when external shutdown (Case-A), Under-voltage lockout (Case-B), and Over-current (Case-C) and Desaturation Protection (Case-D) events.

Figure 40. Overall Operating Waveforms Definitions

#### **Switching Time Definitions**

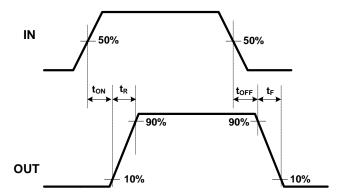

Figure 41 shows an input to output switching timing diagram. The output signal is HIGH when input signal is HIGH (Output In-phase with input signal).

Figure 41. Switching Time Waveforms Definitions

#### APPLICATIONS INFORMATION

This section lists the detail about key features and operating for the FAN3181.

#### Input Stage

The input pins of FAN3181 gate-driver devices are based on a TTL compatible input-threshold logic that is independent of the V<sub>CC</sub> supply voltage. The logic level compatible input provides a typically high threshold of 1.6 V and a typically low threshold of 1.2 V. The input impedance of the FAN3181 is 100 k $\Omega$  typically, as shown in the block diagrams. We recommends an RC filter to be added on the input pin for reducing the impact of system noise and ground bounce, the time constant of the RC filter, for example, 100  $\Omega$  with 1 nF is an acceptable choice.

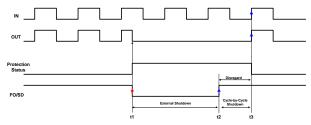

#### **Shutdown Function**

The FAN3181 provide an external shutdown function when FO/SD pin voltage is below typically 1.2 V. The fault-out signal is report to the FO/SD pin and an external RC network is connected to this FO/SD pin in order to provide an adjustable gate driver disable time, which is consist the internal default fault-clear time (typically 110 µs) and shutdown time that follows the fault condition. The FAN3181 shutdown architecture allows immediate turn-off of the outputs of the gate driver in the case of fault, by minimizing the propagation delay between the fault detection event and the actual output switch-off. In fact, the time delay between the fault detection and the output turn-off is no longer dependent on the value of the external RC network connected to the FO/SD pin. In the shutdown circuitry the fault signal has a preferential path which directly switches off the outputs after the shutdown logic triggering. At the same time the internal logic turns on the open drain fault-out switch and holds it during default fault-clear time (typically 110 µs) and until the FO/SD voltage goes above the shutdown (FO/SD) logic input threshold (typically 1.6 V). When such threshold is reached, the open drain output is turned off, allowing the external pull-up to recharge the capacitor. The driver outputs restart following the input pins as soon as the voltage at the FO/SD pin reaches the higher threshold of the shutdown logic input.

The shutdown system provides the possibility to increase the time constant of the external RC network (that determines the disable time after the fault event) up to very large values without increasing the delay time of the protection as shown in Figure 43.

Figure 43. Application Circuit of Fault-Out

An approximation of the disable time is calculated by equation (1):

$$T_{\text{DISABLE}} = T_{\text{FAULT}} + T_{\text{SD}}$$

$$T_{\text{SD}} \cong \tau \times \ln(\frac{(-V_{\text{BIAS}})}{(V_{\text{FOSDH}} - V_{\text{BIAS}})})$$

(1)

Where,  $T_{FAULT} = 110 \ \mu s$ ,  $V_{FOSDH} = 1.6 \ V$ ,  $\tau = R_{PULL} \times C_{SD}$ . We recommended pull-up resistance ( $R_{PULL}$ ) value is 20 k $\Omega$ . The Fault Output (FO) stays in the low state until the fault condition has been removed or the fault clear time ( $T_{FAULT}$ ) expires; once the fault clear timer expires, allowing the external pull-up resistor to recharge the capacitor. When FO/SD pin voltage is reached threshold, the driver outputs restart following the input signal.

#### **Output Stage**

The output stage is able to sink/source about 2.0 A/1.5 A typical at 25°C and the minimum sink/source currents over the full temperature range  $(-40^{\circ}C / +125^{\circ}C)$  are 1.5 A sink and 1.0 A source. Soft turn-off switch in the output drive stage will turn on to softly turn off the IGBT and prevents large di/dt induced voltages when fault conditions are occurred. This device slowly discharges the IGBT gate to prevent fast changes in collector current that could cause damaging voltage spikes due to stray inductances. During the slow turn off, the output stage device remains off.

#### **Protection Function**

FAN3181 provide the protection features include  $V_{CC}$ Under-voltage lockout (UVLO), external shutdown (Externally FO/SD pin is LOW), Over-Current Protection (OCP) or Desaturation protection and the FO/SD pin is internally pulled to GND when above mentioned fault events happened.

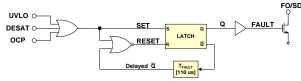

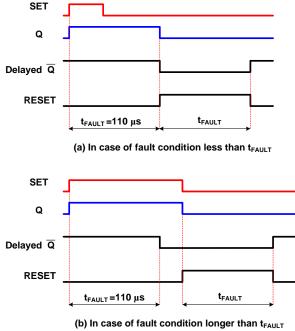

#### Fault-Out (FO) Function

FAN3181 provide the fault-out signal when  $V_{CC}$  Undervoltage lockout (UVLO), Desaturation protection or Over-current (OCP) events happened as shown in Figure 44. The fault output (FO/SD) pin stays in the low state until the fault condition has been removed and the fault clear timer ( $T_{FAULT}$ , typically 110 µs) expires; once the fault clear timer expires, the voltage on the FO/SD pin will return to pull-up voltage.

Figure 44. Functional Block of Fault-Out

If fault condition time is less than fault clear time (Case-a), the pulse width of fault-out (FO) is 110  $\mu$ s. If longer (case-b), pulse width of fault-out same with fault condition time as shown in Figure 45.

#### **Under- Voltage Lockout Protection**

FAN3181 provides an Under-voltage lockout (UVLO) protection circuitry that monitors the supply voltage for  $V_{CC}$ . It can be designed to prevent malfunction when  $V_{CC}$  is lower than the specified threshold voltage and supply voltage ( $V_{CC}$ ) maintains an under-voltage condition over under-voltage filtering times ( $t_{VCCUV}$ , typically 10 µs).

| Table | 1. | U٧ | LO | Conditions |  |

|-------|----|----|----|------------|--|

|       |    |    |    |            |  |

| Case   | Condition                                              | FO         | FO   | OUT  |  |  |  |  |  |

|--------|--------------------------------------------------------|------------|------|------|--|--|--|--|--|

| Case 1 | $t_{UVLO} > t_{FAULT}$                                 | t<br>UVLO  | LOW  | LOW  |  |  |  |  |  |

| Case 2 | $t_{UVLO} < t_{FAULT}$                                 | t<br>FAULT | LOW  | LOW  |  |  |  |  |  |

| Case 3 | $t_{\rm UVLO} < t_{\rm VCCUV}$                         |            | HIGH | HIGH |  |  |  |  |  |

| Case 4 | $V_{cc} < 5 V$                                         |            | Х    | Х    |  |  |  |  |  |

| Note   | t <sub>FAULT</sub> = 110 μs, t <sub>VCCUV</sub> =10 μs |            |      |      |  |  |  |  |  |

If a fault condition occurs, the FO/SD Pin is internally pulled to GND and output (OUT) of the gate driver is soft turned off. The output decline linearly by the internal sink current source ( $I_{SOFT}$ =30 mA) for soft turnoff.

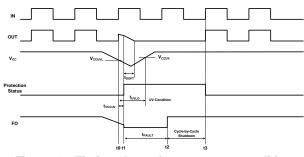

#### In case of tuvlo > tFAULT

Gate drive output is softly turn-off and Fault-Out (FO) stays in low state until fault condition has been removed when the duration of under-voltage condition  $(t_{UVLO})$  longer than fault output (FO) time (typical 110 µs) as shown in Figure 46 The fault output (FO/SD) and gate driver output goes to low state after under-voltage filtering time ( $t_{VCCUV}$ , typically10 µs) when the  $V_{CC}$  is below the under-voltage lockout low threshold voltage.

Figure 46. Timing chart of t<sub>UVLO</sub> > t<sub>FAULT</sub> condition

#### In case of t<sub>UVLO</sub> < t<sub>FAULT</sub>

Gate drive output is softly turn-off and Fault-Out (FO) stays in the low state during fault-out time (typical 110  $\mu$ s) when the duration of under-voltage condition (t<sub>UVLO</sub>) less than fault-out time (t<sub>FAULT</sub>) as shown in Figure 47.

Figure 47. Timing chart of t<sub>UVLO</sub> < t<sub>FAULT</sub> condition

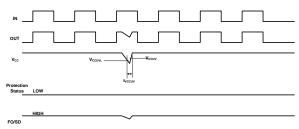

Gate drive output and fault output (FO) does not change when an under-voltage duration ( $t_{UVLO}$ ) less than under voltage filter time ( $t_{VCCUV}$ ) as shown in Figure 48.

Figure 48. Timing chart of t<sub>UVLO</sub> < t<sub>VCCUV</sub> condition

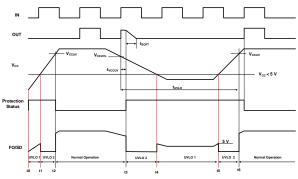

#### In case of very low V<sub>cc</sub> (V<sub>cc</sub> < 5 V) If V<sub>CC</sub> is lower than 5 V (UVLO 1 case: $t_0 \sim t_1$ , and $t_4 \sim t_5$ ), the fault signal cannot be driven to LOW state because V<sub>CC</sub> is not enough to drive internal circuit as shown in Figure 49.

Figure 49. Timing chart of V<sub>CC</sub> less than 5 V

#### **Over-Current Protection**

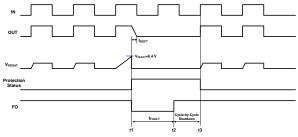

The CIN pin is used for sensing the current. The current sensing circuit includes a Leading Edge Blanking (LEB) time to ensure there is no nuisance tripping during device switch on ( $t_{CINBLT}$ , typically 300 ns). When the input is turned off the fault signal is cleared and the IC is reset. On the next active input signal the IC will repeat the operation described above if the over-current condition remains. Hence the over current control is on a cycle-by-cycle basis. Figure 50 shows the waveform definitions of FO, and an output of low-side driver; which uses a soft turn-off method when the current-sense pin (CIN) recognizes a fault.

Figure 50. Timing chart of OCP Condition

#### **Desaturation Protection**

The desaturation detection technique for identifying a short circuit and fault condition in an IGBT is well known. Generally, a desaturation condition is said to exist if the voltage across the IGBT collector to emitter terminals rises above 5~8 volts while the gate to emitter voltage is high. This condition indicates that the current through the IGBT has exceeded the normal operating level. The gate drive circuit should be designed so that it reacts promptly to the short circuit and safely turns off the IGBT within Short-Circuit Withstand Time (SCWT) rating of the IGBT. However, in recent years, IGBTs have been designed with lower conduction and switching losses but this generally reduces SCWT. A desaturation fault detection circuit provides protection for power semiconductor switches (IGBT or MOSFETs) against short-circuit current events which may lead to destruction of these power switches. The IGBT collector-emitter voltage, V<sub>CESAT</sub>, is monitored by the DESAT pin of the gate driver. When there is short circuit in an application and a very high current flow through the IGBT, it will go into the desaturation mode; hence its V<sub>CESAT</sub> voltage will rise. A fault is detected by the gate driver (while the IGBT is on) once this V<sub>CESAT</sub> voltage goes above the internal desaturation fault detection threshold voltage, which has typically 6.4 V. This fault detection triggers two events:

- Output of the gate driver is slowly brought low in order to "softly" turn off the IGBT and prevent large di/dt induced voltage spikes.

- Fault output (FO/SD) goes to low for the purpose of notifying the microcontroller of the fault condition. At this point, the microcontroller must take the appropriate action to shutdown.

Figure 51 show the desaturation protection circuit, which has 2.8  $\mu$ s internal desaturation blacking timer. So that, external blank capacitor, C<sub>DESAT</sub>, is not needed for blanking time less than 2.8  $\mu$ s.

Figure 51. Desaturation Detection Circuit

#### **Consider of Blanking Time**

The DESAT fault detection circuitry should remain disabled for a short time period following the turn-on of the IGBT to allow the collector voltage to fall below the DESAT threshold. The time period, called the DESAT blanking time, ensures that there is no nuisance tripping during IGBT turn-on. This time also represents the time it takes for the driver to detect a fault condition. For typical applications, the two external components required to build the DESAT circuit are the DESAT diode, D<sub>DESAT</sub>, and DESAT resistor, R<sub>DESAT</sub> and default blanking time has typically 2.8 µs. Also, it is possibile to increase the blanking time by adding an external blank capacitor, C<sub>DESAT</sub>. During operation, blank capacitor is discharged when the driver output is low (IGBT off). That is, the DESAT detection features becomes active only when the output of the gate driver is in the high state, driving the IGBT into saturation. When the IGBT is turned on, the DESAT capacitor starts charging and protection becomes effective only if the DESAT threshold is exceeded after the blanking time.

#### Consider of DESAT Resistor (RDESAT)

Switching inductive loads causes large instantaneous forward voltage transients across the freewheeling diodes of IGBTs. These transients result in large negative voltage spikes on the DESAT pin which draw substantial current out of the device. To limit the current level drawn from the gate driver, a DESAT resistor ( $R_{DESAT}$ ) can be added in series with the DESAT diode ( $D_{DESAT}$ ). The added resistor will not appreciably alter the DESAT threshold or the blanking time. The DESAT resistance value is chosen considering the  $V_{CESAT}$  of IGBT, forward voltage drop of DESAT diode, and threshold voltage of DESAT comparator. The sum of  $V_{CESAT}$  of IGBT and total voltage drop of DESAT diode and resistor must be less than threshold voltage of DESAT comparator.

$$(V_{DESAT} - 1.5) \ge (V_{CESAT} + (R_{DESAT} \times I_{DESAT}) + V_D)$$

(2)

Where,  $V_{CESAT}$  is saturation voltage of IGBT at maximum operating temperature and  $V_D$  is voltage forward drop of DESAT diode. The output voltage is soft turned off and FO/SD goes to LOW state when the  $V_{DESAT}$  voltage goes higher than specified threshold voltage (typically 6.4 V) as shown in Figure 52.

Figure 52. Waveform Definition of Desaturation

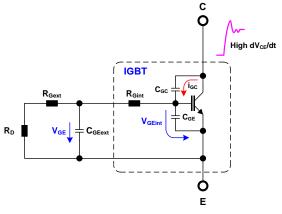

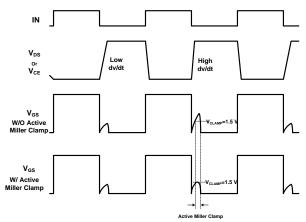

#### **Active Miller Clamp**

Any change in the collector-emitter voltage ( $V_{CE}$ ) causes a displacement current (Miller current) through the Miller capacitance ( $C_{GC}$ ). The value of the current is calculated approximately from the product of the magnitude of the Miller capacitance and the rate of change of the collector-emitter voltage.

$$i_{GC} = C_{GC} \frac{dv_{CE}}{dt}$$

(3)

The displacement current i<sub>GC</sub> increases the voltage at the gate-emitter capacitance  $(C_{GE})$  and thus the gate-emitter voltage V<sub>GE</sub>' of the IGBT. The amplitude of the voltage depends on the capacitive voltage divider of the internal semiconductor capacitances C<sub>GC</sub> and C<sub>GE</sub>, the internal gate resistance RGint, and the gate's external circuitry. Once the gate-emitter voltage  $V_{GE}$ ' reaches the threshold voltage, the IGBT begins to change into the conductive state. A cross-current begins to flow in the phase leg, causing additional losses in both the IGBTs of the bridge leg concerned. (This phenomenon is also known as Miller-induced shoot-through). Neglecting the parasitic inductances in the gate circuit it reduces the equivalent circuit diagram of the feedback circuit to the RCnetwork shown in Figure 53. Once the IGBT is in steady state and the change of the collector-emitter voltage is constant, the gate-emitter voltage  $V_{GEint}$  caused by the displacement current depends on the sum of the gate resistor values and the internal driver resistance ( $R_{GES} =$  $R_{Gext} + R_{Gint} + R_D$ ). The larger the summed resistance, the larger the gate-emitter voltage ( $V_{GEint} = R_{GES} \cdot i_{GC}$ ). The gate-emitter voltage time function is determined by the time constant of the RC-network connected. The larger the capacitances of the network, the longer it takes for the steady state to arrive.

Figure 53. Equivalent circuit of the gate drive

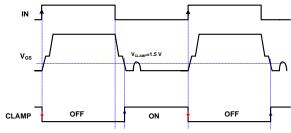

The FAN3181 has an active Miller clamp function to prevent IGBT to turn on due to high collector-to-emitter dv/dt induced during the switching sequence, the GS pin is connected to IGBT gate and Miller current is sinking through a low impedance CLAMP switch. The CLAMP switch is opened when the input is high state and is closed when the actual gate voltage goes to below Clamp threshold voltage (Typically 1.5 V) during turn-off. In this way, the CLAMP function doesn't affect the turn-off characteristic, but only keeps the gate output low during the off time as shown in Figure 54.

Figure 54. Schematic of Active Miller Clamp

The waveform shown in Figure 55 proves how using the Active Miller Clamp provides a consistent reduction of the voltage spike on MOSFET/IGBT gate cause by dV/dt when gate turn-off.

Figure 55. Waveform Definition of Active Miller Clamp

The Miller CLAMP circuit is designed for Miller current typically 1.0 A. When the IGBT is turned-off and the gate driving voltage below 1.5 V the CLAMP current output is activated as shown in Figure 56.

Figure 56. Waveform of Active Miller Clamp

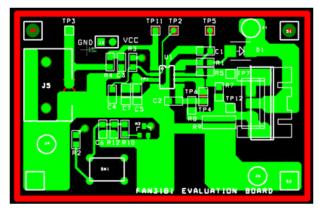

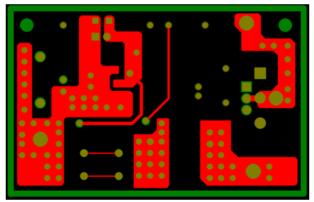

#### **PCB Layout Guideline**

To improve the switching characteristics and efficiency of design, the following should be considered before beginning a PCB layout.

- Should be minimize influence of the parasitic inductance and capacitance on the layout.

- The bypass capacitor for V<sub>CC</sub> should be placed as close as possible to the V<sub>CC</sub> pin.

- The gate driver should be located switching device as close as possible to gate driver.

- A RC filter with 51  $\Omega$  to 100  $\Omega$  and 1 nF for IN pin is recommended.

Figure 57. Top View

Figure 58. Bottom View

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor haves against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death a

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

© Semiconductor Components Industries, LLC

### **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Onsemi: FAN3181TMX