# GaN EiceDRIVER™ product family

Single-channel functional and reinforced isolated gate-drive ICs for high voltage enhancement-mode GaN HEMTs

#### Features

- Dedicated gate driver ICs for Infineon's high voltage GaN power switches (CoolGaN™, X-GaN™)

- low driving impedance (on-resistance  $0.85 \Omega$  source,  $0.35 \Omega$  sink)

- resistor programmable gate current (typ. 10 mA) in steady "on" state

- programmable negative gate voltage to completely avoid spurious turn-on

- Single output supply voltage (typ. 8 V, floating)

- Switching behavior independent of duty-cycle (2"off" voltage levels)

- Differential concept to ensure negative gate drive voltage under any condition

- Fast input-to-output propagation (37 ns) with excellent stability (+7/-6 ns)

- Galvanic input-to-output isolation based on coreless transformer (CT) technology

- Common mode transient immunity (CMTI) > 200 V/ns

- 3 package versions

- 1EDF5673K: 13-pin LGA (5 x 5 mm, PG-TFLGA-13-1) for functional isolation (1.5 kV)

- 1EDF5673F: 16-pin P-DSO (150 mil, PG-DSO-16-11) for functional isolation (1.5 kV)

- 1EDS5663H: 16-pin P-DSO (300 mil, PG-DSO-16-30) for safe isolation (6 kV)

- Fully qualified according to JEDEC for Industrial Applications

#### Description

CoolGaN<sup>™</sup> and similar GaN switches require a continuous gate current of a few mA in their "on" state. Besides, due to low threshold voltage and extremely fast switching transients, a negative "off" voltage level may be needed. The widely used RC-coupled gate driver fulfils these requirements, however it suffers from a duty-cycle dependence of switching dynamics and the lack of negative gate drive in specific situations.

Infineon's GaN EiceDRIVER<sup>™</sup> solves these issues with very low effort. The two output stages shown below enable a zero "off" level to eliminate any duty-cycle dependence. In addition, the differential topology is able to provide negative gate drive without the need for a negative supply voltage. However, it requires a floating supply voltage not compatible with bootstrapping.

#### **Potential applications**

- High-voltage AC/DC conversion

- High-voltage DC/DC conversion

in server and telecom SMPS

#### Isolation and safety approval

- 1EDS5663H with reinforced isolation: certification by VDE, UL, CSA, CQC according to

- DIN V VDE V 0884-10 (2006-12) with  $V_{IOTM} = 8 kV_{pk}$ ,  $V_{IOSM} = 6.25 kV_{pk}$  (tested at 10  $kV_{pk}$ )

- UL1577 (Ed. 5) with  $V_{\rm ISO}$  = 5700  $V_{\rm RMS}$

- IEC60950 and IEC602386 system standards and corresponding CQC certificates

- 1EDF5673K and 1EDF5673F with functional isolation: production test with 1.5 kV for 10 ms

#### **Product versions**

In accordance with the isolation classification for primary and secondary side control, GaN EiceDRIVER<sup>™</sup> is available in different package versions

| Part      | Package            | Source/sink          | Input-to-output isolation |                                                                                |                                                      |                                                  |  |  |  |  |

|-----------|--------------------|----------------------|---------------------------|--------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------|--|--|--|--|

| number    |                    | output<br>resistance | Isolation class           | Rating                                                                         | Surge testing                                        | Safety<br>certification <sup>1)</sup>            |  |  |  |  |

| 1EDF5673K | LGA-13<br>5 x 5 mm | 0.85 Ω / 0.35 Ω      | functional                | V <sub>IO</sub> = 1.5 kV <sub>DC</sub>                                         | n.a                                                  | n.a                                              |  |  |  |  |

| 1EDF5673F | DSO-16<br>150 mil  | 0.85 Ω / 0.35 Ω      | functional                | V <sub>IO</sub> = 1.5 kV <sub>DC</sub>                                         | n.a                                                  | n.a                                              |  |  |  |  |

| 1EDS5663H | DSO-16<br>300 mil  | 0.85 Ω / 0.35 Ω      | reinforced<br>(safe)      | $V_{IOTM} = 8 kV_{pk}$<br>(VDE0884-10)<br>$V_{ISO} = 5.7 kV_{RMS}$<br>(UL1577) | V <sub>IOSM</sub> >10 kV <sub>pk</sub><br>(IEC60065) | VDE0884-10<br>UL1577<br>IEC60950,<br>62386 (CQC) |  |  |  |  |

#### Table 1 GaN EiceDRIVER<sup>™</sup> product family overview

1) certification pending

# **Table of Contents**

|                                                                                        | Features                                                                                                                                                                                                                                                         | . 1                                          |

|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|                                                                                        | Table of Contents                                                                                                                                                                                                                                                | 3                                            |

| 1                                                                                      | Pin configuration and description                                                                                                                                                                                                                                | 4                                            |

| 2                                                                                      | Background and system description                                                                                                                                                                                                                                | 5                                            |

| <b>3</b><br>3.1<br>3.2<br>3.3<br>3.3.1<br>3.3.2<br>3.4<br>3.5<br>3.6                   | Functional description         Block diagram         Isolation         Power supply         Input supply voltage         Output supply voltage         Driver outputs         Undervoltage Lockout (UVLO)         CT communication and data transmission         | <b>8</b><br>8<br>9<br>9<br>9<br>9<br>9<br>10 |

| <ul> <li>3.7</li> <li>4</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> </ul> | Signal timing<br>Electrical characteristics<br>Absolute maximum ratings<br>Thermal characteristics<br>Operating range<br>Electrical characteristics                                                                                                              | <b>11</b><br>11<br>12<br>13                  |

| 5                                                                                      | Timing diagrams                                                                                                                                                                                                                                                  | 16                                           |

| 6                                                                                      | Typical characteristics                                                                                                                                                                                                                                          | 17                                           |

| <b>7</b><br>7.1<br>7.1.1<br>7.1.2<br>7.2<br>7.3                                        | Isolation specificationsFunctional isolation specificationsFunctional isolation in PG-TFLGA-13-1 package (1EDF5673K)Functional isolation in NB PG-DSO-16-11 package (1EDF5673F)Reinforced isolation in WB PG-DSO-16-30 package (1EDS5663H)Safety-limiting values | 21<br>21<br>22<br>23                         |

| 8                                                                                      | Application circuit                                                                                                                                                                                                                                              | 25                                           |

| 9                                                                                      | Layout guidelines                                                                                                                                                                                                                                                | 26                                           |

| <b>10</b><br>10.1<br>10.2<br>10.3                                                      | Package informationPackage PG-TFLGA-13-1Package PG-DSO-16-11Package PG-DSO-16-30                                                                                                                                                                                 | 28<br>30                                     |

| 11                                                                                     | Device numbers and markings                                                                                                                                                                                                                                      | 33                                           |

| 12                                                                                     | Revision History                                                                                                                                                                                                                                                 | 34                                           |

Pin configuration and description

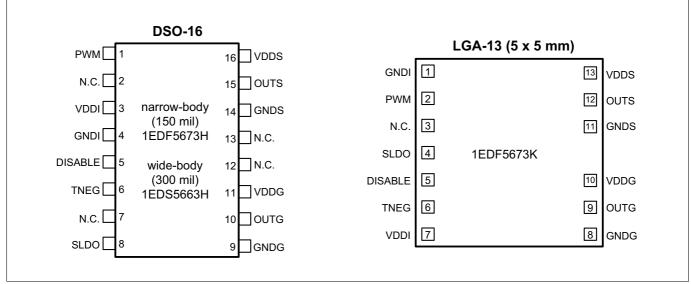

# 1 Pin configuration and description

#### Figure 1 Pin configuration for DSO-16 and LGA-13 packages, top view

| Table 2 | Pin de  | escription |                                                                                                                                                   |  |  |  |  |  |  |  |

|---------|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pin DSO | Pin LGA | Symbol     | Description                                                                                                                                       |  |  |  |  |  |  |  |

| 1       | 2       | PWM        | Input signal (default state Low)<br>Controls switching sequence at OUTG and OUTS                                                                  |  |  |  |  |  |  |  |

| 2       | 3       | N.C.       | Do not connect                                                                                                                                    |  |  |  |  |  |  |  |

| 3       | 7       | VDDI       | Input supply voltage (+3.3 V)                                                                                                                     |  |  |  |  |  |  |  |

| 4       | 1       | GNDI       | Input GND                                                                                                                                         |  |  |  |  |  |  |  |

| 5       | 5       | DISABLE    | Input signal (defaut state Low)<br>Logic High is equivalent to a low state at PWM input                                                           |  |  |  |  |  |  |  |

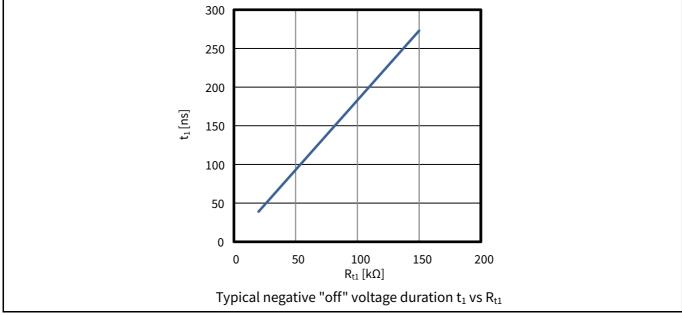

| 6       | 6       | TNEG       | Resistor programmable input to control the duration $t_1$ of negative "off" level ( <b>Figure 4</b> ); $t_1 = R_{t1} * 1.8 \text{ pF}$            |  |  |  |  |  |  |  |

| 7       | 7       | N.C.       | Not connected                                                                                                                                     |  |  |  |  |  |  |  |

| 8       | 4       | SLDO       | N.C. or connected to VDDI: applied voltate (3.3 V) directly used as input supply voltage<br>Connected to GNDI: Internal shunt regulator activated |  |  |  |  |  |  |  |

| 9       | 8       | GNDG       | Ground for OUTG                                                                                                                                   |  |  |  |  |  |  |  |

| 10      | 9       | OUTG       | Output connectd to GaN gate                                                                                                                       |  |  |  |  |  |  |  |

| 11      | 10      | VDDG       | Positive supply for gate connected output stage                                                                                                   |  |  |  |  |  |  |  |

| 12      | -       | N.C.       | Not connected                                                                                                                                     |  |  |  |  |  |  |  |

| 13      | -       | N.C.       | Not connected                                                                                                                                     |  |  |  |  |  |  |  |

| 14      | 11      | GNDS       | Ground for OUTS (has to be connected with GNDG)                                                                                                   |  |  |  |  |  |  |  |

| 15      | 12      | OUTS       | Output connected to GaN source                                                                                                                    |  |  |  |  |  |  |  |

| 16      | 13      | VDDS       | Positive supply voltage for source connected output stage (has to be connected with VDDG)                                                         |  |  |  |  |  |  |  |

#### Background and system description

## 2 Background and system description

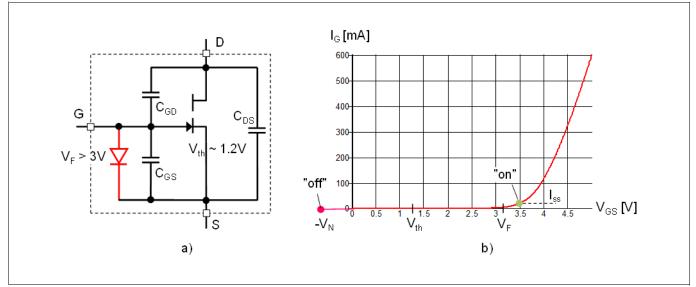

Although gallium nitride high electron mobility transistors (GaN HEMTs) with ohmic pGaN gate like Infineon's 600 V CoolGaN<sup>TM</sup> power switches are robust enhancement-mode ("normally-on") devices, they differ significantly from MOSFETs. The gate module is not isolated from the channel, but behaves like a diode with a forward voltage  $V_{\rm F}$  of 3 to 4 V. Equivalent circuit and typical gate input characteristic are given in **Figure 2**. In the steady "on" state a continuous gate current is required to achieve stable operating conditions. The switch is "normally-off", but the threshold voltage  $V_{\rm th}$  is rather low (~ +1 V). This is why in certain applications a negative gate voltage  $-V_{\rm N}$ , typically in the range of several volts, is required to safely keep the switch "off" (**Figure 2**b).

Figure 2 Equivalent circuit (a) and gate input characteristics (b) of typical normally-off GaN HEMT

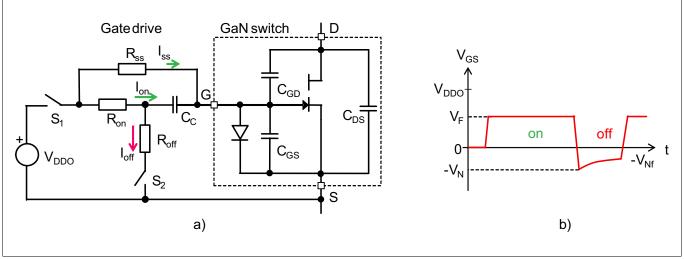

Obviously the transistor in **Figure 2** cannot be driven like a conventional MOSFET due to the need for a steadystate "on" current  $I_{ss}$  and a negative "off" voltage  $-V_N$ . While an  $I_{ss}$  of a few mA is sufficient, fast switching transients require gate charging currents  $I_{on}$  and  $I_{off}$  in the 1 A range. To avoid a dedicated driver with 2 separate "on" paths and bipolar supply voltage, the solution depicted in **Figure 3** is usually chosen, combining a standard gate driver with a passive RC circuit to achieve the intended behavior. The high-current paths containing the small gate resistors  $R_{on}$  and  $R_{off}$ , respectively, are connected to the gate via a coupling capacitance  $C_c$ .  $C_c$  is chosen to have no significant effect on the dynamic gate currents  $I_{on}$  and  $I_{off}$ . In parallel to the high-current charging path the much larger resistor  $R_{ss}$  forms a direct gate connection to continuously deliver the small steady-state gate current,  $I_{ss}$ . In addition,  $C_c$  can be used to generate a negative gate voltage. Obviously, in the "on"-state  $C_c$  is charged to the difference of driver supply  $V_{DDO}$  and diode voltage  $V_F$ . When switching to the "off" state, this charge is redistributed between  $C_c$  and  $C_{GS}$  and causes an initial negative  $V_{GS}$  of value

(2.1)

$$-V_N = -\frac{C_C \cdot (V_{DDO} - V_F) - Q_{Gtot}}{C_C + C_{GS}}$$

with  $Q_{\text{Gtot}}$  denoting the total switching gate charge (e.g. 5 nC for a 70 m $\Omega$  transistor).  $V_{\text{N}}$  can thus be controlled by proper choice of  $V_{\text{DDO}}$  and  $C_{\text{C}}$ . During the "off" state the negative  $V_{\text{GS}}$  decreases, as  $C_{\text{C}}$  is discharged via  $R_{\text{ss}}$ . The associated time constant cannot be chosen independently, but is related to the steady-state current and is typically in the 1 s range. The negative gate voltage at the end of the "off" phase ( $V_{\text{Nf}}$  in **Figure 3**b) thus depends on the "off" duration. It lowers the effective driver voltage for the following switching "on" event, resulting in a dependence of switching dynamics on frequency and duty cycle as one drawback of this approach.

### **Background and system description**

Figure 3 Equivalent circuit of GaN switch with RC gate drive (a) and gate-to-source voltage V<sub>GS</sub> (b)

A second problem might happen if two switches are used alternately in a half-bridge configuration. In normal operation always one of the switches is "on", and before switching on the other one, it has to be switched off, thereby generating the negative gate voltage  $V_{\rm N}$ . The usually short period with both switches "off" (dead time  $t_{\rm d}$ ) does not cause a significant increase of  $V_{\rm GS}$ . If, however, there is by any reason a longer period with both switches in "off" state (e.g. during system start-up, burst mode operation etc.), both coupling capacitors ( $C_{\rm C}$ ) will be discharged. Thus, for the first switching pulse after such an extended non-switching period no negative voltage is available. This could lead to increased transistor stress or even instabilities due to spurious turn-on effects in half-bridge topologies.

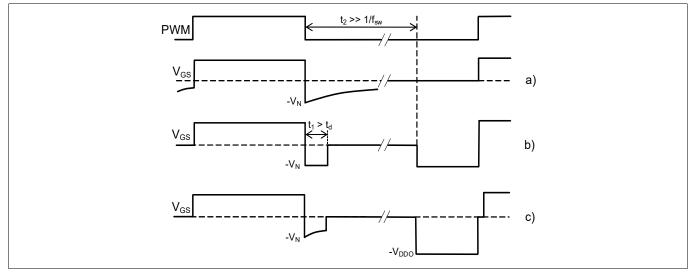

To solve the problems described above, a shape of  $V_{GS}$  like the one in **Figure 4**b) would be required rather than the one in **Figure 4**a) which results from the simple RC circuit. As explained, a negative  $V_{GS}$  might be needed for safe "off" states during the switching transients, but it should be as low as possible. Due to the lack of a physical body diode any negative  $V_{GS}$  adds to the voltage drop of a GaN transistor in reverse polarity (diode operation) thereby increasing the conduction losses during dead time. Thus in the idealized waveform of **Figure 4**b)  $V_{GS}$  is switched to the minimum required  $V_N$  for a constant time  $t_1$  longer than the system dead time  $t_d$ . After that  $V_{GS}$  is switched back to zero to ensure identical conditions for the next switch "on" event and to minimize losses from diode operation. If, however, an "off" state lasts for a time  $t_2$  significantly longer than a normal switching period  $1/f_{SW}$  (e.g. several  $\mu$ s),  $V_{GS}$  should be switched again to  $-V_N$  to avoid the described "first pulse" problem.

Figure 4 *V*<sub>GS</sub> voltage waveforms with RC circuit (a), improved (b) and proposed shape (c)

#### Background and system description

The conceptual goal of the GaN EiceDRIVER<sup>M</sup> is to provide the gate voltage of **Figure 4**b) or a functional equivalent without significantly increasing driving complexity. This is achieved by slightly modifying the gate drive waveform as depicted in **Figure 4**c). The "off" level after a long deadtime need not be the optimized negative voltage - $V_N$ , it could also be the more negative level - $V_{DDO}$ . As these "first pulse" situations happen very rarely compared with regular switching cycles, the resulting higher reverse voltage drop has negligible effect on switching losses.

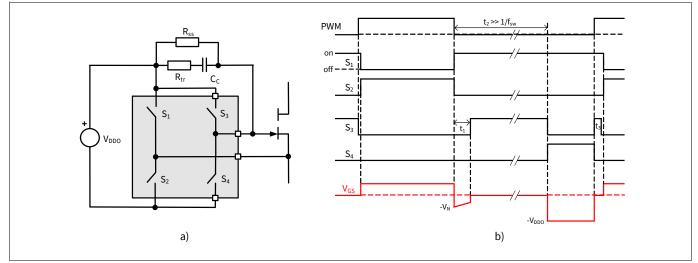

Although going from the 3-level signal of **Figure 4**b) to the 4 levels of **Figure 4**c) seems to increase complexity at first sight, this is finally not true. Waveform **Figure 4**c) can be realized in a very convenient way, if  $V_N$  is generated by the RC network as described above. Then the differential driver concept of **Figure 5**a) with switch control signals as given in **Figure 5**b) is able to fulfil all discussed requirements with lowest effort: a single supply voltage, 4 switches and 4 connection pins are sufficient.

As mentioned, utilizing  $-V_{DDO}$  instead of  $-V_N$  only during extended "off"-phases has no impact on switching losses. However, care has to be taken when switching on again, because  $C_C$  is fully charged to  $V_{DDO}$  in this "first pulse" situation and no current flow is possible via the capacitive path. With the standard switching-on scheme (open  $S_1$  / close  $S_2$ ) the transient current thus would be limited to the small steady-state current. To achieve a faster turn-on,  $C_{GS}$  will be discharged prior to the "on"-transient by switching on  $S_3$  for a short time  $t_3$  before initiating the actual "on"-transient via  $S_1$  and  $S_2$ . A  $t_3$ -duration of typically 20 ns is sufficient.

Figure 5 GaN EiceDRIVER<sup>™</sup> concept (a) and switch control signals (b)

In the topology of **Figure 5**a) a single resistor  $R_{tr}$  is responsible for setting the maximum transient charging and discharging current. This is often acceptable. If it is not, an additional resistor  $R_{off}$  with series diode in parallel with  $R_{tr}$  can be used to realize different impedances for "on" and "off" transients, respectively. All relevant driving parameters are thus easily programmable by choosing  $V_{DDO}$ ,  $R_{ss}$ ,  $R_{tr}$ ,  $R_{off}$  and  $C_{C}$  according to **Equation (2.1)** and the relations

(2.2)

$$I_{ss} = \frac{V_{DDO} - V_F}{R_{ss}}, \qquad I_{on,max} = \frac{V_{DDO}}{R_{tr}}, \qquad I_{off,max} = \frac{V_{th} + V_N}{R_{off}//R_{tr}}$$

Functional description

## 3 Functional description

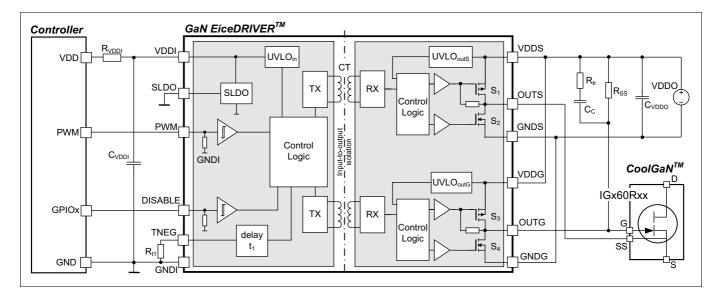

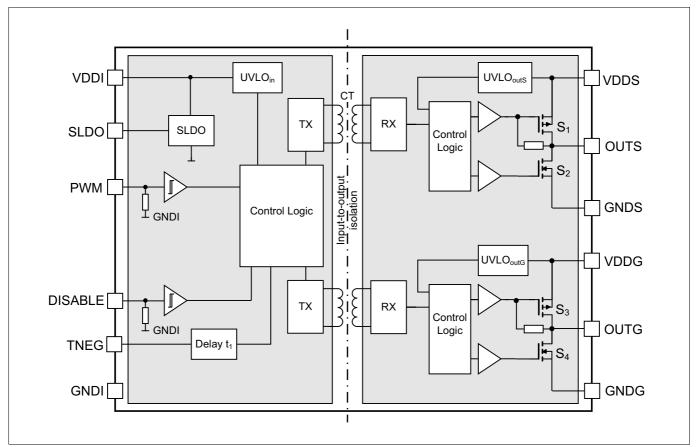

## 3.1 Block diagram

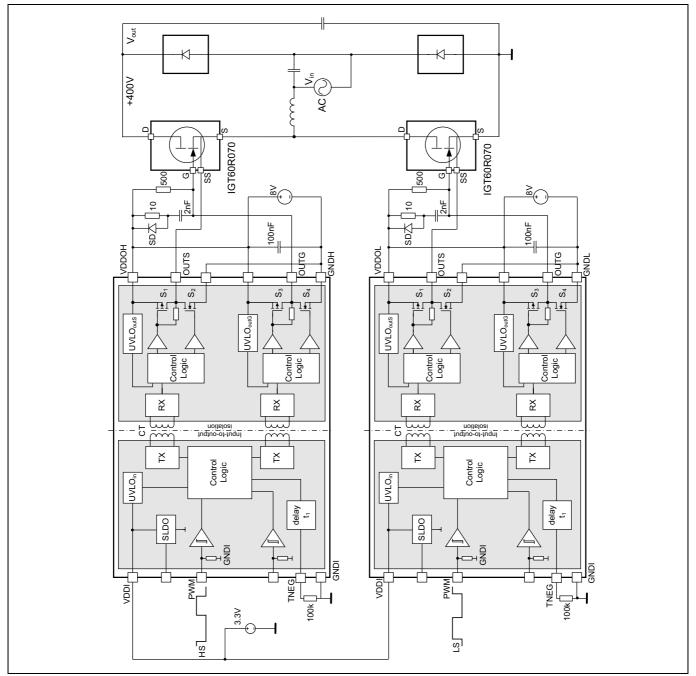

A simplified functional block diagram of the GaN EiceDRIVER<sup>™</sup> is given in **Figure 6**. The 4 output transistors are placed on 2 separate dies. Isolation between input and outputs is achieved by means of two coreless transformer structures (CT) situated on the input die.

## 3.2 Isolation

The GaN EiceDRIVER<sup>™</sup> is available in three package versions in accordance with different classes of input-tooutput isolation voltage requirements

- 1EDF5673K in LGA-13 5 x 5 mm package for functional isolation (1.5 kV)

- 1EDF5673F in DSO-16 narrow-body (150 mil) package for functional isolation (1.5 kV)

- 1EDS5663H in DSO-16 wide-body (300 mil) package for reinforced safe isolation (6 kV)

In SMPS functional isolation is typical for high-voltage systems that are controlled from their primary side, whereas high-voltage switches controlled from the secondary side require safe isolation.

The safe isolation version 1EDS5663H is tested according to VDE0884-10 / IEC60747-17 standards as specified in **Table 15** to **Table 18**. As the CT forming this barrier is placed on the input die, a true "fail-safe" isolation is achieved, i.e. even in case of a destruction of the power switch the driver input remains safely isolated from the output.

### **Functional description**

## 3.3 Power supply

Due to the isolation between input and output side, two power domains with independent power management are required. Undervoltage Lockout (UVLO) functions for both input and output supplies ensure a defined startup and robust functionality under all operating conditions.

## 3.3.1 Input supply voltage

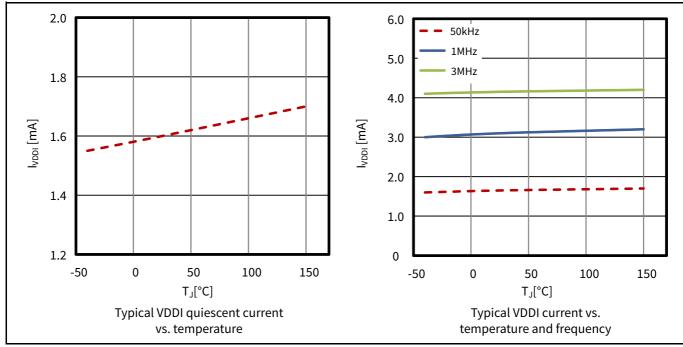

The input die is supplied via VDDI with a nominal voltage of 3.3 V. Power consumption to some extent depends on switching frequency, as the input signal is converted into a train of repetitive current pulses to drive the coreless transformer. Due to the chosen robust encoding scheme the average repetition rate of these pulses and thus the average supply current depends on the switching frequency  $f_{sw}$ . However, for  $f_{sw} < 500$  kHz this effect is very small.

The input side can also be operated with supply voltages higher than 3.3 V. Then a shunt LDO voltage regulator (SLDO) is enabled by connecting pin SLDO to GND. The SLDO regulates the current through an external resistor  $R_{VDDI}$  connected between the external supply voltage VDD and pin VDDI as depicted in the typical application circuit on **Page 1** to generate the required voltage drop. For proper operation it has to be ensured that the current through  $R_{VDDI}$  always exceeds the maximum supply current  $I_{VDDI,max}$  of the input chip.  $R_{VDDI}$  thus has to fulfil

(3.1)

$$R_{VDDI} < \frac{V_{DD} - 3.3V}{I_{VDDI,max}}$$

A typical choice for  $V_{DD}$  = 5 V could be  $R_{VDDI}$  = 470  $\Omega$ , resulting in sufficient margin between resistor current and maximum average operating current. As usual, the dynamic peak current is provided by a blocking cap (10 to 22 nF) between  $V_{DDI}$  and GNDI.

## 3.3.2 Output supply voltage

Both output dies and the respective output switches are supplied by a common voltage of typically 8 V between pins VDDS/G and GNDS/G. A ceramic bypass capacitance in the 20 to 100 nF range has to be placed close to the supply pins. The output supply must be floating with respect to the input supply system. This is not only required by the Kelvin source connection of the GaN switch (results in inductive voltage peaks between input and output ground during switching transient), but also by the differential driving concept as explained in **Chapter 2**.

Again the minimum operating supply voltage is set by an undervoltage lockout function (UVLO<sub>out</sub>), operating independently of the input UVLO function.

## 3.4 Driver outputs

The rail-to-rail driver output stage realized with complementary MOS transistors is able to provide a typical 4 A sourcing and 8 A sinking current. Although these current levels are neither needed nor reached when driving GaN HEMTs (due to their low gate charge of only a few nC), the low on-resistance coming together with high driving current is nevertheless beneficial. With an  $R_{on}$  of 0.85  $\Omega$  for the sourcing pMOS and 0.35  $\Omega$  for the sinking nMOS transistor the driver can be considered as a nearly ideal switch. The gate drive parameters can thus be determined easily and accurately by the external components as described in **Chapter 2**. The p-channel sourcing transistor enables real rail-to-rail behavior without suffering from the voltage drop unavoidably associated with nMOS source follower stages.

### Functional description

## 3.5 Undervoltage Lockout (UVLO)

The Undervoltage Lockout function ensures that the outputs can be switched only, if both input and output supply voltages exceed the corresponding UVLO threshold voltages. Thus it can be guaranteed, that the switch transistors are not operated, if the driving voltage is too low for complete and fast switching on, thereby avoiding excessive power dissipation.

The UVLO levels for the output supply are set to a typical "on" value of 4.5 and 5.5 V (with 0.3 V hysteresis) for OUTG and OUTS, respectively, whereas UVLO<sub>in</sub> for VDDI is set to 2.85 V with 0.15 V hysteresis. The different UVLO levels for OUTG and OUTS help to safely avoid any erroneous turn-on of the GaN switch despite the low GaN threshold voltage. Special attention has been paid to cover all possible operating conditions, like start-up or arbitrary supply voltage situations:

- if V<sub>DDI</sub> drops below UVLO<sub>in</sub>, a "switch-to-low" command is sent to output OUTG, whereas OUTS is switched to "high"; this corresponds to the final state in extended "off" periods with V<sub>GS</sub> = -V<sub>DDO</sub>

- for V<sub>DD</sub> lower than the output UVLO levels, an effective clamping concept has been realized by means of 100 kΩ resistors connecting the outputs OUTS and OUTG to the respective gates of the sourcing pMOS transistors in the output stage

As a result, safe operation of the GaN switch can be guaranteed under any circumstances.

## 3.6 CT communication and data transmission

A coreless transformer (CT) based communication module is used for PWM signal transfer between input and outputs. A proven high-resolution pulse repetition scheme in the transmitter combined with a watchdog timeout at the receiver side enables recovery from communication fails and ensures safe system shut-down in failure cases.

Besides, the repetition scheme is also used to signal a "first pulse" situation (**Figure 5**). If an "off"-state lasts longer than 32  $\mu$ s, the repetition rate of the CT pulses is reduced to a value that causes the watchdog on the output chip to wake up and initiate a change in the "off" state acc. to **Figure 5** (switch  $S_3$  to "off" and  $S_4$  to "on" state).

## 3.7 Signal timing

From the above, the extended "off"-phase  $t_2$  defining a "first pulse" situation, is fixed at a typical value of 32 µs. The other important timing parameter  $t_1$ , i.e. the duration of the negative "off"-voltage, can be programmed by a resistor  $R_{t1}$  connected from TNEG to GNDI according to  $t_1 = R_{t1} * 1.8$  pF. As the main idea is to keep the switch in a safe "off" state during the switching transient,  $t_1$  must be longer than the system dead time  $t_d$ , i.e. the maximum time between an "off"-command and the subsequent switching transient. The upper limit for  $t_1$  obviously is the minimum "off"-period; thus there is usually sufficient margin in the choice of  $t_1$ .

However, it should be mentioned that the actual value of  $t_1$  can be influenced by the switching transient itself due

to small, but unavoidable coupling capacitances between output and input pins. Even with an optimized PCB layout, capacitances inside the package may cause a shortening of  $t_1$  for the high-side switch in fast-switching half-bridges to approx. 50% of the static value. Nevertheless, as the effect is triggered by the transient of the switching node, the essential requirement, i.e.to apply the negative gate voltage during this transient, is always met and the described behavior does not cause any adverse effect in the system.

#### **Electrical characteristics**

## 4 Electrical characteristics

### 4.1 Absolute maximum ratings

The absolute maximum ratings are listed in **Table 3**. Stresses beyond these values may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameter                                         | Symbol                                 |      | Values |                        | Unit            | <b>Note or Test Condition</b>               |  |

|---------------------------------------------------|----------------------------------------|------|--------|------------------------|-----------------|---------------------------------------------|--|

|                                                   |                                        | Min. | Тур.   | Max.                   |                 |                                             |  |

| Input supply voltage                              | V <sub>DDI</sub>                       | -0.3 | -      | 3.7                    | V               | SLDO inactive (N.C. or connected to VDDI)   |  |

| Output supply voltage                             | V <sub>DDO</sub>                       | -0.3 | -      | 22                     | V               | -                                           |  |

| Voltage at pins PWM and                           | V <sub>IN</sub>                        | -0.3 | _      | 17                     | V               | -                                           |  |

| DISABLE                                           |                                        | -5   | _      | _                      | V               | < 50 ns for transient <sup>1)</sup>         |  |

| Voltage at pins TNEG and SLDO                     | V <sub>TNEG</sub><br>V <sub>SLDO</sub> | -0.3 | -      | V <sub>DDI</sub> + 0.3 | V               | -                                           |  |

| Voltage at pins OUTS, OUTG                        | V <sub>OUTS/G</sub>                    | -0.3 | -      | V <sub>DDO</sub> + 0.3 | V               | -                                           |  |

|                                                   |                                        | -2   | _      | V <sub>DDO</sub> + 1.5 | V               | < 200 ns <sup>1)</sup>                      |  |

| Reverse current peak at pins                      | I <sub>SRC_rev</sub>                   | -5   | -      | -                      | A <sub>pk</sub> | < 500 ns <sup>1)</sup>                      |  |

| OUTS, OUTG                                        | I <sub>SNK_rev</sub>                   | _    | _      | 5                      | A <sub>pk</sub> |                                             |  |

| Non-destructive Common<br>Mode Transient Immunity | СМТІ                                   | 400  | -      | -                      | V/ns            | outputs with respect to input               |  |

| Junction temperature                              | T                                      | -40  | _      | 150                    | °C              | -                                           |  |

| Storage temperature                               | T <sub>STG</sub>                       | -65  | _      | 150                    | °C              | -                                           |  |

| Soldering temperature                             | T <sub>SOL</sub>                       | _    | _      | 260                    | °C              | reflow / wave soldering <sup>2)</sup>       |  |

| ESD capability                                    | V <sub>esd_cdm</sub>                   | -    | -      | 0.5                    | kV              | Charged Device Model<br>(CDM) <sup>3)</sup> |  |

| ESD capability                                    | V <sub>ESD_HBM</sub>                   | -    | -      | 2                      | kV              | Human Body Model<br>(HBM) <sup>4)</sup>     |  |

#### Table 3Absolute maximum ratings

1) parameter verified by design, not tested in production

2) according to JESD22A111

3) according to JESD22-002

4) according to JESD22-A114-B (discharging 100 pF capacitor through 1.5 k $\Omega$  resistor)

#### **Electrical characteristics**

## 4.2 Thermal characteristics

#### Table 4Thermal characteristics at $T_A = 25^{\circ}C$

| Symbol Values                                          | /mbol  | rameter                                                                                                                                                                                                       |

|--------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Min. Typ. M                                            | М      |                                                                                                                                                                                                               |

|                                                        |        | TFLGA-13-1 package                                                                                                                                                                                            |

| R <sub>thJA25</sub> – 112                              | hJA25  | ermal resistance junction-<br>bient <sup>1)</sup>                                                                                                                                                             |

| R <sub>thJC25</sub> – 44                               | hJC25  | ermal resistance junction-case<br>o) <sup>2)</sup>                                                                                                                                                            |

| d <sup>3)</sup> R <sub>thJB25</sub> – 66               | hJB25  | ermal resistance junction-board <sup>3)</sup>                                                                                                                                                                 |

| Ψ <sub>thJT25</sub> – 7.7                              |        | aracterization parameter<br>ction-top <sup>4)</sup>                                                                                                                                                           |

| Ψ <sub>thJB25</sub> – 5.6                              | thJB25 | aracterization parameter<br>ction-board <sup>4)</sup>                                                                                                                                                         |

|                                                        |        | DSO-16-30 package                                                                                                                                                                                             |

| R <sub>thJA25</sub> – 59                               | hJA25  | ermal resistance junction-<br>bient <sup>1)</sup>                                                                                                                                                             |

| R <sub>thJC25</sub> – 32                               | hJC25  | ermal resistance junction-case<br>b) <sup>2)</sup>                                                                                                                                                            |

| d <sup>3)</sup> R <sub>thJB25</sub> – 33               | hJB25  | ermal resistance junction-board <sup>3)</sup>                                                                                                                                                                 |

| Ψ <sub>thJT25</sub> – 8.9                              |        | aracterization parameter<br>ction-top <sup>4)</sup>                                                                                                                                                           |

| Ψ <sub>thJB25</sub> – 7.7                              | thJB25 | aracterization parameter<br>ction-board <sup>4)</sup>                                                                                                                                                         |

|                                                        | I      | DSO-16-11 package                                                                                                                                                                                             |

| R <sub>thJA25</sub> – 51                               | hJA25  | ermal resistance junction-<br>bient <sup>1)</sup>                                                                                                                                                             |

| R <sub>thJC25</sub> – 25                               | hJC25  | ermal resistance junction-case<br>c) <sup>2)</sup>                                                                                                                                                            |

| d <sup>3)</sup> R <sub>thJB25</sub> – 36               | hJB25  | ermal resistance junction-board <sup>3)</sup>                                                                                                                                                                 |

| Ψ <sub>thJT25</sub> – 4.4                              |        | aracterization parameter<br>ction-top <sup>4)</sup>                                                                                                                                                           |

| Ψ <sub>thJB25</sub> – 5.4                              | thJB25 | aracterization parameter<br>ction-board <sup>4)</sup>                                                                                                                                                         |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | hJC25  | bient <sup>1)</sup><br>ermal resistance junction-case<br>b) <sup>2)</sup><br>ermal resistance junction-board <sup>3)</sup><br>aracterization parameter<br>ction-top <sup>4)</sup><br>aracterization parameter |

1) obtained by simulating a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

2) obtained by simulating a cold plate test on the package top. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

3) obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

4) estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $R_{\rm th}$ , using a procedure described in JESD51-2a (sections 6 and 7).

#### **Electrical characteristics**

## 4.3 Operating range

#### Table 5Operating range

| Parameter                                      | Symbol Values                          |      |      |                   | Unit | Note or                                   |  |

|------------------------------------------------|----------------------------------------|------|------|-------------------|------|-------------------------------------------|--|

|                                                |                                        | Min. | Тур. | Max.              |      | Test Condition                            |  |

| Input supply voltage                           | V <sub>DDI</sub>                       | 3    | _    | 3.5               | V    | SLDO inactive (N.C. or connected to VDDI) |  |

| Output supply voltage                          | V <sub>DDO</sub>                       | 6.5  | 8    | 20 <sup>1)</sup>  | V    | Min. defined by UVLO                      |  |

| VDDI blocking capacitance                      | C <sub>VDDI</sub>                      | -    | _    | 22                | nF   | SLDO active<br>(connected to GNDI)        |  |

| Logic input voltage at pins<br>PWM and DISABLE | V <sub>IN</sub>                        | 0    | _    | 6.5               | V    | -                                         |  |

| Voltage at pins TNEG and SLDO                  | V <sub>tneg</sub><br>V <sub>sldo</sub> | 0    | _    | 5                 | V    | -                                         |  |

| Junction temperature                           | T                                      | -40  | _    | 150 <sup>2)</sup> | °C   |                                           |  |

| Ambient temperature                            | T <sub>A</sub>                         | -40  | _    | 85                | °C   | -                                         |  |

1) not recommended for CoolGaN<sup>™</sup> HEMTs

2) continuous operation above 125°C may reduce lifetime

## 4.4 Electrical characteristics

Unless otherwise noted, min./max. values of characteristics are the lower and upper limits, respectively. They are valid within the full operating range. Typical values are given at  $T_J = 25^{\circ}$ C with  $V_{DDI} = 3.3$  V and  $V_{DDO} = 8$  V

#### Table 6Power supply

| Parameter              | Symbol              |      | Values | Unit | Note or |                |

|------------------------|---------------------|------|--------|------|---------|----------------|

|                        |                     | Min. | Тур.   | Max. |         | Test Condition |

| VDDI quiescent current | / <sub>VDDIqu</sub> | -    | 1.5    | -    | mA      | no switching   |

| VDDO quiescent current | I <sub>VDDOqu</sub> | -    | 1.3    | -    | mA      | no switching   |

### **Electrical characteristics**

#### Table 7Undervoltage Lockout

| Parameter                                                             | Symbol                |      | Values | Unit | Note or |                       |

|-----------------------------------------------------------------------|-----------------------|------|--------|------|---------|-----------------------|

|                                                                       |                       | Min. | Тур.   | Max. |         | <b>Test Condition</b> |

| Undervoltage Lockout input<br>(UVLO <sub>in</sub> ) turn on threshold | UVLO <sub>in</sub>    | 2.75 | 2.85   | 2.95 | V       | -                     |

| Undervoltage Lockout (UVLO <sub>in</sub> )<br>turn off threshold      | UVLO <sub>in-</sub>   | _    | 2.7    | _    | V       | -                     |

| UVLO <sub>in</sub> threshold hysteresis                               | ΔUVLO <sub>in</sub>   | 0.1  | 0.15   | 0.2  | V       | -                     |

| Undervoltage Lockout outputs                                          | UVLO <sub>outG</sub>  | 4.7  | 5.0    | 5.3  | V       | -                     |

| $(UVLO_{outG/S})$ turn on threshold                                   | UVLO <sub>outS</sub>  | 5.4  | 5.8    | 6.2  | V       | -                     |

| UVLO <sub>out</sub> turn off thresholds                               | UVLO <sub>outG-</sub> | -    | 4.5    | -    | V       | -                     |

|                                                                       | UVLO <sub>outS-</sub> | -    | 5.2    | -    | V       | -                     |

| UVLO <sub>out</sub> threshold hysteresis                              | $\Delta UVLO_{outG}$  | 0.3  | 0.45   | 0.6  | V       | -                     |

|                                                                       | ΔUVLO <sub>outS</sub> | 0.4  | 0.6    | 0.8  | V       | -                     |

### Table 8 Logic inputs PWM and DISABLE

| Parameter                                 | Symbol Values       |      |      |      |    | Note or                         |  |

|-------------------------------------------|---------------------|------|------|------|----|---------------------------------|--|

|                                           |                     | Min. | Тур. | Max. |    | <b>Test Condition</b>           |  |

| Input voltage threshold for transition LH | V <sub>INL</sub>    | 1.7  | 2.0  | 2.3  | V  | independent of V <sub>DDI</sub> |  |

| Input voltage threshold for transition HL | V <sub>INH</sub>    | -    | 1.2  | _    | V  | independent of V <sub>DDI</sub> |  |

| Input voltage hysteresis                  | $\Delta V_{\rm IN}$ | 0.4  | 0.8  | 1.2  | V  | -                               |  |

| Input pull down resistor                  | R <sub>IN</sub>     | -    | 150  | -    | kΩ | -                               |  |

#### Table 9 Static output characteristics

| Parameter                                | Symbol Values       |      |      |      | Unit | Note or                  |  |

|------------------------------------------|---------------------|------|------|------|------|--------------------------|--|

|                                          |                     | Min. | Тур. | Max. |      | <b>Test Condition</b>    |  |

| High level (sourcing) output resistance  | R <sub>on_SRC</sub> | 0.42 | 0.85 | 1.6  | Ω    | / <sub>SRC</sub> = 50 mA |  |

| Peak sourcing output current             | I <sub>SRC_pk</sub> | -    | 4    | 1)   | А    | -                        |  |

| Low level (sinking) output<br>resistance | R <sub>on_SNK</sub> | 0.18 | 0.35 | 0.75 | Ω    | I <sub>SNK</sub> = 50 mA |  |

| Peak sinking output current              | I <sub>SNK_pk</sub> | 2)   | -8   | -    | А    | -                        |  |

1) actively limited to approx. 5.2 A<sub>pk</sub>, not subject to production test - verified by design / characterization

2) actively limited to approx. -10.2  $A_{pk}$ , not subject to production test - verified by design / characterization

### **Electrical characteristics**

| Parameter                                               | Symbol                                          |      | Values             |                  | Unit | Note or Test Condition                                    |

|---------------------------------------------------------|-------------------------------------------------|------|--------------------|------------------|------|-----------------------------------------------------------|

|                                                         |                                                 | Min. | Тур.               | Max.             |      |                                                           |

| PWM to OUTS propagation delay                           | t <sub>PDonS</sub>                              | 31   | 37                 | 44               | ns   | load between OUTS and GNDS                                |

|                                                         | $t_{PDoffS}$                                    | -    | 41                 | -                |      | C <sub>LS</sub> = 1.8 nF                                  |

| PWM to OUTG propagation                                 | t <sub>PDonG</sub>                              | -    | $t_{PDoffS} + t_1$ | -                | ns   | load between OUTG and                                     |

| delay                                                   | t <sub>PDoffG</sub>                             | 31   | 37                 | 44               | ns   | GNDG<br>Z <sub>LG</sub> = 1.8 nF // 20 Ω                  |

| DISABLE to OUTS propagation delay                       | t <sub>PD_DISon</sub><br>t <sub>PD_DISoff</sub> | -    | -                  | 100              | ns   | C <sub>LS</sub> = 1.8 nF                                  |

| Rise time OUTS / OUTG                                   | t <sub>rise</sub>                               | -    | 6.5                | 12 <sup>1)</sup> | ns   | C <sub>LS</sub> = C <sub>LG</sub> = 1.8 nF,<br>10% to 90% |

| Fall time OUTS                                          | t <sub>fall</sub>                               | -    | 4.5                | 8 <sup>1)</sup>  | ns   | C <sub>LS</sub> = 1.8 nF, 90% to 10%                      |

| Minimum input pulse width<br>that changes output state  | t <sub>PW</sub>                                 | -    | 18                 | -                | ns   | -                                                         |

| Duration of negative gate "off" voltage                 | t1                                              | -    | 180                | -                | ns   | R <sub>t1</sub> = 100 kΩ                                  |

| Minimum "off"time before<br>entering "first pulse" mode | t <sub>2</sub>                                  | -    | 32 <sup>1)</sup>   | -                | μs   | -                                                         |

| Discharging time in "first<br>pulse" mode               | t <sub>3</sub>                                  | -    | 201)               | -                | ns   | -                                                         |

## Table 10Dynamic characteristics, $T_{J,max} = 125^{\circ}C$ (see Figure 7 and Figure 8)

1) verified by design, not tested in production

#### Timing diagrams

## 5 Timing diagrams

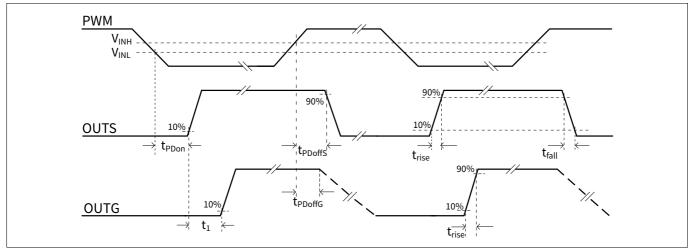

**Figure 7** depicts rise, fall and delay times as observed at the capacitively loaded outputs OUTS and OUTG, resp. As OUTG is not actively switched to low, a resistor in parallel with the load capacitance has to be used for testing. In addition to the signal propagation delay  $t_{PDon}$ , the rising edge of OUTG is delayed by a time  $t_1$  defining the duration of negative  $V_{GS}$ .

Figure 7 Propagation delay, rise and fall time

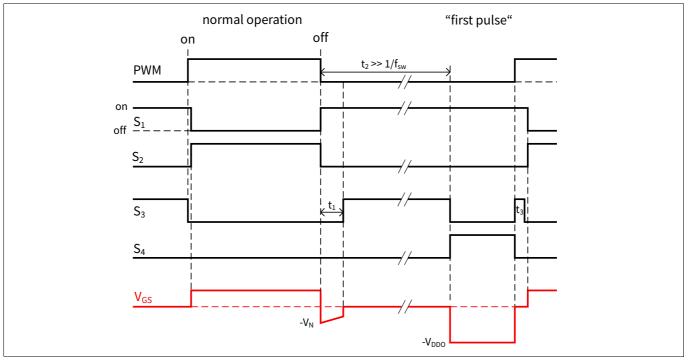

**Figure 8** illustrates a complete switching sequence of the four switches forming the two output stages of GaN EiceDRIVER<sup>TM</sup> (delay, rise and fall times not shown). The sequence in the left part of **Figure 8** corresponds to the normal switching operation, whereas in the right part the "first pulse" situation is depicted. This situation is assumed to happen whenever there is no switching action for an extended period  $t_2$ . Clearly  $t_2$  must be significantly longer than a regular switching period. A typical duration of 32 µs has been chosen, as GaN switches usually operate at switching frequencies significantly above 50 kHz (switching period below 20 µs).

Figure 8 Input signal, output switch sequence and resulting V<sub>GS</sub> for normal operation and "first pulse" situation

**Typical characteristics**

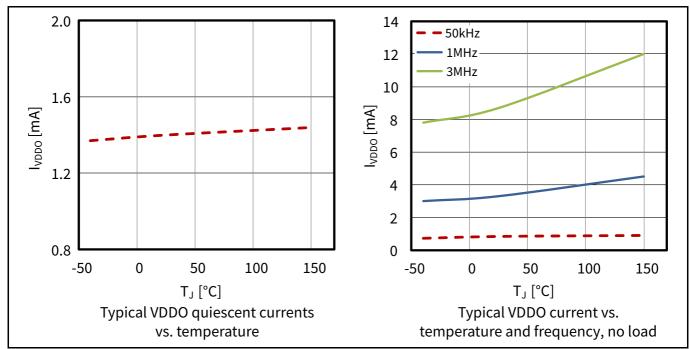

## 6 Typical characteristics

$V_{DD}$ = 8 V,  $V_{DDI}$  = 3.3 V,  $T_{A}$  = 25°C, no load (unless otherwise noted)

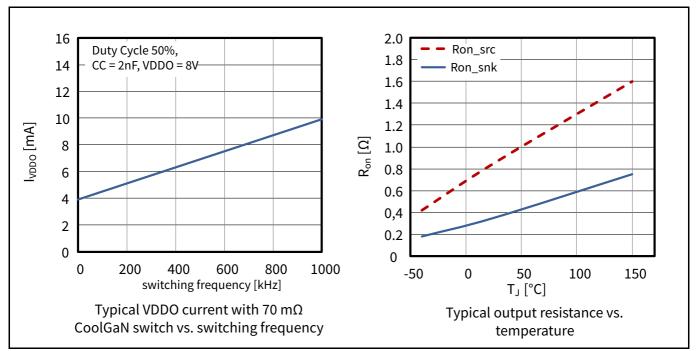

Figure 10 Supply current VDDO

### **Typical characteristics**

Figure 11 Supply current VDDO (with load) and output resistance

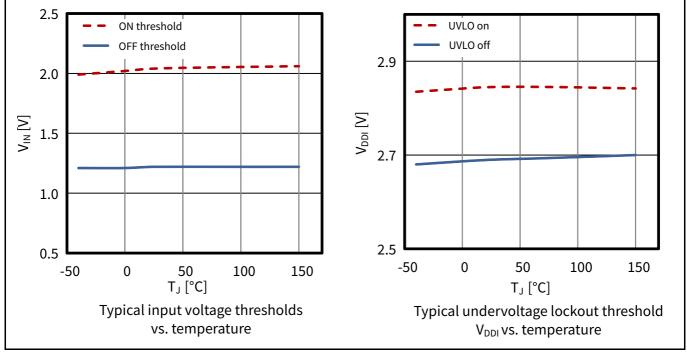

Figure 12 Logic input thresholds and V<sub>DDI</sub> UVLO

### **Typical characteristics**

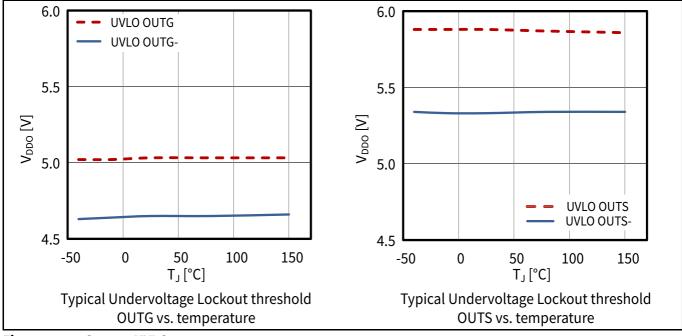

Figure 13 Output UVLO

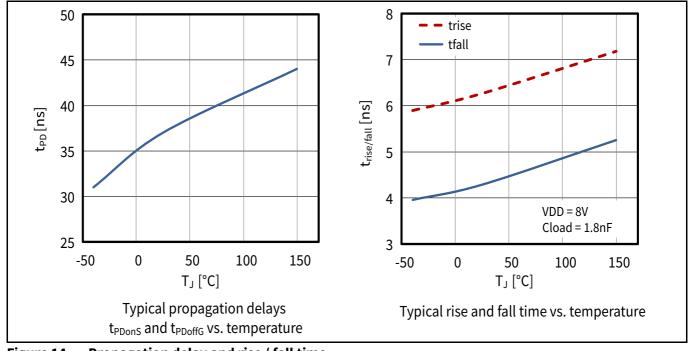

Figure 14 Propagation delay and rise / fall time

### **Typical characteristics**

Figure 15 Typical negative "off" voltage duration  $t_1$  vs.  $R_{t1}$

Figure 16 Thermal derating curves

#### **Isolation specifications**

## 7 Isolation specifications

The following tables summarize the package-specific isolation characteristics and test methods. For reinforced isolation, the regulatory tests described in the component and system standards are applied; functional isolation is guaranteed by the specified in-house test methods.

As soon as the regulatory certificates are available, the reference and / or documents will become available for public download on the Infineon website.

As finally creepage and clearance distances are influenced by PCB layout, it is the customer's responsibility to verify the respective requirements on system level.

## 7.1 Functional isolation specifications

## 7.1.1 Functional isolation in PG-TFLGA-13-1 package (1EDF5673K)

| Parameter                         | Symbol            |      | Values |      | Unit             | Note or Test Condition                                                     |  |

|-----------------------------------|-------------------|------|--------|------|------------------|----------------------------------------------------------------------------|--|

|                                   |                   | Min. | Тур.   | Max. |                  |                                                                            |  |

| Functional isolation test voltage | V <sub>IO</sub>   | 1500 | -      | -    | V <sub>DC</sub>  | impulse test >10 ms,<br>production tested                                  |  |

| Maximum isolation working voltage | V <sub>IOWM</sub> | 460  | _      | -    | V <sub>RMS</sub> | according to IEC 60664-1<br>(PD 2; MG II)                                  |  |

| Package clearance                 | CLR               | -    | 3.4    | _    | mm               | shortest distance over<br>air, from any input pin to<br>any output pin     |  |

| Package creepage                  | CPG               | -    | 3.4    | _    | mm               | shortest distance over<br>surface, from any input<br>pin to any output pin |  |

| Common Mode Transient<br>Immunity | СМТІ              | 200  | -      | -    | V/ns             | according to VDE V0884-<br>10, static and dynamic<br>test                  |  |

| Capacitance input-to-output       | C <sub>IO</sub>   | _    | 2      | _    | pF               | -                                                                          |  |

| Resistance input-to-output        | R <sub>IO</sub>   | _    | >1000  | _    | MΩ               | -                                                                          |  |

Table 11

Functional isolation input-to-output (PG-TFLGA-13-1)

#### **Isolation specifications**

#### Table 12 Package characteristics (PG-TFLGA-13-1)

| Parameter                                  | Symbol |      | Values |      | Unit | Note or Test Condition                     |

|--------------------------------------------|--------|------|--------|------|------|--------------------------------------------|

|                                            |        | Min. | Тур.   | Max. |      |                                            |

| Comparative tracking Index of package mold | СТІ    | 400  | _      | 600  | V    | according to DIN EN<br>60112 (VDE 0303-11) |

| Material group                             | -      | _    | II     | _    | -    | according to IEC 60112                     |

## 7.1.2 Functional isolation in NB PG-DSO-16-11 package (1EDF5673F)

Table 13Functional isolation input-to-output (NB PG-DSO-16-11)

| Parameter                                 | Symbol            |      | Values |      | Unit             | <b>Note or Test Condition</b>                                              |  |

|-------------------------------------------|-------------------|------|--------|------|------------------|----------------------------------------------------------------------------|--|

|                                           |                   | Min. | Тур.   | Max. |                  |                                                                            |  |

| Functional isolation test voltage         | V <sub>IO</sub>   | 1500 | _      | -    | V <sub>DC</sub>  | impulse test > 10 ms,<br>sample tested                                     |  |

| Maximum isolation working voltage         | V <sub>IOWM</sub> | 510  | -      | -    | V <sub>RMS</sub> | according to IEC 60664-1<br>(PD2; MG II) <sup>1)</sup>                     |  |

| Package clearance                         | CLR               | _    | 4.0    | _    | mm               | shortest distance over air,<br>from any input pin to any<br>output pin     |  |

| Package creepage                          | CPG               | _    | 4.0    | _    | mm               | shortest distance over<br>surface, from any input<br>pin to any output pin |  |

| Common Mode Transient<br>Immunity         | СМТІ              | 200  | -      | -    | V/ns             | according to VDE V0884-<br>10, static and dynamic<br>test                  |  |

| Capacitance input-to-output <sup>1)</sup> | C <sub>IO</sub>   | _    | 2      | _    | pF               | -                                                                          |  |

| Resistance input-to-output <sup>1)</sup>  | R <sub>IO</sub>   | _    | >1000  | _    | MΩ               | -                                                                          |  |

1) verified by design, not tested in production

#### Table 14 Package characteristics (NB PG-DSO-16-11)

| Parameter                                  | Symbol |      | Values |      | Unit | Note or Test Condition                     |

|--------------------------------------------|--------|------|--------|------|------|--------------------------------------------|

|                                            |        | Min. | Тур.   | Max. |      |                                            |

| Comparative tracking Index of package mold | СТІ    | 400  | _      | 600  | V    | according to DIN EN 60112<br>(VDE 0303-11) |

| Material group                             | -      | -    | II     | -    | -    | according to IEC 60112                     |

#### **Isolation specifications**

## 7.2 Reinforced isolation in WB PG-DSO-16-30 package (1EDS5663H)

## Table 15 Input-to-output isolation specification according to VDE0884-10 (WB PG-DSO-16-30 )

| Parameter                                         | Symbol            |      | Values |      | Unit            | Note or Test Condition                                                                                                   |

|---------------------------------------------------|-------------------|------|--------|------|-----------------|--------------------------------------------------------------------------------------------------------------------------|

|                                                   |                   | Min. | Тур.   | Max. |                 |                                                                                                                          |

| Maximum transient isolation<br>voltage            | V <sub>IOTM</sub> | 8000 | -      | -    | V <sub>pk</sub> | qualification for t = 60 s;<br>production test with<br>$V_{\text{IOTM}\_\text{test}} = V_{\text{IOTM}} * 1.2$ for t =1 s |

| Maximum repetitive peak isolation voltage         | V <sub>IORM</sub> | 1420 | -      | -    | V <sub>pk</sub> | Time Dependent Dielectric<br>Breakdown test method                                                                       |

| Maximum isolation working                         | V <sub>IOWM</sub> | 1420 | -      | _    | $V_{\rm DC}$    |                                                                                                                          |

| voltage                                           |                   | 1000 | -      | -    | $V_{\rm RMS}$   |                                                                                                                          |

| Partial discharge voltage                         | V <sub>PD</sub>   | 4500 | _      | -    | V <sub>pk</sub> | production test for t=1s,<br>partial discharge Q <sub>PD</sub> < 5 pC                                                    |

| Maximum surge isolation voltage                   | V <sub>IOSM</sub> | 6250 | _      | -    | V <sub>pk</sub> | $V_{\text{IOSM}_{\text{test}}} = 1.6 \times V_{\text{IOSM}} > 10 \text{ k}V_{\text{pk}};$<br>sample tested <sup>1)</sup> |

| Package clearance                                 | CLR               | -    | 8.0    | -    | mm              | from any input pin to any output pin                                                                                     |

| Package creepage                                  | CPG               | _    | 8.0    | -    | mm              | from any input pin to any output pin                                                                                     |

| Overvoltage category per<br>IEC 60664-1 table F.1 | -                 | Ι    | _      | IV   |                 | rated mains voltage<br>≤ 150 V <sub>RMS</sub>                                                                            |

|                                                   |                   | Ι    | _      |      |                 | ≤ 300 V <sub>RMS</sub>                                                                                                   |

|                                                   |                   | I    | _      |      |                 | ≤ 600 V <sub>RMS</sub>                                                                                                   |

| Capacitance input-to-output                       | C <sub>IO</sub>   | -    | 2      | -    | pF              | -                                                                                                                        |

| Resistance input-to-output                        | R <sub>IO</sub>   | -    | >1000  | -    | MΩ              | -                                                                                                                        |

| Common Mode Transient<br>Immunity                 | СМТІ              | 200  | _      | -    | V/ns            | input to output static and dynamic; sample test                                                                          |

1) surge pulse tests applied according to IEC60065-10.1 (Ed 8.0 2014), 61000-4-5, 60060-1 waveforms (1.2 μs slope, 50 μs decay)

| Table 16 | Reinforced isolation package characteristics (WB PG-DSO-16-30) |

|----------|----------------------------------------------------------------|

|----------|----------------------------------------------------------------|

| Parameter                                  | Symbol |      | Values        | Values |   | Note or Test Condition                     |

|--------------------------------------------|--------|------|---------------|--------|---|--------------------------------------------|

|                                            |        | Min. | Тур.          | Max.   |   |                                            |

| Comparative Tracking Index of package mold | СТІ    | 400  | -             | 600    | V | according to DIN EN 60112<br>(VDE 0303-11) |

| Material group                             | -      | -    | II            | _      | - | according to IEC 60112                     |

| Pollution degree                           | -      | -    | 2             | _      | - | -                                          |

| Climatic category                          | -      | _    | 40/125/<br>21 | -      | - | -                                          |

#### **Isolation specifications**

| Parameter                      | Symbol           | Values |      |      | Unit             | Note or Test Condition                                                                                                                                      |

|--------------------------------|------------------|--------|------|------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                |                  | Min.   | Тур. | Max. |                  |                                                                                                                                                             |

| Withstand isolation<br>voltage | V <sub>ISO</sub> | 5700   | -    | -    | V <sub>RMS</sub> | $V_{ISO} = 5700 V_{RMS} \text{ for } t = 60 \text{ s}$<br>(qualification);<br>$V_{ISO\_test} > 1.2 \text{ x} V_{ISO} = 6840 \text{ V for } t = 1 \text{ s}$ |

#### Table 17 Reinforced input-to-output isolation according to UL1577 Ed 5<sup>1)</sup> (WB PG-DSO-16-30)

1) certification pending

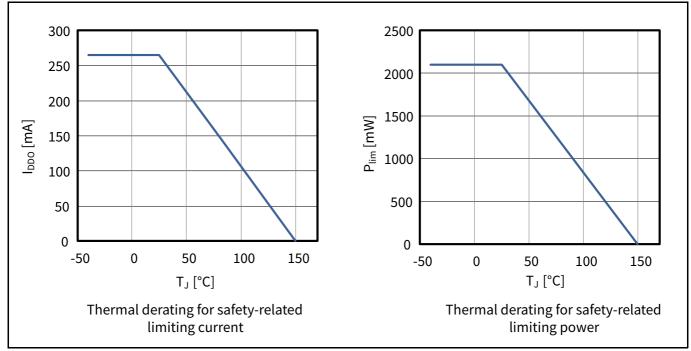

## 7.3 Safety-limiting values

#### Table 18 Reinforced isolation safety-limiting values as outlined in VDE-0884-10 (WB PG-DSO-16-30)

| Parameter             | Side           | Values | Values |      |    | <b>Note or Test Condition</b>                                                                                                                          |

|-----------------------|----------------|--------|--------|------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       |                | Min.   | Тур.   | Max. |    |                                                                                                                                                        |

| Safety supply power   | Input          | -      | -      | 20.0 | mW | $R_{\rm thJA} = 59 \ {\rm K} / {\rm W}^{1)},$                                                                                                          |

|                       | Output         | -      | -      | 2100 | mW | $T_{A} = 25^{\circ}C,$                                                                                                                                 |

|                       | Total          | -      | -      | 2120 | mW | $T_{\rm J} = 150^{\circ}{\rm C}$                                                                                                                       |

| Safety supply current | Output         | _      | -      | 265  | mA | $R_{\text{thJA}} = 59 \text{ K/W}^{1)},$<br>$V_{\text{DDO}} = 8 \text{ V},$<br>$T_{\text{A}} = 25^{\circ}\text{C}, T_{\text{J}} = 150^{\circ}\text{C}$ |

| Safety temperature    | T <sub>s</sub> | -      | -      | 150  | °C | $T_{\rm s} = T_{\rm J,max}$                                                                                                                            |

1) Calculated with the *R*<sub>th</sub> of WB-DSO-16-30 package (see **Table 4**)

According to VDE0884-10 and UL1577, safety-limiting values define the operating conditions under which the isolation barrier can be guaranteed to stay unaffected. This corresponds with the maximum allowed junction temperature, as temperature-induced failures might cause significant overheating and eventually damage the isolation barrier.

**Application circuit**

## 8 Application circuit

**Figure 17** depicts a typical application for CoolGaN<sup>™</sup> switches in a so called "totem-pole" PFC. It consists of a 70 mΩ GaN half-bridge controlled by two GaN EiceDRIVERs; the diode functions indicated in the power path are usually realized with low-*R*<sub>DSON</sub> MOSFETs operating as synchronous rectifiers. 2.5 kW of power can be handled at very high efficiency (above 99%).

The topology in **Figure 17** differs from standard PFCs mainly by the fact that both GaN transistors are used alternately in switch and diode operation mode, depending on the polarity of the input voltage. This eliminates the need for rectifying the input voltage and therefore avoids a significant loss contributor. Such a topology cannot be realized with MOS-switches due to their inherent body diode and the associated large recovery charge.

Further details can be found in application note: www.infineon.com/driving-coolgan

Figure 17 Typical application circuit for 2.5 kW GaN "totem-pole" PFC

Layout guidelines

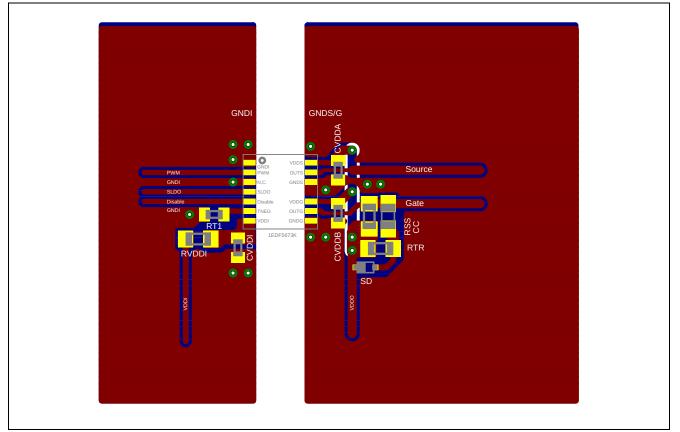

## 9 Layout guidelines

For any fast-switching power system the PCB layout is crucial to achieve optimum performance. Among the many existing rules, recommendations, guidelines, tips and tricks, the following are of highest importance:

- minimize power loop inductance, the most critical limitation of switching speed due to the unavoidable voltage overshoots generated by fast current commutation

- use low-ESR decoupling capacitances for the driver supply voltages and place them as close as possible to the driver (in the layout proposals below the output capacitance has been split and connected to both supply pins)

- strictly avoid any additional coupling capacitance between input and output pins due to PCB layout (see Chapter 3.7)

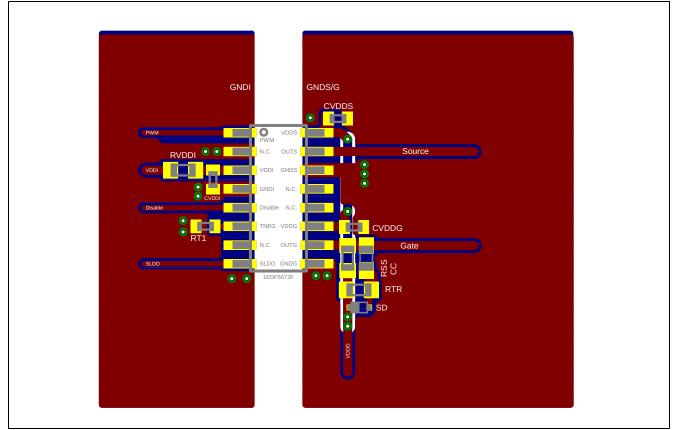

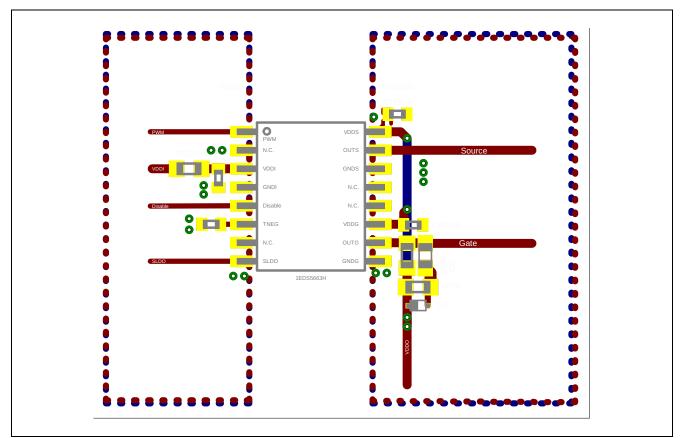

Respective layout proposals for the immediate driver surroundings are given in **Figure 18**, **Figure 19** and **Figure 20** for the different available package types.

Figure 18 Layout recommendation for PG-TFLGA-13-1 package

## GaN EiceDRIVER<sup>™</sup> product family Single-channel functional and reinforced isolated gate-driver ICs for

#### Layout guidelines

Figure 19 Layout recommendation for PG-DSO-16-11 package

Figure 20 Layout recommendation for PG-DSO-16-30 package

#### Package information

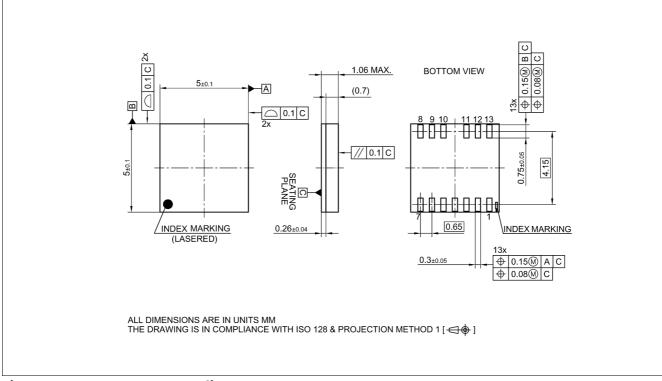

## 10 Package information

The following package versions are available.

- an area optimized 5 x 5 mm<sup>2</sup> PG-TFLGA-13-1

- an NB PG-DSO-16-11 package with typ. 4 mm creepage input to output

- a WB PG-DSO-16-30 package with typ. 8 mm creepage input to output

*Note:* For further information on package types, recommendation for board assembly, please go to **https://www.infineon.com/packages**

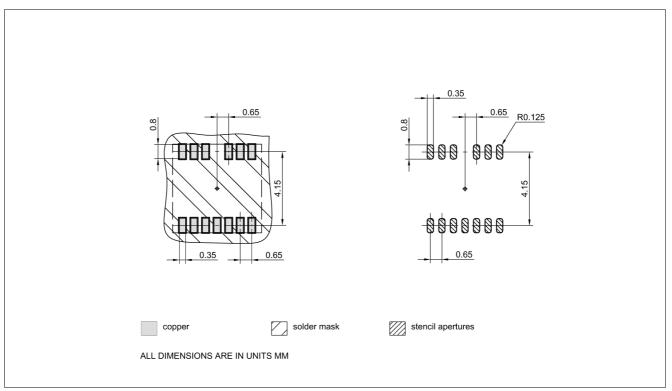

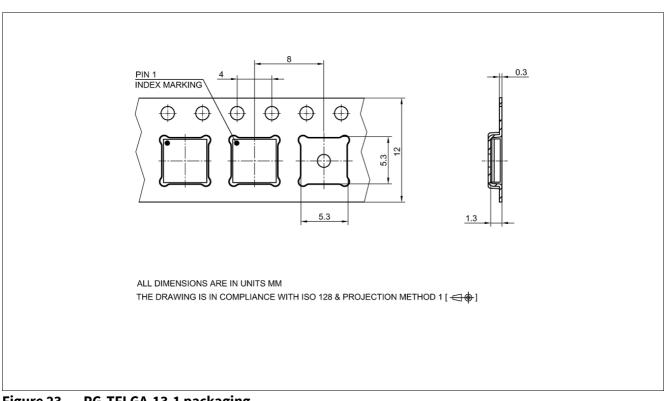

## 10.1 Package PG-TFLGA-13-1

Figure 21 PG-TFLGA-13-1 outline

### **Package information**

PG-TFLGA-13-1 footprint Figure 22

Figure 23 PG-TFLGA-13-1 packaging

### Package information

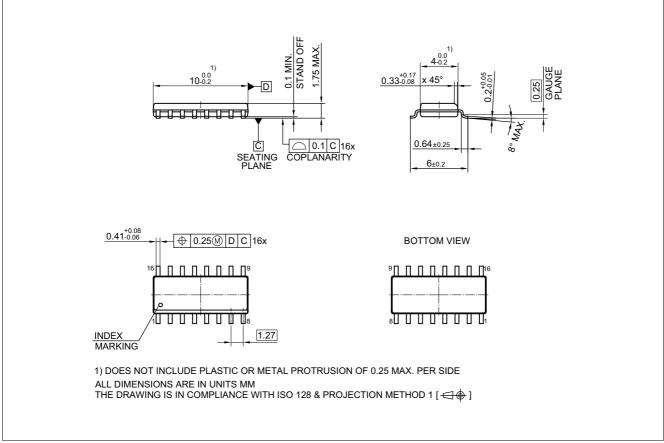

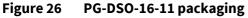

## 10.2 Package PG-DSO-16-11

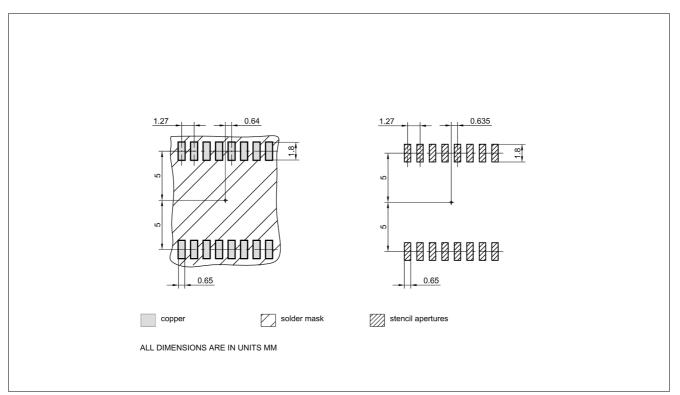

Figure 24 PG-DSO-16-11 outline

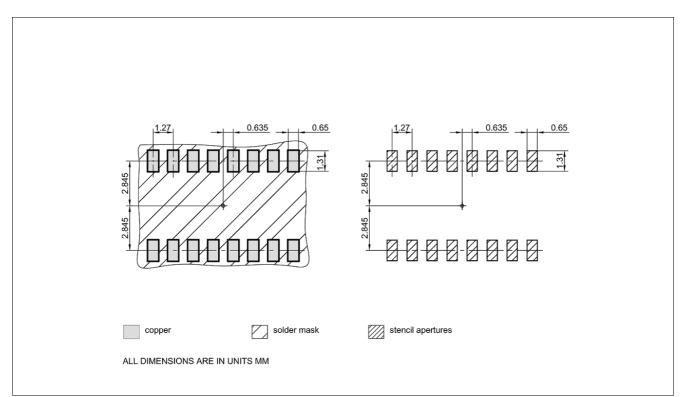

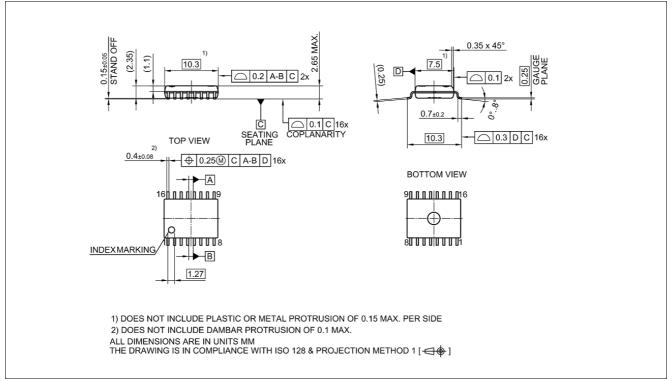

Figure 25 PG-DSO-16-11 footprint

#### Package information

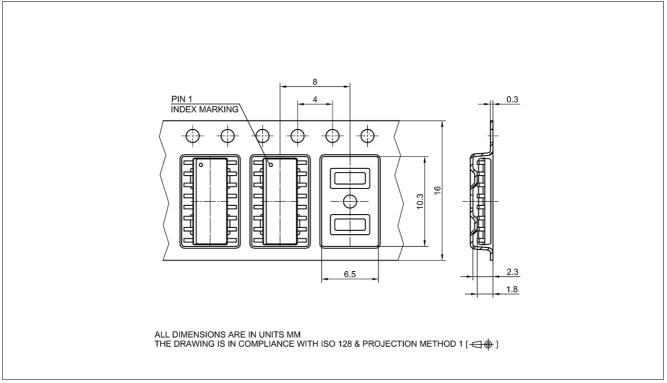

## 10.3 Package PG-DSO-16-30

Figure 27 PG-DSO-16-30 outline

### Package information

Figure 29 PG-DSO-16-30 packaging

Device numbers and markings

## **11** Device numbers and markings

## Table 19Device numbers and markings

| Part number | Package       | Orderable part number (OPN) | Device marking |

|-------------|---------------|-----------------------------|----------------|

| 1EDF5673K   | PG-TFLGA-13-1 | 1EDF5673KXUMA1              | 1F5673A        |

| 1EDF5673F   | PG-DSO-16-11  | 1EDF5673FXUMA1              | 1F5673A        |

| 1EDS5663H   | PG-DSO-16-30  | 1EDS5663HXUMA1              | 1S5663A        |

**Revision History**

## 12 Revision History

| Page or Item    | Subjects (major changes since previous revision) |  |  |  |  |  |  |  |

|-----------------|--------------------------------------------------|--|--|--|--|--|--|--|

| Rev. 2.00, 2018 | 3-11-07                                          |  |  |  |  |  |  |  |

|                 | Final datasheet created                          |  |  |  |  |  |  |  |

| Rev. 1.00, 2018 | 3-10-25                                          |  |  |  |  |  |  |  |

|                 | Initial version available                        |  |  |  |  |  |  |  |

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2018-11-07 Published by Infineon Technologies AG 81726 Munich, Germany

© 2018 Infineon Technologies AG. All Rights Reserved.

Do you have a question about any aspect of this document? Email: erratum@infineon.com

Document reference 1EDF5673K, 1EDF5673F, 1EDS5663H

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application. For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.