## DS90LV110AT 1 to 10 LVDS Data/Clock Distributor with Failsafe

Check for Samples: DS90LV110AT

### **FEATURES**

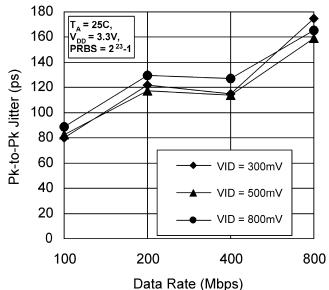

- Low jitter 400 Mbps fully differential data path

- 145 ps (typ) of pk-pk jitter with PRBS = 2<sup>23</sup>-1 data pattern at 400 Mbps

- Single +3.3 V Supply

- · Balanced output impedance

- Output channel-to-channel skew is 35ps (typ)

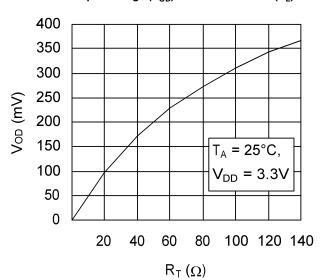

- Differential output voltage ( $V_{OD}$ ) is 320mV (typ) with 100 $\Omega$  termination load.

- LVDS receiver inputs accept LVPECL signals

- · LVDS input failsafe

- Fast propagation delay of 2.8 ns (typ)

- Receiver open, shorted, and terminated input failsafe

- 28 lead TSSOP package

- Conforms to ANSI/TIA/EIA-644 LVDS standard

#### DESCRIPTION

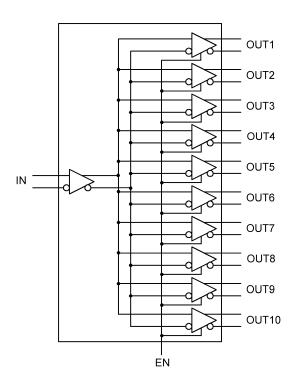

DS90LV110A is a 1 to 10 data/clock distributor utilizing LVDS (Low Voltage Differential Signaling) technology for low power, high speed operation. Data paths are fully differential from input to output for low noise generation and low pulse width distortion. The design allows connection of 1 input to all 10 outputs. LVDS I/O enable high speed data transmission for point-to-point interconnects. This device can be used as a high speed differential 1 to 10 signal distribution / fanout replacing multi-drop bus applications for higher speed links with improved signal quality. It can also be used for clock distribution up to 200MHz.

The DS90LV110A accepts LVDS signal levels, LVPECL levels directly or PECL with attenuation networks.

The LVDS outputs can be put into TRI-STATE by use of the enable pin.

For more details, please refer to the APPLICATION INFORMATION section of this datasheet.

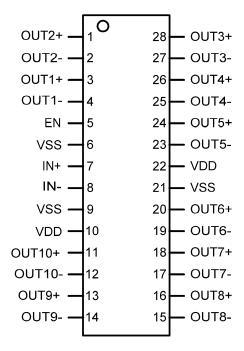

## **Connection Diagram**

Order Number DS90LV110ATMT PW0028A Package

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

## **Block Diagram**

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings (1)

| Supply Voltage (V <sub>DD</sub> -V <sub>SS</sub> ) |                     | -0.3V to +4V                      |  |  |  |  |

|----------------------------------------------------|---------------------|-----------------------------------|--|--|--|--|

| LVCMOS/LVTTL Input Voltage                         | e (EN)              | -0.3V to (V <sub>CC</sub> + 0.3V) |  |  |  |  |

| LVDS Receiver Input Voltage                        | (IN+, IN−)          | -0.3V to +4V                      |  |  |  |  |

| LVDS Driver Output Voltage (                       | OUT+, OUT−)         | -0.3V to +4V                      |  |  |  |  |

| Junction Temperature                               |                     | +150°C                            |  |  |  |  |

| Storage Temperature Range                          |                     | −65°C to +150°C                   |  |  |  |  |

| Lead Temperature (Soldering,                       | 4 sec.)             | +260°C                            |  |  |  |  |

| Maximum Package Power Dissipation at 25°C          | 28 Lead TSSOP       | 2.115 W                           |  |  |  |  |

| Package Derating                                   | 28 Lead TSSOP       | 16.9 mW/°C above +25°C            |  |  |  |  |

| θ <sub>JA</sub><br>(4-Layer, 2 oz. Cu, JEDEC)      | 28 Lead TSSOP       | 59.1 °C/W                         |  |  |  |  |

| EOD Daties                                         | (HBM, 1.5kΩ, 100pF) | > 8 kV                            |  |  |  |  |

| ESD Rating:                                        | (EIAJ, 0Ω, 200pF)   | > 250 V                           |  |  |  |  |

<sup>(1) &</sup>quot;Absolute Maximum Ratings" are these beyond which the safety of the device cannot be verified. They are not meant to imply that the device should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

## **Recommended Operating Conditions**

|                                                     | Min | Тур | Max      | Units |

|-----------------------------------------------------|-----|-----|----------|-------|

| Supply Voltage (V <sub>DD</sub> - V <sub>SS</sub> ) | 3.0 | 3.3 | 3.6      | V     |

| Receiver Input Voltage                              | 0   |     | $V_{DD}$ | V     |

| Operating Free Air Temperature                      | -40 | +25 | +85      | °C    |

### **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified

| Symbol           | Parameter                                      | Conditions                                                     | Min         | Typ <sup>(1)</sup> | Max  | Units |

|------------------|------------------------------------------------|----------------------------------------------------------------|-------------|--------------------|------|-------|

| LVCMOS           | /LVTTL DC SPECIFICATIONS (EN)                  |                                                                |             |                    |      |       |

| V <sub>IH</sub>  | High Level Input Voltage                       | 2.0                                                            |             | $V_{DD}$           | V    |       |

| V <sub>IL</sub>  | Low Level Input Voltage                        | V <sub>SS</sub>                                                |             | 0.8                | V    |       |

| I <sub>IH</sub>  | High Level Input Current                       | V <sub>IN</sub> = 3.6V or 2.0V; V <sub>DD</sub> = 3.6V         |             | ±7                 | ±20  | μΑ    |

| I <sub>IL</sub>  | Low Level Input Current                        | $V_{IN} = 0V \text{ or } 0.8V; V_{DD} = 3.6V$                  |             | ±7                 | ±20  | μA    |

| $V_{CL}$         | Input Clamp Voltage                            | I <sub>CL</sub> = −18 mA                                       |             | -0.8               | -1.5 | V     |

| LVDS OL          | JTPUT DC SPECIFICATIONS (OUT1, OU              | T2, OUT3, OUT4, OUT5, OUT6, OUT7, OUT8                         | , OUT9, OUT | Г10)               |      | •     |

| V <sub>OD</sub>  | Differential Output Voltage                    | $R_L = 100\Omega$                                              | 250         | 320                | 450  | mV    |

|                  |                                                | $R_L = 100\Omega, V_{DD} = 3.3V, T_A = 25^{\circ}C$            | 260         | 320                | 425  | mV    |

| $\Delta V_{OD}$  | Change in V <sub>OD</sub> between Complimentar |                                                                |             | 35                 | mV   |       |

| Vos              | Offset Voltage (2)                             | 1.125                                                          | 1.25        | 1.375              | V    |       |

| $\Delta V_{OS}$  | Change in V <sub>OS</sub> between Complimentar |                                                                |             | 35                 | mV   |       |

| l <sub>OZ</sub>  | Output TRI-STATE Current                       | EN = 0V,<br>$V_{OUT} = V_{DD}$ or GND                          |             | ±1                 | ±10  | μA    |

| I <sub>OFF</sub> | Power-Off Leakage Current                      | $V_{DD} = 0V$ ; $V_{OUT} = 3.6V$ or GND                        |             | ±1                 | ±10  | μA    |

| $I_{SA},I_{SB}$  | Output Short Circuit Current                   | V <sub>OUT+</sub> OR V <sub>OUT-</sub> = 0V or V <sub>DD</sub> |             | 12                 | 24   | mA    |

| I <sub>SAB</sub> | Both Outputs Shorted (3)                       | $V_{OUT+} = V_{OUT-}$                                          |             | 6                  | 12   | mA    |

| LVDS RE          | CEIVER DC SPECIFICATIONS (IN)                  |                                                                | <u> </u>    |                    |      |       |

| V <sub>TH</sub>  | Differential Input High Threshold              | $V_{CM} = +0.05V \text{ or } +1.2V \text{ or } +3.25V,$        |             | 0                  | +100 | mV    |

| V <sub>TL</sub>  | Differential Input Low Threshold               | $V_{DD} = 3.3V$                                                | -100        | 0                  |      | mV    |

| $V_{CMR}$        | Common Mode Voltage Range                      | $V_{ID} = 100 \text{mV}, V_{DD} = 3.3 \text{V}$                | 0.05        |                    | 3.25 | V     |

| I <sub>IN</sub>  | Input Current                                  | $V_{IN} = +3.0V$ , $V_{DD} = 3.6V$ or $0V$                     |             | ±1                 | ±10  | μΑ    |

|                  |                                                | $V_{IN} = 0V$ , $V_{DD} = 3.6V$ or $0V$                        |             |                    |      |       |

| SUPPLY           | CURRENT                                        |                                                                | ·           |                    |      |       |

| I <sub>CCD</sub> | Total Supply Current                           | $R_L = 100\Omega$ , $C_L = 5$ pF, 200 MHz, $EN = High$         |             | 125                | 160  | mA    |

|                  |                                                | No Load, 200 MHz, EN = High                                    |             | 80                 | 125  | mA    |

| I <sub>CCZ</sub> | TRI-STATE Supply Current                       | EN = Low                                                       |             | 15                 | 29   | mA    |

|                  |                                                |                                                                |             |                    |      |       |

Submit Documentation Feedback

Product Folder Links: DS90LV110AT

<sup>(1)</sup> All typical are given for V<sub>CC</sub> = +3.3V and T<sub>A</sub> = +25°C, unless otherwise stated.

(2) V<sub>OS</sub> is defined as (V<sub>OH</sub> + V<sub>OL</sub>) / 2.

(3) Only one output can be shorted at a time. Don't exceed the package absolute maximum rating.

#### **AC Electrical Characteristics**

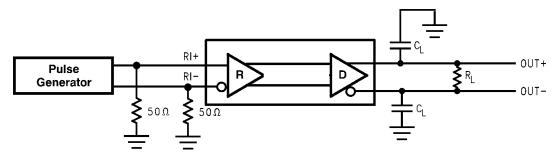

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol            | Parameter                                                                                                                                            | Conditions                                                            | Min  | Тур  | Max  | Units |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------|------|------|-------|

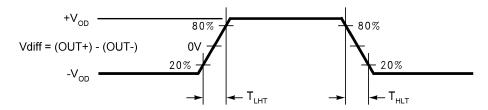

| T <sub>LHT</sub>  | Output Low-to-High Transition Time, 20% to                                                                                                           | 80%, Figure 4 <sup>(1)</sup>                                          |      | 390  | 550  | ps    |

| T <sub>HLT</sub>  | Output High-to-Low Transition Time, 80% to                                                                                                           | 20%, Figure 4 <sup>(1)</sup>                                          |      | 390  | 550  | ps    |

| T <sub>DJ</sub>   | LVDS Data Jitter, Deterministic (Peak-to-Peak) $^{(2)}$ $V_{ID} = 300 \text{mV}$ ; PRBS= $2^{23}$ -1 data; $V_{CM} = 1.2 \text{V}$ at 400 Mbps (NRZ) |                                                                       |      | 145  |      | ps    |

| T <sub>RJ</sub>   | LVDS Clock Jitter, Random (2)                                                                                                                        | $V_{ID} = 300 \text{mV};$<br>$V_{CM} = 1.2 \text{V}$ at 200 MHz clock |      | 2.8  |      | ps    |

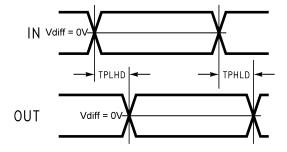

| T <sub>PLHD</sub> | Propagation Low to High Delay, Figure 5                                                                                                              | •                                                                     | 2.2  | 2.8  | 3.6  | ns    |

| T <sub>PHLD</sub> | Propagation High to Low Delay, Figure 5                                                                                                              |                                                                       | 2.2  | 2.8  | 3.9  | ns    |

| T <sub>SKEW</sub> | Pulse Skew  T <sub>PLHD</sub> - T <sub>PHLD</sub>   (1)                                                                                              |                                                                       |      | 20   | 340  | ps    |

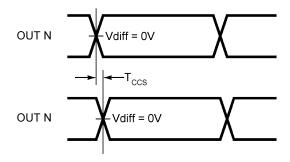

| T <sub>CCS</sub>  | Output Channel-to-Channel Skew, Figure 6                                                                                                             | 1)                                                                    |      | 35   | 91   | ps    |

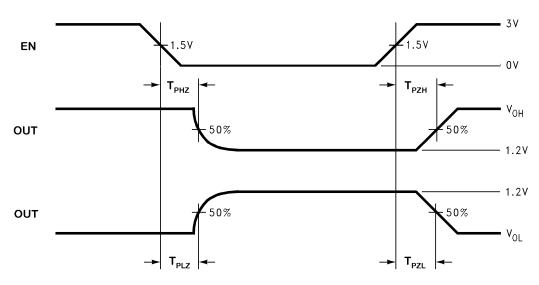

| T <sub>PHZ</sub>  | Disable Time (Active to TRI-STATE) High to                                                                                                           | Z, Figure 1                                                           |      | 3.0  | 6.0  | ns    |

| T <sub>PLZ</sub>  | Disable Time (Active to TRI-STATE) Low to 2                                                                                                          |                                                                       | 1.8  | 6.0  | ns   |       |

| T <sub>PZH</sub>  | Enable Time (TRI-STATE to Active) Z to Hig                                                                                                           |                                                                       | 10.0 | 23.0 | ns   |       |

| T <sub>PZL</sub>  | Enable Time (TRI-STATE to Active) Z to Low                                                                                                           | v, Figure 1                                                           |      | 7.0  | 23.0 | ns    |

- (1) The parameters are specified by design. The limits are based on statistical analysis of the device performance over PVT (process, voltage and temperature) range.

- (2) The measurement used the following equipment and test setup: HP8133A pattern/pulse generator), 5 feet of RG-142 cable with DUT test board and HP83480A (digital scope mainframe) with HP83484A (50GHz scope module). The HP8133A with the RG-142 cable exhibit a T<sub>DJ</sub> = 26ps and T<sub>RJ</sub> = 1.3 ps

#### **AC TIMING DIAGRAMS**

Figure 1. Output active to TRI-STATE and TRI-STATE to active output time

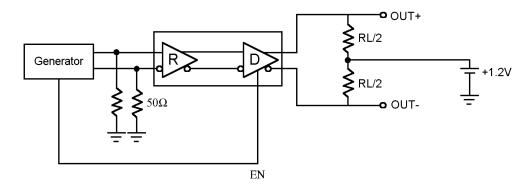

Figure 2. LVDS Driver TRI-STATE Circuit

Figure 3. LVDS Output Load

Figure 4. LVDS Output Transition Time

Figure 5. Propagation Delay Low-to-High and High-to-Low

Copyright © 2004–2013, Texas Instruments Incorporated

Figure 6. Output 1 to 10 Channel-to-Channel Skew

#### APPLICATION INFORMATION

#### INPUT FAIL-SAFE

The receiver inputs of the DS90LV110A have internal fail-safe biasing for short, open, and teminated input conditions.

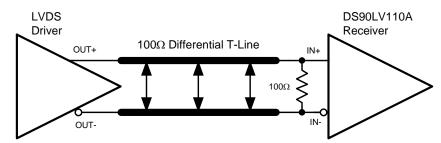

#### LVDS INPUTS TERMINATION

The LVDS Receiver input must have a  $100\Omega$  termination resistor placed as close as possible across the input pins.

#### **UNUSED CONTROL INPUTS**

The EN control input pin has internal pull down device. If left open, the 10 outputs will default to TRI-STATE.

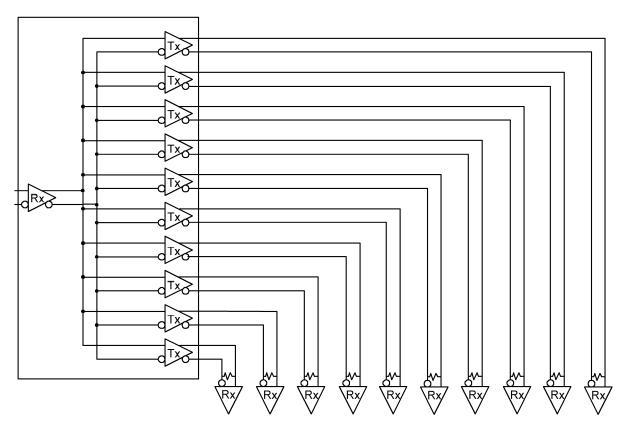

### **EXPANDING THE NUMBER OF OUTPUT PORTS**

To expand the number of output ports, more than one DS90LV110A can be used. Total propagation delay through the devices should be considered to determine the maximum expansion. Adding more devices will increase the output jitter due to each pass.

### PCB LAYOUT AND POWER SYSTEM BYPASS

Circuit board layout and stack-up for the DS90LV110A should be designed to provide noise-free power to the device. Good layout practice also will separate high frequency or high level inputs and outputs to minimize unwanted stray noise pickup, feedback and interference. Power system performance may be greatly improved by using thin dielectrics (4 to 10 mils) for power/ground sandwiches. This increases the intrinsic capacitance of the PCB power system which improves power supply filtering, especially at high frequencies, and makes the value and placement of external bypass capacitors less critical. External bypass capacitors should include both RF ceramic and tantalum electrolytic types. RF capacitors may use values in the range 0.01  $\mu F$  to 0.1  $\mu F$ . Tantalum capacitors may be in the range 2.2  $\mu F$  to 10  $\mu F$ . Voltage rating for tantalum capacitors should be at least 5X the power supply voltage being used. It is recommended practice to use two vias at each power pin of the DS90LV110A as well as all RF bypass capacitor terminals. Dual vias reduce the interconnect inductance by up to half, thereby reducing interconnect inductance and extending the effective frequency range of the bypass components.

The outer layers of the PCB may be flooded with additional ground plane. These planes will improve shielding and isolation as well as increase the intrinsic capacitance of the power supply plane system. Naturally, to be effective, these planes must be tied to the ground supply plane at frequent intervals with vias. Frequent via placement also improves signal integrity on signal transmission lines by providing short paths for image currents which reduces signal distortion. The planes should be pulled back from all transmission lines and component mounting pads a distance equal to the width of the widest transmission line or the thickness of the dielectric separating the transmission line from the internal power or ground plane(s) whichever is greater. Doing so minimizes effects on transmission line impedances and reduces unwanted parasitic capacitances at component mounting pads.

There are more common practices which should be followed when designing PCBs for LVDS signaling. Please see Application Note: AN-1108(SNLA008) for additional information.

#### INPUT INTERFACING

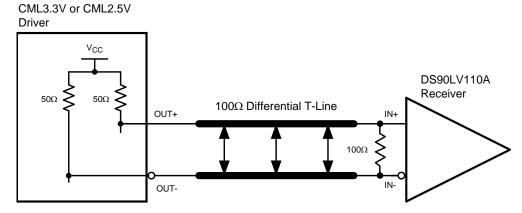

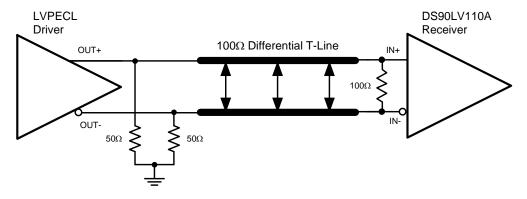

The DS90LV110A accepts differential signals and allow simple AC or DC coupling. With a wide common mode range, the DS90LV110A can be DC-coupled with all common differential drivers (that is, LVPECL, LVDS, CML). Figure 7, Figure 8, and Figure 9 illustrate typical DC-coupled interface to common differential drivers.

Figure 7. Typical LVDS Driver DC-Coupled Interface to DS90LV110A Input

Figure 8. Typical CML Driver DC-Coupled Interface to DS90LV110A Input

Figure 9. Typical LVPECL Driver DC-Coupled Interface to DS90LV110A Input

#### **OUTPUT INTERFACING**

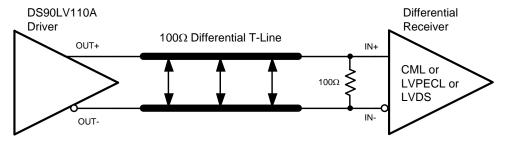

The DS90LV110A outputs signals that are compliant to the LVDS standard. Their outputs can be DC-coupled to most common differential receivers. Figure 10 illustrates typical DC-coupled interface to common differential receivers and assumes that the receivers have high impedance inputs. While most differential receivers have a common mode input range that can accommodate LVDS compliant signals, it is recommended to check respective receiver's data sheet prior to implementing the suggested interface implementation.

Figure 10. Typical DS90LV110A Output DC-Coupled Interface to an LVDS, CML or LVPECL Receiver

#### **DS90LV110A PIN DESCRIPTIONS**

| 20021    |          |              |                                                                                                                                                       |  |  |  |  |  |  |  |  |

|----------|----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Pin Name | # of Pin | Input/Output | Description                                                                                                                                           |  |  |  |  |  |  |  |  |

| IN+      | 1        | I            | Non-inverting LVDS input                                                                                                                              |  |  |  |  |  |  |  |  |

| IN -     | 1        | I            | Inverting LVDS input                                                                                                                                  |  |  |  |  |  |  |  |  |

| OUT+     | 10       | 0            | Non-inverting LVDS Output                                                                                                                             |  |  |  |  |  |  |  |  |

| OUT -    | 10       | 0            | Inverting LVDS Output                                                                                                                                 |  |  |  |  |  |  |  |  |

| EN       | 1        | I            | This pin has an internal pull-down when left open. A logic low on the Enable puts all the LVDS outputs into TRI-STATE and reduces the supply current. |  |  |  |  |  |  |  |  |

| $V_{SS}$ | 3        | Р            | Ground (all ground pins must be tied to the same supply)                                                                                              |  |  |  |  |  |  |  |  |

| $V_{DD}$ | 2        | Р            | Power Supply (all power pins must be tied to the same supply)                                                                                         |  |  |  |  |  |  |  |  |

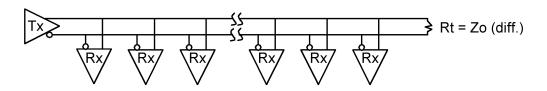

### **MULTI-DROP APPLICATIONS**

### POINT-TO-POINT DISTRIBUTION APPLICATIONS

For applications operating at data rate greater than 400Mbps, a point-to-point distribution application should be used. This improves signal quality compared to multi-drop applications due to no stub PCB trace loading. The only load is a receiver at the far end of the transmission line. Point-to-point distribution applications will have a wider LVDS bus lines, but data rate can increase well above 400Mbps due to the improved signal quality.

# **Typical Performance Characteristics**

Output Voltage (V<sub>OD</sub>) vs. Resistive Load (R<sub>L</sub>)

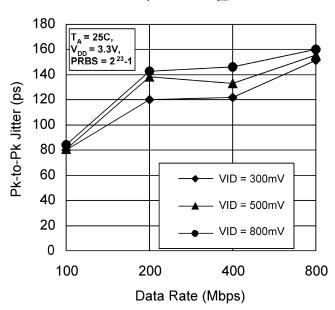

Peak-to-Peak Output Jitter at V<sub>CM</sub> = +0.4V vs. VID

Peak-to-Peak Output Jitter at V<sub>CM</sub> = +1.2V vs. VID

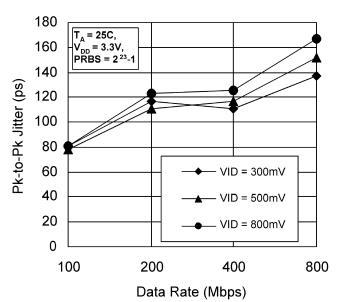

Peak-to-Peak Output Jitter at V<sub>CM</sub> = +2.9V vs. VID

## **REVISION HISTORY**

| Cł | hanges from Revision I (April 2013) to Revision J  | Page |

|----|----------------------------------------------------|------|

| •  | Changed layout of National Data Sheet to TI format | 1    |

Product Folder Links: DS90LV110AT

## PACKAGE OPTION ADDENDUM

25-Sep-2019

#### **PACKAGING INFORMATION**

| Orderable Device    | Status | Package Type | _       | Pins | Package | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking    | Samples |

|---------------------|--------|--------------|---------|------|---------|----------------------------|------------------|---------------------|--------------|-------------------|---------|

|                     | (1)    |              | Drawing |      | Qty     | (2)                        | (6)              | (3)                 |              | (4/5)             |         |

| DS90LV110ATMT       | NRND   | TSSOP        | PW      | 28   | 48      | TBD                        | Call TI          | Call TI             | -40 to 85    | DS90LV<br>110ATMT |         |

| DS90LV110ATMT/NOPB  | ACTIVE | TSSOP        | PW      | 28   | 48      | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-3-260C-168 HR | -40 to 85    | DS90LV<br>110ATMT | Samples |

| DS90LV110ATMTX/NOPB | ACTIVE | TSSOP        | PW      | 28   | 2500    | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-3-260C-168 HR | -40 to 85    | DS90LV<br>110ATMT | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

## **PACKAGE OPTION ADDENDUM**

25-Sep-2019

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com 23-Sep-2013

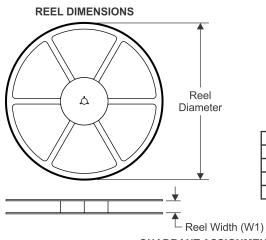

## TAPE AND REEL INFORMATION

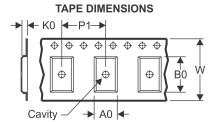

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

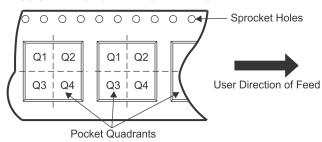

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

### \*All dimensions are nominal

| Device              | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DS90LV110ATMTX/NOPB | TSSOP           | PW                 | 28 | 2500 | 330.0                    | 16.4                     | 6.8        | 10.2       | 1.6        | 8.0        | 16.0      | Q1               |

www.ti.com 23-Sep-2013

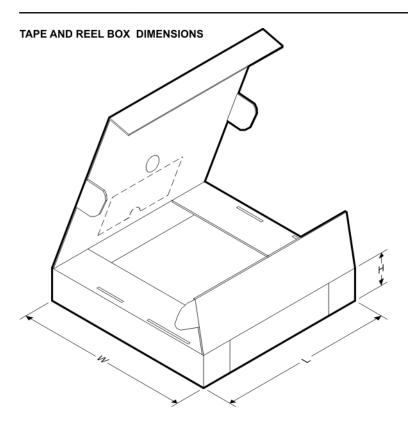

#### \*All dimensions are nominal

| Device              | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---------------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| DS90LV110ATMTX/NOPB | TSSOP        | PW              | 28   | 2500 | 367.0       | 367.0      | 38.0        |  |

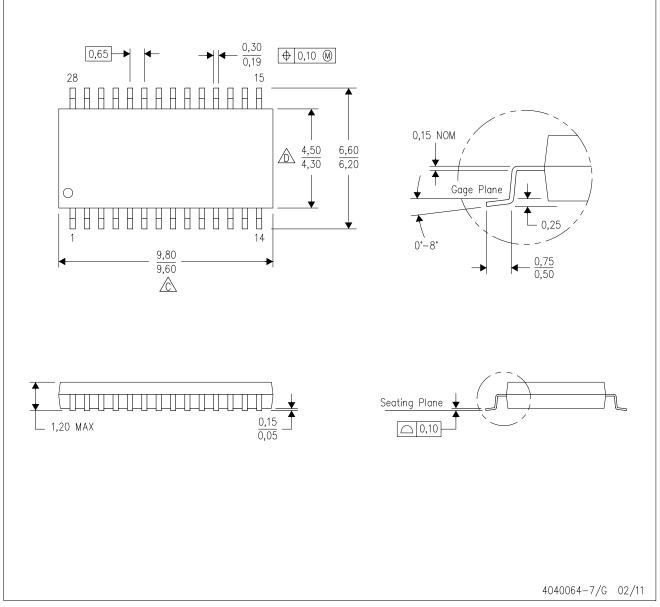

PW (R-PDSO-G28)

## PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994.

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0,15 each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0,25 each side.

- E. Falls within JEDEC MO-153

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated