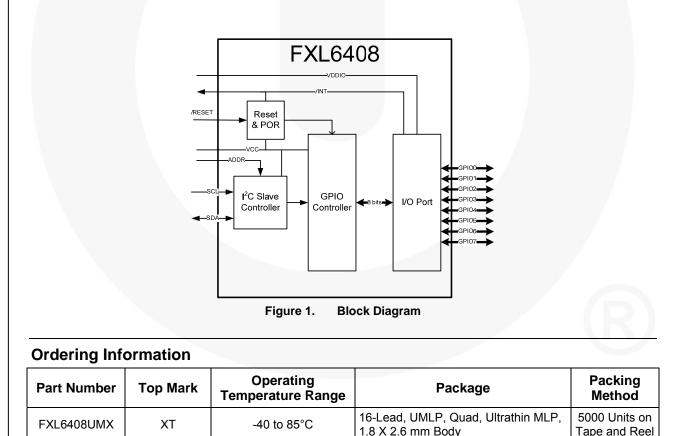

# FXL6408 Fully Configurable 8-Bit I<sup>2</sup>C-Controlled GPIO Expander

### Features

- 4X Expansion of Connected Processor I/O Ports

- Fully Integrated I<sup>2</sup>C Slave

- 8 Independently Configurable I/O Ports

- Low-Power Quiescent Current: 1.5 µA

- Voltage Translation Capable from 1.65 V I<sup>2</sup>C Port Up to 4.0 V GPIO Pins

- Selectable Device Address

- 6 mA Output Drive

- Interrupt Pin to Alert Processor of Status Changes

### Description

The FXL6408 is an 8-bit I<sup>2</sup>C-controlled GPIO expander. When configured in Input Mode, the FXL6408 monitors the input ports for data transitions and signals the baseband by asserting the /INT pin. The input default values can be programmed independently, allowing customized input detection. All inputs can be configured with pull-up or pull-down resistors to pre-bias the inputs in open-drain or non-driven applications. When configured in Output Mode, the GPIO pins are capable of delivering 6 mA output drive according to the I<sup>2</sup>C register set. The FXL6408 is designed to allow voltage translation from levels as low as 1.65 V and up to 4.0 V. The FXL6408 features an active LOW RESET input as well as Power-On Reset (POR) circuit and I<sup>2</sup>C software reset options.

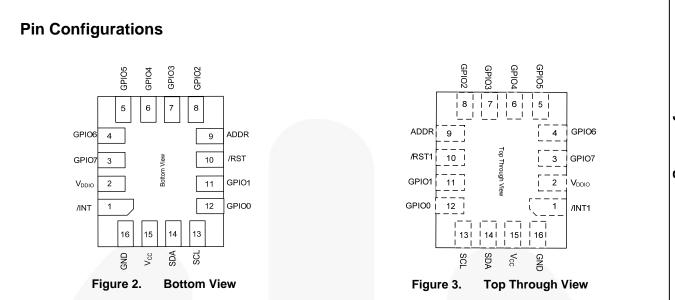

# **Pin Descriptions**

| Pin # | Pin Name          | Description                                                                                                                                |  |  |  |  |

|-------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1     | /INT              | Interrupt output, open-drain, active LOW; requires an external pull-up resistor to $V_{CC}$                                                |  |  |  |  |

| 2     | V <sub>DDIO</sub> | Voltage reference for I/O-side voltage translation (if I/O translation is not needed, tie $V_{\text{DDIO}}$ to the V <sub>CC</sub> supply) |  |  |  |  |

| 3     | GPIO7             | General-purpose programmable I/O                                                                                                           |  |  |  |  |

| 4     | GPIO6             | General-purpose programmable I/O                                                                                                           |  |  |  |  |

| 5     | GPIO5             | General-purpose programmable I/O                                                                                                           |  |  |  |  |

| 6     | GPIO4             | General-purpose programmable I/O                                                                                                           |  |  |  |  |

| 7     | GPIO3             | General-purpose programmable I/O                                                                                                           |  |  |  |  |

| 8     | GPIO2             | General-purpose programmable I/O                                                                                                           |  |  |  |  |

| 9     | ADDR              | Address input, GND or V <sub>CC</sub>                                                                                                      |  |  |  |  |

| 10    | /RST              | Reset input, active LOW, requires a pull-up resistor to V <sub>CC</sub>                                                                    |  |  |  |  |

| 11    | GPIO1             | General-purpose programmable I/O                                                                                                           |  |  |  |  |

| 12    | GPIO0             | General-purpose programmable I/O                                                                                                           |  |  |  |  |

| 13    | SCL               | I <sup>2</sup> C serial bus; requires a pull-up resistor to V <sub>CC</sub>                                                                |  |  |  |  |

| 14    | SDA               | I <sup>2</sup> C serial data; requires a pull-up resistor to V <sub>CC</sub>                                                               |  |  |  |  |

| 15    | V <sub>cc</sub>   | Supply voltage                                                                                                                             |  |  |  |  |

| 16    | GND               | Ground                                                                                                                                     |  |  |  |  |

FXL6408 • Rev. 1.0.0

FXL6408 — Fully Configurable 8-Bit I<sup>2</sup>C-Controlled GPIO Expander

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol             | Parameter                                | Condition                         | Min. | Max. | Unit |

|--------------------|------------------------------------------|-----------------------------------|------|------|------|

| $V_{CC}, V_{DDIO}$ | Supply Voltages                          |                                   | -0.5 | 4.6  | V    |

| V <sub>IN</sub>    | DC Input Voltage                         |                                   | -0.5 | 4.0  | V    |

| V <sub>OUT</sub>   | Output Voltage <sup>(1)</sup>            |                                   | -0.5 | 4.0  | V    |

| I <sub>IK</sub>    | DC Input Diode Current                   | V <sub>IN</sub> < 0 V             |      | -50  | mA   |

| I <sub>ок</sub>    | DC Output Diode Current                  | V <sub>OUT</sub> < 0 V            |      | -50  | mA   |

| I <sub>OL</sub>    | DC Output Sink Current                   |                                   |      | +50  | mA   |

| Icc                | DC V <sub>CC</sub> or Ground Current per | Supply Pin                        |      | ±100 | mA   |

| T <sub>STG</sub>   | Storage Temperature Range                |                                   | -65  | +150 | °C   |

| TJ                 | Junction Temperature under B             | ias                               |      | +150 | °C   |

| TL                 | Junction Lead Temperature, S             | oldering 10 Seconds               |      | +260 | °C   |

| Θ <sub>JA</sub>    | Thermal Resistance, Junction-            |                                   | 115  | °C/W |      |

| ESD                | Electrostatic Discharge                  | Human Body Model, JESD22-A114     |      | 4    |      |

| ESD                | Capability                               | Charged Device Model, JESD22-C101 |      | 2    | - kV |

Note:

1. All output current absolute maximum ratings must be observed.

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol                          | Parameter                             | Condition                                | Min. | Max.              | Unit |  |

|---------------------------------|---------------------------------------|------------------------------------------|------|-------------------|------|--|

| V <sub>cc</sub>                 | Supply Voltage Operating              |                                          | 1.65 | 3.60              | V    |  |

| V <sub>DDIO</sub>               | I/O Side Reference Voltage            |                                          | 1.65 | 4.00              | V    |  |

| V <sub>IN</sub>                 | Input Voltage on I/O pins             |                                          | 0    | 4.0               | V    |  |

| Vout                            | Output Voltage                        |                                          | 0    | V <sub>DDIO</sub> | V    |  |

| T <sub>A</sub>                  | Operating Temperature                 |                                          | -40  | +85               | °C   |  |

|                                 | Input Rise and Fall Times to I/O Pins | V <sub>DDIO</sub> at 1.8 V, 2.5 V ±0.2 V | 0    | 200               |      |  |

| t <sub>r</sub> , t <sub>f</sub> | when Configured as Inputs             | V <sub>DDIO</sub> at 3.6 V ± 0.3 V       | 0    | 100               | ns/V |  |

| Symbol                      | Parameter                                  | Condition                                                     | V <sub>cc</sub> (V)   | т                           | =25°                      | С    | T <sub>A</sub> =-40 to<br>85°C |      | Unit |

|-----------------------------|--------------------------------------------|---------------------------------------------------------------|-----------------------|-----------------------------|---------------------------|------|--------------------------------|------|------|

|                             |                                            |                                                               | ,                     | Min.                        | Тур.                      | Max. | Min.                           | Max. |      |

| RST, ADI                    | DR, SDA, SCL, /INT Pins                    |                                                               |                       |                             |                           |      |                                |      |      |

| $V_{POR}$                   | Power-On Reset Voltage                     | V <sub>DDIO</sub> =0 to 4.0 V                                 |                       |                             |                           | 1.25 |                                | 1.25 | V    |

| I <sub>IN</sub>             | Input Leakage Current                      | $0 \leq V_{IN} \leq V_{CC}$                                   | 0 to 3.6              |                             |                           | ±1   |                                | ±10  | μA   |

| I <sub>OFF</sub>            | Power-Off Leakage<br>Current               | $V_{IN}$ or $V_{OUT}$ =3.6 V                                  | 0                     |                             |                           | 1    |                                | 10   | μA   |

| 1                           | Standby Mode<br>(SCL in Static Condition)  | V <sub>IN</sub> =V <sub>CC</sub> or GND                       | 1.8 to 3.6            |                             |                           | 1.2  |                                | 1.5  |      |

| lcc                         | Active Mode <sup>(2)</sup> (SCL<br>Active) |                                                               | 1.0 10 3.0            |                             |                           | 300  |                                | 300  | μA   |

| GPIO Pi                     | ns                                         |                                                               | V <sub>DDIO</sub> (V) |                             |                           |      |                                |      |      |

| N                           |                                            |                                                               | 1.65 to 1.95          | 0.65<br>V <sub>DDIO</sub>   |                           |      | 0.65<br>V <sub>DDIO</sub>      |      | V    |

| V <sub>IH</sub>             | HIGH Level Input Voltage                   |                                                               | 2.30 to 4.00          | 0.70<br>V <sub>DDIO</sub>   |                           |      | 0.70<br>V <sub>DDIO</sub>      |      |      |

| VIL LOW Level Input Voltage |                                            | 1.65 to 1.95                                                  | -0.3                  |                             | 0.35<br>V <sub>DDIO</sub> | -0.3 | 0.35<br>V <sub>DDIO</sub>      | V    |      |

|                             |                                            | 2.30 to 4.0                                                   | -0.3                  |                             | 0.30<br>V <sub>DDIO</sub> | -0.3 | 0.30<br>V <sub>DDIO</sub>      |      |      |

|                             |                                            | V <sub>IN</sub> =V <sub>IH</sub> ,<br>I <sub>OH</sub> =100 μΑ | 1.8                   | V <sub>DDIO</sub><br>- 0.2  |                           |      | V <sub>DDIO</sub><br>- 0.2     |      | V    |

|                             |                                            |                                                               | 3.6                   | V <sub>DDIO</sub><br>- 0.2  |                           |      | V <sub>DDIO</sub><br>- 0.2     |      |      |

| V <sub>OH</sub>             | HIGH Level Output<br>Voltage               |                                                               | 4.0                   | V <sub>DDIO</sub><br>- 0.2  |                           |      | V <sub>DDIO</sub><br>- 0.2     |      |      |

|                             |                                            | I <sub>ОН</sub> =6 mA                                         | 1.8                   | V <sub>DDIO</sub><br>- 0.45 |                           |      | V <sub>DDIO</sub><br>- 0.45    |      |      |

|                             |                                            |                                                               | 3.6                   | V <sub>DDIO</sub><br>- 0.45 |                           |      | V <sub>DDIO</sub><br>- 0.45    |      |      |

|                             |                                            | V <sub>IN</sub> =V <sub>IL</sub> ,                            | 1.8                   |                             |                           | 0.2  |                                | 0.2  | V    |

|                             |                                            | I <sub>OL</sub> = -100 μA                                     | 3.6                   |                             |                           | 0.2  |                                | 0.2  |      |

| V <sub>OL</sub>             | LOW Level Output Voltage                   |                                                               | 4.0                   |                             |                           | 0.2  |                                | 0.2  |      |

|                             |                                            | I <sub>OL</sub> =-6 mA                                        | 1.8                   |                             |                           | 0.45 |                                | 0.45 |      |

|                             |                                            |                                                               | 3.6                   |                             |                           | 0.5  |                                | 0.5  |      |

| $R_{PULL}$                  | Pull-Up or Pull-Down<br>Resistors          |                                                               |                       |                             | 100                       |      |                                |      | kΩ   |

| I <sub>OL</sub>             | Output Low Current                         |                                                               | 1.8 to 4.0            | 6.0                         |                           |      | 6.0                            |      | mA   |

| I <sub>OH</sub>             | Output High Current                        |                                                               | 1.8 to 4.0            | -6.0                        |                           |      | -6.0                           |      |      |

| I <sub>IN</sub>             | Input Low Current <sup>(3)</sup>           | $0 \le V_{IN} \le V_{DDIO}$                                   | 1.8 to 4.0            |                             |                           | ±50  |                                | ±50  | μA   |

| I <sub>OFF</sub>            | Power-Off Leakage<br>Current               | V <sub>IN</sub> =4.0 V                                        | 0                     |                             |                           | 1    |                                | 10   | μA   |

2. Includes all internal circuitry consumption from the  $V_{\text{CC}}$  supply. Does not include the I/O buffers, which are

supplied by V<sub>DDIO</sub> and are load dependent. I<sub>IL</sub> and I<sub>IH</sub> specifications only apply when the outputs are configured with pull-down or pull-up resistors, respectively. Specifications values assume V<sub>IN</sub> <= V<sub>DDIO</sub>. 3.

# DC Characteristics (I<sup>2</sup>C Controller SDA, SCL)

| Symbol           | Beremeter                                              | Fast Mode (400 kHz)   |                      |                     |    |  |

|------------------|--------------------------------------------------------|-----------------------|----------------------|---------------------|----|--|

| Symbol           | Parameter                                              | Min.                  | Max.                 | Unit                |    |  |

| VIL              | Low-Level Input Voltage                                |                       | -0.5                 | 0.3 V <sub>CC</sub> | V  |  |

| V <sub>IH</sub>  | High-Level Input Voltage                               | 0.7 V <sub>CC</sub>   |                      | V                   |    |  |

| V                | Hustoropia of Cohmitt Trigger Inputs                   | V <sub>CC</sub> > 2 V | 0.05 V <sub>CC</sub> |                     | v  |  |

| V <sub>HYS</sub> | Hysteresis of Schmitt Trigger Inputs                   | $V_{CC}$ < 2 V        | 0.1 V <sub>CC</sub>  |                     | v  |  |

| M                | Low-level Output Voltage at 3 mA Sink Current          | V <sub>CC</sub> > 2 V | 0                    | 0.4                 | V  |  |

| V <sub>OL</sub>  | (Open-Drain or Open-Collector)                         | $V_{CC}$ < 2 V        |                      | $0.2 V_{CC}$        | V  |  |

| I <sub>I</sub>   | Input Current of Each I/O Pin, Input Voltage 0.26 V to | -10                   | 10                   | μA                  |    |  |

| Cı               | Capacitance for Each I/O Pin                           |                       |                      | 10                  | pF |  |

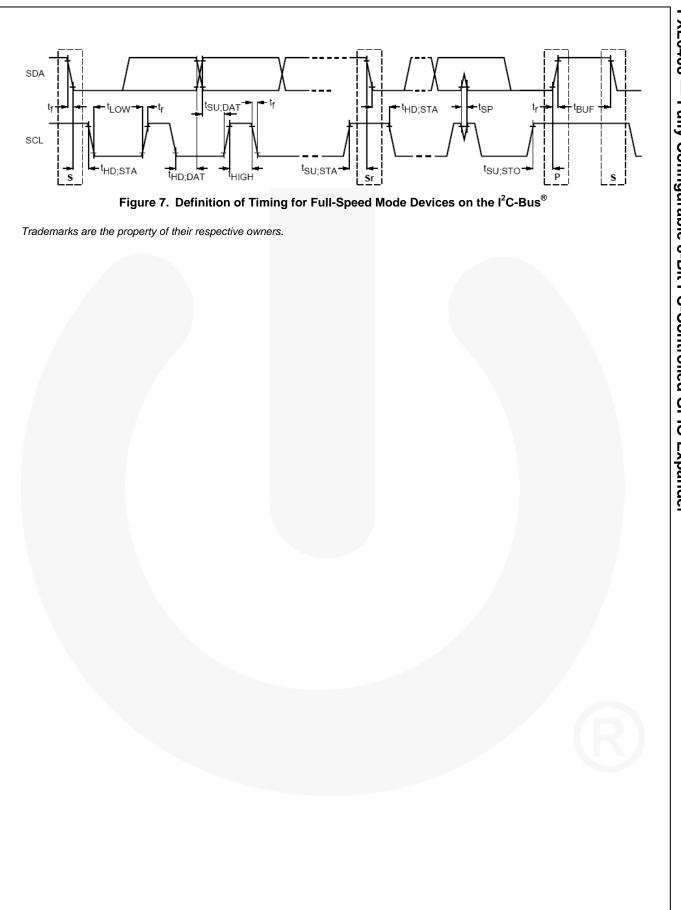

# AC Electrical Characteristics (I<sup>2</sup>C Controller SDA, SCL)

| Ourseland           | Baramatan                                                         | Fast Mode (400 kHz)       |      |      |  |  |

|---------------------|-------------------------------------------------------------------|---------------------------|------|------|--|--|

| Symbol              | Parameter                                                         | Min.                      | Max. | Unit |  |  |

| f <sub>SCL</sub>    | SCL Clock Frequency                                               | 0                         | 400  | kHz  |  |  |

| t <sub>HD;STA</sub> | Hold Time (Repeated) START Condition                              | 0.6                       |      | μs   |  |  |

| t <sub>LOW</sub>    | LOW Period of SCL Clock                                           | 1.3 <sup>(4)</sup>        |      | μs   |  |  |

| t <sub>HIGH</sub>   | HIGH Period of SCL Clock                                          | 0.6                       |      | μs   |  |  |

| t <sub>su;sta</sub> | Set Up Time for Repeated START Condition                          | 0.6                       |      | μs   |  |  |

| t <sub>HD;DAT</sub> | Data Hold Time (See Figure 7)                                     | 0                         | 0.9  | μs   |  |  |

| t <sub>su;dat</sub> | Data Set Up Time (See Figure 7)                                   | 100 <sup>(5)</sup>        |      | ns   |  |  |

| t <sub>PS</sub>     | Set Up Time Required by SDA Input Buffer (When Receiving Data)    | 0                         |      | ns   |  |  |

| t <sub>PH</sub>     | Out Delay Required by SDA Output Buffer (When Transmitting Data)  | 300                       |      | ns   |  |  |

| tr                  | Rise Time of SDA and SCL Signals                                  | 20+0.1Cb <sup>(6,7)</sup> | 300  | ns   |  |  |

| t <sub>f</sub>      | Fall Time of SDA and SCL Signals                                  | 20+0.1Cb <sup>(6,7)</sup> | 300  | ns   |  |  |

| tsu;stop            | Set Up Time for STOP Condition                                    | 0.6                       |      | μs   |  |  |

| t <sub>BUF</sub>    | Bus Free Time between a STOP and START Conditions                 | 1.3                       |      | μs   |  |  |

| t <sub>SP</sub>     | Pulse Width of Spikes that Must Be Suppressed by the Input Filter | 0                         | 50   | ns   |  |  |

All typical value are for  $V_{CC}$ =1.8 V at  $T_A$ =25°C unless otherwise specified.

Notes:

4. The FXL6408 can accept clock signals with LOW as low as 1.1 μs, provided that the received SDA signal t<sub>HD;DAT</sub>+ t<sub>r/f</sub><=1.1 μs. The FXL6408 features a 0 ns SDA input setup time and, therefore, this parameter is not included in the above equation.</p>

5. A Fast-Mode I<sup>2</sup>C-Bus<sup>®</sup> device can be used in a Standard-Mode I<sup>2</sup>C-Bus system, but the requirement t<sub>SU;DAT</sub> ≥ 250 ns must be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal. It must output the next data bit to the SDA line t<sub>r\_max</sub> + t<sub>SU;DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard-Mode I<sup>2</sup>C bus specification) before the SCL line is released.

C<sub>b</sub> equals the total capacitance of one bus line in pF. If mixed with High-Speed Mode devices, faster fall times are allowed, according to the l<sup>2</sup>C specification.

7. The FXL6408 ensures that the SDA signal out must coincide with SCL LOW for worst-case SCL t<sub>f</sub> maximum times of 300 ns. This requirement prevents data loss by preventing SDA out transitions during the undefined region of the falling edge of SCL. Consequently, the FXL6408 fulfils the following requirement from the l<sup>2</sup>C specification, note 2 on page 77: "A device must internally provide a hold time of at least 300 ns for the SDA signal (referred to the V<sub>IHmin</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL."

8. FXL6408 I<sup>2</sup>C slave is fully compliant the NXP (Phillips) I<sup>2</sup>C specification Rev. 0.3 UM10204 (2007).

## **Functional Description**

### **Overview**

The FXL6408 I/O expander frees up six ports of the central processor to be dedicated for more critical functions. The FXL6408 enables the addition of eight General-Purpose Input / Output (GPIO) ports to a system processor while using two I/O ports for I<sup>2</sup>C control (net six additional I/Os). The device can be used in multiple applications, from button monitoring to driving control pins of other ICs in the system. It also allows the system designer to add new features and functions quickly without upgrading the central processor. The FXL6408 includes eight I/O pins controlled by an integrated I<sup>2</sup>C slave and allows the central processor to control each I/O independently. When configured as outputs, each pin can deliver up to 6 mA drive. When configured as inputs, the default state can be independently configured. In addition, the FXL6408 has integrated pull-up and pull-down resistors that are enabled via I<sup>2</sup>C commands in the register map. This allows the system designer to pre-bias the inputs to a known level to allow use with un-driven input signals.

### **Interrupt Operation**

The /INT pin is a LOW-asserted open-drain output and requires an external pull-up resistor. The FXL6408 signals an interrupt to the processor when an event occurs, removing the need for the processor to continuously poll the FXL6408 registers. Immediately after detecting a change at an input, the FXL6408 writes the corresponding bit in the input interrupt status register (13<sub>h</sub>) and asserts the /INT pin by pulling it LOW. The interrupt status register bit remains HIGH until the processor reads the register and clears the bit. If the input pin remains in the non-default state after the interrupt has been serviced, a new interrupt is not generated until after the input state has first returned to its default state and changed back to its non-default state. The FXL6408 also contains an Input Status register (0F<sub>h</sub>) used to verify the current status of the given input at the time when the interrupt is serviced by the processor. These two registers allow the processor to determine the following information about any input every time the register map is read:

- If the input state changed from the default state since the most recent register read; and

- The current state of the input pin.

The interrupt output /INT, once asserted, is held LOW until the interrupt is serviced by the processor. This means that the system uses level-sensitive interrupts. Interrupt signaling is asynchronous to the SCL signal.

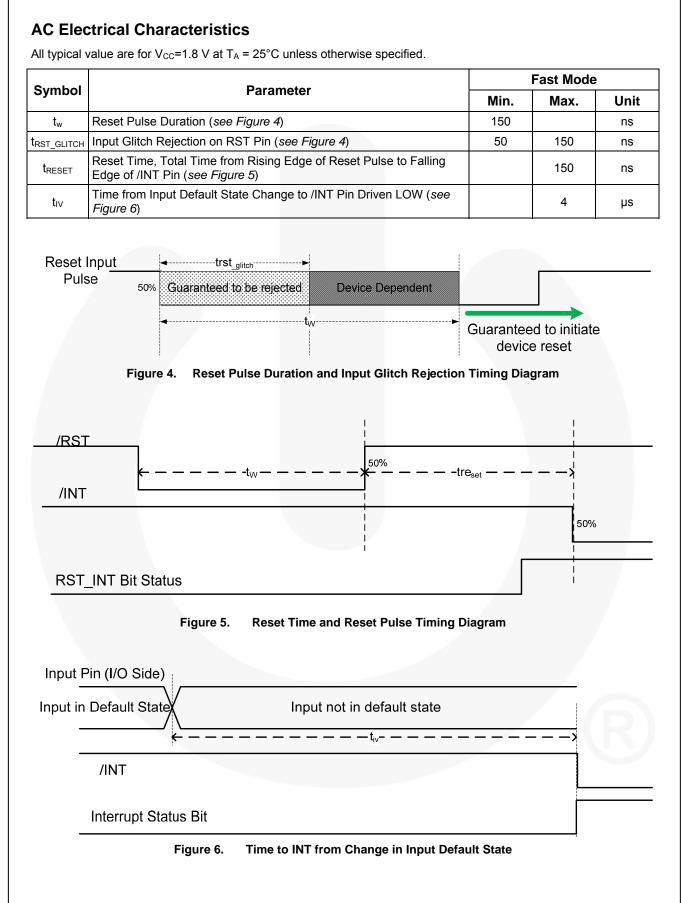

### **Device Reset**

The FXL6408 has three reset options, all of which cause the part to reset all register settings to their default states. Immediately after device reset, the RST\_INT bit in the Device ID & Ctrl register (01h) is HIGH and an interrupt signal is generated by the FXL6408. After the processor reads the register, this bit is cleared and, on future register reads, the processor can verify that the FXL6408 has not been reset if this bit remains LOW. Following are descriptions of the three reset methods.

### Power-On Reset (POR)

On device power-up, when  $V_{CC}$  reaches  $V_{POR}$  or if the  $V_{CC}$  supply voltage drops below  $V_{POR}$  during operation, the FXL6408 immediately resets.

### Software Reset

The FXL6408 can be reset by the processor using an  $I^2C$  write command to change bit 0 of register 01h to a 1. Immediately following this change, the FXL6408 resets and all register values return to their default values. In this case, the SW\_RST bit returns to 0 as soon as the reset sequence is completed.

### **Reset Pin**

The FXL6408 is reset when the /RST pin (C3) is pulled LOW.

### Translation

The FXL6408 has the ability to translate between the system  $I^2C$  voltage reference and the I/O voltage reference. The V<sub>CC</sub> pin is used both as the FXL6408 power supply as well as the voltage reference for the  $I^2C$  inputs, ADDR, /INT, and RESET pins. The V<sub>DDIO</sub> pin is used only for the voltage supply reference of the I/O ports. For example, a 1.8 V-referenced  $I^2C$  Bus can be used to interface with the FXL6408 and control 3.6 V-referenced I/Os by supplying V<sub>CC</sub> = 1.8 V and V<sub>DDIO</sub> = 3.6 V. If translation is not needed, the system provides the same voltage to both the V<sub>CC</sub> and V<sub>DDIO</sub> pins. If both the I/O and  $I^2C$  interfaces are referenced to 1.8 V, the V<sub>CC</sub> supply and V<sub>DDIO</sub> pin should both be tied to 1.8 V.

| I <sup>2</sup> C Read /<br>Figure 8 and<br>or write optior | Figure 9 i                                             | llustrate co  | ompatible | e I <sup>2</sup> C<br><sup>2</sup> C sta | write a<br>andard. | nd read             | sequenc    | es. The                  | FXL6408   | does no | ot support | t burst read   |

|------------------------------------------------------------|--------------------------------------------------------|---------------|-----------|------------------------------------------|--------------------|---------------------|------------|--------------------------|-----------|---------|------------|----------------|

|                                                            |                                                        |               | 8bit      | S                                        |                    | 8b                  | its        | 8bi                      | ts        |         |            |                |

|                                                            |                                                        | S SI          | ave Addr  | ress                                     | WRAR               | egister A           | Address K  | A Write                  | Data A P  | 7       |            |                |

|                                                            |                                                        |               |           | Figu                                     |                    |                     | ite Sequ   |                          |           | _       |            |                |

|                                                            | 8b                                                     | its           |           | 8bit                                     |                    |                     | 8bit       |                          | 8k        | oits    |            |                |

| s                                                          | Slave Add                                              | Iress WR      | A Regist  | er Ad                                    | ldress K           | ASS                 | lave Addr  | ess RD                   | A Read    | Data K  | NA P       |                |

| <u> </u>                                                   | Slave Alae                                             |               |           |                                          |                    |                     |            |                          | neuu      | Dutu K  |            |                |

|                                                            | Regis                                                  | ter address   | to read s | pecif                                    | ied                | -                   |            | -byte read<br>on (single |           |         |            |                |

|                                                            | ite Bis                                                |               |           | peen                                     |                    | 105                 |            |                          | byterea   |         | cuj        |                |

|                                                            | Note:                                                  | If register i | s not spe | cified                                   | l, the ma          | ster read           | ls from th | e current                | register. |         |            |                |

|                                                            |                                                        |               |           |                                          |                    | 2                   |            |                          |           |         |            |                |

|                                                            |                                                        |               |           | Figu                                     | re 9.              | I <sup>2</sup> C Re | ad Sequ    | ence                     |           |         |            |                |

|                                                            | n Master to                                            |               |           |                                          | dition             |                     |            | Acknowle                 | edge (SDA | High)   |            | ead =1         |

| Fror                                                       | n Slave to N                                           | Aaster        | A Ack     | nowle                                    | edge (SD/          | A Low)              | WR Writ    | te=0                     |           |         | P St       | op Condition   |

|                                                            |                                                        |               |           |                                          |                    |                     |            |                          |           |         |            |                |

|                                                            | C Addre                                                |               |           |                                          |                    |                     |            |                          |           |         |            |                |

| Register                                                   | -                                                      | DR Pin        | B7        | B6                                       |                    | 5                   | B4         | B3                       |           | B2      | B1         | BO             |

| Device Addro                                               | ess                                                    | DR=0<br>DR=1  | 1         | 0                                        |                    | )<br>)              | 0          | 0                        |           | 1       | 1<br>0     | WR<br>WR       |

|                                                            |                                                        | DIX=1         | ·         | 0                                        |                    | 5                   | 0          |                          |           | •       | 0          | VVIX           |

| Fable 2. I <sup>2</sup>                                    | C Regis                                                | tor Man       |           |                                          |                    |                     |            |                          |           |         |            |                |

|                                                            | C Regis                                                |               |           |                                          |                    |                     |            |                          | [         |         |            | Deeet          |

| Register                                                   | Address                                                | Туре          | B7        |                                          | B6                 | B5                  | B4         | B3                       | B2        | B1      | B0         | Reset<br>Value |

| Device ID &<br>Ctrl                                        | 01h                                                    | R/W           | MF        | 3                                        | MF2                | MF1                 | FW_rev3    | FW_rev2                  | FW_rev1   | RST_INT | SW_RST     | 10100010       |

| IO Direction                                               | 03h                                                    | R/W           | GPIC      | )7                                       | GPIO6              | GPIO5               | GPIO4      | GPIO3                    | GPIO2     | GPIO1   | GPIO0      | 0000000        |

| Output State                                               | 05h                                                    | R/W           | Out       | 7                                        | Out 6              | Out 5               | Out 4      | Out 3                    | Out 2     | Out 1   | Out 0      | 0000000        |

| Dutput High-Z                                              | 07h                                                    | R/W           | Out       | 7                                        | Out 6              | Out 5               | Out 4      | Out 3                    | Out 2     | Out 1   | Out 0      | 11111111       |

| Input Default<br>State                                     | 09h                                                    | R/W           | In 7      | ,                                        | In 6               | In 5                | ln 4       | In 3                     | In 2      | In 1    | In 0       | 0000000        |

| Pull Enable                                                | 0Bh                                                    | R/W           | In 7      | ,                                        | In 6               | ln 5                | In 4       | In 3                     | In 2      | In 1    | In 0       | 111111111      |

| Pull-Down/<br>Pull-Up                                      | 0Dh                                                    | R/W           | In 7      | ,                                        | In 6               | In 5                | In 4       | In 3                     | In 2      | In 1    | In 0       | 00000000       |

| Input Status                                               | 0Fh                                                    | R             | In 7      | ,                                        | In 6               | ln 5                | In 4       | In 3                     | In 2      | In 1    | In 0       | XXXXXXXX       |

| nterrupt Mask                                              | 11h                                                    | R/W           | In 7      | ,                                        | ln 6               | ln 5                | In 4       | In 3                     | In 2      | In 1    | In 0       | 0000000        |

| Interrupt<br>Status                                        | 13h                                                    | R/W           | In 7      |                                          | ln 6               | ln 5                | In 4       | In 3                     | ln 2      | In 1    | In 0       | XXXXXXXX       |

| Reserved                                                   | 02h, 04h,<br>06h, 08h,<br>0Ah, 0Ch,<br>OEh,10h,<br>12h | Reserved      | xxxxx     | xxx                                      |                    |                     |            |                          |           |         |            |                |

### Table 3. Device ID & Control

- Address 01<sub>h</sub>

- RST INT flag is cleared after being read by master.

- For SW reset, the master writes bit 0 HIGH.

| Bit# | Name    | Bit Size | Description                                                                                                                                                                                      |

|------|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5  | MF      | 3        | 3-bit manufacturer ID assigned by Nokia, Bits 7:5 are 101 for Fairchild.                                                                                                                         |

| 4:2  | FW_rev  | 3        | 3-bit ascending value, indicating the firmware revision.<br>Initial revision is 000.                                                                                                             |

| 1    | RST_INT | 1        | <ul><li>Indicates that the device has been reset and the default values are set.</li><li>0: normal operation</li><li>1: the device has been reset and register default values are set.</li></ul> |

| 0    | SW_RST  | 1        | Software reset:<br>0: normal operation<br>1: SW reset commanded                                                                                                                                  |

## Table 4. IO Direction

Address 03<sub>h</sub>

| Bit# | Name  | Bit Size | Description                   |

|------|-------|----------|-------------------------------|

| 7    | GPIO7 | 1        |                               |

| 6    | GPIO6 | 1        |                               |

| 5    | GPIO5 | 1        |                               |

| 4    | GPIO4 | 1        | 0: GPIO configured as input.  |

| 3    | GPIO3 | 1        | 1: GPIO configured as output. |

| 2    | GPIO2 | 1        |                               |

| 1    | GPIO1 | 1        |                               |

| 0    | GPIO0 | 1        |                               |

### Table 5. Output State

- Address 05<sub>h</sub>

- If the pin is defined as input in register 03<sub>h</sub>, the corresponding bit has no effect.

| Bit# | Name  | Bit Size | Description            |

|------|-------|----------|------------------------|

| 7    | Out 7 | 1        |                        |

| 6    | Out 6 | 1        |                        |

| 5    | Out 5 | 1        |                        |

| 4    | Out 4 | 1        | 0: GPIO output = LOW.  |

| 3    | Out 3 | 1        | 1: GPIO output = HIGH. |

| 2    | Out 2 | 1        |                        |

| 1    | Out 1 | 1        | ]                      |

| 0    | Out 0 | 1        |                        |

### Table 6. Output High-Z

- Address 07<sub>h</sub>

- If the pin is defined as input in register 03<sub>h</sub>, the corresponding bit has no effect.

| Bit# | Name  | Bit Size | Description                               |

|------|-------|----------|-------------------------------------------|

| 7    | Out 7 | 1        |                                           |

| 6    | Out 6 | 1        |                                           |

| 5    | Out 5 | 1        |                                           |

| 4    | Out 4 | 1        | 0: GPIO output state follows register 05h |

| 3    | Out 3 | 1        | 1: GPIO output = High-Z                   |

| 2    | Out 2 | 1        |                                           |

| 1    | Out 1 | 1        |                                           |

| 0    | Out 0 | 1        |                                           |

### Table 7. Input Default State

- Address 09<sub>h</sub>

- Defines the expected state of the GPIO

- If the pin is defined as output in register 03<sub>h</sub>, the corresponding bit has no effect.

| Bit# | Name | Bit Size | Description                                         |

|------|------|----------|-----------------------------------------------------|

| 7    | In 7 | 1        |                                                     |

| 6    | In 6 | 1        |                                                     |

| 5    | In 5 | 1        | 0: GPIO input default is set to LOW; when the GPIO  |

| 4    | In 4 | 1        | goes HIGH, an interrupt is triggered.               |

| 3    | In 3 | 1        | 1: GPIO input default is set to HIGH; when the GPIO |

| 2    | In 2 | 1        | goes LOW, an interrupt is triggered.                |

| 1    | In 1 | 1        |                                                     |

| 0    | In 0 | 1        |                                                     |

### Table 8. Pull Enable

- Address 0B<sub>h</sub>

- Pull enable for input pin

- If the pin is defined as output in register 03<sub>h</sub>, the corresponding bit has no effect.

| Bit# | Name | Bit Size | Description                                     |

|------|------|----------|-------------------------------------------------|

| 7    | In 7 | 1        |                                                 |

| 6    | In 6 | 1        |                                                 |

| 5    | In 5 | 1        |                                                 |

| 4    | In 4 | 1        | 0: GPIO input pull-up/pull-down is not enabled. |

| 3    | In 3 | 1        | 1: GPIO input Pull-up/Pull-down is enabled.     |

| 2    | In 2 | 1        |                                                 |

| 1    | In 1 | 1        |                                                 |

| 0    | In 0 | 1        |                                                 |

### Table 9. Pull-Down / Pull-Up

- Address 0D<sub>h</sub>

- If the pin is defined as output in register 03<sub>h</sub>, the corresponding bit has no effect.

- If the corresponding bit in register 0B<sub>h</sub>=0, this register setting has no effect.

| Bit# | Name | Bit Size | Description                         |

|------|------|----------|-------------------------------------|

| 7    | In 7 | 1        |                                     |

| 6    | In 6 | 1        |                                     |

| 5    | In 5 | 1        |                                     |

| 4    | In 4 | 1        | 0: GPIO input pull-down is enabled. |

| 3    | In 3 | 1        | 1: GPIO input pull-up is enabled.   |

| 2    | In 2 | 1        |                                     |

| 1    | In 1 | 1        |                                     |

| 0    | In 0 | 1        |                                     |

### Table 10. Input Status

- Address 0F<sub>h</sub>

- If the pin is defined as output in register 03<sub>h</sub>, the corresponding bit has no effect.

- This bit shows the real-time input pin status.

| Bit# | Name | Bit Size | Description            |

|------|------|----------|------------------------|

| 7    | In 7 | 1        |                        |

| 6    | In 6 | 1        |                        |

| 5    | In 5 | 1        |                        |

| 4    | In 4 | 1        | 0: GPIO input is LOW.  |

| 3    | In 3 | 1        | 1: GPIO input is HIGH. |

| 2    | In 2 | 1        |                        |

| 1    | In 1 | 1        |                        |

| 0    | In 0 | 1        |                        |

### Table 11. Interrupt Mask

- Address 11<sub>h</sub>

- If the pin is defined as output in register 03<sub>h</sub>, the corresponding bit has no effect.

- This bit enables the interrupt generation from input pin state change to INT.

| Bit# | Name | Bit Size | Description                           |

|------|------|----------|---------------------------------------|

| 7    | In 7 | 1        |                                       |

| 6    | In 6 | 1        |                                       |

| 5    | In 5 | 1        |                                       |

| 4    | In 4 | 1        | 0: GPIO input interrupt is generated. |

| 3    | In 3 | 1        | 1: GPIO input interrupt is masked.    |

| 2    | In 2 | 1        |                                       |

| 1    | In 1 | 1        |                                       |

| 0    | In 0 | 1        |                                       |

# FXL6408 — Fully Configurable 8-Bit I<sup>2</sup>C-Controlled GPIO Expander

### Table 12. Interrupt Status

- Address 13<sub>h</sub>

- This bit is HIGH if input GPIO ≠ default state (register 09h).

- The flag is cleared after being read by the master (bit returns to 0).

- The input must go back to default state and change again before this flag is raised again.

| Bit# | Name | Bit Size | Description                                                     |

|------|------|----------|-----------------------------------------------------------------|

| 7    | ln 7 | 1        |                                                                 |

| 6    | In 6 | 1        |                                                                 |

| 5    | ln 5 | 1        |                                                                 |

| 4    | In 4 | 1        | 0: GPIO input is in default state or the flag has been cleared. |

| 3    | ln 3 | 1        | 1: GPIO input has changed state from default.                   |

| 2    | ln 2 | 1        |                                                                 |

| 1    | In 1 | 1        |                                                                 |

| 0    | In 0 | 1        |                                                                 |

|      |      |          |                                                                 |

### FAIRCHILD SEMICONDUCTOR TRADEMARKS The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks. 2CoolTN F-PESTM PowerTrench<sup>®</sup> The Power Franchise® FRFET® AccuPower™ PowerXS<sup>TI</sup> wer Global Power Resource<sup>SM</sup> Programmable Active Droop™ AX-CAP™\* franchise GreenBridge™ QFET BitSiC™ TinyBoost™ Build it Now™ Green FPS™ QS™ TinyBuck™ Green FPS™ e-Series™ Quiet Series™ CorePLUS™ TinyCalc™ Gmax™ RapidConfigure™ CorePOWER™ TinyLogic® GTO™ **CROSSVOLT™ TINYOPTO<sup>TM</sup>** IntelliMAX<sup>TN</sup> CTL™ Saving our world, 1mW/W/kW at a time™ TinyPower™ **ISOPLANAR™** Current Transfer Logic™ SignalWise™ TinyPWM™ Making Small Speakers Sound Louder DEUXPEED® TinyWire™ SmartMax™ and Better Dual Cool™ SMART START TranSiC™ EcoSPARK<sup>®</sup> MegaBuck™ Solutions for Your Success™ TriFault Detect™ MICROCOUPLER™ EfficientMax™ TRUECURRENT®\* SPM® **MicroFET™** ESBC<sup>Th</sup> STEALTH™ μSerDes™ MicroPak™ SuperFET<sup>®</sup> MicroPak2™ SuperSOT™-3 Fairchild® MillerDrive™ SuperSOT™-6 UHC Fairchild Semiconductor® MotionMax™ SuperSOT™-8 FACT Quiet Series™ Ultra FRFET™ mWSaver™ SupreMOS® UniFET™ FACT FAST® **OntoHiT™** SyncFET™ VCX™ **OPTOLOGIC®** Sync-Lock™ FastvCore™ VisualMax™ **OPTOPLANAR®** GENERAL®. **FETBench**<sup>™</sup> VoltagePlus™ FlashWriter®\* XST **FPSTM** \* Trademarks of System General Corporation, used under license by Fairchild Semiconductor. DISCLAIMER FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN. WHICH COVERS THESE PRODUCTS LIFE SUPPORT POLICY FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein 1. Life support devices or systems are devices or systems which, (a) are 2. A critical component in any component of a life support, device, or intended for surgical implant into the body or (b) support or sustain system whose failure to perform can be reasonably expected to life, and (c) whose failure to perform when properly used in cause the failure of the life support device or system, or to affect its accordance with instructions for use provided in the labeling, can be safety or effectiveness. reasonably expected to result in a significant injury of the user ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild's for handling and storage and provide access to Fairchild's combat this global problem and encourage our customers to obt this prought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to obt their parts buying direct or from authorized distributors.

### PRODUCT STATUS DEFINITIONS

| Definition of Terms      |                       |                                                                                                                                                                                                        |

|--------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Datasheet Identification | Product Status        | Definition                                                                                                                                                                                             |

| Advance Information      | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                          |

| Preliminary              | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild<br>Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make<br>changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor.<br>The datasheet is for reference information only.                                                    |

Rev. 162

XL6408

— Fully Configurable 8-Bit I<sup>2</sup>C-Controlled GPIO Expander