| LTR                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |         |          |         |          |          |          | F        | REVISI     | ONS                       |       |            |                 |       |       |      |            |          |         |          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|---------|----------|---------|----------|----------|----------|----------|------------|---------------------------|-------|------------|-----------------|-------|-------|------|------------|----------|---------|----------|

| REV                                                                                                                                                                                                                                                                                                                                                                                                                                | LTR      |       |         |          |         | ı        | DESCR    | RIPTION  |          |            |                           |       |            | DATE (YR-MO-DA) |       |       |      | APPROVED   |          |         |          |

| REV                                                                                                                                                                                                                                                                                                                                                                                                                                | Δ        | bbA   | case oi | ıtline Y | ′ add v | endor (  | CAGE     | code 18  | 324      |            |                           |       |            | 90-03-08        |       |       |      | W. Hookman |          | 1       |          |

| Table   . Add new footnote 3/ to table   . Editorial changes throughout.                                                                                                                                                                                                                                                                                                                                                           |          |       |         |          |         |          |          |          |          | Tochi      | nical ch                  | angoc | to         |                 |       |       |      | ١,         |          |         |          |

| REV                                                                                                                                                                                                                                                                                                                                                                                                                                | ь        | table | I. Add  | I new fo | onage   | 3/ to ta | able I.  | Editoria | all chan | ges thr    | oughou                    | it.   | 10         |                 | 92-0  | )3-10 |      | '          | vioriica | rueikii | ig       |

| SHEET                                                                                                                                                                                                                                                                                                                                                                                                                              | С        | Upda  | erplate | to curr  | ent MIL | -PRF-    | 38535 ı  | equire   | ments.   | - CFS      | ;                         |       |            | 06-0            | 02-08 |       | 1    | Thomas     | s M. He  | SS      |          |

| SHEET                                                                                                                                                                                                                                                                                                                                                                                                                              |          |       |         |          |         |          |          |          |          |            |                           |       |            |                 |       |       |      |            |          |         |          |

| REV                                                                                                                                                                                                                                                                                                                                                                                                                                |          |       |         |          |         |          |          |          |          |            |                           |       |            |                 |       |       |      |            |          |         |          |

| SHEET                                                                                                                                                                                                                                                                                                                                                                                                                              |          | С     | C       | С        | С       | С        | С        | С        | С        | C          | C                         | С     | С          | C               | C     | С     | С    | C          | C        | C       | С        |

| REV   C   C   C   C   C   C   C   C   C                                                                                                                                                                                                                                                                                                                                                                                            |          |       |         |          |         |          |          |          |          |            |                           |       |            | <u> </u>        | -     |       |      |            |          |         | <u> </u> |

| PMIC N/A  PREPARED BY Todd D. Creek  DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43218-3990 http://www.dscc.dla.mil  APPROVED BY  Michael A. Frye DEPARTMENTS AND AGENCIES OF THE DEPARTMENT OF DEFENSE  AMSC N/A  PREPARED BY  CHECKED BY Ray Monnin  APPROVED BY  Michael A. Frye  MICROCIRCUIT, DIGITAL, CMOS, DUAL ASYNCHRONOUS RECEIVER/TRANSMITTER, MONOLITHIC SILICON  REVISION LEVEL  SIZE CAGE CODE A 67268  5962-89532 |          |       |         |          |         | l        |          |          |          |            |                           |       | 1          |                 |       |       |      |            |          |         |          |

| STANDARD MICROCIRCUIT DRAWING  THIS DRAWING IS AVAILABLE FOR USE BY ALL DEPARTMENTS AND AGENCIES OF THE DEPARTMENT OF DEFENSE  AMSC N/A  TODED D. Creek  DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43218-3990 http://www.dscc.dla.mil  MICROCIRCUIT, DIGITAL, CMOS, DUAL ASYNCHRONOUS RECEIVER/TRANSMITTER, MONOLITHIC SILICON  SIZE CAGE CODE A 67268  5962-89532                                                             |          |       |         |          |         |          |          | 1        | 2        | 3          | 4                         |       | 6          | 1               | 8     | -     | 10   | 11         | 12       | 13      | 14       |

| STANDARD MICROCIRCUIT DRAWING  THIS DRAWING IS AVAILABLE FOR USE BY ALL DEPARTMENTS AND AGENCIES OF THE DEPARTMENT OF DEFENSE  AMSC N/A  THIS DRAWING APPROVAL DATE O4 April 1989  DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43218-3990 http://www.dscc.dla.mil  MICROCIRCUIT, DIGITAL, CMOS, DUAL ASYNCHRONOUS RECEIVER/TRANSMITTER, MONOLITHIC SILICON  REVISION LEVEL  SIZE CAGE CODE A 67268  5962-89532                   | PMIC N/A |       |         |          | PRE     | PARE     | ) BY     | 1        | 1        | 1          |                           | 1     |            |                 | I     | 1     | 1    | 1          | I.       | I       |          |

| STANDARD MICROCIRCUIT DRAWING  THIS DRAWING IS AVAILABLE FOR USE BY ALL DEPARTMENTS AND AGENCIES OF THE DEPARTMENT OF DEFENSE  AMSC N/A  CHECKED BY Ray Monnin  APPROVED BY  Michael A. Frye  Michael A. Frye  DRAWING APPROVAL DATE 04 April 1989  MICROCIRCUIT, DIGITAL, CMOS, DUAL ASYNCHRONOUS RECEIVER/TRANSMITTER, MONOLITHIC SILICON  SIZE CAGE CODE A 67268  5962-89532                                                    |          |       |         |          |         |          | Todd D   | . Creel  | <        |            |                           |       |            |                 |       |       |      |            |          |         |          |

| MICROCIRCUIT DRAWING  THIS DRAWING IS AVAILABLE FOR USE BY ALL DEPARTMENTS AND AGENCIES OF THE DEPARTMENT OF DEFENSE  AMSC N/A  Ray Monnin  APPROVED BY  Michael A. Frye  MICROCIRCUIT, DIGITAL, CMOS, DUAL  ASYNCHRONOUS RECEIVER/TRANSMITTER, MONOLITHIC SILICON  REVISION LEVEL  SIZE CAGE CODE A 67268  5962-89532                                                                                                             | 074      | NDAF  |         |          |         |          |          |          |          |            | COLUMBUS, OHIO 43218-3990 |       |            |                 |       |       |      |            |          |         |          |

| THIS DRAWING IS AVAILABLE FOR USE BY ALL DEPARTMENTS AND AGENCIES OF THE DEPARTMENT OF DEFENSE  AMSC N/A  APPROVED BY  Michael A. Frye  MICROCIRCUIT, DIGITAL, CMOS, DUAL ASYNCHRONOUS RECEIVER/TRANSMITTER, MONOLITHIC SILICON  REVISION LEVEL  SIZE CAGE CODE A 67268  5962-89532                                                                                                                                                |          |       |         |          | CHE     | CKED     |          |          |          |            |                           |       |            |                 |       |       |      |            |          |         |          |

| THIS DRAWING IS AVAILABLE FOR USE BY ALL DEPARTMENTS AND AGENCIES OF THE DEPARTMENT OF DEFENSE  AMSC N/A  Michael A. Frye  MICROCIRCUIT, DIGITAL, CMOS, DUAL ASYNCHRONOUS RECEIVER/TRANSMITTER, MONOLITHIC SILICON  REVISION LEVEL  SIZE A 67268  SHEET                                                                                                                                                                            |          |       |         |          |         |          | Ray N    | /lonnin  |          |            |                           |       |            |                 |       |       |      |            |          |         |          |

| FOR USE BY ALL DEPARTMENTS AND AGENCIES OF THE DEPARTMENT OF DEFENSE  AMSC N/A  REVISION LEVEL  Michael A. Frye  MICROCIRCUIT, DIGITAL, CMOS, DUAL  ASYNCHRONOUS RECEIVER/TRANSMITTER, MONOLITHIC SILICON  SIZE CAGE CODE A 67268  5962-89532                                                                                                                                                                                      |          |       |         |          | APP     | ROVE     | ) BY     |          |          |            |                           |       |            |                 |       |       |      |            |          |         |          |

| DEPARTMENTS AND AGENCIES OF THE DEPARTMENT OF DEFENSE  AMSC N/A  REVISION LEVEL  MICROCIRCUIT, DIGITAL, CMOS, DUAL ASYNCHRONOUS RECEIVER/TRANSMITTER, MONOLITHIC SILICON  REVISION LEVEL  SIZE CAGE CODE A 67268  5962-89532                                                                                                                                                                                                       |          |       |         | BLE      |         | 1        | Michae   | I A. Frv | е        |            |                           |       |            |                 |       |       | _    |            |          |         |          |

| DEPARTMENT OF DEFENSE                                                                                                                                                                                                                                                                                                                                                                                                              | DEPA     | RTMEN | ITS     |          |         |          |          |          |          |            | 4                         |       |            |                 |       |       |      |            |          |         |          |

| AMSC N/A  REVISION LEVEL  SIZE CAGE CODE A 67268  5962-89532                                                                                                                                                                                                                                                                                                                                                                       |          |       |         |          | DRA     | WING     | APPRO    | DVAL D   | ATE      |            |                           |       |            |                 |       |       | ER/T | RAN        | SMIT     | TER,    |          |

| A 67268 5962-89532                                                                                                                                                                                                                                                                                                                                                                                                                 |          |       |         |          |         | 04 Арі   | ril 1989 |          |          | MONOLITHIC |                           |       | IC SILICON |                 |       |       |      |            |          |         |          |

| A 67268 5962-89532                                                                                                                                                                                                                                                                                                                                                                                                                 | AMSC N/A |       |         | REV      | ISION   | LEVEI    |          |          |          | SI         | ZE                        | CA    | GE CC      | DDE             |       |       |      |            |          |         |          |

| C SHEET                                                                                                                                                                                                                                                                                                                                                                                                                            |          |       |         |          |         | <b></b>  |          |          |          |            |                           |       |            |                 |       |       | 5962 | -8953      | 32       |         |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |       |         |          |         | С        |          |          |          | SHEET      |                           |       |            |                 |       |       |      |            |          |         |          |

DSCC FORM 2233 APR 97

### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing describes device requirements for MIL-STD-883 compliant, non-JAN class level B microcircuits in accordance with MIL-PRF-38535, appendix A.

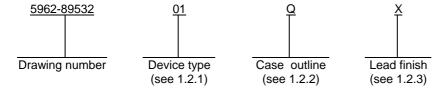

- 1.2 Part or Identifying Number (PIN). The complete PIN is as shown in the following example:

1.2.1 <u>Device type(s)</u>. The device type(s) identify the circuit function as follows:

| Device type | Generic number | <u>Circuit function</u>                                                                |

|-------------|----------------|----------------------------------------------------------------------------------------|

| 01          | 88C681, 2692   | Dual asynchronous receiver/transmitter (DUART)                                         |

| 02          | 88C681, 2692   | Dual asynchronous receiver/transmitter (DUART) with 7-bit input and 8-bit output ports |

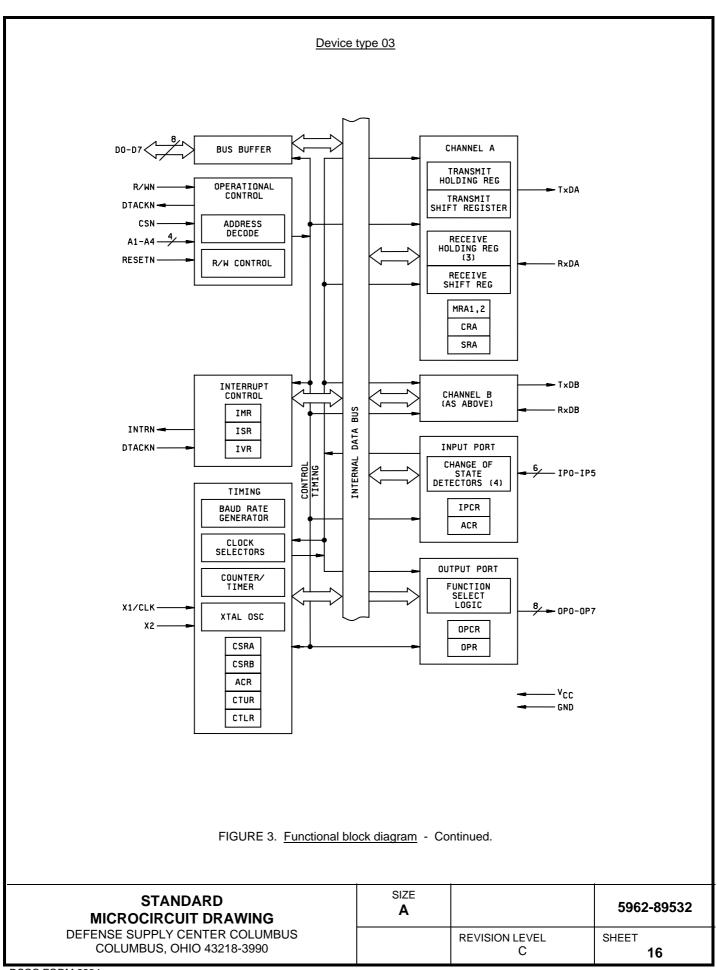

| 03          | 68C681         | Dual asynchronous receiver/transmitter (DUART)                                         |

1.2.2 <u>Case outline(s)</u>. The case outline(s) are as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style                |

|----------------|------------------------|------------------|------------------------------|

| Q              | GDIP1-T40 or CDIP2-T40 | 40               | Dual-in-line                 |

| X              | GDIP1-T28 or CDIP2-T28 | 28               | Dual-in-line                 |

| U              | CQCC1-N44              | 44               | Square leadless chip carrier |

| Υ              | See figure 1.          | 52               | Flat pack                    |

- 1.2.3 Lead finish. The lead finish is as specified in MIL-PRF-38535, appendix A.

- 1.3 Absolute maximum ratings.

| Supply voltage range                                    | 0.5 V dc to +7.0 V dc |

|---------------------------------------------------------|-----------------------|

| Storage temperature range                               |                       |

| Maximum power dissipation (P <sub>D</sub> )             | 1.0 W                 |

| Lead temperature (soldering, 5 seconds)                 |                       |

| Maximum junction temperature (T <sub>1</sub> )          |                       |

| Thermal resistance, junction-to-case ( $\theta_{JC}$ ): |                       |

| Cases X, Q, and U                                       | See MIL-STD-1835      |

| Case Y                                                  | 20°C/W                |

|                                                         |                       |

1.4 Recommended operating conditions.

| Supply voltage (V <sub>CC</sub> )                    | 4.5 V dc to 5.5 V dc |

|------------------------------------------------------|----------------------|

| Minimum high level input voltage (V <sub>IH</sub> ): |                      |

| Logic inputs                                         | 2.0 V dc             |

| X1/CLK input                                         | 4.0 V dc             |

| Maximum low level input voltage (V <sub>IL</sub> )   | 0.8 V dc             |

| Maximum high level output current (I <sub>OH</sub> ) | -400 μΑ              |

| Maximum low level output current (I <sub>OL</sub> )  |                      |

| Case operating temperature range (T <sub>C</sub> )   | -55°C to +125°C      |

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-89532 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>C | SHEET 2    |

### 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

### DEPARTMENT OF DEFENSE SPECIFICATION

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

### DEPARTMENT OF DEFENSE STANDARDS

MIL-STD-883 - Test Method Standard Microcircuits.

MIL-STD-1835 - Interface Standard Electronic Component Case Outlines.

### DEPARTMENT OF DEFENSE HANDBOOKS

MIL-HDBK-103 - List of Standard Microcircuit Drawings.

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Copies of these documents are available online at http://assist.daps.dla.mil/quicksearch/ or http://assist.daps.dla.mil or from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

### 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein. Product built to this drawing that is produced by a Qualified Manufacturer Listing (QML) certified and qualified manufacturer or a manufacturer who has been granted transitional certification to MIL-PRF-38535 may be processed as QML product in accordance with the manufacturers approved program plan and qualifying activity approval in accordance with MIL-PRF-38535. This QML flow as documented in the Quality Management (QM) plan may make modifications to the requirements herein. These modifications shall not affect form, fit, or function of the device. These modifications shall not affect the PIN as described herein. A "Q" or "QML" certification mark in accordance with MIL-PRF-38535 is required to identify when the QML flow option is used.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535, appendix A and herein.

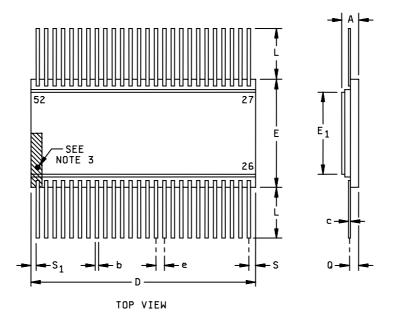

- 3.2.1 <u>Case outlines</u>. The case outlines shall be in accordance with 1.2.2 herein and figure 1.

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 2.

- 3.2.3 Functional block diagram. The functional block diagram shall be as specified on figure 3.

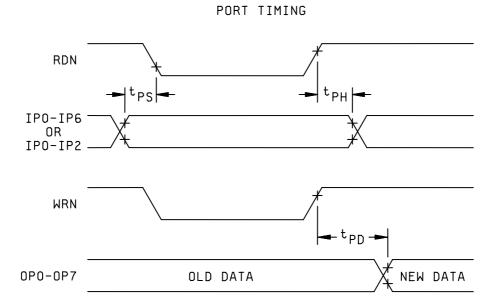

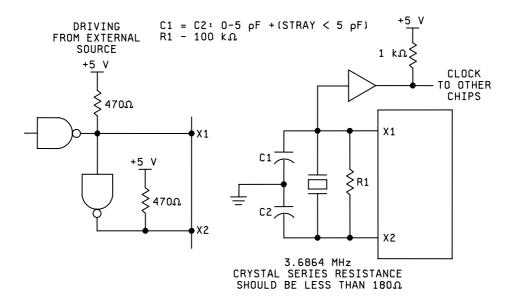

- 3.2.4 <u>Timing waveforms and test circuits</u>. The timing waveforms and test circuits shall be as specified on figure 3.

- 3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

- 3.5 <u>Marking</u>. Marking shall be in accordance with MIL-PRF-38535, appendix A. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-89532 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>C | SHEET 3    |

- 3.5.1 <u>Certification/compliance mark</u>. A compliance indicator "C" shall be marked on all non-JAN devices built in compliance to MIL-PRF-38535, appendix A. The compliance indicator "C" shall be replaced with a "Q" or "QML" certification mark in accordance with MIL-PRF-38535 to identify when the QML flow option is used.

- 3.6 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.6 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply shall affirm that the manufacturer's product meets the requirements of MIL-PRF-38535, appendix A and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 Notification of change. Notification of change to DSCC-VA shall be required for any change that affects this drawing.

- 3.9 <u>Verification and review</u>. DSCC, DSCC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

| STANDARD             |

|----------------------|

| MICROCIRCUIT DRAWING |

DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43218-3990

| SIZE<br><b>A</b> |                | 5962-89532 |

|------------------|----------------|------------|

|                  | REVISION LEVEL | SHEET      |

|                                                     | Т                    | ABLE I. Electrical performance                                                                                                                                                                                 | characteristics   | <u>3</u> .     |      |      |      |

|-----------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|------|------|------|

| Test                                                | Symbol               | $ \begin{array}{c c} Conditions & \underline{1}/\underline{2}/\\ -55^{\circ}C \leq T_{C} \leq +125^{\circ}C\\ 4.5 \text{ V dc} \leq V_{CC} \leq 5.5 \text{ V dc}\\ unless otherwise specified \\ \end{array} $ | Group A subgroups | Device<br>type | Lir  | nits | Unit |

|                                                     |                      |                                                                                                                                                                                                                |                   |                | Min  | Max  |      |

| Input low voltage                                   | V <sub>IL</sub>      |                                                                                                                                                                                                                | 1, 2, 3           | All            |      | 0.8  | V    |

| Input high voltage<br>(except X1/CLK)               | V <sub>IH</sub>      |                                                                                                                                                                                                                |                   |                | 2.0  |      | V    |

| Input high voltage<br>(X1/CLK)                      | V <sub>IH</sub>      |                                                                                                                                                                                                                |                   |                | 4.0  |      | V    |

| Output low voltage                                  | V <sub>OL</sub>      | $I_{OL} = 2.4 \text{ mA}, V_{CC} = 4.5 \text{ V}$                                                                                                                                                              |                   |                |      | 0.4  | V    |

| Output high voltage (except open collector outputs) | V <sub>OH</sub>      | $I_{OH} = -400 \ \mu A, \ V_{CC} = 4.5 \ V$                                                                                                                                                                    |                   |                | 2.4  |      | V    |

| Input leakage current                               | I <sub>IL</sub>      | V <sub>I</sub> = 0 V to V <sub>CC</sub>                                                                                                                                                                        |                   |                | -25  | 10   | μΑ   |

| Data bus three-state leakage current                | I <sub>OZL</sub> ,   | $V_{O} = 0.4 \text{ V to } V_{CC}$                                                                                                                                                                             |                   |                | -10  | 10   | μΑ   |

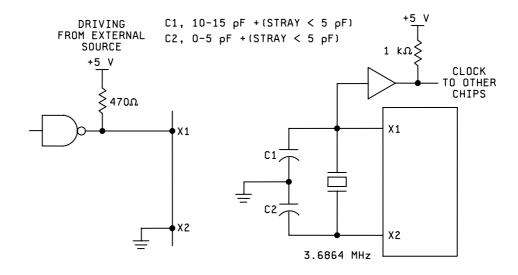

| X1/CLK low input current                            | I <sub>IL</sub> (X1) | V <sub>I</sub> = 0 V, X2 grounded                                                                                                                                                                              |                   |                | -6.0 | 0.0  | mA   |

| X1/CLK high input current                           | I <sub>IH</sub> (X1) | V <sub>I</sub> = V <sub>CC</sub> , X2 grounded                                                                                                                                                                 |                   |                | -1.0 | 1.0  | mA   |

| X2 low input current 3/                             | I <sub>IL</sub> (X2) | V <sub>I</sub> = 0 V, X1/CLK floated                                                                                                                                                                           |                   |                | -100 | 0.0  | μΑ   |

| X2 high input current 3/                            | I <sub>IH</sub> (X2) | $V_I = V_{CC}$ , X1/CLK floated                                                                                                                                                                                |                   |                | 0.0  | 100  | μΑ   |

| Open collector output leakage current               | I <sub>OH</sub>      | $V_{O} = 0.4 \text{ V to } V_{CC}$                                                                                                                                                                             |                   |                | -10  | 10   | μΑ   |

| Power supply current                                | I <sub>CC</sub>      | V <sub>CC</sub> = 5.5 V                                                                                                                                                                                        |                   |                |      | 15   | mA   |

| Input capacitance                                   | C <sub>IN</sub>      | V <sub>IN</sub> = 0 V, F <sub>C</sub> = 1 MHz                                                                                                                                                                  | 4                 |                |      | 20   | pF   |

See footnotes at end of table.

Functional tests

| STANDARD MICROCIRCUIT DRAWING                               | SIZE<br><b>A</b> |                     | 5962-89532 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>C | SHEET 5    |

7, 8

See 4.3.1c

See 4.3.1d

|                                            | TABLE I          | . Electrical performance charac                                                                                                                                                                                | eteristics - Co   | ntinued.       |        |     |      |

|--------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|--------|-----|------|

| Test                                       | Symbol           | $ \begin{array}{c c} Conditions & \underline{1}/\underline{2}/\\ -55^{\circ}C \leq T_{C} \leq +125^{\circ}C\\ 4.5 \text{ V dc} \leq V_{CC} \leq 5.5 \text{ V dc}\\ unless otherwise specified \\ \end{array} $ | Group A subgroups | Device<br>type | Limits |     | Unit |

|                                            |                  |                                                                                                                                                                                                                |                   |                | Min    | Max |      |

| Reset pulse width                          | t <sub>RES</sub> | See figure 4. 4/                                                                                                                                                                                               | 9, 10, 11         | 01, 02         | 1.0    |     | ns   |

| A0–A3 setup time to RDN,<br>WRN low        | t <sub>AS</sub>  |                                                                                                                                                                                                                |                   |                | 10     |     | ns   |

| A0–A3 hold time from<br>RDN, WRN low       | t <sub>AH</sub>  |                                                                                                                                                                                                                |                   |                | 100    |     | ns   |

| CEN setup time to RDN,<br>WND low          | t <sub>CS</sub>  |                                                                                                                                                                                                                |                   |                | 0      |     | ns   |

| CEN hold time from RDN,<br>WRN high        | t <sub>CH</sub>  |                                                                                                                                                                                                                |                   |                | 0      |     | ns   |

| WRN, RDN pulse width                       | t <sub>RW</sub>  |                                                                                                                                                                                                                |                   |                | 225    |     | ns   |

| Data valid after RDN low                   | t <sub>DD</sub>  |                                                                                                                                                                                                                |                   |                |        | 175 | ns   |

| Data bus floating after<br>RDN high        | t <sub>DF</sub>  |                                                                                                                                                                                                                |                   |                |        | 110 | ns   |

| Data setup time before WRN high            | t <sub>DS</sub>  |                                                                                                                                                                                                                |                   |                | 100    |     | ns   |

| Data hold time after WRN high              | t <sub>DH</sub>  |                                                                                                                                                                                                                |                   |                | 20     |     | ns   |

| High time between READS and/or WRITES 5/6/ | t <sub>RWD</sub> |                                                                                                                                                                                                                |                   |                | 200    |     | ns   |

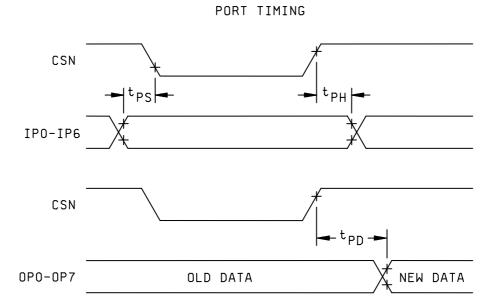

| Port input setup time before RDN low       | t <sub>PS</sub>  |                                                                                                                                                                                                                |                   |                | 0      |     | ns   |

| Port input hold time after RDN high        | t <sub>PH</sub>  |                                                                                                                                                                                                                |                   |                | 0      |     | ns   |

| Port output valid after<br>WRN high        | t <sub>PD</sub>  |                                                                                                                                                                                                                |                   |                |        | 400 | ns   |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-89532 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>C | SHEET 6    |

|                                                             | TABI F I         | . Electrical performan                                                                                                                       | ce characte                      | eristics - C      | ontinued         |        |       |         |

|-------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------|------------------|--------|-------|---------|

| Test                                                        | Symbol           | Conditions $\underline{1}$<br>-55°C $\leq$ T <sub>C</sub> $\leq$ +1<br>4.5 V dc $\leq$ V <sub>CC</sub> $\leq$ 5<br>unless otherwise specific | / <u>2</u> /<br>25°C<br>5.5 V dc | Group A subgroups | Device           | Limits |       | Unit    |

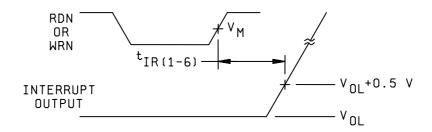

| INTRN (or OP3-OP7 when us                                   | ed as            | See figure 4. <u>4</u> /                                                                                                                     |                                  |                   |                  | Min    | Max   |         |

| interrupts) negated from:                                   | ou uo            | Coo ngulo 1. <u>.</u> ,                                                                                                                      |                                  |                   |                  |        |       |         |

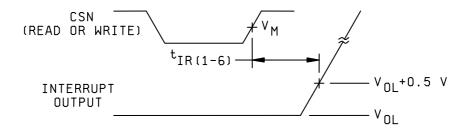

| Read RHR (RxRDY/FFULL interrupt)                            | t <sub>IR1</sub> |                                                                                                                                              |                                  | 9, 10, 11         | 01, 02           |        | 325   | ns      |

| Write THR (TxRDY interrupt                                  | t <sub>IR2</sub> |                                                                                                                                              |                                  |                   |                  |        | 325   | ns      |

| Reset command (delta break interrupt)                       | t <sub>IR3</sub> |                                                                                                                                              |                                  |                   |                  |        | 325   | ns      |

| Stop C/T command (counter interrupt)                        | t <sub>IR4</sub> |                                                                                                                                              |                                  |                   |                  |        | 325   | ns      |

| Read IPCR (input port change interrupt)                     | t <sub>IR5</sub> |                                                                                                                                              |                                  |                   |                  |        | 325   | ns      |

| Write IMR (clear of interrupt mask bit)                     | t <sub>IR6</sub> |                                                                                                                                              |                                  |                   |                  |        | 325   | ns      |

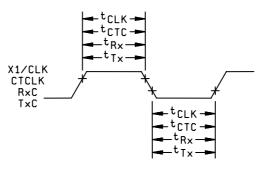

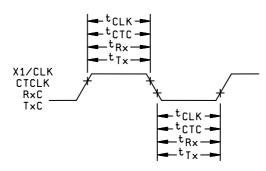

| X1/CLK high or low time                                     | t <sub>CLK</sub> |                                                                                                                                              |                                  |                   |                  | 100    |       | ns      |

| X1/CLK frequency                                            | f <sub>CLK</sub> |                                                                                                                                              |                                  |                   |                  | 2.0    | 4.0   | MHz     |

| CTCLK (IP2) high or low time                                | t <sub>CTC</sub> |                                                                                                                                              |                                  |                   |                  | 100    |       | ns      |

| CTCLK (IP2) frequency 7/                                    | f <sub>CTC</sub> |                                                                                                                                              |                                  |                   |                  | 0      | 4.0   | MHz     |

| RxC high or low time                                        | t <sub>RX</sub>  |                                                                                                                                              |                                  |                   |                  | 220    |       | ns      |

| RxC frequency (16X) 7/                                      | f <sub>RX</sub>  |                                                                                                                                              |                                  |                   |                  | 0      | 2.0   | MHz     |

| RxC frequency (1X) 7/                                       | f <sub>RX</sub>  |                                                                                                                                              |                                  |                   |                  | 0      | 1.0   | MHz     |

| TxC high or low time                                        | t <sub>TX</sub>  |                                                                                                                                              |                                  |                   |                  | 220    |       | ns      |

| TxC frequency (16X) 7/                                      | f <sub>TX</sub>  |                                                                                                                                              |                                  |                   |                  | 0      | 2.0   | MHz     |

| TxC frequency (1X) 7/                                       | f <sub>TX</sub>  |                                                                                                                                              |                                  |                   |                  | 0      | 1.0   | MHz     |

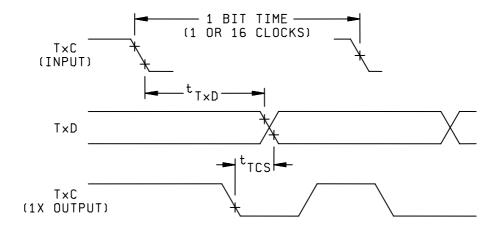

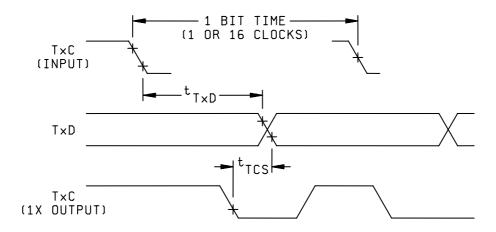

| TxD output delay from TxC low                               | t <sub>TXD</sub> |                                                                                                                                              |                                  |                   |                  |        | 350   | ns      |

| See footnotes at end of table.                              |                  |                                                                                                                                              |                                  |                   |                  |        |       |         |

| MICROCIRC                                                   |                  |                                                                                                                                              | SIZE<br><b>A</b>                 |                   |                  |        | 5962  | 2-89532 |

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |                  |                                                                                                                                              |                                  | RE'               | VISION LEVE<br>C | L      | SHEET | 7       |

| Test                                            | Symbol           | $ \begin{array}{c} Conditions & \underline{1}/\ \underline{2}/\\ -55^{\circ}C \leq T_{C} \leq +125^{\circ}C\\ 4.5\ V\ dc \leq V_{CC} \leq 5.5\ V\ dc\\ unless \ otherwise\ specified \end{array} $ | Group A subgroups | Device<br>type | Limits | nits | Unit    |

|-------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|--------|------|---------|

|                                                 |                  |                                                                                                                                                                                                    |                   |                | Min    | Max  |         |

| Output delay from TxC low to TxD data output    | t <sub>TCS</sub> | See figure 4. 4/                                                                                                                                                                                   | 9, 10, 11         | 01, 02         | 0      | 150  | ns      |

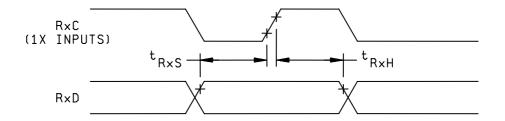

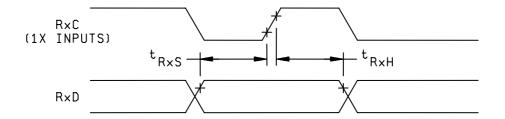

| RxD data setup time to<br>RxC high              | t <sub>RXS</sub> |                                                                                                                                                                                                    |                   |                | 240    |      | ns      |

| RxD data hold time from RxC high                | t <sub>RXH</sub> |                                                                                                                                                                                                    |                   |                | 200    |      | ns      |

| RESETN pulse width                              | t <sub>RES</sub> |                                                                                                                                                                                                    |                   | 03             | 1.0    |      | μS      |

| A1-A4 setup to CSN low                          | t <sub>AS</sub>  |                                                                                                                                                                                                    |                   |                | 10     |      | ns      |

| A1-A4 hold time from CSN high                   | t <sub>AH</sub>  |                                                                                                                                                                                                    |                   |                | 0      |      | ns      |

| R/WN setup time to CSN high                     | t <sub>RWS</sub> |                                                                                                                                                                                                    |                   |                | 0      |      | ns      |

| R/WN holdup time to CSN<br>high                 | t <sub>RWH</sub> |                                                                                                                                                                                                    |                   |                | 0      |      | ns      |

| CSN high pulse width <u>8</u> /                 | t <sub>CSW</sub> |                                                                                                                                                                                                    |                   |                | 90     |      | ns      |

| CSN or IACKN high from DTACKN low 9/            | t <sub>CSD</sub> |                                                                                                                                                                                                    |                   |                | 20     |      | ns      |

| Data valid from CSN or<br>IACKN low             | t <sub>DD</sub>  |                                                                                                                                                                                                    |                   |                |        | 175  | ns      |

| Data bus floating from CSN or IACKN high        | t <sub>DF</sub>  |                                                                                                                                                                                                    |                   |                |        | 100  | ns      |

| Data setup time to CLK                          | t <sub>DS</sub>  |                                                                                                                                                                                                    |                   |                | 100    |      | ns      |

| Data hold time from CSN high                    | t <sub>DH</sub>  |                                                                                                                                                                                                    |                   |                | 0      |      | ns      |

| DTACKN low from read data                       | t <sub>DAL</sub> |                                                                                                                                                                                                    |                   |                | 0      |      | ns      |

| DTACKN low (read cycle) from CLK high           | t <sub>DCR</sub> |                                                                                                                                                                                                    |                   |                |        | 125  | ns      |

| DTACKN low (write cycle) from CLK high          | t <sub>DCW</sub> |                                                                                                                                                                                                    |                   |                |        | 125  | ns      |

| DTACKN high from CSN or<br>IACKN high           | t <sub>DAH</sub> |                                                                                                                                                                                                    |                   |                |        | 100  | ns      |

| DTACKN high impedance<br>from CSN or IACKN high | t <sub>DAT</sub> |                                                                                                                                                                                                    |                   |                |        | 125  | ns      |

| See footnotes at end of table.                  |                  |                                                                                                                                                                                                    |                   |                |        |      |         |

| STAN                                            | IDARD            | SIZ<br>A                                                                                                                                                                                           |                   |                |        | 596  | 2-89532 |

|                                                     | TABLE I          | . Electrical performan | ce characte                      | eristics - C      | ontinued.        |     |       |         |

|-----------------------------------------------------|------------------|------------------------|----------------------------------|-------------------|------------------|-----|-------|---------|

| Test                                                | Symbol           |                        | / <u>2</u> /<br>25°C<br>5.5 V dc | Group A subgroups | Device           | Lir | nits  | Unit    |

|                                                     |                  |                        |                                  |                   |                  | Min | Max   |         |

| CSN or IACKN setup time to clock high 10/           | t <sub>CSC</sub> | See figure 4. 4/       |                                  | 9, 10, 11         | 03               | 90  |       | ns      |

| Port input setup to CSN low                         | t <sub>PS</sub>  |                        |                                  |                   |                  | 0   |       | ns      |

| Port input hold time CSN high                       | t <sub>PH</sub>  |                        |                                  |                   |                  | 0   |       | ns      |

| Port output valid from CSN high                     | t <sub>PD</sub>  |                        |                                  |                   |                  |     | 400   | ns      |

| INTRN, or OP3-OP7 when us interrupts, negated from: | sed as           |                        |                                  |                   |                  |     |       |         |

| Read RHR (RxRDY/FFULL interrupts)                   | t <sub>IR1</sub> |                        |                                  | 9, 10, 11         | 03               |     | 325   | ns      |

| Write THR (TxRDY interrupt)                         | t <sub>IR2</sub> |                        |                                  |                   |                  |     | 325   | ns      |

| Reset command (delta break interrupt)               | t <sub>IR3</sub> |                        |                                  |                   |                  |     | 325   | ns      |

| Stop C/T command (counter interrupts)               | t <sub>IR4</sub> |                        |                                  |                   |                  |     | 325   | ns      |

| Read IPCR (input port change interrupt)             | t <sub>IR5</sub> |                        |                                  |                   |                  |     | 325   | ns      |

| Write IMR (clear of interrupt mask bit)             | t <sub>IR6</sub> |                        |                                  |                   |                  |     | 325   | ns      |

| X1/CLK high or low time                             | t <sub>CLK</sub> |                        |                                  |                   |                  | 100 |       | ns      |

| X1/CLK frequency                                    | f <sub>CLK</sub> |                        |                                  |                   |                  | 2.0 | 4.0   | MHz     |

| CTCLK high or low time                              | t <sub>CTC</sub> |                        |                                  |                   |                  | 100 |       | ns      |

| CTCLK frequency                                     | f <sub>CTC</sub> |                        |                                  |                   |                  | 0   | 4.0   | MHz     |

| RxC high or low time                                | t <sub>RX</sub>  |                        |                                  |                   |                  | 220 |       | ns      |

| RxC frequency (16X)                                 | f <sub>RX</sub>  |                        |                                  |                   |                  | 0   | 2.0   | MHz     |

| RxC frequency (1X)                                  | f <sub>RX</sub>  |                        |                                  |                   |                  | 0   | 1.0   | MHz     |

| See footnotes at end of table.                      |                  |                        |                                  |                   |                  |     |       |         |

| MICROCIRC                                           |                  |                        | SIZE<br><b>A</b>                 | :                 |                  |     | 596   | 2-89532 |

| DEFENSE SUPPLY<br>COLUMBUS, C                       |                  |                        |                                  | RE <sup>1</sup>   | /ISION LEVE<br>C | L   | SHEET | 9       |

| TABLE I. | Electrical | performance | characteristics | - | Continued. |

|----------|------------|-------------|-----------------|---|------------|

|----------|------------|-------------|-----------------|---|------------|

| Test                                         | Symbol           | $ \begin{array}{c} \text{Conditions}  \underline{1}/\ \underline{2}/\\ -55^{\circ}\text{C} \leq \text{T}_{\text{C}} \leq +125^{\circ}\text{C}\\ \text{4.5 V dc} \leq \text{V}_{\text{CC}} \leq 5.5 \text{ V dc}\\ \text{unless otherwise specified} \end{array} $ | Group A subgroups | Device<br>type | Lin | nits | Unit |

|----------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|-----|------|------|

|                                              |                  |                                                                                                                                                                                                                                                                   |                   |                | Min | Max  |      |

| TxC high or low time                         | t <sub>TX</sub>  | See figure 4. 4/                                                                                                                                                                                                                                                  | 9, 10, 11         | 03             | 220 |      | ns   |

| TxC frequency (16X)                          | f <sub>TX</sub>  |                                                                                                                                                                                                                                                                   |                   |                | 0   | 2.0  | MHz  |

| TxC frequency (1X)                           | f <sub>TX</sub>  |                                                                                                                                                                                                                                                                   |                   |                | 0   | 1.0  | MHz  |

| TxD output delay from TxC low                | t <sub>TXD</sub> |                                                                                                                                                                                                                                                                   |                   |                |     | 350  | ns   |

| Output delay from TxC low to TxD data output | t <sub>TCS</sub> |                                                                                                                                                                                                                                                                   |                   |                | 0   | 150  | ns   |

| RxD data setup time to RxC high              | t <sub>RXS</sub> |                                                                                                                                                                                                                                                                   |                   |                | 240 |      | ns   |

| RxD data hold time from RxC high             | t <sub>RXH</sub> |                                                                                                                                                                                                                                                                   |                   |                | 200 |      | ns   |

- All voltage measurements are referenced to ground (GND). For testing, all inputs except X1/CLK swing between 0.4 V and 2.4 V with a transition time of < 20 ns. For X1/CLK this swing is between 0.4 V and 4.4 V. All time measurements referenced at input voltages of 0.8 V and 2.0 V as appropriate.</p>

- $\underline{2}/$  Test condition for outputs:  $C_L$  = 150 pF tied to ground, except interrupt outputs. Test condition for interrupt outputs:  $C_L$  = 50 pF tied to ground,  $R_L$  = 2.7 k $\Omega$  to  $V_{CC}$ .

- 3/ For CMOS technology:  $I_{IL(X2)}$  X1/CLK =  $V_{CC}$ ,  $I_{IH(X2)}$  X1/CLK = 0.0 V.

- 4/ Timing is illustrated and referenced to the WRN and RDN inputs. The device may also be operated with CEN as the "strobing" input. In this case, all timing specifications apply referenced to the falling and rising edges of CEN. CEN and RDN (also CEN and WRN) are AND'ed internally. As a consequence, the signal asserted last initiates the cycle and the signal negated first terminates the cycle.

- 5/ If CEN is used as the "strobing" input, the parameter defines the minimum high times between one CEN and the next. The RDN signal must be negated for t<sub>RWD</sub> to guarantee that any status register changes are valid.

- 6/ Consecutive write operations to the same command register require at least three edges of the X1 clock between writes.

- 7/ Minimum frequencies may not be tested, but are guaranteed by design.

- This specification will impose maximum 68000 CPU CLK to 6 MHz. Higher CPU CLK can be used if repeating bus reads are not performed. Consecutive write operations to the same command register require at least three edges of the X1 clock between writes.

- 9/ This specification imposed a lower bound on CSN and IACKN low, guaranteeing that it will be low for at least 1 CLK period. This requirement is made on CSN only to insure assertion of DTACKN and not to guarantee operation of the part.

- 10/ This specification is made only to insure that DTACKN is asserted with respect to the rising edge of the X1/CLK pin as shown in the timing diagram, not to guarantee operation of the part. If the setup time is violated, DTACKN may be asserted as shown, or may be asserted one clock cycle later.

| STANDARD MICROCIRCUIT DRAWING                               | SIZE<br><b>A</b> |                     | 5962-89532 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>C | SHEET 10   |

### Case Y

|                | Inch   | nes      | Millimeters |       |       |

|----------------|--------|----------|-------------|-------|-------|

| Symbol         | Min    | Max      | Min         | Max   | Notes |

| Α              | .045   | .100     | 1.14        | 2.54  |       |

| b              | .015   | .026     | 0.38        | 0.66  | 7     |

| С              | .008   | .015     | 0.20        | 0.38  | 7     |

| D              |        | 1.330    |             | 33.78 | 4     |

| Е              | .620   | .660     | 15.75       | 16.76 |       |

| E <sub>1</sub> | .488   | .498     | 12.40       | 12.65 |       |

| е              | .050 I | .050 BSC |             | BSC   | 5     |

| L              | .250   | .370     | 6.35        | 9.40  |       |

| Q              | .054   | .066     | 1.37        | 1.68  | 6     |

| S              |        | .045     |             | 1.14  |       |

| S <sub>1</sub> | .005   |          | 0.13        |       |       |

### NOTES:

- 1. Dimensions are in inches.

- 2. Metric equivalents are for general information only.

- 3. A lead tap (enlargement) or index dot is located within the shaded area shown at pin 1. Other pin numbers proceed sequentially from pin 1 counterclockwise (as viewed from the top of the device).

- 4. This dimension allows for off-center lid, meniscus, and glass overrun.

- 5. The reference pin spacing is .050 (1.27 mm) between centerlines. Each pin centerline is located within  $\pm$ .005 (0.13 mm) of its longitudinal position relative to the first and last pin numbers.

- 6. This dimension is measured at the point of exit of the lead body.

- 7. Lead dimensions include .003 inch allowance for hot solder dip lead finish.

FIGURE 1. Case outlines.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-89532 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>C | SHEET 11   |

| Device          | type:           | 01                 |                 |  |  |

|-----------------|-----------------|--------------------|-----------------|--|--|

| Case o          | utline:         | Χ                  |                 |  |  |

| Terminal number | Terminal symbol | Terminal<br>number | Terminal symbol |  |  |

| 1               | A0              | 15                 | INTRN           |  |  |

| 2               | A1              | 16                 | D6              |  |  |

| 3               | A2              | 17                 | D4              |  |  |

| 4               | A3              | 18                 | D2              |  |  |

| 5               | WRN             | 19                 | D0              |  |  |

| 6               | RDN             | 20                 | OP0             |  |  |

| 7               | RxDB            | 21                 | TxDA            |  |  |

| 8               | TxDB            | 22                 | RxDA            |  |  |

| 9               | OP1             | 23                 | X1/CLK          |  |  |

| 10              | D1              | 24                 | X2              |  |  |

| 11              | D3              | 25                 | RESET           |  |  |

| 12              | D5              | 26                 | CEN             |  |  |

| 13              | D7              | 27                 | IP2             |  |  |

| 14              | GND             | 28                 | V <sub>CC</sub> |  |  |

| Device          | tvpe:           | 02              |                 |  |  |

|-----------------|-----------------|-----------------|-----------------|--|--|

| Case            |                 | Q               |                 |  |  |

| Terminal number | Terminal symbol | Terminal number | Terminal symbol |  |  |

| 1               | A0              | 21              | INTRN           |  |  |

| 2               | IP3             | 22              | D6              |  |  |

| 3               | A1              | 23              | D4              |  |  |

| 4               | IP1             | 24              | D2              |  |  |

| 5               | A2              | 25              | D0              |  |  |

| 6               | A3              | 26              | OP6             |  |  |

| 7               | IP0             | 27              | OP4             |  |  |

| 8               | WRN             | 28              | OP2             |  |  |

| 9               | RDN             | 29              | OP0             |  |  |

| 10              | RxDB            | 30              | TxDA            |  |  |

| 11              | TxDB            | 31              | RxDA            |  |  |

| 12              | OP1             | 32              | X1/CLK          |  |  |

| 13              | OP3             | 33              | X2              |  |  |

| 14              | OP5             | 34              | RESET           |  |  |

| 15              | OP7             | 35              | CEN             |  |  |

| 16              | D1              | 36              | IP2             |  |  |

| 17              | D3              | 37              | IP6             |  |  |

| 18              | D5              | 38              | IP5             |  |  |

| 19              | D7              | 39              | IP4             |  |  |

| 20              | GND             | 40              | V <sub>CC</sub> |  |  |

FIGURE 2. <u>Terminal connections</u>.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-89532      |

|-------------------------------------------------------------|------------------|---------------------|-----------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>C | SHEET <b>12</b> |

| Device          | e type:         | 02              |                 |                 |                 |                 |                 |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Case o          | outline:        | U               |                 |                 |                 |                 |                 |

| Terminal number | Terminal symbol |

| 1               | NC              | 12              | NC              | 23              | NC              | 34              | NC              |

| 2               | A0              | 13              | TxDB            | 24              | INTRN           | 35              | RxDA            |

| 3               | IP3             | 14              | OP1             | 25              | D6              | 36              | X1/CLK          |

| 4               | A1              | 15              | OP3             | 26              | D4              | 37              | X2              |

| 5               | IP1             | 16              | OP5             | 27              | D2              | 38              | RESET           |

| 6               | A2              | 17              | OP7             | 28              | D0              | 39              | CEN             |

| 7               | A3              | 18              | D1              | 29              | OP6             | 40              | IP2             |

| 8               | IP0             | 19              | D3              | 30              | OP4             | 41              | IP6             |

| 9               | WRN             | 20              | D5              | 31              | OP2             | 42              | IP5             |

| 10              | RDN             | 21              | D7              | 32              | OP0             | 43              | IP4             |

| 11              | RxDB            | 22              | GND             | 33              | TxDA            | 44              | $V_{CC}$        |

NC = No connection.

| Device          | type:           | 02              |                 |                    |                 |                 |                 |

|-----------------|-----------------|-----------------|-----------------|--------------------|-----------------|-----------------|-----------------|

| Case c          | utline:         |                 |                 |                    | Υ               |                 |                 |

| Terminal number | Terminal symbol | Terminal number | Terminal symbol | Terminal<br>number | Terminal symbol | Terminal number | Terminal symbol |

| 1               | A0              | 14              | TxDB            | 27                 | INTRN           | 40              | RxDA            |

| 2               | IP3             | 15              | OP1             | 28                 | D6              | 41              | X1/CLK          |

| 3               | A1              | 16              | OP3             | 29                 | D4              | 42              | X2              |

| 4               | IP1             | 17              | OP5             | 30                 | D2              | 43              | RESET           |

| 5               | A2              | 18              | OP7             | 31                 | D0              | 44              | CEN             |

| 6               | A3              | 19              | NC              | 32                 | NC              | 45              | NC              |

| 7               | NC              | 20              | NC              | 33                 | NC              | 46              | NC              |

| 8               | NC              | 21              | NC              | 34                 | NC              | 47              | NC              |

| 9               | NC              | 22              | D1              | 35                 | OP6             | 48              | IP2             |

| 10              | IP0             | 23              | D3              | 36                 | OP4             | 49              | IP6             |

| 11              | WRN             | 24              | D5              | 37                 | OP2             | 50              | IP5             |

| 12              | RDN             | 25              | D7              | 38                 | OP0             | 51              | IP4             |

| 13              | RxDB            | 26              | GND             | 39                 | TxDA            | 52              | V <sub>CC</sub> |

NC = No connection.