# RENESAS

## RAA211450

4.5V to 42V, 5A, DC/DC Synchronous Step-Down Regulator w/ Internal Compensation and Adjustable Frequency

The RAA211450 is a DC/DC synchronous step-down (Buck) regulator that supports a 4.5V to 42V input voltage range and adjustable output voltage. It can deliver up to continuous 5A of continuous output current with premium load and line regulation performance.

The RAA211450 uses peak-current mode control architecture. Its PWM switching frequency is programmable to provide the best trade-off between transient response and efficiency. It also supports PFM operation and DEM to maximize light load efficiency, in addition to an external bias LDO input to further reduce power dissipation across the load range. The regulator also has an internal loop compensation circuit to reduce the external component count and BOM cost.

The RAA211450 provides useful functions such as internal or programmable soft-start and power good indicator. For safe operation, the RAA211450 also offers protection features such as cycle-by-cycle peak and valley current limit, input voltage UVLO, output voltage undervoltage (short-circuit) protection, and thermal shutdown.

#### Applications

- Industrial power systems

- Distributed power supplies and general-purpose point-of-load

- Telecommunication base station power supplies

- High-voltage single-board systems

#### Features

- Wide input voltage range: 4.5V to 42V

- Adjustable output voltage: 0.8V to 90% of VIN (limited by minimum off time)

- Up to 5A of continuous output current

- Default 400kHz switching frequency and programmable switching frequency range from 200kHz to 800kHz

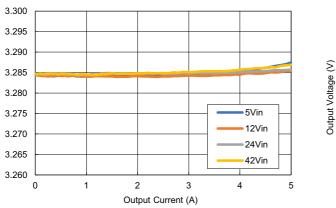

- ±1% Load regulation accuracy from -40°C to 125°C, ±0.5% Load regulation accuracy at 25°C

- 95µA typical quiescent current

- Internal compensation

- Internal 0.5ms soft-start in QFN

- External programmable soft-start (HTSSOP)

- PFM operation and DEM at light load

- Integrated external bias LDO

- Power-good indicator

- Integrated MOSFET r<sub>DS(ON)</sub> (typical): 70mΩ/25mΩ (QFN); 115mΩ/40mΩ (TSSOP)

- Cycle-by-cycle peak and valley current limit

- Input voltage UVLO and output voltage undervoltage (short-circuit) protection

- Thermal Shutdown

- Available in 20 Ld QFN 4mm × 3.5mm and 16 Ld HTSSOP packages

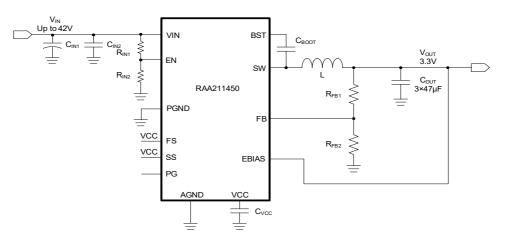

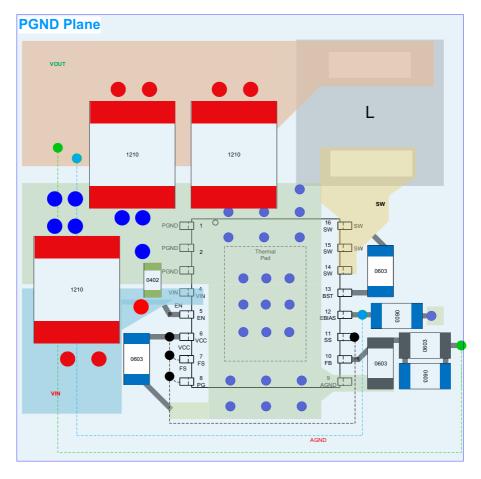

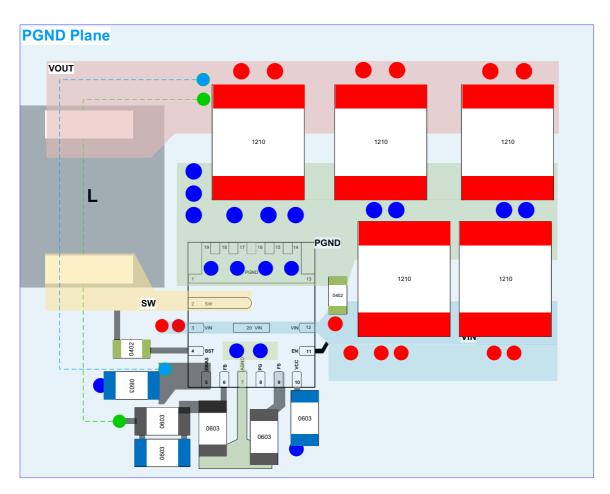

**Figure 1. Typical Application Circuit**

## Contents

| 1.  | Over         | view                                                   | 3 |

|-----|--------------|--------------------------------------------------------|---|

|     | 1.1          | Block Diagram                                          | 3 |

| 2.  | Pin Ir       | nformation                                             | 3 |

|     | 2.1          | Pin Assignments                                        | 3 |

|     | 2.2          | Pin Descriptions                                       | 4 |

|     | 2.3          | Recommended Components Values for Typical Applications | 5 |

| 3.  | Spec         | ifications                                             | 6 |

|     | 3.1          | Absolute Maximum Ratings                               | 6 |

|     | 3.2          | ESD Ratings                                            | 6 |

|     | 3.3          | Thermal Information                                    |   |

|     | 3.4          | Recommended Operating Conditions                       |   |

|     | 3.5          | Electrical Specifications                              | 7 |

| 4.  | Туріс        | al Performance Curves                                  | 9 |

| 5.  | Func         | tional Description                                     | 3 |

|     | 5.1          | Fixed Frequency Operation Mode                         | 3 |

|     | 5.2          | Discontinuous Operation Mode 1                         | 3 |

|     | 5.3          | Soft-Start Timing 1                                    | 4 |

|     | 5.4          | Start-Up Process                                       |   |

|     | 5.5          | BOOT Refresh and Capacitor Selection 1                 |   |

|     | 5.6          | Power-Good                                             |   |

|     | 5.7          | Switching Frequency Resistor Selection                 |   |

|     | 5.8          | Input Undervoltage Lockout                             |   |

|     | 5.9          | VCC and EBIAS                                          |   |

|     | 5.10         | Overcurrent Protection (OCP)                           |   |

|     | 5.11<br>5.12 | Undervoltage and Overvoltage Protection                |   |

| _   | -            |                                                        |   |

| 6.  | ••           | cations Information                                    |   |

|     | 6.1          | Output Voltage Feedback Resistor Divider               |   |

|     | 6.2          | Inductor Selection                                     |   |

|     | 6.3          | Input Capacitor Selection                              |   |

|     | 6.4          | Output Capacitor Selection                             |   |

| 7.  | Layo         | ut Suggestions                                         |   |

|     | 7.1          | Layout Examples                                        | 9 |

| 8.  | Pack         | age Outline Drawings                                   | 1 |

| 9.  | Orde         | ring Information                                       | 3 |

| 10. | Revis        | sion History                                           | 3 |

### 1. Overview

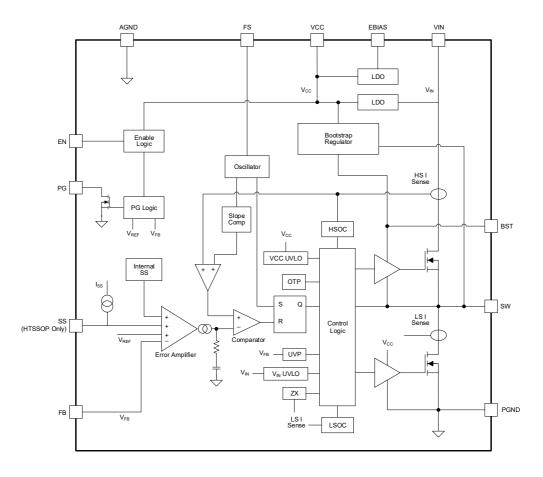

#### 1.1 Block Diagram

Figure 2. Functional Block Diagram

## 2. Pin Information

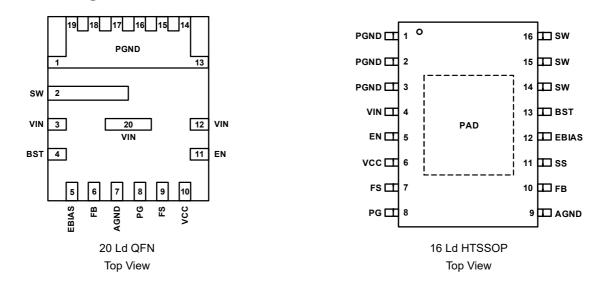

#### 2.1 Pin Assignments

## 2.2 Pin Descriptions

| Pin                              | #          | Dia Marra | Description                                                                                                                                                                                                                                                   |  |  |  |

|----------------------------------|------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| QFN                              | HTSSOP     | Pin Name  | Description                                                                                                                                                                                                                                                   |  |  |  |

| 1, 13, 14, 15,<br>16, 17, 18, 19 | 1, 2, 3    | PGND      | These pins are connected to the source of the integrated low-side FET and are used as the power ground. Place input bypass capacitors as close as possible to the PGND pins and VIN pin(s).                                                                   |  |  |  |

| 2                                | 14, 15, 16 | SW        | These pins are the phase node of the regulator. They are connected to the source of the high-side FET and the drain of the low-side FET. Connect these pins to the inductor and the boot capacitor.                                                           |  |  |  |

| 3, 12, 20                        | 4          | VIN       | This pin is connected to the drain of the integrated high-side FET. This pin is also connected to the input of internal linear regulator that provides bias for the IC. Connect this pin to the input rail and decouple to PGND with input bypass capacitors. |  |  |  |

| 4                                | 13         | BST       | This pin is the bootstrap circuit supply pin. Connect this pin to SW with a capacitor to provide bias voltage for the integrated high-side FET gate driver.                                                                                                   |  |  |  |

| 5                                | 12         | EBIAS     | This pin is connected to the auxiliary internal linear regulator. This pin can be connected to the output of the regulator to provide bias for the IC.                                                                                                        |  |  |  |

| N/A                              | 11         | SS        | This pin configures the soft-start time. Connect a capacitor from this pin to ground to program the soft-start time. Tie this pin to VCC for default 0.5ms soft-start time.                                                                                   |  |  |  |

| 6                                | 10         | FB        | This pin is connected to the inverting input of the feedback error amplifier and should<br>be connected to a properly selected resistor divider from VOUT to ground to set the<br>output voltage.                                                             |  |  |  |

| 7                                | 9          | AGND      | This pin is connected to the analog ground of the IC. Connect this pin to the PCB ground plane.                                                                                                                                                               |  |  |  |

| 8                                | 8          | PG        | This pin is an open-drain power-good output. It can be pulled up with a resistor to VCC or another rail. The recommended pull-up voltage is 3.3V or lower.                                                                                                    |  |  |  |

| 9                                | 7          | FS        | This pin sets the switching frequency. Connect a resistor from this pin to ground to set the switching frequency from 200kHz to 800kHz. Connect this pin to VCC for default 400kHz switching frequency.                                                       |  |  |  |

| 10                               | 6          | VCC       | This pin is connected to the output of internal linear regulators and provides bias for the IC including the gate driver. Connect this pin to ground with a ceramic decoupling capacitor.                                                                     |  |  |  |

| 11                               | 5          | EN        | This pin is the enable pin. It is high voltage tolerant and can be directly connected to VIN. When using EN to turn the device on or off, connect this pin to GND with a $1M\Omega$ resistor.                                                                 |  |  |  |

| N/A                              | -          | PAD       | This is the bottom thermal pad. It should be connected to AGND and to the PCB ground plane with thermal vias.                                                                                                                                                 |  |  |  |

## 2.3 Recommended Components Values for Typical Applications

| f <sub>SW</sub> (kHz) | V <sub>OUT</sub> (V) | R <sub>FB1</sub> (kΩ) | R <sub>FB2</sub> (kΩ) | L (µH) | C <sub>OUT</sub>                                 |

|-----------------------|----------------------|-----------------------|-----------------------|--------|--------------------------------------------------|

|                       | 0.8                  | 0                     | 20                    | 1.0    | 5 × 100µF/1210/6.3V/X7S                          |

|                       | 1.8                  | 24.9                  | 20                    | 2.2    | 2 × 100µF/1210/6.3V/X7S + 1 × 47µF/1210/6.3V/X7R |

| 400                   | 3.3                  | 61.9                  | 20                    | 3.3    | 3 × 47µF/1210/10V/X7R                            |

| 400                   | 5                    | 105                   | 20                    | 4.7    | 2 × 47µF/1210/16V/X7R                            |

|                       | 12                   | 280                   | 20                    | 10     | 2 × 22µF/1210/50V/X7R                            |

|                       | 24                   | 576                   | 20                    | 22     | 2 × 10µF/1210/50V/X7R                            |

|                       | 0.8                  | 0                     | 20                    | 0.56   | 3 × 100µF/1210/6.3V/X7S                          |

|                       | 1.8                  | 24.9                  | 20                    | 1.0    | 1 × 100µF/1210/6.3V/X7S + 1 × 47µF/1210/6.6V/X7R |

| 600                   | 3.3                  | 61.9                  | 20                    | 2.2    | 2 × 47µF/1210/10V/X7R                            |

| 000                   | 5                    | 105                   | 20                    | 3.3    | 1 × 47μF/1210/16V/X7R + 1 × 10μF/1210/16V/X7R    |

|                       | 12                   | 280                   | 20                    | 6.8    | 1 × 22µF/1210/50V/X7R                            |

|                       | 24                   | 576                   | 20                    | 10     | 1 × 10µF/1210/50V/X7R                            |

|                       | 0.8                  | 0                     | 20                    | 0.47   | 2 × 100µF/1210/6.3V/X7S + 1 × 47µF/1210/6.3V/X7R |

|                       | 1.8                  | 24.9                  | 20                    | 1.0    | 1 × 100µF/1210/6.3V/X7S + 1 × 22µF/1210/6.3V/X7R |

| 800                   | 3.3                  | 61.9                  | 20                    | 1.5    | 1 × 47µF/1210/10V/X7R + 1 × 22µF/1210/10V/X7R    |

| 000                   | 5                    | 105                   | 20                    | 2.2    | 1 × 47µF/1210/16V/X7R                            |

|                       | 12                   | 280                   | 20                    | 4.7    | 1 × 22µF/1210/50V/X7R                            |

|                       | 24                   | 576                   | 20                    | 6.8    | 1 × 10µF/1210/50V/X7R                            |

# 3. Specifications

#### 3.1 Absolute Maximum Ratings

*CAUTION:* Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

| Parameter                      | Minimum       | Maximum            | Unit |

|--------------------------------|---------------|--------------------|------|

| VIN                            | -0.3          | 45                 | V    |

| EBIAS                          | -0.3          | 45                 | V    |

| EN                             | -0.3          | 45                 | V    |

| SW                             | -0.7          | Vin+0.3            | V    |

| SW Transient                   | -3 (for 15ns) | V <sub>IN</sub> +2 | V    |

| BST                            | -0.7          | SW+4               | V    |

| BST to SW                      | -0.3          | 4                  | V    |

| All other pins                 | -0.3          | 4                  | V    |

| Operating junction temperature | -40           | 150                | °C   |

| Storage temperature range      | -65           | 150                | °C   |

### 3.2 ESD Ratings

| ESD Model/Test                                  | Rating | Unit |

|-------------------------------------------------|--------|------|

| Human Body Model (Tested per JS-001-2017)       | 2      | kV   |

| Charged Device Model (Tested per JS-002-2018)   | 750    | V    |

| Latch-Up (Tested per JESD78E; Class 2, Level A) | 100    | mA   |

## 3.3 Thermal Information

| Backago Tupo   | Thermal Resistance (Typical)          |                                            |                                       |  |  |  |  |

|----------------|---------------------------------------|--------------------------------------------|---------------------------------------|--|--|--|--|

| Package Type   | θ <sub>JA</sub> (°C/W) <sup>[1]</sup> | θ <sub>JA(EVB)</sub> (°C/W) <sup>[2]</sup> | θ <sub>JC</sub> (°C/W) <sup>[3]</sup> |  |  |  |  |

| QFN Package    | 48.3                                  | 27.3                                       | 6.0                                   |  |  |  |  |

| HTSSOP Package | 35.0                                  | 20.1                                       | 3.0                                   |  |  |  |  |

1. θ<sub>JA</sub> is measured in free air with the component mounted on a JEDEC std. high-effective thermal conductivity test board with direct attach features, including:

• For the QFN, 3 thermal vias under the bottom PGND area of the QFN.

• For the HTSSOP, 9 thermal vias under the bottom EPAD of the HTSSOP.

Note: See TB379 for general thermal metric information.

θ<sub>JA(EVB)</sub> is measured in free air with the component mounted on a 4-layer PCB (2oz Cu outer layers and 1 oz Cu inner layers) evaluation board.

3. For  $\theta_{JC}$ :

• For the QFN, the case temperature is taken on the pin #2 SW epad strip near the center of the package underside.

• For the HTSSOP, the case temperature is taken at the center of the exposed metal pad on the package underside.

| Parameter                         | Minimum | Maximum   | Unit |

|-----------------------------------|---------|-----------|------|

| Maximum Junction Temperature      |         | +150      | °C   |

| Maximum Storage Temperature Range | -65     | +150      | °C   |

| Pb-Free Reflow Profile            |         | see TB493 |      |

## 3.4 Recommended Operating Conditions

| Parameter                              | Minimum | Maximum                | Unit |

|----------------------------------------|---------|------------------------|------|

| Input Voltage (V <sub>IN</sub> )       | 4.5     | 42                     | V    |

| Output Voltage (V <sub>OUT</sub> )     | 0.8     | 90% of V <sub>IN</sub> | V    |

| EBIAS Operating Voltage (EBIAS)        | 3.3     | 40                     | V    |

| Output Current (I <sub>OUT</sub> )     | 0       | 5                      | A    |

| Junction Temperature (T <sub>J</sub> ) | -40     | 125                    | °C   |

#### **3.5 Electrical Specifications**

Typical Values are at  $T_A = +25^{\circ}$ C,  $V_{IN} = 24$ V unless otherwise noted. Min and Max values apply across the junction temperature range, -40°C to +125°C.

| Parameter                                  | Symbol              | Test Conditions                                                      | Min   | Тур  | Max   | Unit |

|--------------------------------------------|---------------------|----------------------------------------------------------------------|-------|------|-------|------|

| V <sub>IN</sub> Supply                     |                     |                                                                      |       | 1    | 1     | 1    |

| Input Voltage Range                        | V <sub>IN</sub>     |                                                                      | 4.5   |      | 42    | V    |

| Shutdown Current                           |                     |                                                                      |       | 1    |       | μA   |

| Quiescent Current                          | ۱ <sub>q</sub>      | EN = 2V, VFB = 0.825V, $V_{IN}$ = 24V,<br>EBIAS = 3.3V, No Switching |       | 90   | 200   | μA   |

| V <sub>IN</sub> UVLO/EN                    |                     |                                                                      |       | 1    | 1     | 1    |

| V <sub>IN</sub> UVLO Rising Threshold      |                     |                                                                      | 3.9   | 4.25 | 4.5   | V    |

| V <sub>IN</sub> UVLO Falling<br>Hysteresis |                     |                                                                      |       | 325  |       | mV   |

| EN Rising Threshold                        |                     |                                                                      | 1.125 | 1.3  | 1.375 | V    |

| EN Falling Hysteresis                      |                     |                                                                      |       | 170  |       | mV   |

| EN Deglitch Filter                         |                     |                                                                      |       | 2.5  |       | μs   |

| Feedback Voltage Referenc                  | e                   |                                                                      | 1     |      |       |      |

| Feedback Voltage                           | N                   | 25°C                                                                 | 0.796 | 0.8  | 0.804 | V    |

| Reference                                  | V <sub>FB</sub>     | -40°C to 125°C                                                       | 0.792 | 0.8  | 0.808 | V    |

| Integrated MOSFETs (QFN)                   |                     |                                                                      |       |      |       |      |

| High-Side FET<br>On-Resistance             | $R_{DS\_onh}$       |                                                                      |       | 70   |       | mΩ   |

| Low-Side FET<br>On-Resistance              | R <sub>DS_onl</sub> |                                                                      |       | 25   |       | mΩ   |

Typical Values are at  $T_A = +25^{\circ}$ C,  $V_{IN} = 24$ V unless otherwise noted. Min and Max values apply across the junction temperature range, -40°C to +125°C. (Cont.)

| Parameter                               | Symbol                       | Test Conditions                               | Min  | Тур | Мах | Unit  |

|-----------------------------------------|------------------------------|-----------------------------------------------|------|-----|-----|-------|

| Integrated MOSFETs (HTSSC               | DP)                          |                                               |      | 1   |     |       |

| High-Side FET                           | P                            |                                               |      | 115 |     | mΩ    |

| On-Resistance                           | $R_{DS_{ONH}}$               |                                               |      | 115 |     | 11152 |

| Low-Side FET                            | R <sub>DS_onl</sub>          |                                               |      | 40  |     | mΩ    |

| On-Resistance                           |                              |                                               |      |     |     |       |

| Soft-Start                              |                              |                                               |      | 1   |     |       |

| Internal Soft-Start Time                | t <sub>SS</sub>              |                                               |      | 0.5 |     | ms    |

| Soft-Start Charge Current               | I <sub>SS</sub>              |                                               | 3.75 | 5.3 | 6.5 | μA    |

| Soft-Start Pull-Down<br>Resistance      | R <sub>SS</sub>              |                                               |      | 1.1 |     | kΩ    |

| Soft-Start Done Threshold               |                              |                                               |      | 1.2 |     | V     |

| Oscillator/PWM Comparator               |                              |                                               |      | 1   |     |       |

| Switching Frequency                     | f <sub>SW</sub>              | V <sub>FB</sub> = 0.8 V, FS = V <sub>CC</sub> | 360  | 400 | 440 | kHz   |

| Minimum On-Time                         | t <sub>ON_MIN</sub>          |                                               |      | 96  |     | ns    |

| Minimum Off-Time                        | t <sub>OFF_MIN</sub>         |                                               |      |     | 220 | ns    |

| Switching Frequency<br>Range            |                              |                                               | 200  |     | 800 | kHz   |

| Overcurrent Protection (OCF             | )/V <sub>OUT</sub> Undervolt | age Protection (UVP)                          |      |     |     |       |

| Peak Current Limit<br>Threshold         | I <sub>HSOC</sub>            |                                               | 7.0  | 8.5 | 9.5 | A     |

| Low-Side Current Limit<br>Threshold     | I <sub>LSOC</sub>            |                                               | 5    | 6   |     | Α     |

| VFB Undervoltage<br>Threshold           |                              |                                               |      | 0.4 |     | v     |

| Foldback Frequency                      |                              | V <sub>FB</sub> = 0V                          |      | 50  |     | kHz   |

| Hiccup Time                             | t <sub>HICCUP</sub>          |                                               |      | 23  |     | ms    |

| Thermal Shutdown (OTP)                  |                              |                                               |      |     |     |       |

| Thermal Shutdown<br>Threshold           |                              |                                               |      | 155 |     | °C    |

| Thermal Shutdown<br>Recovery Hysteresis |                              |                                               |      | 20  |     | °C    |

| Power Good                              |                              | [                                             | 1    | I   |     | 1     |

| PG Overvoltage Threshold                |                              | % of FB Rising                                | 109  | 112 | 115 | %     |

| PG Undervoltage<br>Threshold            |                              | % of FB Falling                               | 85   | 88  | 91  | %     |

| Hysteresis                              |                              | % of FB                                       |      | 3   |     | %     |

| Deglitch Filter                         |                              | Rising and Falling Edges                      |      | 4   |     | μs    |

| Pull-Down Resistance                    |                              |                                               |      | 65  |     | Ω     |

Typical Values are at  $T_A = +25^{\circ}$ C,  $V_{IN} = 24$ V unless otherwise noted. Min and Max values apply across the junction temperature range, -40°C to +125°C. (Cont.)

| Parameter                              | Symbol | Test Conditions | Min  | Тур | Мах  | Unit |

|----------------------------------------|--------|-----------------|------|-----|------|------|

| V <sub>CC</sub> /EBIAS                 | I      |                 | 1    | 1   | I    | 1    |

| V <sub>CC</sub> Voltage                |        |                 | 3.1  | 3.3 | 3.5  | V    |

| VCC Output Current Limit               |        |                 |      | 50  |      | mA   |

| VCC UVLO Rising<br>Threshold           |        |                 | 2.75 | 3   | 3.15 | V    |

| VCC UVLO Falling<br>Hysteresis         |        |                 |      | 280 |      | mV   |

| EBIAS Operating Voltage                |        |                 | 3.3  |     | 40   | V    |

| EBIAS Switchover Rising<br>Threshold   |        |                 |      | 3.0 |      | V    |

| EBIAS Switchover Falling<br>Hysteresis |        |                 |      | 200 |      | mV   |

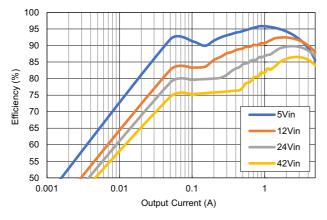

# 4. Typical Performance Curves

Waveforms and curves were measured on RTKA211450E00000BU or RTKA211450E00010BU, unless otherwise noted.

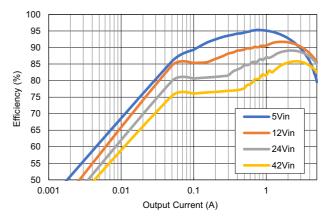

Figure 3. Efficiency vs Load, 3.3V V<sub>OUT</sub>, 400kHz, QFN

Figure 4. Efficiency vs Load, 3.3V V<sub>OUT</sub>, 400kHz, HTSSOP

3.295 3.290 3.285 3.280 5Vin 3.275 12Vin 3.270 24Vin 3.265 42Vin 3.260 0 1 2 3 4 5 Output Current (A)

Output Voltage (V)

3.300

#### RAA211450 Datasheet

Waveforms and curves were measured on RTKA211450E00000BU or RTKA211450E00010BU, unless otherwise noted. (Cont.)

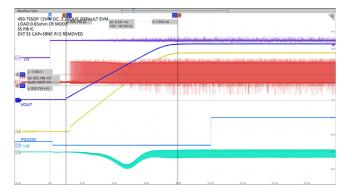

| 0-QFN:12VIN-DC, 3.3YOUT, DE     | AULT EVM | Δt: 546.682 μs<br>1/Δt: 1.83 kHz |        | C1<br>t: 546.421 µs      |                     |           |              |                                               |

|---------------------------------|----------|----------------------------------|--------|--------------------------|---------------------|-----------|--------------|-----------------------------------------------|

|                                 |          |                                  |        |                          |                     |           |              | · · · · · · · · · · •                         |

| V: 3.270 V                      |          |                                  |        | a en a la marca aprilado | e a station of a la |           | ******       | *********                                     |

| Δν: 3.233 V<br>Δν:δt: 5.91 kV/s |          |                                  |        |                          |                     | la valuar | N PROVIDENCE | unartaise anaras                              |

| v: 37.093 mV                    |          |                                  | 112.00 |                          | A MARINE            | MANAN     |              | <i>`</i> #################################### |

|                                 |          |                                  |        |                          |                     |           |              |                                               |

| lin<br>PGOOD                    |          |                                  |        |                          |                     |           |              | · · · · · · a                                 |

|                                 |          |                                  |        |                          |                     |           |              |                                               |

|                                 |          |                                  |        |                          |                     |           |              |                                               |

| laveform View                                                    |           | E |      |  |                                             |

|------------------------------------------------------------------|-----------|---|------|--|---------------------------------------------|

| 150-QFN:5VIN-DC, 3.3VOUT, DEP<br>OAD:1.5-OHM CR MODE<br>N AT 1HZ | ULT EVM   |   |      |  | B C 2 A<br>Δt: 135.240 μs<br>1/Δt: 7.39 kHz |

| _                                                                |           |   |      |  | t: 1.399 ms<br>t: 1.264 ms                  |

| v: 11.152 V                                                      |           |   |      |  |                                             |

| 6 EN<br>dw: 16.167 V<br>dw/dt: 119.54 kV/s                       | $\square$ |   | <br> |  |                                             |

| V:-5.015 V                                                       |           |   | -    |  |                                             |

|                                                                  |           |   |      |  |                                             |

| ▶ <u>I</u> L                                                     |           |   |      |  |                                             |

| PGOOD                                                            |           |   |      |  |                                             |

|                                                                  |           |   |      |  |                                             |

# Figure 7. EN Start-Up, $12V_{\text{IN}},\,3.3V\,V_{\text{OUT}},\,400\text{kHz},\\1.0\Omega\,\,\text{Load},\,\text{QFN}$

# Figure 8. EN Shutdown, 5V\_{IN}, 3.3V V\_{OUT}, 400kHz, 1.5\Omega Load, QFN

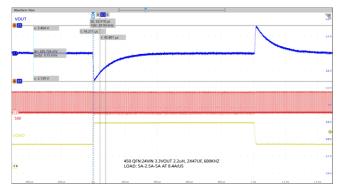

Figure 9. External SS,  $12V_{IN}$ ,  $3.3V_{OUT}$ ,  $0.65\Omega$  Load,  $C_{SS}$  = 39nF, HTSSOP

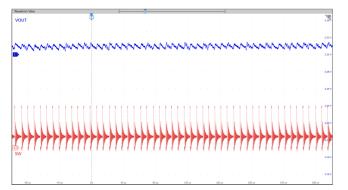

Figure 10. Steady-State, 3.3V V<sub>OUT</sub>, Full Load, 400kHz, QFN

Figure 11. Steady State, 3.3V V<sub>OUT</sub>, No Load, 400kHz, QFN

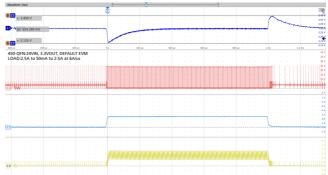

Figure 12. Load Transient,  $24V_{IN}$ ,  $3.3V_{OUT}$ , 400kHz, 50mA to 2.5A, QFNP

#### RAA211450 Datasheet

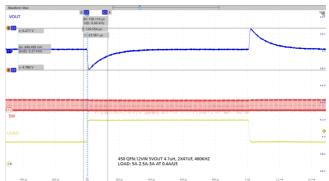

Waveforms and curves were measured on RTKA211450E00000BU or RTKA211450E00010BU, unless otherwise noted. (Cont.)

Figure 13. Load Transient,  $24V_{IN},\,3.3V_{OUT},\,600kHz,\,$  2.5A to 5A, QFN

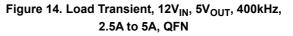

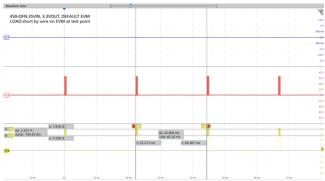

Figure 15. Output Voltage Short Protection, 12Vin,  $$3.3V_{OUT},\,\rm QFN$$

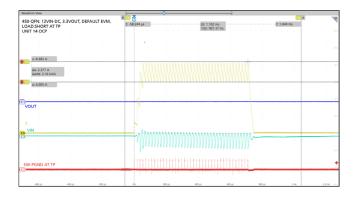

Figure 17. Undervoltage Protection,  $12V_{IN}$ ,  $3.3V_{OUT}$ , QFN

Figure 16. Output Short Protection with Hiccup, QFN

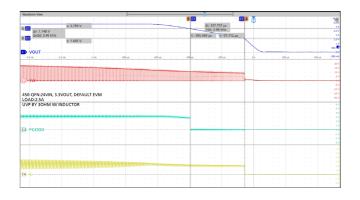

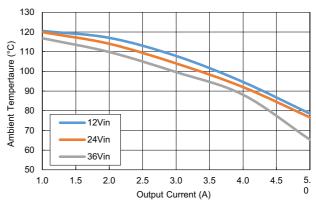

Figure 18. Safe Operating Area: 3.3V<sub>OUT</sub>, 400kHz, QFN, Default EVM

Waveforms and curves were measured on RTKA211450E00000BU or RTKA211450E00010BU, unless otherwise noted. (Cont.)

Figure 19. Safe Operating Area: 3.3V<sub>OUT</sub>, 400kHz, HTSSOP, Default EVM

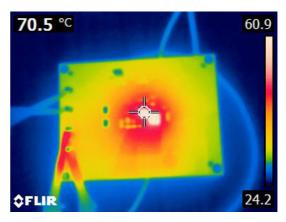

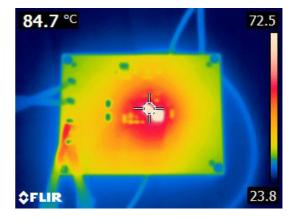

Figure 20. Thermal Image,  $12V_{IN},\,3.3V_{OUT},\,400kHz,\,5A,$  QFN,  $T_J$  = 70.5°C

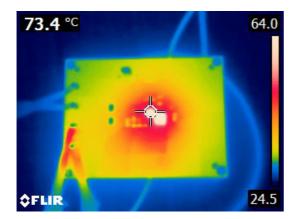

Figure 21. Thermal Image,  $24V_{IN},\,3.3V_{OUT},\,400kHz,\,5A,$  QFN,  $T_J$  =  $73.4^\circ\text{C}$

Figure 22. Thermal Image,  $36V_{IN},\,3.3V_{OUT},\,400kHz,\,5A,$  QFN,  $T_J$  =  $84.7^\circ\text{C}$

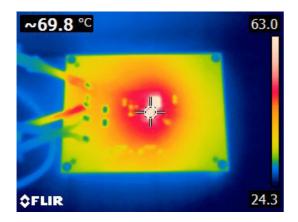

Figure 23. Thermal Image,  $12V_{IN}$ ,  $3.3V_{OUT}$ , 400kHz, 5A, HTSSOP, T<sub>J</sub> = 69.8°C

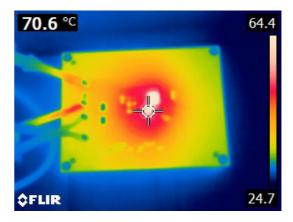

Figure 24. Thermal Image,  $24V_{IN}$ ,  $3.3V_{OUT}$ , 400kHz, 5A, HTSSOP, T<sub>J</sub> = 70.6°C

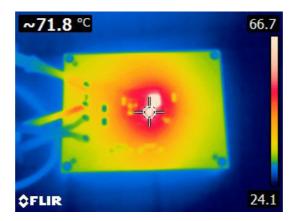

Waveforms and curves were measured on RTKA211450E00000BU or RTKA211450E00010BU, unless otherwise noted. (Cont.)

Figure 25. Thermal Image,  $36V_{IN}$ ,  $3.3V_{OUT}$ , 400kHz, 5A, HTSSOP, T<sub>J</sub> = 71.8°C

## 5. Functional Description

The control architecture is based on peak current mode control. The output voltage is sensed by a resistor divider from the output of the converter to the FB pin. An internal transconductance error amplifier (EA) compares the FB voltage with an internal 0.8V reference voltage and produces an amplified compensated signal (COMP) to minimize the error in  $V_{OUT}$ . The EA has internal compensation that provides stable operation across operating conditions and switching frequency range. The COMP signal is compared with the sum of sensed high-side current and the slope compensation value.

#### 5.1 Fixed Frequency Operation Mode

In the continuous conduction mode (CCM) operation where the load current is higher one-half of inductor peak-to-peak inductor current, the RAA211450 operates at a programmed fixed frequency. At the rising edge of the PWM clock, the high-side FET turns on and the inductor current ramps up at a slew rate determined by the inductor value, input voltage, and output voltage. The high-side FET is switched off when the sum of the sampled high-side FET current and slope compensation reaches the COMP signal level or when either the maximum duty cycle or high-side overcurrent is reached. *Note:* The high-side FET must stay on for at least 96ns as the minimum on-time expires.

When the high-side FET is turned off, the low-side FET turns on after a small amount of dead time. The dead time between the two MOSFETs prevents shoot-through. When the low-side FET is turned on for the remainder of period, the inductor current ramps down at a rate determined by the output voltage and inductor value. *Note:* The low-side FET must stay on for at least 220ns as the minimum off-time expires.

#### 5.2 Discontinuous Operation Mode

To improve efficiency at light load, RAA211450 allows operation with the switching frequency lower than programmed frequency. The switching frequency is varied and depends on the output load. RAA211450 enters the discontinuous conduction mode (DCM) when the output load is less than one-half of the peak-to-peak ripple current of the inductor. In this mode, the COMP signal value is lower than the preset DCM value. Also, the internal oscillator clock is forced to skip pulses and allows reduction of the cycle switching frequency.

When the output load is increasing, the COMP signal rises above the preset DCM value and exits the DCM.

#### 5.3 Soft-Start Timing

Depending on which RAA211450 package you are using, there are two options to configure soft-start timing. The QFN package has a fixed soft-start time of 500 $\mu$ s (typical), which is not adjustable. The HTSSOP package allows soft-start time to be set to an interval longer than 500 $\mu$ s by placing a capacitor from the SS pin to ground. Use Equation 1 to calculate the C<sub>SS</sub> value. If you want to use 500 $\mu$ s soft-start time with the HTSSOP package, short the SS pin to VCC.

(EQ. 1)  $t_{SS} = C_{SS} \times \frac{V_{REF}}{I_{SS}}$

#### 5.4 Start-Up Process

When both EN and V<sub>IN</sub> UVLO meet the thresholds, RAA211450 initiates the start-up process. When the output voltage starts from 0V, RAA211450 uses the SS voltage as the reference voltage for the EA during start-up. The SS voltage starts from 0V and finishes the soft-start when the SS voltage reaches 0.8V. After soft-start, RAA211450 switches to its 0.8V reference voltage for the EA. The SS voltage continues ramping up, and when it reaches 1.2V, it asserts the PG signal.

When pre-bias is present on the output, RAA211450 does not generate any pulses until the SS voltage is greater than the FB voltage.

#### 5.5 BOOT Refresh and Capacitor Selection

Approximately 500µs after EN is driven high and before the start-up process begins, the RAA211450 turns on the low-side FET for 250ns with a 2µs period and repeats this for 32 cycles. This action charges the boot capacitor before the start-up process begins. After the regulator has started up, if it is operating in DCM in a light load condition, the boot refresh circuitry is enabled when the cycle switching frequency is longer than 3.7ms.

A capacitor is needed between the BST pin and SW pin to provide gate voltage for the high-side internal MOSFET. Renesas recommends using a 16V X7R 0.1µF ceramic capacitor as the bootstrap capacitor for most applications.

#### 5.6 Power-Good

The RAA211450 provides a Power-Good (PG) signal to alert the system that the output voltage is within regulation. Power-good logic is functional when VCC voltage is above UVLO.

The PG pin is the open drain of a MOSFET. Renesas recommends connecting it to a voltage source through a pull-up resistor such as  $100k\Omega$ . At the start-up, the PG signal is held low before SS is ready, and it is asserted when the SS voltage reaches 1.2V, and FB voltage is within the regulation window. When the FB voltage goes 12% below or 12% above the nominal value, PG is pulled low.

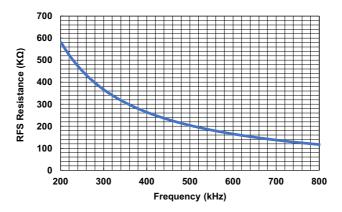

### 5.7 Switching Frequency Resistor Selection

The default switching frequency of 400kHz is programmed by shorting the FS pin to VCC. Connect a resistor from the FS pin to AGND to program the switching frequency from 200kHz to 800kHz. See Figure 26 and Table 1 to select a resistor value for a specific frequency.

Figure 26. Switching Frequency versus FS Resistance

| Table 1. Typica | Switching Frequency Resistor Value |

|-----------------|------------------------------------|

|                 |                                    |

| Switching Frequency (kHz) | R <sub>FS</sub> (kΩ) |

|---------------------------|----------------------|

| 200                       | 590                  |

| 300                       | 374                  |

| 400                       | 261                  |

| 500                       | 205                  |

| 600                       | 165                  |

| 700                       | 140                  |

| 800                       | 121                  |

#### 5.8 Input Undervoltage Lockout

The input undervoltage lockout level can be set with a resistor divider from VIN to the EN pin to GND based on Equation 2 (see Figure 1).

(EQ. 2)

$$R_{IN1} = R_{IN2} \times \frac{V_{INR} - 1.25}{1.25}$$

where  $V_{INR}$  is the minimum input voltage for the part to turn on. The resulting input voltage ( $V_{INF}$ ) for the part to be turned off is calculated using Equation 3 (see Figure 1).

(EQ. 3)

$$V_{INF} = 1.125 \times \frac{R_{IN1} + R_{IN2}}{R_{IN2}}$$

#### 5.9 VCC and EBIAS

RAA211450 uses the VCC voltage to bias the IC, charges the boot capacitor and drives the low-side MOSFET. VCC is an output of two internal LDOs. One LDO is connected to VIN and the other LDO is connected to EBIAS.

The EBIAS pin allows you to connect an external bias source to the IC. The typical usage case is to connect the output voltage rail (VOUT) to EBIAS. Any other voltage source that is in the 3.3V to 40V range can also be used for this purpose. When EBIAS is connected to VOUT, RAA211450 automatically detects and switches over to the

VOUT bias source when it is greater than 3.1V. Using the EBIAS pin results in higher efficiency if the external bias voltage level is lower than the input voltage. The EBIAS pin can be grounded if not used.

### 5.10 Overcurrent Protection (OCP)

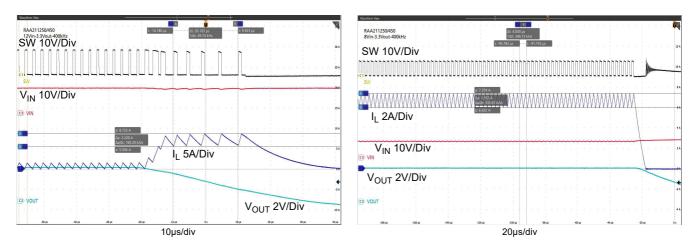

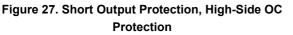

RAA211450 detects both high-side and low-side overcurrent using a cycle-by-cycle sensing method. Overcurrent in the high-side FET is detected by sensing the voltage across the FET while it is on. After the high-side FET is on, there is a noise blanking interval before the inductor current is compared to a fixed peak current threshold value of 8.3A. The high-side FET on-time is terminated immediately when the inductor current reaches 8.3A. The low-side FET is switched on to draw down the inductor current. The low-side FET remains on until the valley inductor current falls below a fixed threshold value of 6A. Overcurrent in the low-side FET is detected by sensing the voltage across the FET while it is on. After the low-side FET is on, there is a noise blanking time before the OC comparator is enabled. When the valley inductor current is below 6A, the high-side FET can turn on. Because of this, the cycle switching frequency is lower than programmed switching frequency. The output voltage is reduced during OCP events. When the FB voltage falls to 50% of 0.8V<sub>REF</sub>, RAA211450 enters hiccup mode until the excessive load is removed.

For an application that operates near minimum on-time or if there is a hard short on the output, the COMP voltage moves higher to extend the on-time to respond to the lower output voltage. In this case, the high-side OCP dominates. When the output current ramps up gradually and the peak inductor current does not reach 8.3A, the low-side OCP dominates. Figure 27 and Figure 28 show the cases for output hard short and slowly ramping up the output current. These protections work together to prevent damage to the system such as IC, components, and the load.

#### 5.11 Undervoltage and Overvoltage Protection

When the RAA211450 senses that the FB voltage has dropped to 50% of  $V_{REF}$  (or lower), an undervoltage fault condition exists. Both the high-side and low-side FETs are tri-stated when this condition is detected and the RAA211450 enters a hiccup mode for a 23ms period. The converter attempts to start up after the 23ms hiccup timer expires. If the short or heavy load has been removed, it resumes normal voltage regulation. If the short or heavy load is still present, the fault condition continues, and the converter repeats the hiccup process.

#### 5.12 Thermal Protection

If RAA211450 senses a temperature above the thermal limit (typically 150°C), the converter is disabled and remains disabled until the temperature drops down to 130°C. The PG signal is pulled low during the over-temperature event.

## 6. Applications Information

#### 6.1 Output Voltage Feedback Resistor Divider

The output voltage can be programmed down to 0.8V with a resistor divider from VOUT to the FB pin to GND based on Equation 4. The recommended  $R_{FB2}$  (see Figure 1) resistance is  $20k\Omega$ . See Recommended Components Values for Typical Applications for  $R_{FB1}$  and  $R_{FB2}$  values for typical V<sub>OUT</sub> applications.

(EQ. 4)

$$R_{FB1} = R_{FB2} \times \frac{V_{OUT} - 0.8}{0.8}$$

#### 6.2 Inductor Selection

Several factors need to be considered when selecting an inductor for use with the RAA211450. An inductor with lower DC resistance results in higher efficiency; however, the part may be physically larger than required. The saturation current rating needs to be high enough to accommodate DC load current and AC ripple current with additional margin for overload conditions. Selecting a higher inductance value results in lower output ripple voltage; however, transient performance is impacted. Renesas recommends starting off by assuming a range of inductor ripple current of 30% to 50% of maximum output current. Inductor ripple current is calculated using Equation 5.

(EQ. 5)

$$\Delta I = \frac{V_{OUT} \times (1-D)}{L \times f_{SW}}$$

Considering the wide operating input voltage range of the part, Renesas recommends calculating the required inductor by using Equation 6. Recommended Components Values for Typical Applications can be referenced for selecting the inductance for typical  $V_{OUT}$  applications., where  $V_{OUT}$  is the output voltage in V, L is the inductance in  $\mu$ H, and  $f_{SW}$  is the switching frequency in kHz.

(EQ. 6)

$$L(\mu H) = \frac{1000 \times V_{OUT} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)}{\Delta I \times f_{SW}(kHz)}$$

#### 6.3 Input Capacitor Selection

The input capacitor is used in the buck converter to maintain the input voltage by suppressing the voltage ripple induced by discontinuous switching current. The required RMS current rating  $I_{IN(RMS)}$  of the input capacitor is calculated using Equation 7, where  $I_{OUT(MAX)}$  is the maximum average load current and D is the duty ratio. When D equals 0.5,  $I_{IN(RMS)}$  has the maximum value which is  $I_{OUT(MAX)}/2$ .

(EQ. 7)  $I_{\text{IN}(\text{RMS})} = I_{\text{OUT}(\text{MAX})} \times \sqrt{D \times (1-D)}$

The voltage rating of the input capacitor should be higher than the maximum input voltage. The required capacitance  $C_{IN}$  of the input capacitor to ensure the expected peak-to-peak input voltage ripple  $\Delta V_{IN}$  is calculated using Equation 8, where  $f_{SW}$  is the switching frequency.

(EQ. 8)

$$C_{IN} = I_{OUT(MAX)} \times \frac{D \times (1-D)}{f_{SW} \times \Delta V_{IN}}$$

The required capacitance also has the maximum value when D equals 0.5. Renesas recommends using low ESR/low ESL ceramic capacitors across the input of the regulator. When selecting the ceramic capacitors for

power supply applications, consider that the effective capacitance reduces with DC bias voltage across it, so you need to consult the capacitor datasheets to understand the impact of this effect. Also, Renesas recommends using X7R dielectric ceramic capacitors because of their small temperature coefficient.

If the input to the regulator is fed through a high impedance path, Renesas recommends adding an electrolytic capacitor in addition to the ceramic capacitor to dampen the input voltage oscillation effects.

#### 6.4 Output Capacitor Selection

Output capacitor selection impacts both steady state performance and transient performance of the buck converter. Factors such as output voltage ripple, output voltage variation during transients, and control loop stability should be considered when selecting the output capacitor. Renesas recommends using X7R dielectric ceramic for the output capacitor. When selecting the ceramic capacitor, consider that the effective capacitance reduces with DC bias voltage across it.

The effective capacitance of the ceramic capacitor should be used when determining output voltage ripple. The required capacitance  $C_{OUT(RIPPLE)}$  for the expected peak-to-peak output voltage ripple  $\Delta V_{OUT(RIPPLE)}$  is calculated using Equation 9:, where  $\Delta I_L$  is the inductor peak-to-peak current ripple and  $f_{SW}$  is the switching frequency.

(EQ. 9)

$$C_{OUT(RIPPLE)} = \frac{\Delta I_L}{8 \times f_{SW} \times \Delta V_{OUT(RIPPLE)}}$$

To meet the output voltage variation requirements during load step up and load step down transients, the required capacitance  $C_{OUT(STEPUP)}$  is calculated using Equation 10 and  $C_{OUT(STEPDOWN)}$  is calculated using Equation 11, where  $I_{STEP}$  is the transient load step and  $\Delta V_{OUT}$  is the expected voltage variation during the transient.

(EQ. 10)

$$C_{OUT(STEPUP)} = \frac{L \times \left(I_{STEP} + \frac{\Delta I_{L}}{2}\right)^{2}}{2 \times (V_{IN} - V_{OUT}) \times \Delta V_{OUT}}$$

(EQ. 11)

$$C_{OUT(STEPDOWN)} = \frac{L \times \left(I_{STEP} + \frac{\Delta I_L}{2}\right)^2}{2 \times V_{OUT} \times \Delta V_{OUT}}$$

To have a stable control loop with adequate gain margin, phase margin, and bandwidth, the required capacitance  $C_{OUT(LOOP)}$  is derived using Equation 12:, where  $C_{OUT(LOOP)}$  is in µF and  $V_{OUT}$  is in V.

$$(\textbf{EQ. 12}) \quad \textbf{C}_{OUT(LOOP)}(\mu F) = \frac{150000}{f_{SW}(kHz) \times V_{OUT}}$$

The output capacitors should be selected so that requirements are met: this means that the total output capacitance should be greater than the highest value calculated in Equation 9, Equation 10, Equation 11, or Equation 12.

See Recommended Components Values for Typical Applications for further guidance when selecting output capacitors for typical V<sub>OUT</sub> applications.

# 7. Layout Suggestions

- Place the input ceramic capacitor(s) as close as possible to the IC VIN pin and PGND pins. Keep the power loop (input ceramic capacitor, IC VIN and PGND pins) as small as possible to minimize switch node voltage ringing caused by parasitic inductance in the PCB traces. Minimizing loop size also results in better EMI performance.

- Place an 0402 or 0603 size 0.1µF capacitor as close as possible to VIN and PGND pins. Then place a higher value capacitor such as 1µF or 10µF right next to the 0.1µF capacitor. If an aluminum electrolytic capacitor is used, place it as close as possible to the 0.1µF/1µF/10µF capacitors near the VIN pin.

- Keep the phase node copper area small to reduce parasitic capacitance, but large enough to handle the load current.

- The power ground (CIN and COUT ground) should be connected to the analog ground layer or island, which connects to GND pin, in only one spot.

- Place feedback resistors close to the FB and GND pin and away from phase and boot signals.

- Place the ceramic decoupling capacitor for VCC on the same side of the PCB as the IC, as close as possible to the pin.

- Add additional thermal vias to thermal PGND pad for better heat transfer.

*Note:* The thermal performance depends on the PCB area and copper layer thickness. For the evaluation board, 2oz copper for top and bottom layers and 1oz copper for two internal layers were used. Use the evaluation board manual as a reference for the PCB layout and further details.

#### 7.1 Layout Examples

Figure 29. HTSSOP Package Layout Recommendation

Figure 30. QFN Package Layout Recommendation

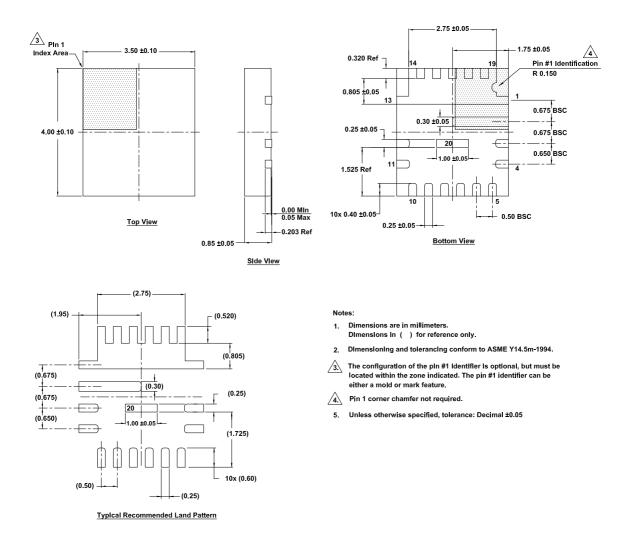

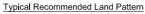

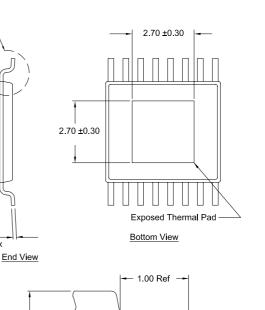

## 8. Package Outline Drawings

For the most recent package outline drawing, see L20.3.5x4.

L20.3.5x4 20 Lead Quad Flat No-Lead Package (QFN) Rev 2, 8/2022

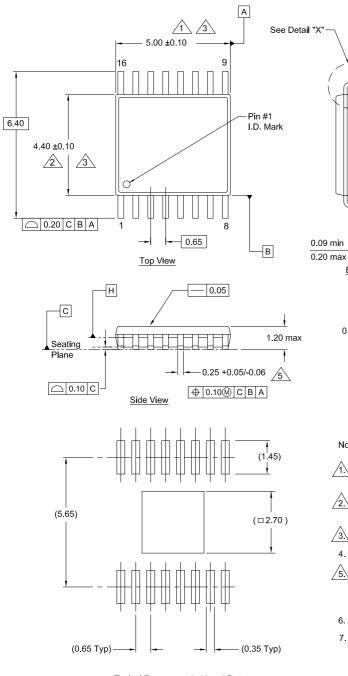

For the most recent package outline drawing, see M16.173B.

M16.173B

16 Lead Heatsink Thin Shrink Small Outline Package (HTSSOP) Rev 0, 9/20

Notes:

- <u>\_\_\_\_\_\_</u> Dimension does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs can not exceed 0.15 per side.

- 2. Dimension does not include interlead flash or protrusion. Interlead flash or protrusion can not exceed 0.25 per side.

- 3 Dimensions are measured at datum plane H.

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

- Dimension does not include dambar protrusion. Allowable protrusion is 0.08mm total in excess of dimension at maximum material condition. Minimum space between protrusion and adjacent lead is 0.07mm.

- 6. Dimensions in ( ) are for reference only.

- 7. Conforms to JEDEC MO-153

## 9. Ordering Information

| Part Number <sup>[1][2]</sup> | Part Marking  | Package Description<br>(RoHS Compliant) | Pkg.<br>Dwg # | Carrier<br>Type <sup>[3]</sup> | Junction Temp.<br>Range |  |

|-------------------------------|---------------|-----------------------------------------|---------------|--------------------------------|-------------------------|--|

| RAA211450GNP#HA0              | RAA<br>211450 | 3.5×4 mm QFN                            | L20.3.5x4     | Reel, 6k                       | -40°C to +125°C         |  |

| RAA211450GSP#HA0              | RAA2<br>11450 | 16 Lead HTSSOP                          | M16.173B      | Reel, 2.5k                     | -40 C 10 +125 C         |  |

These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J-STD-020.

2. For Moisture Sensitivity Level (MSL), see the RAA211450 device page. For more information about MSL, see TB363.

3. See TB347 for details about reel specifications.

## 10. Revision History

| Revision | Date         | Description                                                                                                                                                                                                          |

|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.02     | Oct 12, 2022 | Updated VIN UVLO Rising Threshold minimum value from 4.05V to 3.9V.<br>Updated EN Deglitch Filter typical value from 1µs to 2.5µs.<br>Updated Figure 1.                                                              |

| 1.01     | Sep 1, 2022  | <ul> <li>Updated POD L20.3.5x4 to the latest revision, changes are as follows:</li> <li>Changed "9x" to "10x" in the bottom view to account for the correct number of leads.</li> <li>Updated Equation 5.</li> </ul> |

| 1.00     | Aug 4, 2022  | Initial release                                                                                                                                                                                                      |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Renesas Electronics: RAA211450GNP#HA0 RAA211450GSP#HA0