## TEXAS INSTRUMENTS

SLUS025F - MAY 2001 - REVISED JULY 2002

## ADVANCED LINEAR CHARGE MANAGEMENT IC FOR SINGLE- AND TWO-CELL LITHIUM-ION AND LITHIUM-POLYMER

### FEATURES

- Ideal for Single (4.1 V or 4.2 V) and Dual-Cell (8.2 V or 8.4 V) Li-Ion or Li-Pol Packs

- Requires Small Number of External Components

- 0.3 V Dropout Voltage for Minimizing Heat Dissipation

- Better Than ±1% Voltage Regulation Accuracy With Preset Voltages

- AutoComp<sup>™</sup> Dynamic Compensation of Battery Pack's Internal Impedance to Reduce Charge Time

- Optional Cell-Temperature Monitoring Before and During Charge

- Integrated Voltage and Current Regulation With Programmable Charge-Current and Highor Low-Side Current Sensing

- Integrated Cell Conditioning for Reviving Deeply Discharged Cells and Minimizing Heat Dissipation During Initial Stage Of Charge

- Charge Status Output for Single or Dual Led or Host Processor Interface

- Automatic Battery-Recharge Feature

- Charge Termination by Minimum Current

- Automatic Low-Power Sleep Mode When V<sub>CC</sub> Is Removed

- EVMs Available for Quick Evaluation

- Packaging: 8-Pin SOIC, 8-Pin TSSOP, 8-Pin MSOP

## DESCRIPTION

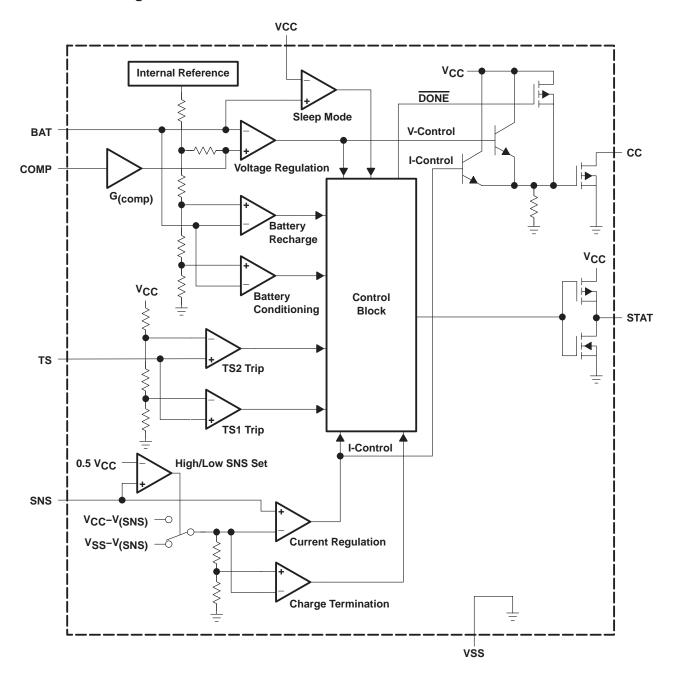

The BENCHMARQ bq2057 series advanced Lithium-Ion (Li-Ion) and Lithium-Polymer (Li-Pol) linear charge-management ICs are designed for costsensitive and compact portable electronics. They combine high-accuracy current and voltage regulation, battery conditioning, temperature monitoring, charge termination, charge-status indication, and AutoComp charge-rate compensation in a single 8-pin IC. MSOP, TSSOP, and SOIC package options are offered to fit a wide range of end applications.

bq2057 The continuously measures battery temperature using an external thermistor. For safety, the bg2057 inhibits charge until the battery temperature is within user-defined thresholds. The bg2057 then charges the battery in three phases: conditioning, constant current, and constant voltage. If the battery voltage is below the low-voltage threshold, V(min), the bg2057 precharges using a low current to condition the battery. The conditioning charge rate is approximately 10% of the regulation current. The conditioning current also minimizes heat dissipation in the external passelement during the initial stage of the charge. After conditioning, the bg2057 applies a constant current to the battery. An external sense-resistor sets the current. The sense-resistor can be on either the high or low side of the battery without additional components. The constant-current phase continues until the battery reaches the charge-regulation voltage.

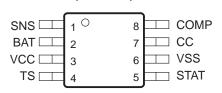

bq2057xSN or bq2057xTS

SOIC (SN) or TSSOP (TS) PACKAGE

(TOP VIEW)

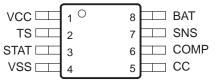

bq2057xDGK MSOP (DGK) PACKAGE (TOP VIEW)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

AutoComp is a trademark of Texas Instruments.

#### **DESCRIPTION** (continued)

The bq2057 then begins the constant-voltage phase. The accuracy of the voltage regulation is better than  $\pm 1\%$  over the operating-temperature and supply-voltage ranges. For single and dual cells, the bq2057 is offered in four fixed-voltage versions: 4.1 V, 4.2 V, 8.2 V, and 8.4 V. Charge stops when the current tapers to the charge termination threshold, I<sub>(TERM)</sub>. The bq2057 automatically restarts the charge if the battery voltage falls below the V<sub>(RCH)</sub> threshold.

The designer also may use the AutoComp feature to reduce charging time. This proprietary technique allows safe and dynamic compensation for the internal impedance of the battery pack during charge.

|               | PACKAGE                      |               |               |                  |  |  |  |  |  |  |

|---------------|------------------------------|---------------|---------------|------------------|--|--|--|--|--|--|

| TA            | CHARGE REGULATION<br>VOLTAGE | SOIC<br>(SN)  | TSSOP<br>(TS) | MSOP†<br>(DGK)   |  |  |  |  |  |  |

| –20°C to 70°C | 4.1 V                        | Not available | bq2057TS      | bq2057DGK        |  |  |  |  |  |  |

|               | 4.2 V                        | bq2057CSN     | bq2057CTS     | bq2057CDGK       |  |  |  |  |  |  |

|               | 8.2 V                        | Not available | bq2057TTS     | Not ever lieb to |  |  |  |  |  |  |

|               | 8.4 V                        | bq2057WSN     | bq2057WTS     | Not available    |  |  |  |  |  |  |

AVAILABLE OPTIONS

<sup>†</sup>Note the difference in pinout for this package.

SLUS025F - MAY 2001 - REVISED JULY 2002

### function block diagram

### **Terminal Functions**

|      | TERMINAL                    |               |     |                                           |  |  |

|------|-----------------------------|---------------|-----|-------------------------------------------|--|--|

|      | NO.                         |               | 1/0 | DESCRIPTION                               |  |  |

| NAME | SOIC (SN) and<br>TSSOP (TS) | MSOP<br>(DGK) | 1/0 | DESCRIPTION                               |  |  |

| BAT  | 2                           | 8             | Ι   | Voltage sense input                       |  |  |

| CC   | 7                           | 5             | 0   | Charge control output                     |  |  |

| COMP | 8                           | 6             | Ι   | Charge-rate compensation input (AutoComp) |  |  |

| SNS  | 1                           | 7             | Ι   | Current sense input                       |  |  |

| STAT | 5                           | 3             | 0   | Charge status output                      |  |  |

| TS   | 4                           | 2             | Ι   | Temperature sense input                   |  |  |

| VCC  | 3                           | 1             | Ι   | Supply voltage                            |  |  |

| VSS  | 6                           | 4             |     | Ground                                    |  |  |

#### detailed description

#### current-sense input

Battery current is sensed via the voltage developed on this pin by an external sense resistor. The external resistor can be placed on either the high or low side of the battery. (See schematics for details.)

#### battery-voltage input

Voltage sense-input tied directly to the positive side of the battery.

#### temperature sense input

Input for an external battery-temperature monitoring circuit. Connecting this input to VCC/2 disables this feature.

#### charge-status output

3-state indication of charge in progress, charge complete, and temperature fault or sleep mode.

#### charge-control output

Source-follower output that drives an external pass-transistor (PNP or P-channel MOSFET) for current and voltage regulation.

#### charge-rate compensation input

Sets the charge-rate compensation level. The voltage-regulation output may be programmed to vary as a function of the charge current delivered to the battery.

#### supply voltage input

Power supply input and current reference for high-side sensing configuration.

SLUS025F - MAY 2001 - REVISED JULY 2002

#### absolute maximum ratings over operating free-air temperature (unless otherwise noted)<sup>†</sup>

| Supply voltage (V <sub>CC</sub> with respect to GND)<br>Input voltage, SNS, BAT, TS, COMP (all with respect to GND)<br>Sink current (STAT pin) not to exceed P <sub>D</sub> | . –0.3 V to $V_{CC}$ +0.3 V |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Source current (STAT pin) not to exceed P <sub>D</sub>                                                                                                                      | 10 mA                       |

| Output current (CC pin) not to exceed P <sub>D</sub>                                                                                                                        | 40 mA                       |

| Total power dissipation, P <sub>D</sub> (at 25°C)                                                                                                                           | 300mW                       |

| Operating free-air temperature range, T <sub>A</sub>                                                                                                                        | –20°C to 70°C               |

| Storage temperature range, T <sub>stg</sub>                                                                                                                                 | –40°C to 125°C              |

| Lead temperature (soldering, 10 s)                                                                                                                                          | 300°C                       |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### DISSIPATION RATING TABLE

| PACKAGE | DERATING FACTOR             | T <sub>A</sub> ≤ 25°C | T <sub>A</sub> = 70°C |

|---------|-----------------------------|-----------------------|-----------------------|

|         | ABOVE T <sub>A</sub> = 25°C | POWER RATING          | POWER RATING          |

| DGK     | 3.4 mW/°C                   | 424 mW                | 271 mW                |

#### recommended operating conditions

|                                          | MIN | MAX | UNIT |

|------------------------------------------|-----|-----|------|

| Supply voltage, V <sub>CC</sub>          | 4.5 | 15  | V    |

| Operating free-air temperature range, TA | -20 | 70  | °C   |

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                      | TEST CONDITIONS                                                            | MIN                                                   | TYP  | MAX   | UNIT |  |  |

|-----------------------|--------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------|------|-------|------|--|--|

| I(VCC)                | V <sub>CC</sub> Current        | $V_{CC} > V_{CC(min)}$ , Excluding external loads                          | > V <sub>CC(min)</sub> , Excluding external loads 2 4 |      |       |      |  |  |

|                       |                                | For bq2057 and bq2957C, $V(BAT) \ge V(min)$ , $V(BAT) - V_{CC} \ge 0.8 V$  |                                                       | 3    | 6     |      |  |  |

| I(VCCS)               | V <sub>CC</sub> Sleep current  | For bq2057T and bq2957W, $V(BAT) \ge V(min)$ , $V(BAT) - V_{CC} \ge 0.8 V$ |                                                       |      | 10    | μA   |  |  |

| I <sub>IB(BAT)</sub>  | Input bias current on BAT pin  | V(BAT) = V(REG)                                                            |                                                       |      | 1     | μΑ   |  |  |

| I <sub>IB</sub> (SNS) | Input bias current on SNS pin  | V(SNS)= 5 V                                                                |                                                       |      | 5     | μΑ   |  |  |

| I <sub>IB(TS)</sub>   | Input bias current on TS pin   | V(TS) = 5 V                                                                |                                                       |      | 5     | μΑ   |  |  |

| IB(COMP)              | Input bias current on COMP pin | V(COMP) = 5 V                                                              |                                                       |      | 5     | μΑ   |  |  |

| BATTERY \             | OLTAGE REGULATION              | •                                                                          | -                                                     |      |       |      |  |  |

|                       |                                | bq2057, See Notes 1, 2, 3                                                  | 4.059                                                 | 4.10 | 4.141 |      |  |  |

|                       | Output voltage                 | bq2057C, See Notes 1, 2, 3 4.15                                            |                                                       | 4.20 | 4.242 |      |  |  |

| V <sub>O(REG)</sub>   |                                | bq2057T, See Notes 1, 2, 3 8.                                              |                                                       | 8.20 | 8.282 | V    |  |  |

|                       |                                | bq2057W, See Notes 1, 2, 3                                                 | 8.317                                                 | 8.40 | 8.484 |      |  |  |

NOTES: 1. For high-side current sensing configuration

2. For low-side current sensing configuration, the tolerance is  $\pm 1\%$  for T<sub>A</sub> = 25°C and  $\pm 1.2\%$  for  $-20°C \ge T_A \ge 70°C$

3.  $V_{(BAT)}$ +0.3  $V \le V_{CC} \le V_{CC}(max)$

SLUS025F - MAY 2001 - REVISED JULY 2002

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted) (continued)

| PA                                        | RAMETER                                           | TEST CONDITIONS                                                                                                                                          | MIN                            | TYP                                        | MAX                            | UNIT |  |

|-------------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------|--------------------------------|------|--|

| CURRENT R                                 | REGULATION                                        |                                                                                                                                                          |                                |                                            |                                |      |  |

|                                           |                                                   | bq2057 and bq2057C,<br>High-side current sensing configuration                                                                                           | 95.4                           | 105                                        | 115.5                          |      |  |

|                                           | Current regulation                                | bq2057T and bq2057W,<br>High-side current sensing configuration                                                                                          | 113.6                          | 125                                        | 137.5                          |      |  |

| V(SNS)                                    | threshold                                         | bq2057 and bq2057C,<br>Low-side current sensing configuration                                                                                            | 100                            | 110                                        | 121                            | mV   |  |

|                                           |                                                   | bq2057T and bq2057W,<br>Low-side current sensing configuration                                                                                           | 118.1                          | 130                                        | 143                            |      |  |

| CHARGE TE                                 | RMINATION DETEC                                   | TION                                                                                                                                                     |                                |                                            |                                |      |  |

| <sup>I</sup> (TERM)                       | Charge termination<br>current detect<br>threshold | Voltage at pin SNS, relative to V <sub>CC</sub> for high-side sensing, and to Vss for low-side sensing, $0^{\circ}C \le T_A \le 50^{\circ}C$             | -24                            | -14                                        | -4                             | mV   |  |

| TEMPERATU                                 | URE COMPARATOR                                    | 1                                                                                                                                                        | 1                              |                                            |                                |      |  |

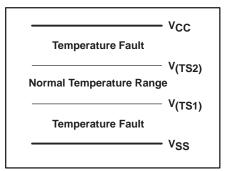

| V <sub>(TS1)</sub>                        | Lower temperature threshold                       |                                                                                                                                                          | 29.1                           | 30                                         | 30.9                           |      |  |

| V <sub>(TS2)</sub>                        | Upper temperature threshold                       | TS pin voltage                                                                                                                                           | 58.3                           | 60                                         | 61.8                           | %Vcc |  |

| PRECHARG                                  | E COMPARATOR                                      |                                                                                                                                                          |                                |                                            |                                | 1    |  |

|                                           |                                                   | bq2057                                                                                                                                                   | 2.94                           | 3                                          | 3.06                           |      |  |

|                                           | Precharge                                         | bq2057C                                                                                                                                                  | 3.04                           | 3.1                                        | 3.16                           |      |  |

| V <sub>(min)</sub>                        | threshold                                         | bq2057T                                                                                                                                                  | 5.98                           | 6.1                                        | 6.22                           | V    |  |

|                                           |                                                   | bq2057W                                                                                                                                                  | 6.18                           | 6.3                                        | 6.43                           |      |  |

| PRECHARG                                  | E CURRENT REGUL                                   | ATION                                                                                                                                                    |                                |                                            |                                |      |  |

| Precharge current<br>I(PRECHG) regulation |                                                   | Voltage at pin SNS, relative to V <sub>CC</sub> for high-side sensing, and to V <sub>SS</sub> for low-side sensing, $0^{\circ}C \le T_A \le 50^{\circ}C$ |                                | 13                                         |                                | mV   |  |

| (                                         | regulation                                        | Voltage at pin SNS, relative to V <sub>CC</sub> for high-side sensing, 0°C $\leq$ T <sub>A</sub> $\leq$ 50°C, V <sub>CC</sub> = 5 V                      | 3                              | 13                                         | 22                             | mV   |  |

| V <sub>RCH</sub> COM                      | PARATOR (Battery R                                | echarge Threshold)                                                                                                                                       | -                              |                                            |                                | -    |  |

| .,                                        | Recharge                                          | bq2057 and bq2057C                                                                                                                                       | VO(REG) <sup>-</sup><br>98 mV  | VO(REG) <sup>_</sup><br>100 mV             | VO(REG) <sup>-</sup><br>102 mV |      |  |

| V(RCH)                                    | threshold                                         | bq2057T and bq2057W                                                                                                                                      | VO(REG) <sup>-</sup><br>196 mV | <sup>V</sup> O(REG) <sup>-</sup><br>200 mV | VO(REG) <sup>-</sup><br>204 mV | V    |  |

| CHARGE-RA                                 | ATE COMPENSATIO                                   | N (AutoComp)                                                                                                                                             | •                              |                                            |                                | •    |  |

|                                           |                                                   | $V_{(BAT)}$ +0.3 V $\leq V_{CC} \leq V_{CC(max)}$ , bq2057, bq2057C, bq2057T, bq2057W                                                                    | 1.87                           | 2.2                                        | 2.53                           |      |  |

| G <sub>(COMP)</sub>                       | AutoComp gain                                     | $V_{(BAT)}$ +0.3 V $\leq~V_{CC} \leq V_{CC(max)}$ , bq2057T and bq2057W in low-side sensing configuration                                                | 2.09                           | 2.4                                        | 2.76                           | V/V  |  |

| STAT PIN                                  |                                                   | ·                                                                                                                                                        |                                |                                            |                                | -    |  |

| VOL(STAT)                                 | Output (low)<br>voltage                           | I <sub>OL</sub> = 10 mA                                                                                                                                  |                                |                                            | 0.7                            |      |  |

| VOH(STAT)                                 | Output (high)<br>voltage                          | I <sub>OH</sub> = 5 mA                                                                                                                                   | V <sub>CC</sub> -0.5           |                                            |                                | V    |  |

| CC PIN                                    |                                                   | ·                                                                                                                                                        | •                              |                                            |                                | ·    |  |

| VOL(CC)                                   | Output low voltage                                | $I_{O(CC)} = 5 \text{ mA} \text{ (sink)}$                                                                                                                |                                |                                            | 1.5                            | V    |  |

| IO(CC)                                    | Sink current                                      | Not to exceed power rating specification (PD)                                                                                                            | 5                              |                                            | 40                             | mA   |  |

SLUS025F - MAY 2001 - REVISED JULY 2002

#### **APPLICATION INFORMATION**

#### functional description

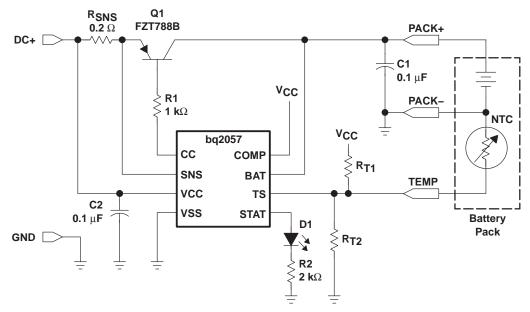

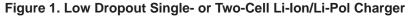

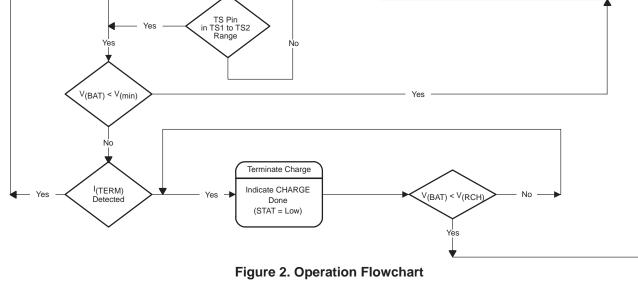

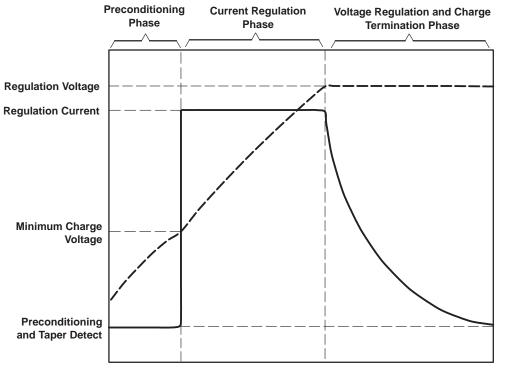

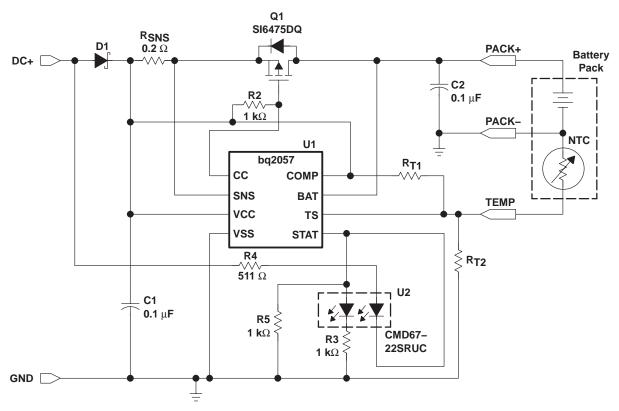

The bq2057 is an advanced linear charge controller for single or two-cell Li-Ion or Li-Pol applications. Figure 1 shows the schematic of charger using a PNP pass transistor. Figure 2 is an operational state diagram, and Figure 3 is a typical charge profile. Figure 4 shows the schematic of a charger using P-channel MOSFET.

SLUS025F - MAY 2001 - REVISED JULY 2002

#### POR k 1 Sleep Mode VCC > V(BAT) Checked at All Indicate SLEEP No MODE Times (STAT = Hi-Z) Yes Suspend Charge TS Pin in TS1 to TS2 Range Indicate CHARGE No SUSPEND (STAT = Hi-Z) Yes Regulate I(PRECHG) V(BAT) < V(min) Indicate Yes Charge In-Progress (STAT = High) Suspend Charge No TS Pin in TS1 to TS2 Range Indicate CHARGE SUSPEND Regulate Current or Voltage (STAT = Hi-Z) Indicate Charge In-Progress Yes (STAT = High) TS Pin in TS1 to TS2 Range Suspend Charge No V(BAT) < V(min)TS Pin in TS1 to TS2 Range No Indicate CHARGE No SUSPEND (STAT = Hi-Z) TS Pin in TS1 to TS2 Range Yes Yės No $V_{(BAT)} < V_{(min)}$ Yes

**APPLICATION INFORMATION**

#### **APPLICATION INFORMATION**

Figure 3. Typical Charge Profile

#### qualification and precharge

When power is applied, the bq2057 starts a charge-cycle if a battery is already present or when a battery is inserted. Charge qualification is based on battery temperature and voltage. The bq2057 suspends charge if the battery temperature is outside the V<sub>(TS1)</sub> to V<sub>(TS2)</sub> range and suspends charge until the battery temperature is within the allowed range. The bq2057 also checks the battery voltage. If the battery voltage is below the precharge threshold V<sub>(min)</sub>, the bq2057 uses precharge to condition the battery. The conditioning charge rate I<sub>(PRECHG)</sub> is set at approximately 10% of the regulation current. The conditioning current also minimizes heat dissipation in the external pass-element during the initial stage of charge. See Figure 3 for a typical charge-profile.

**APPLICATION INFORMATION**

Figure 4. 0.5-A Charger Using P-Channel MOSFET

#### current regulation phase

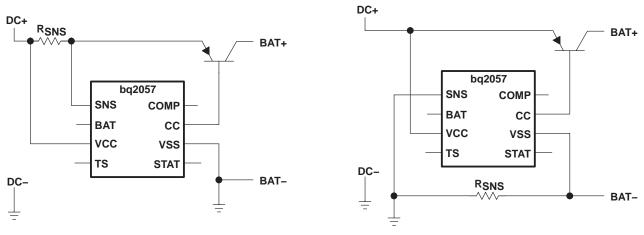

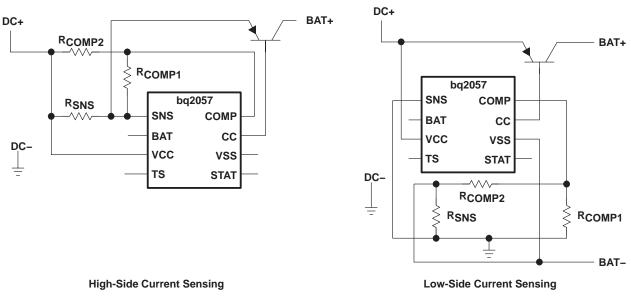

The bq2057 regulates current while the battery-pack voltage is less than the regulation voltage,  $V_{O(REG)}$ . The bq2057 monitors charge current at the SNS input by the voltage drop across a sense-resistor,  $R_{SNS}$ , in series with the battery pack. In high-side current sensing configuration (Figure 5),  $R_{SNS}$  is between the VCC and SNS pins, and in low-side sensing (Figure 6) the  $R_{SNS}$  is between VSS (battery negative) and SNS (charger ground) pins. Charge-current feedback, applied through pin SNS, maintains a voltage of  $V_{(SNS)}$  across the current sense resistor. The following formula calculates the value of the sense resistor:

$$R_{SNS} = \frac{V_{(SNS)}}{I_{O(REG)}}$$

(1)

Where I<sub>O(REG)</sub> is the desired charging current.

SLUS025F - MAY 2001 - REVISED JULY 2002

#### **APPLICATION INFORMATION**

Figure 5. High-Side Current Sensing

#### voltage regulation phase

The voltage regulation feedback is through the BAT pin. This input is tied directly to the positive side of the battery pack. The bq2057 monitors the battery-pack voltage between the BAT and VSS pins. The bq2057 is offered in four fixed-voltage versions: 4.1 V, 4.2 V, 8.2 V and 8.4 V.

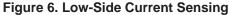

Other regulation voltages can be achieved by adding a voltage divider between the positive and negative terminals of the battery pack and using bq2057T or bq2057W. The voltage divider presents scaled battery-pack voltage to BAT input. (See Figure 7 and Figure 8.) The resistor values RB1 and RB2 for the voltage divider are calculated by the following equation:

$$\frac{R_{B1}}{R_{B2}} = \left(N \times \frac{V(CELL)}{V_{O(REG)}}\right) - 1$$

<sup>(2)</sup>

Where:

N = Number of cells in series

V<sub>(CELL)</sub> = Desired regulation voltage per cell

....

SLUS025F - MAY 2001 - REVISED JULY 2002

### **APPLICATION INFORMATION**

#### charge termination and recharge

The bq2057 monitors the charging current during the voltage-regulation phase. The bq2057 declares a done condition and terminates charge when the current tapers off to the charge termination threshold,  $I_{(TERM)}$ . A new charge cycle begins when the battery voltage falls below the  $V_{(RCH)}$  threshold.

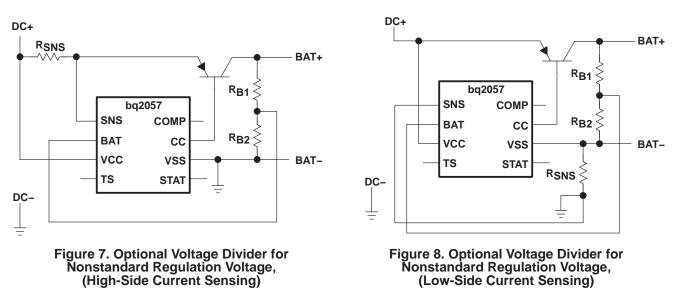

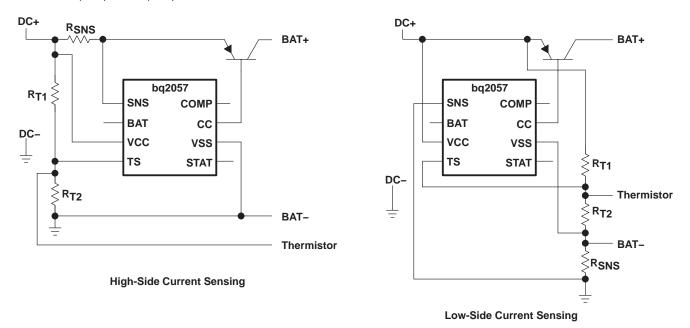

#### battery temperature monitoring

The bq2057 continuously monitors temperature by measuring the voltage between the TS and VSS pins. A negative- or a positive-temperature coefficient thermistor (NTC, PTC) and an external voltage divider typically develop this voltage. (See Figure 9.) The bq2057 compares this voltage against its internal  $V_{(TS1)}$  and  $V_{(TS2)}$  thresholds to determine if charging is allowed. (See Figure 10.) The temperature sensing circuit is immune to any fluctuation in  $V_{CC}$ , since both the external voltage divider and the internal thresholds ( $V_{(TS1)}$  and  $V_{(TS2)}$ ) are referenced to VCC.

The resistor values of  $R_{(T1)}$  and  $R_{(T2)}$  are calculated by the following equations:

For NTC Thermistors

$$R_{T1} = \frac{5 \times R_{TH} \times R_{TC}}{3 \times (R_{TC} - R_{TH})}$$

(3)

$$R_{T2} = \frac{5 \times R_{TH} \times R_{TC}}{\left[ \left( 2 \times R_{TC} \right) - \left( 7 \times R_{TH} \right) \right]}$$

(4)

SLUS025F - MAY 2001 - REVISED JULY 2002

### **APPLICATION INFORMATION**

#### battery temperature monitoring (continued)

For PTC Thermistors

$$R_{T1} = \frac{5 \times R_{TH} \times R_{TC}}{3 \times (R_{TH} - R_{TC})}$$

(5)

$$R_{T2} = \frac{5 \times R_{TH} \times R_{TC}}{\left[ \left( 2 \times R_{TH} \right) - \left( 7 \times R_{TC} \right) \right]}$$

(6)

Where  $R_{(TC)}$  is the cold temperature resistance and  $R_{(TH)}$  is the hot temperature resistance of thermistor, as specified by the thermistor manufacturer.

$R_{T1}$  or  $R_{T2}$  can be omitted If only one temperature (hot or cold) setting is required. Applying a voltage between the  $V_{(TS1)}$  and  $V_{(TS2)}$  thresholds to pin TS disables the temperature-sensing feature.

Figure 9. Temperature Sensing Circuits

Figure 10. bq2057 TS Input Thresholds

### **APPLICATION INFORMATION**

#### charge inhibit function

The TS pin can be used as charge-inhibit input. The user can inhibit charge by connecting the TS pin to VCC or VSS (or any level outside the  $V_{(TS1)}$  to  $V_{(TS2)}$  thresholds). Applying a voltage between the  $V_{(TS1)}$  and  $V_{(TS2)}$  thresholds to pin TS returns the charger to normal operation.

#### charge status indication

The bq2057 reports the status of the charger on the 3-state STAT pin. The following table summarized the operation of the STAT pin.

| CONDITION                         | STAT PIN |

|-----------------------------------|----------|

| Battery conditioning and charging | High     |

| Charge complete (Done)            | Low      |

| Temperature fault or sleep mode   | Hi-Z     |

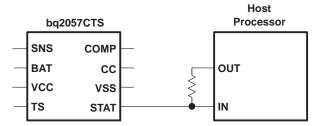

The STAT pin can be used to drive a single LED (Figure 1), dual-chip LEDs (Figure 4) or for interface to a host or system processor (Figure 11). When interfacing the bq2057 to a processor, the user can use an output port, as shown in Figure 11, to recognize the high-Z state of the STAT pin. In this configuration, the user needs to read the input pin, toggle the output port and read the STAT pin again. In a high-Z condition, the input port always matches the signal level on the output port.

Figure 11. Interfacing the bq2057 to a Host Processor

#### low-power sleep mode

The bq2057 enters the sleep mode if the VCC falls below the voltage at the BAT input. This feature prevents draining the battery pack during the absence of VCC.

#### **APPLICATION INFORMATION**

#### selecting an external pass-transistor

The bq2057 is designed to work with both PNP transistor and P-channel MOSFET. The device should be chosen to handle the required power dissipation, given the circuit parameters, PCB layout and heat sink configuration. The following examples illustrate the design process for either device:

#### **PNP** transistor:

Selection steps for a PNP bipolar transistor: Example:  $V_I = 4.5 \text{ V}$ ,  $I_{(REG)} = 1 \text{ A}$ , 4.2-V single-cell Li-Ion (bq2057C).  $V_I$  is the input voltage to the charger and  $I_{(REG)}$  is the desired charge current (see Figure 1).

Determine the maximum power dissipation, P<sub>D</sub>, in the transistor. The worst case power dissipation happens when the cell voltage, V<sub>(BAT)</sub>, is at its lowest (typically 3 V at the beginning of current regulation phase) and V<sub>I</sub> is at its maximum. Where V<sub>CS</sub> is the voltage drop across the current sense resistor.

$$P_{D} = (V_{I} - V_{CS} - V_{(BAT)}) \times IREG$$

$$P_{D} = (4.5 - 0.1 - 3) \times 1 A$$

$$P_{D} = 1.4 W$$

(7)

Determine the package size needed in order to keep the junction temperature below the manufacturer's recommended value, T<sub>(J)max</sub>. Calculate the total theta, θ(°C/W), needed.

$$\theta_{JC} = \frac{\left(T_{(J)max} - T_{A(max)}\right)}{P_{D}}$$

$$\theta_{JC} = \frac{(150-40)}{1.4}$$

$$\theta_{JC} = 78^{\circ}C/W$$

(8)

Now choose a device package with a theta at least 10% below this value to account for additional thetas other than the device. A SOT223 package, for instance, has typically a theta of 60°C/W.

- Select a collector-emitter voltage, V<sub>(CE)</sub>, rating greater than the maximum input voltage. A 15-V device will be adequate in this example.

- 4. Select a device that has at least 50% higher drain current I<sub>C</sub> rating than the desired charge current I<sub>(REG)</sub>.

- 5. Using the following equation, calculate the minimum beta ( $\beta$  or h<sub>FF</sub>) needed:

$$\beta_{\min} = \frac{I_{CMAX}}{I_B}$$

$$\beta_{\min} = \frac{1}{0.035}$$

$$\beta_{\min} = 28$$

where  $I_{max(C)}$  is the maximum collector current (in this case same as  $I_{(REG)}$ ), and  $I_B$  is the base current (chosen to be 35 mA in this example).

#### NOTE:

The beta of a transistor drops off by a factor of 3 over temperature and also drops off with load. Therefore, note the beta of device at  $I_{(REG)}$  and the minimum ambient temperature when choosing the device. This beta should be larger than the minimum required beta.

Now choose a PNP transistor that is rated for  $V_{(CE)} \ge 15 \text{ V}$ ,  $\theta_{JC} \le 78^{\circ}\text{C/W}$ ,  $I_C \ge 1.5 \text{ A}$ ,  $\beta_{min} \ge 28$  and that is in a SOT223 package.

(9)

### **APPLICATION INFORMATION**

#### selecting an external pass-transistor (continued)

#### P-channel MOSFET:

Selection steps for a P-channel MOSFET: Example:  $V_I = 5.5 \text{ V}$ ,  $I_{(REG)} = 500 \text{ mA}$ , 4.2-V single-cell Li–Ion (bq2057C).  $V_I$  is the input voltage to the charger and  $I_{(REG)}$  is the desired charge current. (See Figure 4.)

1. Determine the maximum power dissipation, P<sub>D</sub>, in the transistor.

The worst case power dissipation happens when the cell voltage,  $V_{(BAT)}$ , is at its lowest (typically 3 V at the beginning of current regulation phase) and V<sub>1</sub> is at its maximum.

Where  $V_D$  is the forward voltage drop across the reverse-blocking diode (if one is used), and  $V_{CS}$  is the voltage drop across the current sense resistor.

$$P_{D} = (V_{I} - V_{D} - V_{(CS)} - V_{(BAT)}) \times I_{(REG)}$$

$$P_{D} = (5.5 - 0.4 - 0.1 - 3) \times 0.5 \text{ A}$$

$$P_{D} = 1 \text{ W}$$

(10)

2. Determine the package size needed in order to keep the junction temperature below the manufacturer's recommended value,  $T_{JMAX}$ . Calculate the total theta,  $\theta(^{\circ}C/W)$ , needed.

$$\theta_{JC} = \frac{\left(T_{max}(J)^{-T}A(max)\right)}{P_{D}}$$

$$\theta_{JC} = \frac{(150-40)}{1}$$

$$\theta_{JC} = 110^{\circ}C/W$$

(11)

Now choose a device package with a theta at least 10% below this value to account for additional thetas other than the device. A TSSOP-8 package, for instance, has typically a theta of 70°C/W.

- 3. Select a drain-source voltage, V<sub>(DS)</sub>, rating greater than the maximum input voltage. A 12 V device will be adequate in this example.

- 4. Select a device that has at least 50% higher drain current (I<sub>D</sub>) rating than the desired charge current I<sub>(REG)</sub>.

- 5. Verify that the available drive is large enough to supply the desired charge current.

$$V_{(GS)} = (V_D + V_{(CS)} + V_{OL(CC)}) - V_1$$

$$V_{(GS)} = (0.4 + 0.1 + 1.5) - 5.5$$

$$V_{(GS)} = -3.5$$

(12)

Where  $V_{(GS)}$  is the gate-to-source voltage,  $V_D$  is the forward voltage drop across the reverse-blocking diode (if one is used), and  $V_{CS}$  is the voltage drop across the current sense resistor, and  $V_{OL(CC)}$  is the CC pin output low voltage specification for the bq2057.

Select a MOSFET with gate threshold voltage, V(GSth), rating less than the calculated V(GS).

Now choose a P-channel MOSFET transistor that is rated for VDS  $\leq$  -15 V,  $\theta_{JC} \leq$  110°C/W, I<sub>D</sub>  $\geq$  1 A, V<sub>(GSth)</sub>  $\geq$  -3.5 V and in a TSSOP package.

### **APPLICATION INFORMATION**

#### selecting input capacitor

In most applications, all that is needed is a high-frequency decoupling capacitor. A 0.1  $\mu$ F ceramic, placed in proximity to VCC and VSS pins, works well. The bq2057 works with both regulated and unregulated external dc supplies. If a non-regulated supply is chosen, the supply unit should have enough capacitance to hold up the supply voltage to the minimum required input voltage at maximum load. If not, more capacitance must be added to the input of the charger.

#### selecting output capacitor

The bq2057 does not require any output capacitor for loop stability. The user can add output capacitance in order to control the output voltage when a battery is not present. The charger quickly charges the output capacitor to the regulation voltage, but the output voltage decays slowly, because of the low leakage current on the BAT pin, down to the recharge threshold. Addition of a  $0.1\mu$ F ceramic capacitor, for instance, results in a 100 mV(pp) ripple waveform, with an approximate frequency of 25Hz. Higher capacitor values can be used if a lower frequency is desired.

#### automatic charge-rate compensation

To reduce charging time, the bq2057 uses the proprietary AutoComp technique to compensate safely for internal impedance of the battery pack. The AutoComp feature is disabled by connecting the COMP pin to VCC in high-side current-sensing configuration, and to VSS in low-side current-sensing configuration. The COMP pin must not be left floating.

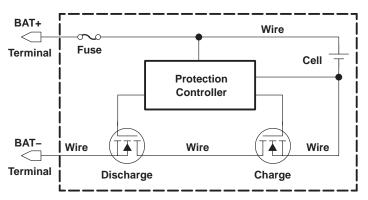

Figure 12 outlines the major components of a single-cell Li-Ion battery pack. The Li-Ion battery pack consists of a cell, protection circuit, fuse, connector, current sense-resistors, and some wiring. Each of these components contains some resistance. Total impedance of the battery pack is the sum of the minimum resistances of all battery-pack components. Using the minimum resistance values reduces the odds for overcompensating. Overcompensating may activate the safety circuit of the battery pack.

Figure 12. Typical Components of a Single-Cell Li-Ion Pack

Compensation is achieved through input pin COMP (Figure 13). A portion of the current-sense voltage, presented through this pin, is scaled by a factor of  $G_{(COMP)}$  and summed with the regulation threshold,  $V_{O(REG)}$ . This process increases the output voltage to compensate for the battery pack's internal impedance and for undesired voltage drops in the circuit.

### **APPLICATION INFORMATION**

#### automatic charge-rate compensation (continued)

AutoComp setup requires the following information:

- Total impedance of battery pack (Z(PACK))

- Maximum charging current (I<sub>(REG)</sub>)

The voltage drop across the internal impedance of battery pack,  $V_{(Z)}$ , can then be calculated using the following equation:

$$V_{(Z)} = Z_{(PACK)} \times I_{(REG)}$$

<sup>(13)</sup>

The required compensation is then calculated using the following equations:

$$V_{(COMP)} = \frac{V_{(Z)}}{G_{(COMP)}}$$

(14)

$$V_{(PACK)} = V_{O(REG)} + (G_{(COMP)} \times V_{(COMP)})$$

Where  $V_{(COMP)}$  is the voltage on COMP pin. This voltage is referenced to VCC in high-side current sensing configuration and to VSS for low-side sensing.  $V_{(PACK)}$  is the voltage across the battery pack.

The values of  $R_{(COMP1)}$  and  $R_{(COMP2)}$  can be calculated using the following equation:

### **APPLICATION INFORMATION**

### automatic charge-rate compensation (continued)

The following example illustrates these calculations:

Assume  $Z_{(PACK)}$  = 100 m $\Omega$ ,  $I_{(REG)}$  = 500 mA, high-side current sensing bq2057C

$$V_{(Z)} = Z_{(PACK)} \times I_{(REG)}$$

(16)

$$V_{(Z)} = 0.1 \times 0.5$$

$$V_{(Z)} = 50 \text{ mV}$$

(17)

$$V_{(COMP)} = \frac{V_{(Z)}}{G_{(COMP)}}$$

(17)

$$V_{(COMP)} = \frac{0.05}{2.2}$$

$$V_{(COMP)} = 22.7 \text{ mV}$$

Let  $R_{COMP2} = 10 \text{ k}\Omega$

$$R_{COMP1} = \frac{R_{COMP2} \times (V_{(SNS)} - V_{(COMP)})}{V_{(COMP)}}$$

(18)

$$R_{COMP1} = 10 \text{k} \times \frac{(105 \text{ mV} - 22.7 \text{ mV})}{22.7 \text{ mV}}$$

(18)

$$R_{COMP1} = 36.25 \text{ k}\Omega$$

Use the closest standard value (36.0 k $\Omega$ ) for R<sub>COMP1</sub>

SLUS025F - MAY 2001 - REVISED JULY 2002

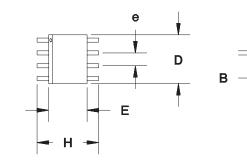

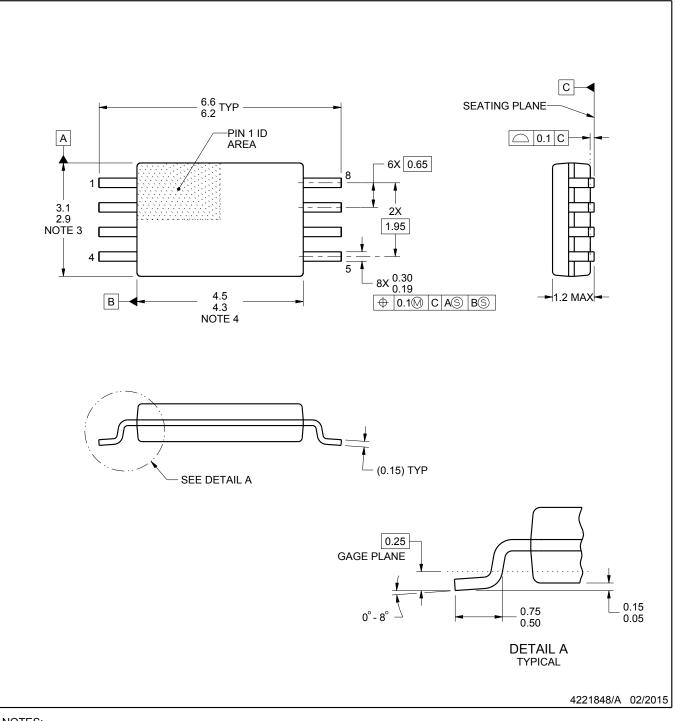

#### **MECHANICAL DATA**

8-Pin SOIC Narrow (SN)

| 8-Pin SN (0.150" SOIC ) |       |       |             |      |  |  |  |  |  |

|-------------------------|-------|-------|-------------|------|--|--|--|--|--|

|                         | Inc   | hes   | Millimeters |      |  |  |  |  |  |

| Dimension               | Min.  | Max.  | Min.        | Max. |  |  |  |  |  |

| А                       | 0.060 | 0.070 | 1.52        | 1.78 |  |  |  |  |  |

| A1                      | 0.004 | 0.010 | 0.10        | 0.25 |  |  |  |  |  |

| В                       | 0.013 | 0.020 | 0.33        | 0.51 |  |  |  |  |  |

| С                       | 0.007 | 0.010 | 0.18        | 0.25 |  |  |  |  |  |

| D                       | 0.185 | 0.200 | 4.70        | 5.08 |  |  |  |  |  |

| Е                       | 0.150 | 0.160 | 3.81        | 4.06 |  |  |  |  |  |

| е                       | 0.045 | 0.055 | 1.14        | 1.40 |  |  |  |  |  |

| Н                       | 0.225 | 0.245 | 5.72        | 6.22 |  |  |  |  |  |

| L                       | 0.015 | 0.035 | 0.38        | 0.89 |  |  |  |  |  |

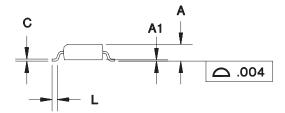

TS: 8-Pin TSSOP

| Dimension | Incl   | nes              | Millimeters |      |  |  |

|-----------|--------|------------------|-------------|------|--|--|

| Dimension | Min.   | Max.             | Min.        | Max. |  |  |

| А         | -      | 0.043            | -           | 1.10 |  |  |

| A1        | 0.002  | 0.006            | 0.05        | 0.15 |  |  |

| В         | 0.007  | 0.012            | 0.18        | 0.30 |  |  |

| C         | 0.004  | 0.007            | 0.09        | 0.18 |  |  |

| D         | 0.114  | 0.122            | 2.90        | 3.10 |  |  |

| Е         | 0.169  | 0.169 0.176 4.30 |             | 4.48 |  |  |

| е         | 0.0256 | BSC              | 0.651       | BSC  |  |  |

| Н         | 0.246  | 0.256            | 6.25        | 6.50 |  |  |

Controlling dimension: millimeters. Inches shown for reference only.

2 'D' and 'E' do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0,15 mm per side 3 Each lead centerline shall be located within ±0,10 mm of its exact true position.

4 Leads shall be coplanar within 0,08 mm at the seating plane.

5 Dimension 'B' does not include dambar protrusion. The dambar protrusion(s) shall not cause the lead width to exceed 'B' maximum by more than 0,08 mm.

6 Dimension applies to the flat section of the lead between 0,10 mm and 0,25 mm from the lead tip.

A1' is defined as the distance from the seating plane to the lowest point of the package body (base plane).

10-Dec-2020

### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| BQ2057CDGK       | ACTIVE        | VSSOP        | DGK                | 8    | 80             | RoHS & Green    | NIPDAUAG                             | Level-2-260C-1 YEAR  | -20 to 70    | 2057C                   | Samples |

| BQ2057CDGKR      | ACTIVE        | VSSOP        | DGK                | 8    | 2500           | RoHS & Green    | NIPDAUAG                             | Level-2-260C-1 YEAR  | -20 to 70    | 2057C                   | Samples |

| BQ2057CDGKRG4    | ACTIVE        | VSSOP        | DGK                | 8    | 2500           | RoHS & Green    | NIPDAUAG                             | Level-2-260C-1 YEAR  | -20 to 70    | 2057C                   | Samples |

| BQ2057CSN        | ACTIVE        | SOIC         | D                  | 8    | 75             | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -20 to 70    | 2057C                   | Samples |

| BQ2057CSNTR      | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -20 to 70    | 2057C                   | Samples |

| BQ2057CTS        | ACTIVE        | TSSOP        | PW                 | 8    | 150            | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -20 to 70    | 2057C                   | Samples |

| BQ2057CTSTR      | ACTIVE        | TSSOP        | PW                 | 8    | 2000           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -20 to 70    | 2057C                   | Samples |

| BQ2057CTSTRG4    | ACTIVE        | TSSOP        | PW                 | 8    | 2000           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -20 to 70    | 2057C                   | Samples |

| BQ2057DGK        | ACTIVE        | VSSOP        | DGK                | 8    | 80             | RoHS & Green    | NIPDAUAG                             | Level-2-260C-1 YEAR  | -20 to 70    | 2057                    | Samples |

| BQ2057SN         | ACTIVE        | SOIC         | D                  | 8    | 75             | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -20 to 70    | 2057                    | Samples |

| BQ2057SNG4       | ACTIVE        | SOIC         | D                  | 8    | 75             | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -20 to 70    | 2057                    | Samples |

| BQ2057TS         | ACTIVE        | TSSOP        | PW                 | 8    | 150            | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -20 to 70    | 2057                    | Samples |

| BQ2057TSN        | ACTIVE        | SOIC         | D                  | 8    | 75             | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -20 to 70    | 2057T                   | Samples |

| BQ2057TTS        | ACTIVE        | TSSOP        | PW                 | 8    | 150            | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -20 to 70    | 2057T                   | Samples |

| BQ2057TTSG4      | ACTIVE        | TSSOP        | PW                 | 8    | 150            | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -20 to 70    | 2057T                   | Samples |

| BQ2057TTSTR      | ACTIVE        | TSSOP        | PW                 | 8    | 2000           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -20 to 70    | 2057T                   | Samples |

| BQ2057TTSTRG4    | ACTIVE        | TSSOP        | PW                 | 8    | 2000           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -20 to 70    | 2057T                   | Samples |

| BQ2057WSN        | ACTIVE        | SOIC         | D                  | 8    | 75             | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -20 to 70    | 2057W                   | Samples |

| BQ2057WSNTR      | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -20 to 70    | 2057W                   | Samples |

| BQ2057WSNTRG4    | ACTIVE        | SOIC         | D                  | 8    | 2500           | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -20 to 70    | 2057W                   | Samples |

10-Dec-2020

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| BQ2057WTS        | ACTIVE        | TSSOP        | PW                 | 8    | 150            | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -20 to 70    | 2057W                   | Samples |

| BQ2057WTSG4      | ACTIVE        | TSSOP        | PW                 | 8    | 150            | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -20 to 70    | 2057W                   | Samples |

| BQ2057WTSTR      | ACTIVE        | TSSOP        | PW                 | 8    | 2000           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -20 to 70    | 2057W                   | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

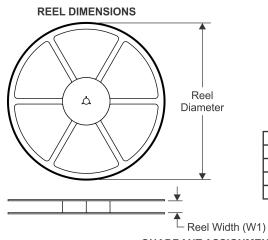

## PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

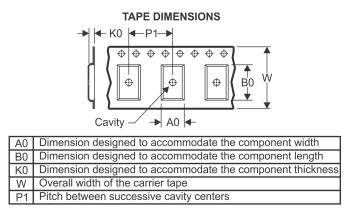

### TAPE AND REEL INFORMATION

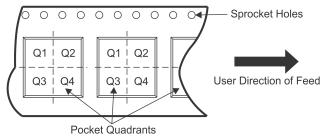

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| BQ2057CDGKR                 | VSSOP           | DGK                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| BQ2057CSNTR                 | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| BQ2057CTSTR                 | TSSOP           | PW                 | 8 | 2000 | 330.0                    | 12.4                     | 7.0        | 3.6        | 1.6        | 8.0        | 12.0      | Q1               |

| BQ2057TTSTR                 | TSSOP           | PW                 | 8 | 2000 | 330.0                    | 12.4                     | 7.0        | 3.6        | 1.6        | 8.0        | 12.0      | Q1               |

| BQ2057WSNTR                 | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| BQ2057WTSTR                 | TSSOP           | PW                 | 8 | 2000 | 330.0                    | 12.4                     | 7.0        | 3.6        | 1.6        | 8.0        | 12.0      | Q1               |

TEXAS INSTRUMENTS

www.ti.com

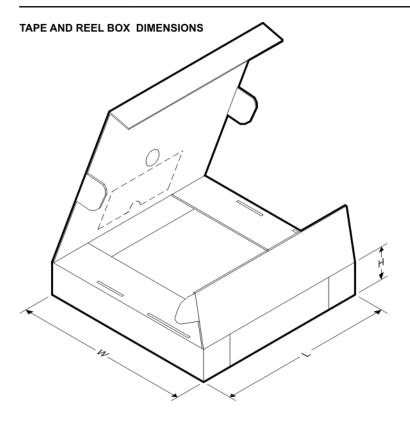

## PACKAGE MATERIALS INFORMATION

11-Jun-2013

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| BQ2057CDGKR | VSSOP        | DGK             | 8    | 2500 | 367.0       | 367.0      | 35.0        |

| BQ2057CSNTR | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

| BQ2057CTSTR | TSSOP        | PW              | 8    | 2000 | 367.0       | 367.0      | 35.0        |

| BQ2057TTSTR | TSSOP        | PW              | 8    | 2000 | 367.0       | 367.0      | 35.0        |

| BQ2057WSNTR | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

| BQ2057WTSTR | TSSOP        | PW              | 8    | 2000 | 367.0       | 367.0      | 35.0        |

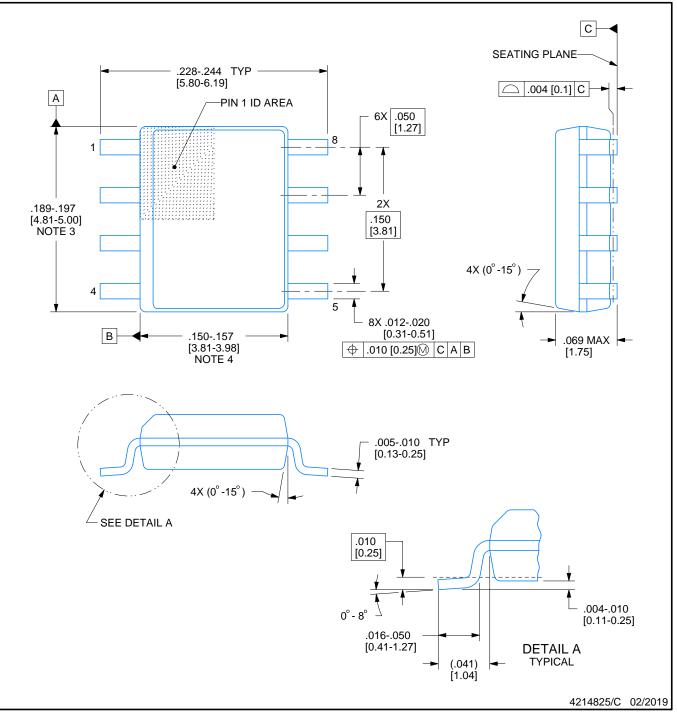

## D0008A

## **PACKAGE OUTLINE**

### SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES:

1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

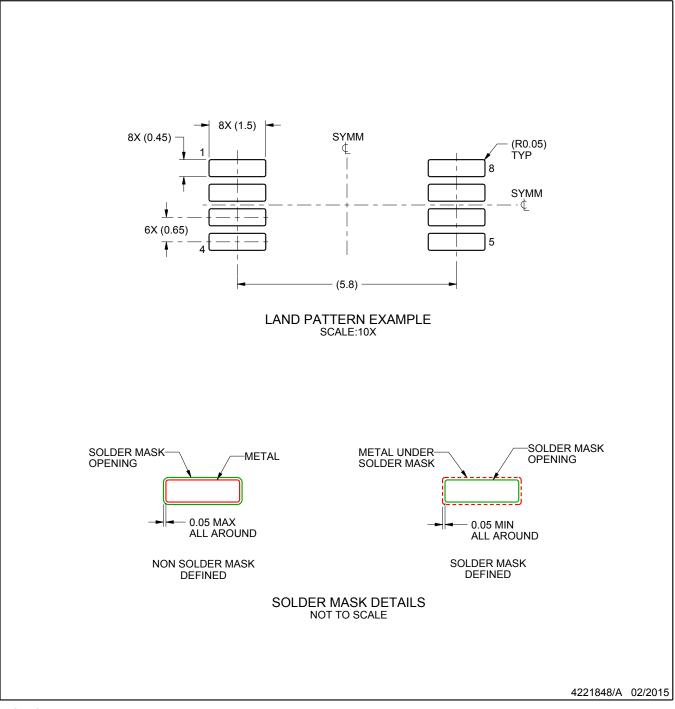

## D0008A

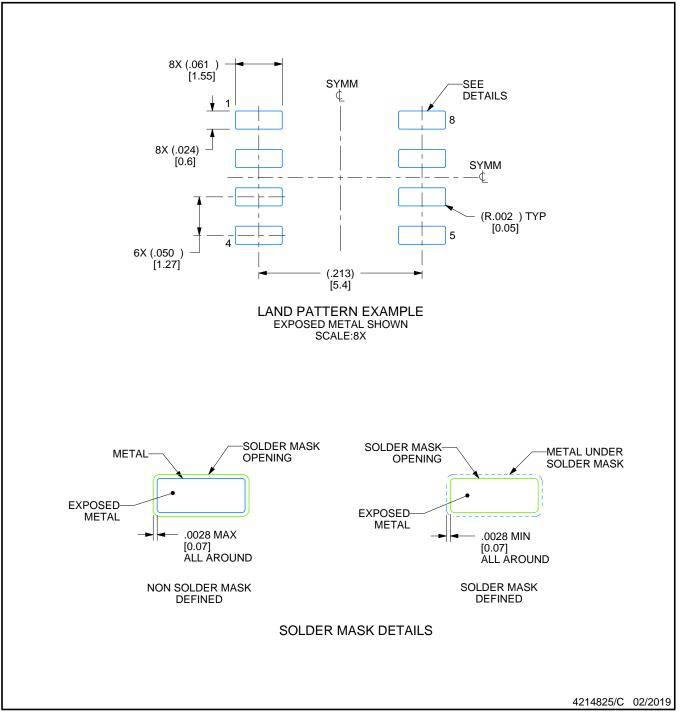

## **EXAMPLE BOARD LAYOUT**

### SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

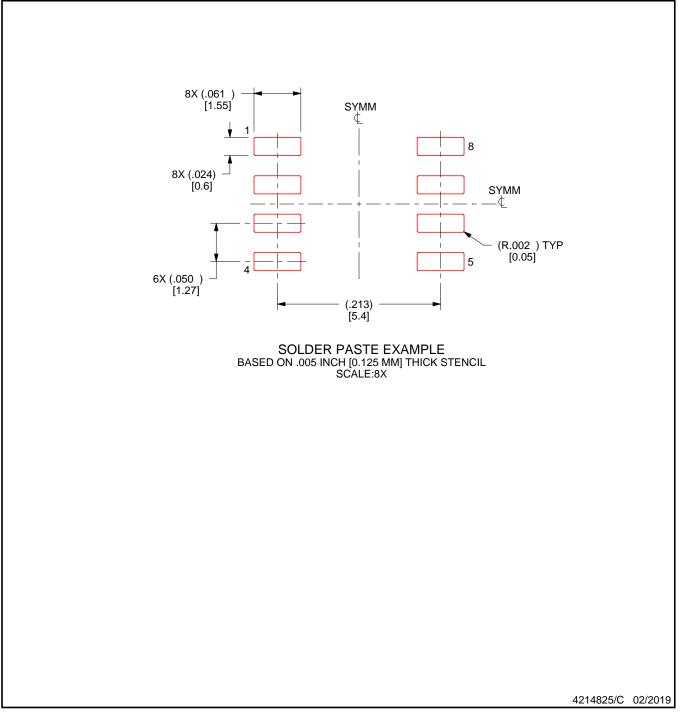

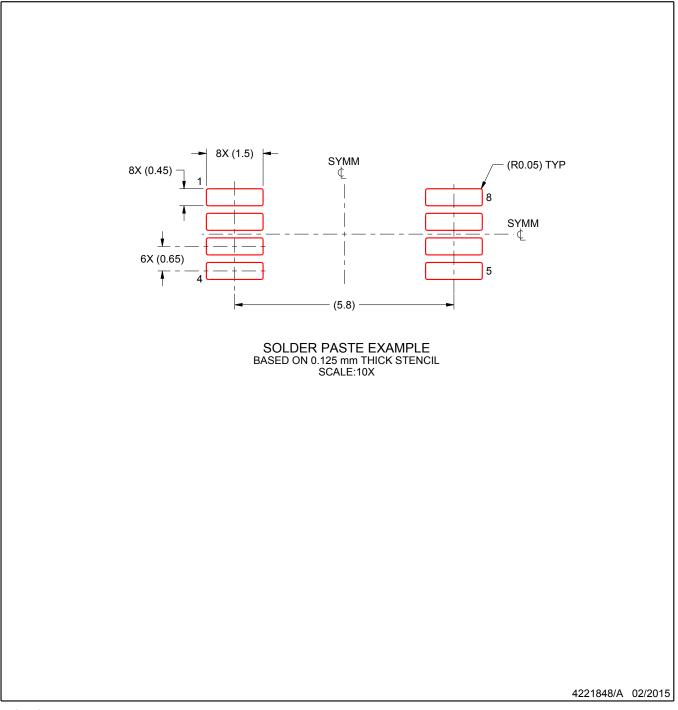

## D0008A

## **EXAMPLE STENCIL DESIGN**

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

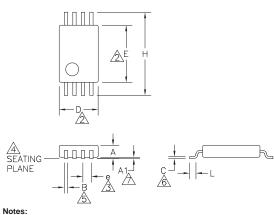

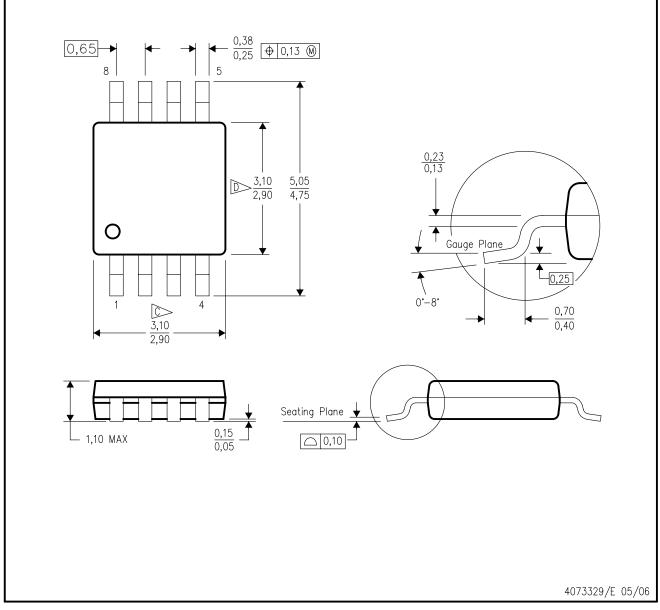

DGK (S-PDSO-G8)

PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 per end.

- D Body width does not include interlead flash. Interlead flash shall not exceed 0.50 per side.

- E. Falls within JEDEC MO-187 variation AA, except interlead flash.

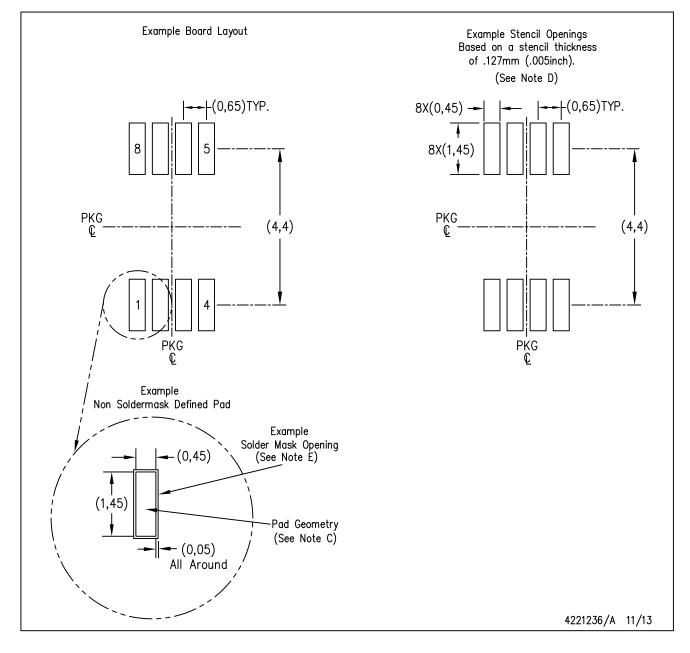

## DGK (S-PDSO-G8)

## PLASTIC SMALL OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

## **PW0008A**

## **PACKAGE OUTLINE**

## TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153, variation AA.

## PW0008A

## **EXAMPLE BOARD LAYOUT**

## TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

## PW0008A

## **EXAMPLE STENCIL DESIGN**

## TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

9. Board assembly site may have different recommendations for stencil design.

<sup>8.</sup> Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated