# Robust, Industrial, Low Power 10BASE-T1L Ethernet PHY

**ADIN1100**

# **Preliminary Technical Data**

## **FEATURES**

10BASE-T1L IEEE<sup>®</sup> Std 802.3cg-2019<sup>™</sup> compliant Supports 1.0 V pk-pk & 2.4 V pk-pk transmit levels **Auto-Negotiation capability** Supports intrinsic safety applications **MII & RMII MAC interfaces** MDIO Management Interface, Clause 45 only Unmanaged configuration using pin strapping including: Master/Slave selection **Transmit amplitude** PHY address 25 MHz crystal oscillator/25 MHz external clock input (50 MHz external clock for RMII) Single supply 1.8 V/3.3 V operation (mode dependent) **EMC test standards** IEC 61000-4-4 electrical fast transient (EFT) (±4 kV) IEC 61000-4-2 ESD (±8 kV contact discharge) IEC 61000-4-2 ESD (±15 kV air discharge) IEC 61000-4-6 conducted immunity (10 V) EN55032 radiated emissions (Class A) **Cable Reach** 1200 meters+ with 1.0 V pk-pk 1200 meters+ with 2.4 V pk-pk Low power consumption Single supply 1 V pk-pk – 45 mW typ Dual supply 1 V pk-pk - 39 mW typ Single supply 2.4 V pk-pk – 109 mW typ Dual supply 2.4 V pk-pk - 81 mW typ Triple supply 2.4 V pk-pk – 75 mW typ 3.3 V/2.5 V/1.8 V MAC interface VDDIO supply Integrated power supply monitoring and POR Diagnostics **Frame Generator and Checker Multiple Loopback Modes IEEE Test Mode Support Cable Diagnostics** Link/Activity LED Small package 40-lead (6 mm x 6 mm) LFCSP Industrial temperature range -40°C to 105°C

### APPLICATIONS

Process Control Factory Automation Building Automation

### **GENERAL DESCRIPTION**

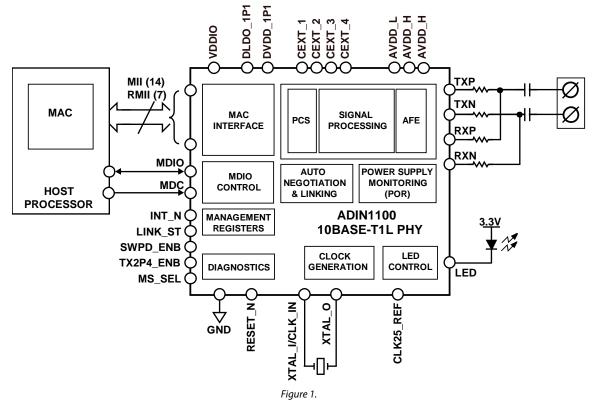

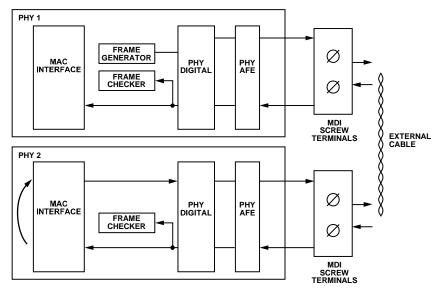

The ADIN1100 is a low power single port 10BASE-T1L transceiver designed for industrial Ethernet applications and is compliant with the IEEE 802.3cg Ethernet standard for long reach 10 Mb/s Single Pair Ethernet. It integrates an Ethernet PHY core with all the associated analog circuitry, input and output clock buffering, the management interface control register and subsystem registers, as well as the MAC interface and control logic to manage the reset and clock control and pin configuration.

The PHY core supports the 1.0 V pk-pk operating mode and the 2.4 V pk-pk operating mode defined in the standard and can operate from a single power supply rail of 1.8V or 3.3V, with the lower voltage option supporting the 1.0 V pk-pk transmit voltage level.

The 1.0 V pk-pk operating mode, external termination resistors and independent Rx/Tx pins make the ADIN1100 suited to intrinsic safety applications.

The ADIN1100 has an integrated voltage supply monitoring circuit and power on reset circuitry to improve system level robustness.

The MDIO interface is a two-wire serial interface for communication between a host processor or MAC and the ADIN1100, thereby allowing access to control and status information in the PHY core management registers. This interface is compatible with IEEE 802.3 Std Clause 45 management frame structures. The MDIO interfaces of microcontrollers that only support IEEE 802.3 Std Clause 22 cannot be used in their default manner with the ADIN1100 MDIO interface. A common alternative is to use two GPIO pins to replicate the IEEE 802.3 Std Clause 45 frame in software.

The ADIN1100 is available in a 6 mm x 6 mm 40-ld package.

#### Rev. PrF

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2020 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# TABLE OF CONTENTS

| Features                                     |

|----------------------------------------------|

| Applications 1                               |

| General Description1                         |

| Functional Block Diagram                     |

| Specifications                               |

| Timing Characteristics                       |

| Power-Up Timing 6                            |

| Management Interface Timing 6                |

| Absolute Maximum Ratings 8                   |

| Thermal Resistance                           |

| ESD Caution                                  |

| Pin Configuration and Function Descriptions9 |

| Theory of Operation12                        |

| Power Supply Domains12                       |

| MAC Interface 12                             |

| Auto-Negotiation                             |

| Management Interface13                       |

| MDI Interface                                |

| Reset Operation14                            |

| Status LED                           | . 14 |

|--------------------------------------|------|

| Powerdown Modes                      | . 15 |

| Hardware Configuration Pins          | . 16 |

| Hardware Configuration Pin Functions | . 16 |

| Bringing Up 10BASE-T1L Links         | . 19 |

| Unmanaged PHY Operation              | . 19 |

| Managed PHY Operation                | . 19 |

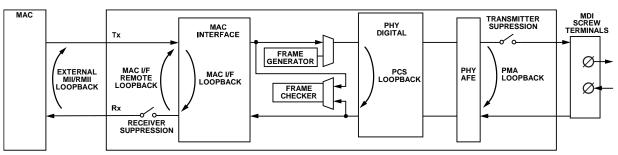

| On-Chip Diagnostics                  | . 22 |

| Loopback Modes                       | . 22 |

| Frame Generator and Checker          | . 23 |

| Applications Information             | . 25 |

| System Level Power Management        | . 25 |

| Component Recommendations            | . 27 |

| Register Summary                     | . 28 |

| Register Details                     | . 30 |

| PCB Layout Recommendations           | . 49 |

| PHY Package Layout                   | . 49 |

| Component Placement                  | . 49 |

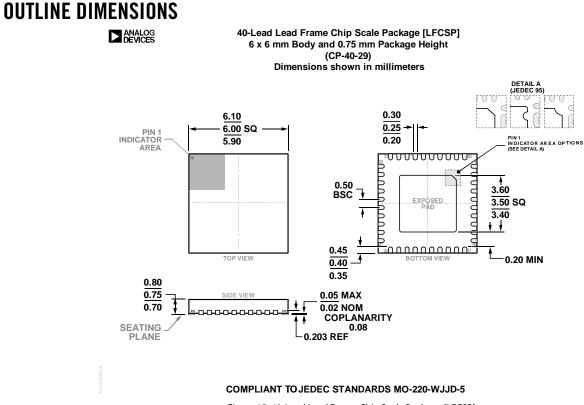

| Outline Dimensions                   | . 50 |

|                                      |      |

# FUNCTIONAL BLOCK DIAGRAM

# **SPECIFICATIONS**

AVDD\_H = AVDD\_L = VDDIO = 3.3 V; DVDD\_1P1 from internal LDO (DVDD\_1P1 = DLDO\_1P1); All specifications at -40°C to +105°C, unless otherwise noted.

Table 1.

| Parameter                                     | Min  | Тур             | Мах  | Unit | <b>Test Conditions/Comments</b>                                              |

|-----------------------------------------------|------|-----------------|------|------|------------------------------------------------------------------------------|

| POWER REQUIREMENTS                            |      |                 |      |      |                                                                              |

| Supply Voltage Range                          |      |                 |      |      |                                                                              |

| AVDD_H                                        | 3.13 | 3.3             | 3.46 | V    | 2.4 V pk-pk or 1.0 V pk-pk Transmit Level                                    |

| AVDD_L                                        | 1.71 | 1.8/3.3         | 3.46 | V    |                                                                              |

| AVDD_H, AVDD_L                                | 1.71 | 1.8             | 3.46 | V    | 1.0 V pk-pk Transmit Level                                                   |

| DVDD_1P1                                      | 1.0  | 1.1             | 1.2  | V    |                                                                              |

| VDDIO                                         | 1.71 | 1.8/2.5<br>/3.3 | 3.46 | V    |                                                                              |

| 1.0 V pk-pk Transmit Level (Single<br>Supply) |      |                 |      |      | AVDD_H = AVDD_L = VDDIO = 1.8 V<br>DVDD_1P1 = DLDO_1P1                       |

| Supply Current, AIDD                          |      | 25              |      | mA   |                                                                              |

| Power Consumption                             |      | 45              |      | mW   | 100% data throughput, full activity                                          |

| 1.0 V pk-pk Transmit Level (Dual<br>Supply)   |      |                 |      |      | AVDD_H = AVDD_L = VDDIO = 1.8 V<br>DVDD_1P1 = External 1.1 V                 |

| Supply Current, AIDD                          |      | 16              |      | mA   |                                                                              |

| Supply Current, DIDD                          |      | 9               |      | mA   |                                                                              |

| Power Consumption                             |      | 39              |      | mW   | 100% data throughput, full activity                                          |

| 2.4 V pk-pk Transmit Level (Single<br>Supply) |      |                 |      |      | AVDD_H = AVDD_L = VDDIO = 3.3 V<br>DVDD_1P1 = DLDO_1P1                       |

| Supply Current, AIDD                          |      | 33              |      | mA   |                                                                              |

| Power Consumption                             |      | 109             |      | mW   | 100% data throughput, full activity                                          |

| 2.4 V pk-pk Transmit Level (Dual<br>Supply)   |      |                 |      |      | AVDD_H = 3.3 V, AVDD_L = VDDIO = 1.8 V<br>DVDD_1P1 = DLDO_1P1                |

| Supply Current, AIDD                          |      | 16.5            |      | mA   |                                                                              |

| Supply Current, IDDIO                         |      | 15              |      | mA   |                                                                              |

| Power Consumption                             |      | 81              |      | mW   | 100% data throughput, full activity                                          |

| 2.4 V pk-pk Transmit Level (Triple<br>Supply) |      |                 |      |      | AVDD_H = 3.3 V, AVDD_L = VDDIO = 1.8 V<br>DVDD_1P1 = External 1.1 V          |

| Supply Current, AIDD                          |      | 16.5            |      | mA   |                                                                              |

| Supply Current, IDDIO                         |      | 6               |      | mA   |                                                                              |

| Supply Current, DIDD                          |      | 9               |      | mA   |                                                                              |

| Power Consumption                             |      | 75              |      | mW   | 100% data throughput, full activity                                          |

| TIMING/LATENCY                                |      |                 |      |      |                                                                              |

| MII Latency                                   |      |                 |      |      |                                                                              |

| TX Latency                                    |      | <3.2            |      | μs   | 32 bit frames                                                                |

| RX Latency                                    |      | <6.4            |      | μs   | 64 bit frames                                                                |

| Total Latency                                 |      | ≤9.6            |      | μs   |                                                                              |

| DIGITAL INPUTS/OUTPUTS                        |      |                 |      |      | Applies to MAC interface pins, MDC, MDIO,<br>INT_N, LINK_ST, RESET_N and LED |

| VDDIO = 3.3 V                                 |      |                 |      |      |                                                                              |

| Input Low Voltage (V <sub>IL</sub> )          |      |                 | 0.8  | V    |                                                                              |

| Input High Voltage (V <sub>IH</sub> )         | 2.0  |                 |      | V    |                                                                              |

| Output Low Voltage (V <sub>OL</sub> )         |      |                 | 0.4  | V    | Output low current ( $I_{OL}$ ) (min) = 4 mA                                 |

| Output High Voltage (V <sub>OH</sub> )        | 2.4  |                 |      | V    | Output high current ( $I_{OH}$ ) (min) = 4 mA                                |

| VDDIO = 2.5 V                                 |      |                 |      |      |                                                                              |

| VIL                                           |      |                 | 0.7  | V    |                                                                              |

| V <sub>IH</sub>                               | 1.7  |                 |      | V    |                                                                              |

| Vol                                           |      |                 | 0.4  | V    | $I_{OL}$ (min) = 4 mA                                                        |

| V <sub>OH</sub>                               | 2.0  |                 |      | V    | $I_{OH}$ (min) = 4 mA                                                        |

# **Preliminary Technical Data**

| Parameter                          | Min   | Тур  | Max   | Unit   | Test Conditions/Comments                                                  |

|------------------------------------|-------|------|-------|--------|---------------------------------------------------------------------------|

| VDDIO = 1.8 V                      |       |      |       |        |                                                                           |

| V <sub>IL</sub>                    |       |      | 0.3 × | V      |                                                                           |

|                                    |       |      | VDDIO |        |                                                                           |

| V <sub>IH</sub>                    | 0.7 × |      |       | V      |                                                                           |

|                                    | VDDIO |      |       |        |                                                                           |

| Vol                                |       |      | 0.2×  | V      | $I_{OL}$ (min) = 4 mA                                                     |

| M                                  | 0.8×  |      | VDDIO | v      |                                                                           |

| V <sub>он</sub>                    | VDDIO |      |       | v      | $I_{OH}$ (min) = 4 mA                                                     |

| RESET_N deglitch time              | 0.3   | 0.5  | 1     | μs     |                                                                           |

| LED OUTPUT                         |       |      |       |        |                                                                           |

| Output Drive Current               | 8     |      |       | mA     | VDDIO = 3.3 V                                                             |

|                                    | 6     |      |       | mA     | VDDIO = 2.5 V                                                             |

|                                    | 4     |      |       | mA     | VDDIO = 1.8 V                                                             |

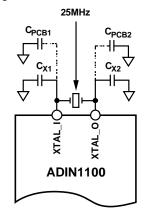

| CLOCKS                             |       |      |       |        |                                                                           |

| External Crystal (XTAL)            |       |      |       |        | Requirements for external crystal used on                                 |

|                                    |       |      |       |        | XTAL_I pin and XTAL_O pin                                                 |

| Crystal Frequency                  |       | 25   |       | MHz    |                                                                           |

| Crystal Frequency Tolerance        | -30   |      | +30   | ppm    |                                                                           |

| Crystal Drive Level                |       | <200 |       | μW     |                                                                           |

| Crystal ESR                        |       |      | 60    | Ω      |                                                                           |

| XTAL_I, XTAL_O C <sub>in,eq</sub>  |       | 1.5  |       | pF     | Equivalent parallel differential input capacitance looking into XTAL pins |

| Crystal Load Capacitance $(C_L)^1$ |       | 10   | 18    | pF     | Including PCB trace capacitance and XTAL_I,<br>XTAL_O C <sub>ineq</sub>   |

| XTAL_I Jitter                      |       | 2    | TBD   | ps     | Absolute rms jitter, frequency range 1 kHz to 12.5 MHz                    |

| Start-up Time                      |       |      | 2     | ms     | Crystal Oscillator Only                                                   |

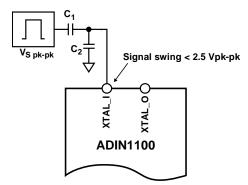

| Clock Input (CLK_IN)               |       |      |       |        |                                                                           |

| Clock Input Frequency              |       | 25   |       | MHz    | Requirements for external clock applied to XTAL_I pin, MII mode           |

|                                    |       | 50   |       | MHz    | RMII mode                                                                 |

| Clock Input Voltage Range          | 0.8   |      | 2.5   | Vp-p   | AC-coupled sine or square wave at XTAL_I pin                              |

| Clock Input Duty Cycle             | 45    |      | 55    | %      |                                                                           |

| XTAL_I Z <sub>in,eq</sub>          |       |      |       |        |                                                                           |

| R <sub>p</sub>                     |       | 6    |       | kΩ     | R <sub>p</sub>   C <sub>p</sub>                                           |

| Cp                                 |       | 3    |       | pF     |                                                                           |

| Jitter                             |       |      | TBD   | ps rms |                                                                           |

| CLK25_REF clock output             |       |      |       |        |                                                                           |

| CLK25_REF Frequency                |       | 25   |       | MHz    |                                                                           |

| Vон                                |       | 1.05 |       | V      | Load 10pF                                                                 |

| Vol                                |       | 0    |       | V      | Load 10pF                                                                 |

| CLK25_REF Duty Cycle               | 45    |      | 55    | %      | Load 10pF                                                                 |

<sup>1</sup> Where load capacitance ( $C_L$ ) = (( $C1 \times C2$ )/(C1 + C2) +  $C_{STRAY}$ ), where  $C_{STRAY}$  is the stray capacitance including routing and package parasitics.

# TIMING CHARACTERISTICS

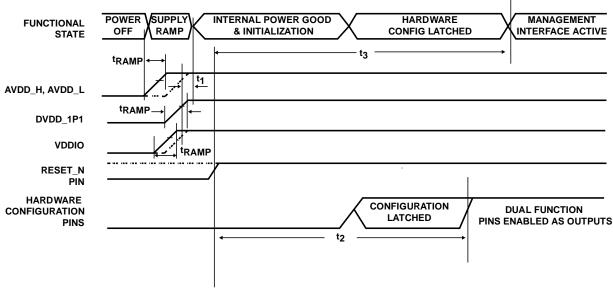

## **POWER-UP TIMING**

#### Table 2. Power Up Timing

| Parameter | Description                                               | Min | Тур | Max | Unit |

|-----------|-----------------------------------------------------------|-----|-----|-----|------|

| tramp     | Power supply ramp time                                    |     |     | 40  | ms   |

| t1        | Minimum time interval to internal power good <sup>1</sup> | 20  |     | 43  | ms   |

| t2        | Hardware configuration latch time                         | 6   | 8   | 14  | μs   |

| t3        | Management interface active                               |     |     | 50  | ms   |

<sup>1</sup> The minimum time interval is referenced to the last supply to reach its rising threshold. There is no specific power supply sequencing required.

Figure 2. Power-Up Timing

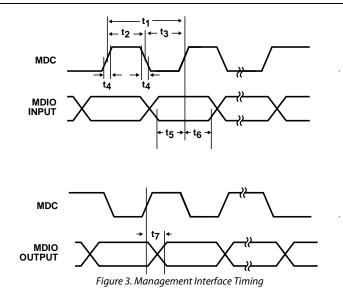

## MANAGEMENT INTERFACE TIMING

Table 3. Management Interface Timing

| Parameter Description |                               | Min | Тур | Max | Unit |

|-----------------------|-------------------------------|-----|-----|-----|------|

| t1                    | MDC period                    | 400 |     |     | ns   |

| t2                    | MDC high time                 | 100 |     |     | ns   |

| t3                    | MDC low time                  | 100 |     |     | ns   |

| t4                    | MDC rise/fall time            |     |     | 5   | ns   |

| t5                    | MDIO signal setup time to MDC | 10  |     |     | ns   |

| t6                    | MDIO signal hold time to MDC  | 10  |     |     | ns   |

| t7                    | MDIO delay time to MDC        |     |     | 300 | ns   |

# **Preliminary Technical Data**

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 4.

| Parameter                                     | Rating                        |

|-----------------------------------------------|-------------------------------|

| VDDIO to GND                                  | –0.3 V to +4 V                |

| DVDD_1P1, DLDO_1P1 to GND                     | –0.3 V to +1.35 V             |

| AVDD_H, AVDD_L to GND                         | –0.3 V to +4 V                |

| MAC Interface, MDIO, MDC, INT_N<br>to GND     | –0.3 V to VDDIO + 0.3 V       |

| TXN, TXP, RXN, RXP to GND                     | -0.3 V to AVDD + 0.3 V        |

| LED, RESET_N, LINK_ST to GND                  | -0.3 V to VDDIO + 0.3 V       |

| XTAL_I/CLK_IN to GND                          | –0.3 V to 2.75 V              |

| XTAL_O, CLK25_REF to GND                      | –0.3 V to 1.35 V              |

| Operating Temperature Range (T <sub>A</sub> ) |                               |

| Industrial                                    | -40°C to +105°C               |

| Storage Temperature Range                     | –65°C to +150°C               |

| Junction Temperature (TJ max)                 | 125°C                         |

| Power Dissipation                             | $(T_J max - T_A)/\Theta_{JA}$ |

| Lead Temperature                              | JEDEC industry standard       |

| Soldering                                     | J-STD-020                     |

| ESD                                           |                               |

| Human Body Model (HBM)                        |                               |

| TXN, TXP, RXN, RXP Pins                       | 4kV                           |

| All Other Pins                                | 2 kV                          |

| Machine Model (MM)                            | 200V                          |

| Field Induced Charged                         | 1.25 kV                       |

| Device Model (FICDM)                          |                               |

|                                               |                               |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

#### Table 5. Thermal Resistance

| Package Type | Αιθ | Unit |

|--------------|-----|------|

| CP-40-29     | TBD | °C/W |

Test Condition 1: thermal impedance simulated values are based on a JEDEC 2S2P thermal test board with thermal vias. See JEDEC JESD51.

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

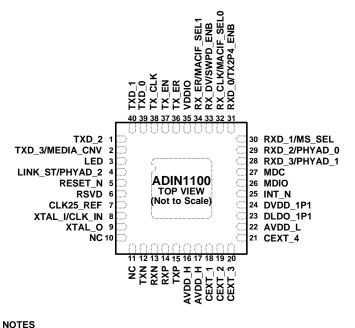

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

1. EXPOSED PAD. THE LFCSP HAS AN EXPOSED PAD THAT MUST BE SOLDERED TO A METAL PLATE ON THE PCB FOR MECHANICAL REASONS AND TO GND.

Figure 4.

Table 6. Pin Function Descriptions (hardware pin configuration groupings are subject to change)

| Pin No.   | Mnemonic <sup>1</sup>       | Description                                                                                                                                                                                        |  |

|-----------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CLOCK INT | TERFACE                     | ·                                                                                                                                                                                                  |  |

| 8         | XTAL_I/CLK_IN               | Input for crystal/single ended 25 MHz reference clock or 50 MHz clock input for RMII.                                                                                                              |  |

| 9         | XTAL_O                      | Crystal output. If using a single ended reference clock on XTAL_I/CLK_IN, leave XTAL_O open circuit. See External Clock Input section.                                                             |  |

| 7         | CLK25_REF                   | Analog reference clock output. The 25 MHz reference clock from the crystal oscillator is available on the CLK25_REF pin. This can be used as an input to another PHY.                              |  |

| MANAGEN   | MENT INTERFACE              |                                                                                                                                                                                                    |  |

| 26        | MDIO                        | Management Data Input/Output synchronous to the MDC clock. This pin is open-drain and requires a 1.5 k $\Omega$ pull-up resistor to VDDIO.                                                         |  |

| 27        | MDC                         | Management Data Clock input up to 2.5 MHz.                                                                                                                                                         |  |

| 25        | INT_N                       | Management interface interrupt pin output. Open drain, active low output. A low on INT_N indicates an unmasked management interrupt. This pin requires a 1.5 k $\Omega$ pull-up resistor to VDDIO. |  |

| RESET     |                             |                                                                                                                                                                                                    |  |

| 5         | RESET_N                     | Active low input. Hold low for >10 $\mu$ s. See Hardware Reset section. RESET_N does not require a pull-up resistor as there is an internal pull-up already in place.                              |  |

| MEDIA DE  | PENDENT INTERFACE (MDI)     | ·                                                                                                                                                                                                  |  |

| 15        | ТХР                         | Transmit Positive pin.                                                                                                                                                                             |  |

| 12        | TXN                         | Transmit Negative pin.                                                                                                                                                                             |  |

| 14        | RXP                         | Receive Positive pin.                                                                                                                                                                              |  |

| 13        | RXN                         | Receive Negative pin.                                                                                                                                                                              |  |

| MAC INTE  | RFACE                       |                                                                                                                                                                                                    |  |

| 28        | RXD_3/ PHYAD_1 <sup>2</sup> | RXD_3: MII Receive Data 3 output. See the MAC Interface section.                                                                                                                                   |  |

|           |                             | PHYAD_1: PHY Address hardware configuration pin.                                                                                                                                                   |  |

| Pin No.  | Mnemonic <sup>1</sup>          | Description                                                                                                                                                                                                                                                                                                                                                  |

|----------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29       | RXD_2/PHYAD_0 <sup>2</sup>     | RXD_2: MII Receive Data 2 output. See the MAC Interface section.                                                                                                                                                                                                                                                                                             |

|          |                                | PHYAD_0: PHY Address hardware configuration pin.                                                                                                                                                                                                                                                                                                             |

| 30       | RXD_1/ MS_SEL <sup>2</sup>     | RXD_1: RMII/MII Receive Data 1 output. See the MAC Interface section.                                                                                                                                                                                                                                                                                        |

|          |                                | MS_SEL: Master/Slave Selection. Set high for prefer master selection, low for prefer slave selection. See Table 9.                                                                                                                                                                                                                                           |

| 31       | RXD_0/TX2P4_ENB <sup>2</sup>   | RXD_0: RMII/MII Receive Data 0 output. See the MAC Interface section.                                                                                                                                                                                                                                                                                        |

|          |                                | TX2P4_ENB: Transmit Level Amplitude hardware configuration pin. Set high for 1 V pk-pk transmit amplitude, low supports both 1 V pk-pk and 2.4 V pk-pk transmit amplitude. See Table 10.                                                                                                                                                                     |

| 32       | RX_CLK/MACIF_SEL0 <sup>2</sup> | RX_CLK: 2.5 MHz MII Receive Clock output.                                                                                                                                                                                                                                                                                                                    |

|          |                                | MACIF_SEL0: MAC Interface Selection hardware configuration pin. See Table 11.                                                                                                                                                                                                                                                                                |

| 33       | RX_DV/SWPD_ENB <sup>2</sup>    | RX_DV: RMII/MII mode Received Data Valid output. This signal is known as CRS_DV in RMII mode. When asserted high, it indicates valid data is present on the RXD_x pins.                                                                                                                                                                                      |

|          |                                | SWPD_ENB: Software Powerdown Configuration. Set low to configure PHY to enter software powerdown mode after power-up/reset. See Table 8.                                                                                                                                                                                                                     |

| 34       | RX_ER/MACIF_SEL1 <sup>2</sup>  | RX_ER: RMII/MII mode Receive Error detected output. When asserted high, it indicates that the PHY has detected a receive error.                                                                                                                                                                                                                              |

|          |                                | MACIF_SEL1: MAC Interface Selection hardware configuration pin. See Table 11.                                                                                                                                                                                                                                                                                |

| 36       | TX_ER                          | RMII/MII mode Transmit Error detected input from the MAC to the PHY.                                                                                                                                                                                                                                                                                         |

| 37       | TX_EN                          | RMII/MII mode Transmit Enable input from the MAC to the PHY, indicating that transmission data is available on the TXD_x lines.                                                                                                                                                                                                                              |

| 38       | TX_CLK                         | 2.5 MHz MII Transmit Clock output.                                                                                                                                                                                                                                                                                                                           |

| 2        | TXD_3/MEDIA_CNV <sup>2</sup>   | TXD_3: MII Transmit Data 3 input. See the MAC Interface section.                                                                                                                                                                                                                                                                                             |

|          |                                | MEDIA_CNV: Media Convertor hardware configuration pin.                                                                                                                                                                                                                                                                                                       |

| 1        | TXD_2                          | MII Transmit Data 2 input. See the MAC Interface section.                                                                                                                                                                                                                                                                                                    |

| 40       | TXD_1                          | RMII/MII Transmit Data 1 input. See the MAC Interface section.                                                                                                                                                                                                                                                                                               |

| 39       | TXD_0                          | RMII/MII Transmit Data 0 input. See the MAC Interface section.                                                                                                                                                                                                                                                                                               |

| STATUS   |                                |                                                                                                                                                                                                                                                                                                                                                              |

| 4        | LINK_ST/PHYAD_2 <sup>2</sup>   | LINK_ST: Link Status output to indicate whether a valid link has been established. LINK_ST is active high.                                                                                                                                                                                                                                                   |

|          |                                | PHYAD_2: PHY Address hardware configuration pin.                                                                                                                                                                                                                                                                                                             |

| 3        | LED                            | LED: Programmable LED indicator for general purpose LED. The LED is active low. By default, LED is disabled but a common configuration (configured over MDIO) is for the LED to turn on when a link is established and blink when there is activity. See the LED Link/Activity section.                                                                      |

| LDO AND  | REFERENCE DECOUPLING           |                                                                                                                                                                                                                                                                                                                                                              |

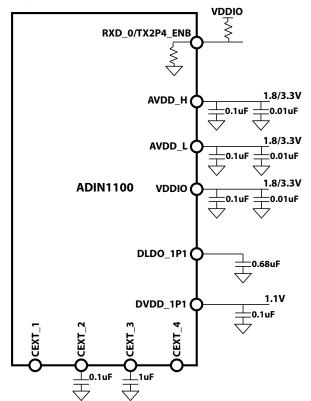

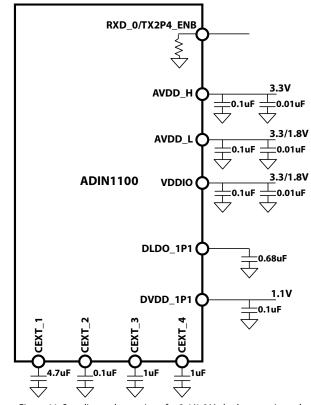

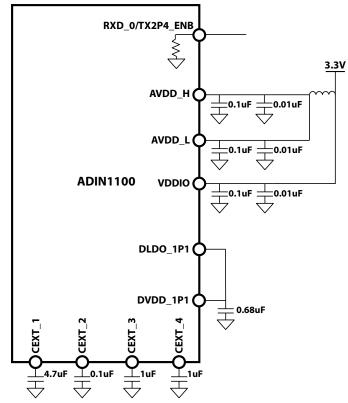

| 18       | CEXT_1                         | External decoupling for reference used in analog circuit. Connect a 4.7 µF cap to ground as close as possible to this pin. When TX2P4_ENB has been set to allow 1 V pk-pk transmission mode only, this capacitor is not required. (See System Level Power Management for more information). Do not use this pin as a voltage source for an external circuit. |

| 19       | CEXT_2                         | External decoupling for LDO circuit. Connect a 0.1 $\mu$ F cap to ground as close as possible to this pin. Do not use this pin as a voltage source for an external circuit.                                                                                                                                                                                  |

| 20       | CEXT_3                         | External decoupling for LDO circuit. Connect a 1 µF cap to ground as close as possible to this pin. Do not use this pin as a voltage source for an external circuit.                                                                                                                                                                                         |

| 21       | CEXT_4                         | External decoupling for LDO circuit. Connect a 1 µF cap to ground as close as possible to this pin. When TX2P4_ENB has been set to allow 1 V pk-pk transmission mode only, this capacitor is not required. (See System Level Power Management for more information). Do not use this pin as a voltage source for an external circuit.                        |

| POWER AI | ND GROUND PINS                 |                                                                                                                                                                                                                                                                                                                                                              |

| 16, 17   | AVDD_H                         | Analog supply voltage for the various analog circuits in the device. This supply rail can be supplied by 1.8 V to 3.3 V depending on the transmit level configuration. If AVDD_H is 3.3 V both 1.0 V pk-pk and 2.4 V pk-pk transmit operating modes are supported. If AVDD_H is 1.8                                                                          |

# **Preliminary Technical Data**

| Pin No.  | Mnemonic <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                       | V only 1.0 V pk-pk transmit operating mode is supported. Connect 0.1 $\mu$ F and 0.01 $\mu$ F capacitors to GND as close as possible to this pin.                                                                                                                                                                                                                                     |

| 22       | AVDD_L                | Analog supply voltage for the internal LDOs. This supply rail can be supplied by 1.8 V to 3.3 V. It could be connected direct to the AVDD_H rail in long reach applications or alternatively to the VDDIO rail when the device is configured with dual supplies for lower power consumption. Connect 0.1 $\mu$ F and 0.01 $\mu$ F capacitors to GND as close as possible to this pin. |

| 35       | VDDIO                 | $3.3$ V/2.5 V/1.8 V digital power for MDIO and MAC interface. Connect 0.1 $\mu$ F and 0.01 $\mu$ F capacitors to GND as close as possible to the pin.                                                                                                                                                                                                                                 |

| 24       | DVDD_1P1              | Input pin for 1.1 V DVDD_1P1 supply rail. When using the internal LDO, connect this pin directly to the DLDO_1P1 pin. Alternatively, an external 1.1 V rail can be provided to the DVDD_1P1 pin for greater power efficiency. Connect a 0.1 µF to ground as close as possible to this pin.                                                                                            |

| 23       | DLDO_1P1              | Output from an internal 1.1V LDO. This pin can be connected to DVDD_1P1 to eliminate an additional power supply rail. Connect a 0.68 $\mu$ F cap to ground as close as possible to this pin.                                                                                                                                                                                          |

| 6        | RSVD                  | Reserved. This pin must be connected to GND.                                                                                                                                                                                                                                                                                                                                          |

|          | EP                    | Exposed Pad. This is GND Paddle and needs to be connected to GND. The LFCSP package has an exposed pad that needs to be connected to GND for electrical reasons and must be soldered to a metal plate on the PCB for mechanical reasons. A 4 × 4 array of thermal vias beneath the exposed GND pad is also recommended.                                                               |

| OTHER PI | NS                    |                                                                                                                                                                                                                                                                                                                                                                                       |

| 10, 11   | NC                    | No connect. These pins must be left open-circuit.                                                                                                                                                                                                                                                                                                                                     |

<sup>1</sup> Where a pin is shared between a functional signal and a hardware pin configuration, the hardware pin configuration signal is listed last and the pin will be referred to using the functional signal(s) name throughout the datasheet.

$^{2}$  All of the hardware configuration pins have internal pull-down resistors. The default mode of operation without any external resistors connected to these pins is captured in Table 7. If an alternative mode of operation is required, 4.7 k $\Omega$  pull-up resistors should be used.

# THEORY OF OPERATION

The ADIN1100 is a low power single port 10 Mb/s long reach single pair Ethernet PHY (10BASE-T1L). It is compliant with the IEEE 802.3cg Ethernet standard for long reach 10 Mb/s Single Pair Ethernet.

It integrates a PHY core with all the associated common analog circuitry, input and output clock buffering, the management interface and subsystem registers as well as the MAC interface and control logic to manage the reset and clock control and hardware pin configuration. The ADIN1100 is available in a 40-ld LFCSP package.

## POWER SUPPLY DOMAINS

The ADIN1100 has three power supply domains and requires a minimum of one supply rail.

- AVDD\_H is the analog power supply input for the analog front end (AFE) circuitry in the ADIN1100.

- AVDD\_L is the analog supply voltage for the internal LDOs. It can be connected to the AVDD\_H rail when in single supply mode, or to an alternative lower voltage rail when the device is configured with dual supplies for lower power consumption.

- DVDD\_1P1 is the 1.1 V digital core power supply input, it can operate from an internal 1.1 V LDO coming from the DLDO\_1P1 pin to the DVDD\_1P1 pin. Alternatively, it can be driven from an external 1.1 V supply for greater power efficiency.

- VDDIO enables the MDIO and MAC interface voltage supply to be configured independently of the other circuitry on the ADIN1100. It can be connected directly to the AVDD\_L rail.

In a single supply application, connect AVDD\_H = AVDD\_L = VDDIO and use the internal 1.1 V LDO for DVDD\_1P1. The appropriate supply voltage used will depend on the end application and cable length. For long reach/trunk applications the higher transmit amplitude of 2.4 V pk-pk requires AVDD\_H = 3.3 V whereas spur applications can use a lower transmit amplitude of 1.0 V pk-pk with an AVDD\_H = 1.8 V.

## **MAC INTERFACE**

The ADIN1100 provides the option of MII or RMII MAC interfaces. The MAC interface is selected using hardware configuration pins (MACIF\_SEL0/1) or via software.

## **MII Interface Mode**

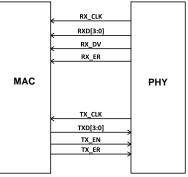

For the RX interface, the ADIN1100 generates a 2.5 MHz RX\_CLK signal to synchronize the RXD[3:0] receive data. RX\_DV indicates to the MAC that there is valid data present on RXD[3:0]. RX\_ER is driven high by the ADIN1100 if an error was detected in the frame that was received from the MDI interface and is being transmitted to the MAC.

Figure 5. MII MAC-PHY Interface Signals

For the TX interface, the PHY generates a 2.5 MHz reference clock on TX\_CLK. The MAC transmits data on TXD[3:0] that is synchronized with TX\_CLK. The MAC asserts TX\_EN to indicate to the ADIN1100 that transmission data is available on the TXD[3:0] lines.

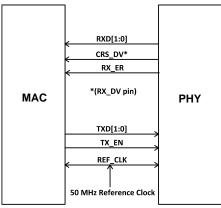

### **RMII Interface Mode**

RMII mode requires an external 50 MHz clock, which can be sourced from the MAC or an external clock and applied to the XTAL\_I/CLK\_IN pin for both the TX and RX interfaces. The RMII interface should only be selected from hardware configuration. As RMII mode requires a 50 MHz reference clock, software should not be used to configure the MAC interface to RMII.

Figure 6. RMII MAC-PHY Interface Signals

The receive data, RXD[1:0], transitions synchronously to the reference clock, REF\_CLK. The Carrier sense/Received data valid signal - CRS\_DV - is a combination of the CRS and RX\_DV signals and is asserted while the receive medium is non-idle. It is asserted asynchronously to REF\_CLK and de-asserted synchronously. RX\_ER is also synchronous to REF\_CLK and asserted when an error is detected in the received frame or when a false carrier is detected. RX\_ER assertion on false carrier can be disabled by software.

# **AUTO-NEGOTIATION**

The ADIN1100 uses Auto-Negotiation capability in accordance with IEEE 802.3 Clause 98, providing a mechanism for exchanging information between PHYs to allow link partners to agree to a common mode of operation. During the Auto-Negotiation process, the PHY advertises its own capabilities and compares to those received from the link partner. The concluded operating mode is the transmit amplitude mode and master/slave preference common across the two devices.

In the event of the link being dropped, the Auto-Negotiation process restarts automatically. Auto-Negotiation can be restarted by request through a write to the Auto-Negotiation restart bit (AN\_RESTART) in the Auto-Negotiation control register (AN\_CONTROL, device address 0x07, register address 0x0200, bit 9).

The Auto-Negotiation process takes some time to complete, depending on the number of pages exchanged, but is always the fastest way to bring up a link. Clause 98 of the IEEE 802.3 standard details the timers related to Auto-Negotiation.

Note, Auto-Negotiation is enabled by default for the ADIN1100 and it is strongly recommended that Auto-Negotiation is always enabled.

### Transmit Amplitude Resolution

Auto-Negotiation is used to resolve the transmit amplitude resolution. The PHY can be configured to support both 1.0 V pk-pk and 2.4 V pk-pk transmit levels or to operate with 1.0 V pk-pk transmit level only through the hardware configuration (see Table 10). This configuration can also be done in software using the 10BASE-T1L high level transmit operating mode ability (AN\_ADV\_B10L\_TX\_LVL\_HI\_ABL) and 10BASE-T1L high level transmit operating mode request (AN\_ADV\_B10L\_TX\_LVL\_HI\_REQ) register bits (device address 0x07, register address 0x0204, bits 13 and 12 respectively).

To operate at 2.4 V pk-pk transmit level, both the local and remote PHYs must advertise that they are capable of operating at 2.4 V and at least one PHY must request 2.4 V pk-pk transmit level operation.

If it is required to only operate the PHY at 1.0 V pk-pk transmit level operation, then AN\_ADV\_B10L\_TX\_LVL\_HI\_ABL should be 0, so that 2.4 V pk-pk transmit level operation is not advertised. In this case Auto-Negotiation can only resolve to 1.0 V pk-pk transmit level operation, irrespective of what setting the remote PHY advertises.

## Master/Slave Resolution

Auto-Negotiation is also used to resolve master or slave status. The PHY can be configured to prefer slave or prefer master through the hardware configuration (see Table 9). If Auto-Negotiation is disabled, the MS\_SEL hardware configuration pin sets the default master/slave selection. Note that the recommended use of the ADIN1100 is with Auto-Negotiation enabled.

During Auto-Negotiation, when prefer slave is selected, and the remote end is prefer or forced Master, the local PHY will be set to slave (and remote to master). When the remote end is prefer or forced slave, the local PHY will be set to master (and remote to slave).

## **MANAGEMENT INTERFACE**

The MII management interface provides a two-wire serial interface between a host processor or MAC and the ADIN1100 allowing access to control and status information in the subsystem and PHY core management registers.

The MII management interface consists of the following:

- MDC, clock line

- MDIO, bidirectional data line

- PHYAD\_0, PHYAD\_1 and PHYAD\_2 pin2 which configure device addresses for each PHY

- INT\_N, management interrupt

The interface is compatible with IEEE Standard 802.3 Clause 45 management frame structures (see Register Summary section). Note that the MDIO interfaces of microcontrollers that only support IEEE Standard 802.3 Clause 22 cannot be used to interface with the ADIN1100 MDIO interface. In cases where this is required, the user can replicate the IEEE Standard 802.3 Clause 45 frame using two of the microcontroller's GPIO pins.

#### Interrupt (INT\_N)

The ADIN1100 is capable of generating an interrupt to a host processor or MAC using the INT\_N pin in response to a variety of user-selectable conditions. The following conditions can be selected to generate an interrupt:

- Link status change

- MAC interface FIFO overflow/underflow

There is also a non-maskable Hardware reset interrupt. The system interrupt mask and PHY subsystem interrupt mask registers (CRSM\_IRQ\_MASK and PHY\_SUBSYS\_IRQ\_MASK respectively) are used to make these selections.

When an interrupt occurs, the system can poll the status of the interrupt status register (CRSM\_IRQ\_STATUS and PHY\_SUBSYS\_IRQ\_STATUS registers) on each device to determine the origin of the interrupt.

## **MDI INTERFACE**

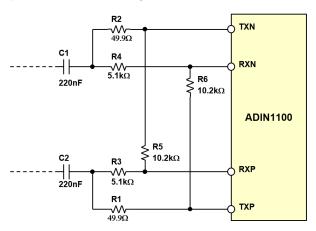

The Media Dependent Interface (MDI) connects the ADIN1100 to the Ethernet network via a twisted wire pair.

The ADIN1100 requires an external hybrid between the separate TXN/P and RXN/P pins and the twisted wire pair. This external hybrid allows the system to have full-duplex communication, by removing the local transmit signal from the combined signal on the cable, leaving just the desired receive signal.

The ADIN1100 hybrid requires a specific topology and values for correct operation. The topology and values for the components can be seen in Figure 7.

Figure 7. Recommended hybrid for the ADIN1100.

The size, power and voltage rating of these components should be considered in the context of other system requirements, for example, requirements of intrinsic safety.

## **RESET OPERATION**

The ADIN1100 supports a number of resets - power-on reset, hardware reset, and multiple software reset types. All of these put the ADIN1100, including the PHY core into a known state. Whenever the PHY core is reset, the MAC interface output pins (output pins with respect to the ADIN1100) are driven to a low state.

## Power-On Reset

The ADIN1100 includes power monitoring circuitry to monitor all of the supplies. At power-up the ADIN1100 is held in hardware reset until each of the supplies has crossed its minimum rising threshold value and the power is considered good.

Brown out protection is provided by monitoring the supplies to detect if one or more of the supplies drops below a minimum falling threshold value and holding the part in hardware reset until the power is good again.

## Hardware Reset

A hardware reset is initiated by the power-on reset circuitry or by asserting the RESET\_N pin low. The pin should be brought low for a minimum of 10  $\mu$ s. De-glitch circuitry is included on this pin to reject pulses shorter than approximately 1  $\mu$ s.

When the RESET\_N pin is de-asserted, all the I/O pins are held in tristate mode and the hardware configuration pins are latched, and then the I/O pins are configured for their functional mode. Once all the external and internal supplies are valid and stable, the crystal oscillator circuit is enabled, and after some time for the crystal start-up and stabilization, the PLL is enabled. After approximately 50 ms (max) from the deassertion of RESET\_N, all the internal clocks are valid, the internal logic is released from reset and all the management interface registers are accessible so that the device can be programmed.

## Software Reset

A full chip software reset can be initiated by setting the software reset bit (CRSM\_SFT\_RST, device address 0x1E, register address 0x8810, bit 0). When this bit is set, a full initialization of the chip, almost equivalent to a hardware reset, is done. The I/O pins are held in tristate mode and the hardware configuration pins are latched, and then the I/O pins are configured for their functional mode. The crystal oscillator circuit is enabled, and after some time for the crystal start-up and stabilization, the PLL is enabled. Approximately 10 ms (max) after setting the CRSM\_SFT\_RST bit, the internal logic is released from reset and all the management interface registers are accessible. The system ready bit (CRSM\_SYS\_RDY, device address 0x1E, register address 0x8818, bit 0) indicates that the start-up sequence is complete and the system is ready for normal operation.

## PHY Subsystem Reset

The PHY subsystem is the part of the ADIN1100 that incorporates the 10BASE-T1L PHY transceiver analog and digital circuits. A PHY subsystem reset can be initiated by setting the PHY subsystem reset register bit (CRSM\_PHY\_SUBSYS\_RST, device address 0x1E, register address 0x8814, bit 0). When this bit is set, the PHY subsystem is reset. The reset is applied for about 1.2 µs and then this bit self clears. All of the PHY digital circuitry is reset and any existing link will drop. The management registers are not initialized by this reset, and access to all the management registers is available during the PHY subsystem reset. This is a short reset and can be used to put the part into a known state while retaining any software initialization of the part.

## **MAC Interface Reset**

A MAC interface reset can be initiated by setting the PHY MAC interface reset register bit (CRSM\_MAC\_IF\_RST, device address 0x1E, register address 0x8815, bit 0). When this bit is set, a reset sequence is provided to the MAC interface to the 10BASE-T1L PHY, but without dropping an existing link. The reset is applied for about 1.2 µs and then this bit self clears. The MAC interface reset will interrupt any TX/RX packet exchange between the MAC and the 10BASE-T1L PHY, but will not drop an existing link, nor will prevent a link being established. No management registers are initialized and access to all the management registers is available during the MAC interface reset.

# STATUS LED

## LED Link/Activity

The ADIN1100 provides a configurable status LED. The LED can be used to indicate link status and Tx/Rx activity by blinking. By default, the LED is disabled and can be enabled by setting the LED enable bit (LED\_EN) within the LED control

register (LED\_CNTRL, device address 0x1E, register address 0x8C81, bit 0). There is some programmability around the LED on/off blinking activity which is controlled via the LED blink time control register (LED\_BLINK\_TIME\_CNTRL, device address 0x1E, register address 0x8C80).

#### Link Status Pin

In addition to the LED pin, there is also a LINK\_ST pin. This pin is asserted when the link status bit (AN\_LINK\_STATUS, device address 0x07, register address 0x0201, bit 2) is asserted and indicates that the link is established. The LINK\_ST pin is active high.

## **POWERDOWN MODES**

The ADIN1100 supports a number of powerdown modes - hardware powerdown and software powerdown. The lowest power mode is hardware powerdown where the part is turned fully off and the registers are not accessible.

#### Hardware Powerdown Mode

Hardware powerdown is a useful mode when operation of the ADIN1100 is not required and power is to be minimized. The ADIN1100 enters hardware powerdown mode when the RESET\_N pin is asserted and held low. In this mode, all analog and digital circuits are disabled, the clocks are gated off, all the I/O pins are held in tristate mode and the only power is the

leakage power of the circuits. The management registers are not accessible in this mode.

### Software Powerdown Mode

Software powerdown mode is a useful mode when the part is being configured by software before links are brought up. The ADIN1100 can be configured to enter software powerdown mode after reset using the RX\_DV/SWPD\_ENB pin. The ADIN1100 can also be instructed to enter software powerdown mode by setting the software powerdown bit (CRSM\_SFT\_PD, device address 0x1E, register address 0x8812, bit 0).

The software powerdown status bit (CRSM\_SFT\_PD\_RDY, device address 0x1E, register address 0x8818, bit 1) indicates that the part is in the software powerdown state. In software powerdown mode, the analog and digital circuits are in a low power state, the PLL is active and can provide output clocks if configured to do so. Any signal or energy on the MDI pins are ignored and no link will be brought up. The MAC Interface output pins are asserted low. The management interface registers are accessible, and the part can be configured using software. The ADIN1100 exits software powerdown mode when the CRSM\_SFT\_PD bit is cleared. At this point the PHY will start Auto-Negotiation and attempt to bring up a link after Auto-Negotiation completes successfully.

# HARDWARE CONFIGURATION PINS

The ADIN1100 can operate in unmanaged or managed applications. In unmanaged applications, it is possible to configure the desired operation of the PHY from hardware configuration pins without any software intervention. The hardware configuration pins set the default values of the corresponding management registers. After coming out of reset, the PHY will immediately start to attempt to bring up a link. Note for an unmanaged application, the PHY should not be hardware configured to enter software powerdown after reset.

In managed applications, software is available to configure the PHY via the management interface. In this case, the user can configure the PHY to enter software powerdown after reset, software can then intervene to configure the device as required and bring the PHY out of software powerdown to allow links to be established.

Hardware configuration pins are pins shared with functional pins and the voltage level on the pin is sensed and latched upon exiting from a reset. All hardware configuration pins are 2-level sense using a pull-down or pull-up resistor.

## HARDWARE CONFIGURATION PIN FUNCTIONS

The following functions are configurable from the ADIN1100 hardware pins:

- PHY address

- Software powerdown mode after reset

- Transmit amplitude configuration

- Master/Slave selection

- MAC interface selection (RMII/MII)

- Media convertor operation.

All of these pins have internal pull-down resistors, so the default mode of operation without any external resistors connected to these pins is captured in Table 7. If an alternative mode of operation is required, 4.7 k $\Omega$  pull-up resistors should be used. Note it is only ok to rely on the internal pull-down resistor if the MAC/host also has an internal pull-down on this pin. Otherwise an external pull-down should be used.

#### Table 7. Default Hardware Configuration Modes

| Hardware Configuration Pin<br>Function | Default Mode                      |

|----------------------------------------|-----------------------------------|

| PHY address                            | 0x0                               |

| Software PD mode after reset           | PHY in software PD after<br>reset |

| Master/slave selection                 | Prefer slave                      |

| Transmit amplitude                     | 1.0 V pk-pk/ 2.4 V pk-pk          |

| MAC interface selection                | RMII                              |

| Media convertor                        | Normal PHY operation              |

#### **PHY Address Configuration**

Three of the ADIN1100 pins (RXD\_2, RXD\_3 and LINK\_ST) are available for configuring the PHY address. These are two

**Preliminary Technical Data**

used and in that case, it may not be necessary to configure these pins externally because the shared pins have weak internal pulldown resistors. This assumes that no other system level circuitry attached to these nodes, such as the MAC or Ethernet switch has internal pull-up resistors on these pins.

### Software Powerdown after Reset

The SWPD\_ENB hardware configuration pin is shared with the RX\_DV pin and configures the default setting of the software powerdown bit (CRSM\_SFT\_PD, device address 0x1E, register address 0x8812, bit 0).

If the ADIN1100 is configured so that it does not enter software powerdown mode after reset, then once it exits reset, the ADIN1100 will start Auto-Negotiation and try to bring up a link after Auto-Negotiation completes successfully. If the ADIN1100 is configured so that it enters software powerdown mode after reset, the ADIN1100 will wait in software powerdown mode until it is configured over the MDIO interface at which point, the PHY configuration can be set to exit software powerdown by software.

#### Table 8. Software Powerdown (Hardware Configuration)

| Software Powerdown Configuration | SWPD_ENB |

|----------------------------------|----------|

| PHY in software PD after reset   | 0        |

| PHY not in software PD           | 1        |

#### Master/Slave Preference

The MS\_SEL hardware configuration pin is shared with the RXD\_1 pin and configures the default master/slave selection. If MS\_SEL is pulled low during power-up/reset the part is configured by default to prefer slave (this is the case if no external pull-up resistor is connected to MS\_SEL pin due to the presence of the internal pull-down resistor). If MS\_SEL is pulled high during power-up/reset the part is configured by default to prefer master.

If Auto-Negotiation is disabled, this pin sets the default master/slave selection. Note, Auto-Negotiation is enabled by default for the ADIN1100 and it is strongly recommended that Auto-Negotiation is always enabled.

During Auto-Negotiation when prefer slave is selected, and the remote end is prefer or forced master, the local PHY will be set to slave (and remote to master). When the remote end is prefer or forced slave, the local PHY will be set to master (and remote to slave).

#### Table 9. Master/Slave Selection (Hardware Configuration)

| Master/Slave Selection  | MS_SEL |

|-------------------------|--------|

| Prefer Slave selection  | 0      |

| Prefer Master selection | 1      |

The MS\_SEL hardware configuration pin configures the default setting of Master/Slave Configuration register bit

(AN\_ADV\_MST, device address 0x07, register address 0x0203,

bit 4). The MS\_SEL hardware configuration pin also configures the default setting of the master slave config register bit (CFG\_MST, device address 0x01, register address 0x0834, bit 14), which is used when Auto-Negotiation is disabled. Note, Auto-Negotiation is enabled by default for the ADIN1100 and it is strongly recommended that Auto-Negotiation is always enabled.

If MS\_SEL is pulled low during power-up/reset, the default value of AN\_ADV\_MST and CFG\_MST is 0. If MS\_SEL is pulled high during power-up/reset, the default value of these bits is 1.

The AN\_ADV\_MST bit advertises the master/slave configuration, as follows:

0 =slave;

1 = master.

### Transmit Amplitude

The TX2P4\_ENB hardware configuration pin is shared with the RXD\_0 pin and allows the user to configure the required transmit amplitude mode for the intended application. If TX2P4\_ENB is pulled low, the ADIN1100 is configured by default to support both 1.0 V pk-pk and 2.4 V pk-pk transmit levels, to be decided by Auto-Negotiation. If TX2P4\_ENB is pulled high, the ADIN1100 is configured to disable 2.4 V pk-pk transmit operating mode by default and operate with 1.0 V pk-pk transmit level only. Note that if the TX2P4\_ENB pin is strapped high (1.0 V pk-pk only), the associated register cannot be changed through the MDIO interface, i.e. 2.4 V pk-pk operation is not possible if the ADIN1100 has been hardware pin-configured for 1.0 V pk-pk only.

The 1.0 V pk-pk transmit operating mode supports the spur use case and can operate at a lower AVDD\_H supply voltage of 1.8 V. This supports cable lengths of up to 400 m.

The higher transmit operating mode of 2.4 V pk-pk supports trunk applications and requires higher AVDD\_H supply voltage (3.3 V). This supports using longer cable lengths of up to 1000 m.

# Table 10. Transmit Amplitude Configuration (HardwareConfiguration)

| Transmit Amplitude Selection | TX2P4_ENB |

|------------------------------|-----------|

| 1.0 V/ 2.4 V pk-pk           | 0         |

| 1.0 V pk-pk                  | 1         |

The TX2P4\_ENB hardware configuration pin configures the value of the 10BASE-T1L high voltage Tx ability read only register bit (B10L\_TX\_LVL\_HI\_ABLE, device address 0x01, register address 0x08F7, bit 12). If TX2P4\_ENB is pulled low during power-up/reset, the 2.4 V pk-pk transmit operating mode is enabled and the value of B10L\_TX\_LVL\_HI\_ABLE is 1. If TX2P4\_ENB is pulled high during power-up/reset, the 2.4 V pk-pk transmit operating mode is disabled, and the value of B10L\_TX\_LVL\_HI\_ABLE is 0.

The B10L\_TX\_LVL\_HI\_ABLE bit reports whether the PHY is capable of operating in the 10BASE-T1L high transmit voltage mode:

0 = PHY does not support 10BASE-T1L high voltage (2.4 V pkpk) transmit level operating mode;

1 = PHY supports 10BASE-T1L high voltage (2.4 V pk-pk) transmit level operating mode.

The default values of the BASE-T1 Auto-Negotiation advertisement register bits and the 10BASE-T1L transmit voltage amplitude control bit are set to match the 10BASE-T1L high voltage Tx ability bit and it is not possible to write a 1 to these bits if the 10BASE-T1L high voltage Tx ability read only register bit is zero (TX2P4\_ENB pin is strapped high i.e. 1.0 V pk-pk only).

The value of the 10BASE-T1L high voltage Tx ability bit configures the default setting of the advertisement of 10BASE-T1L high level transmit operating mode ability bit (AN\_ADV\_B10L\_TX\_LVL\_HI\_ABL, device address 0x07, register address 0x0204, bit 13), the default setting of the advertisement of 10BASE-T1L high level transmit operating mode request bit (AN\_ADV\_B10L\_TX\_LVL\_HI\_REQ, device address 0x07, register address 0x0204, bit 12), and the default setting of the 10BASE-T1L transmit voltage amplitude control bit (B10L\_TX\_LVL\_HI, device address 0x01, register address 0x08F6, bit 12). The latter is used when Auto-Negotiation is disabled. Note, Auto-Negotiation is enabled by default for the ADIN1100 and it is strongly recommended that Auto-Negotiation is always enabled.

- If it is desired to allow both 1.0 V pk-pk and 2.4 V pkpk transmit level operation then AN\_ADV\_B10L\_TX\_LVL\_HI\_ABL should be set to indicate that the part is capable of 2.4 V pk-pk transmit level operation (and a 3.3V supply is required to power the AVDD\_H supply).

- If 2.4 V pk-pk transmit level operation is preferred then AN\_ADV\_B10L\_TX\_LVL\_HI\_REQ should be set, to request 2.4 V pk-pk transmit level operation. Auto-Negotiation will determine the transmit level that the link will operate at.

- If 1.0 V pk-pk transmit level operation is preferred then AN\_ADV\_B10L\_TX\_LVL\_HI\_REQ should be 0. Auto-Negotiation will determine the transmit level that the link will operate at.

To operate at 2.4 V pk-pk transmit level, both the local and remote PHYs must advertise that they are capable of operating at 2.4 V pk-pk and at least one PHY must request 2.4 V pk-pk transmit level operation.

If it is required to only operate the PHY at 1.0 V pk-pk transmit level operation, then the AN\_ADV\_B10L\_TX\_LVL\_HI\_ABL should be 0, so that 2.4 V pk-pk transmit level operation is not advertised. In this case Auto-Negotiation can only resolve to 1.0 V pk-pk transmit level operation, irrespective of what setting the remote PHY advertises. For very long cable lengths

depending on the characteristics of the cable it may not be possible to bring up a link at 1.0 V pk-pk operation.

When TX2P4\_ENB is 1, the AVDD\_H supply can be supplied from either 1.8V or 3.3V for 1.0 V pk-pk transmit level operation.

### **MAC Interface Selection**

The MAC interface hardware configuration pin selection is shared with the RX\_CLK and RX\_ER pins and can be configured according to Table 11. The RX\_CLK and RX\_ER pins have weak internal pull-down resistors so, by default the ADIN1100 is configured in RMII mode. External resistors must be used to select the MII MAC interface mode.

# Table 11. MAC Interface Selection (Hardware Configuration)

| MAC Interface Selection | MACIF_SEL1 | MACIF_SEL0 |

|-------------------------|------------|------------|

| RMII                    | 0          | 0          |

| Reserved                | 0          | 1          |

| Reserved                | 1          | 0          |

| MII                     | 1          | 1          |

## Media Convertor

The ADIN1100 can operate as a media convertor. This allows to have a 10BASE-T PHY connected directly to the ADIN1100 via the RMII interface, connecting to a 10BASE-T1L remote PHY via the MDI pins.

The MEDIA\_CNV hardware configuration pin is shared with the TXD\_3 pin, therefore, this mode of operation is only available when the RMII MAC interface mode is selected (see Table 11).

The MEDIA\_CNV pin has a weak internal pull-down resistor so, by default, the ADIN1100 is configured for normal PHY operation. An external pull-up resistor must be used to select the media convertor operation.

# Table 12. Media Convertor Selection (HardwareConfiguration)

| Media Convertor Selection | MEDIA_CNV |

|---------------------------|-----------|

| Normal PHY operation      | 0         |

| Media Convertor operation | 1         |

# BRINGING UP 10BASE-T1L LINKS UNMANAGED PHY OPERATION

For an unmanaged PHY or lightly managed PHY application where there is no software management of the PHY, the hardware configuration pins determine the operating mode. The TX2P4\_ENB pin configures the PHY to advertise the support of both 1.0 V pk-pk and 2.4 V pk-pk transmit level operation or to only advertise support of 1.0 V pk-pk transmit level operation. The MS\_SEL pin is used to configure the PHY to advertise prefer slave or prefer master. The SWPD\_ENB pin should be asserted at power-up and reset so that the PHY does not enter software powerdown mode when it exits reset. Once it exits reset, the ADIN1100 will start Auto-Negotiation and try to bring up a link after Auto-Negotiation completes successfully.

A lightly managed PHY may use the hardware configuration pins to determine the operation of the PHY and to bring up a 10BASE-T1L link. And afterwards software can monitor the operation of the PHY.