#### General Description

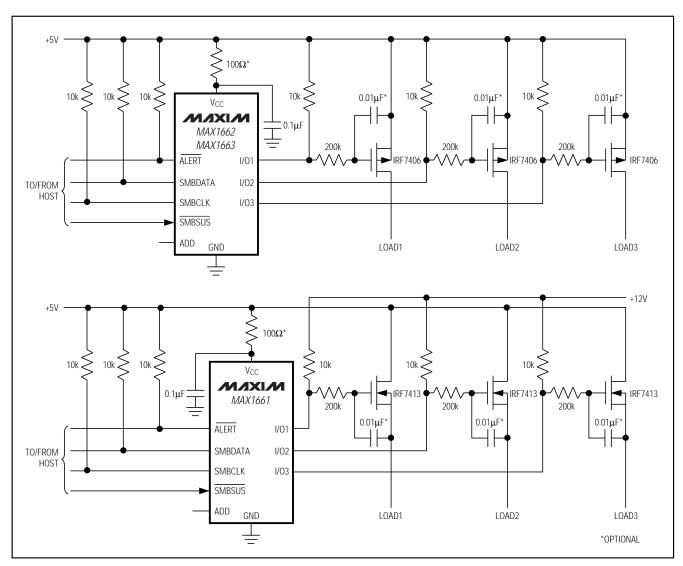

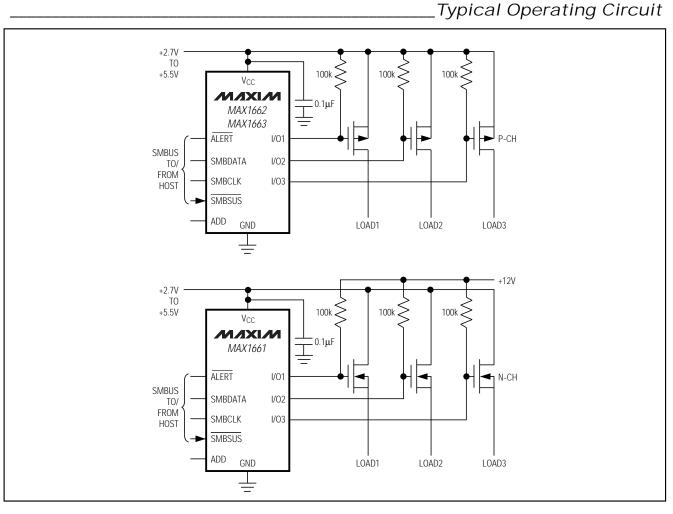

The MAX1661/MAX1662/MAX1663 serial-to-parallel/ parallel-to-serial converters are intended to control external power MOSFETs in power-plane switching applications. These small, low-cost devices can be used on a system motherboard to control point-of-load switching from a 2wire SMBus™ serial interface. Each device has three highvoltage open-drain outputs that double as TTL-level logic inputs, giving them bidirectional capabilities. The I/O pins can withstand +28V, so they can control battery voltagedistribution switches in notebook computers.

The MAX1661 is intended for driving N-channel MOSFETs and its outputs are low upon power-up. The MAX1662/ MAX1663 are intended for P-channel MOSFETs, and their outputs are high-impedance upon power-up. This ensures that the MOSFETs are off at power-up, so the system can enforce power-plane sequencing.

The SMBSUS control input selects control data between two separate data registers. This feature allows the system to select between two different power-plane configurations asynchronously, eliminating latencies introduced by the serial bus. Other features include thermal-overload and overcurrent protection, ultra-low supply current, and both hardware and software interrupt capabilities. These devices are available in the space-saving 10-pin µMAX package.

#### **Applications**

Power-Plane Switching Point-of-Load Power-Bus Switching Notebook and Subnotebook Computers **Desktop Computers Smart Batteries**

### **Features**

- ♦ Performs Serial-to-Parallel and Parallel-to-Serial Conversions

- **♦** Three General-Purpose Digital Input/Output Pins (withstand +28V)

- **♦ SMBus 2-Wire Serial Interface**

- **♦ Supports SMBSUS Asynchronous Suspend Mode**

- ♦ 3µA Supply Current

- ♦ +2.7V to +5.5V Supply Range

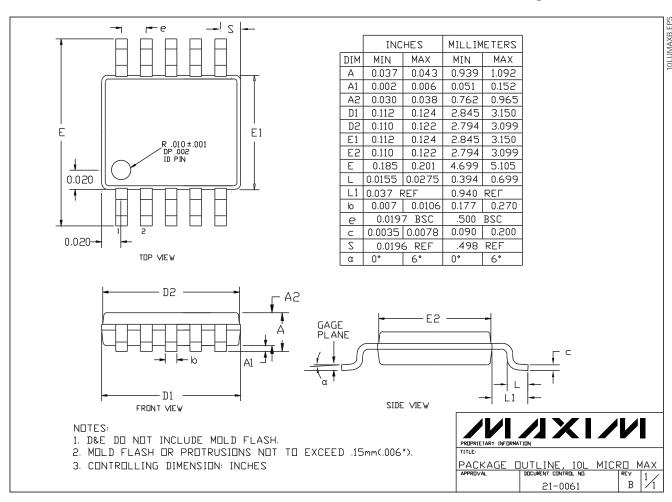

- ♦ Space-Saving, Low-Cost 10-Pin µMAX Package

#### Ordering Information

| PART       | TEMP. RANGE    | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX1661EUB | -40°C to +85°C | 10 μMAX     |

| MAX1662EUB | -40°C to +85°C | 10 μMAX     |

| MAX1663EUB | -40°C to +85°C | 10 μMAX     |

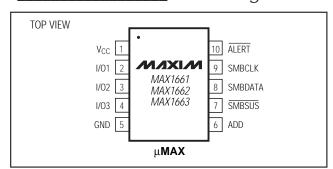

#### Pin Configuration

Typical Operating Circuits appear at end of data sheet.

#### Selector Guide

| PART    | POWER-ON-                      | INTENDED          | SMBus ADDRESS        |                               |  |

|---------|--------------------------------|-------------------|----------------------|-------------------------------|--|

| PARI    | RESET STATE                    | APPLICATION       | ADDRESS PIN          | ADDRESS                       |  |

| MAX1661 | Outputs Low                    | N-Channel MOSFETs | GND<br>High-Z<br>Vcc | 0100000<br>0111100<br>1001000 |  |

| MAX1662 | Outputs High<br>(high-Z state) | P-Channel MOSFETs | GND<br>High-Z<br>Vcc | 0100001<br>0111101<br>1001001 |  |

| MAX1663 | Outputs High<br>(high-Z state) | P-Channel MOSFETs | GND<br>High-Z<br>Vcc | 0100010<br>0111110<br>1001010 |  |

SMBus is a trademark of Intel Corp.

NIXIN

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND             |              |

|------------------------------------|--------------|

| I/O to GND (I/O1, I/O2, I/O3)      | 0.3V to +30V |

| Internally Limited                 | 1mA to +50mA |

| Digital Inputs to GND (SMBCLK, SMI |              |

| SMBSUS, ALERT)                     | 0.3V to +6V  |

| ADD to GND                         | ,            |

| SMBDATA Current, ALERT Current     | 1mA to +50mA |

| Continuous Power Dissipation (TA : | = +70°C)          |

|------------------------------------|-------------------|

| 10-pin µMAX (derate 5.6mW/°C       | above +70°C)444mW |

| Operating Temperature Range        |                   |

| MAX166_EUB                         | 40°C to +85°C     |

| Storage Temperature Range          |                   |

| Lead Temperature (soldering, 10se  | ec)+300°C         |

|                                    |                   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +2.7V \text{ to } +5.5V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are for } T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                                         | SYMBOL           | CONDITIONS                                                                                                   | MIN | TYP | MAX | UNITS |

|---------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Input Voltage Range                               |                  |                                                                                                              | 2.7 |     | 5.5 | V     |

| Supply Current                                    |                  | Static condition; SMBDATA, SMBCLK, ADD, ALERT = V <sub>CC</sub> or GND (Note 2)                              |     | 3   | 10  | μΑ    |

| Undervoltage Lockout/<br>Power-On Reset Threshold |                  | V <sub>CC</sub> falling                                                                                      | 1.2 | 1.6 | 2.5 | V     |

| I/O Sink Current                                  |                  | $V_{I/O_{-}} = 0.4V$ , $V_{CC} = 2.7V$ or 5.5V                                                               | 2   |     |     | mA    |

| 1/O SIIIK CUITEIT                                 |                  | $V_{I/O_{-}} = 1.0V, V_{CC} = 4.5V$                                                                          | 8   | 13  |     | IIIA  |

| I/O Current Limit                                 |                  | I/O1, I/O2, or I/O3; V <sub>CC</sub> = 4.5V                                                                  | 15  | 20  | 50  | mA    |

| Thermal Shutdown                                  |                  | Typical hysteresis of 10°C                                                                                   |     | 140 |     | °C    |

| UO Lookaga Current                                |                  | V <sub>I/O</sub> _ = 28V, high-impedance state                                                               |     | 0.5 | 5   |       |

| I/O Leakage Current                               |                  | $V_{I/O_{-}} = 0V$ , $V_{CC}$ ; high-impedance state                                                         | -1  | 0.5 | 1   | μΑ    |

| Digital Input Current                             |                  | V <sub>SMBDATA</sub> , V <sub>SMBCLK</sub> , V <del>SMBSUS</del> ,<br>V <sub>ADD</sub> = 0V, V <sub>CC</sub> | -1  |     | 1   | μΑ    |

| SMBus Logic Input<br>Voltage Range                |                  | V <sub>CC</sub> = 2.7V to 5.5V;<br>SMBDATA, SMBCLK, SMBSUS                                                   | 0   |     | 5.5 | V     |

| Logic Input High Voltage                          |                  | I/O_, SMBSUS, SMBCLK, SMBDATA                                                                                | 2.4 |     |     | V     |

| Logic Input Low Voltage                           |                  | I/O_, SMBSUS, SMBCLK, SMBDATA                                                                                |     |     | 0.8 | V     |

| SMBDATA Output Low Sink<br>Current                |                  | V <sub>SMBDATA</sub> = 0.6V                                                                                  | 6   |     |     | mA    |

| ALERT Output Low Sink Current                     |                  | VALERT = 0.4V                                                                                                | 1   |     |     | mA    |

| ALERT Output Leakage Current                      |                  | VALERT = 5.5V, high-Z state                                                                                  |     |     | 1   | μΑ    |

| SMBus Input Capacitance                           |                  | SMBCLK, SMBDATA                                                                                              |     | 5   |     | pF    |

| SMBus Clock Frequency                             |                  | (Notes 3, 4)                                                                                                 |     |     | 100 | kHz   |

| SMBCLK High Time                                  | tHIGH            | Measured between the 90% level of the rising edge and the 90% level of the falling edge                      | 4   |     |     | μs    |

| SMBCLK Low Time                                   | t <sub>LOW</sub> | Measured between the 10% level of the falling edge and the 10% level of the rising edge                      | 4.7 |     |     | μs    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +2.7V \text{ to } +5.5V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are for } T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER                                              | SYMBOL                                                    | CONDITION                                                                                 | S                | MIN | TYP | MAX | UNITS |

|--------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------|-----|-----|-----|-------|

| Start-Condition Setup Time                             | tsu:sta                                                   | Measured from 90% of the SMBCLK rising edge to 90% of the SMBDATA falling edge            |                  | 4.7 |     |     | μs    |

| Start-Condition Hold Time                              | thd:STA                                                   | Measured from 10% of the fa<br>of SMBDATA to 90% of the fa<br>SMBCLK                      | 5 5              | 4   |     |     | μs    |

| SMBus Stop-Condition Setup<br>Time                     | tsu:sto                                                   | Measured from 90% of the rising edge of SMBCLK to 10% of the rising edge of SMBDATA       |                  | 4   |     |     | μs    |

| SMBDATA Valid to SMBCLK<br>Rising Edge Time, Slave     | Time, Slave t <sub>SU:DAT</sub> to 10% of the rising edge |                                                                                           | 500              |     |     | ns  |       |

| Clocking in Data                                       |                                                           |                                                                                           | 1000             |     |     | 115 |       |

| SMBCLK Falling Edge to<br>SMBDATA Transition Hold Time | t <sub>HD:DAT</sub>                                       | (Notes 4, 5)                                                                              |                  | 0   |     |     | μs    |

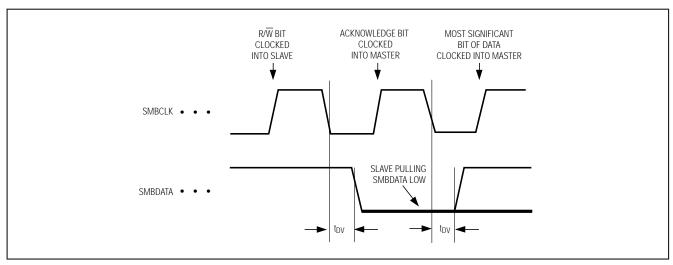

| SMBCLK Falling Edge to<br>SMBus Data Valid Time        | t <sub>DV</sub>                                           | Tested with a $10k\Omega$ pull-up resistor on SMBDATA (Note 6)                            |                  |     |     | 1   | μs    |

| SMBus Bus-Free Time                                    | tBUF                                                      | Between stop and start cond                                                               | litions (Note 7) | 4.7 |     |     | μs    |

| SMBus Write to I/O_<br>Propagation Delay               | t <sub>P:I/O</sub>                                        | Measured from SMBCLK rising edge to 10% or 90% of I/O (Note 4)                            |                  |     | 100 |     | ns    |

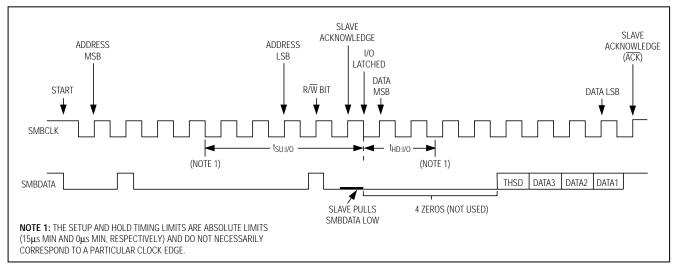

| I/O Data Valid to SMBCLK<br>Rising-Edge Setup Time     | t <sub>SU:I/O</sub>                                       | Measured from 10% or 90% of V <sub>I/O</sub> to 10% of the rising edge of SMBCLK (Note 8) |                  | 15  |     |     | μs    |

| I/O Data Hold Time                                     | thd:I/O                                                   | (Note 8)                                                                                  |                  | 0   |     |     | μs    |

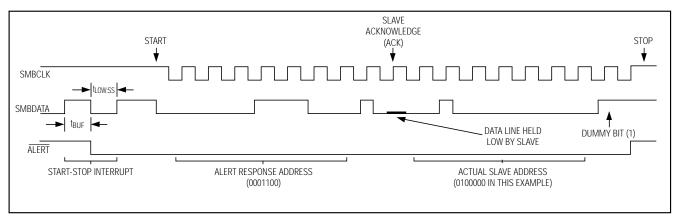

| START-STOP Software-Interrupt<br>Pulse Width           | t <sub>LOW:SS</sub>                                       | Measured from the 10% poir edge of SMBDATA to the 10° rising edge of SMBDATA (No          | % point of the   | 10  | 15  | 30  | μs    |

Note 1: Specifications from 0°C to -40°C are guaranteed by design, not production tested.

Note 2: Supply current is specified for static state only.

**Note 3:** The SMBus logic block is a static design that works with clock frequencies down to DC. While slow operation is possible, it violates the 10kHz minimum clock frequency of the SMBus specifications, and may monopolize the bus.

Note 4: Refer to Figures 2a and 2b for SMBus timing parameter definitions (write and read diagrams).

Note 5: A transition must internally provide a hold time of 300ns to accommodate for the undefined region of the falling edge.

**Note 6:** Refer to Figure 3 for the acknowledge timing diagram and t<sub>DV</sub> parameter definition.

Note 7: Refer to Figure 5 for START-STOP interrupt timing diagrams and parameter definitions.

Note 8: Refer to Figure 4 for I/O setup and hold timing parameter definitions.

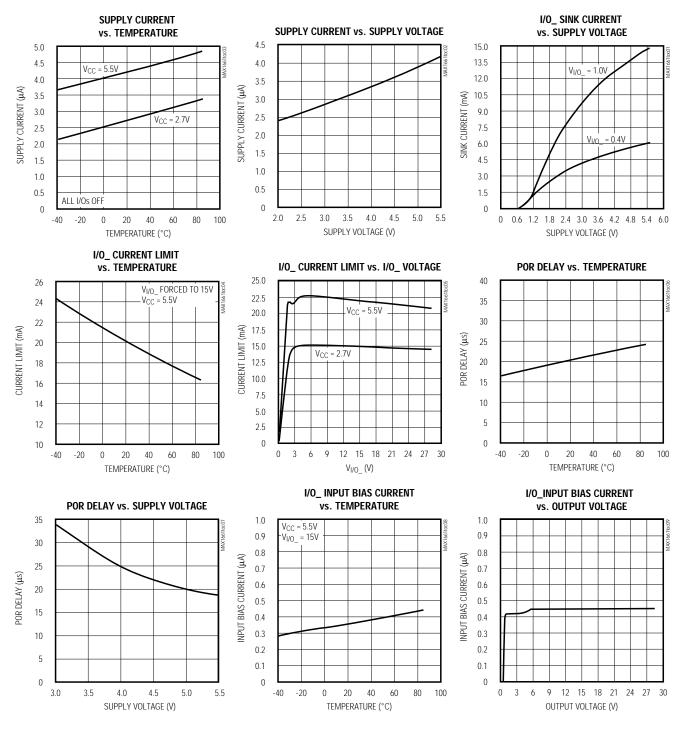

Typical Operating Characteristics

$(V_{CC} = +5.0V, T_A = +25^{\circ}C, unless otherwise noted.)$

Pin Description

| PIN | NAME    | FUNCTION                                                                                                                                                            |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Vcc     | Supply Voltage Input, 2.7V to 5.5V.                                                                                                                                 |

| 2   | I/O1    | Input 1 or Output 1 (open drain). This pin can tolerate up to 28V.                                                                                                  |

| 3   | 1/02    | Input 2 or Output 2 (open drain). This pin can tolerate up to 28V.                                                                                                  |

| 4   | I/O3    | Input 3 or Output 3 (open drain). This pin can tolerate up to 28V.                                                                                                  |

| 5   | GND     | Ground                                                                                                                                                              |

| 6   | ADD     | SMBus Address Select Pin (see Table 1 for details).                                                                                                                 |

| 7   | SMBSUS  | SMBus Suspend-Mode Control Input. Drive low to select the suspend-mode register. Drive high to select the normal-mode register. (See <i>Detailed Description</i> .) |

| 8   | SMBDATA | SMBus Serial-Data Input/Output (open drain)                                                                                                                         |

| 9   | SMBCLK  | SMBus Serial Clock Input                                                                                                                                            |

| 10  | ALERT   | Interrupt Output, active low, open drain                                                                                                                            |

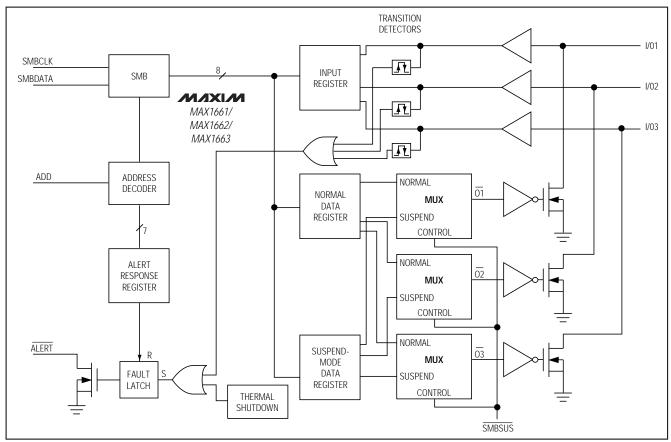

Figure 1. Functional Diagram

#### Detailed Description

The MAX1661/MAX1662/MAX1663 convert 2-wire SMBus serial data into three latched parallel outputs (I/O1, I/O2, I/O3). These devices are intended to drive N-channel and P-channel, high-side MOSFET switches in load power-management systems. Readback capabilities allow them to function as parallel-to-serial devices. The MAX1661/MAX1662/MAX1663 operate from a single supply with a typical quiescent current of 3µA, making them ideal for portable applications (Figure 1).

#### SMBus Interface Operation

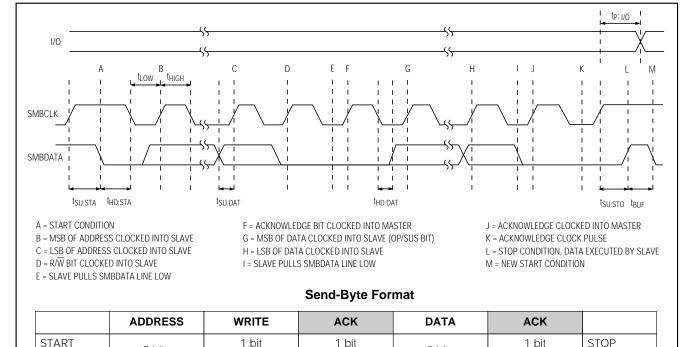

The SMBus serial interface is a 2-wire interface with multi-mastering capability. From a software perspective, the MAX1661/MAX1662/MAX1663 appears as a set of byte-wide registers that contain information controlling the I/O\_ pins, masking capabilities, and a control bit that determines which register is being addressed. The 2-wire slave interface employs standard SMBus send-byte and receive-byte protocols. SMBDATA and SMBCLK are Schmitt-triggered inputs that can accommodate slower edges; however, the rising and falling edges should still be faster than 1µs and 300ns, respectively. Except for the stop and start conditions, the SMBDATA input never transitions while SMBCLK is high. A third interface line (SMBSUS) is used to execute commands asynchronously from previously stored registers (see the section SMBSUS (Suspend-Mode) Input). This reduces the inherent delay in a standard 2-wire serial interface. In the receive-byte operation, the SMBus interface reads back I/O states and thermal-shutdown status.

#### SMBus Addressing

Each slave device only responds to two addresses: its own unique address and the alert response address. The device's unique address is determined at power-up (Table 1). The three-level state of the address-select pin (ADD) is only sampled upon power-on reset (POR) causing momentary input bias current of 100µA. The address will not change until the part is power cycled. Stray capacitance in excess of 50pF on the ADD pin when floating may cause address recognition problems.

The normal start condition consists of a high-to-low transition on SMBDATA while SMBCLK is high. After the start condition, the master transmits a 7-bit address followed by a single bit to determine whether the device is sending or receiving (high = READ, low = WRITE). If the address is correct, the MAX1661/MAX1662/MAX1663 sends an acknowledgment pulse by pulling SMBDATA low. Otherwise, the address is not recognized and the device stays off the bus and waits until another start condition occurs.

**Table 1. SMBus Addresses**

| ADD                  | MAX1661 | MAX1662 | MAX1663 |

|----------------------|---------|---------|---------|

| GND                  | 0100000 | 0100001 | 0100010 |

| High-Z<br>(floating) | 0111100 | 0111101 | 0111110 |

| V <sub>C</sub> C     | 1001000 | 1001001 | 1001010 |

#### SMBus Send-Byte Commands

If the MAX1661/MAX1662/MAX1663 receives its correct slave address (Table 1) followed by R/W low, it expects to receive a byte of information. If the device detects a start or stop condition prior to clocking in the byte of data, it considers this an error condition and disregards all of the data.

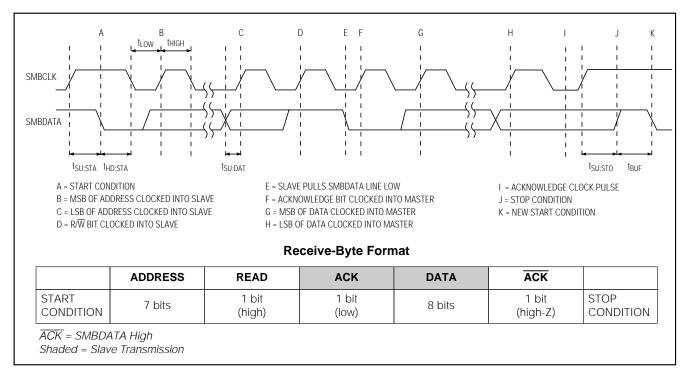

The MAX1661/MAX1662/MAX1663 generates a first acknowledge after the write bit and another acknowledge after the data. It executes the data byte at the rising edge of SMBCLK following the second acknowledge, just prior to the stop condition (Figure 2a). See Table 2 for send-byte operations.

#### SMBSUS (Suspend-Mode) Input

The SMBus can write to either of the normal-data and suspend-mode registers via the MSB (bit 7) of the send-byte word (Table 2). The state of the SMBSUS input selects which register contents (normal data or suspend mode) are applied to the I/O\_ pins. Driving SMBSUS low selects the suspend-mode register, while driving SMBSUS high selects the normal-data register. This feature allows the system to select between two different power-plane configurations asynchronously, eliminating latencies introduced by the serial bus. SMBSUS typically connects to the SUSTAT# signal in a notebook computer.

#### SMBus Receive-Byte Operation

If the MAX1661/MAX1662/MAX1663 receives its correct slave address, followed by R/W high, the device becomes a slave transmitter (Figure 2b). After receiving the address data, the device generates an acknowledge during the acknowledge clock pulse and drives SMBDATA in sync with SMBCLK. The SMB protocol requires that the master terminate the read transmission by not acknowledging during the acknowledge bit of SMBCLK. See Table 3 for receive-byte data format. Figure 4 shows the complete receive-byte operation timing diagram.

The logic states of the three I/O pins can be read over the serial interface (Table 3). The state of the I/O pins is sampled at the falling edge of the SMBCLK pulse that follows the  $R/\overline{W}$  bit and acknowledge bit (Figure 4). The states of the I/O bits in the status register reflect the

1 bit

(low)

8 bits

Figure 2a. SMBus Send-Byte Timing Diagram and Format

7 bits

**CONDITION**

Shaded = Slave Transmission

1 bit

(low)

#### Table 2. Format for Send-Byte Data

| BIT     | NAME POR STATE* POR STATE* (MAX1661) (MAX1662/MAX16 |     | POR STATE*<br>(MAX1662/MAX1663) | FUNCTION                                                                            |

|---------|-----------------------------------------------------|-----|---------------------------------|-------------------------------------------------------------------------------------|

| 7 (MSB) | SELECT                                              | N/A | N/A                             | Writes data to normal register when high; writes data to suspend register when low. |

| 6       | Mask SS                                             | 1   | 1                               | Masks START-STOP software interrupts when high.                                     |

| 5       | Mask 3                                              | 1   | 1                               | Masks I/O3 interrupts when high.                                                    |

| 4       | Mask 2                                              | 1   | 1                               | Masks I/O2 interrupts when high.                                                    |

| 3       | Mask 1                                              | 1   | 1                               | Masks I/O1 interrupts when high.                                                    |

| 2       | I/O3                                                | 0   | 1                               | I/O output enable bit. I/O3 is on when this bit is low (low state).                 |

| 1       | I/O2                                                | 0   | 1                               | I/O output enable bit. I/O2 is on when this bit is low (low state).                 |

| 0       | I/O1                                                | 0   | 1                               | I/O output enable bit. I/O1 is on when this bit is low (low state).                 |

<sup>\*</sup>Note: POR states apply to both suspend- and normal-mode registers.

current I/O pin states (i.e., they are not latched). There is a 15µs data-setup time requirement, due to the slow level translators needed for high-voltage (28V) operation. Data-hold time is zero.

#### Interrupts

The MAX1661/MAX1662/MAX1663 generate interrupts (hardware and software) whenever the logic states of the I/O pins change or when thermal shutdown occurs. Interrupts are signaled with the hardware ALERT pin

1 bit

(low)

CONDITION

Figure 2b. SMBus Receive-Byte Timing Diagram and Format

#### Table 3. Format for Receive-Byte Data

| ВІТ     | NAME   | POR STATE | FUNCTION                                            | LATCHED |

|---------|--------|-----------|-----------------------------------------------------|---------|

| 7 (MSB) | _      | 0         | Not used                                            | _       |

| 6       | _      | 0         | Not used                                            | _       |

| 5       | _      | 0         | Not used                                            | _       |

| 4       | _      | 0         | Not used                                            | _       |

| 3       | THSD   | N/A       | This bit indicates a thermal shutdown.              | Yes     |

| 2       | Data 3 | N/A       | This bit indicates the state of I/O3 (high or low). | No      |

| 1       | Data 2 | N/A       | This bit indicates the state of I/O2 (high or low). | No      |

| 0       | Data 1 | N/A       | This bit indicates the state of I/O1 (high or low). | No      |

and with the software START-STOP method (software interrupts are discussed in the *START-STOP Software Interrupt* section). The I/O interrupts can be masked individually. In addition, the software START-STOP interrupt can be masked independently. The power-on-reset state masks the START-STOP interrupt, as well as the individual I/O interrupts to the ALERT pin (Table 1). The thermal-shutdown interrupt cannot be masked. Note that excessive noise on the supply can cause false interrupts (see *Applications Information*).

The MAX1661/MAX1662/MAX1663 are slave-only devices that never initiate communications, except when asserting an interrupt by forcing ALERT low, or via the software START-STOP interrupt.

#### Alert Response Address (0001100)

The Alert Response (interrupt pointer) address provides quick fault identification for simple slave devices that lack the complex, expensive logic needed to be a bus master. When a slave device generates an inter-

Figure 3. SMB Serial-Interface Timing—Acknowledge and Data Valid

Figure 4. I/O Read Timing Diagram

rupt, the host (Bus Master) interrogates the bus slave devices via a special receive-byte operation that includes the alert response address. The data returned by this receive-byte operation is the address of the offending slave device. The interrupt pointer address can activate several different slave devices simultaneously. If more than one slave attempts to respond, bus arbitration rules apply, with the lowest address code going first. The other device(s) will not generate an acknowledge and will continue to hold the ALERT line low or repeat the START-STOP interrupt until serviced.

Clearing Interrupts via Alert Response When a fault occurs, ALERT asserts and latches low. If the fault is momentary and disappears before the device is serviced, ALERT remains asserted. Normally, the master sends out the Alert Response address followed by a read bit (00011001). ALERT clears when the device responds by successfully putting its address on the bus. Reading the Alert Response address is the only method for clearing hardware and software interrupt latches. Clearing the interrupt has no effect on the state of the status registers.

Figure 5. START-STOP Software Interrupt Timing Diagram and Alert Response

#### START-STOP Software Interrupt

The START-STOP interrupt is a method for the slave device to initiate a signal over the 2-wire interface without the need for a third (interrupt) wire. A START-STOP interrupt is a start condition followed by a stop condition; in other words, SMBDATA goes low and then high with SMBCLK high (Figure 5 shows the START-STOP interrupt and a subsequent Alert Response transmission used to clear the interrupt). The START-STOP function can be disabled (masked) by setting the data register mask SS (bit 6) high.

In order to avoid bus collisions, the START-STOP interrupt will not occur when the bus is busy. If the device begins a start condition simultaneously with another transmitter on the bus, it recognizes the falling SMB-CLK as a collision and re-transmits the interrupt when the bus becomes available. Upon thermal shutdown or a transition on an I/O line, the device issues only one START-STOP interrupt, and won't repeat it unless there has been a collision. However, thermal-shutdown faults, not being edge triggered, may result in a continuous stream of START-STOP bits.

#### Input/Output Pins

Each input/output (I/O) is protected by an internal 20mA (typical) current-limit circuit. The I/O current limit depends on the supply voltage and the voltage applied to the I/O pins (see *Typical Operating Characteristics*). The typical I/O bias current is  $0.5\mu A$  to  $V_{I/O} = 28V$ .

The ability of the I/Os to sink current depends on V<sub>CC</sub> as well as the voltage on the I/O. Typical pull-down onresistance at V<sub>CC</sub> = 2.7V and 5.5V is  $106\Omega$  and  $66\Omega$ , respectively. I/O source and sink capability can affect the rise and fall times of external power MOSFETs com-

monly used in power-switching applications. Other factors include the VGS, the input capacitance of the MOSFET, and the pull-up resistor value used in the circuit. Typical MOSFET gate capacitance ranges from 150pF to 2000pF. Increasing the RC time constant slows down the MOSFET's response, but provides for a smoother transition.

#### Power-On Reset

The power-on reset circuit keeps the external MOSFETs off during a power-up sequence. When the supply voltage falls below the power-on reset threshold voltage, the MAX1662/MAX1663's outputs reset to a high-impedance state, and the MAX1661's outputs reset to a low state. During the initial power-up sequence, as VCC increases, the ALERT pin goes low and then high, which indicates the device is powered on. The time between the low and high state on ALERT is the power-on delay time. Below VCC = 0.8V (typical) the POR states can't be enforced, and the I/O pins of all versions exhibit increasingly weak pull-down current capability, eventually becoming high impedance.

#### Thermal Shutdown

These devices have internal thermal-shutdown circuitry that turns off all output stages (I/O pins) when the junction temperature exceeds +140°C typical. Thermal shutdown only occurs during an overload condition on the I/O pins. The device cycles between thermal shutdown and the overcurrent condition until the overload condition is removed. This could cause a sustained START-STOP interrupt and, in the extreme case, tie up the master controller. However, the device asserts ALERT low, indicating this fault status.

#### \_Applications Information

Bypassing and Grounding Considerations Voltage transients exceeding 500mV at 25V/ $\mu$ s may trigger a false interrupt and thermal-shutdown indication. If large V<sub>CC</sub> transients are expected, add a 100 $\Omega$  resistor in series with V<sub>CC</sub>. Retain the 0.1 $\mu$ F capacitor from V<sub>CC</sub> to GND to act as a filter.

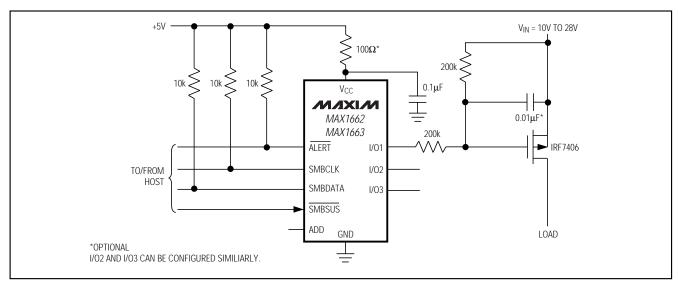

## P-Channel/N-Channel Load Switch with Controlled Turn-On

For a more controlled voltage-switching application, add a series resistor to slow the switch turn-on time. The external MOSFET gate has typical capacitance of 150pF to 2000pF, but an optional external capacitance can be added to further slow the switching time (Figure 6).

Figure 6. Load Switch with Controlled Turn-On

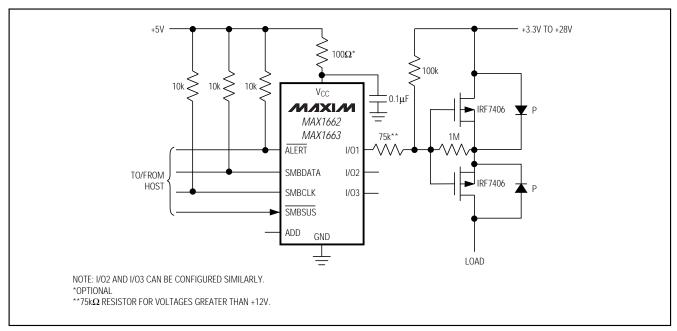

## Battery Switch with Back-to-Back MOSFETs

For battery-operated applications, use back-to-back MOSFETs to keep reverse currents from flowing from the load to the supply (Figure 7). This protects the battery from potential damage, and isolates the load from the power source.

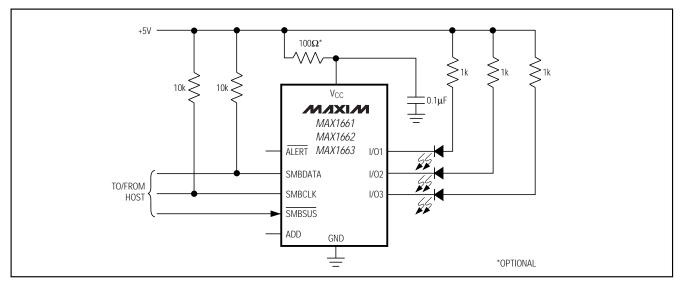

#### LED Drivers

A MAX1661/MAX1662/MAX1663 can be used as a programmable LED driver (Figure 8). With their low quiescent current, these devices are ideal for use as indicator light drivers on the front panel of a notebook computer.

Figure 7. Battery Switch with Back-to-Back MOSFETs

Figure 8. LED Drivers

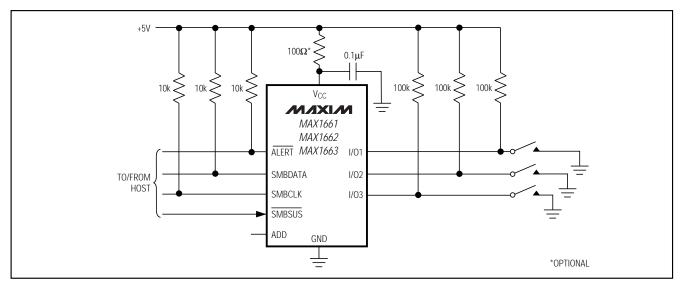

#### Mechanical Switch Monitor

The ability of the MAX1661/MAX1662/MAX1663 to read back the logic state of the I/Os makes them suitable for checking system status. They can be used as an "open-lid indicator", sensing a change in the I/O and sending an interrupt to the master to indicate a change in status (Figure 9). The same can be done to detect a chassis intrusion.

Simple High-Voltage Switch

For applications requiring a higher voltage, use a simple resistive divider to protect the gate from breakdown yet allow the MOSFETs to handle higher-voltage applications (Figure 10).

Figure 9. Open-Lid Detect or Chassis Intrusion Detector

Figure 10. Simple High-Voltage Switch

Chip Information

TRANSISTOR COUNT: 3334

SUBSTRATE CONNECTED TO GND

Package Information

**NOTES**

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

### **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

#### Maxim Integrated:

MAX708CPA+ MAX708CSA+ MAX708CSA+T MAX708ESA+ MAX708RESA+ MAX708SCSA+ MAX708SESA+ MAX708TCSA+ MAX708TEPA+ MAX708TESA+ MAX813LCPA+ MAX813LCSA+ MAX813LEPA+ MAX813LESA+ MAX813LCSA+T MAX813LESA+T MAX708TCUA+T MAX708TESA+T MAX708MJA/883B MAX706AREPA+ MAX706ARESA+T MAX706ARESA+T MAX706ARESA+T MAX706ARESA+T MAX706AREUA+T MAX706AREUA+T MAX706ASEPA+ MAX706ASESA+T MAX706ASEUA+T MAX706ASEUA+T MAX706ATESA+T MAX706ATESA+T MAX706ATESA+T MAX706ATESA+T MAX706ATESA+T MAX706ATESA+T MAX708ATESA+T MAX708ATES