# TLE 8718 SA

Smart 18-Channel Lowside Switch with Micro Second Bus

# Data Sheet

Rev. 1.1, 2012-07-31

# Automotive Power

#### **Table of Contents**

# **Table of Contents**

| <b>1</b><br>1.1                                                                 | Overview                                                                                                                                                                                                                                                                              |                                                    |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 2                                                                               | Block Diagram                                                                                                                                                                                                                                                                         | 7                                                  |

| <b>3</b><br>3.1<br>3.2<br>3.3                                                   | Pin Configuration         Pin Assignment         Pin Definitions and Functions         Abbreviations                                                                                                                                                                                  | 8<br>9                                             |

| <b>4</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.5                                     | General Product Characteristics       7         Test coverage (TC) in series production       7         Absolute Maximum Ratings       7         Thermal Resistance       7         ESD       7         Operating Range       7                                                       | 11<br>11<br>13<br>14                               |

| <b>5</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10 | Power StagesFunctional DescriptionPower Stages OUT1 and OUT3Power Stages OUT2 and OUT4Power Stages OUT5OUT8Power Stages OUT9 and OUT10Power Stages OUT11OUT14Power Stages OUT15 and OUT16Power Stages OUT17 and OUT18Timing Diagram MSC to OUTnParallel connection of PS              | 15<br>15<br>17<br>19<br>21<br>23<br>26<br>28<br>30 |

| <b>6</b><br>6.1<br>6.2<br>6.3<br>6.4                                            | Device Self Protection                                                                                                                                                                                                                                                                | 32<br>32<br>32                                     |

| 7                                                                               | Supervisory (DIS5_10, DELAYIN, DELAYOUT)                                                                                                                                                                                                                                              | 34                                                 |

| 8<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6                                     | Diagnosis       2         Diagnostic Functions       2         Encoding of Diagnostic Information       2         State Diagram of the Device Diagnosis       2         Reset of the Diagnostic Information       2         Electrical Characteristics       2         Timing       2 | 36<br>39<br>40<br>41<br>41                         |

| <b>9</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5                                     | Supply, $V_{DD}$ Monitoring, Reset and ABE       4         General functions of $V_{DD}$ Monitoring       4 $V_{DD}$ Undervoltage       4 $V_{DD}$ Overvoltage       4         Thresholds       4         ABE Pin       4                                                             | 43<br>44<br>44<br>45                               |

| 9.6<br>9.7<br>9.8                                                               | Testing of V <sub>DD</sub> Monitoring       4         Testing procedure of VDD Monitoring in the application       4         Electrical Characteristics       4                                                                                                                       | 46                                                 |

#### **Table of Contents**

| 10                                                                                                                                                                                                                                                                       | Device Logic Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 50                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

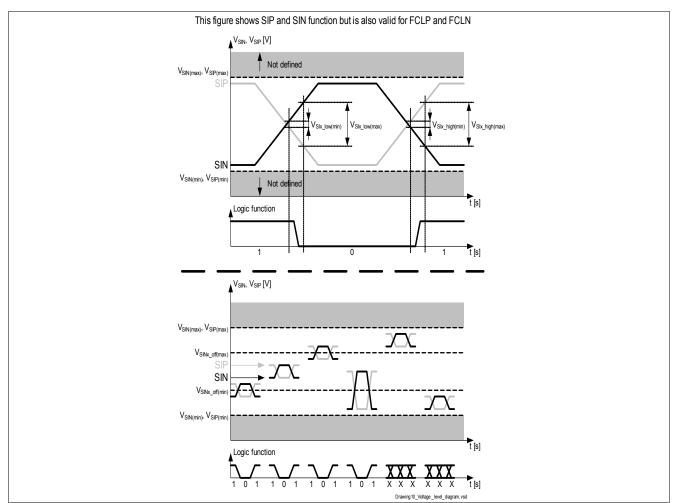

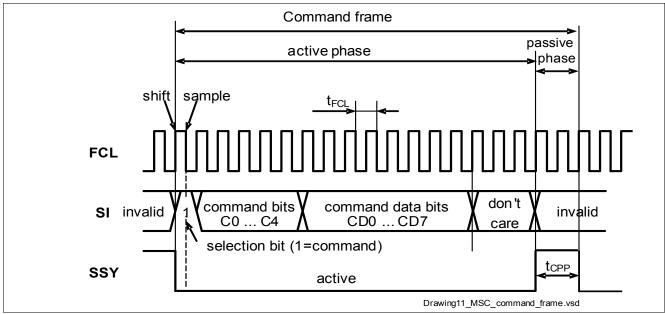

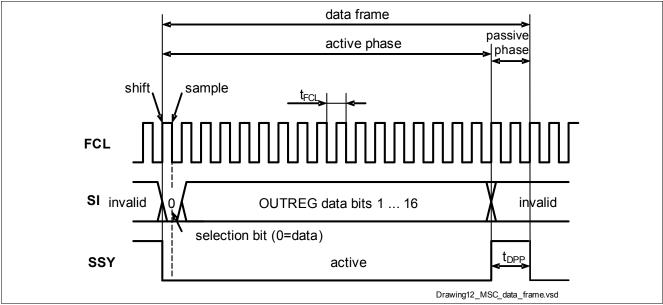

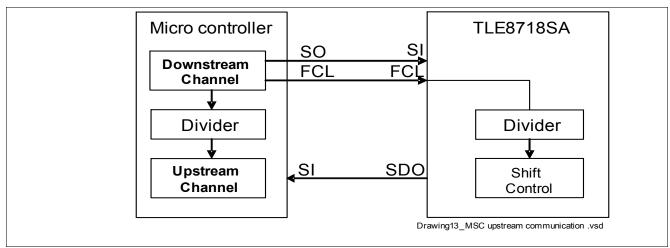

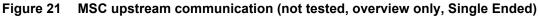

| <b>11</b><br>11.1<br>11.1.1<br>11.1.2<br>11.1.3<br>11.1.4<br>11.2                                                                                                                                                                                                        | Micro Second Channel MSC<br>Downstream Communication<br>Voltage Level Diagrams of low voltage differential pins<br>Downstream Supervisory Functions<br>Command Frame<br>Data Frame<br>Upstream Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 53<br>54<br>54<br>54<br>55<br>57                                                                   |

| 11.3<br>11.4<br>11.5                                                                                                                                                                                                                                                     | Timing Characteristics       Internal Clock Signal         Electrical Characteristics       Internal Clock Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 58                                                                                                 |

| <b>12</b><br>12.1<br>12.1.1<br>12.1.2<br>12.1.3<br>12.1.4<br>12.1.5<br>12.2<br>12.2.1<br>12.2.2<br>12.2.3<br>12.2.4<br>12.2.5<br>12.2.6<br>12.2.7<br>12.2.8<br>12.2.9<br>12.2.10<br>12.2.11<br>12.2.12<br>12.2.13<br>12.2.14<br>12.2.15<br>12.2.16<br>12.2.17<br>12.2.18 | Control of the device           Commands           WR_OUT1516           WR_RST           WR_START           RD_CONFIG           RD_DATA           Registers           CONREG1           CONREG2           CONREG3           CONREG4           OUT1516           OUT1516           OUT1516           OUT1516           OUTREG4           OUT1516           OUTREG_EVEN           OUTREG_ODD           DIAREG1           DIAREG1           DIAREG2           DIAREG3           DIAREG4           DIAREG5           DIAREG5           DIAREG5           DIAREG6           DIAREG5           REL_THRES           FUSE SC | 62<br>63<br>64<br>66<br>67<br>67<br>68<br>69<br>70<br>71<br>72<br>73<br>74<br>75<br>77<br>77<br>77 |

|                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                    |

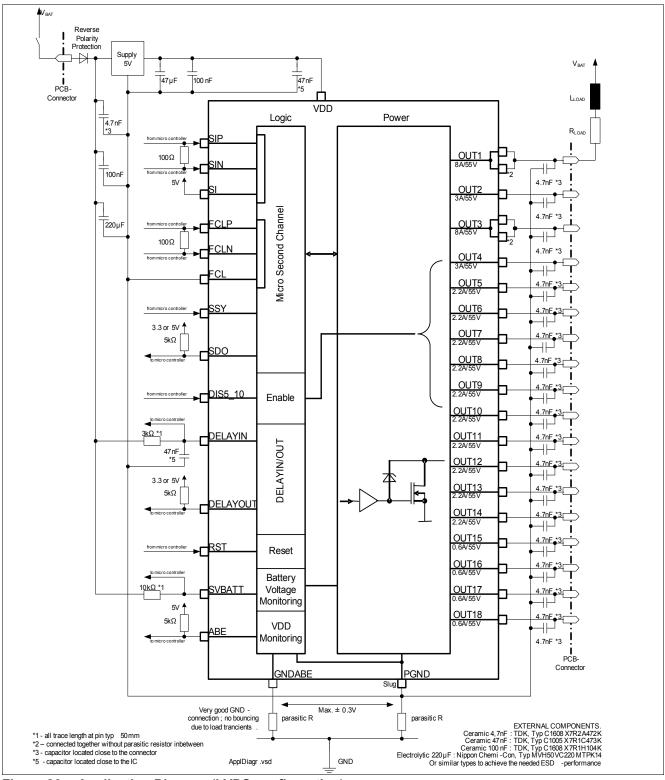

| 13                                                                                                                                                                                                                                                                       | Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                    |

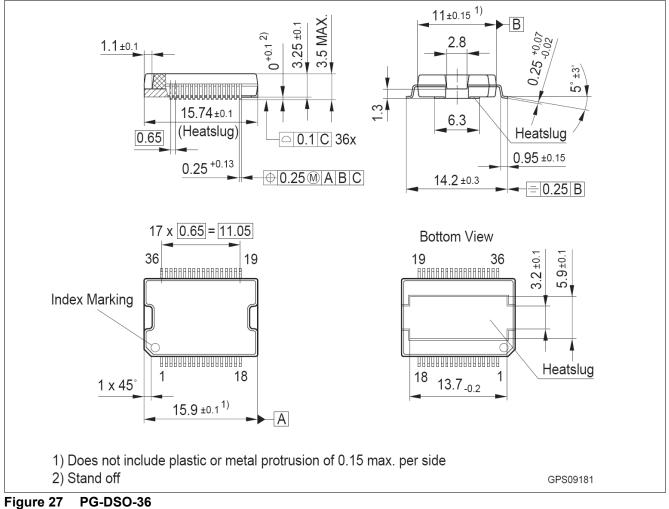

| 14<br>15                                                                                                                                                                                                                                                                 | Package Outlines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                    |

|                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>.</b> .                                                                                         |

# Smart 18-Channel Lowside Switch with Micro Second Bus speedFLEX

**TLE8718SA**

#### **Overview** 1

#### Features

- Operating Conditions -40...150°C

- **Over Temperature Warning** ٠

- ESD Capability 2/4KV HBM on-/off board Pins •

- Short Circuit Protected for V<sub>BAT</sub> = 36V •

- Active Zener Clamping at typically 55V •

- Open Load, Short to Ground, Short Circuit Diagnosis (2 bit/OUT) •

- Output control, diagnostics and initialisation via high speed ٠ serial communication: Micro Second Channel [MSC]

- all Pins protected against ≤36V •

- Over-Voltage and Under-Voltage Monitoring

- Two Output Channels operating during low supply voltage possible •

- Programmable Short circuit behavior: switch off or current limitation

- Green Product (RoHS compliant)

- **AEC Qualified**

#### Application

- Automotive Engine Management Applications

- Driver IC for inductive and ohmic actuators, such as Injectors, Solenoids, Relays, Lambda Heater. •

| Table 1 | Output Stage Overview and Product Summary |

|---------|-------------------------------------------|

|---------|-------------------------------------------|

| Output               | Maximum current      | RON_max at <i>Tj</i> = 150°C without clamping |

|----------------------|----------------------|-----------------------------------------------|

| OUT1, OUT3           | 8A                   | 200mΩ                                         |

| OUT2, OUT4           | 3A                   | 350mΩ                                         |

| OUT5OUT8             | 2.2A                 | 720mΩ                                         |

| OUT9OUT10            | 2.2A                 | 470mΩ                                         |

| OUT11OUT14           | 2.2A                 | 720mΩ                                         |

| OUT15, OUT16         | 0.6A                 | 2400mΩ                                        |

| OUT17, OUT18         | 0.6A                 | 2400mΩ                                        |

| Operating Voltage    | V <sub>DD_RES</sub>  | 2.5V (defined behavior of the device)         |

|                      | V <sub>DD_POR</sub>  | 33.5V (OUT15,16 delayed switch-off)           |

|                      | V <sub>DD</sub>      | 4.55.5V (operating range)                     |

| Active Zener Voltage | V <sub>DS (AZ)</sub> | 5060V                                         |

| Туре      | Package   | Marking   |  |  |

|-----------|-----------|-----------|--|--|

| TLE8718SA | PG-DSO-36 | TLE8718SA |  |  |

# 1.1 Device Description

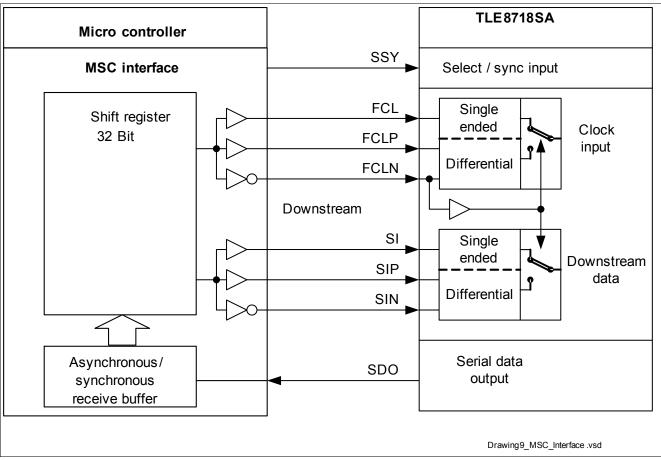

All stages are controlled by MSC interface. The MSC interface can be single ended or low voltage differential type. Serial transmission of the error code (diagnostic) via MSC interface (upstream channel).

All power stages (PS) are protected against short circuit to battery voltage (SCB). All PS (OUT1...18) are equipped with switch off mode and current control mode in case of SCB (configurable).

Diagnosis of open load (OL), short-circuit to ground (SCG), short-circuit to battery voltage (SCB) and over temperature (DOT) individually for each PS.

The fault conditions SCB, SCG, OL and DOT are not stored until an integrated filtering time has expired. If, at one output, several errors occur in a sequence, always the last detected error is stored (after filtering time). All fault conditions are encoded in two bits per stage and stored in the corresponding MSC interface registers. Additionally there is one common diagnostic bit for fault occurrence (FAILURE\_FLAG) at any output and one common diagnostic bit (COTW) for diagnosis over temperature (DOT). The diagnostic registers can be read via MSC interface. During the start-bit of a read out cycle the corresponding diagnostic register is cleared, nevertheless the status of the diagnostic register before the start-bit is send. Pull-down Diagnostic currents and Open Load OL can be switched off by configuration for OUT11...18; (CONREG3 and OUT1516).

Each stage (OUT1...14, 17, 18) is controlled with a separate bit of the data frame (downstream channel). The control bit is non inverting, i.e. if a control bit is '1' the corresponding stage is off. Stages are disabled – i.e. switched off and switching on disabled if  $V_{\text{DD}}$  is too low ( $V_{\text{DD}}$  undervoltage or power on reset) or  $V_{\text{DD}}$  too high ( $V_{\text{DD}}$  overvoltage). The same applies when the MSC monitoring detects an error, micro controller reset is active (i.e. external signal on pin RST = low or external signal on Pin ABE is logical low level).

All outputs are designed with internal zener diodes for applications with inductive loads.

OUT1 and OUT3 are designed for normal operation with 4A and extended current of 8A for maximum of 200 seconds each vehicle driving cycle.

OUT5...OUT10 are disabled by active low level on pins DIS5\_10 (with short delay).

OUT9 and OUT10 are designed for actuators with higher clamping energy.

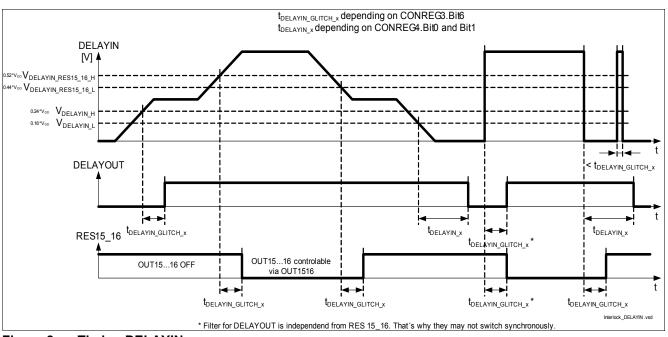

OUT15 and OUT16 can be forced OFF with the higher thresholds of DELAYIN ( $V_{DELAYIN\_RES15\_16\_L}$  and  $V_{DELAYIN\_RES15\_16\_H}$ ) (see **Figure 8**). OUT15 and OUT16 can be configured to delayed reset behavior, in this case, the switching-off algorithm is delayed by internal filtering time (exception: power on reset (POR), RES15\\_16 and valid command frame to switch off stages is not delayed).

Parallel connection of stages (OUT1...14, 17, 18) is possible as the control bits that switch on and off these stages are all transmitted in the same data frame. OUT15 and OUT16 are only allowed to be connected to each other and not to other stages (see **Chapter 5.10**).

DELAYOUT is pulled active low to switch off external components by the lower thresholds of DELAYIN ( $V_{DELAYIN_L}$  and  $V_{DELAYIN_H}$ ), ABE or  $V_{DD}$  monitoring.

#### Overview

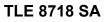

Figure 1 Output stages, functional schematic

**Block Diagram**

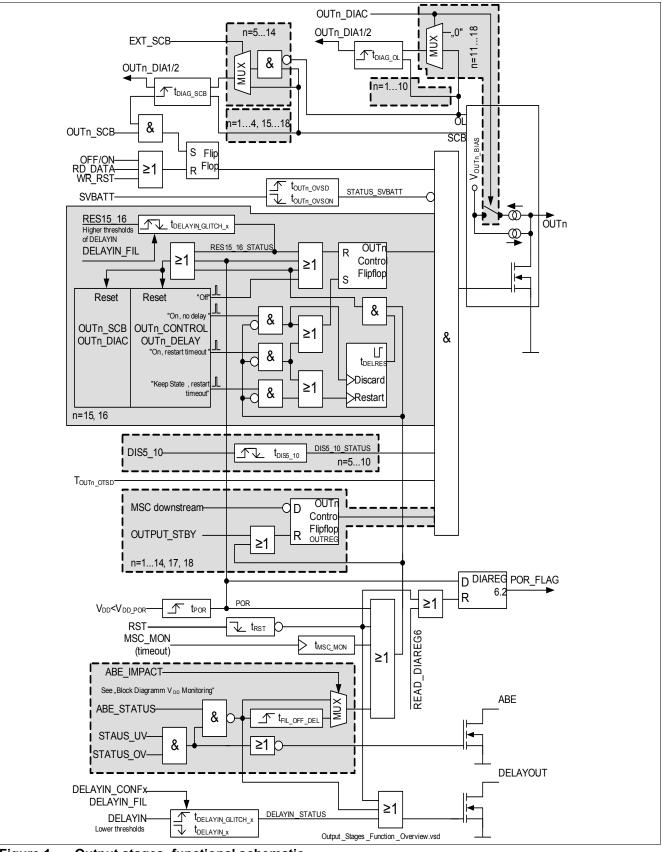

# 2 Block Diagram

Figure 2 Block Diagram

**Pin Configuration**

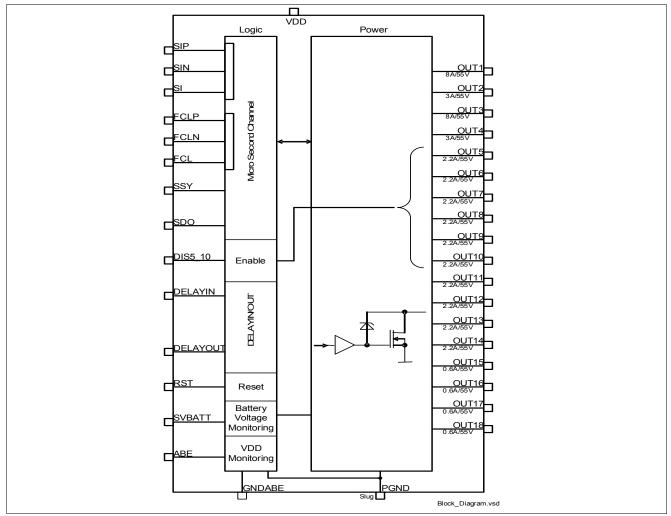

# 3 Pin Configuration

# 3.1 Pin Assignment

Figure 3 Pin Assignment

#### **Pin Configuration**

# 3.2 Pin Definitions and Functions

| Pin    | Symbol             | Function                                                                                                                                                                                                                                                          |

|--------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2   | OUT1 <sup>1)</sup> | Drain Connection of Power stage.                                                                                                                                                                                                                                  |

| 36     | OUT2               | Short circuit proof                                                                                                                                                                                                                                               |

| 17, 18 | OUT3 <sup>2)</sup> | Individually protected against overtemperature                                                                                                                                                                                                                    |

| 19     | OUT4               | ─ diagnostic functions                                                                                                                                                                                                                                            |

| 3      | OUT5               | Clamping of the output voltage by zener diodes                                                                                                                                                                                                                    |

| 35     | OUT6               |                                                                                                                                                                                                                                                                   |

| 16     | OUT7               |                                                                                                                                                                                                                                                                   |

| 20     | OUT8               |                                                                                                                                                                                                                                                                   |

| 4      | OUT9               |                                                                                                                                                                                                                                                                   |

| 34     | OUT10              |                                                                                                                                                                                                                                                                   |

| 15     | OUT11              |                                                                                                                                                                                                                                                                   |

| 21     | OUT12              |                                                                                                                                                                                                                                                                   |

| 5      | OUT13              |                                                                                                                                                                                                                                                                   |

| 33     | OUT14              |                                                                                                                                                                                                                                                                   |

| 14     | OUT15              |                                                                                                                                                                                                                                                                   |

| 22     | OUT16              |                                                                                                                                                                                                                                                                   |

| 6      | OUT17              |                                                                                                                                                                                                                                                                   |

| 32     | OUT18              |                                                                                                                                                                                                                                                                   |

| 9      | DIS5_10            | Disable pin for OUT5OUT10 (low level disables OUT5OUT10 after filtering time $(t_{\text{DIS5}\_10})$ has expired). The thresholds are defined in <b>Chapter 7</b> (active low, internal pull-up)                                                                  |

| 7      | DELAYIN            | DELAYIN input (internal pull-down, active low): Disable pin for DELAYOUT after the configurable filtering time ( $t_{\text{DELAYIN}}$ ) has expired and Reset pin for OUT15 and OUT16. The thresholds are defined in <b>Chapter 7</b> .                           |

| 8      | DELAYOUT           | Open drain output generating active low level if DELAYIN is low level (below $V_{\text{DELAYIN}_L}$ ) and $t_{\text{DELYAIN}}$ has expired, input ABE disables stages or $V_{\text{DD}}$ monitoring has detected a supply voltage failure. See <b>Chapter 7</b> . |

| 11     | ABE                | Bidirectional pin (active low).<br>Indicates VDD overvoltage and undervoltage condition by pulling ABE-pin low.<br>If forced to low from externally all stages are turned off.                                                                                    |

| 12     | GNDABE             | Sense ground. Reference ground for $V_{\rm DD}$ monitoring only. Connect this pin to ground.                                                                                                                                                                      |

| 13     | VDD                | Supply voltage 5V                                                                                                                                                                                                                                                 |

| 24     | SDO                | MSC interface. Upstream data, open drain output                                                                                                                                                                                                                   |

| 25     | SSY                | MSC interface. Chip select and synchronization strobe.                                                                                                                                                                                                            |

| 26     | SIP                | MSC interface. Downstream data positive for differential interface                                                                                                                                                                                                |

| 27     | SIN                | MSC interface. Downstream data negative for differential interface                                                                                                                                                                                                |

| 28     | SI                 | MSC interface optional downstream data input for single ended interface                                                                                                                                                                                           |

| 29     | FCLP               | MSC interface. Clock positive for differential interface                                                                                                                                                                                                          |

| 30     | FCLN               | MSC interface. Clock negative for differential interface                                                                                                                                                                                                          |

| 31     | FCL                | MSC interface optional clock input for single ended interface                                                                                                                                                                                                     |

#### **Pin Configuration**

| Pin  | Symbol | Function                                                                                                                                                                            |

|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23   | RST    | Reset input (active low, internal pull-up). Shuts down all stages regardless of their input signals. Clears the fault registers and resets the MSC interface registers (partially). |

| 10   | SVBATT | Sense Battery Voltage Monitoring Pin. Connect to V <sub>BAT</sub> . Used to activate factory test mode. See <b>Chapter 6.4</b> .                                                    |

| Slug | PGND   | Power Ground. Internally used as PGND. Analogue circuits except VDD-monitoring refer to PGND. Connect to Ground.                                                                    |

1) Pin1 and Pin2 have to be connected together without any parasitic resistor

2) Pin17 and Pin18 have to be connected together without any parasitic resistor in between.

# 3.3 Abbreviations

| Table 2 Abbreviation | ons                                                                                   |

|----------------------|---------------------------------------------------------------------------------------|

| ABE                  | "ABschaltung Endstufen" (switch off output stages)                                    |

| С                    | Command bit                                                                           |

| CD                   | Command data bit                                                                      |

| DC                   | Don't care bit                                                                        |

| DOT                  | Diagnosis overtemperature                                                             |

| LVDS                 | Low voltage differential signal                                                       |

| MSC                  | Micro Second Channel                                                                  |

| NCB                  | Number of bits of the active phase of a command frame                                 |

| NDB                  | Number of bits of the active phase of a data frame                                    |

| OL                   | Open Load (diagnostic stage information)                                              |

| OTSD                 | Over Temperature Shut Down (threshold to shut down stages for device self protection) |

| OTW                  | Over Temperature Warning (diagnostic information)                                     |

| POR                  | Power On Reset, including filter time t <sub>POR</sub>                                |

| PS                   | Power Stage(s)                                                                        |

| RST                  | ReSeT input pin                                                                       |

| SCB                  | Short Circuit to Battery (diagnostic stage information)                               |

| SCG                  | Short Circuit to Ground (diagnostic stage information)                                |

| SSY                  | Select / SYnc signal for MSC communication                                            |

| SB                   | Selection bit                                                                         |

| TC                   | Test coverage                                                                         |

| UD                   | Upstream data bit                                                                     |

# 4 General Product Characteristics

# 4.1 Test coverage (TC) in series production

In the standard production flow not all parameters can be covered due to technical or economic reasons. Therefore the following test coverage classes are defined:

A) Parameter test (parameter is measured in production test)

B) Go/NoGo test (parameter within specified range is guaranteed by Go/NoGo-test in production)

C) Specified by design (covered by lab tests, not considered within the standard production flow)

The given supply voltage range is only valid as long as the related function is active. (e.g. the power stages are shut off if  $V_{BAT} > 28V$ . In that case, no function is available to be tested at  $V_{BAT} = 40V$ ).

# 4.2 Absolute Maximum Ratings

The integrated circuit will not be damaged if maximum ratings are reached. Every maximum rating is allowed to be reached at the same time, as long as no other maximum rating is exceeded. But see **Item Note:**

Unless otherwise indicated all voltages are referred to PGND (all PGND and GNDABE are externally connected to each other) Positive current flows into the pin.

#### Table 3 Maximum Ratings

$T_j$  = -40°C to +150°C, all voltages with respect to PGND, positive current flowing into pin, unless otherwise specified

| Pos.   | Parameter                                                                          | Symbol                                                                                                                                                                                                                                                                                           | Va   | Values |   | ТС | Conditions                |  |

|--------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|---|----|---------------------------|--|

|        |                                                                                    |                                                                                                                                                                                                                                                                                                  | min. | max.   | _ |    |                           |  |

| Supp   | ly and Power Pins                                                                  |                                                                                                                                                                                                                                                                                                  |      |        |   |    | 1                         |  |

| 4.2.1  | Supply Voltage Range<br>pin VDD, static                                            | V <sub>DD_MR</sub>                                                                                                                                                                                                                                                                               | -0.3 | 36     | V | С  | -                         |  |

| 4.2.2  | Battery Voltage<br>stages output pins via load                                     | V <sub>BAT_MR</sub>                                                                                                                                                                                                                                                                              | -1   | 40     | V | С  | -                         |  |

| 4.2.3  | Total current over the PGND                                                        | I <sub>PGND_MR</sub>                                                                                                                                                                                                                                                                             | -38  | 38     | А | С  | -                         |  |

| 4.2.4  | Ground Voltage Offset<br>maximum permissible offset<br>between GNDABE and the PGND | dV <sub>GND_MR</sub>                                                                                                                                                                                                                                                                             | -0.3 | 0.3    | V | С  | -                         |  |

| 4.2.5  | Output Stages<br>static voltage OUTn (n=118)                                       | V <sub>OUTn_MR</sub>                                                                                                                                                                                                                                                                             | -0.3 | 50     | V | С  | OUTn OFF                  |  |

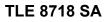

| 4.2.6  | Short Circuit to V <sub>BAT</sub><br>(single event)                                | V <sub>BAT_SC</sub>                                                                                                                                                                                                                                                                              | -0.3 | 36     | V | С  | OUTn (n=118),<br>Figure 4 |  |

| Interf | ace and Logic                                                                      |                                                                                                                                                                                                                                                                                                  |      |        |   |    |                           |  |

| 4.2.7  | Logic Input Pins<br>SIP, SIN, SI,<br>FCLP, FCLN, FCL,<br>SSY, DIS5_10, RST         | $V_{\text{SIP}_{\text{MR}}}, V_{\text{SIN}_{\text{MR}}}, V_{\text{SI}_{\text{MR}}}, V_{\text{FCLP}_{\text{MR}}}, V_{\text{FCLN}_{\text{MR}}}, V_{\text{FCLN}_{\text{MR}}}, V_{\text{FCL}_{\text{MR}}}, V_{\text{SSY}_{\text{MR}}}, V_{\text{DIS5}_{10}_{\text{MR}}}, V_{\text{RST}_{\text{MR}}}$ | -0.3 | 36     | V | С  | -                         |  |

| 4.2.8  | Bidirectional Pin ABE                                                              | V <sub>ABE_MR</sub>                                                                                                                                                                                                                                                                              | -0.3 | 36     | V | С  | -                         |  |

| 4.2.9  | Output Pins<br>DELAYOUT, SDO                                                       | $V_{\text{DELAYOUT_MR}}$<br>$V_{\text{SDO_MR}}$                                                                                                                                                                                                                                                  | -0.3 | 36     | V | С  | -                         |  |

#### Table 3Maximum Ratings

$T_{j}$  = -40°C to +150°C, all voltages with respect to PGND, positive current flowing into pin, unless otherwise specified

| Pos.   | Parameter                                                                                           | Symbol                                                                                                                                                                                                                                                                                           | Values |      | Unit | тс | Conditions |  |

|--------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|----|------------|--|

|        |                                                                                                     |                                                                                                                                                                                                                                                                                                  | min.   | max. | 1    |    |            |  |

| 4.2.10 | Input Pins<br>DELAYIN, SVBATT                                                                       | $V_{\text{DELAYIN}_{MR,}}$<br>$V_{\text{SVBATT}_{MR}}$                                                                                                                                                                                                                                           | -0.3   | 40   | V    | С  | -          |  |

| 4.2.11 | Current into Pin<br>SIP, SIN, SI,<br>FCLP, FCLN, FCL,<br>SSY, DIS5_10, RST,<br>DELAYIN, SVBATT, SDO | I <sub>SIP_MR</sub> , I <sub>SIN_MR</sub> , I <sub>SI_MR</sub> ,<br>I <sub>FCLP_MR</sub> , I <sub>FCLN_MR</sub> ,<br>I <sub>FCL_MR</sub> , I <sub>SSY_MR</sub> ,<br>I <sub>DIS5_10_MR</sub> , I <sub>RST_MR</sub> ,<br>I <sub>DELAYIN_MR</sub> ,<br>I <sub>SVBATT_MR</sub> , I <sub>SDO_MR</sub> | -10    | 10   | mA   | С  | 1)         |  |

| 4.2.12 | Current into Pin DELAYOUT, ABE                                                                      | I <sub>DELAYOUT_MR</sub> , I <sub>ABE_MR</sub>                                                                                                                                                                                                                                                   | -10    | 15   | mA   | С  | 1)         |  |

| Temp   | eratures                                                                                            |                                                                                                                                                                                                                                                                                                  |        |      |      |    |            |  |

| 4.2.13 | Junction Temperature                                                                                | Tj                                                                                                                                                                                                                                                                                               | -40    | 150  | °C   | С  | -          |  |

| 4.2.14 | Storage Temperature                                                                                 | T <sub>STG</sub>                                                                                                                                                                                                                                                                                 | -55    | 150  | °C   | С  | -          |  |

1) Other maximum ratings (like Item 4.2.7 to Item 4.2.10 or Item 4.2.13) are not allowed to be exceeded.

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous or repetitive operation.

Figure 4 Short Circuit test set-up

## 4.3 Thermal Resistance

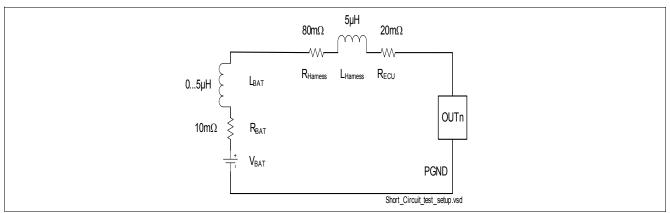

Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

#### Table 4 Thermal Resistance

$T_{j}$  = -40°C to +150°C, all voltages with respect to PGND, positive current flowing into pin, unless otherwise specified

| Pos.  | Parameter           | Symbol            | I Values<br>min. typ. max. |    | Values |     |   | ol Value:                  |  | Unit | тс | Conditions |

|-------|---------------------|-------------------|----------------------------|----|--------|-----|---|----------------------------|--|------|----|------------|

|       |                     |                   |                            |    |        |     |   |                            |  |      |    |            |

| 4.3.1 | Junction to Case    | R <sub>thJC</sub> | -                          | -  | 2      | K/W | С | 1)                         |  |      |    |            |

| 4.3.2 | Junction to Ambient | R <sub>thJA</sub> | -                          | 25 | -      | K/W | С | see Figure 5 <sup>1)</sup> |  |      |    |            |

1) Power dissipation Pv=3W distributed statically and homogeneously over all power stages. Resistive Load.

Figure 5 Thermal simulation - PCB setup

## 4.4 ESD

Of the various ESD models, the integrated circuit meets at least the "human body model" according to the requirements of the EIA/JESD22-A114-F. During manufacturing process, ESD pulses according to "charged device model" (EIA/JESD22-C101-D) may be exposed to each pin. ESD Specification Details in the following Table.

#### Table 5ESD Susceptibility

$T_j$  = -40°C to +150°C, all voltages with respect to PGND, positive current flowing into pin, unless otherwise specified

| Pos.   | Parameter                                                        | Symbol            |      | Values |      |          | тс | Conditions          |

|--------|------------------------------------------------------------------|-------------------|------|--------|------|----------|----|---------------------|

|        |                                                                  |                   | min. | typ.   | max. |          |    |                     |

| Standa | ard Requirements for all Pins                                    |                   |      |        |      |          |    |                     |

| 4.4.1  | Electro Static Discharge Voltage<br>"Human-Body-Model – HBM"     | V <sub>ESD1</sub> | -2   | -      | 2    | kV       | С  | All Pins            |

| 4.4.2  | Electro Static Discharge Voltage<br>"Charged-Device-Model – CDM" | V <sub>ESD2</sub> | -500 | -      | 500  | V        | С  | All Pins            |

| Pins w | ith Extended Requirements                                        |                   |      |        |      | <b>I</b> | 1  |                     |

| 4.4.3  | Electro Static Discharge Voltage<br>"Human-Body-Model – HBM"     | V <sub>ESD3</sub> | -6   | -      | 6    | kV       | С  | OUT114<br>vs. PGND  |

| 4.4.4  | Electro Static Discharge Voltage<br>"Human-Body-Model – HBM"     | V <sub>ESD4</sub> | -4   | -      | 4    | kV       | С  | OUT1518<br>vs. PGND |

## 4.5 Operating Range

#### Table 6Operating Range

$T_j$  = -40°C to +150°C, all voltages with respect to PGND, positive current flowing into pin, unless otherwise specified

| Pos.  | Parameter                  | Symbol                 | Va       | Values |   | Values |    | тс | Conditions |

|-------|----------------------------|------------------------|----------|--------|---|--------|----|----|------------|

|       |                            |                        | min.     | max.   |   |        |    |    |            |

| Suppl | y, Battery Voltage         |                        | <b>I</b> |        |   |        |    |    |            |

| 4.5.1 | Supply Voltage Range       | V <sub>DD</sub>        | 4.5      | 5.5    | V | С      | -  |    |            |

| 4.5.2 | Battery Voltage            | V <sub>BAT(typ)</sub>  | 1        | 3.5    | V | С      | -  |    |            |

| 4.5.3 | Nominal Total PGND Current | I <sub>PGND(typ)</sub> | -12      | 0      | А | С      | 1) |    |            |

Total PGND current influences e.g. the RON-measurement of the Power Stages or voltage thresholds of the input buffers because of common PGND bond wires. As basis for definition of the RON or the voltage thresholds, the defined PGND current is used.

## 5.1 Functional Description

The following general description is valid for the channel groups OUT1,3, OUT2,4, OUT5...8, OUT9,10, OUT11...14, OUT17,18. The specific function of the channel group OUT15,16 is described in **Chapter 5.7**.

The reset input of the OUTn-control flip-flop is active high and dominant, delivering a logic low level at the output of the OUTn-control flip-flop.Only in failure-free condition, output can be switched on by MSC downstream.

Disabling inputs DIS5\_10 and DELAYIN have different input characteristics and delay ( $t_{\text{DELAYIN}} >> t_{\text{DIS5}_10}$ ). For details concerning DIS5\_10, DELAYIN and DELAYOUT see **Chapter 7** and **Figure 1**.

# 5.2 Power Stages OUT1 and OUT3

#### Table 7 Electrical Characteristics Power Stages OUT1 and OUT3

n = 1 and 3, all channels ON or OFF, nominal load conditions,  $4.5V < V_{DD} < 5.5V$ ,  $4.5V < V_{BAT} < 40V$ , all voltages with respect to PGND, positive current flowing into pin.  $T_i = -40^{\circ}C$  to  $+150^{\circ}C$ , unless otherwise specified

| Pos.   | Parameter                                                                  | Symbol                      |      | Value | S    | Unit | тс | Conditions                                                 |

|--------|----------------------------------------------------------------------------|-----------------------------|------|-------|------|------|----|------------------------------------------------------------|

|        |                                                                            |                             | min. | typ.  | max. |      |    |                                                            |

| Load ( | Current                                                                    |                             | 1    | -     | 1    |      |    | 1                                                          |

| 5.2.1  | Continuous Load Current                                                    | $I_{\rm OUTn}$              | -    | -     | 4    | А    | С  |                                                            |

| 5.2.2  | Extended Load Current                                                      | $I_{\rm OUTn\_ex}$          | -    | -     | 8    | А    | С  | max 800h                                                   |

| 5.2.3  | Extended current time,<br>Accumulated operating time                       | t <sub>OUTn_ec</sub>        | -    | -     | 60   | h    | С  | V <sub>BAT</sub> ≤14V,<br>R <sub>L</sub> ≥0.88Ω            |

| 5.2.4  | Maximum current, (short circuit limited current / switch off threshold)    | $I_{\rm OUTn\_max}$         | 8    | -     | 12.5 | A    | A  |                                                            |

| ON-Re  | esistance without clamping <sup>1)</sup>                                   |                             |      | 1     | 4    |      |    | 1                                                          |

| 5.2.5  | On Resistance <i>Tj</i> =-40°C                                             | R <sub>on-40_n</sub>        | -    | -     | 120  | mΩ   | С  | I <sub>OUTn</sub> =4A                                      |

| 5.2.6  | On Resistance <i>Tj</i> =25°C                                              | R <sub>on+25_n</sub>        | -    | -     | 148  | mΩ   | С  | I <sub>OUTn</sub> =4A                                      |

| 5.2.7  | On Resistance <i>Tj</i> =150°C                                             | R <sub>on+150_n</sub>       | -    | _     | 200  | mΩ   | А  | I <sub>OUTn</sub> =4A                                      |

| 5.2.8  | On Resistance <i>Tj</i> ≤150°C                                             | R <sub>on_n</sub>           | -    | _     | 210  | mΩ   | С  | I <sub>OUTn</sub> <8A                                      |

| ON-Re  | esistance with clamping <sup>2)</sup>                                      |                             |      | 1     | 4    |      |    |                                                            |

| 5.2.9  | On Resistance <i>Tj</i> =-40°C                                             | R <sub>on-40_n</sub>        | -    | -     | 156  | mΩ   | С  | I <sub>OUTn</sub> =4A                                      |

| 5.2.10 | On Resistance <i>Tj</i> =25°C                                              | <i>R</i> <sub>on+25_n</sub> | -    | _     | 193  | mΩ   | С  | I <sub>OUTn</sub> =4A                                      |

| 5.2.11 | On Resistance <i>Tj</i> =150°C                                             | R <sub>on+150_n</sub>       | -    | -     | 260  | mΩ   | А  | I <sub>OUTn</sub> =4A                                      |

| 5.2.12 | On Resistance <i>Tj</i> ≤150°C                                             | R <sub>on_n</sub>           | -    | -     | 273  | mΩ   | С  | I <sub>OUTn</sub> <8A                                      |

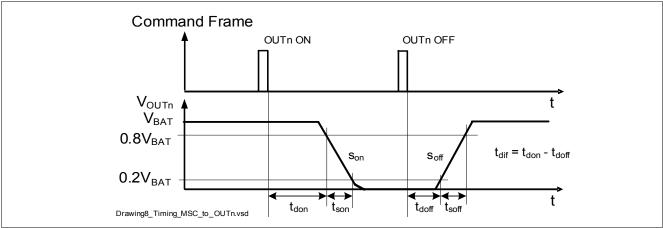

| Delay  | times, Slew rates (see Figure 6)                                           |                             |      |       |      |      |    |                                                            |

| 5.2.13 | Switch on delay                                                            | t <sub>don_n</sub>          | -    | -     | 15   | μs   | С  | $R_{\text{Load}}$ =5.9 $\Omega$ ,<br>$V_{\text{BAT}}$ =14V |

| 5.2.14 | Switch off delay                                                           | t <sub>doff_n</sub>         | -    | -     | 15   | μs   | С  | $R_{\text{Load}}$ =5.9 $\Omega$ ,<br>$V_{\text{BAT}}$ =14V |

| 5.2.15 | Difference of switch on and off delay $t_{dif_n} = t_{don_n} - t_{doff_n}$ | t <sub>dif_n</sub>          | -8   | -     | 8    | μs   | С  | $R_{\text{Load}}$ =5.9 $\Omega$ ,<br>$V_{\text{BAT}}$ =14V |

| 5.2.16 |                                                                            | S <sub>on_n</sub>           | 0.5  | 1     | 2.5  | V/µs | С  | $R_{\text{Load}}$ =5.9 $\Omega$ ,<br>$V_{\text{BAT}}$ =14V |

#### Table 7 Electrical Characteristics Power Stages OUT1 and OUT3

n = 1 and 3, all channels ON or OFF, nominal load conditions,  $4.5V < V_{DD} < 5.5V$ ,  $4.5V < V_{BAT} < 40V$ , all voltages with respect to PGND, positive current flowing into pin.  $T_i = -40^{\circ}C$  to  $+150^{\circ}C$ , unless otherwise specified

| Pos.   | Parameter                                                                                                                                                                                                                                                                                                                        | Symbol                   |      | Value | S    | Unit | тс | Conditions                                                            |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|-------|------|------|----|-----------------------------------------------------------------------|

|        |                                                                                                                                                                                                                                                                                                                                  |                          | min. | typ.  | max. | -    |    |                                                                       |

| 5.2.17 | Switch off slew rates                                                                                                                                                                                                                                                                                                            | S <sub>off_n</sub>       | 0.5  | 1     | 2.5  | V/µs | С  | $R_{ m Load}$ =5.9 $\Omega$ ,<br>$V_{ m BAT}$ =14V                    |

| Leaka  | ge current                                                                                                                                                                                                                                                                                                                       |                          |      |       |      |      |    |                                                                       |

| 5.2.18 | Leakage current of the Output Stage                                                                                                                                                                                                                                                                                              | I <sub>LOUTn</sub>       | -    | -     | 5    | μA   | С  | V <sub>OUTn</sub> =14V,<br>V <sub>DD</sub> =0V, <i>Tj</i> =60°(       |

| 5.2.19 | Leakage current of the Output Stage                                                                                                                                                                                                                                                                                              | I <sub>LOUTn</sub>       | -    | -     | 10   | μA   | С  | V <sub>OUTn</sub> =28V,<br>V <sub>DD</sub> =0V, <i>Tj</i> =60°        |

| 5.2.20 | Leakage current of the Output Stage                                                                                                                                                                                                                                                                                              | I <sub>LOUTn</sub>       | _    | -     | 30   | μA   | A  | V <sub>OUTn</sub> <28V,<br>V <sub>DD</sub> =0V,<br><i>Tj</i> =150°C   |

| Clamp  | ing voltage                                                                                                                                                                                                                                                                                                                      |                          |      |       |      |      |    | I                                                                     |

| 5.2.21 |                                                                                                                                                                                                                                                                                                                                  | $V_{\rm CL_n}$           | 50   | -     | 60   | V    | С  | I <sub>OUTn</sub> =3A                                                 |

| 5.2.22 | Clamping voltage                                                                                                                                                                                                                                                                                                                 | V <sub>CL_n</sub>        | 50   | _     | 60   | V    | А  | I <sub>OUTn</sub> =0.2A                                               |

| Clamp  | ing energy <sup>3)</sup>                                                                                                                                                                                                                                                                                                         | - <u>-</u>               |      |       |      |      |    |                                                                       |

| 5.2.23 | Standard operating range, max. 1000Mio cycles                                                                                                                                                                                                                                                                                    | $E_{\rm CL\_OUTn}$       | -    | -     | 25   | mJ   | С  | <i>Tj</i> <sub>(0)</sub> =125°C,<br><i>I</i> <sub>OUTn(0)</sub> <2.8A |

| 5.2.24 | Jump Start, max. 0.01Mio cycles                                                                                                                                                                                                                                                                                                  | $E_{\rm CL\_OUTn}$       | -    | -     | 27   | mJ   | С  | <i>Tj</i> <sub>(0)</sub> =85°C,<br><i>I</i> <sub>OUTn(0)</sub> <5.6A  |

| 5.2.25 | Load Dump, max. 10 pulses                                                                                                                                                                                                                                                                                                        | $E_{\rm CL\_OUTn}$       | -    | -     | 90   | mJ   | С  | <i>Tj</i> <sub>(0)</sub> =35°C,<br><i>I</i> <sub>OUTn(0)</sub> <8A    |

| 5.2.26 | Load Dump, max. 10 pulses                                                                                                                                                                                                                                                                                                        | $E_{\rm CL\_OUTn}$       | -    | -     | 26   | mJ   | С  | <i>Tj</i> <sub>(0)</sub> =150°C,<br><i>I</i> <sub>OUTn(0)</sub> <8A   |

| Revers | se current through OUTn                                                                                                                                                                                                                                                                                                          |                          |      |       |      |      |    |                                                                       |

| 5.2.27 | In operation mode, static, no destruction                                                                                                                                                                                                                                                                                        | $I_{\rm R\_S\_OUTn}$     | -3   | -     | -    | Α    | С  | <i>Tj</i> =150°C, <i>V</i> <sub>DD</sub> =5                           |

| 5.2.28 | Without supply voltage, possibly Leakage<br>Current out of neighbor channels.<br>10ms after the reverse current disappears<br>leakage current criteria are kept.                                                                                                                                                                 | I <sub>R_Soff_OUTn</sub> | -3   | _     | _    | A    | С  | V <sub>DD</sub> <1V                                                   |

| 5.2.29 | In operation mode, No unwanted<br>switching of channels; No unwanted<br>Reset, No unwanted change of Voltage<br>Monitoring Thresholds; No unwanted<br>communication errors or register changes<br>beside diagnostic registers.<br>Possibly unwanted diagnostic entries.<br>Possibly Leakage Current out of neighbor<br>channels. | $I_{\rm R_S_OUTn}$       | -1.5 | -     | -    | A    | С  | <i>Tj</i> =150°C,<br><i>V</i> <sub>DD</sub> =5V                       |

Item 5.2.5 to Item 5.2.8 has to be considered for applications with resistive load or inductive load with external freewheeling.

2) Item 5.2.9 to Item 5.2.12 has to be considered for applications where clamping occurs.

3) Clamping energy, Linear decreasing current, fcl<67Hz.

# 5.3 Power Stages OUT2 and OUT4

#### Table 8 Electrical Characteristics Power Stages OUT2 and OUT4

n = 2 and 4, all channels ON or OFF, nominal load conditions,  $4.5V < V_{DD} < 5.5V$ ,  $4.5V < V_{BAT} < 40V$ , all voltages with respect to PGND, positive current flowing into pin.,  $T_j = -40^{\circ}C$  to  $+150^{\circ}C$ , unless otherwise specified

| Pos.   | Parameter                                                                  | Symbol                      |      | Value | s    | Unit | тс | Conditions                                                          |

|--------|----------------------------------------------------------------------------|-----------------------------|------|-------|------|------|----|---------------------------------------------------------------------|

|        |                                                                            |                             | min. | typ.  | max. |      |    |                                                                     |

| Load C | Current                                                                    | ł                           |      |       |      |      | 1  | L                                                                   |

| 5.3.1  | Continuous Load Current                                                    | $I_{\rm OUTn}$              | -    | _     | 3    | А    | С  |                                                                     |

| 5.3.2  | Extended Current time<br>Accumulated Operating time                        | t <sub>OUTn_ec</sub>        | -    | -     | 100  | h    | С  | V <sub>BAT</sub> ≤14V,<br>R <sub>L</sub> ≥1.98Ω                     |

| 5.3.3  | Maximum Current, (short circuit limited current / switch off threshold)    | $I_{\rm OUTn\_max}$         | 3    | -     | 6    | A    | A  |                                                                     |

| ON-Re  | esistance without clamping <sup>1)</sup>                                   |                             |      |       |      |      |    | L                                                                   |

| 5.3.4  | On Resistance <i>Tj</i> =-40°C                                             | R <sub>on-40_n</sub>        | -    | _     | 210  | mΩ   | С  | I <sub>OUTn</sub> =3A                                               |

| 5.3.5  | On Resistance <i>Tj</i> =25°C                                              | R <sub>on+25_n</sub>        | _    | _     | 259  | mΩ   | С  | I <sub>OUTn</sub> =3A                                               |

| 5.3.6  | On Resistance <i>Tj</i> ≤150°C                                             | R <sub>on_n</sub>           | -    | _     | 350  | mΩ   | А  | I <sub>OUTn</sub> =3A                                               |

| ON-Re  | sistance with clamping <sup>2)</sup>                                       |                             |      |       |      |      |    | L                                                                   |

| 5.3.7  | On Resistance <i>Tj</i> =-40°C                                             | <i>R</i> <sub>on-40_n</sub> | -    | _     | 273  | mΩ   | С  | I <sub>OUTn</sub> =3A                                               |

| 5.3.8  | On Resistance <i>Tj</i> =25°C                                              | R <sub>on+25_n</sub>        | -    | -     | 337  | mΩ   | С  | I <sub>OUTn</sub> =3A                                               |

| 5.3.9  | On Resistance <i>Tj</i> ≤150°C                                             | R <sub>on_n</sub>           | -    | -     | 455  | mΩ   | А  | I <sub>OUTn</sub> =3A                                               |

| Delay  | times, Slew rates (see Figure 6)                                           |                             |      |       |      |      |    | L                                                                   |

| 5.3.10 | Switch on delay                                                            | t <sub>don_n</sub>          | -    | -     | 15   | μs   | С  | $R_{\text{Load}}$ =5.9 $\Omega$ ,<br>$V_{\text{BAT}}$ =14V          |

| 5.3.11 | Switch off delay                                                           | t <sub>doff_n</sub>         | -    | -     | 15   | μs   | С  | $R_{\text{Load}}$ =5.9 $\Omega$ ,<br>$V_{\text{BAT}}$ =14V          |

| 5.3.12 | Difference of switch on and off delay $t_{dif_n} = t_{don_n} - t_{doff_n}$ | t <sub>dif_n</sub>          | -5   | -     | 5    | μs   | С  | $R_{\text{Load}}$ =5.9 $\Omega$ ,<br>$V_{\text{BAT}}$ =14V          |

| 5.3.13 |                                                                            | s <sub>on_n</sub>           | 1.1  | 2.5   | 5.8  | V/µs | С  | $R_{\text{Load}}$ =5.9 $\Omega$ ,<br>$V_{\text{BAT}}$ =14V          |

| 5.3.14 | Switch off slew rates                                                      | S <sub>off_n</sub>          | 1.1  | 2.5   | 5.8  | V/µs | С  | $R_{\text{Load}}$ =5.9 $\Omega$ ,<br>$V_{\text{BAT}}$ =14V          |

| Leaka  | ge current                                                                 | ł                           |      |       |      |      |    | L                                                                   |

| 5.3.15 | Leakage current of the Output Stage                                        | I <sub>L_OUTn</sub>         | -    | -     | 5    | μA   | С  | V <sub>OUTn</sub> =14V,<br>V <sub>DD</sub> =0V, <i>Tj</i> =60°0     |

| 5.3.16 | Leakage current of the Output Stage                                        | $I_{\rm I\_OUTn}$           | -    | -     | 10   | μA   | С  | V <sub>OUTn</sub> =28V,<br>V <sub>DD</sub> =0V, <i>Tj</i> =60°0     |

| 5.3.17 | Leakage current of the Output Stage                                        | I <sub>LOUTn</sub>          | -    | -     | 30   | μA   | A  | V <sub>OUTn</sub> <28V,<br>V <sub>DD</sub> =0V,<br><i>Tj</i> =150°C |

| Clamp  | ing voltage                                                                |                             | 1    |       |      |      |    |                                                                     |

| 5.3.18 | Clamping voltage                                                           | $V_{\rm CL_n}$              | 50   | -     | 60   | V    | С  | I <sub>OUTn</sub> =3A                                               |

| 5.3.19 | Clamping voltage                                                           | V <sub>CL_n</sub>           | 50   | _     | 60   | V    | А  | I <sub>OUTn</sub> =0.2A                                             |

#### Table 8 Electrical Characteristics Power Stages OUT2 and OUT4

n = 2 and 4, all channels ON or OFF, nominal load conditions,  $4.5V < V_{DD} < 5.5V$ ,  $4.5V < V_{BAT} < 40V$ , all voltages with respect to PGND, positive current flowing into pin.,  $T_i = -40^{\circ}C$  to  $+150^{\circ}C$ , unless otherwise specified

| Pos.   | Parameter                                                                                                                                                                                                                                                                                                                        | Symbol                   |      | Value | s    | Unit | тс | Conditions                                                             |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|-------|------|------|----|------------------------------------------------------------------------|

|        |                                                                                                                                                                                                                                                                                                                                  |                          | min. | typ.  | max. |      |    |                                                                        |

| Clamp  | ing energy <sup>3)</sup>                                                                                                                                                                                                                                                                                                         |                          | 1    | 1     | 1    |      |    |                                                                        |

| 5.3.20 | Standard operating range, max. 1000Mio cycles                                                                                                                                                                                                                                                                                    | $E_{\rm CL\_OUTn}$       | -    | -     | 22   | mJ   | С  | <i>Tj</i> <sub>(0)</sub> =125°C,<br><i>I</i> <sub>OUTn(0)</sub> <1.05A |

| 5.3.21 | Jump Start, max. 0.01Mio cycles                                                                                                                                                                                                                                                                                                  | $E_{\rm CL_OUTn}$        | -    | -     | 18   | mJ   | С  | <i>Tj</i> <sub>(0)</sub> =85°C,<br><i>I</i> <sub>OUTn(0)</sub> <2.1A   |

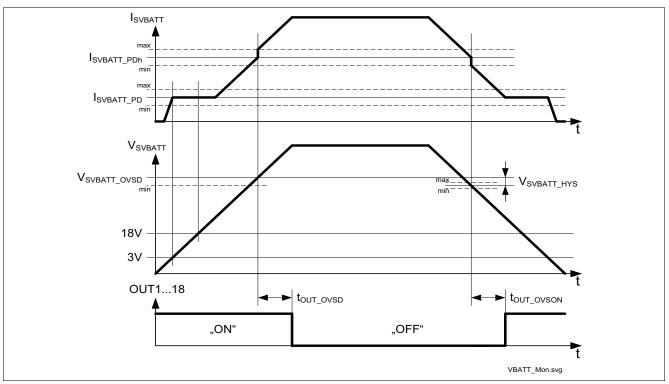

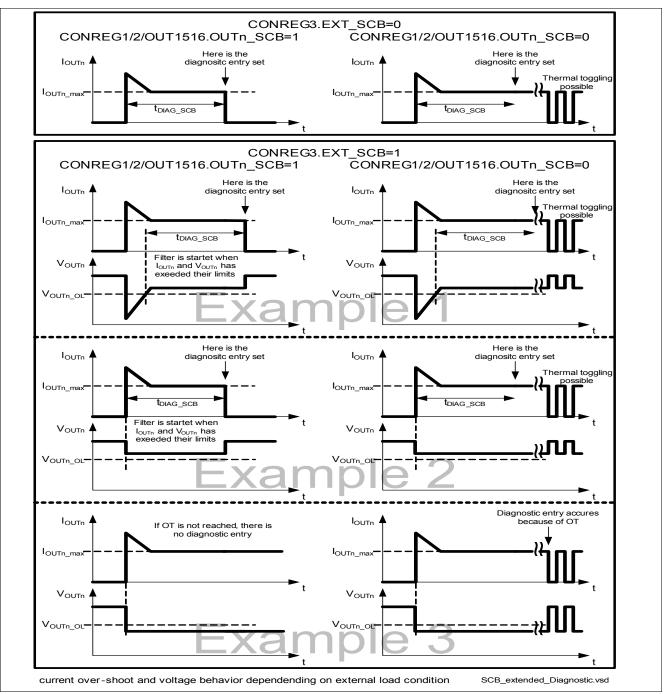

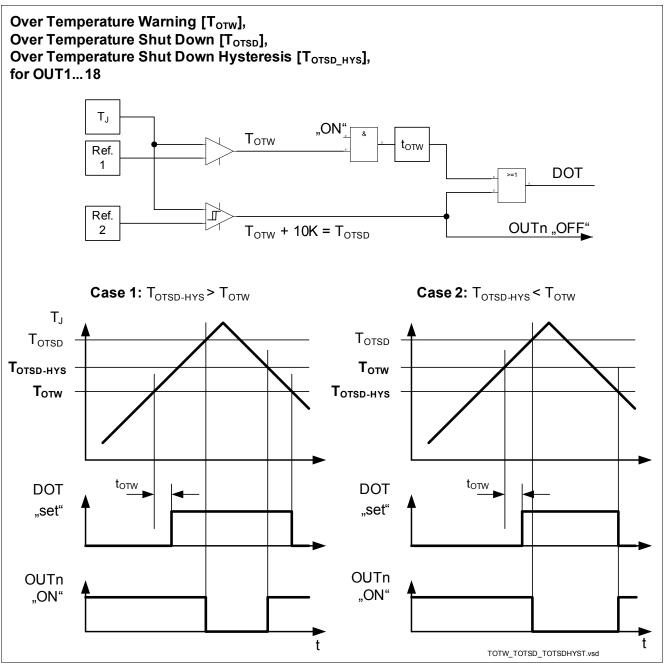

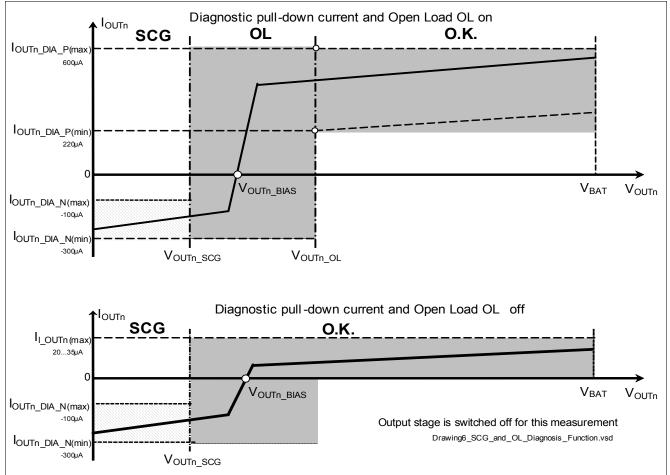

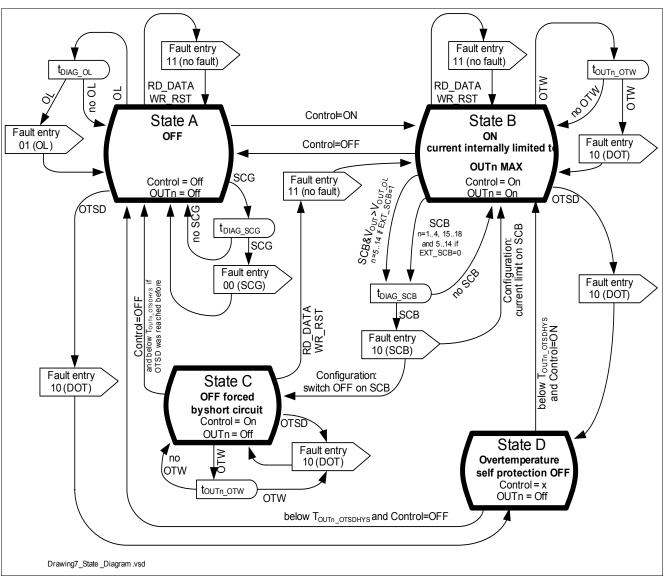

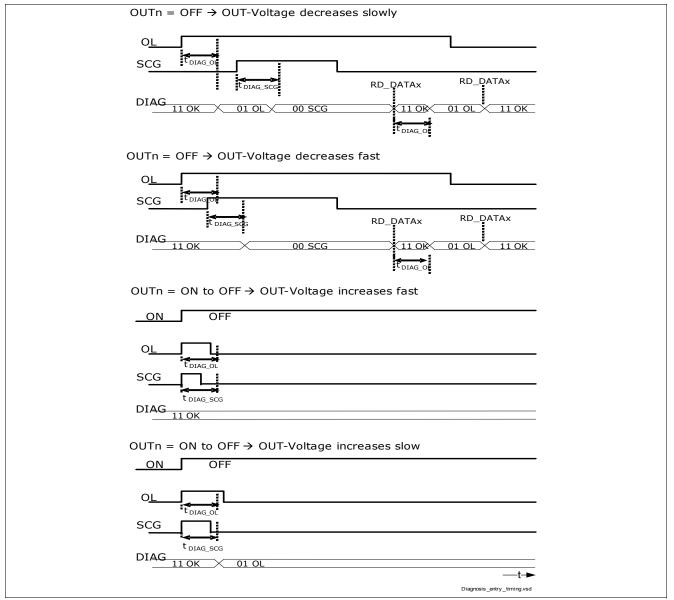

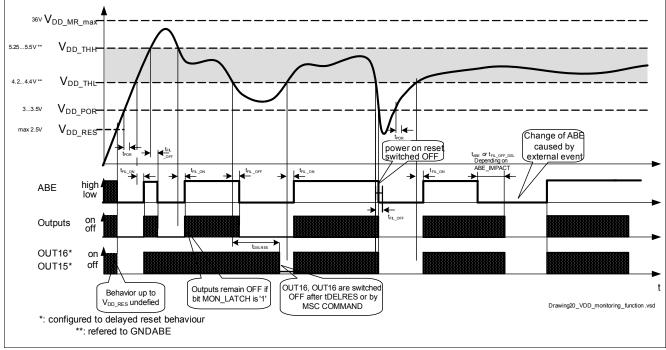

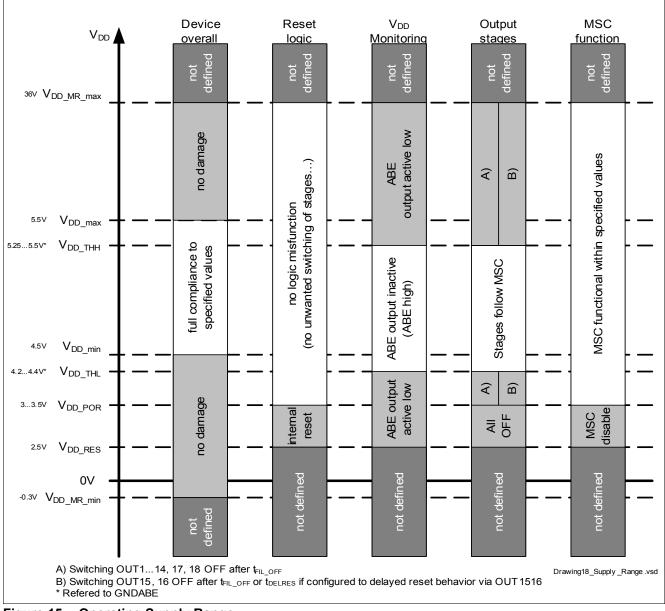

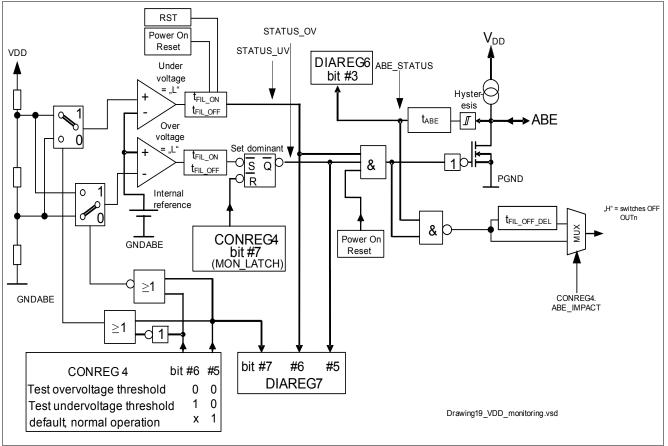

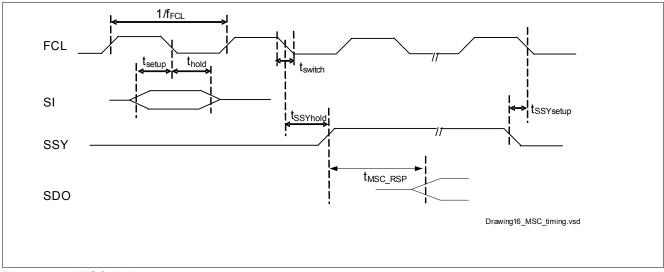

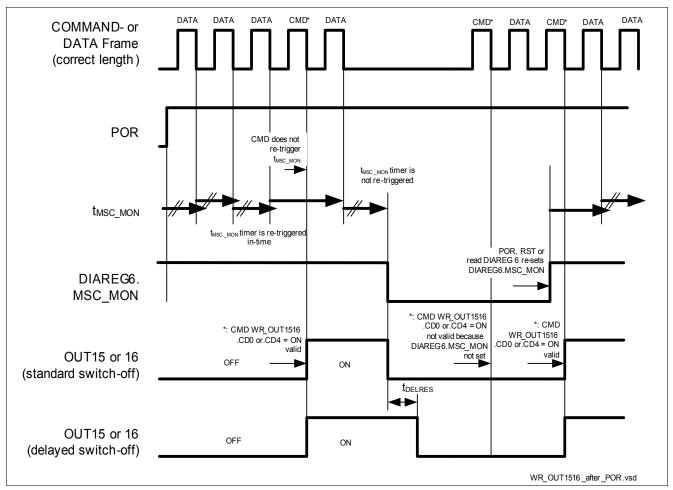

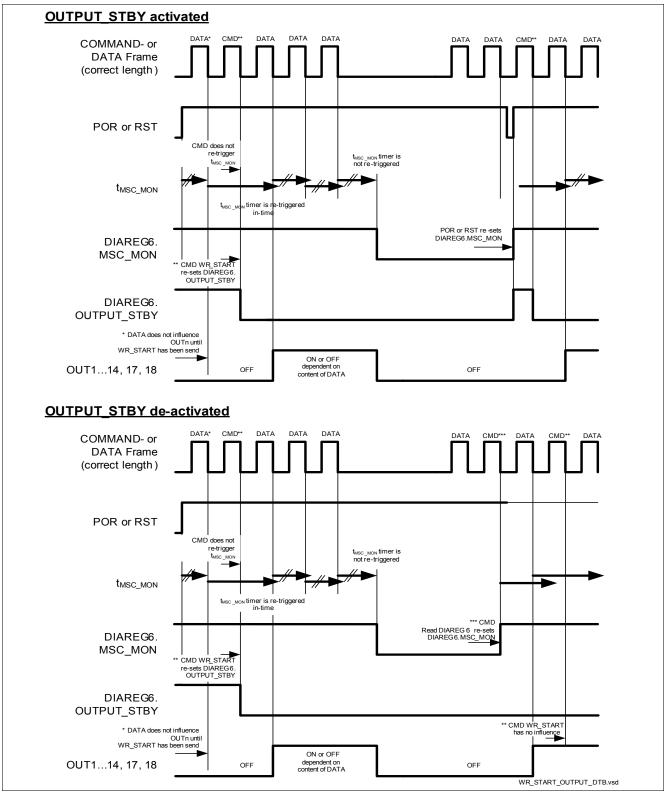

| 5.3.22 | Load Dump, max. 10 pulses                                                                                                                                                                                                                                                                                                        | $E_{\rm CL_OUTn}$        | -    | -     | 76   | mJ   | С  | <i>Tj</i> <sub>(0)</sub> =35°C,<br><i>I</i> <sub>OUTn(0)</sub> <3A     |