# Full-Duplex, Low Power, Slew Rate Limited, EIA RS-485 Transceivers

**Data Sheet**

ADM488A/ADM489A

#### **FEATURES**

Complies with ANSI TIA/EIA-485-A-1998 and ISO 8482: 1987(E)

250 kbps data rate ±4 kV HBM ESD protection on all pins

Single 5 V ± 10% supply

-7 V to +12 V bus common-mode range

Connect up to 32 nodes on the bus

Reduced slew rate for low EM interference

Short-circuit protection

#### **APPLICATIONS**

30 µA supply current

Low power RS-485 and RS-422 systems

DTE-DCE interface

Packet switching

Local area networks

Data concentration

Data multiplexers

Integrated services digital network (ISDN)

#### **GENERAL DESCRIPTION**

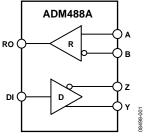

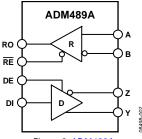

The ADM488A and ADM489A are low power, differential line transceivers suitable for communication on multipoint bus transmission lines. They are intended for balanced data transmission and comply with both RS-485 and RS-422 standards of the Electronics Industries Association (EIA). Both products contain a single differential line driver and a single differential line receiver, making them suitable for full-duplex data transfer. The ADM489A contains an additional receiver and driver enable control.

The input impedance is 12 k $\Omega$ , allowing 32 transceivers to be connected on the bus. The ADM488A/ADM489A operate from a single 5 V  $\pm$  10% power supply.

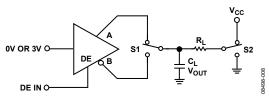

#### **FUNCTIONAL BLOCK DIAGRAMS**

Figure 1. ADM488A

Figure 2. ADM489A

Excessive power dissipation that is caused by bus contention or output shorting is prevented by a thermal shutdown circuit. This feature forces the driver output into a high impedance state if, during fault conditions, a significant temperature increase is detected in the internal driver circuitry.

The receiver contains a fail-safe feature that results in a logic high output state if the inputs are unconnected (floating).

The ADM488A/ADM489A are fabricated on BiCMOS, an advanced mixed technology process combining low power CMOS with fast switching bipolar technology.

The ADM488A/ADM489A are fully specified over the industrial temperature range and are available in SOIC and MSOP packages.

Trademarks and registered trademarks are the property of their respective owners.

### **TABLE OF CONTENTS**

| Features                                                  |

|-----------------------------------------------------------|

| Applications1                                             |

| General Description                                       |

| Functional Block Diagrams                                 |

| Revision History                                          |

| Specifications                                            |

| Timing Specifications4                                    |

| Absolute Maximum Ratings                                  |

| ESD Caution5                                              |

| Pin Configurations and Function Descriptions6             |

|                                                           |

|                                                           |

| REVISION HISTORY                                          |

| REVISION HISTORY<br>6/14—Rev. A to Rev. B                 |

| 6/14—Rev. A to Rev. B Changes to Features Section         |

| 6/14—Rev. A to Rev. B                                     |

| 6/14—Rev. A to Rev. B Changes to Features Section         |

| 6/14—Rev. A to Rev. B  Changes to Features Section        |

| 6/14—Rev. A to Rev. B         Changes to Features Section |

| 6/14—Rev. A to Rev. B         Changes to Features Section |

| 6/14—Rev. A to Rev. B         Changes to Features Section |

| 6/14—Rev. A to Rev. B         Changes to Features Section |

| Typical Performance Characteristics | 8  |

|-------------------------------------|----|

| Test Circuits                       | 9  |

| Switching Characteristics           | 10 |

| Theory of Operation                 | 11 |

| Applications Information            | 13 |

| Differential Data Transmission      | 13 |

| Cable and Data Rate                 | 13 |

| Outline Dimensions                  | 14 |

| Ordering Guide                      | 15 |

### **SPECIFICATIONS**

$V_{\text{CC}}$  = 5 V  $\pm$  10%; all specifications  $T_{\text{MIN}}$  to  $T_{\text{MAX}},$  unless otherwise noted.

Table 1.

| Parameter                                                | Symbol           | Min  | Тур | Max  | Unit | Test Conditions/Comments                                                                 |

|----------------------------------------------------------|------------------|------|-----|------|------|------------------------------------------------------------------------------------------|

| DRIVER                                                   |                  |      |     |      |      |                                                                                          |

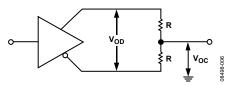

| Differential Output Voltage                              | V <sub>OD</sub>  |      |     | 5.0  | V    | R = ∞, see Figure 11                                                                     |

|                                                          |                  | 2.0  |     | 5.0  | V    | $V_{CC} = 5 \text{ V}, R = 50 \Omega \text{ (RS-422)}, see Figure 11$                    |

|                                                          |                  | 1.5  |     | 5.0  | V    | R = 27 Ω (RS-485), see Figure 11                                                         |

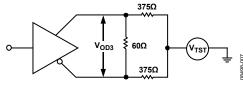

|                                                          |                  | 1.5  |     | 5.0  | ٧    | $V_{TST} = -7 \text{ V to } +12 \text{ V, see Figure } 12, V_{CC} = 5 \text{ V} \pm 5\%$ |

| $\Delta  V_{\text{OD}} $ for Complementary Output States |                  |      |     | 0.2  | ٧    | R = 27 $\Omega$ or 50 $\Omega$ , see Figure 11                                           |

| Common-Mode Output Voltage                               | Voc              |      |     | 3.0  | V    | $R = 27 \Omega$ or 50 $\Omega$ , see Figure 11                                           |

| $\Delta  V_{OC} $ for Complementary Output States        |                  |      |     | 0.2  | V    | $R = 27 \Omega \text{ or } 50 \Omega$                                                    |

| Output Short-Circuit Current                             |                  |      |     |      |      |                                                                                          |

| V <sub>OUT</sub>                                         |                  |      |     | 250  | mA   | $-7 \text{ V} \le \text{V}_0 \le +12 \text{ V}$                                          |

| CMOS Input Logic Threshold Low                           | $V_{INL}$        |      | 1.4 | 8.0  | ٧    |                                                                                          |

| CMOS Input Logic Threshold High                          | V <sub>INH</sub> | 2.0  | 1.4 |      | V    |                                                                                          |

| Logic Input Current (DE, DI)                             |                  |      |     | ±1.0 | μΑ   |                                                                                          |

| RECEIVER                                                 |                  |      |     |      |      |                                                                                          |

| Differential Input Threshold Voltage                     | $V_{TH}$         | -0.2 |     | +0.2 | ٧    | $-7 \text{ V} \leq \text{V}_{\text{CM}} \leq +12 \text{ V}$                              |

| Input Voltage Hysteresis                                 | $\Delta V_{TH}$  |      | 70  |      | mV   | $V_{CM} = 0 V$                                                                           |

| Input Resistance                                         |                  | 12   |     |      | kΩ   | $-7 \text{ V} \leq \text{V}_{\text{CM}} \leq +12 \text{ V}$                              |

| Input Current (A, B)                                     |                  |      |     | 1    | mA   | $V_{IN} = 12 V$                                                                          |

|                                                          |                  |      |     | -0.8 | mA   | $V_{IN} = -7 V$                                                                          |

| Logic Enable Input Current (RE)                          |                  |      |     | ±1   | μΑ   |                                                                                          |

| CMOS Output Voltage Low                                  | $V_{OL}$         |      |     | 0.4  | ٧    | $I_{OUT} = +4.0 \text{ mA}$                                                              |

| CMOS Output Voltage High                                 | V <sub>OH</sub>  | 4.0  |     |      | V    | $I_{OUT} = -4.0 \text{ mA}$                                                              |

| Short-Circuit Output Current                             |                  | 7    |     | 85   | mA   | $V_{OUT} = GND \text{ or } V_{CC}$                                                       |

| Three-State Output Leakage Current                       |                  |      |     | ±1.0 | μΑ   | $0.4 \text{ V} \leq \text{V}_{\text{OUT}} \leq 2.4 \text{ V}$                            |

| POWER SUPPLY CURRENT                                     | Icc              |      |     |      |      | Outputs unloaded, receivers enabled                                                      |

|                                                          |                  |      | 30  | 60   | μΑ   | DE = 0 V  (disabled)                                                                     |

|                                                          |                  |      | 37  | 74   | μΑ   | DE = 5 V (enabled)                                                                       |

### **TIMING SPECIFICATIONS**

$V_{\text{CC}}$  = 5 V  $\pm$  10%. All specifications  $T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , unless otherwise noted.

### Table 2.

| Parameter                         | Symbol                              | Min | Тур | Max  | Unit | Test Conditions/Comments                                                                  |

|-----------------------------------|-------------------------------------|-----|-----|------|------|-------------------------------------------------------------------------------------------|

| DRIVER                            |                                     |     |     |      |      |                                                                                           |

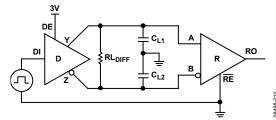

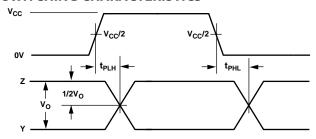

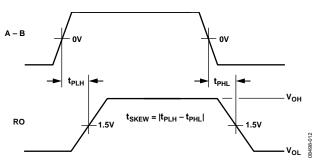

| Propagation Delay Input to Output | t <sub>PLH</sub> , t <sub>PHL</sub> | 250 |     | 2000 | ns   | $R_L$ differential = 54 $\Omega$ , $C_{L1}$ = $C_{L2}$ = 100 pF, see Figure 15, Figure 16 |

| Driver Output Skew                | tskew                               |     | 100 | 800  | ns   | $R_L$ differential = 54 $\Omega$ , $C_{L1}$ = $C_{L2}$ = 100 pF, see Figure 15            |

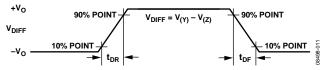

| Driver Rise/Fall Time             | t <sub>DR</sub> , t <sub>DF</sub>   | 250 |     | 2000 | ns   | $R_L$ differential = 54 $\Omega$ , $C_{L1}$ = $C_{L2}$ = 100 pF, see Figure 15, Figure 16 |

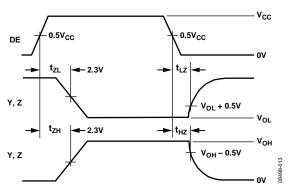

| Driver Enable to Output Valid     | t <sub>ZL</sub> , t <sub>ZH</sub>   | 250 |     | 2000 | ns   | $R_L = 500 \Omega$ , $C_L = 100 pF$ , see Figure 12, Figure 18                            |

| Driver Disable Timing             | t <sub>LZ</sub> , t <sub>HZ</sub>   | 300 |     | 3000 | ns   | $R_L = 500 \Omega$ , $C_L = 15 pF$ , see Figure 12, Figure 18                             |

| Maximum Data Rate                 |                                     | 250 |     |      | kbps |                                                                                           |

| RECEIVER                          |                                     |     |     |      |      |                                                                                           |

| Propagation Delay Input to Output | t <sub>PLH</sub> , t <sub>PHL</sub> | 250 |     | 2000 | ns   | $C_L = 15$ pF, see Figure 15, Figure 17                                                   |

| Skew                              | t <sub>PLH</sub> — t <sub>PHL</sub> |     | 100 |      | ns   |                                                                                           |

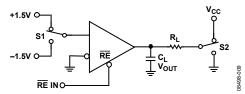

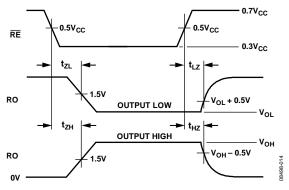

| Receiver Enable                   | t <sub>EN1</sub>                    |     | 10  | 50   | ns   | $R_L = 1 \text{ k}\Omega$ , $C_L = 15 \text{ pF}$ , see Figure 14, Figure 19              |

| Receiver Disable                  | t <sub>EN2</sub>                    |     | 10  | 50   | ns   | $R_L = 1 \text{ k}\Omega$ , $C_L = 15 \text{ pF}$ , see Figure 14, Figure 19              |

| Maximum Data Rate                 |                                     | 250 |     |      | kbps |                                                                                           |

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 3.

| Parameter                            | Rating                                       |

|--------------------------------------|----------------------------------------------|

| Vcc                                  | 7 V                                          |

| Inputs                               |                                              |

| Driver Input (DI)                    | $-0.3  \text{V}$ to $V_{CC} + 0.3  \text{V}$ |

| Control Inputs (DE, RE)              | $-0.3  \text{V}$ to $V_{CC} + 0.3  \text{V}$ |

| Receiver Inputs (A, B)               | –14 V to +14 V                               |

| Outputs                              |                                              |

| Driver Outputs                       | -14 V to +12.5 V                             |

| Receiver Output                      | $-0.5  \text{V}$ to $V_{CC} + 0.5  \text{V}$ |

| Power Dissipation 8-Lead SOIC        | 520 mW                                       |

| $\theta_{JA}$ , Thermal Impedance    | 110°C/W                                      |

| Power Dissipation 14-Lead SOIC       | 800 mW                                       |

| $\theta_{JA}$ , Thermal Impedance    | 120°C/W                                      |

| Operating Temperature Range          |                                              |

| Industrial (A Version)               | −40°C to +85°C                               |

| Storage Temperature Range            | −65°C to +150°C                              |

| Lead Temperature (Soldering, 10 sec) | 300°C                                        |

| Vapor Phase (60 sec)                 | 215℃                                         |

| Infrared (15 sec)                    | 220°C                                        |

| ESD Protection on All Pins           |                                              |

| Human Body Model (HBM)               | ±4 kV                                        |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

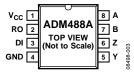

### PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 3. ADM488A SOIC\_N and MSOP Pin Configuration

#### Table 4. ADM488A Pin Function Descriptions

| Pin No. | Mnemonic | Description                                                                                                  |

|---------|----------|--------------------------------------------------------------------------------------------------------------|

| 1       | Vcc      | Power Supply, 5 V $\pm$ 10%.                                                                                 |

| 2       | RO       | Receiver Output. When $A > B$ by 200 mV, $RO = high$ . If $A < B$ by 200 mV, $RO = low$ .                    |

| 3       | DI       | Driver Input. A logic low on DI forces Y low and Z high, whereas a logic high on DI forces Y high and Z low. |

| 4       | GND      | Ground Connection, 0 V.                                                                                      |

| 5       | Υ        | Noninverting Driver, Differential Output Y.                                                                  |

| 6       | Z        | Inverting Driver, Differential Output Z.                                                                     |

| 7       | В        | Inverting Receiver, Input B.                                                                                 |

| 8       | Α        | Noninverting Receiver, Input A.                                                                              |

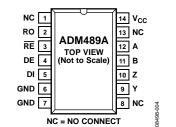

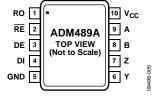

Figure 4. ADM489A SOIC\_N Pin Configuration

Figure 5. ADM489A MSOP Pin Configuration

Table 5. ADM489A Pin Function Descriptions

| Р        | Pin No.          |          |                                                                                                                                                 |

|----------|------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| SOIC_N   | MSOP             | Mnemonic | Description                                                                                                                                     |

| 1, 8, 13 | N/A <sup>1</sup> | NC       | No Connect. No connections are required to this pin.                                                                                            |

| 2        | 1                | RO       | Receiver Output. When enabled, if A > B by 200 mV, RO = high. If A < B by 200 mV, RO = low.                                                     |

| 3        | 2                | RE       | Receiver Output Enable. A low level enables the receiver output, RO. A high level places the ADM489A in a high impedance state.                 |

| 4        | 3                | DE       | Driver Output Enable. A high level enables the driver differential outputs (Y and Z). A low level places the ADM489A in a high impedance state. |

| 5        | 4                | DI       | Driver Input. When the driver is enabled, a logic low on DI forces Y low and Z high, whereas a logic high on DI forces Y high and Z low.        |

| 6, 7     | 5                | GND      | Ground Connection, 0 V.                                                                                                                         |

| 9        | 6                | Υ        | Noninverting Driver, Differential Output Y.                                                                                                     |

| 10       | 7                | Z        | Inverting Driver, Differential Output Z.                                                                                                        |

| 11       | 8                | В        | Inverting Receiver, Input B.                                                                                                                    |

| 12       | 9                | Α        | Noninverting Receiver, Input A.                                                                                                                 |

| 14       | 10               | Vcc      | Power Supply, 5 V ± 10%.                                                                                                                        |

<sup>&</sup>lt;sup>1</sup> N/A means not applicable.

### TYPICAL PERFORMANCE CHARACTERISTICS

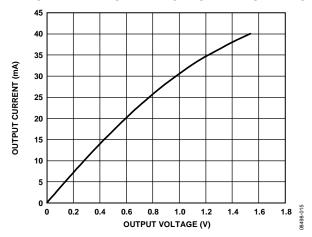

Figure 6. Output Current vs. Receiver Output Low Voltage

Figure 7. Output Current vs. Receiver Output High Voltage

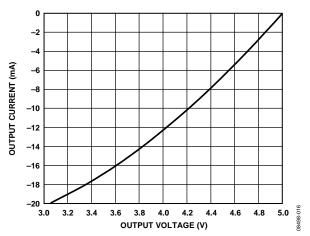

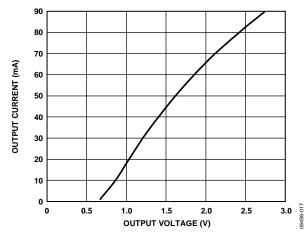

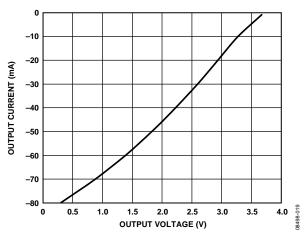

Figure 8. Output Current vs. Driver Output Low Voltage

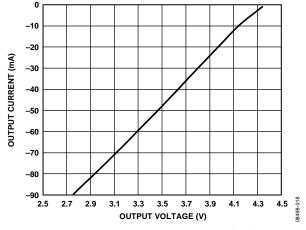

Figure 9. Output Current vs. Driver Output High Voltage

Figure 10. Output Current vs. Driver Differential Output Voltage

### **TEST CIRCUITS**

Figure 11. Driver Voltage Measurement Test Circuit

Figure 12. Driver Enable/Disable Test Circuit

Figure 13. Driver Voltage Measurement Test Circuit

Figure 14. Receiver Enable/Disable Test Circuit

Figure 15. Driver/Receiver Propagation Delay Test Circuit

### **SWITCHING CHARACTERISTICS**

Figure 16. Driver Propagation Delay, Rise/Fall Timing

Figure 17. Receiver Propagation Delay

Figure 18. Driver Enable/Disable Timing

Figure 19. Receiver Enable/Disable Timing

### THEORY OF OPERATION

The ADM488A/ADM489A are ruggedized RS-485 transceivers that operate from a single 5 V supply. They contain protection against radiated and conducted interference and are ideally suited for operation in electrically harsh environments or where cables can be plugged/unplugged. They are also immune to high RF field strengths without special shielding precautions.

The ADM488A/ADM489A are intended for balanced data transmission and comply with both EIA RS-485 and RS-422 standards. They contain a differential line driver and a differential line receiver, and are suitable for full-duplex data transmission.

The input impedance on the ADM488A/ADM489A is  $12~k\Omega$ , allowing up to 32 transceivers on the differential bus. The ADM488A/ADM489A operate from a single  $5~V~\pm~10\%$  power supply. A thermal shutdown circuit prevents excessive power dissipation caused by bus contention or by output shorting. This feature forces the driver output into a high impedance state if, during fault conditions, a significant temperature increase is detected in the internal driver circuitry.

The receiver contains a fail-safe feature that results in a logic high output state if the inputs are unconnected (floating).

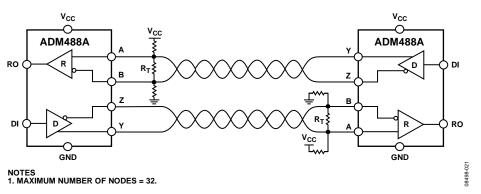

The ADM488A/ADM489A can transmit at data rates up to 250 kbps. Figure 20 shows a typical application for the ADM488A/ADM489A, a full-duplex link where data transfers at rates of up to 250 kbps. A terminating resistor is shown at both ends of the link. This termination is not critical because

the slew rate is controlled by the ADM488A/ADM489A and reflections are minimized.

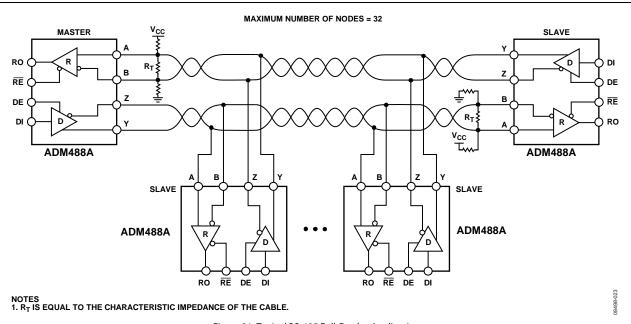

The communications network can be extended to include multipoint connections, as shown in Figure 22. As many as 32 transceivers can be connected to the bus.

Table 6 and Table 7 show the truth tables for transmitting and receiving.

Table 6. Transmitting Truth Table

| Inputs         |    |                | Outputs          |                  |  |

|----------------|----|----------------|------------------|------------------|--|

| RE             | DE | DI             | z                | Υ                |  |

| X <sup>1</sup> | 1  | 1              | 0                | 1                |  |

| $X^1$          | 1  | 0              | 1                | 0                |  |

| 0              | 0  | X <sup>1</sup> | High-Z           | High-Z<br>High-Z |  |

| 1              | 0  | X <sup>1</sup> | High-Z<br>High-Z | High-Z           |  |

<sup>&</sup>lt;sup>1</sup> X is don't care.

Table 7. Receiving Truth Table

|    | lr | Output              |        |

|----|----|---------------------|--------|

| RE | DE | A to B              | RO     |

| 0  | 0  | ≥ +0.2 V            | 1      |

| 0  | 0  | ≤ -0.2 V            | 0      |

| 0  | 0  | Inputs open circuit | 1      |

| 1  | 0  | X <sup>1</sup>      | High-Z |

<sup>1</sup> X is don't care.

Figure 20. ADM488A/ADM489A Full-Duplex Data Link

Figure 21. Typical RS-485 Full-Duplex Application

## APPLICATIONS INFORMATION DIFFERENTIAL DATA TRANSMISSION

Differential data transmission reliably transmits data at high rates over long distances and through noisy environments. Differential transmission nullifies the effects of ground shifts and noise signals, which appear as common-mode voltages on the line. Two main standards that specify the electrical characteristics of transceivers used in differential data transmission are approved by the EIA.

The RS-422 standard specifies data rates up to 10 Mbps and line lengths up to 4000 ft. A single driver can drive a transmission line with up to 10 receivers.

To cater to true multipoint communications, the RS-485 standard was defined to meet or exceed the requirements of RS-422. It also allows up to 32 drivers and 32 receivers to be connected to a single bus. An extended common-mode range of –7 V to +12 V is defined. The most significant difference between the RS-422 and RS-485 is that the RS-485 drivers can be disabled, thereby allowing up to 32 receivers to be connected to a single line. Only one driver should be enabled at a time, but the RS-485 standard contains additional specifications to guarantee device safety in the event of line contention.

#### **CABLE AND DATA RATE**

The transmission line of choice for RS-485 communications is a twisted pair. Twisted pair cable tends to cancel common-mode noise and causes cancellation of the magnetic fields generated by the current flowing through each wire, thereby reducing the effective inductance of the pair.

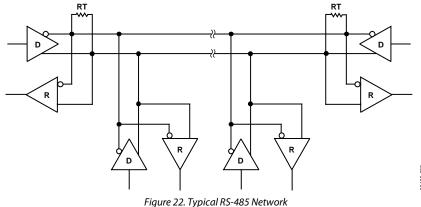

The ADM488A/ADM489A are designed for bidirectional data communications on multipoint transmission lines. A typical application with a multipoint transmission network is illustrated in Figure 22. An RS-485 transmission line can have up to 32 transceivers on the bus. Only one driver can transmit at a particular time, but multiple receivers can be simultaneously enabled.

As with any transmission line, it is important to minimize reflections. This can be achieved by terminating the extreme ends of the line using resistors equal to the characteristic impedance of the line. Keep stub lengths of the main line as short as possible. A properly terminated transmission line appears purely resistive to the driver.

Table 8. Comparison of RS-422 and RS-485 Interface Standards

| Specification                        | RS-422       | RS-485        |

|--------------------------------------|--------------|---------------|

| Transmission Type                    | Differential | Differential  |

| Maximum Data Rate                    | 10 Mbps      | 10 Mbps       |

| Maximum Cable Length                 | 4000 ft.     | 4000 ft.      |

| Minimum Driver Output Voltage        | ±2 V         | ±1.5 V        |

| Driver Load Impedance                | 100 Ω        | 54 Ω          |

| Receiver Input Resistance            | 4 kΩ minimum | 12 kΩ minimum |

| Receiver Input Sensitivity           | ±200 mV      | ±200 mV       |

| Receiver Input Voltage Range         | −7 V to +7 V | −7 V to +12 V |

| Number of Drivers/Receivers per Line | 1/10         | 32/32         |

Rev. B | Page 13 of 16

### **OUTLINE DIMENSIONS**

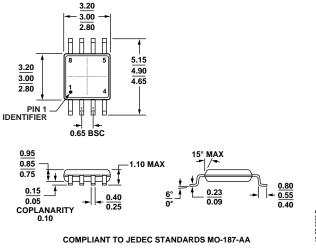

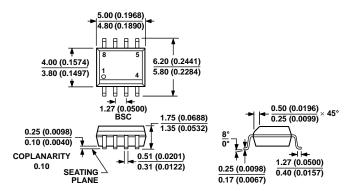

Figure 23. 8-Lead Mini Small Outline Package [MSOP] (RM-8) Dimensions shown in millimeters

COMPLIANT TO JEDEC STANDARDS MS-012-AA CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 24. 8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8)

Dimensions shown in millimeters and (inches)

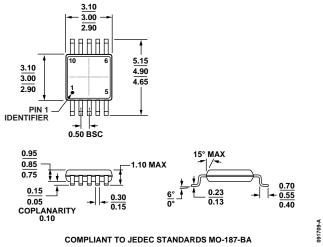

Figure 25. 10-Lead Mini Small Outline Package [MSOP] (RM-10) Dimensions shown in millimeters

COMPLIANT TO JEDEC STANDARDS MS-012-AB

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

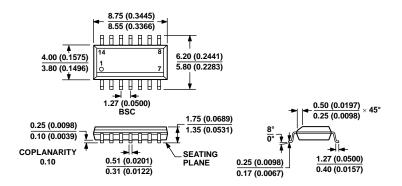

Figure 26. 14-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-14) Dimensions shown in millimeters and (inches)

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature<br>Range | Package Description                                          | Package<br>Option | Branding |

|--------------------|----------------------|--------------------------------------------------------------|-------------------|----------|

| ADM488ABRMZ        | -40°C to +85°C       | 8-Lead Mini Small Outline Package [MSOP]                     | RM-8              | FOF      |

|                    |                      | J                                                            |                   | 1        |

| ADM488ABRMZ-REEL7  | −40°C to +85°C       | 8-Lead Mini Small Outline Package [MSOP]                     | RM-8              | F0F      |

| ADM488ABRZ         | −40°C to +85°C       | 8-Lead Standard Small Outline Package, Narrow Body [SOIC_N]  | R-8               |          |

| ADM488ABRZ-REEL7   | −40°C to +85°C       | 8-Lead Standard Small Outline Package, Narrow Body [SOIC_N]  | R-8               |          |

| ADM489ABRMZ        | −40°C to +85°C       | 10-Lead Mini Small Outline Package [MSOP]                    | RM-10             | F0G      |

| ADM489ABRMZ-REEL7  | -40°C to +85°C       | 10-Lead Mini Small Outline Package [MSOP]                    | RM-10             | F0G      |

| ADM489ABRZ         | −40°C to +85°C       | 14-Lead Standard Small Outline Package, Narrow Body [SOIC_N] | R-14              |          |

| ADM489ABRZ-REEL7   | −40°C to +85°C       | 14-Lead Standard Small Outline Package, Narrow Body [SOIC_N] | R-14              |          |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

**NOTES**

Rev. B | Page 16 of 16