# Wide bandwidth, dual bipolar operational amplifier

#### **DW SO-8 exposed-pad** (plastic micropackage) **DW SO-8 exposed-pad** (plastic micropackage) **Diametric micropackage Diametric micropacka**

#### Features

- Operating from  $V_{CC}$  = 2.5 V to 5.5 V

- 200 mA output current on each amplifier

- High dissipation package

- Rail-to-rail input and output

- Unity gain stable

### Applications

- Hall sensor compensation coils

- Servo amplifiers

- Motor drivers

- Industrial

- Automotive

```

March 2018

```

#### Datasheet - production data

#### Description

The TS982 device is a dual operational amplifier able to drive 200 mA down to voltages as low as 2.7 V.

The SO-8 exposed-pad package allows high current output at high ambient temperatures making it a reliable solution for automotive and industrial applications.

The TS982 device is stable with a unity gain.

# Contents

| 1 | Absolute maximum ratings and operating conditions |

|---|---------------------------------------------------|

| 2 | Electrical characteristics 4                      |

| 3 | Application information14                         |

|   | 3.1 Exposed-pad package description 14            |

|   | 3.2 Exposed-pad electrical connection             |

|   | 3.3    Thermal management benefits    15          |

|   | 3.4   Thermal management guidelines   15          |

|   | 3.5 Parallel operation                            |

| 4 | Package information                               |

|   | 4.1 SO-8 exposed pad package information 17       |

| 5 | Ordering information                              |

| 6 | Revision history                                  |

# 1 Absolute maximum ratings and operating conditions

| Symbol            | Parameter                                             | Value                            | Unit |

|-------------------|-------------------------------------------------------|----------------------------------|------|

| V <sub>CC</sub>   | Supply voltage <sup>(1)</sup>                         | 6                                | V    |

| V <sub>in</sub>   | Input voltage                                         | -0.3 V to V <sub>CC</sub> +0.3 V | V    |

| T <sub>oper</sub> | Operating free-air temperature range                  | -40 to + 125                     | °C   |

| T <sub>stg</sub>  | Storage temperature                                   | -65 to +150                      | °C   |

| Тj                | Maximum junction temperature                          | 150                              | °C   |

| R <sub>thja</sub> | Thermal resistance junction to ambient <sup>(2)</sup> | 45                               | °C/W |

| R <sub>thjc</sub> | Thermal resistance junction to case                   | 10                               | °C/W |

|                   | Human body model (HBM) <sup>(3)</sup>                 | 2                                | kV   |

| ESD               | Charged device model (CDM) <sup>(4)</sup>             | 1.5                              | kV   |

|                   | Machine model (MM) <sup>(5)</sup>                     | 200                              | V    |

| Latch-up          | Latch-up immunity (all pins)                          | 200                              | mA   |

|                   | Lead temperature (soldering, 10 s)                    | 250                              | °C   |

|                   | Output short-circuit duration                         | See note <sup>(6)</sup>          |      |

| Table 1. Abs | solute maxim | um ratings | (AMR) |

|--------------|--------------|------------|-------|

|--------------|--------------|------------|-------|

1. All voltage values are measured with respect to the ground pin.

2. With two sides, two-plane PCB following the EIA/JEDEC JESD51-7 standard.

- 3. Human body model: A 100 pF capacitor is charged to the specified voltage, then discharged through a 1.5 k $\Omega$  resistor between two pins of the device. This is done for all couples of connected pin combinations while the other pins are left floating.

- 4. Charged device model: all pins and the package are charged together to the specified voltage and then discharged directly to the ground through only one pin. This is done for all pins.

- 5. Machine model: A 200 pF capacitor is charged to the specified voltage, then discharged directly between two pins of the device with no external series resistor (internal resistor < 5 Ω). This is done for all couples of connected pin combinations while the other pins are left floating.

- 6. Short-circuits can cause excessive heating. Destructive dissipation can result from a short-circuit on one or two amplifiers simultaneously.

| Symbol           | Parameter                                                          | Value                  | Unit |

|------------------|--------------------------------------------------------------------|------------------------|------|

| V <sub>CC</sub>  | Supply voltage                                                     | 2.5 to 5.5             | V    |

| V <sub>icm</sub> | Common mode input voltage range                                    | GND to V <sub>CC</sub> | V    |

| CL               | Load capacitor<br>R <sub>L</sub> < 100 Ω<br>R <sub>L</sub> > 100 Ω | 400<br>100             | pF   |

#### Table 2. Operating conditions

# 2 Electrical characteristics

| Symbol          | otherwise specifie<br>Parameter                                                                                                  | Min.     | Тур.      | Max.          | Unit             |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------|----------|-----------|---------------|------------------|

| I <sub>CC</sub> | Supply current - No input signal, no load                                                                                        |          | 5.5       | 7.2           | mA               |

| V <sub>IO</sub> | $T_{min} < T_{op} < T_{max}$ Input offset voltage (V <sub>icm</sub> = V <sub>CC</sub> /2)<br>$T_{min} < T_{op} < T_{max}$        |          | 1         | 7.2<br>5<br>7 | mV               |

| $\Delta V_{IO}$ | Input offset voltage drift                                                                                                       |          | 2         |               | µV/°C            |

| I <sub>IB</sub> | Input bias current - $V_{icm} = V_{CC}/2$<br>T <sub>min</sub> < T <sub>op</sub> < T <sub>max</sub>                               |          | 200       | 500<br>500    | nA               |

| I <sub>IO</sub> | Input offset current<br>$V_{icm} = V_{CC}/2$                                                                                     |          | 10        |               | nA               |

| V <sub>OH</sub> | High level output voltage<br>$R_L = 16 \Omega$<br>$R_L = 16 \Omega$ , $T_{min} < T_{op} < T_{max}$<br>$I_{out} = 200 \text{ mA}$ | 4.2<br>4 | 4.4       |               | v                |

|                 | V <sub>CC</sub> = 4.75 V, T = 125 °C, I <sub>out</sub> = 25 mA                                                                   | 4.3      |           |               | V                |

| V <sub>OL</sub> | Low level output voltage<br>$R_L = 16 \Omega$<br>$R_L = 16 \Omega$ , $T_{min} < T_{op} < T_{max}$<br>$I_{out} = 200 \text{ mA}$  |          | 0.55<br>1 | 0.65<br>0.95  | v                |

|                 | V <sub>CC</sub> = 4.75 V, T = 125 °C, I <sub>out</sub> = 25 mA                                                                   |          |           | 0.45          | V                |

| A <sub>VD</sub> | Large signal voltage gain $R_L$ = 16 $\Omega$                                                                                    |          | 95        |               | dB               |

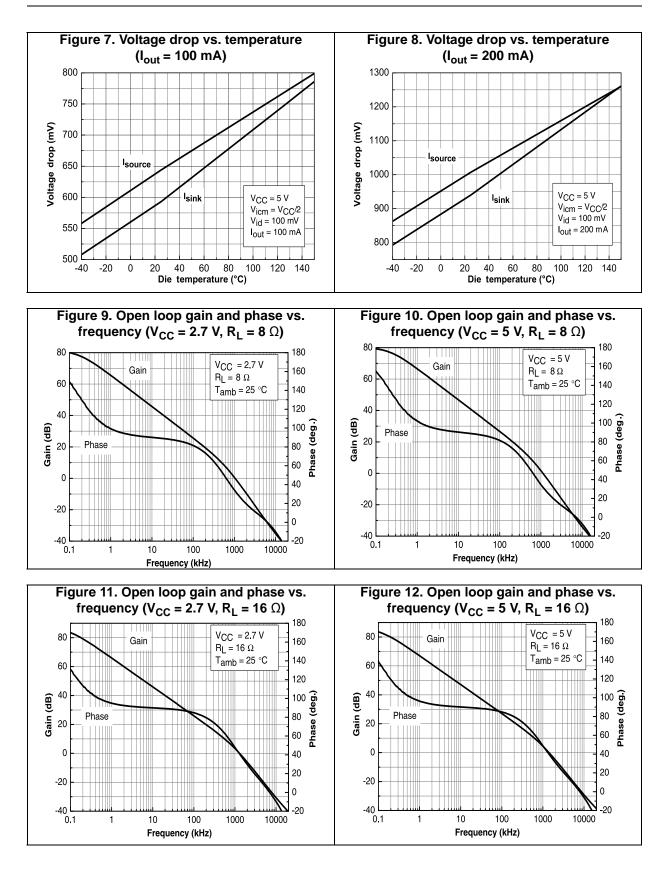

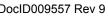

| GBP             | Gain bandwidth product $R_L$ = 32 $\Omega$                                                                                       | 1.35     | 2.2       |               | MHz              |

| CMR             | Common mode rejection ratio                                                                                                      |          | 80        |               | dB               |

| SVR             | Supply voltage rejection ratio                                                                                                   |          | 95        |               | dB               |

| SR              | Slew rate, unity gain inverting $R_L$ = 16 $\Omega$                                                                              | 0.45     | 0.7       |               | V/µs             |

| $\Phi_{m}$      | Phase margin at unit gain<br>$R_L = 16 \Omega$ , $C_L = 400 pF$                                                                  |          | 56        |               | Degrees          |

| G <sub>m</sub>  | Gain margin<br>R <sub>L</sub> = 16 $\Omega$ , C <sub>L</sub> = 400 pF                                                            |          | 18        |               | dB               |

| e <sub>n</sub>  | Equivalent input noise voltage<br>F = 1 kHz                                                                                      |          | 17        |               | <u>nV</u><br>√Hz |

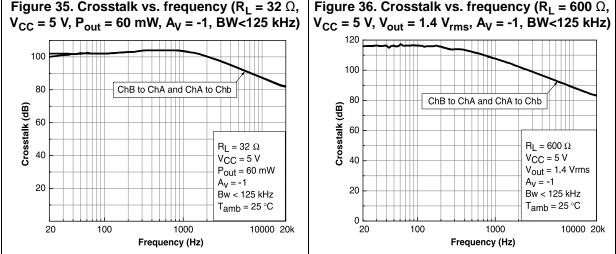

| Crosstalk       | Channel separation<br>$R_L = 16 \Omega$ , F = 1 kHz                                                                              |          | 100       |               | dB               |

| Table 3. Electrical characteristics for $V_{CC+}$ = +5 V, $V_{CC-}$ = 0 V, and $T_{amb}$ = 25 °C (unless |

|----------------------------------------------------------------------------------------------------------|

| otherwise specified)                                                                                     |

| Symbol          | Parameter                                                                                                                                                       | Min.         | Тур.        | Max.         | Unit              |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|--------------|-------------------|

| I <sub>CC</sub> | Supply current - No input signal, no load<br>T <sub>min</sub> < T <sub>op</sub> < T <sub>max</sub>                                                              |              | 5.3         | 7.2<br>7.2   | mA                |

| V <sub>IO</sub> | Input offset voltage ( $V_{icm} = V_{CC}/2$ )<br>T <sub>min</sub> < T <sub>op</sub> < T <sub>max</sub>                                                          |              | 1           | 5<br>7       | mV                |

| $\Delta V_{IO}$ | Input offset voltage drift                                                                                                                                      |              | 2           |              | µV/°C             |

| Ι <sub>ΙΒ</sub> | Input bias current - $V_{icm} = V_{CC}/2$<br>T <sub>min</sub> < T <sub>op</sub> < T <sub>max</sub>                                                              |              | 200         | 500<br>500   | nA                |

| Ι <sub>ΙΟ</sub> | Input offset current<br>V <sub>icm</sub> = V <sub>CC</sub> /2                                                                                                   |              | 10          |              | nA                |

| V <sub>OH</sub> | High level output voltage<br>R <sub>L</sub> = 16 Ω<br>R <sub>L</sub> = 16 Ω, T <sub>min</sub> < T <sub>op</sub> < T <sub>max</sub><br>I <sub>out</sub> = 200 mA | 2.68<br>2.64 | 2.85<br>2.3 |              | V                 |

| V <sub>OL</sub> | Low level output voltage<br>R <sub>L</sub> = 16 Ω<br>R <sub>L</sub> = 16 Ω, T <sub>min</sub> < T <sub>op</sub> < T <sub>max</sub><br>I <sub>out</sub> = 200 mA  |              | 0.45<br>1   | 0.52<br>0.65 | v                 |

| A <sub>VD</sub> | Large signal voltage gain $R_L = 16 \ \Omega$                                                                                                                   |              | 92          |              | dB                |

| GBP             | Gain bandwidth product $R_L = 32 \ \Omega$                                                                                                                      | 1.2          | 2           |              | MHz               |

| CMR             | Common mode rejection ratio                                                                                                                                     |              | 75          |              | dB                |

| SVR             | Supply voltage rejection ratio                                                                                                                                  |              | 95          |              | dB                |

| SR              | Slew rate, unity gain inverting $R_L$ = 16 $\Omega$                                                                                                             | 0.45         | 0.7         |              | V/µs              |

| $\Phi_{m}$      | Phase margin at unit gain $R_L = 16 \Omega$ , $C_L = 400 pF$                                                                                                    |              | 57          |              | Degrees           |

| G <sub>m</sub>  | Gain margin<br>R <sub>L</sub> = 16 Ω, C <sub>L</sub> = 400 pF                                                                                                   |              | 16          |              | dB                |

| e <sub>n</sub>  | Equivalent input noise voltage<br>F = 1 kHz                                                                                                                     |              | 17          |              | <u>_nV</u><br>√Hz |

| Crosstalk       | Channel separation $R_L = 16 \Omega, F = 1 \text{ kHz}$                                                                                                         |              | 100         |              | dB                |

Table 4. Electrical characteristics for V<sub>CC+</sub> = +3.3 V, V<sub>CC-</sub> = 0 V, and T<sub>amb</sub> = 25 °C (unless otherwise specified)<sup>(1)</sup>

1. All electrical values are guaranteed by correlation with measurements at 2.7 V and 5 V.

| Symbol                 | Parameter                                                                                                                                                      | Min.        | Тур.        | Max.         | Unit                   |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|--------------|------------------------|

| I <sub>CC</sub>        | Supply current - No input signal, no load<br>T <sub>min</sub> < T <sub>op</sub> < T <sub>ma</sub>                                                              |             | 5.3         | 6.4<br>6.4   | mA                     |

| V <sub>IO</sub>        | Input offset voltage ( $V_{icm} = V_{CC}/2$ )<br>T <sub>min</sub> < T <sub>op</sub> < T <sub>max</sub>                                                         |             | 1           | 5<br>7       | mV                     |

| $\Delta V_{\text{IO}}$ | Input offset voltage drift                                                                                                                                     |             | 2           |              | μV/°C                  |

| I <sub>IB</sub>        | Input bias current - $V_{icm} = V_{CC}/2$<br>T <sub>min</sub> < T <sub>op</sub> < T <sub>max</sub>                                                             |             | 200         | 500<br>500   | nA                     |

| I <sub>IO</sub>        | Input offset current<br>$V_{icm} = V_{CC}/2$                                                                                                                   |             | 10          |              | nA                     |

| V <sub>OH</sub>        | High level output voltage<br>$R_L = 16 \Omega$<br>$R_L = 16 \Omega$ , $T_{min} < T_{op} < T_{max}$<br>$I_{out} = 20 \text{ mA}$                                | 2.3<br>2.25 | 2.85<br>2.3 |              | V                      |

| V <sub>OL</sub>        | Low level output voltage<br>R <sub>L</sub> = 16 Ω<br>R <sub>L</sub> = 16 Ω, T <sub>min</sub> < T <sub>op</sub> < T <sub>max</sub><br>I <sub>out</sub> = 200 mA |             | 0.45<br>1   | 0.37<br>0.42 | v                      |

| $A_{VD}$               | Large signal voltage gain $R_L = 16 \Omega$                                                                                                                    |             | 92          |              | dB                     |

| GBP                    | Gain bandwidth product $R_L = 32 \ \Omega$                                                                                                                     | 1.2         | 2           |              | MHz                    |

| CMR                    | Common mode rejection ratio                                                                                                                                    |             | 75          |              | dB                     |

| SVR                    | Supply voltage rejection ratio                                                                                                                                 |             | 95          |              | dB                     |

| SR                     | Slew rate, unity gain inverting $R_L = 16 \ \Omega$                                                                                                            | 0.45        | 0.7         |              | V/µs                   |

| $\Phi_{m}$             | Phase margin at unit gain $R_L = 16 \Omega$ , $C_L = 400 pF$                                                                                                   |             | 57          |              | Degrees                |

| G <sub>m</sub>         | Gain margin<br>R <sub>L</sub> = 16 Ω, C <sub>L</sub> = 400 pF                                                                                                  |             | 16          |              | dB                     |

| e <sub>n</sub>         | Equivalent input noise voltage<br>F = 1 kHz                                                                                                                    |             | 17          |              | $\frac{nV}{\sqrt{Hz}}$ |

| Crosstalk              | Channel separation<br>R <sub>L</sub> = 16 Ω, F = 1 kHz                                                                                                         |             | 100         |              | dB                     |

Table 5. Electrical characteristics for V<sub>CC</sub> = +2.7 V, V<sub>CC</sub> = 0 V, and T<sub>amb</sub> = 25 °C (unless otherwise specified)

7/21

10/21

0 ⊑ 2.0

2.5

3.0

3.5

Power supply voltage (V)

4.0

4.5

5.0

0

2.0

2.5

3.0

3.5

Power supply voltage (V)

5.0

4.5

4.0

12/21

# 3 Application information

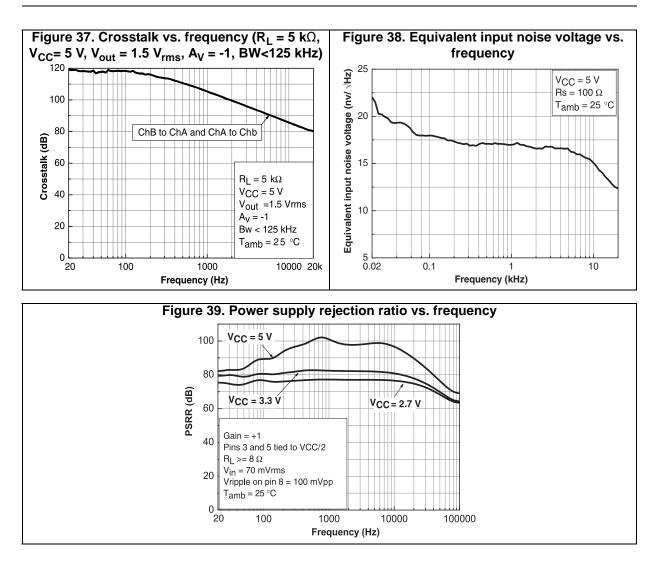

### 3.1 Exposed-pad package description

The dual operational amplifier TS982 is housed in an SO-8 exposed-pad plastic package. As shown in *Figure 40*, the die is mounted and glued on a lead frame. This lead frame is exposed as a thermal pad on the underside of the package. The thermal contact is direct with the die and therefore, offers an excellent thermal performance in comparison with the common SO packages. The thermal contact between the die and the exposed-pad is characterized using the parameter  $R_{thjc}$ .

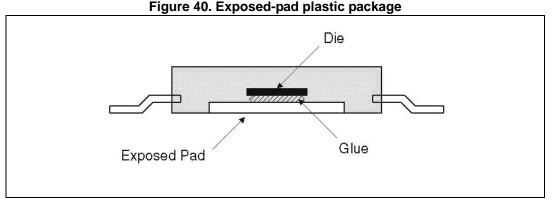

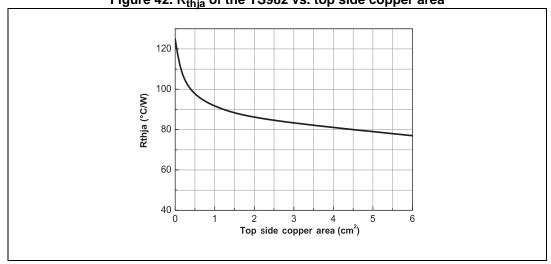

As 90% of the heat is removed through the pad, the thermal dissipation of the circuit is directly linked to the copper area soldered to the pad. In other words, the  $R_{thja}$  depends on the copper area and the number of layers of the printed circuit board under the pad.

Figure 41. TS982 test board layout - 6 cm<sup>2</sup> of copper topside

## 3.2 Exposed-pad electrical connection

In the SO-8 exposed-pad package, the silicon die is mounted on the thermal pad (see *Figure 40*). The silicon substrate is not directly connected to the pad because of the glue. Therefore, the copper area of the exposed-pad must be connected to the substrate voltage  $(V_{CC})$  pin 4.

#### 3.3 Thermal management benefits

A good thermal design is important to maintain the temperature of the silicon junction below  $T_j = 150$  °C as given in the absolute maximum ratings and also to maintain the operating power level.

Another effect of temperature is that the life expectancy of an integrated circuit decreases exponentially when operating at high temperature over an extended period of time. It is estimated that, the chip failure rate doubles for every 10 to 20 °C. This demonstrates that reducing the junction temperature is also important to improve the reliability of the amplifier.

Because of the high dissipation capability of the SO-8 exposed-pad package, the dual op amp TS982 has a lower junction temperature for high current applications in high ambient temperatures.

#### 3.4 Thermal management guidelines

The following guidelines are a simple procedure to determine the PCB you should use in order to get the best from the SO-8 exposed-pad package:

1. Determine the total power P<sub>total</sub> to be dissipated by the IC.

$P_{total} = I_{CC} \times V_{CC} + V_{drop1} \times I_{out1} + V_{drop2} \times I_{out2}$

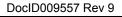

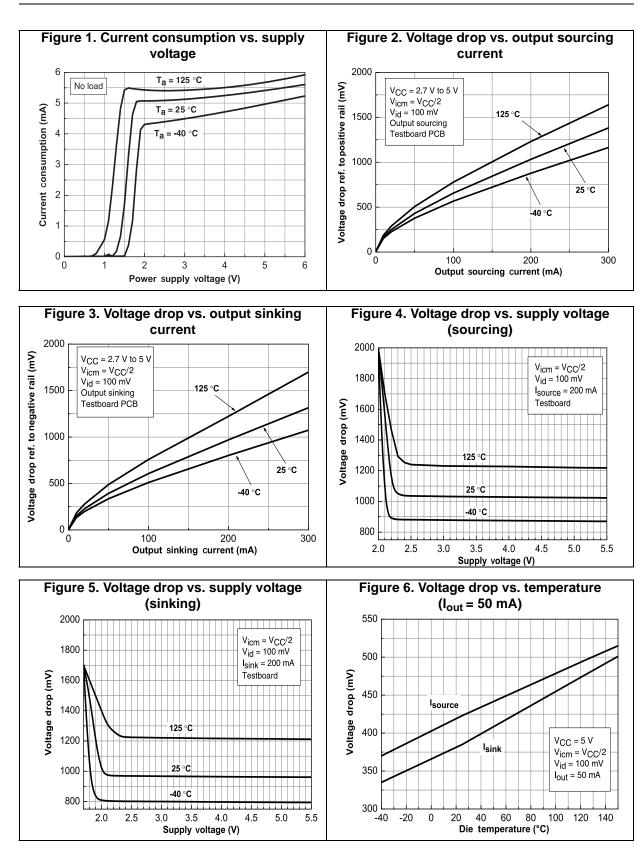

$I_{CC} \times V_{CC}$  is the DC power needed by the TS982 to operate with no load. Refer to *Figure 1: Current consumption vs. supply voltage on page 7* to determine  $I_{CC}$  versus  $V_{CC}$  and versus temperature.

The other terms are the power dissipated by the two operators to source the load. If the output signal can be assimilated to a DC signal, you can calculate the dissipated power using the voltage drop curves versus output current, supply voltage, and temperature (*Figure 2 on page 7* to *Figure 8 on page 8*).

- 2. Specify the maximum operating temperature, (T<sub>a</sub>) of the TS982.

- Specify the maximum junction temperature (T<sub>j</sub>) at the maximum output power. As discussed above, T<sub>j</sub> must be below 150 °C and as low as possible for reliability considerations.

Therefore, the maximum thermal resistance between junction and ambient R<sub>thia</sub> is:

$R_{thja} = (T_j - T_a)/P_{total}$

Different PCBs can give the right  $R_{thja}$  for a given application. *Figure 42* gives the  $R_{thja}$  of the SO-8 exposed pad versus the copper area of a top side PCB.

Figure 42.  $R_{thja}$  of the TS982 vs. top side copper area

The ultimate  $R_{thja}$  of the package on a 4-layer PCB under natural convection conditions, is 45  $^\circ C/W$  by using two power planes and metallized holes.

#### 3.5 Parallel operation

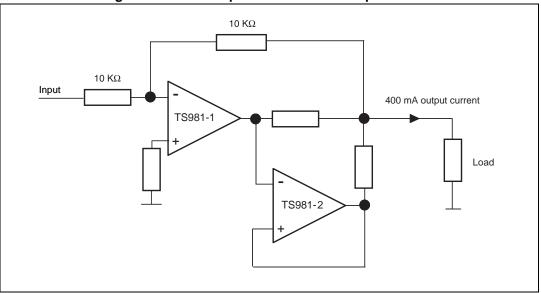

Using the two amplifiers of the TS982 device in parallel mode provides a higher output current: 400 mA.

Figure 43. Parallel operation - 400 mA output current

# 4 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK is an ST trademark.

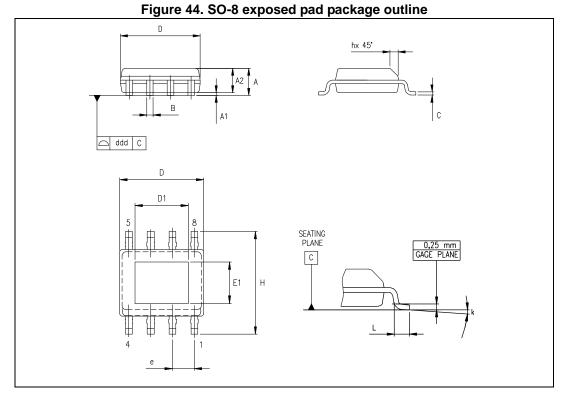

### 4.1 SO-8 exposed pad package information

### Table 6. SO-8 exposed pad package mechanical data

|        |             |      | Dime   | nsions |       |       |

|--------|-------------|------|--------|--------|-------|-------|

| Symbol | Millimeters |      | Inches |        |       |       |

| -      | Min.        | Тур. | Max.   | Min.   | Тур.  | Max.  |

| А      | 1.35        |      | 1.75   | 0.053  |       | 0.069 |

| A1     | 0.10        |      | 0.15   | 0.04   |       | 0.059 |

| A2     | 1.10        |      | 1.65   | 0.043  |       | 0.065 |

| В      | 0.33        |      | 0.51   | 0.013  |       | 0.020 |

| С      | 0.19        |      | 0.25   | 0.007  |       | 0.010 |

| D      | 4.80        |      | 5.00   | 0.189  |       | 0.197 |

| D1     |             | 3.1  | I      | 0.122  |       |       |

| E      | 3.80        |      | 4.00   | 0.150  |       | 0.157 |

| E1     |             | 2.41 |        |        | 0.095 |       |

| е      |             | 1.27 |        |        | 0.050 |       |

| Н      | 5.80        |      | 6.20   | 0.228  |       | 0.244 |

| h      | 0.25        |      | 0.50   | 0.010  |       | 0.020 |

| L      | 0.40        |      | 1.27   | 0.016  |       | 0.050 |

| k      | 8° (max.)   |      |        |        |       |       |

| ddd    |             |      | 0.1    |        |       | 0.04  |

# 5 Ordering information

Table 7. Order code

| Order code                | Temperature range | Package                             | Packing       | Marking |

|---------------------------|-------------------|-------------------------------------|---------------|---------|

| TS982IDWT                 |                   | SO-8 exposed-pad                    | Tape and reel | TS982I  |

| TS982IYDWT <sup>(1)</sup> | -40 °C to +125 °C | SO-8 exposed-pad (automotive-grade) | Tape and reel | TS982IY |

1. Qualified and characterized according to AEC Q100 and Q003 or equivalent, advanced screening according to AEC Q001 and Q002 or equivalent.

# 6 Revision history

| Table 8. | Document | revision | history |

|----------|----------|----------|---------|

|----------|----------|----------|---------|

| Date         | Revision | Changes                                                                                                                                                                                                                                                                                                               |

|--------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02-Jan-2004  | 1        | First release.                                                                                                                                                                                                                                                                                                        |

| 01-Feb- 2004 | 2        | Order codes modified on cover page.                                                                                                                                                                                                                                                                                   |

| 01-Dec-2005  | 3        | PPAP references inserted in the datasheet see <i>Table 4: Ordering information on page 19.</i>                                                                                                                                                                                                                        |

| 02-Apr-2006  | 4        | $V_{OH}$ and $V_{OL}$ limits (at $V_{CC}$ = 4.75 V, $T_{amb}$ = 125° C) added in <i>Table 3. on page 4.</i>                                                                                                                                                                                                           |

| 24-Oct-2006  | 5        | Corrections to Section 2.3: Thermal management benefits and<br>Section 2.4: Thermal management guidelines on page 15.<br>Pad size added to package mechanical data table under SO-8<br>exposed pad package outline on page 18, and stand-off value<br>corrected.<br>Corrected value of $V_{OH}$ for $V_{CC}$ = 2.7 V. |

| 5-Jun-2008   | 6        | Moved ordering information from cover page to end of document.<br>Added footnotes for ESD parameters in <i>Table 1: Absolute maximum ratings (AMR)</i> .<br>Added footnote for automotive grade parts in <i>Table 7: Order codes</i> .                                                                                |

| 28-Aug-2012  | 7        | Corrected numbering of tables, added conditions to titles of <i>Figure 9</i> to <i>Figure 37</i> , updated ECOPACK text, removed TS982IDW and TS982IYDW device from <i>Table 7</i> , minor corrections throughout document.                                                                                           |

| 10-Mar-2014  | 8        | Updated R <sub>thjc</sub> in <i>Table 1: Absolute maximum ratings (AMR)</i> .                                                                                                                                                                                                                                         |

| 15-Mar-2018  | 9        | Updated R <sub>thjc</sub> in Table 1: Absolute maximum ratings (AMR)                                                                                                                                                                                                                                                  |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics - All rights reserved

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

STMicroelectronics: <u>TS982IDWT</u> <u>TS982IYDWT</u>