## 512-Kbit SPI Bus Serial EEPROM

#### **Device Selection Table**

| Part Number | Vcc Range | Page Size | Temp. Ranges | Packages      |

|-------------|-----------|-----------|--------------|---------------|

| 25LC512     | 2.5V-5.5V | 128 Byte  | I,E          | P, SN, SM, MF |

#### **Features**

- · 20 MHz maximum Clock Speed

- Byte and Page-level Write Operations:

- 128-byte page

- 5 ms maximum

- No page or sector erase required

- · Low-Power CMOS Technology:

- Max. Write current: 7 mA at 5.5V

- Max. Read current: 10 mA at 5.5V, 20 MHz

- Standby current:  $1\mu A$  at 2.5V,  $85^{\circ}C$  (Deep power-down)

- · Electronic Signature for Device ID

- · Self-Timed Erase and Write cycles:

- Page Erase (5 ms, typical)

- Sector Erase (10 ms/sector, typical)

- Bulk Erase (10 ms, typical)

- Sector Write Protection (16K byte/sector):

- Protect none, 1/4, 1/2 or all of array

- · Built-In Write Protection:

- Power-on/off data protection circuitry

- Write enable latch

- Write-protect pin

- Seguential Read

- · High Reliability:

- Endurance: 1 Million erase/write cycles

- Data Retention: >200 years

- ESD Protection: >4000V

- · Temperature Ranges Supported:

- Industrial (I): -40°C to +85°C - Extended (E): -40°C to +125°C

- RoHS Compliant

- Automotive AEC-Q100 Qualified

#### **Pin Function Table**

| Name | Function           |

|------|--------------------|

| CS   | Chip Select Input  |

| SO   | Serial Data Output |

| WP   | Write-Protect      |

| Vss  | Ground             |

| SI   | Serial Data Input  |

| SCK  | Serial Clock Input |

| HOLD | Hold Input         |

| Vcc  | Supply Voltage     |

### **Description**

The Microchip Technology Inc. 25LC512 is a 512-Kbit serial EEPROM memory with byte-level and page-level serial EEPROM functions. It also features Page, Sector and Chip erase functions typically associated with Flash-based products. These functions are not required for byte or page write operations. The memory is accessed via a simple Serial Peripheral Interface (SPI) compatible serial bus. The bus signals required are a clock input (SCK) plus separate data in (SI) and data out (SO) lines. Access to the device is controlled by a Chip Select  $(\overline{CS})$  input.

Communication to the device can be paused via the hold pin (HOLD). While the device is paused, transitions on its inputs will be ignored, with the exception of Chip Select, allowing the host to service higher priority interrupts.

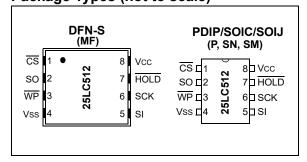

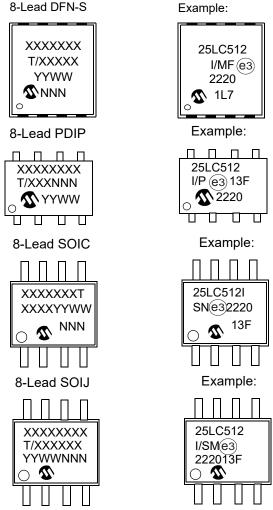

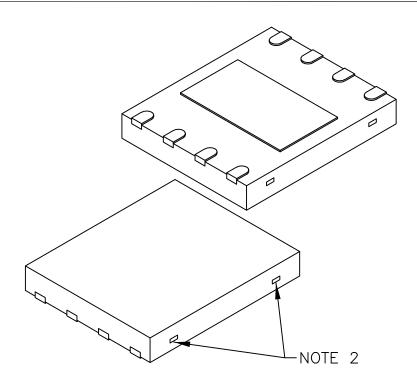

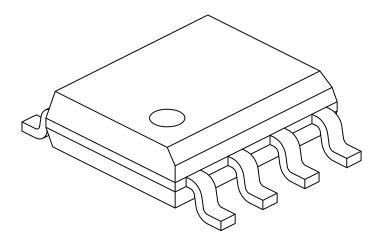

#### **Packages**

8-Lead DFN-S, 8-Lead PDIP, 8-Lead SOIC and 8-Lead SOIJ

## Package Types (not to scale)

## 1.0 ELECTRICAL CHARACTERISTICS

## Absolute Maximum Ratings (†)

| Vcc                               | 6.5\              |

|-----------------------------------|-------------------|

| All inputs and outputs w.r.t. Vss | 0.6V to Vcc +1.0\ |

| Storage temperature               | 65°C to 150°C     |

| Ambient temperature under bias    | 40°C to 125°C     |

| ESD protection on all pins        | 4 k\              |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for an extended period of time may affect device reliability.

TABLE 1-1: DC CHARACTERISTICS

| DC CHARACTERISTICS |                      |                                                     |                                |           |                 |                                                   |

|--------------------|----------------------|-----------------------------------------------------|--------------------------------|-----------|-----------------|---------------------------------------------------|

| Param.<br>No.      | SVM   Characteristic |                                                     | Characteristic Min. Max. Units |           | Test Conditions |                                                   |

| D001               | VIH1                 | High-level input voltage                            | 0.7 x Vcc                      | Vcc + 1   | V               |                                                   |

| D002               | VIL1                 | Low-level input                                     | -0.3                           | 0.3 x Vcc | V               | Vcc ≥ 2.7V                                        |

| D003               | VIL2                 | voltage                                             | -0.3                           | 0.2 x Vcc | V               | Vcc < 2.7V                                        |

| D004               | Vol                  | Low-level output voltage                            | _                              | 0.4       | V               | IOL = 2.1 mA                                      |

| D005               | Vон                  | High-level output voltage                           | Vcc - 0.2                      | _         | V               | Іон = -400 μΑ                                     |

| D006               | ILI                  | Input leakage current                               | _                              | ±1        | μΑ              | CS = Vcc, Vin = Vss or Vcc                        |

| D007               | ILO                  | Output leakage current                              | _                              | ±1        | μА              | CS = Vcc, Vout = Vss or Vcc                       |

| D008               | CINT                 | Internal capacitance<br>(all inputs and<br>outputs) | _                              | 7         | pF              | TA = 25°C, CLK = 1.0 MHz,<br>VCC = 5.0V (Note)    |

| D009               | Icc Bood             |                                                     | _                              | 10        | mA              | VCC = 5.5V; FCLK = 20.0 MHz;<br>SO = Open         |

| D009               | 9 Icc Read           | Operating current                                   | _                              | 5         | mA              | VCC = 2.5V; FCLK = 10.0 MHz;<br>SO = Open         |

| D010               | Icc Write            |                                                     | _                              | 7         | mA              | Vcc = 5.5V                                        |

| D010               | icc wiile            |                                                     | _                              | 5         | mA              | Vcc = 2.5V                                        |

| D044               | logo                 | Ctan dhy ay mant                                    | _                              | 20        | μΑ              | CS = Vcc = 5.5V, Inputs tied to Vcc or Vss, 125°C |

| D011               | Iccs                 | Standby current                                     | _                              | 10        | μΑ              | CS = Vcc = 5.5V, Inputs tied to Vcc or Vss, 85°C  |

| D012               | locopp               | Deep power-down                                     | _                              | 2         | μΑ              | CS = Vcc = 2.5V, Inputs tied to Vcc or Vss, 125°C |

| D012               | ICCSPD               | current                                             | _                              | 1         | μΑ              | CS = Vcc = 2.5V, Inputs tied to Vcc or Vss, 85°C  |

Note: This parameter is periodically sampled and not 100% tested.

TABLE 1-2: AC CHARACTERISTICS

| AC CHARACTERISTICS |        |                             | Electrical Characteristics: Industrial (I): TA = -40°C to +85°C |      |       |                                   |

|--------------------|--------|-----------------------------|-----------------------------------------------------------------|------|-------|-----------------------------------|

| Param.<br>No.      | Sym.   | Characteristic              | Min.                                                            | Max. | Units | Conditions                        |

| 1                  | Four   | Clask fraguency             | _                                                               | 20   | MHz   | 4.5V ≤ VCC ≤ 5.5V (I)             |

| 1                  | FCLK   | Clock frequency             | _                                                               | 10   | MHz   | 2.5V ≤ VCC < 5.5V (I, E)          |

| 2                  | Tcss   | CS setup time               | 25                                                              |      | ns    | 4.5V ≤ Vcc ≤ 5.5V (I)             |

| 2                  | 1055   | C5 setup time               | 50                                                              | _    | ns    | 2.5V ≤ VCC < 5.5V (I, E)          |

| 0                  | Tage   | CS hold time                | 50                                                              | _    | ns    | 4.5V ≤ VCC ≤ 5.5V (I)             |

| 3                  | Тсѕн   | CS noid time                | 100                                                             | _    | ns    | 2.5V ≤ VCC < 5.5V (I, E)          |

| 4                  | TCSD   | CS disable time             | 50                                                              |      | ns    | _                                 |

| 5                  | Tour   | Data catus time             | 5                                                               |      | ns    | 4.5V ≤ VCC ≤ 5.5V (I)             |

| 5                  | Tsu    | Data setup time             | 10                                                              | _    | ns    | 2.5V ≤ VCC < 5.5V (I, E)          |

| 6                  | THD    | Data hold time              | 10                                                              | _    | ns    | 4.5V ≤ VCC ≤ 5.5V (I)             |

| 0                  | וחט    | Data floid time             | 20                                                              |      | ns    | $2.5V \le VCC < 5.5V (I, E)$      |

| 7                  | TR     | CLK rise time               | _                                                               | 20   | ns    | (Note 1)                          |

| 8                  | TF     | CLK fall time               | _                                                               | 20   | ns    | (Note 1)                          |

| 9                  | THI    | Clock high time             | 25                                                              | _    | ns    | 4.5V ≤ VCC ≤ 5.5V (I)             |

|                    |        | Green ingriums              | 50                                                              | _    | ns    | 2.5V ≤ VCC < 5.5V (I, E)          |

| 10                 | TLO    | Clock low time              | 25                                                              | _    | ns    | 4.5V ≤ VCC ≤ 5.5V (I)             |

|                    |        |                             | 50                                                              | _    | ns    | 2.5V ≤ VCC < 5.5V (I, E)          |

| 11                 | TCLD   | Clock delay time            | 50                                                              |      | ns    | _                                 |

| 12                 | TCLE   | Clock enable time           | 50                                                              |      | ns    | _                                 |

| 13                 | Tv     | Output valid from clock low |                                                                 | 25   | ns    | 4.5V ≤ VCC ≤ 5.5V (I)             |

|                    | _      | 0 ( ) ( )                   | _                                                               | 50   | ns    | 2.5V ≤ VCC < 5.5V (I, E)          |

| 14                 | Тно    | Output hold time            | 0                                                               |      | ns    | (Note 1)                          |

| 15                 | TDIS   | Output disable time         | _                                                               | 25   | ns    | 4.5V ≤ VCC ≤ 5.5V (I)             |

|                    |        |                             | <u> </u>                                                        | 50   | ns    | 2.5V ≤ VCC < 5.5V (I, E)          |

| 16                 | THS    | HOLD setup time             | 10                                                              | _    | ns    | 4.5V ≤ VCC ≤ 5.5V (I)             |

|                    |        |                             | 20                                                              | _    | ns    | 2.5V ≤ VCC < 5.5V (I, E)          |

| 17                 | Тнн    | HOLD hold time              | 10                                                              |      | ns    | 4.5V ≤ VCC ≤ 5.5V (I)             |

|                    |        |                             | 20                                                              | _    | ns    | 2.5V ≤ VCC < 5.5V (I, E)          |

|                    |        | HOLD low to output          | _                                                               | 15   | ns    | 4.5V ≤ VCC ≤ 5.5V (I)             |

| 18                 | THZ    | High-Z                      | _                                                               | 30   | ns    | 2.5V ≤ VCC < 5.5V (I, E) (Note 1) |

| 19                 | TH∨    | HOLD high to output valid   | _                                                               | 15   | ns    | 4.5V ≤ VCC ≤ 5.5V (I)             |

|                    | 1 TI V | TIOLD High to output valid  | _                                                               | 30   | ns    | $2.5V \le VCC < 5.5V (I, E)$      |

| 20                 | TREL   | CS High to Standby mode     | _                                                               | 100  | μS    | _                                 |

| 21                 | TPD    | CS High to Deep power-down  | _                                                               | 100  | μS    | _                                 |

| 22                 | TCE    | Chip erase cycle time       | _                                                               | 10   | ms    | _                                 |

| 23                 | TSE    | Sector erase cycle time     | _                                                               | 10   | ms    |                                   |

Note 1: This parameter is periodically sampled and not 100% tested.

2: This parameter is not tested but established by characterization and qualification.

TABLE 1-2: AC CHARACTERISTICS (CONTINUED)

| AC CHARACTERISTICS |      |                           | Electrical C<br>Industrial (<br>Extended ( | ,    | cs:<br>-40°C to<br>-40°C to |                                     |

|--------------------|------|---------------------------|--------------------------------------------|------|-----------------------------|-------------------------------------|

| Param.<br>No.      | Sym. | Characteristic            | Min.                                       | Max. | Units                       | Conditions                          |

| 24                 | Twc  | Internal write cycle time | _                                          | 5    | ms                          | Byte or Page mode and Page<br>Erase |

| 25                 | _    | Endurance                 | 1M                                         | _    | E/W<br>Cycles               | Page mode, 25°C, 5.5V (Note 2)      |

**Note 1:** This parameter is periodically sampled and not 100% tested.

TABLE 1-3: AC TEST CONDITIONS

| AC Waveform:                       |          |  |  |  |  |

|------------------------------------|----------|--|--|--|--|

| VLO = 0.2V                         |          |  |  |  |  |

| VHI = VCC - 0.2V                   | (Note 1) |  |  |  |  |

| VHI = 4.0V                         | (Note 2) |  |  |  |  |

| CL = 30 pF                         | _        |  |  |  |  |

| Timing Measurement Reference Level |          |  |  |  |  |

| Input                              | 0.5 Vcc  |  |  |  |  |

| Output                             | 0.5 Vcc  |  |  |  |  |

**Note 1:** For  $Vcc \le 4.0V$

2: For Vcc > 4.0V

<sup>2:</sup> This parameter is not tested but established by characterization and qualification.

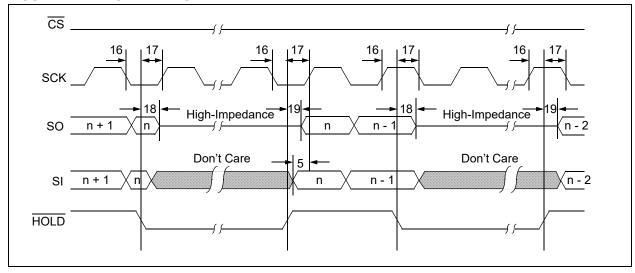

FIGURE 1-1: HOLD TIMING

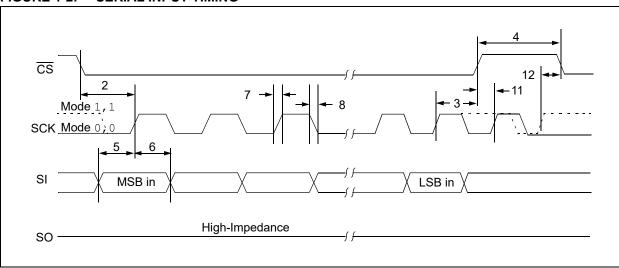

FIGURE 1-2: SERIAL INPUT TIMING

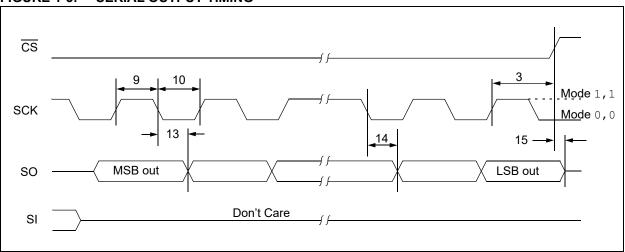

FIGURE 1-3: SERIAL OUTPUT TIMING

## 2.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 2-1.

TABLE 2-1: PIN FUNCTION TABLE

| Name | 8-Lead DFN-S <sup>(1)</sup> | 8-Lead PDIP | 8-Lead SOIC | 8-Lead SOIJ | Function           |  |

|------|-----------------------------|-------------|-------------|-------------|--------------------|--|

| CS   | 1                           | 1           | 1           | 1           | Chip Select Input  |  |

| SO   | 2                           | 2           | 2           | 2           | Serial Data Output |  |

| WP   | 3                           | 3           | 3           | 3           | Write-Protect Pin  |  |

| Vss  | 4                           | 4           | 4           | 4           | Ground             |  |

| SI   | 5                           | 5           | 5           | 5           | Serial Data Input  |  |

| SCK  | 6                           | 6           | 6           | 6           | Serial Clock Input |  |

| HOLD | 7                           | 7           | 7           | 7           | Hold Input         |  |

| Vcc  | 8                           | 8           | 8           | 8           | Supply Voltage     |  |

Note 1: The exposed pad on DFN-S package can be connected to Vss or left floating.

## 2.1 Chip Select (CS)

A low level on this pin selects the device. A high level deselects the device and forces it into Standby mode. However, a programming cycle which is already initiated or in progress will be completed, regardless of  $\overline{CS}$  input signal. If  $\overline{CS}$  is brought high during a program cycle, the device will go into Standby mode as soon as programming cycle is complete. When device is deselected, SO goes to the high-impedance state, allowing multiple parts to share the same SPI bus. A low-to-high transition on  $\overline{CS}$  after a valid write sequence initiates an internal write cycle. After power-up, a low level on  $\overline{CS}$  is required prior to any sequence being initiated.

### 2.2 Serial Output (SO)

The SO pin is used to transfer data out of the 25LC512. During a read cycle, data is shifted out on this pin after the falling edge of the serial clock.

## 2.3 Write-Protect (WP)

This pin is used in conjunction with WPEN bit in STATUS register to prohibit writes to the nonvolatile bits in the STATUS register. When  $\overline{\text{WP}}$  is low and WPEN is high, writing to the nonvolatile bits in the STATUS register is disabled. All other operations function normally. When  $\overline{\text{WP}}$  is high, all functions, including writes to the nonvolatile bits in the STATUS register, operate normally. If the WPEN bit is set,  $\overline{\text{WP}}$  low during a STATUS register write sequence will disable writing to the STATUS register. If an internal write cycle has already begun,  $\overline{\text{WP}}$  going low will have no effect on the write.

The WP pin function is blocked when WPEN bit in STATUS register is low. This allows the user to install the 25LC512 in a system with WP pin grounded and still be able to write to the STATUS register. The WP pin functions will be enabled when the WPEN bit is set high.

## 2.4 Serial Input (SI)

The SI pin is used to transfer data into the device. It receives instructions, addresses and data. Data is latched on the rising edge of the serial clock.

## 2.5 Serial Clock (SCK)

The SCK is used to synchronize the communication between a host and the 25LC512. Instructions, addresses or data present on the SI pin are latched on the rising edge of the clock input, while data on the SO pin is updated after the falling edge of the clock input.

## 2.6 Hold (HOLD)

The HOLD pin is used to suspend transmission to the 25LC512 while in the middle of a serial sequence without having to re-transmit the entire sequence over again. It must be held high any time this function is not being used. Once the device is selected and a serial sequence is underway, the HOLD pin may be pulled low to pause further serial communication without resetting the serial sequence.

The HOLD pin must be brought low while SCK is low, otherwise the HOLD function will not be invoked until the next SCK high-to-low transition. The 25LC512 must remain selected during this sequence. The SI and SCK levels are "don't cares" during the time the device is paused and any transitions on these pins will be ignored. To resume serial communication, HOLD must be brought high while the SCK pin is low, otherwise serial communication will not be resumed until the next SCK high-to-low transition.

The SO line will tri-state immediately upon a high-to-low transition of the HOLD pin, and will begin outputting again immediately upon a subsequent low-to-high transition of the HOLD pin, independent of the state of SCK.

## 3.0 FUNCTIONAL DESCRIPTION

## 3.1 Principles of Operation

The 25LC512 is a 65,536 byte Serial EEPROM designed to interface directly with the Serial Peripheral Interface (SPI) port of many of today's popular microcontroller families, including Microchip's PIC® microcontrollers. It may also interface with microcontrollers that do not have a built-in SPI port by using discrete I/O lines programmed properly in firmware to match the SPI protocol.

The 25LC512 contains an 8-bit instruction register. The device is accessed via the SI pin, with data being clocked in on the rising edge of SCK. The CS pin must be low and the HOLD pin must be high for the entire operation.

Table 3-1 contains a list of the possible instruction bytes and format for device operation. All instructions, addresses, and data are transferred MSB first, LSB last

Data  $\underline{(SI)}$  is sampled on the first rising edge of SCK after  $\overline{CS}$  goes low. If the clock line is shared with other peripheral devices on the SPI bus, the user can assert the  $\overline{HOLD}$  input and place the 25LC512 in 'HOLD' mode. After releasing the  $\overline{HOLD}$  pin, operation will resume from the point when the  $\overline{HOLD}$  was asserted.

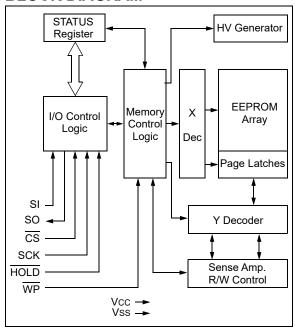

### **BLOCK DIAGRAM**

TABLE 3-1: INSTRUCTION SET

| Instruction Name | Instruction Format | Description                                                |

|------------------|--------------------|------------------------------------------------------------|

| READ             | 0000 0011          | Read data from memory array beginning at selected address  |

| WRITE            | 0000 0010          | Write data to memory array beginning at selected address   |

| WREN             | 0000 0110          | Set the write enable latch (enable write operations)       |

| WRDI             | 0000 0100          | Reset the write enable latch (disable write operations)    |

| RDSR             | 0000 0101          | Read STATUS register                                       |

| WRSR             | 0000 0001          | Write STATUS register                                      |

| PE               | 0100 0010          | Page Erase – erase one page in memory array                |

| SE               | 1101 1000          | Sector Erase – erase one sector in memory array            |

| CE               | 1100 0111          | Chip Erase – erase all sectors in memory array             |

| RDID             | 1010 1011          | Release from Deep power-down and read electronic signature |

| DPD              | 1011 1001          | Deep Power-Down mode                                       |

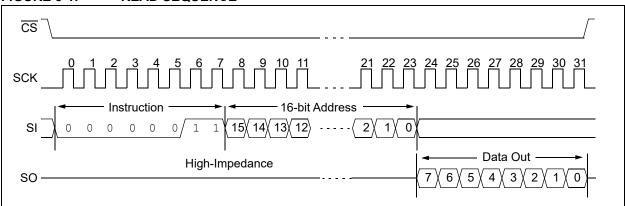

## 3.2 Read Sequence

The device is selected by pulling  $\overline{\text{CS}}$  low. The 8-bit READ instruction is transmitted to the 25LC512 followed by the 16-bit address.

After the correct READ instruction and address are sent, the data stored in the memory at the selected address is shifted out on the SO pin. The data stored in the memory at the next address can be read sequentially by continuing to provide clock pulses.

The internal Address Pointer is automatically incremented to the next higher address after each byte of data is shifted out. When the highest address is reached (FFFFh), the address counter rolls over to address 0000h allowing the read cycle to be continued indefinitely. The READ instruction is terminated by raising the  $\overline{\text{CS}}$  pin (Figure 3-1).

FIGURE 3-1: READ SEQUENCE

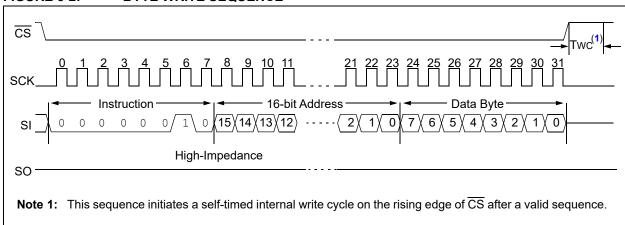

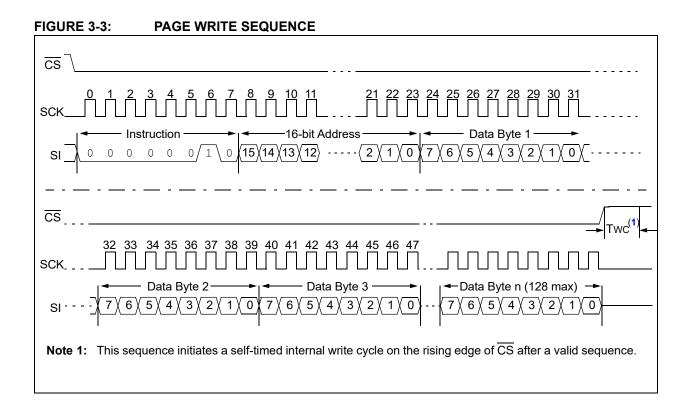

## 3.3 Write Sequence

Prior to any attempt to write data to the 25LC512, the write enable latch must be set by issuing the  $\underline{\mathtt{WREN}}$  instruction (Figure 3-4). This is done by setting  $\overline{\mathtt{CS}}$  low and then clocking out the proper instruction into the 25LC512. After all eight bits of the instruction are transmitted, the  $\overline{\mathtt{CS}}$  must be brought high to set the write enable latch.

If the write operation is initiated immediately after the WREN instruction without  $\overline{\text{CS}}$  being brought high, the data will not be written to the array because the write enable latch will not have been properly set.

A write sequence includes an automatic, self timed erase cycle. It is not required to erase any portion of the memory prior to issuing a WRITE instruction.

Once the write enable latch is set, the user may proceed by setting the  $\overline{\text{CS}}$  low, issuing a WRITE instruction, followed by the 16-bit address, and then the data to be written. Up to 128 bytes of data can be sent to the device before a write cycle is necessary. The only restriction is that all of the bytes must reside in the same page.

**Note:** When doing a write of less than 128 bytes the data in the rest of the page is refreshed along with the data bytes being written. This will force the entire page to endure a write cycle, for this reason

endurance is specified per page.

Page write operations are limited to writing bytes within a single physical page. regardless of the number of bytes actually being written. Physical page boundaries start at addresses that are integer multiples of the page buffer size (or 'page size'), and end at addresses that are integer multiples of page size – 1. If a Page Write command attempts to write across a physical page boundary, the result is that the data wraps around to the beginning of the current page (overwriting data previously stored there), instead of being written to the next page as might be expected. It is therefore necessary for the application software to prevent page write operations that would attempt to cross a

Note:

For the data to be actually written to the array, the CS must be brought high after the Least Significant bit (D0) of the *n*<sup>th</sup> data byte has been clocked in. If CS is brought high at any other time, the write operation will not be completed. Refer to Figure 3-2 and Figure 3-3 for more detailed illustrations on the byte write sequence and the page write sequence, respectively. While the write is in progress, the STATUS register may be read to check the status of the WPEN, WIP, WEL, BP1 and BP0 bits (Figure 3-6). A read attempt of a memory array location will not be possible during a write cycle. When the write cycle is completed, the write enable latch is reset.

page boundary.

### FIGURE 3-2: BYTE WRITE SEQUENCE

## 25LC512

## 3.4 Write Enable (WREN) and Write Disable (WRDI)

The 25LC512 contains a write enable latch. See Table 3-4 for the Write-Protect Functionality Matrix. This latch must be set before any write operation will be completed internally. The  $\mathtt{WREN}$  instruction will set the latch, and the  $\mathtt{WRDI}$  will reset the latch.

The following is a list of conditions under which the write enable latch will be reset:

- Power-up

- WRDI instruction successfully executed

- · WRSR instruction successfully executed

- WRITE instruction successfully executed

- PE instruction successfully executed

- · SE instruction successfully executed

- · CE instruction successfully executed

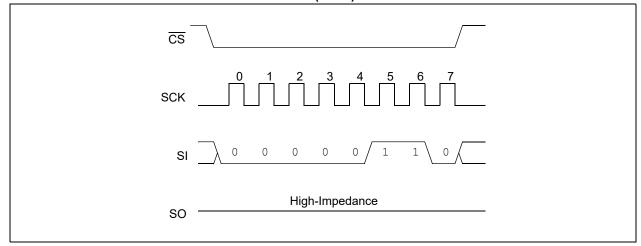

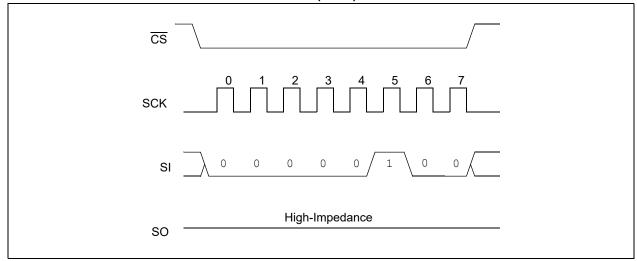

FIGURE 3-4: WRITE ENABLE SEQUENCE (WREN)

FIGURE 3-5: WRITE DISABLE SEQUENCE (WRDI)

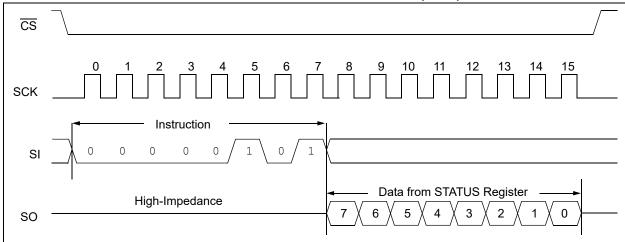

## 3.5 Read Status Register Instruction (RDSR)

The Read Status Register instruction (RDSR) provides access to the STATUS register. See Figure 3-6 for the RDSR timing sequence. The STATUS register may be read at any time, even during a write cycle. The STATUS register is formatted as follows:

TABLE 3-2: STATUS REGISTER

| 7    | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|------|---|---|---|-----|-----|-----|-----|

| W/R  | - | - | - | W/R | W/R | R   | R   |

| WPEN | Χ | Χ | Χ | BP1 | BP0 | WEL | WIP |

**Note:** W/R = writable/readable. R = read-only.

The **Write-In-Process (WIP)** bit indicates whether the 25LC512 is busy with a write operation. When set to a '1', a write is in progress, when set to a '0', no write is in progress. This bit is read-only.

The **Write Enable Latch (WEL)** bit indicates the status of the write enable latch and is read-only. When set to a '1', the latch allows writes to the array, when set to a '0', the latch prohibits writes to the array. The state of this bit can always be updated via the WREN or WRDI commands regardless of the state of write protection on the STATUS register. These commands are shown in Figure 3-4 and Figure 3-5.

The **Block Protection (BP0 and BP1)** bits indicate which blocks are currently write-protected. These bits are set by the user issuing the WRSR instruction. These bits are nonvolatile, and are shown in Table 3-3.

FIGURE 3-6: READ STATUS REGISTER TIMING SEQUENCE (RDSR)

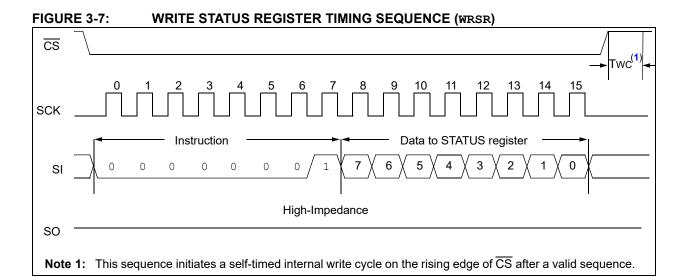

## 3.6 Write Status Register Instruction (WRSR)

The Write Status Register instruction (WRSR) allows the user to write to the nonvolatile bits in the STATUS register as shown in Table 3-2. The user is able to select one of four levels of protection for the array by writing to the appropriate bits in the STATUS register. The array is divided up into four segments. The user has the ability to write-protect none, one, two or all four of the segments of the array. The partitioning is controlled as shown in Table 3-3.

The Write-Protect Enable (WPEN) bit is a nonvolatile bit that is available as an enable bit for the  $\overline{\text{WP}}$  pin. The Write-Protect ( $\overline{\text{WP}}$ ) pin and the Write-Protect Enable (WPEN) bit in the STATUS register control the programmable hardware write-protect feature. Hardware write protection is enabled when  $\overline{\text{WP}}$  pin is low and the WPEN bit is high. Hardware write protection is disabled when either the  $\overline{\text{WP}}$  pin is high or the WPEN bit is low. When the chip is hardware write-protected, only writes to nonvolatile bits in the STATUS register are disabled. See Table 3-4 for a matrix of functionality on the WPEN bit.

See Figure 3-7 for the WRSR timing sequence.

**TABLE 3-3: ARRAY PROTECTION**

| BP1 | BP0 | Array Addresses<br>Write-Protected         | Array Addresses<br>Unprotected                |

|-----|-----|--------------------------------------------|-----------------------------------------------|

| 0   | 0   | none                                       | All (Sectors 0, 1, 2 & 3)<br>(0000h-FFFFh)    |

| 0   | 1   | Upper 1/4 (Sector 3)<br>(C000h-FFFFh)      | Lower 3/4 (Sectors 0, 1 & 2)<br>(0000h-BFFFh) |

| 1   | 0   | Upper 1/2 (Sectors 2 & 3)<br>(8000h-FFFFh) | Lower 1/2 (Sectors 0 & 1)<br>(0000h-7FFFh)    |

| 1   | 1   | All (Sectors 0, 1, 2 & 3)<br>(0000h-FFFFh) | none                                          |

TABLE 3-4: WRITE-PROTECT FUNCTIONALITY MATRIX

| WEL<br>(SR bit 1) | WPEN<br>(SR bit 7) | WP<br>(pin 3) | Protected Blocks | Unprotected Blocks | STATUS Register |

|-------------------|--------------------|---------------|------------------|--------------------|-----------------|

| 0                 | Х                  | Х             | Protected        | Protected          | Protected       |

| 1                 | 0                  | Х             | Protected        | Writable           | Writable        |

| 1                 | 1                  | 0 (low)       | Protected        | Writable           | Protected       |

| 1                 | 1                  | 1 (high)      | Protected        | Writable           | Writable        |

x = don't care

## 25LC512

#### 3.7 PAGE ERASE

The PAGE ERASE instruction will erase all bits (FFh) inside the given page. A Write Enable (WREN) instruction must be given prior to attempting a PAGE ERASE. This is done by setting  $\overline{\text{CS}}$  low and then clocking out the proper instruction into the 25LC512. After all eight bits of the instruction are transmitted, the  $\overline{\text{CS}}$  must be brought high to set the write enable latch.

The PAGE ERASE instruction is entered by driving  $\overline{\text{CS}}$  low, followed by the instruction code (Figure 3-8) and two address bytes. Any address inside the page to be erased is a valid address.

$\overline{\text{CS}}$  must then be driven high after the last bit of the address or the PAGE ERASE will not execute. Once the  $\overline{\text{CS}}$  is driven high the self-timed PAGE ERASE cycle is started. The WIP bit in the STATUS register can be read to determine when the PAGE ERASE cycle is complete.

If a PAGE ERASE instruction is given to an address that has been protected by the Block Protect bits (BP0, BP1) then the sequence will be aborted and no erase will occur.

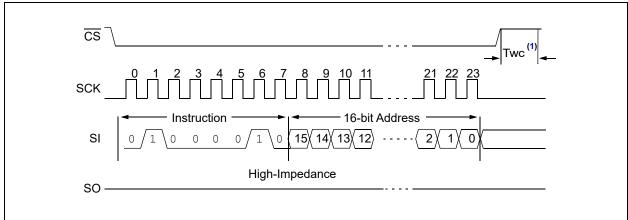

### FIGURE 3-8: PAGE ERASE SEQUENCE

Note 1: This sequence initiates a self-timed internal write cycle on the rising edge of CS after a valid sequence.

#### 3.8 SECTOR ERASE

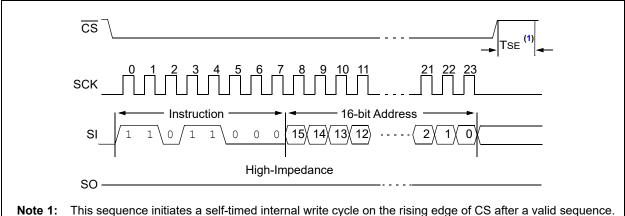

The SECTOR ERASE instruction will erase all bits (FFh) inside the given sector. A Write Enable (WREN) instruction must be given prior to attempting a SECTOR ERASE. This is done by setting CS low and then clocking out the proper instruction into the 25LC512. After all eight bits of the instruction are transmitted, the  $\overline{\text{CS}}$ must be brought high to set the write enable latch.

The SECTOR ERASE instruction is entered by driving CS low, followed by the instruction code (Figure 3-9) and two address bytes. Any address inside the sector to be erased is a valid address.

CS must then be driven high after the last bit of the address or the SECTOR ERASE will not execute. Once the  $\overline{\text{CS}}$  is driven high the self-timed SECTOR ERASE cycle is started. The WIP bit in the STATUS register can be read to determine when the SECTOR ERASE cycle is complete.

If a SECTOR ERASE instruction is given to an address that has been protected by the Block Protect bits (BP0, BP1) then the sequence will be aborted and no erase will occur.

See Table 3-3 for Sector Addressing.

FIGURE 3-9: **SECTOR ERASE SEQUENCE**

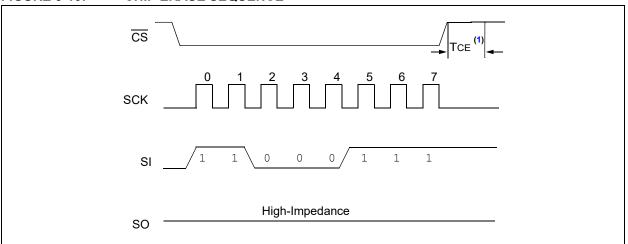

#### 3.9 CHIP ERASE

The CHIP ERASE instruction will erase all bits (FFh) in the array. A Write Enable (WREN) instruction must be given prior to executing a CHIP ERASE. This is done by setting  $\overline{\text{CS}}$  low and then clocking out the proper instruction into the 25LC512. After all eight bits of the instruction are transmitted, the  $\overline{\text{CS}}$  must be brought high to set the write enable latch.

The CHIP ERASE instruction is entered by driving the  $\overline{\text{CS}}$  low, followed by the instruction code (Figure 3-10) onto the SI line.

The  $\overline{\text{CS}}$  pin must be driven high after the eighth bit of the instruction code has been given or the CHIP ERASE instruction will not be executed. Once the  $\overline{\text{CS}}$  pin is driven high the self-timed CHIP ERASE instruction begins. While the device is executing the CHIP ERASE instruction the WIP bit in the STATUS register can be read to determine when the CHIP ERASE instruction is complete.

The CHIP ERASE instruction is ignored if either of the Block Protect bits (BP0, BP1) are set, meaning  $\frac{1}{4}$ ,  $\frac{1}{2}$ , or all of the array is protected.

FIGURE 3-10: CHIP ERASE SEQUENCE

Note 1: This sequence initiates a self-timed internal write cycle on the rising edge of CS after a valid sequence.

## 3.10 DEEP POWER-DOWN MODE

Deep Power-Down mode of the 25LC512 is its lowest power consumption state. The device will not respond to any of the Read or Write commands while in Deep Power-Down mode, and therefore it can be used as an additional software write protection feature.

The Deep Power-Down mode is entered by driving  $\overline{\text{CS}}$  low, followed by the instruction  $\underline{\text{code}}$  (Figure 3-11) onto the SI line, followed by driving  $\overline{\text{CS}}$  high.

If the  $\overline{CS}$  pin is not driven high after the eighth bit of the instruction code has been given, the device will not execute Deep power-down. Once the  $\overline{CS}$  line is driven high there is a delay  $(T_{DP})$  before the current settles to its lowest consumption.

All instructions given during Deep Power-Down mode are ignored except the Read Electronic Signature command (RDID). The RDID command will release the device from Deep power-down and outputs the electronic signature on the SO pin, and then returns the device to Standby mode after delay ( $T_{\rm REI}$ )

Deep Power-Down mode automatically releases at device power-down. Once power is restored to the device it will power-up in the Standby mode.

FIGURE 3-11: DEEP POWER-DOWN SEQUENCE

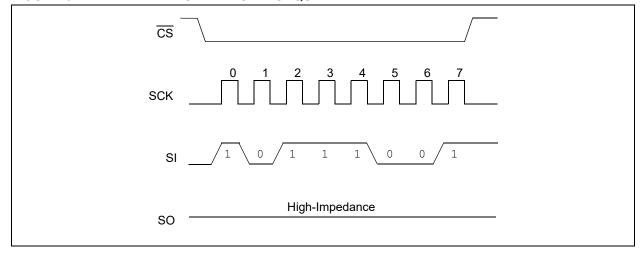

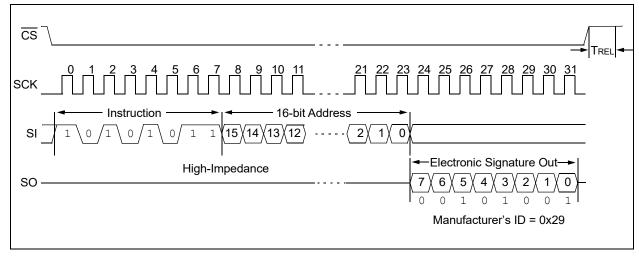

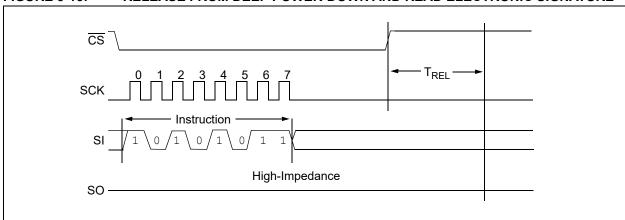

# 3.11 RELEASE FROM DEEP POWER-DOWN AND READ ELECTRONIC SIGNATURE

Once the device has entered Deep Power-Down mode all instructions are ignored except the Release from Deep Power-down and Read Electronic Signature command. This command can also be used when the device is not in Deep power-down to read the electronic signature out on the SO pin unless another command is being executed such as Erase, Program or Write Status Register.

Release from Deep Power-Down mode and Read Electronic Signature is entered by driving  $\overline{CS}$  low, followed by the RDID instruction code (Figure 3-12) and then a dummy address of 16 bits (A15-A0). After the last bit of the dummy address is clock in, the 8-bit Electronic Signature is clocked out on the SO pin.

After the signature has been read out at least once, the sequence can be terminated by driving  $\overline{\text{CS}}$  high. After a delay of TREL, the device will then return to Standby mode and will wait to be selected so it can be given new instructions. If additional clock cycles are sent after the electronic signature has been read once, it will continue to output the signature on the SO line until the sequence is terminated.

FIGURE 3-12: RELEASE FROM DEEP POWER-DOWN AND READ ELECTRONIC SIGNATURE

Driving  $\overline{\text{CS}}$  high after the 8-bit RDID command but before the Electronic Signature has been transmitted will still ensure the device will be taken out of Deep Power-Down mode, as shown in Figure 3-13.

FIGURE 3-13: RELEASE FROM DEEP POWER-DOWN AND READ ELECTRONIC SIGNATURE

## 4.0 DATA PROTECTION

The following protection has been implemented to prevent inadvertent writes to the array:

- · The write enable latch is reset on power-up

- A write enable instruction must be issued to set the write enable latch

- After a byte write, page write or STATUS register write, the write enable latch is reset

- CS must be set high after the proper number of clock cycles to start an internal write cycle

- Access to the array during an internal write cycle is ignored and programming is continued

### 5.0 POWER-ON STATE

The 25LC512 powers on in the following state:

- The device is in low-power Standby mode (CS = 1)

- · The write enable latch is reset

- · SO is in high-impedance state

### 6.0 PACKAGING INFORMATION

## 6.1 Package Marking Information

| 1 <sup>st</sup> Line Marking Codes |         |         |          |         |  |  |  |

|------------------------------------|---------|---------|----------|---------|--|--|--|

| Device                             | DFN-S   | PDIP    | SOIC     | SOIJ    |  |  |  |

| 25LC512                            | 25LC512 | 25LC512 | 25LC512T | 25LC512 |  |  |  |

Legend: XX...X Part number or part number code

T Temperature (I, E)

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code (2 characters for small packages)

e3 RoHS-compliant JEDEC® designator for Matte Tin (Sn)

Note: For very small packages with no room for the RoHS-compliant JEDEC®

designator (e3), the marking will only appear on the outer carton or reel label.

Note: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available

characters for customer-specific information.

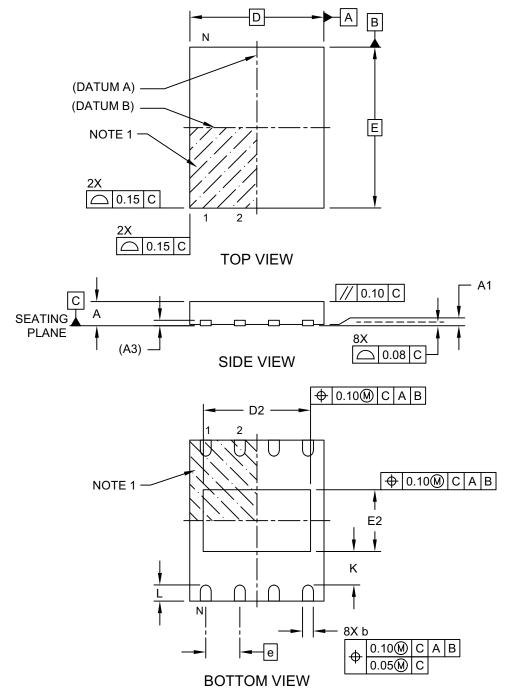

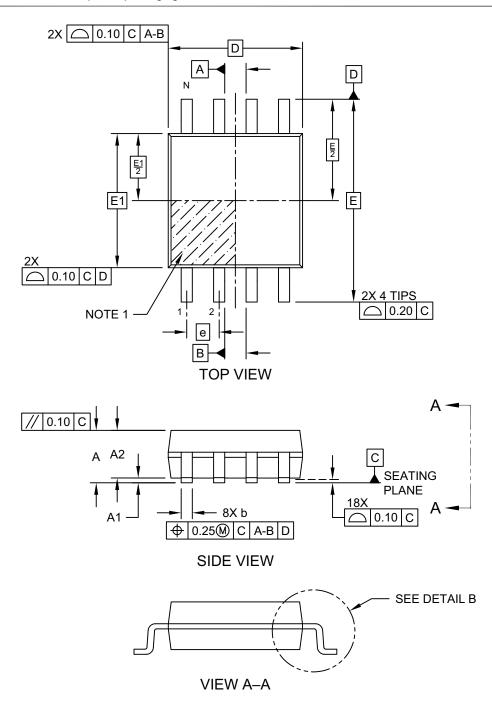

## 8-Lead Plastic Dual Flat, No Lead Package (MF) - 6x5 mm Body [DFN-S] Saw Singulated

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-122 Rev C Sheet 1 of 2

## 8-Lead Plastic Dual Flat, No Lead Package (MF) - 6x5 mm Body [DFN-S] Saw Singulated

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |                |          |      |  |  |

|-------------------------|-------------|----------------|----------|------|--|--|

| Dimension               | Limits      | MIN            | NOM      | MAX  |  |  |

| Number of Terminals     | N           |                | 8        |      |  |  |

| Pitch                   | е           |                | 1.27 BSC |      |  |  |

| Overall Height          | Α           | 0.80           | 0.85     | 1.00 |  |  |

| Standoff                | A1          | 0.00           | 0.02     | 0.05 |  |  |

| Terminal Thickness      | A3          | 0.20 REF       |          |      |  |  |

| Overall Length          | D           | 5.00 BSC       |          |      |  |  |

| Exposed Pad Length      | D2          | 3.90 4.00 4.10 |          |      |  |  |

| Overall Width           | Е           | 6.00 BSC       |          |      |  |  |

| Exposed Pad Width       | E2          | 2.20           | 2.30     | 2.40 |  |  |

| Terminal Width          | b           | 0.30           | 0.40     | 0.50 |  |  |

| Terminal Length         | L           | 0.50           | 0.60     | 0.75 |  |  |

| Terminal-to-Exposed-Pad | K           | 0.20           | -        | -    |  |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package may have one ore more exposed tie bars at ends.

- 3. Package is saw singulated

- 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-122 Rev C Sheet 2 of 2

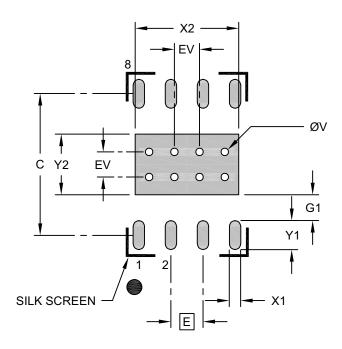

## 8-Lead Plastic Dual Flat, No Lead Package (MF) - 6x5 mm Body [DFN-S] Saw Singulated

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                                 | MILLIMETERS      |          |      |      |

|---------------------------------|------------------|----------|------|------|

| Dimension                       | Dimension Limits |          |      | MAX  |

| Contact Pitch                   | Е                | 1.27 BSC |      |      |

| Optional Center Pad Width       | X2               |          |      | 2.40 |

| Optional Center Pad Length      | Y2               |          |      | 4.10 |

| Contact Pad Spacing C           |                  |          | 5.60 |      |

| Contact Pad Width (X20)         | X1               |          |      | 0.45 |

| Contact Pad Length (X20)        | Y1               |          |      | 1.15 |

| Contact Pad to Center Pad (X20) | G1               | 0.20     |      |      |

| Thermal Via Diameter V          |                  |          | 0.30 |      |

| Thermal Via Pitch               | EV               |          | 1.00 |      |

## Notes:

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-2122 Rev C

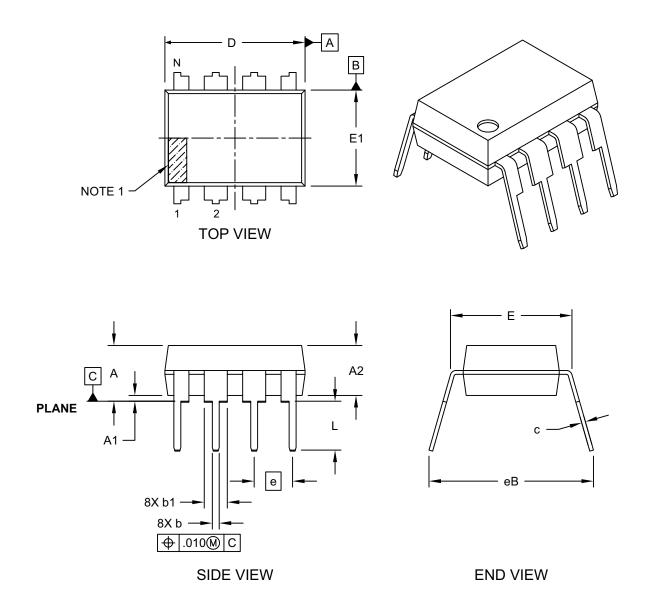

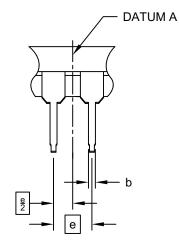

## 8-Lead Plastic Dual In-Line (P) - 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-018-P Rev F Sheet 1 of 2  $\,$

## 8-Lead Plastic Dual In-Line (P) - 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## ALTERNATE LEAD DESIGN (NOTE 5)

|                            | INCHES           |      |          |      |

|----------------------------|------------------|------|----------|------|

| Dimensior                  | Dimension Limits |      |          | MAX  |

| Number of Pins             | N                |      | 8        | -    |

| Pitch                      | е                |      | .100 BSC |      |

| Top to Seating Plane       | Α                | ı    | -        | .210 |

| Molded Package Thickness   | A2               | .115 | .130     | .195 |

| Base to Seating Plane      | A1               | .015 | -        | -    |

| Shoulder to Shoulder Width | .290             | .310 | .325     |      |

| Molded Package Width       | E1               | .240 | .250     | .280 |

| Overall Length             | D                | .348 | .365     | .400 |

| Tip to Seating Plane       | L                | .115 | .130     | .150 |

| Lead Thickness             | С                | .008 | .010     | .015 |

| Upper Lead Width b1        |                  | .040 | .060     | .070 |

| Lower Lead Width           | .014             | .018 | .022     |      |

| Overall Row Spacing §      | eВ               | -    | -        | .430 |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 5. Lead design above seating plane may vary, based on assembly vendor.

Microchip Technology Drawing No. C04-018-P Rev F Sheet 2 of 2

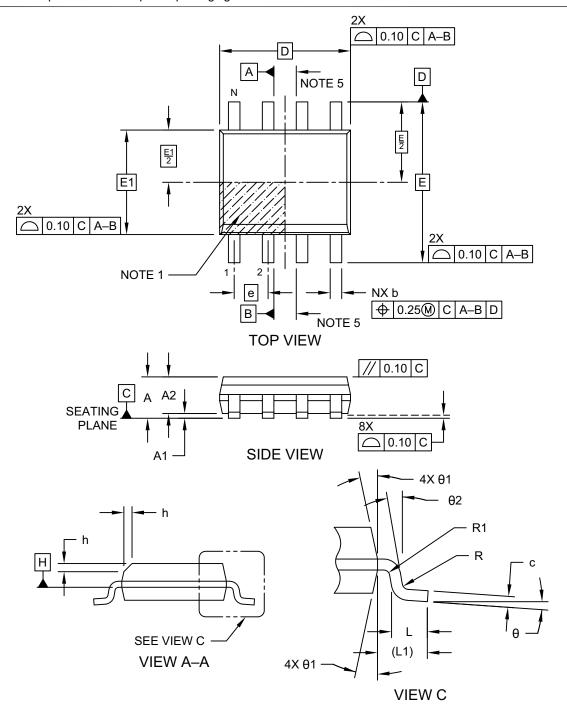

## 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm (.150 ln.) Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-057-SN Rev J Sheet 1 of 2

## 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm (.150 ln.) Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |          |      |  |

|--------------------------|-------------|----------|----------|------|--|

| Dimension                | MIN         | NOM      | MAX      |      |  |

| Number of Pins           | N           |          | 8        |      |  |

| Pitch                    | е           |          | 1.27 BSC |      |  |

| Overall Height           | Α           | -        | -        | 1.75 |  |

| Molded Package Thickness | A2          | 1.25     | -        | ı    |  |

| Standoff §               | A1          | 0.10     | -        | 0.25 |  |

| Overall Width            | Е           |          | 6.00 BSC |      |  |

| Molded Package Width     | E1          | 3.90 BSC |          |      |  |

| Overall Length           | D           | 4.90 BSC |          |      |  |

| Chamfer (Optional)       | h           | 0.25     | -        | 0.50 |  |

| Foot Length              | L           | 0.40     | -        | 1.27 |  |

| Footprint                | L1          | 1.04 REF |          |      |  |

| Lead Thickness           | С           | 0.17     | -        | 0.25 |  |

| Lead Width               | b           | 0.31     | -        | 0.51 |  |

| Lead Bend Radius         | R           | 0.07     | -        | _    |  |

| Lead Bend Radius         | R1          | 0.07     | -        | _    |  |

| Foot Angle               | θ           | 0°       | _        | 8°   |  |

| Mold Draft Angle θ1      |             | 5°       | _        | 15°  |  |

| Lead Angle               | θ2          | 0°       | _        | 8°   |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-057-SN Rev J Sheet 2 of 2

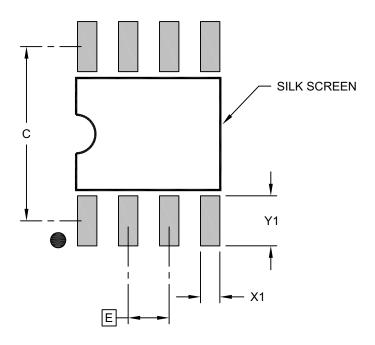

## 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm (.150 ln.) Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                         | Units |     |          | S    |

|-------------------------|-------|-----|----------|------|

| Dimension               | MIN   | NOM | MAX      |      |

| Contact Pitch           | Е     |     | 1.27 BSC |      |

| Contact Pad Spacing     | С     |     | 5.40     |      |

| Contact Pad Width (X8)  | X1    |     |          | 0.60 |

| Contact Pad Length (X8) |       |     | 1.55     |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2057-SN Rev J

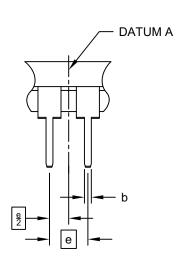

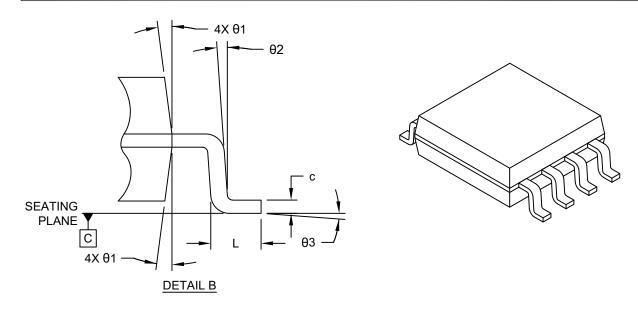

## 8-Lead Plastic Small Outline (SM) - Medium, 5.28 mm (.208 Inch) Body [SOIJ]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-056 Rev D Sheet 1 of 2

## 8-Lead Plastic Small Outline (SM) - Medium, 5.28 mm (.208 Inch) Body [SOIJ]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          |          | MILLIMETERS |  |  |  |

|--------------------------|------------------|----------|----------|-------------|--|--|--|

| Dimension                | Dimension Limits |          | NOM      | MAX         |  |  |  |

| Number of Terminals      | N                |          | 8        |             |  |  |  |

| Pitch                    | е                |          | 1.27 BSC |             |  |  |  |

| Overall Height           | Α                | 1.77     | _        | 2.03        |  |  |  |

| Standoff §               | A1               | 0.05     | _        | 0.25        |  |  |  |

| Molded Package Thickness | A2               | 1.75     | _        | 1.98        |  |  |  |

| Overall Length           | D                | 5.26 BSC |          |             |  |  |  |

| Overall Width            | E                | 7.94 BSC |          |             |  |  |  |

| Molded Package Width     | E1               |          | 5.25 BSC |             |  |  |  |

| Terminal Width           | b                | 0.36     | _        | 0.51        |  |  |  |

| Terminal Thickness       | С                | 0.15     | _        | 0.25        |  |  |  |

| Terminal Length          | L                | 0.51     | _        | 0.76        |  |  |  |

| Foot Angle               | θ1               | 0°       | _        | 8°          |  |  |  |

| Lead Angle               | θ2               | 0°       | _        | 8°          |  |  |  |

| Mold Draft Angle         | θ3               | _        | _        | 15°         |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. SOIJ JEITA/EIAJ Standard, Formerly called SOIC

- 3. § Significant Characteristic

- Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25mm per side.

- 5. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-056 Rev D Sheet 2 of 2

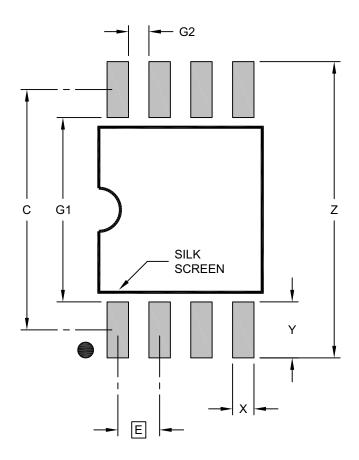

## 8-Lead Plastic Small Outline (SM) - Medium, 5.28 mm (.208 Inch) Body [SOIJ]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                                 | MILLIMETERS |          |      |      |

|---------------------------------|-------------|----------|------|------|

| Dimension                       | MIN         | NOM      | MAX  |      |

| Contact Pitch                   | Е           | 1.27 BSC |      |      |

| Overall Width                   | Z           |          |      | 9.00 |

| Contact Pad Spacing C           |             |          | 7.30 |      |

| Contact Pad Width (X8) X        |             |          |      | 0.65 |

| Contact Pad Length (X8) Y       |             |          |      | 1.70 |

| Contact Pad to Contact Pad (X4) | G1          | 5.60     |      |      |

| Contact Pad to Contact Pad (X6) | G2          | 0.62     |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M  $\,$

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2056 Rev D

## APPENDIX A: REVISION HISTORY

## **Revision E (07/2022)**

Fixed clock bit count and page size errors on Byte Write and Page Write sequences. Made minor grammar and punctuation fixes throughout the document. Updated SOIC and SOIJ package drawings.

## **Revision D (08/2021)**

Updated Pin Description section; Updated Package Drawings; Added Product Identification System for Automotive; Replaced terminology "Master" and "Slave" with "Host" and "Client", respectively; Reformatted some sections for better readability.

## Revision C (05/2010)

Revised Table 1-2, Param. No. 25 Conditions; Revised Section 2.2, added note; Updated SOIJ package drawings.

## **Revision B (05/2008)**

Modified parameter D006 in Table 1-1; Revised Package Marking Information; Replaced Package Drawings; Revised Product ID section.

## **Revision A (10/2007)**

Original release.

## THE MICROCHIP WEBSITE

Microchip provides online support via our WWW site at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://microchip.com/support

## PRODUCT IDENTIFICATION SYSTEM (NON-AUTOMOTIVE)

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.              |                     | <u>X</u> <sup>(1)</sup> | – <del>X</del> /XX                                                                                                                                                                                                                                                 |

|-----------------------|---------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                | Tape a              | and R                   | eel Temp Range Package                                                                                                                                                                                                                                             |

| Device:               | 25LC51              | 12                      | 512-Kbit, 2.5V, 128-Byte Page SPI Serial EEPROM                                                                                                                                                                                                                    |

| Tape & Reel:          | Blank<br>T          | =<br>=                  | Standard packaging (tube) Tape & Reel <sup>(1)</sup>                                                                                                                                                                                                               |

| Temperature<br>Range: | I<br>E              | =<br>=                  | -40°C to+85°C (Industrial)<br>-40°C to+125°C (Extended)                                                                                                                                                                                                            |

| Package:              | MF<br>P<br>SN<br>SM | = = =                   | Plastic Dual Flat, No Lead Package<br>5 x 6 x 0.85 mm Body, 8-lead (DFN-S)<br>Plastic Dual In-Line - 300 mil Body, 8-lead (PDIP)<br>Plastic Small Outline - Narrow,<br>3.90 mm Body, 8-lead (SOIC)<br>Plastic Small Outline - Wide,<br>5.28 mm Body, 8-lead (SOIJ) |

#### Examples:

- a) 25LC512-I/SM = 512-Kbit, 2.5V Serial EEPROM, Industrial temperature, Tape and Reel, SOIC package

- 25LC512-I/SM = 512-Kbit, 2.5V Serial EEPROM, Industrial temperature, SOIJ package

- c) 25LC512-I/P = 512-Kbit, 2.5V Serial EEPROM, Industrial temperature, PDIP package

- d) 25LC512T-E/MF = 512-Kbit, 2.5V Serial EEPROM, Extended temperature, Tape and Reel, DFN-S package

- Note 1: Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the Tape and

## PRODUCT IDENTIFICATION SYSTEM (AUTOMOTIVE)

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                   | ¥ <sup>(</sup>     | <b>1)</b> –  | <u>x</u>                                                                         | /XX             | <u>xxx</u> <sup>(2,3)</sup> |

|----------------------------|--------------------|--------------|----------------------------------------------------------------------------------|-----------------|-----------------------------|

| Device                     | Tape and           | Reel         | Temp Range                                                                       | Package         | Variant                     |

|                            |                    |              |                                                                                  |                 |                             |

| Device:                    | 25LC512            | 512-         | Kbit, 2.5V, 128-Byte                                                             | e Page SPI Ser  | ial EEPROM                  |

| Tape and Reel:             | Blank =<br>T =     |              | idard packaging (ti<br>e & Reel <sup>(1)</sup>                                   | ube)            |                             |

| Temperature<br>Range:      | I =<br>E =         |              | C to+85°C (AEC-C<br>C to+125°C (AEC-                                             |                 | )                           |

| Package:                   | SN =<br>SM =       | 3.90<br>Plas | tic Small Outline -<br>mm Body, 8-lead<br>tic Small Outline -<br>mm Body, 8-lead | (SOIC)<br>Wide, |                             |

| Variant <sup>(2,3)</sup> : | 16KVAO=<br>16KVXX= |              | idard Automotive,<br>tomer-Specific Aut                                          |                 | Process                     |

| 1                          |                    |              |                                                                                  |                 |                             |

#### Examples:

- a) 25LC512-I/SN16KVAO = 512-Kbit, 2.5V Serial EEPROM, Automotive Grade 3, SOIC package

- b) 25LC512T-I/SN16KVAO = 512-Kbit, 2.5V Serial EEPROM, Automotive Grade 3, Tape and Reel, SOIC package

- c) 25LC512-E/SN16KVAO = 512-Kbit, 2.5V Serial EEPROM, Automotive Grade 1, SOIC package

- d) 25LC512T-E/SN16KVAO = 512-Kbit, 2.5V Serial EEPROM, Automotive Grade 1, Tape and Reel, SOIC package

- e) 25LC512-E/SM16KVAO = 512-Kbit, 2.5V Serial EEPROM, Automotive Grade 1, SOIJ package

- f) 25LC512T-E/SM16KVAO = 512-Kbit, 2.5V Serial EEPROM, Automotive Grade 1, Tape and Reel, SOIJ package

- Note 1: Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the Tape and Reel option.

- 2: The VAO/VXX automotive variants have been designed, manufactured, tested and qualified in accordance with AEC-Q100 requirements for automotive applications.

- 3: For customers requesting a PPAP, a customer-specific part number will be generated and provided. A PPAP is not provided for VAO part numbers.

#### Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable" Code protection is constantly evolving. Microchip is committed to

continuously improving the code protection features of our products.

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <a href="https://www.microchip.com/en-us/support/design-help/client-support-services">https://www.microchip.com/en-us/support/design-help/client-support-services</a>.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AVR, AVR logo, AVR Freaks, Bes Time, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet- Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, IntelliMOS, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, KoD, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach. Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, Trusted Time, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2007-2022, Microchip Technology Incorporated and its subsidiaries.

All Rights Reserved.

ISBN: 978-1-6683-0701-4

## **Worldwide Sales and Service**

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support

Web Address:

www.microchip.com

Atlanta Duluth, GA

Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Tel: 281-894-5983

Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

**Raleigh, NC** Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110

Tel: 408-436-4270

Canada - Toronto

Tel: 905-695-1980

Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

**China - Chengdu** Tel: 86-28-8665-5511

China - Chongqing Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

**China - Guangzhou** Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

**China - Nanjing** Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

**China - Shanghai** Tel: 86-21-3326-8000

China - Shenyang Tel: 86-24-2334-2829

**China - Shenzhen** Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

China - Wuhan

Tel: 86-27-5980-5300 China - Xian

Tel: 86-29-8833-7252

**China - Xiamen** Tel: 86-592-2388138

**China - Zhuhai** Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

Japan - Tokyo

Tel: 81-3-6880- 3770

Korea - Daegu Tel: 82-53-744-4301

Korea - Seoul Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

Taiwan - Taipei

Tel: 886-2-2508-8600 Thailand - Bangkok

Tel: 66-2-694-1351 Vietnam - Ho Chi Minh

Tel: 84-28-5448-2100

#### **EUROPE**

**Austria - Wels** Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4485-5910 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

**France - Paris** Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79 **Germany - Garching**Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

**Germany - Heilbronn** Tel: 49-7131-72400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

**Israel - Ra'anana** Tel: 972-9-744-7705

**Italy - Milan** Tel: 39-0331-742611

Fax: 39-0331-466781 **Italy - Padova** Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820