#### www.maxim-ic.com

### **GENERAL DESCRIPTION**

The DS2786 estimates available capacity for rechargeable Li-lon and Li-lon Polymer batteries based on the cell voltage in the open-circuit state following a relaxation period. The open-circuit voltage (OCV) is used to determine relative cell capacity based on a lookup table stored in the IC. This capability makes accurate capacity information available immediately after a battery pack is inserted. During periods of moderate to high rate discharging, which preclude OCV measurements, the DS2786 uses coulomb counting as a secondary means of estimating relative capacity.

Remaining capacity is reported in percent, along with cell voltage, current and temperature information. Cell characteristics and application parameters used in the calculations are stored in on-chip EEPROM.

The DS2786 is intended for use on the host side of portable devices, though it can also be mounted within a battery pack. Measurement and estimated capacity data are accessed through an I<sup>2</sup>C interface. Temperature data is available from an on-die sensor. Resistance measurements of a pack identification resistor and pack thermistor are supported by ratiometric measurements on two auxiliary inputs.

### **APPLICATIONS**

3G Multimedia Wireless Handsets Digital Still Cameras Digital Audio (MP3) Players

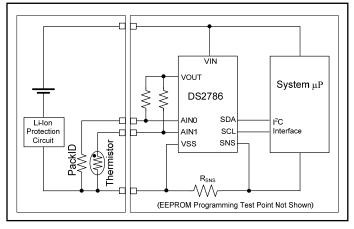

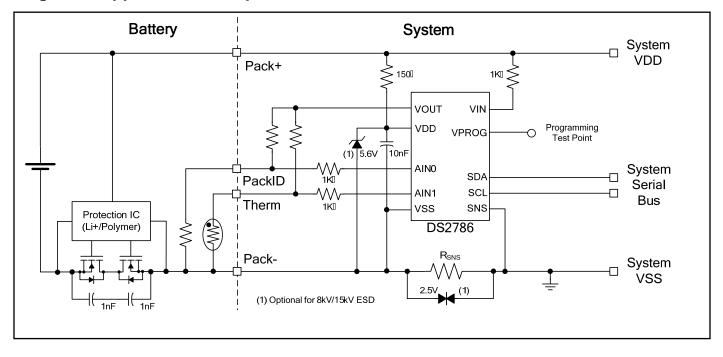

## **TYPICAL OPERATING CIRCUIT**

Commands, Registers, and Modes are capitalized for clarity.

# DS2786 Stand-Alone OCV-Based Fuel Gauge

#### **FEATURES**

- Relative Capacity Calculated from Combination Coulomb Counter and Open-Circuit Cell Voltage (OCV) Battery Model

- Accurate Warning of Low Battery Conditions Even On First Cycle (No Learn Cycle Needed)

- 12-Bit Battery Voltage Measurement: ±10mV Accuracy 1.22mV LSB, 0V to 4.5V Input Range

- 11-Bit Bidirectional Current Measurement:

- $25\mu$ V LSB, ±51.2mV Dynamic Range 1.67mA LSB, ±3.4A (R<sub>SNS</sub> = 15m $\Omega$ )

- Current Accumulation Measurement Resolution: ±204.8mVh Range ±13.65Ah (R<sub>SNS</sub> = 15mΩ)

- Internal Temperature Measurement: 0.125°C LSB, ±3°C Accuracy

- Two 11-Bit Aux Input Voltage Measurements: ±8 LSB Accuracy, Ratiometric Inputs Eliminate Supply Accuracy Issues

- V<sub>OUT</sub> Pin Drives Resistive Dividers, Reduces Current Consumption

- 2-Wire Interface

- Low Power Consumption: Active Current: 50μA typ, 80μA max Sleep Current: 1μA typ, 3μA max

### **ORDERING INFORMATION**

| PART        | TEMP RANGE     | PIN-PACKAGE |

|-------------|----------------|-------------|

| DS2786G+    | -20°C to +70°C | 10 TDFN-EP* |

| DS2786G+T&R | -20°C to +70°C | 10 TDFN-EP* |

+Denotes a lead(Pb)-free/RoHS-compliant package. T&R = Tape and reel.

\*EP = Exposed pad.

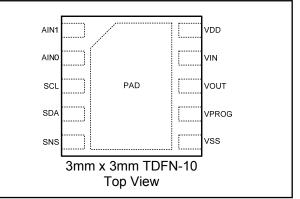

## **PIN CONFIGURATION**

## ABSOLUTE MAXIMUM RATINGS

Voltage Range on All Pins Except V\_{PROG} Relative to V\_{SS} Voltage Range on V\_{PROG} Relative to V\_{SS}

Operating Temperature Range

Storage Temperature Range

Soldering Temperature

-0.3V to +6V -0.3V to +18V -40°C to +85°C -55°C to +125°C Refer to the IPC/JEDECJ-STD-020 Specification.

This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

## **RECOMMENDED DC OPERATING CONDITIONS**

| $(2.5V \le V_{DD} \le 4.5V, I_A = -2)$ | $0^{\circ}$ C to +70°C.)        |            |      |                       |       |

|----------------------------------------|---------------------------------|------------|------|-----------------------|-------|

| PARAMETER                              | SYMBOL                          | CONDITIONS | MIN  | TYP MAX               | UNITS |

| Supply Voltage                         | V <sub>DD</sub>                 | (Note 1)   | +2.5 | +4.5                  | V     |

| Data I/O Pins                          | SCL, SDA                        | (Note 1)   | -0.3 | +4.5                  | V     |

| Programming Pin                        | V <sub>PROG</sub>               | (Note 1)   | -0.3 | +15.5                 | V     |

| VIN, AIN0, AIN1 Pin                    | V <sub>IN</sub> , AIN0,<br>AIN1 | (Note 1)   | -0.3 | V <sub>DD</sub> + 0.3 | V     |

$(2.5V \le V_{DD} \le 4.5V, T_A = -20^{\circ}C \text{ to } +70^{\circ}C.)$

## DC ELECTRICAL CHARACTERISTICS

$(2.5V \le V_{DD} \le 4.5V, T_A = -20^{\circ}C$  to  $+70^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                   | SYMBOL              | CONDITIONS                                                               | MIN  | ТҮР                   | МАХ  | UNITS           |

|---------------------------------------------|---------------------|--------------------------------------------------------------------------|------|-----------------------|------|-----------------|

| Active Current                              | I <sub>ACTIVE</sub> |                                                                          |      | 50                    | 75   | μΑ              |

|                                             |                     | $V_{DD}$ = 2.0V,<br>SCL, SDA = $V_{SS}$                                  |      | 0.3                   | 1.0  |                 |

| Sleep-Mode Current                          | I <sub>SLEEP</sub>  | SCL, SDA = V <sub>SS</sub>                                               |      | 1                     | 3    | μΑ              |

| Current Measurement<br>Resolution           | I <sub>LSB</sub>    | DS2786                                                                   |      | 25                    |      | μV              |

| Current Measurement<br>Full-Scale Magnitude | I <sub>FS</sub>     | (Note 1)                                                                 |      | ±51.2                 |      | mV              |

| Current Measurement<br>Offset Error         | I <sub>OERR</sub>   | DS2786 (Note 2)                                                          | -50  |                       | +50  | μV              |

| Current Measurement<br>Gain Error           | I <sub>GERR</sub>   |                                                                          | -1.5 |                       | +1.5 | % of<br>reading |

|                                             |                     | V <sub>DD</sub> = 3.6V at +25°C                                          | -1   |                       | +1   |                 |

| Timebase Accuracy                           | t <sub>ERR</sub>    | $T_A = 0^{\circ}C$ to +70°C                                              | -2   |                       | +2   | %               |

|                                             |                     | T <sub>A</sub> = -20°C to +70°C                                          | -3   |                       | +3   | -               |

| Voltage Error                               | V <sub>GERR</sub>   | $V_{DD} = V_{IN} = 3.6V,$<br>$T_A = 0^{\circ}C \text{ to } +50^{\circ}C$ | -10  |                       | +10  | mV              |

|                                             | ¥ GERR              | T <sub>A</sub> = -20°C to +70°C                                          | -20  |                       | +20  | IIIV            |

| Input Resistance<br>VIN, AIN0, AIN1         | R <sub>IN</sub>     |                                                                          | 15   |                       |      | MΩ              |

| AIN0, AIN1 Error                            |                     |                                                                          | -8   |                       | +8   | LSB             |

| V <sub>OUT</sub> Output Drive               |                     | I <sub>O</sub> = 1mA                                                     |      | V <sub>DD</sub> - 0.5 |      | V               |

| PARAMETER                       | SYMBOL             | CONDITIONS                           | MIN  | TYP  | MAX  | UNITS  |

|---------------------------------|--------------------|--------------------------------------|------|------|------|--------|

| V <sub>OUT</sub> Precharge Time | t <sub>PRE</sub>   |                                      | 13.2 | 13.7 | 14.2 | ms     |

| Temperature Error               | T <sub>ERR</sub>   |                                      | -3   |      | +3   | °C     |

| Input Logic High:<br>SCL, SDA   | V <sub>IH</sub>    | (Note 1)                             | 1.4  |      |      | V      |

| Input Logic Low:<br>SCL, SDA    | V <sub>IL</sub>    | (Note 1)                             |      |      | 0.6  | V      |

| Output Logic Low:<br>SDA        | V <sub>OL</sub>    | I <sub>OL</sub> = 4mA (Note 1)       |      |      | 0.4  | V      |

| Pulldown Current:<br>SCL, SDA   | I <sub>PD</sub>    | $V_{DD} = 4.2V,$<br>$V_{PIN} = 0.4V$ |      | 0.2  | 1.0  | μA     |

| V <sub>PROG</sub> Pulldown      | R <sub>VPROG</sub> |                                      |      | 20   |      | kΩ     |

| Input Capacitance:<br>SCL, SDA  | C <sub>BUS</sub>   |                                      |      |      | 50   | pF     |

| Bus Low Timeout                 | t <sub>SLEEP</sub> | (Note 3)                             | 1.5  |      | 2.2  | S      |

| EEPROM Programming<br>Voltage   | V <sub>PROG</sub>  |                                      | 14   |      | 15   | V      |

| EEPROM Programming<br>Current   | I <sub>PROG</sub>  |                                      |      |      | 2    | mA     |

| EEPROM Programming<br>Time      | t <sub>PROG</sub>  |                                      | 3.1  |      | 14   | ms     |

| EEPROM Copy<br>Endurance        |                    |                                      | 100  |      |      | writes |

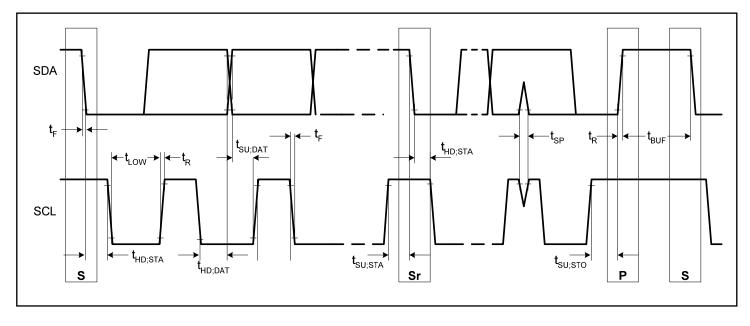

## **ELECTRICAL CHARACTERISTICS: 2-WIRE INTERFACE**

$(2.5V \le V_{DD} \le 4.5V, T_A = -20^{\circ}C \text{ to } +70^{\circ}C.)$

| PARAMETER                                              | SYMBOL              | CONDITIONS   | MIN                    | TYP MAX | UNITS |

|--------------------------------------------------------|---------------------|--------------|------------------------|---------|-------|

| SCL Clock Frequency                                    | f <sub>SCL</sub>    | (Note 4)     | 0                      | 400     | kHz   |

| Bus Free Time Between<br>a STOP and START<br>Condition | t <sub>BUF</sub>    |              | 1.3                    |         | μs    |

| Hold Time (Repeated)<br>START Condition                | t <sub>HD:STA</sub> | (Note 5)     | 0.6                    |         | μs    |

| Low Period of SCL Clock                                | $t_{LOW}$           |              | 1.3                    |         | μs    |

| High Period of SCL Clock                               | t <sub>HIGH</sub>   |              | 0.6                    |         | μs    |

| Setup Time for a<br>Repeated<br>START Condition        | t <sub>su:sta</sub> |              | 0.6                    |         | μs    |

| Data Hold Time                                         | t <sub>HD:DAT</sub> | (Notes 6, 7) | 0                      | 0.9     | μs    |

| Data Setup Time                                        | t <sub>su:dat</sub> | (Note 6)     | 100                    |         | ns    |

| Rise Time of Both SDA and SCL Signals                  | t <sub>R</sub>      |              | 20 + 0.1C <sub>B</sub> | 300     | ns    |

| Fall Time of Both SDA<br>and SCL Signals               | t <sub>F</sub>      |              | 20 + 0.1C <sub>B</sub> | 300     | ns    |

| Setup Time for STOP<br>Condition                       | t <sub>su:sto</sub> |              | 0.6                    |         | μs    |

| PARAMETER                     | SYMBOL           | CONDITIONS | MIN | ТҮР | MAX | UNITS |

|-------------------------------|------------------|------------|-----|-----|-----|-------|

| Spike Pulse Widths            |                  |            |     |     |     |       |

| Suppressed by Input<br>Filter | t <sub>SP</sub>  | (Note 8)   | 0   |     | 50  | ns    |

| Capacitive Load for Each      | C                | (Nata O)   |     |     | 400 |       |

| Bus Line                      | C <sub>B</sub>   | (Note 9)   |     |     | 400 | pF    |

| SCL, SDA Input<br>Capacitance | C <sub>BIN</sub> |            |     |     | 60  | pF    |

- Note 1: All voltages are referenced to V<sub>SS</sub>.

- **Note 2:** Offset specified after auto-calibration cycle and Current Offset Bias Register = 00h.

- **Note 3:** The DS2786 enters the Sleep mode 1.5s to 2.2s after (SCL  $< V_{IL}$ ) AND (SDA  $< V_{IL}$ ).

- Note 4: Timing must be fast enough to prevent the DS2786 from entering Sleep mode due to bus low for period  $> t_{SLEEP}$ .

- **Note 5:** f<sub>SCL</sub> must meet the minimum clock low time plus the rise/fall times.

- Note 6: The maximum  $t_{HD:DAT}$  has only to be met if the device does not stretch the LOW period ( $t_{LOW}$ ) of the SCL signal.

- **Note 7:** This device internally provides a hold time of at least 100ns for the SDA signal (referred to the V<sub>IHmin</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- Note 8: Filters on SDA and SCL suppress noise spikes at the input buffers and delay the sampling instant.

- Note 9:  $C_B$ —total capacitance of one bus line in pF.

## Figure 1. 2-Wire Bus Timing Diagram

| PIN | NAME              | FUNCTION                                                                                                                                                                                  |

|-----|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | AIN1              | Aux Voltage Input Number 1                                                                                                                                                                |

| 2   | AIN0              | Aux Voltage Input Number 0                                                                                                                                                                |

| 3   | SCL               | <b>Serial Clock Input.</b> Input only 2-wire clock line. Connect this pin to the clock signal of the 2-wire interface. This pin has a $0.2\mu$ A typical pulldown to sense disconnection. |

| 4   | SDA               | Serial Data Input/Output. Open drain 2-wire data line. Connect this pin to the clock signal of the 2-wire interface. This pin has a 0.2µA typical pulldown to sense disconnection.        |

| 5   | SNS               | Current-Sense Input. Connect to the handset side of the sense resistor.                                                                                                                   |

| 6   | V <sub>SS</sub>   | Device Ground. Connect to the battery side of the sense resistor.                                                                                                                         |

| 7   | V <sub>PROG</sub> | <b>EEPROM Programming Voltage Input.</b> Connect to external supply for production programming. Connect to V <sub>ss</sub> during normal operation.                                       |

| 8   | V <sub>OUT</sub>  | <b>Voltage Out.</b> Supply for Aux Input Voltage Measurement Dividers. Connect to high side of resistor divider circuits.                                                                 |

| 9   | V <sub>IN</sub>   | Battery Voltage Input. The voltage of the cell pack is measured through this pin.                                                                                                         |

| 10  | V <sub>DD</sub>   | <b>Power-Supply Input.</b> 2.5V to 4.5V input range. Connect to system power through a decoupling network.                                                                                |

| PAD | PAD               | Exposed Pad. Connect to V <sub>SS</sub> .                                                                                                                                                 |

## PIN DESCRIPTION

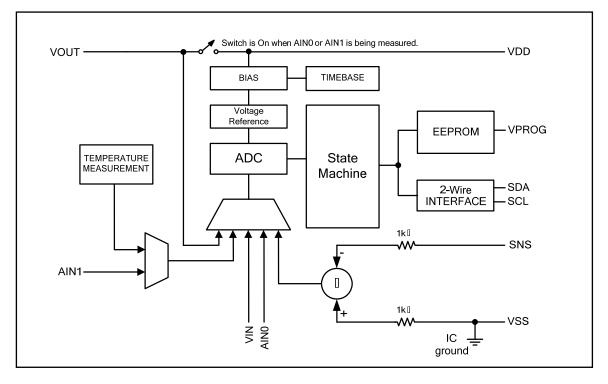

## Figure 2. Block Diagram

## DESCRIPTION

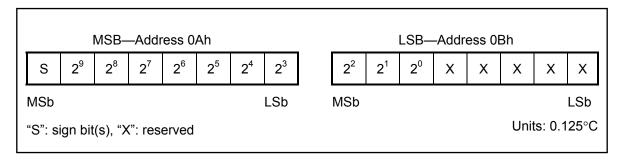

The DS2786 provides current-flow, voltage, and temperature measurement data to support battery-capacity monitoring in cost-sensitive applications. Current is measured bidirectionally over a dynamic range of  $\pm$ 51.2mV with a resolution of 25µV. Assuming a 15m $\Omega$  sense resistor, the current sense range is  $\pm$ 3.4A, with a 1 LSB resolution of 1.667mA. Current measurements are performed at regular intervals and accumulated with each measurement to support "coulomb counting" during periods of host power consumption. Each current measurement is reported with sign and magnitude in the two-byte Current Register. Battery voltage measurements are reported in the two-byte Voltage Register with 12-bit (1.22mV) resolution, and auxiliary voltage measurements are reported in the two-byte Aux Volt Registers with 11-bit resolution. Additionally, the Temperature Register reports temperature with 0.125°C resolution and  $\pm$ 3°C accuracy from the on-chip sensor. The on-chip temperature measurement is optional and replaces the auxiliary voltage channel AIN1.

The DS2786 provides accurate relative capacity measurements during periods of host system inactivity by looking at cell open circuit voltage. Cell capacity is calculated using an OCV voltage profile and a 1-byte scale factor to weight accumulated current during the coulomb-counting periods. The OCV voltage profile and scale factor are stored in EEPROM memory. The EEPROM memory is constructed with a SRAM shadow so that the OCV voltage profile and scale factor can be overwritten by the host to accommodate a variety of cell types and capacities from multiple cell vendors. The I<sup>2</sup>C interface also allows read/write access to the Status, Configuration, and Measurement Registers.

## **Figure 3. Application Example**

## POWER MODES

The DS2786 operates in one of two power modes: Active and Sleep. While in Active mode, the DS2786 operates as a high-precision battery monitor with temperature, voltage, auxiliary inputs, current, and accumulated current measurements acquired continuously and the resulting values updated in the Measurement Registers. In Sleep mode, the DS2786 operates in a low-power mode with no measurement activity. Read and write access is allowed to all registers in either mode.

The DS2786 operating mode transitions from Sleep to Active when:

$$(SCL > V_{IH}) OR (SDA > V_{IH})$$

The DS2786 operating mode transitions from Active to Sleep when:

SMOD = 1 AND [ ( SCL <  $V_{IL}$  ) AND ( SDA <  $V_{IL}$  ) ] for  $t_{SLEEP}$

**CAUTION:** If SMOD = 1, a pullup resistor is required on SCL and SDA in order to ensure that the DS2786 transitions from Sleep to Active mode when the battery is charged. If the bus is not pulled up, the DS2786 remains in Sleep and cannot accumulate the charge current. This caution statement applies particularly to a battery that is charged on a stand-alone charger.

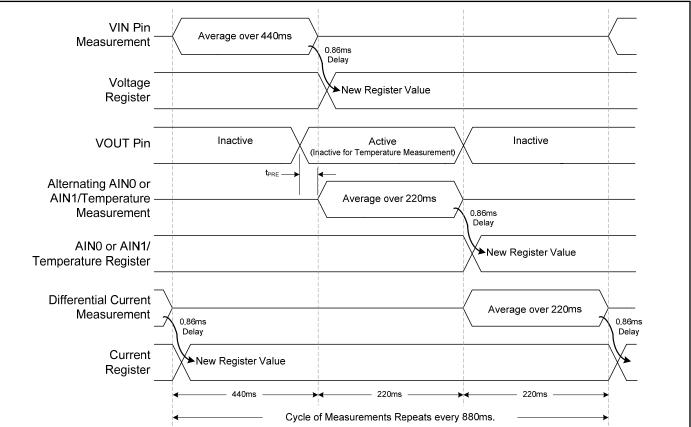

## PARAMETER MEASUREMENT

The DS2786 uses a Sigma Delta A/D converter to make measurements. The measurement sequence shown in Figure 4 repeats continuously while the DS2786 is in Active mode. The  $V_{OUT}$  pin is activated  $t_{PRE}$  before the AIN0 and AIN1 conversion to allow for the  $V_{OUT}$  output voltage to settle. The DS2786 can be configured to measure temperature using its on-chip sensor instead of the AIN1 input. When the internal temperature measurement uses the AIN1 conversion timeslot,  $V_{OUT}$  is not activated. A full sequence of voltage measurements nominally takes 1760ms to complete.

## Figure 4. Measurement Sequence

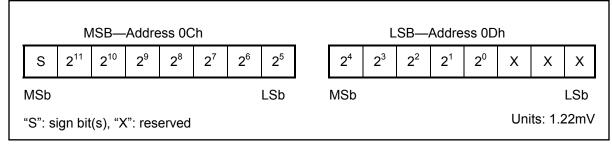

## VOLTAGE MEASUREMENT

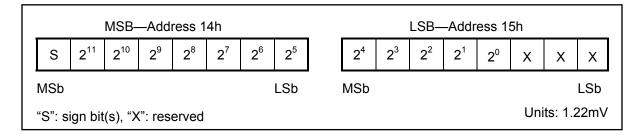

Battery voltage is measured at the  $V_{IN}$  input with respect to  $V_{SS}$  over a range of 0V to 4.5V and with a resolution of 1.22mV. The result is updated every 880ms and placed in the Voltage Register in two's complement form. Voltages above the maximum register value are reported as 7FFFh.

### Figure 5. Voltage Register Format

The input impedance of V<sub>IN</sub> is sufficiently large (>15M $\Omega$ ) to be connected to a high-impedance voltage divider in order to support multiple-cell applications. The pack voltage should be divided by the number of series cells to present a single-cell average voltage to the V<sub>IN</sub> input.

Every 1024th conversion, the ADC measures its input offset to facilitate offset correction to improve voltage accuracy. Offset correction occurs approximately every 15 minutes. The resulting correction factor is applied to the subsequent 1023 measurements. During the offset correction conversion, the ADC does not measure the  $V_{IN}$  signal. The voltage measurement just prior to the offset conversion is displayed in the voltage register. The OCV algorithm automatically adjusts for the effects of the offset correction cycle.

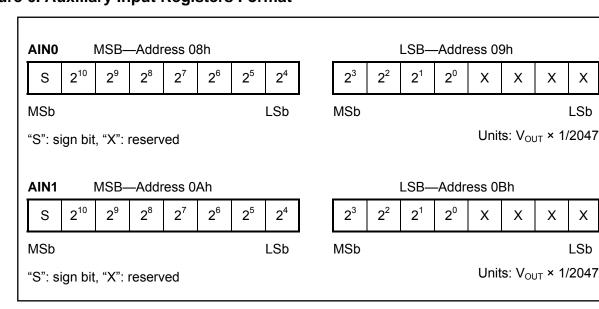

## **AUXILARY INPUT MEASUREMENTS**

The DS2786 has two auxiliary voltage measurement inputs, AIN0 and AIN1. Both are measured with respect to  $V_{SS}$ . These inputs are designed for measuring resistor ratios, particularly useful for measuring thermistor or pack identification resistors. Prior to the beginning of a measurement cycle on AIN0 or AIN1, the  $V_{OUT}$  pin outputs a reference voltage in order to drive a resistive divider formed by a known resistor value, and the unknown resistance to be measured. This technique delivers good accuracy at a reasonable cost, as it removes reference tolerance from the error calculations. Measurements alternate between each input. Each auxiliary measurement is therefore updated every 1760ms and placed in the corresponding AIN0 or AIN1 Register in two's complement form.

## Figure 6. Auxiliary Input Registers Format

## **TEMPERATURE MEASUREMENT**

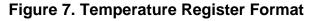

The DS2786 uses an integrated temperature sensor to measure battery temperature with a resolution of 0.125°C. Temperature measurements are updated every 1760ms and placed in the Temperature Register in two's complement form. The format of the Temperature Register is shown in Figure 7. The ITEMP bit in the Status/Configuration Register must be set to enable the internal temperature measurement instead of the AIN1 measurement.

## **CURRENT MEASUREMENT**

In the Active mode of operation, the DS2786 continually measures the current flow into and out of the battery by measuring the voltage drop across a low-value current-sense resistor,  $R_{SNS}$ , connected between the SNS and  $V_{SS}$  pins. The voltage sense range between SNS and  $V_{SS}$  is ±51.2mV. Note that positive current values occur when  $V_{SNS}$  is less than  $V_{SS}$ , and negative current values occur when  $V_{SNS}$  is greater than  $V_{SS}$ . Peak signal amplitudes up to 102mV are allowed at the input as long as the continuous or average signal level does not exceed ±51.2mV over the conversion cycle period. The ADC samples the input differentially and updates the Current Register every 880ms at the completion of each conversion cycle. Figure 8 describes the Current Measurement Register format and resolution for each option. Charge currents above the maximum register value are reported at the minimum value (7FFFh = +51.2mV). Discharge currents below the minimum register value are reported at the minimum value (8000h = -51.2mV).

Every 1024th conversion, the ADC measures its input offset to facilitate offset correction to improve Current accuracy. Offset correction occurs approximately every 15 minutes. The resulting correction factor is applied to the subsequent 1023 measurements. During the offset correction conversion, the ADC does not make a measurement. The current measurement just prior to the offset conversion is displayed in the Current Register.

## Figure 8. Current Register Formats

$5 m\Omega$

±10.24A

| CURRENT RESOLU                     | TION (1 LSB) |                  |       |             |  |  |

|------------------------------------|--------------|------------------|-------|-------------|--|--|

| $ V_{SS} - V_{SNS} $               |              | R <sub>SNS</sub> |       |             |  |  |

|                                    | 20mΩ         | $15 m\Omega$     | 10mΩ  | $5 m\Omega$ |  |  |

| 25μV                               | 1.25mA       | 1.667mA          | 2.5mA | 5mA         |  |  |

|                                    |              |                  |       |             |  |  |

| CURRENT INPUT RANGE                |              |                  |       |             |  |  |

| V <sub>SS</sub> - V <sub>SNS</sub> |              | R <sub>SNS</sub> |       |             |  |  |

| VSS-VSNS                           | <b>22</b>    |                  |       |             |  |  |

$20 \text{m}\Omega$

±2.56A

### Table 1. Current Range and Resolution for Various R<sub>SNS</sub> Values

## **CURRENT OFFSET BIAS**

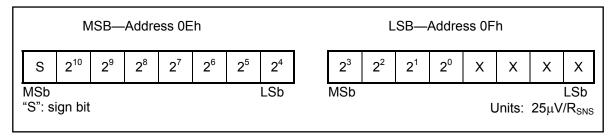

The Current Offset Bias Register (COBR) allows a programmable offset value to be added to raw current measurements. The result of the raw current measurement plus the COBR value is displayed as the current measurement result in the Current Register, and is used for current accumulation and detection of an OCV condition. The COBR value can be used to correct for a static offset error, or can be used to intentionally skew the current results and therefore the current accumulation.

$15m\Omega$

±3.41A

$10 \text{m}\Omega$

±5.12A

Read and write access is allowed to COBR. Whenever the COBR is written, the new value is applied to all subsequent current measurements. COBR can be programmed in  $25\mu$ V steps to any value between +3.175mV and -3.2mV. The COBR value is stored as a two's complement value in nonvolatile (NV) memory. The COBR factory default value is 00h.

## Figure 9. Current Offset Bias Register Format

±51.2mV

## **CURRENT ACCUMULATION**

An Internal Accumulated Current Register (IACR) serves as an up/down counter holding a running count of charge since the last OCV condition. Current measurement results, plus a programmable bias value are internally summed, or accumulated, at the completion of each current measurement conversion period. The IACR has a range of  $\pm 204.8$  mVh. The IACR uses the Initial or Learned Cell Capacity Registers to increment or decrement the Relative Capacity Register as current flows into or out of the battery. In this way, the fuel gauge is accurate even when an OCV condition does not occur for an extended time period.

### Table 2. Accumulated Current Range for Various R<sub>SNS</sub> Values

| IACR RANGE                         |                  |              |                     |             |  |  |  |

|------------------------------------|------------------|--------------|---------------------|-------------|--|--|--|

| V <sub>SS</sub> - V <sub>SNS</sub> | R <sub>SNS</sub> |              |                     |             |  |  |  |

|                                    | 20mΩ             | $15 m\Omega$ | $10 \text{m}\Omega$ | $5 m\Omega$ |  |  |  |

| ±204.8mVh                          | ±10.24Ah         | ±13.65Ah     | ±20.48Ah            | ±40.96Ah    |  |  |  |

## **CELL CAPACITY ESTIMATION**

The DS2786 uses a hybrid OCV measurement and coulomb counting algorithm to estimate remaining cell capacity. During periods of charging or discharging of the cell, the DS2786 counts charge flow into and out of the cell. When the application becomes inactive, the DS2786 waits for the cell voltage to relax and then adjusts the coulomb count based on an open-circuit voltage cell model stored in device EEPROM. The resulting calculation is reported to the system as a percentage value between 0% and 100%. As the cell ages, a Learn feature adjusts for changes in capacity.

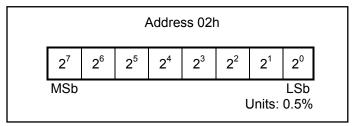

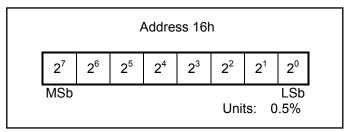

The Relative Capacity Register reports remaining cell charge as a percentage of full. Relative Capacity is reported with a resolution of 0.5% and is limited to a value between 0% and 100%. The Relative Capacity Register is updated each time the IC performs a current measurement or open-circuit cell voltage measurement.

### Figure 10. Relative Capacity Register Format

Prior to the first Learn operation, the Relative Capacity value is calculated by adding the IACR multiplied by the Initial Capacity Scaling Factor (7Ah) to the Last OCV Relative Capacity (16h). After the first Learn operation, the Relative Capacity value is calculated by adding the IACR multiplied by the Learned Capacity Scaling Factor (17h) to the Last OCV Relative Capacity (16h).

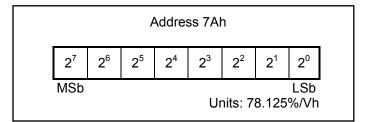

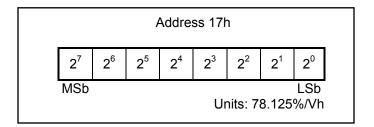

Each Capacity Scaling Factor Register has a resolution of 78.125%/Vh and a maximum range of 0 to 19921.875%/Vh. During assembly, the Initial Capacity Register should be programmed to the capacity of the cell. For example, an application using a 1Ah cell and  $0.015\Omega$  sense resistor would set the Initial Capacity Register to a value of  $(100\% \div (1Ah \times 0.015\Omega)) \div 78.125\%/Vh = 55h$ . The Learned Capacity Scaling Factor Register is controlled by the DS2786. The power up value is 00h, and the register is updated with the calculated new cell capacity value after every Learn operation.

## Figure 11. Initial Capacity Scaling Factor Register Format

## Figure 12. Learned Capacity Scaling Factor Register Format

## OCV DETECTION AND CURRENT BLANKING

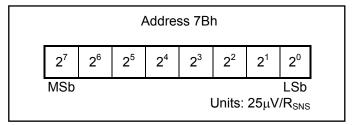

The Blanking/OCV Threshold Register sets the current measurement level at which the DS2786 switches between coulomb counting and open-circuit voltage measurement. When the magnitude of the measured current (after COBR is applied) is less than the value defined by the Blanking/OCV Threshold Register, the measurement is not summed into the IACR. Instead, the IACR is maintained at its present value and the DS2786 begins dV/dt measurement evaluation to detect an OCV voltage condition. A threshold value that is below the minimum operational current, but above the maximum idle current of the application should be selected. The Blanking/OCV Threshold Register has a resolution of  $25\mu$ V/R<sub>SNS</sub>, and a range from 0mV/R<sub>SNS</sub> to 6.375mV/R<sub>SNS</sub>. The factory default value is 06h

### Figure 13. Blanking/OCV Threshold Register Format

While the measured current is below the Blanking/OCV Threshold level, the DS2786 actively searches for a relaxed cell by calculating the change in cell voltage as reported in the Voltage Register over 15 minute intervals (dV/dt). If the 15 minute dV/dt change of the Voltage Register is less than the value stored in the OCV dV/dt Threshold Register, the DS2786 determines that the cell is now in a relaxed state and the Relative Capacity Register is adjusted based on the OCV cell model stored in parameter EEPROM. This operation will occur repeatedly every 15 minutes until the DS2786 returns to coulomb-counting mode of operation.

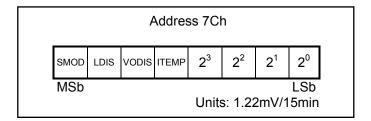

The OCV dV/dt Threshold Register has a resolution of 1.22mV/15min and a range from 0mV/15min to 18.3mV/15min. The factory default value is 3.66mV/15min. Note that the upper 4 bits of the OCV dV/dt Threshold Register are used to EEPROM back bits from the Status/Configuration Register.

## Figure 14. OCV dV/dt Threshold Register Format

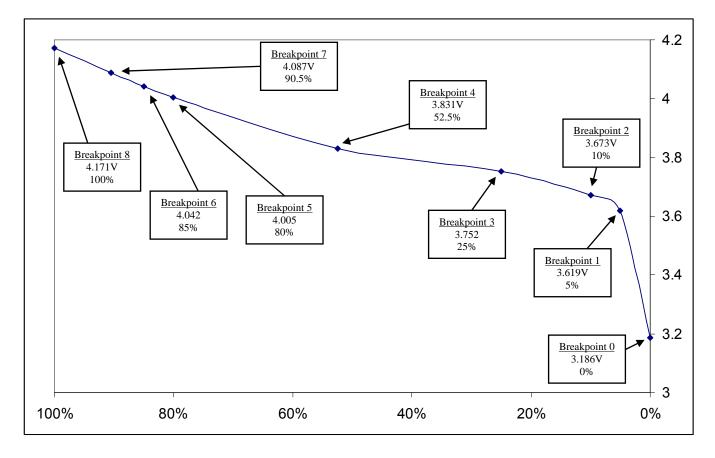

## OCV CELL MODEL

The OCV cell model is a 9-point piece-wise linear approximation of open circuit cell voltage versus the remaining capacity of the cell. Whenever an OCV update occurs, the Relative Capacity Register is adjusted to a new value based on the OCV voltage reading and a linear approximation of the table values. Figure 15 shows the factory-default cell model stored in EEPROM.

Figure 15. Default OCV Cell Model

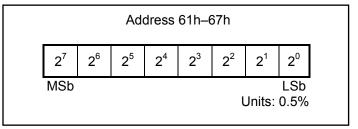

The OCV cell model can be modified by changing the Capacity and Voltage Breakpoint Registers in EEPROM. Capacity 0 is fixed at 0% and cannot be changed. Capacity 1 through Capacity 7 are stored with 0.5% resolution at addresses 61h through 67h respectively. Capacity values must be monotonic (Capacity 1 > Capacity 0, Capacity 2 > Capacity 1, etc.), but otherwise can be written to any value between 0.5% to 99.5%. Capacity 8 is fixed at a value of 100% and cannot be changed.

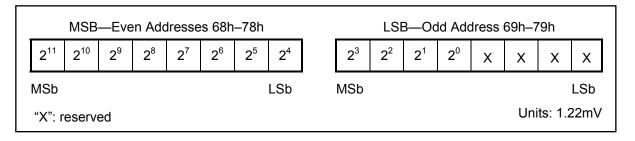

Voltage breakpoints require two bytes per breakpoint, but are otherwise stored in a similar manner. Voltage Breakpoint 0: MSB stored at address 68h, LSB stored at address 69h. Other voltage breakpoints stored sequentially through address location 79h. Each voltage breakpoint has a resolution of 1.22mV, and a range from 0.0V to 4.996V (IC operation limited to 4.5V). Voltage breakpoint values must also be monotonic.

### Figure 16. Capacity 1 to Capacity 7 Registers Format

## Figure 17. Voltage Breakpoint Register Format

## **INITIAL CAPACITY ESTIMATION**

The DS2786 calculates Relative Capacity immediately upon power up. During initialization, the DS2786 makes a voltage measurement and uses the OCV cell model data to determine a starting point for the Relative Capacity Register. This estimation occurs regardless of the load on the cell. Any error induced from cell loading will be removed at the next OCV adjustment. The initial voltage measurement used in determining the starting point is stored in the Initial Voltage Register until the IC is power cycled.

## Figure 18. Initial Voltage Register Format

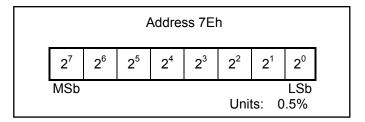

## NEW CAPACITY LEARNING

As the cell ages, the Initial Capacity Scaling Factor Register value may no longer accurately reflect the true capacity of the cell causing error in Relative Capacity calculation while in coulomb-counting mode of operation. The DS2786 has a learn feature that allows the IC to remain accurate as the cell changes. The DS2786 compares the percent Relative Capacity difference between the last two OCV updates to the change in the coulomb count to learn the new cell capacity. The Last OCV Register maintains the Relative Capacity percentage at the previous OCV adjustment point used for learning the new cell capacity. Last OCV will be updated with a new value at each OCV adjustment.

Example: Assuming a  $15m\Omega$  sense resistor, the DS2786 adjusts the Relative Capacity of a 1000mAH cell to 10% based on an OCV measurement during an idle period of the application. The cell is then charged by 500mAH (to 60% expected) based on the internal coulomb count multiplied by the Learned Capacity Scaling Factor value of 55h. The next OCV adjustment determines the Relative Capacity should actually be at 65%, not 60%. The DS2786 then adjusts the Learned Capacity Scaling Factor value upward to (65% - 10%)  $\div$  (500mAH × 0.015 $\Omega$ ) = 5Eh lowering the expected cell capacity by approximately 10%.

## Figure 19. Last OCV Register Format

The Learn Delta Percent Threshold allows the application to select how large of a cell capacity change is required before the new cell capacity value is learned. The difference between the present OCV measurement and the Last OCV measurement must be greater than the Learn Delta Percent Threshold value for a Learn to occur. This prevents IC measurement resolution from adding error to the Learned Cell Capacity value. It is recommended this register be set to a value of at least 50%.

### Figure 20. Learn Delta Percent Threshold

## MEMORY MAP

The DS2786 has memory space with registers for instrumentation, status, and control. When the MSB of a twobyte register is read, both the MSB and LSB are latched and held for the duration of the read data command to prevent updates during the read and ensure synchronization between the two register bytes. For consistent results, always read the MSB and the LSB of a two-byte register during the same read data command sequence.

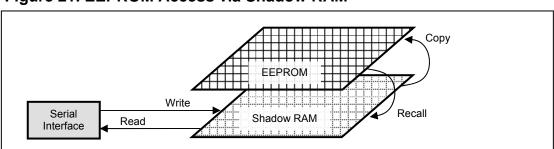

Memory locations 60h through 7Fh are EEPROM storage locations. EEPROM memory is shadowed by RAM to eliminate programming delays between writes and to allow the data to be verified by the host system before being copied to EEPROM. The Read Data and Write Data protocols to/from EEPROM memory addresses access the shadow RAM. Setting the RCALL bit in the Command Register (FEh) initiate data transfer from the EEPROM to the shadow RAM.

Setting the COPY bit in the Command Register initiates data transfer from the shadow RAM to the EEPROM. An external voltage supply must be provided on the VPROG pin prior to writing the COPY bit. The DS2786 requires the COPY bit be reset to 0 within the  $t_{PROG}$  time window to properly program EEPROM. Resetting COPY too soon may prevent a proper write of the cells. Resetting COPY too late may degrade EEPROM Copy Endurance.

The DS2786 uses shadow RAM data for fuel gauge calculations. Fuel gauge information can be changed in the application by writing the shadow RAM locations. Afterwards the SOCV bit should be written to reset the fuel gauge. Note that any reset of the I.C. will cause the Shadow RAM data to be restored from EEPROM.

## Figure 21. EEPROM Access via Shadow RAM

| ADDRESS (HEX) | DESCRIPTION                         | <b>READ/WRITE</b> |

|---------------|-------------------------------------|-------------------|

| 00h           | Reserved                            | _                 |

| 01h           | Status/Config Register              | R/W               |

| 02h           | Relative Capacity                   | R                 |

| 03h to 07h    | Reserved                            | _                 |

| 08h           | Auxiliary Input 0 MSB               | R                 |

| 09h           | Auxiliary Input 0 LSB               | R                 |

| 0Ah           | Auxiliary Input 1 / Temperature MSB | R                 |

| 0Bh           | Auxiliary Input 1 / Temperature LSB | R                 |

| 0Ch           | Voltage Register MSB                | R                 |

| 0Dh           | Voltage Register LSB                | R                 |

| 0Eh           | Current Register MSB                | R                 |

| 0Fh           | Current Register LSB                | R                 |

| 10h to 13h    | Reserved                            | _                 |

| 14h           | Initial Voltage MSB                 | R                 |

| 15h           | Initial Voltage LSB                 | R                 |

| 16h           | Last OCV Relative Capacity          | R                 |

| 17h           | Learned Capacity Scaling Factor     | R                 |

| 18h to 5Fh    | Reserved                            | _                 |

| 60h to 7Fh    | Parameter EEPROM                    | R/W               |

| 80h to FDh    | Reserved                            | <u> </u>          |

| Feh           | Command                             | R/W               |

| FFh           | Reserved                            |                   |

## Table 3. Memory Map

## Table 4. Parameter EEPROM Memory Block

| ADDRESS | DESCRIPTION                  | FACTORY<br>VALUE | ADDRESS | DESCRIPTION                             | FACTORY<br>VALUE |

|---------|------------------------------|------------------|---------|-----------------------------------------|------------------|

| 60h     | Current Offset Bias Register | 00h              | 70h     | Voltage Breakpoint 4 MSB                | C4h              |

| 61h     | Capacity 1                   | 0Ah              | 71h     | Voltage Breakpoint 4 LSB                | 20h              |

| 62h     | Capacity 2                   | 14h              | 72h     | Voltage Breakpoint 5 MSB                | CDh              |

| 63h     | Capacity 3                   | 32h              | 73h     | Voltage Breakpoint 5 LSB                | 10h              |

| 64h     | Capacity 4                   | 69h              | 74h     | Voltage Breakpoint 6 MSB                | Ceh              |

| 65h     | Capacity 5                   | A0h              | 75h     | Voltage Breakpoint 6 LSB                | F0h              |

| 66h     | Capacity 6                   | Aah              | 76h     | Voltage Breakpoint 7 MSB                | D1h              |

| 67h     | Capacity 7                   | B5h              | 77h     | Voltage Breakpoint 7 LSB                | 40h              |

| 68h     | Voltage Breakpoint 0 MSB     | A3h              | 78h     | Voltage Breakpoint 8 MSB                | D5h              |

| 69h     | Voltage Breakpoint 0 LSB     | 20h              | 79h     | Voltage Breakpoint 8 LSB                | 90h              |

| 6Ah     | Voltage Breakpoint 1 MSB     | B9h              | 7Ah     | Initial Capacity Scaling Factor         | 80h              |

| 6Bh     | Voltage Breakpoint 1 LSB     | 50h              | 7Bh     | Blanking/OCV Current Threshold          | 06h              |

| 6Ch     | Voltage Breakpoint 2 MSB     | BCh              | 7Ch     | OCV dV/dt Threshold                     | 93h              |

| 6Dh     | Voltage Breakpoint 2 LSB     | 10h              | 7Dh     | I <sup>2</sup> C Address Configuration* | 60h*             |

| 6Eh     | Voltage Breakpoint 3 MSB     | C0h              | 7Eh     | Learn Threshold                         | 78h              |

| 6Fh     | Voltage Breakpoint 3 LSB     | 20h              | 7Fh     | User EEPROM                             | 00h              |

\*The factory default 7-bit Slave Address is 0110110. The upper 3 bits are fixed at 011, the lower 4 bits can be changed by writing the  $l^2C$  Address Configuration Register as illustrated in Figures 24 and 25.

## STATUS/CONFIG REGISTER

The Status/Config Register is read/write with individual bits designated as read only. Bit values indicate status as well as program or select device functionality. Bits 3 though 6 are EEPROM backed at memory location 7Ch. Note that their bit positions differ between these locations.

### Figure 22. Status/Config Register Format

| ADDRESS 01h |       |       |       |       |       |       |       |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|

| BIT 7       | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |  |

| Х           | PORF  | SMOD  | LDIS  | VODIS | ITEMP | AIN1  | AIN0  |  |

|             |       |       |       |       |       |       |       |  |

Bit 7: X—Reserved.

**Bit 6: PORF**—The Power-On-Reset Flag is set to indicate initial power-up. PORF is not cleared internally. The user must write this flag value to a 0 in order to use it to indicate subsequent power-up events. POR event will cause a reset of the fuel gauge. PORF is read/write-to-zero.

**Bit 5: SMOD**—Sleep Mode Enable. A value of 1 allows the DS2786 to enter Sleep mode when SCL AND SDA are low for  $t_{SLEEP}$ . A value of 0 disables the transition to Sleep mode. This bit is EEPROM backed by bit 7 of memory location 7Ch. The factory programmed value is 1.

**Caution:** SMOD Sleep feature must be disabled when a battery is charged on an external charger that does not connect to the SDA or SCL pins. SMOD Sleep can be used if the charger pulls SDA or SCL high. The DS2786 remains in Sleep on a charger that fails to properly drive SDA or SCL and therefore does not adjust Relative Capacity when a battery is charged.

**Bit 4: LDIS**—LEARN Disable. A value of 1 disables cell capacity learning by the DS2786. A value of 0 allows cell capacity learning to occur normally. This bit is EEPROM backed by bit 6 of memory location 7Ch. The factory programmed value is 0.

**Bit 3 : VODIS**—V<sub>OUT</sub> Disable. A value of 1 disables the V<sub>OUT</sub> output. When set to 0 this output is driven  $t_{PRE}$  before the AIN0 conversion begins, and disabled after the AIN1 conversion ends. This bit is EEPROM backed by bit 5 of memory location 7Ch. The factory-programmed value is 0.

**Bit 2: ITEMP**—ITEMP. A value of 1 enables measurement of temperature using the internal sensor during the AIN1 conversion timeslot. AIN1 input is not selected and  $V_{OUT}$  is not enabled during the AIN1 timeslot. A value of 0 restores the measurement of AIN1 and enables  $V_{OUT}$  during the AIN1 timeslot. This bit is EEPROM backed by bit 4 of memory location 7Ch. The factory-programmed value is 1.

**Bit 1 : AIN1**—AIN1 Conversion Valid. This read only bit indicates that the  $V_{OUT}$  output was enabled, and a conversion has occurred on the AIN1 pin. When using the VODIS bit, before reading the AIN1 Registers, read the AIN1 bit. Only once the AIN1 bit is set, should the AIN1 Register be read.

**Bit 0 : AIN0**—AIN0 Conversion Valid. This read only bit indicates that the  $V_{OUT}$  output was enabled, and a conversion has occurred on the AIN0 pin. When using the VODIS bit, before reading the AIN0 Registers, read the AIN0 bit. Only once the AIN0 bit is set, should the AIN0 Register be read.

### COMMAND REGISTER

The Command Register is read/write accessible. Bit values indicate operations requested to be performed by the device.

### Figure 23. Command Register Format

|   |       |       |       | ADDRE | SS Feh |       |       |       |   |

|---|-------|-------|-------|-------|--------|-------|-------|-------|---|

|   | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3  | BIT 2 | BIT 1 | BIT 0 |   |

|   | POR   | 0     | Х     | Х     | POCV   | SOCV  | RCALL | COPY  | Ĩ |

| 1 |       |       |       |       |        |       |       |       | - |

**Bit 7: POR**—Power-On Reset. A value of 1 starts a power-on reset event. The bit is cleared on the next start or stop on the 2-Wire bus, exiting the reset state.

Bit 6: 0—Bit always reads logic 0.

#### Bits 5 and 4: X—Reserved.

**Bit 3: POCV**—Present OCV Calculation. When set to one the part is performing an OCV calculation based on the voltage stored in the Voltage Register, and the OCV lookup table values present in the scratch pad. Writing the bit to 1 forces a calculation. This function should be used for test purposes only. Forcing an OCV calculation will create capacity estimation error. The bit is cleared when the hardware completes the calculation.

**Bit 2: SOCV**—Stored OCV Calculation. This command may be used to reset the Relative Capacity calculation after updating OCV cell model data in the Scratchpad. When set to one the part is performing an OCV calculation based on the voltage stored in the Initial Voltage Register, and the OCV lookup table values present in the scratch pad. Writing the bit to 1 forces a calculation. Forcing an OCV calculation will create capacity estimation error. The bit is cleared when the hardware completes the calculation.

Bit 1: RCALL—The Recall bit is set to recall the contents of EEPROM into the scratch pad.

**Bit 0: COPY**—The Copy bit is set to start a copy command of the scratch pad to EEPROM. A programming voltage must be present on the VPROG pin prior for the copy to be successful. The COPY bit must be cleared by software within the  $t_{PROG}$  time window.

### USER EEPROM

Location 7Fh provides one byte available for storage of user-defined information. This byte does not affect operation of the fuel gauge. Factory default is 00h.

### 2-WIRE BUS SYSTEM

The 2-Wire bus system supports operation as a slave only device in a single or multislave, and single- or multimaster system. The 2-wire interface consists of a serial data line (SDA) and serial clock line (SCL). SDA and SCL provide bidirectional communication between the DS2786 slave device and a master device at speeds up to 400kHz. The DS2786's SDA pin operates bidirectionally, that is, when the DS2786 receives data, SDA operates as an input, and when the DS2786 returns data, SDA operates as an open-drain output, with the host system providing a resistive pullup. The DS2786 always operates as a slave device, receiving and transmitting data under the control of a master device. The master initiates all transactions on the bus and generates the SCL signal as well as the START and STOP bits which begin and end each transaction.

#### Bit Transfer

One data bit is transferred during each SCL clock cycle, with the cycle defined by SCL transitioning low-to-high and then high-to-low. The SDA logic level must remain stable during the high period of the SCL clock pulse. Any change in SDA when SCL is high is interpreted as a START or STOP control signal.

#### Bus Idle

The bus is defined to be idle, or not busy, when no master device has control. Both SDA and SCL remain high when the bus is idle. The STOP condition is the proper method to return the bus to the idle state.

#### **START and STOP Conditions**

The master initiates transactions with a START condition (S), by forcing a high-to-low transition on SDA while SCL is high. The master terminates a transaction with a STOP condition (P), a low-to-high transition on SDA while SCL is high. A Repeated START condition (Sr) can be used in place of a STOP then START sequence to terminate one transaction and begin another without returning the bus to the idle state. In multimaster systems, a Repeated START allows the master to retain control of the bus. The START and STOP conditions are the only bus activities in which the SDA transitions when SCL is high.

#### Acknowledge Bits

Each byte of a data transfer is acknowledged with an Acknowledge bit (A) or a No Acknowledge bit (N). Both the master and the DS2786 slave generate acknowledge bits. To generate an Acknowledge, the receiving device must pull SDA low before the rising edge of the acknowledge-related clock pulse (ninth pulse) and keep it low until SCL returns low. To generate a No Acknowledge (also called NAK), the receiver releases SDA before the rising edge of the acknowledge SDA high until SCL returns low. Monitoring the acknowledge bits allows for detection of unsuccessful data transfers. An unsuccessful data transfer can occur if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master should reattempt communication.

#### Data Order

A byte of data consists of 8 bits ordered most significant bit (MSB) first. The least significant bit (LSB) of each byte is followed by the Acknowledge bit. DS2786 registers composed of multibyte values are ordered most significant byte (MSB) first. The MSB of multibyte registers is stored on even data memory addresses.

#### Slave Address

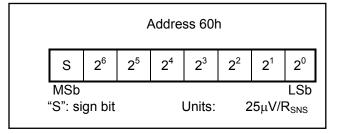

A bus master initiates communication with a slave device by issuing a START condition followed by a Slave Address (Saddr) and the read/write (R/W) bit. When the bus is idle, the DS2786 continuously monitors for a START condition followed by its slave address. When the DS2786 receives a slave address that matches its Slave Address, it responds with an Acknowledge bit during the clock period following the R/W bit. The factory default 7-bit Slave Address is 0110110. The upper 3 bits are fixed at 011, the lower 4 bits can be changed by writing the  $I^2C$  Address Configuration Register at location 7Dh.

## Figure 24. I<sup>2</sup>C Address Configuration Register Format

|       |       |       | ADDRE | SS 7Dh |       |       |       |

|-------|-------|-------|-------|--------|-------|-------|-------|

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3  | BIT 2 | BIT 1 | BIT 0 |

| ADDR3 | ADDR2 | ADDR1 | ADDR0 | Х      | Х     | Х     | Х     |

Bits 7 to 4: ADDR[3:0]—User-adjustable bits of the DS2786's I<sup>2</sup>C address. Factory default is 0110.

Bits 3 to 0: X—Reserved.

### Figure 25. DS2786 I<sup>2</sup>C Address Byte Format

|                   | BIT 2 BIT 1 BIT 0 |

|-------------------|-------------------|

| 0 1 1 ADDR3 ADDR3 | 2 ADDR1 ADDR0 R/W |

#### **Read/Write Bit**

The R/W bit following the slave address determines the data direction of subsequent bytes in the transfer. R/W = 0 selects a write transaction, with the following bytes being written by the master to the slave. R/W = 1 selects a read transaction, with the following bytes being read from the slave by the master. With the ADDR3–ADDR0 bits at their default of 0110, writes occur using address 0x6Ch, while reads occur at 0x6Dh.

#### **Bus Timing**

The DS2786 is compatible with any bus timing up to 400kHz. No special configuration is required to operate at any speed.

#### 2-Wire Command Protocols

The command protocols involve several transaction formats. The simplest format consists of the master writing the START bit, slave address, R/W bit, and then monitoring the acknowledge bit for presence of the DS2786. More complex formats such as the Write Data, Read Data, and Function command protocols write data, read data, and execute device specific operations. All bytes in each command format require the slave or host to return an Acknowledge bit before continuing with the next byte. Each function command definition outlines the required transaction format. The following key applies to the transaction formats.

| KEY   | DESCRIPTION                 | KEY  | DESCRIPTION                 |

|-------|-----------------------------|------|-----------------------------|

| S     | START bit                   | Sr   | Repeated START              |

| Saddr | Slave Address (7-bit)       | W    | $R/\overline{W}$ bit = 0    |

| FCmd  | Function Command byte       | R    | $R/\overline{W}$ bit = 1    |

| Maddr | Memory Address byte         | Р    | STOP bit                    |

| Data  | Data byte written by master | Data | Data byte returned by slave |

| А     | Acknowledge bit—Master      | A    | Acknowledge bit—Slave       |

| Ν     | No AcknowledgeMaster        | Ν    | No Acknowledge—Slave        |

#### Table 5. 2-Wire Protocol Key

#### **Basic Transaction Formats**

Write: S Saddr W A Maddr A Data0 A P

A write transaction transfers one or more data bytes *to* the DS2786. The data transfer begins at the memory address supplied in the Maddr byte. Control of the SDA signal is retained by the master throughout the transaction, except for the Acknowledge cycles.

Read: S Saddr W A Maddr A Sr Saddr R A Data0 N P

Write Portion

Read Portion

A read transaction transfers one or more bytes *from* the DS2786. Read transactions are composed of two parts, a write portion followed by a read portion, and is therefore inherently longer than a write transaction. The write portion communicates the starting point for the read operation. The read portion follows immediately, beginning with a Repeated START, Slave Address with R/W set to a 1. Control of SDA is assumed by the DS2786 beginning with the Slave Address Acknowledge cycle. Control of the SDA signal is retained by the DS2786 throughout the transaction, except for the Acknowledge cycles. The master indicates the end of a read transaction by responding to the last byte it requires with a No Acknowledge. This signals the DS2786 that control of SDA is to remain with the master following the Acknowledge clock.

#### Write Data Protocol

The write data protocol is used to write to register and shadow RAM data to the DS2786 starting at memory address Maddr. Data0 represents the data written to Maddr, Data1 represents the data written to Maddr + 1 and DataN represents the last data byte, written to Maddr + N. The master indicates the end of a write transaction by sending a STOP or Repeated START after receiving the last acknowledge bit.

S Saddr W A Maddr A Data0 A Data1 A ... DataN A P

The MSB of the data to be stored at address Maddr can be written immediately after the Maddr byte is acknowledged. Because the address is automatically incremented after the least significant bit (LSB) of each byte is received by the DS2786, the MSB of the data at address Maddr + 1 is can be written immediately after the acknowledgement of the data at address Maddr. If the bus master continues an auto-incremented write transaction beyond address 4Fh, the DS2786 ignores the data. Data is also ignored on writes to read-only addresses and reserved addresses, as well as a write that auto increments to the Function Command Register (address Feh). Incomplete bytes and bytes that are Not Acknowledged by the DS2786 are not written to memory. As noted in the Memory Section, writes to EEPROM locations modify the shadow RAM only.

#### Read Data Protocol

The Read Data protocol is used to read register and shadow RAM data from the DS2786 starting at memory address specified by Maddr. Data0 represents the data byte in memory location Maddr, Data1 represents the data from Maddr + 1 and DataN represents the last byte read by the master.

S Saddr W A Maddr A Sr Saddr R A Data0 A Data1 A ... DataN N P

Data is returned beginning with the MSB of the data in Maddr. Because the address is automatically incremented after the LSB of each byte is returned, the MSB of the data at address Maddr + 1 is available to the host immediately after the acknowledgement of the data at address Maddr. If the bus master continues to read beyond address FFh, the DS2786 outputs data values of FFh. Addresses labeled "Reserved" in the Memory Map (Table 3) return undefined data. The bus master terminates the read transaction at any byte boundary by issuing a No Acknowledge followed by a STOP or repeated START.

### PACKAGE INFORMATION

For the latest package outline information and land patterns, go to <u>www.maxim-ic.com/packages</u>.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 10 TDFN-EP   | T1033+1      | <u>21-0137</u> |

| REVISION<br>DATE | DESCRIPTION                                                                                                                                     |                |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|

|                  | In the <i>Recommended DC Operating Characteristics</i> , changed the PIO pin range to VPROG pin range and changed the operating range to 15.5V. | 2              |  |  |

| 030708           | Corrected bit locations of VDIS and LODIS bits in EEPROM (Figure 14 and <i>Status/Config Register</i> section).                                 |                |  |  |

|                  | Fixed grammatical error under OCV cell model section: "required" to "require."                                                                  |                |  |  |

|                  | Fixed grammatical error describing Copy bit under Memory Map section.                                                                           | 15             |  |  |

| 070808           | In Figure 23, changed bit 6 from X (reserved) to 0.                                                                                             | 18             |  |  |

| 101708           | Changed operation to 4.5V maximum.                                                                                                              | 2, 3, 5, 8, 13 |  |  |

| 051000           | Changed the V <sub>DD</sub> maximum operating range in the <i>Electrical Characteristics</i> table to 4.5V.                                     | 2, 3           |  |  |

| 051209           | Added "V <sub>IN</sub> pin is limited to V <sub>DD</sub> voltage" text in the <i>Voltage Measurement</i> section.                               | 8              |  |  |

## **REVISION HISTORY**

Maxim/Dallas Semiconductor cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim/Dallas Semiconductor product. No circuit patent licenses are implied. Maxim/Dallas Semiconductor reserves the right to change the circuitry and specifications without notice at any time. Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 © 2009 Maxim Integrated Products

The Maxim logo is a registered trademark of Maxim Integrated Products, Inc. The Dallas logo is a registered trademark of Dallas Semiconductor Corporation.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated: DS2786G+ DS2786G+T&R