# Single phase PWM controller

#### **Feature**

- Flexible power supply from 5 V to 12 V

- Power conversion input as low as 1.5 V

- 1% output voltage accuracy

- High-current integrated drivers

- Adjustable output voltage

- 0.8 V internal reference

- Sensorless and programmable OCP across Low-side R<sub>dsON</sub>

- Oscillator internally fixed at 270 kHz

- Programmable soft-start

- Ls-less start up

- Disable function

- FB disconnection protection

- SO-8 package

# **Applications**

- Subsystem power supply (MCH, IOCH, PCI...)

- Memory and termination supply

- CPU and DSP power supply

- Distributed power supply

- General DC / DC converters

#### **Description**

L6726A is a single-phase step-down controller with integrated high-current drivers that provides complete control logic, protections and reference voltage to realize in an easy and simple way general DC-DC converters by using a compact SO-8 package.

Device flexibility allows managing conversions with power input  $V_{\text{IN}}$  as low as 1.5 V and device supply voltage ranging from 5 V to 12 V.

L6726A provides simple control loop with transconductance error amplifier. The integrated 0.8 V reference allows regulating output voltage with ±1% accuracy over line and temperature variations. Oscillator is internally fixed to 270 kHz.

L6726A provides programmable over current protection. Current information is monitored across the low-side MOSFET  $R_{dsON}$  saving the use of expensive and space-consuming sense resistors.

FB disconnection protection prevents excessive and dangerous output voltages in case of floating FB pin.

Table 1. Device summary

| Order codes | Package | Packaging     |

|-------------|---------|---------------|

| L6726A      | SO-8    | Tube          |

| L6726ATR    | SO-8    | Tape and reel |

Contents L6726A

# **Contents**

| 1 | Typi  | cal application circuit and block diagram | . 4 |

|---|-------|-------------------------------------------|-----|

|   | 1.1   | Application circuit                       | 4   |

|   | 1.2   | Block diagram                             | 4   |

| 2 | Pins  | description and connection diagrams       | . 5 |

|   | 2.1   | Pin descriptions                          | 5   |

|   | 2.2   | Thermal data                              | 6   |

| 3 | Elec  | trical specifications                     | . 7 |

|   | 3.1   | Absolute maximum ratings                  | 7   |

|   | 3.2   | Electrical characteristics                | 7   |

| 4 | Devi  | ce description                            | . 9 |

| 5 | Drive | er section                                | 10  |

|   | 5.1   | Power dissipation                         | 11  |

| 6 | Soft  | start and disable                         | 12  |

|   | 6.1   | Low-side-less start up (LSLess)           | 12  |

|   | 6.2   | Enable / disable                          | 12  |

| 7 | Prot  | ections                                   | 13  |

|   | 7.1   | Overcurrent protection                    | 13  |

|   |       | 7.1.1 Overcurrent threshold setting       | 13  |

|   | 7.2   | Feedback disconnection protection         | 13  |

|   | 7.3   | Undervoltage lock out                     | 14  |

| 8 | App   | lication details                          | 15  |

|   | 8.1   | Output voltage selection                  | 15  |

|   | 8.2   | Compensation network                      | 15  |

|   | 8.3   | Soft-start time calculation               | 18  |

|   | 8.4   | Layout guidelines                         | 18  |

|   | 8.5   | Embedding L6726A-based VRs                | 20  |

|   |       |                                           |     |

| 9  | Appl  | Application Information               |    |  |  |  |

|----|-------|---------------------------------------|----|--|--|--|

|    | 9.1   | Output inductor                       | 21 |  |  |  |

|    | 9.2   | Output capacitors                     | 22 |  |  |  |

|    | 9.3   | Input capacitors                      | 22 |  |  |  |

| 10 | 20 A  | lemonstration board                   | 23 |  |  |  |

|    | 10.1  | Board description                     | 27 |  |  |  |

|    |       | 10.1.1 Power input (VIN)              | 27 |  |  |  |

|    |       | 10.1.2 Power output (VOUT)            | 27 |  |  |  |

|    |       | 10.1.3 IC additional supply (VCC)     | 27 |  |  |  |

|    |       | 10.1.4 Test points                    | 27 |  |  |  |

|    |       | 10.1.5 Demonstration board efficiency | 27 |  |  |  |

| 11 | 5 A c | emonstration board 2                  | 28 |  |  |  |

|    | 11.1  | Board description                     | 30 |  |  |  |

|    |       | 11.1.1 Power input (VIN)              | 30 |  |  |  |

|    |       | 11.1.2 Power output (VOUT)            | 31 |  |  |  |

|    |       | 11.1.3 IC additional supply (VCC)     | 31 |  |  |  |

|    |       | 11.1.4 Test points                    | 31 |  |  |  |

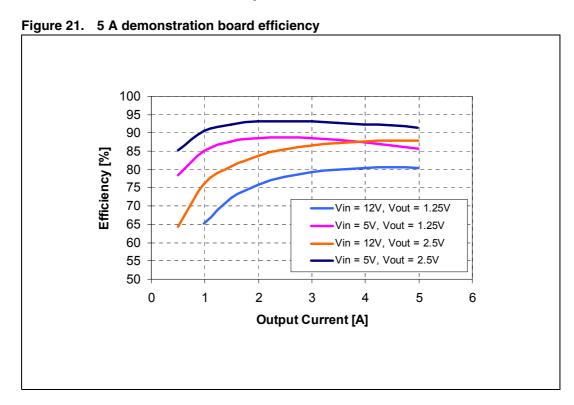

|    |       | 11.1.5 Demonstration board efficiency | 31 |  |  |  |

| 12 | Pack  | ge mechanical data                    | 2  |  |  |  |

| 13 | Revi  | ion history 3                         | 14 |  |  |  |

# 1 Typical application circuit and block diagram

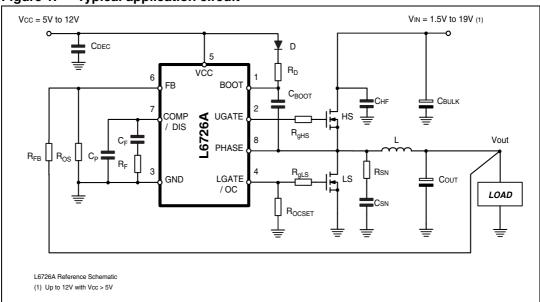

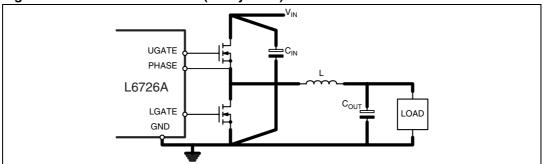

# 1.1 Application circuit

Figure 1. Typical application circuit

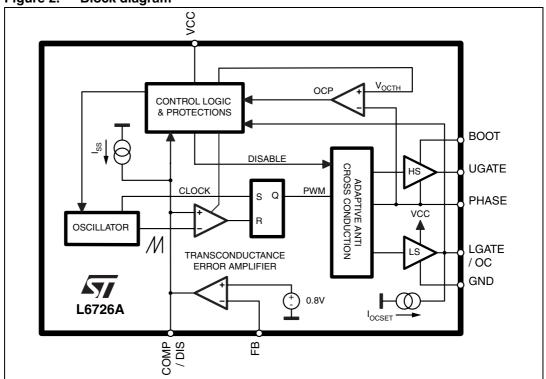

## 1.2 Block diagram

Figure 2. Block diagram

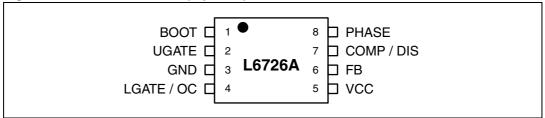

# 2 Pins description and connection diagrams

Figure 3. Pins connection (top view)

# 2.1 Pin descriptions

Table 2. Pins descriptions

| Pin n | Name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | воот       | HS driver supply.  Connect through a capacitor (100 nF) to the floating node (LS-drain) pin and provide necessary bootstrap diode from VCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2     | UGATE      | HS driver output. Connect to HS MOSFET gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3     | GND        | All internal references, logic and drivers are connected to this pin.  Connect to the PCB ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4     | LGATE / OC | $\it LGATE$ . LS driver output. Connect to LS MOSFET gate. $\it OC$ . Over current threshold set. During a short period of time following VCC rising over UVLO threshold, a $10\mu A$ current is sourced from this pin. Connect to GND with an $R_{OCSET}$ resistor greater than $5k\Omega$ to program OC Threshold. The resulting voltage at this pin is sampled and held internally as the OC set point. Maximum programmable OC threshold is 0.55 V. A voltage greater than 0.75V (max) activates an internal clamp and causes OC threshold to be set at 400 mV. $R_{OCSET}$ not connected sets the 400 mV default threshold. |

| 5     | VCC        | Device and LS driver power supply.  Operative range from 4.1 V to 13.2 V. Filter with at least 1μF MLCC to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6     | FB         | Error amplifier inverting input. Connect with a resistor $R_{FB}$ to the output regulated voltage. Additional resistor $R_{OS}$ to GND may be used to regulate voltages higher than the reference.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7     | COMP / DIS | COMP. Error amplifier output. Connect with an $R_F$ - $C_F$ // $C_P$ to GND to compensate the device control loop in conjunction to the FB pin. During the soft-start phase, a 10 $\mu$ A current is sourced from this pin so the compensation capacitors also act to program the SS time. DIS. The device can be disabled by pulling this pin lower than 0.4 V (min). Setting free the pin, the device enables again.                                                                                                                                                                                                           |

| 8     | PHASE      | HS driver return path, current-reading and adaptive-dead-time monitor. Connect to the LS drain to sense R <sub>dsON</sub> drop to measure the output current. This pin is also used by the adaptive-dead-time control circuitry to monitor when HS MOSFET is OFF.                                                                                                                                                                                                                                                                                                                                                                |

# 2.2 Thermal data

6/35

Table 3. Thermal data

| Symbol           | Parameter                                             | Value      | Unit |

|------------------|-------------------------------------------------------|------------|------|

| $R_{thJA}$       | Thermal resistance junction to ambient <sup>(1)</sup> | 85         | °C/W |

| T <sub>MAX</sub> | Maximum junction temperature                          | 150        | °C   |

| T <sub>STG</sub> | Storage temperature range                             | -40 to 150 | °C   |

| T <sub>J</sub>   | Junction temperature range                            | -20 to 150 | °C   |

<sup>1.</sup> Measured with the component mounted on a 2S2P board in free air (6.7 cm x 6.7 cm, 35  $\mu$ m (P) and 17.5  $\mu$ m (S) copper thickness).

# 3 Electrical specifications

# 3.1 Absolute maximum ratings

Table 4. Absolute maximum ratings

| Symbol             | Parameter                                | Value                                                                                    | Unit |

|--------------------|------------------------------------------|------------------------------------------------------------------------------------------|------|

| V <sub>CC</sub>    | to GND                                   | -0.3 to 15                                                                               | ٧    |

| V <sub>BOOT</sub>  | to PHASE<br>to GND                       | 15<br>45                                                                                 | V    |

| V <sub>UGATE</sub> | to PHASE<br>to PHASE; t < 50ns<br>to GND | -0.3 to (V <sub>BOOT</sub> - V <sub>PHASE</sub> ) + 0.3<br>-1<br>V <sub>BOOT</sub> + 0.3 | V    |

| V <sub>PHASE</sub> | to GND                                   | -8 to 30                                                                                 | ٧    |

| V <sub>LGATE</sub> | to GND<br>to GND; t < 50ns               | -0.3 to V <sub>CC</sub> + 0.3<br>-2.5                                                    | V    |

|                    | FB, COMP to GND                          | -0.3 to 3.6                                                                              | V    |

#### 3.2 Electrical characteristics

$V_{CC}$  = 12 V;  $T_A$  = -20  $^{\circ}C$  to +85  $^{\circ}C$  unless otherwise specified.

Table 5. Electrical characteristics

| Symbol            | Parameter Test conditions        |                                                               | Min. | Тур. | Max. | Unit  |  |

|-------------------|----------------------------------|---------------------------------------------------------------|------|------|------|-------|--|

| Recommend         | Recommended operating conditions |                                                               |      |      |      |       |  |

| V <sub>CC</sub>   | Device supply voltage            | - See <i>Figure</i> 1                                         | 4.1  |      | 13.2 | V     |  |

| V <sub>IN</sub>   | Conversion input voltage         | - See Figure 1                                                |      |      | 13.2 | V     |  |

|                   | Conversion input voitage         | V <sub>CC</sub> < 7.0 V                                       |      |      | 19.0 | V     |  |

| Supply curr       | Supply current and power-ON      |                                                               |      |      |      |       |  |

| I <sub>CC</sub>   | VCC supply current               | UGATE and LGATE = OPEN                                        |      | 6    |      | mA    |  |

| I <sub>BOOT</sub> | BOOT supply current              | UGATE = OPEN; PHASE to GND                                    |      | 0.5  |      | mA    |  |

| UVLO              | VCC Turn-ON                      | VCC rising                                                    |      |      | 4.1  | V     |  |

|                   | Hysteresis                       |                                                               |      | 0.2  |      | V     |  |

| Oscillator        |                                  |                                                               |      |      |      |       |  |

| F <sub>SW</sub>   | Main oscillator accuracy         | $T_A = 0  ^{\circ}\text{C} \text{ to } +70  ^{\circ}\text{C}$ | 243  | 270  | 297  | kHz   |  |

|                   | Iviairi oscillator accuracy      |                                                               | 225  | 270  | 315  | NI IZ |  |

| ΔV <sub>OSC</sub> | PWM ramp amplitude               |                                                               |      | 1.1  |      | V     |  |

| d <sub>MAX</sub>  | Maximum duty cycle               |                                                               | 80   |      |      | %     |  |

Table 5. Electrical characteristics (continued)

| Symbol                  | Parameter                       | Test conditions                                                                     | Min. | Тур. | Max. | Unit |  |

|-------------------------|---------------------------------|-------------------------------------------------------------------------------------|------|------|------|------|--|

| Reference               |                                 |                                                                                     |      |      |      |      |  |

|                         | Output valtage cooursev         | $V_{OUT} = 0.8 \text{ V}, T_A = 0 ^{\circ}\text{C} \text{ to } 70 ^{\circ}\text{C}$ | -1   | -    | 1    | 0/   |  |

|                         | Output voltage accuracy         | V <sub>OUT</sub> = 0.8 V                                                            | -1.5 | -    | 1.5  | %    |  |

| Transconduc             | ctance error amplifier          |                                                                                     |      |      |      |      |  |

| gm                      | Transconductance <sup>(1)</sup> |                                                                                     |      |      | 5    | mS   |  |

| I <sub>FB</sub>         | Input bias current              | Sourced from FB                                                                     |      | 100  |      | nA   |  |

| A <sub>0</sub>          | Open loop gain <sup>(1)</sup>   |                                                                                     |      | 70   |      | dB   |  |

| F <sub>0</sub>          | Unity gain <sup>(1)</sup>       |                                                                                     |      | 4    |      | MHz  |  |

| I <sub>COMP</sub>       | Current capability              | Source current                                                                      |      | 360  |      | μΑ   |  |

|                         | Current capability              | Sink current                                                                        |      | -360 |      | μΑ   |  |

| Soft-Start an           | d disable                       |                                                                                     |      |      |      |      |  |

| I <sub>SS</sub>         | Soft-start current              | From COMP pin                                                                       |      | 10   |      | μΑ   |  |

| DIS                     | Disable threshold               | COMP falling                                                                        | 0.4  | 0.5  |      | V    |  |

| Gate drivers            |                                 |                                                                                     |      |      |      |      |  |

| I <sub>UGATE</sub>      | HS source current               | BOOT - PHASE = 5 V to 12 V                                                          |      | 1.5  |      | Α    |  |

| R <sub>UGATE</sub>      | HS sink resistance              | BOOT - PHASE = 5 V to 12 V                                                          |      | 1.1  |      | Ω    |  |

| I <sub>LGATE</sub>      | LS source current               | VCC = 5 V to 12 V                                                                   |      | 1.5  |      | Α    |  |

| R <sub>LGATE</sub>      | LS sink resistance              | VCC = 5 V to 12 V                                                                   |      | 0.65 |      | Ω    |  |

| Over-current            | protection                      |                                                                                     |      |      |      |      |  |

| I <sub>OCSET</sub>      | OCSET current source            | Sourced from LGATE pin.<br>See Section 7.1.1                                        |      | 10   |      | μА   |  |

| V <sub>OC_SW</sub>      | OC switch-over threshold        | V <sub>LGATE/OC</sub> rising                                                        |      |      | 780  | mV   |  |

| V <sub>OCTH_FIXED</sub> | Fixed OC threshold              | V <sub>PHASE</sub> to GND                                                           |      | -400 |      | mV   |  |

<sup>1.</sup> Guaranteed by design, not subject to test.

L6726A Device description

## 4 Device description

L6726A is a single-phase PWM controller with embedded high-current drivers that provides complete control logic and protections to realize in an easy and simple way a general DC-DC step-down converter. Designed to drive N-channel MOSFETs in a synchronous buck topology, with its high level of integration this 8-pin device allows reducing cost and size of the power supply solution.

L6726A is designed to operate from a 5 V or 12 V supply bus. Thanks to the high precision 0.8V internal reference, the output voltage can be precisely regulated to as low as 0.8 V with  $\pm 1\%$  accuracy over line and temperature variations (between 0 °C and  $\pm 70$  °C). The switching frequency is internally set to 270 kHz.

This device provides a simple control loop with externally compensated transconductance error-amplifier and programmable soft start. Low-side-less feature allows the device to perform soft-start over pre-charged output avoiding negative spikes at the load side.

In order to avoid load damages, L6726A provides programmable threshold over current protection. Output current is monitored across low-side MOSFET R<sub>dsON</sub>, saving the use of expensive and space-consuming sense resistor. L6726A also features FB disconnection protection, preventing dangerous uncontrolled output voltages in case of floating FB pin.

Driver section L6726A

#### 5 Driver section

The integrated high-current drivers allow using different types of power MOSFET (also multiple MOSFETs to reduce the equivalent  $R_{dsON}$ ), maintaining fast switching transition.

The driver for high-side MOSFET uses BOOT pin for supply and PHASE pin for return. The driver for low-side MOSFET uses the VCC pin for supply and GND pin for return.

The controller embodies an anti-shoot-through and adaptive dead-time control to minimize low side body diode conduction time, maintaining good efficiency while saving the use of Schottky diode:

- to check for high-side MOSFET turn off, PHASE pin is sensed. When the voltage at PHASE pin drops down, the low-side MOSFET gate drive is suddenly applied;

- to check for low-side MOSFET turn off, LGATE pin is sensed. When the voltage at LGATE has fallen, the high-side MOSFET gate drive is suddenly applied.

If the current flowing in the inductor is negative, voltage on PHASE pin will never drop. To allow the low-side MOSFET to turn-on even in this case, a watchdog controller is enabled: if the source of the high-side MOSFET doesn't drop, the low side MOSFET is switched on so allowing the negative current of the inductor to recirculate. This mechanism allows the system to regulate even if the current is negative.

Power conversion input is flexible: 5 V, 12 V bus or any bus that allows the conversion (See maximum duty cycle limitation and recommended operating conditions) can be chosen freely.

L6726A Driver section

#### 5.1 Power dissipation

L6726A embeds high current MOSFET drivers for both high side and low side MOSFETs: it is then important to consider the power that the device is going to dissipate in driving them in order to avoid overcoming the maximum junction operative temperature.

Two main terms contribute in the device power dissipation: bias power and drivers power.

Device bias power (P<sub>DC</sub>) depends on the static consumption of the device through the supply pins and it is simply quantifiable as follow (assuming to supply HS and LS drivers with the same VCC of the device):

$$P_{DC} = V_{CC} \cdot (I_{CC} + I_{BOOT})$$

• Drivers power is the power needed by the driver to continuously switch on and off the external MOSFETs; it is a function of the switching frequency, the voltage supply of the driver and total gate charge of the selected MOSFETs. It can be quantified considering that the total power P<sub>SW</sub> dissipated to switch the MOSFETs (easy calculable) is dissipated by three main factors: external gate resistance (when present), intrinsic MOSFET resistance and intrinsic driver resistance. This last term is the important one to be determined to calculate the device power dissipation. The total power dissipated to switch the MOSFETs results:

$$P_{SW} = F_{SW} \cdot [Q_{gHS} \cdot (V_{BOOT} - V_{PHASE}) + Q_{gLS} \cdot V_{CC}]$$

where  $V_{\mbox{\footnotesize{BOOT}}}$  -  $V_{\mbox{\footnotesize{PHASE}}}$  is the voltage across the bootstrap capacitor.

External gate resistors helps the device to dissipate the switching power since the same power P<sub>SW</sub> will be shared between the internal driver impedance and the external resistor resulting in a general cooling of the device.

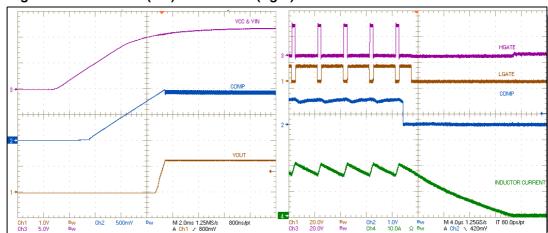

Figure 4. Soft start (left) and disable (right)

Soft start and disable L6726A

#### 6 Soft start and disable

L6726A implements a soft start to smoothly charge the output filter avoiding high in-rush currents to be required from the input power supply. The device sources a 10  $\mu$ A soft start current from COMP, linearly charging the compensation network capacitors. The ramping COMP voltage is compared to the oscillator triangular waveform generating PWM pulses of increasing width that charge the output capacitors.

When the FB voltage crosses 800 mV, the output voltage is in regulation: soft start phase will end and the transconductance error amplifier output will be enabled closing the control loop.

In the event of an over current during soft start, the over current logic will override the soft start sequence and will shut down the PWM logic and both the high side and low side gates. This condition is latched, cycle VCC to recover.

The device sources soft start current only when VCC power supply is above UVLO threshold and over current threshold setting phase has been completed.

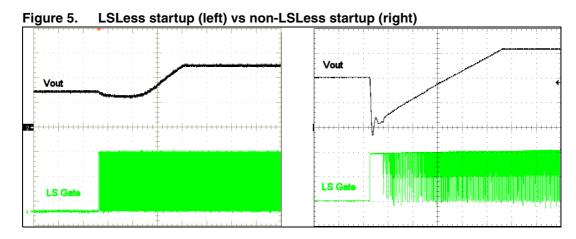

#### 6.1 Low-side-less start up (LSLess)

L6726A performs a special sequence in enabling LS driver to switch: during the soft-start phase, the LS driver results disabled (LS = OFF) until the HS starts to switch. This avoids the dangerous negative spike on the output voltage that can happen if starting over a precharged output and limits the output discharge (amount of output discharge depends on programmed SS time length: the shorter the programmed SS, the more limited the output discharge).

If the output voltage is pre-charged to a voltage higher than the final one, the HS would never start to switch. In this case, LS is enabled and discharges the output to the final regulation value.

#### 6.2 Enable / disable

The device can be disabled by pushing COMP / DIS pin under 0.4 V (min). In this condition HS and LS MOSFETs are turned off, and the 10  $\mu$ A SS current is sourced from COMP / DIS pin. Setting free the pin, the device enables again performing a new SS.

L6726A Protections

#### 7 Protections

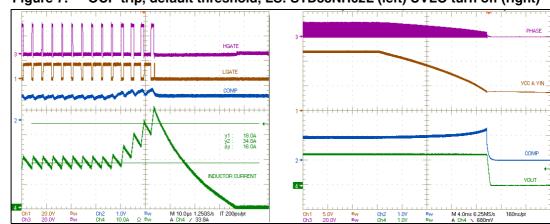

#### 7.1 Overcurrent protection

The overcurrent feature protects the converter from a shorted output or overload, by sensing the output current information across the low side MOSFET drain-source on-resistance, R<sub>dsON</sub>. This method reduces cost and enhances converter efficiency by avoiding the use of expensive and space-consuming sense resistors.

The low side  $R_{dsON}$  current sense is implemented by comparing the voltage at the PHASE node when LS MOSFET is turned on with the programmed OCP threshold voltage, internally held. If the monitored voltage drop (GND to PHASE) exceeds this threshold, an Overcurrent event is detected. If two overcurrent events are detected in two consecutive switching cycles, the protection will be triggered and the device will turn off both LS and HS MOSFETs in a latched condition.

To recover from over current protection triggered, VCC power supply must be cycled.

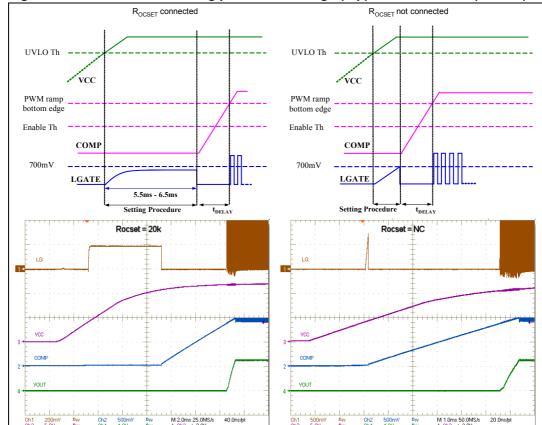

#### 7.1.1 Overcurrent threshold setting

L6726A allows to easily program an overcurrent threshold ranging from 50 mV to 550 mV, simply by adding a resistor (R<sub>OCSET</sub>) between LGATE and GND.

During a short time following VCC rising over UVLO threshold, an internal  $10\mu A$  current ( $I_{OCSET}$ ) is sourced from LGATE pin, determining a voltage drop across  $R_{OCSET}$ . This voltage drop will be sampled and internally held by the device as overcurrent Threshold. The OC setting procedure overall time length ranges from 5.5 ms to 6.5 ms, proportionally to the threshold being set.

Connecting a R<sub>OCSET</sub> resistor between LGATE and GND, the programmed threshold will be:

$$I_{OCth} = \frac{I_{OCSET} \cdot R_{OCSET}}{R_{dsON}}$$

$R_{OCSET}$  values range from 5  $k\Omega$  to 55  $k\Omega$

If the voltage drop across  $R_{OCSET}$  is too low, the system will be very sensitive to start-up inrush current and noise. This can result in undesired OCP triggering. In this case, consider increasing  $R_{OCSET}$  value.

In case  $R_{OCSET}$  is not connected, the device switches the OCP threshold to a 400 mV default value: an internal safety clamp on LGATE is triggered as soon as LGATE voltage reaches 700 mV (typ), enabling the 400 mV default threshold and suddenly ending OC setting phase.

See *Figure 6* for OC threshold setting procedure timings picture and oscilloscope sample waveforms.

## 7.2 Feedback disconnection protection

In order to provide load protection even if FB pin is not connected, a 100 nA bias current is always sourced from this pin. If FB pin is not connected, bias current will permanently pull up FB: this forces COMP pin low, avoiding output voltage rising to dangerous levels.

Protections L6726A

Figure 6. OC threshold setting procedure timings (top) and waveforms (bottom)

## 7.3 Undervoltage lock out

In order to avoid anomalous behaviors of the device when the supply voltage is too low to support its internal rails, UVLO is provided: the device will start up when VCC reaches UVLO upper threshold and will shutdown when VCC drops below UVLO lower threshold.

The 4.1 V maximum UVLO upper threshold allows L6726A to be supplied from 5 V and 12 V busses in or-ing diode configuration.

Figure 7. OCP trip, default threshold, LS: STD38NH02L (left) UVLO turn off (right)

L6726A Application details

## 8 Application details

#### 8.1 Output voltage selection

L6726A is capable to precisely regulate an output voltage as low as 0.8 V. In fact, the device comes with a fixed 0.8 V internal reference that guarantees the output regulated voltage to be within  $\pm 1\%$  tolerance over line and temperature variations between 0 °C and 70 °C (excluding output resistor divider tolerance, when present).

Output voltage higher than 0.8 V can be achieved by adding a resistor  $R_{OS}$  between FB pin and ground. Referring to *Figure 1*, the steady state DC output voltage will be:

$$V_{OUT} = V_{REF} \cdot \left(1 + \frac{R_{FB}}{R_{OS}}\right)$$

where V<sub>RFF</sub> is 0.8 V.

#### 8.2 Compensation network

The control loop shown in *Figure 8* is a voltage mode control loop. The error amplifier is a transconductance type with fixed gain (3.3 ms typ.). The FB voltage is regulated to the internal reference, thus the output voltage is fixed accordingly to the output resistor divider (when present).

Transconductance error amplifier output current generates a voltage across  $Z_{\text{F}}$  which is compared to oscillator saw-tooth waveform to provide PWM signal to the driver section. PWM signal is then transferred to the switching node with  $V_{\text{IN}}$  amplitude. This waveform is filtered by the output filter.

Figure 8. PWM control loop

ΔV<sub>OSC</sub>

ΔV<sub>OSC</sub>

COMP

COMP

COMP

R

FB

R

R

OUTPUT

DIVIDER

The converter transfer function is the small signal transfer function between the voltage at the output node of the EA (COMP) and  $V_{OUT}$ . This function has a double pole (complex conjugate) at frequency  $F_{LC}$  depending on the L-C<sub>OUT</sub> resonance and a zero at  $F_{ESR}$

L6726A Application details

> depending on the output capacitor ESR. The DC gain of the modulator is simply the input voltage V<sub>IN</sub> divided by the peak-to-peak oscillator voltage ΔV<sub>OSC</sub>.

V<sub>OUT</sub> is scaled and transferred to FB node by the output resistor divider.

The compensation network closes the loop joining FB and COMP node with transfer function ideally equal to -gm·Z<sub>F</sub>.

Compensation goal is to close the control loop assuring high DC regulation accuracy, good dynamic performances and stability. To achieve this, the overall loop needs high DC gain, high bandwidth and good phase margin.

High DC gain is achieved giving an integrator shape to compensation network transfer function. Loop bandwidth (F<sub>0dB</sub>) can be fixed choosing the right R<sub>F</sub>; however, for stability, it should not exceed  $F_{SW}/2\pi$ . To achieve a good phase margin, the control loop gain has to cross 0 dB axis with -20 dB/decade slope.

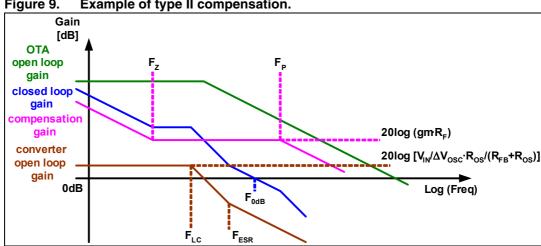

As an example, Figure 9 shows an asymptotic bode plot of a type II compensation.

Figure 9. Example of type II compensation.

Open loop converter singularities:

a)

$$F_{LC} = \frac{1}{2\pi \sqrt{L \cdot C_{OUT}}}$$

b)

$$F_{ESR} = \frac{1}{2\pi \cdot C_{OUT} \cdot ESR}$$

Compensation Network singularities frequencies:

a)

$$F_Z = \frac{1}{2\pi \cdot R_F \cdot C_F}$$

b)

$$F_{P} = \frac{1}{2\pi \cdot R_{F} \cdot \left(\frac{C_{F} \cdot C_{P}}{C_{F} + C_{P}}\right)}$$

L6726A Application details

Type II compensation relies on the zero introduced by the output capacitors bank to achieve stability. Thus, a needed condition to successfully apply type II compensation is  $F_{ESR} < F_{0dB}$  (usually true when output capacitor is based on electrolytic, aluminium electrolytic or tantalum capacitor).

To define compensation network components values, the below suggestions may be followed:

a) Set the output resistor divider in order to obtain the desired output voltage:

$$\frac{R_{FB}}{R_{OS}} = \frac{V_{OUT}}{V_{RFF}} - 1$$

Usual values of R<sub>FB</sub> and R<sub>OS</sub> ranges from some hundreds of  $\Omega$  to some k $\Omega$  (consider trade-off between power dissipation on output resistor divider and offset introduced by FB bias current).

If the desired output voltage is equal to internal reference,  $R_{OS}$  has to be NC and FB pin can be directly connected to  $V_{OUT}$ .

b) Set R<sub>F</sub> in order to obtain the desired closed loop regulator bandwidth according to the approximated formula:

$$\mathsf{R}_\mathsf{F} = \frac{\mathsf{F}_{\mathsf{0dB}} \cdot \mathsf{F}_{\mathsf{ESR}}}{\mathsf{F}_{\mathsf{LC}}^2} \cdot \frac{\Delta \mathsf{V}_{\mathsf{OSC}}}{\mathsf{V}_{\mathsf{IN}}} \cdot \frac{\mathsf{1}}{\mathsf{gm}} \cdot \frac{\mathsf{R}_{\mathsf{FB}} + \mathsf{R}_{\mathsf{OS}}}{\mathsf{R}_{\mathsf{OS}}}$$

If  $V_{OUT} = V_{REF}$  just consider  $(R_{FB}+R_{OS})/R_{OS}$  factor equal to 1.

c) Place F<sub>Z</sub> below F<sub>LC</sub> (typically 0.2·F<sub>LC</sub>):

$$C_{F} = \frac{5}{2\pi \cdot R_{F} \cdot F_{LC}}$$

d) Place  $F_P$  at  $0.5 \cdot F_{SW}$

$$C_{P} = \frac{C_{F}}{\pi \cdot R_{F} \cdot C_{F} \cdot F_{SW} - 1} \cong \frac{1}{\pi \cdot R_{F} \cdot F_{SW}}$$

- e) Check that compensation network gain is lower than open loop transconductance EA gain.

- f) Estimate phase margin obtained (it should be greater than 45°) and repeat, modifying parameters, if necessary.

Application details L6726A

#### 8.3 Soft-start time calculation

To calculate SS time ( $t_{SS}$ ), the following approximated equation can be used ( $C_P << C_F$ ):

$$t_{SS} = \frac{C_F \cdot \frac{V_{OUT}}{V_{IN}} \cdot \Delta V_{OSC}}{I_{SS}}$$

The previous equation refers only to  $V_{OUT}$  ramp up time. The time elapsed from the end of OC setting phase or COMP set free to the beginning of  $V_{OUT}$  ramp up (see *Figure 6*) can be approximately estimated as follow:

$$t_{delay} = \frac{C_F \cdot 0.8V}{I_{SS}}$$

Once calculated  $t_{SS}$ , also the current delivered by the converter during SS to charge the output capacitor bank can be estimated:

$$I_{startup} = \frac{C_{OUT} \cdot V_{OUT}}{t_{SS}}$$

#### 8.4 Layout guidelines

L6726A provides control functions and high current integrated drivers to implement high-current step-down DC-DC converters. In this kind of application, a good layout is very important.

The first priority when placing components for these applications has to be reserved to the power section, minimizing the length of each connection and loop as much as possible. To minimize noise and voltage spikes (EMI and losses) power connections (highlighted in *Figure 10*) must be a part of a power plane and anyway realized by wide and thick copper traces: loop must be anyway minimized. The critical components, i.e. the power MOSFETs, must be close one to the other. The use of multi-layer printed circuit board is recommended.

Figure 10. Power connections (heavy lines)

The input capacitance ( $C_{\text{IN}}$ ), or at least a portion of the total capacitance needed, has to be placed close to the power section in order to eliminate the stray inductance generated by the copper traces. Low ESR and ESL capacitors are preferred, MLCC are suggested to be connected near the HS drain.

Use proper number of vias when power traces have to move between different planes on the PCB in order to reduce both parasitic resistance and inductance. Moreover, reproducing the same high-current trace on more than one PCB layer will reduce the parasitic resistance associated to that connection.

L6726A Application details

Connect output bulk capacitors ( $C_{OUT}$ ) as near as possible to the load, minimizing parasitic inductance and resistance associated to the copper trace, also adding extra decoupling capacitors along the way to the load when this results in being far from the bulk capacitors bank.

Gate traces and phase trace must be sized according to the driver RMS current delivered to the power MOSFET. The device robustness allows managing applications with the power section far from the controller without losing performances. Anyway, when possible, it is recommended to minimize the distance between controller and power section. See *Figure 11* for drivers current paths.

Small signal components and connections to critical nodes of the application, as well as bypass capacitors for the device supply, are also important. Locate bypass capacitor (VCC and Bootstrap capacitor) and loop compensation components as close to the device as practical. For over current programmability, place  $R_{OCSET}$  close to the device and avoid leakage current paths on LGATE / OC pin, since the internal current source is only 10  $\mu A$

Systems that do not use Schottky diode in parallel to the Low-Side MOSFET might show big negative spikes on the PHASE pin. This spike must be limited within the absolute maximum ratings (for example, adding a gate resistor in series to HS MOSFET gate, or a phase resistor in series to PHASE pin), as well as the positive spike, but has an additional consequence: it causes the bootstrap capacitor to be over-charged. This extra-charge can cause, in the worst case condition of maximum input voltage and during particular transients, that boot-to-phase voltage overcomes the absolute maximum ratings also causing device failures. It is then suggested in this case to limit this extra-charge by adding a small resistor in series to the bootstrap diode (R<sub>D</sub> in *Figure 1*).

LS DRIVER

LS MOSFET

HS DRIVER

HS MOSFET

HS MOSFET

HS MOSFET

BOOT

GRATE

GRATE

GRATE

HS MOSFET

HS MOSFET

HS MOSFET

HS MOSFET

BOOT

GRATE

GRATE

HS MOSFET

HS MOSFE

Figure 11. Drivers turn-on and turn-off paths

Application details L6726A

#### 8.5 Embedding L6726A-based VRs...

20/35

When embedding the VR into the application, additional care must be taken since the whole VR is a switching DC/DC regulator and the most common system in which it has to work is a digital system such as MB or similar. In fact, latest MBs have become faster and more powerful: high speed data busses are more and more common and switching-induced noise produced by the VR can affect data integrity if additional layout guidelines are not followed. Few easy points must be considered mainly when routing traces in which switching high currents flow (switching high currents cause voltage spikes across the stray inductance of the traces causing noise that can affect the near traces):

When reproducing high current path on internal layers, keep all layers the same size in order to avoid "surrounding" effects that increase noise coupling.

Keep safe guard distance between high current switching VR traces and data busses, especially if high-speed data busses, to minimize noise coupling.

Keep safe guard distance or filter properly when routing bias traces for I/O sub-systems that must walk near the VR.

Possible causes of noise can be located in the PHASE connections, MOSFETs gate drive and Input voltage path (from input bulk capacitors and HS drain). Also GND connection must be considered if not insisting on a power ground plane. These connections must be carefully kept far away from noise-sensitive data busses.

Since the generated noise is mainly due to the switching activity of the VR, noise emissions depend on how fast the current switches. To reduce noise emission levels, it is also possible, in addition to the previous guidelines, to reduce the current slope and thus to increase the switching times: this will cause, as a consequence of the higher switching time, an increase in switching losses that must be considered in the thermal design of the system.

# 9 Application Information

#### 9.1 Output inductor

Inductor value is defined by a compromise between dynamic response, ripple, efficiency, cost and size. Usually, inductance is calculated to maintain inductor ripple current ( $\Delta I_L$ ) between 20% and 30% of maximum output current. Given the switching frequency ( $F_{SW}$ ), the input voltage ( $V_{IN}$ ), the output voltage ( $V_{OUT}$ ) and the desired ripple current ( $\Delta I_L$ ), inductance can be calculated as follows:

$$L = \frac{V_{IN} - V_{OUT}}{F_{SW} \cdot \Delta I_{I}} \cdot \frac{V_{OUT}}{V_{IN}}$$

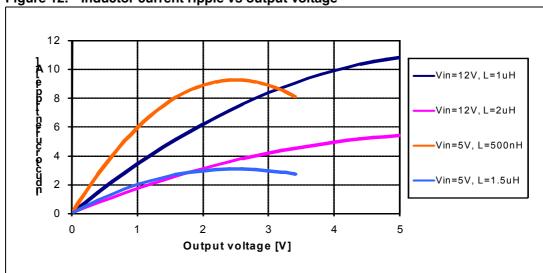

Figure 12 shows the ripple current vs. the output voltage for different inductance, with  $V_{IN} = 5 \text{ V}$  and  $V_{IN} = 12 \text{ V}$ .

Increasing inductance reduces inductor ripple current (and output voltage ripple accordingly) but, at the same time, increases the converter response time to load transients. Higher inductance means that the inductor needs more time to change its current from initial to final value. Until the inductor has not finished its charging, the additional output current is supplied by output capacitors. Minimizing the response time lead to minimize the output capacitance required. If the compensation network is designed with high bandwidth, during an heavy load transient the device is able to saturate duty cycle (0% or 80%). When this condition is reached, the response time is limited only by the time required to charge the inductor.

Figure 12. Inductor current ripple vs output voltage

#### 9.2 Output capacitors

Output capacitors choice depends on the application constraints in point of output voltage ripple and output voltage deviation during a load transient.

During steady-state conditions, the output voltage ripple is influenced by ESR and capacitance of the output capacitors as follows:

$$\Delta V_{OUT ESR} = \Delta I_{L} \cdot ESR$$

$$\Delta V_{OUT\_C} = \Delta I_L \cdot \frac{1}{8 \cdot C_{OUT} \cdot F_{SW}}$$

Where  $\Delta I_L$  is the inductor current ripple. These contribution are not in phase, so total ripple will be lower than the sum of their moduli. Even ESL and board parasitic inductance can contribute significantly to output ripple.

During a load variation, the output capacitors supply to the load the additional current or absorb the current in excess delivered by the inductor until converter reaction is completed. In fact, even if the controller react immediately to the load transient saturating the duty cycle to 80% or 0%, the current slew rate is limited by the inductance. At first approximation, output voltage drop, based on ESR and capacitor charge/discharge and considering an ideal load-step, can be estimated as follows:

$$\Delta V_{OUT ESR} = \Delta I_{OUT} \cdot ESR$$

$$\Delta V_{OUT\_C} = \frac{L \cdot \Delta I_{OUT}^2}{2 \cdot C_{OUT} \cdot \Delta V_L}$$

Where  $\Delta V_L$  is the voltage applied to the inductor during the transient ( $D_{MAX} \cdot V_{IN} - V_{OUT}$  for the load appliance or  $V_{OUT}$  for the load removal).

MLCC capacitors typically have low ESR to minimize the ripple but also have low capacitance that do not minimize the capacitive voltage deviation during load transient. On the contrary, electrolytic capacitors usually have higher capacitance to minimize capacitive voltage deviation during load transient, but also higher ESR value resulting in higher ripple voltage and resistive voltage drop. For these reasons, a mix between electrolytic and MLCC capacitor is usually suggested to minimize ripple as well as reducing voltage deviation in dynamic conditions.

## 9.3 Input capacitors

The input capacitor bank is designed mainly to stand input rms current, which depends on output current (I<sub>OUT</sub>) and duty-cycle (D) for the regulation as follows:

$$I_{rms} = I_{OUT} \cdot \sqrt{D \cdot (1 - D)}$$

The equation reaches its maximum value,  $I_{OUT}/2$ , when D = 0.5. Losses depend on input capacitor ESR:

$$P = ESR \cdot I_{rms}^{2}$$

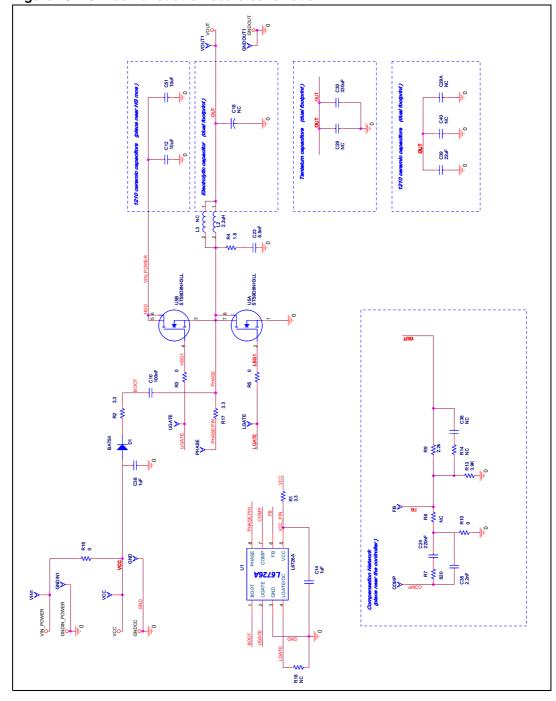

### 10 20 A demonstration board

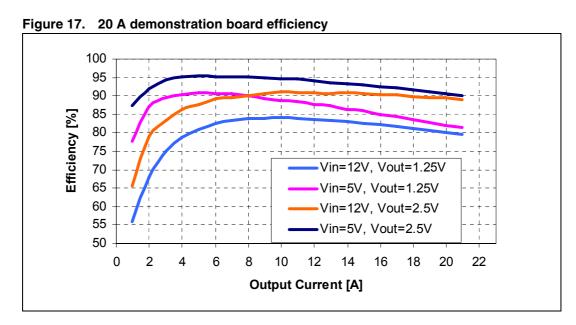

L6726A demonstration board realizes on a four-layer PCB a step-down DC/DC converter and shows the operation of the device in a general purpose application. Input voltage can range from 5 V to 12 V bus. Output voltage is programmed to 1.25 V. The voltage regulator can deliver up to 20 A output current. The switching frequency is 270 kHz.

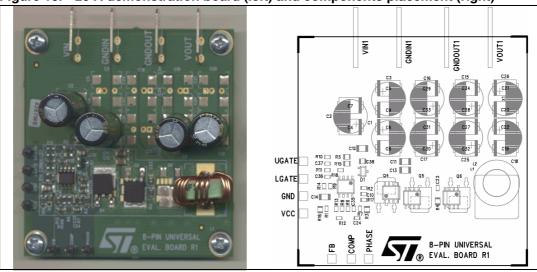

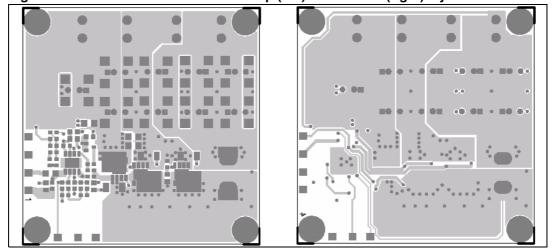

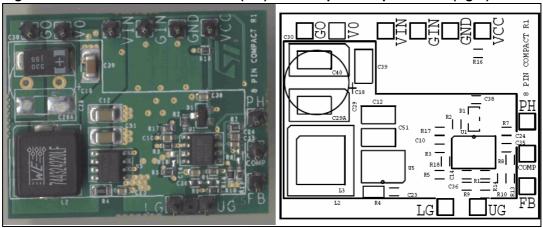

Figure 13. 20 A demonstration board (left) and components placement (right)

Figure 14. 20 A demonstration board top (left) and bottom (right) layers

20 A demonstration board L6726A

Figure 15. 20 A demonstration board inner layers

24/35

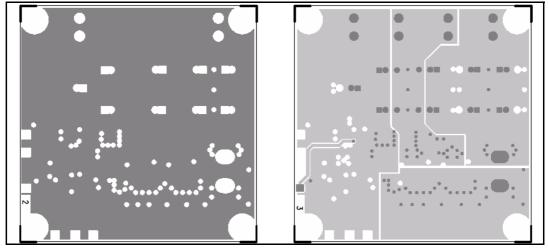

Figure 16. 20 A demonstration board schematic

**577**

Table 6. 20 A demonstration board - bill of material

| Qty       | Reference   | Description                                                       | Package          |  |  |  |

|-----------|-------------|-------------------------------------------------------------------|------------------|--|--|--|

| Capac     | Capacitors  |                                                                   |                  |  |  |  |

| 2         | C1, C2      | Electrolytic Cap 1800 μF 16 V<br>Nippon Chemi-Con KZJ or KZG      |                  |  |  |  |

| 1         | C10         | MLCC, 100 nF, 25 V, X7R                                           | SMD0603          |  |  |  |

| 3         | C11 to C13  | MLCC, 4.7 μF, 16 V, X5R<br>Murata GRM31CR61C475MA01               | SMD1206          |  |  |  |

| 2         | C14, C38    | MLCC, 1 μF, 16 V, X7R                                             | SMD0805          |  |  |  |

| 2         | C18, C25    | Electrolytic Cap 2200 μF 6.3 V<br>Nippon Chemi-Con KZJ or KZG     | Radial 10 x 20mm |  |  |  |

| 1         | C23         | MLCC, 6.8 nF, X7R                                                 |                  |  |  |  |

| 1         | C24         | MLCC, 68 nF, X7R                                                  | SMD0603          |  |  |  |

| 1         | C35         | MLCC, 470 pF, X7R                                                 | ]                |  |  |  |

| Resistors |             |                                                                   |                  |  |  |  |

| 3         | R1, R2, R17 | Resistor, 3R3, 1/16 W, 1%                                         | SMD0603          |  |  |  |

| 3         | R3, R5, R16 | Resistor, 0R, 1/8 W, 1%                                           | CMDOOGE          |  |  |  |

| 1         | R4          | Resistor, 1R8, 1/8 W, 1%                                          | - SMD0805        |  |  |  |

| 2         | R11, R12    | Resistor, 0R, 1/16 W, 1%                                          |                  |  |  |  |

| 1         | R9          | Resistor, 2K2, 1/16 W, 1%                                         | ]                |  |  |  |

| 1         | R13         | Resistor, 3K9, 1/16 W, 1%                                         | SMD0603          |  |  |  |

| 1         | R7          | Resistor, 2K, 1/16 W, 1%                                          | CIVIDOGGG        |  |  |  |

| 1         | R18         | Resistor, 20K, 1/16 W, 1%                                         |                  |  |  |  |

| Induct    | or          | ·                                                                 | •                |  |  |  |

| 1         | L1          | Inductor, 1.25 μH, T60-18, 6Turns<br>Easymagnet AP106019006P-1R1M | na               |  |  |  |

| Active    | components  |                                                                   | •                |  |  |  |

| 1         | D1          | Diode, 1N4148 or BAT54                                            | SOT23            |  |  |  |

| 1         | Q5          | STD70NH02LT4                                                      | DDACK            |  |  |  |

| 1         | Q6          | STD95NH02LT4                                                      | DPACK            |  |  |  |

| 1         | U1          | Controller, L6726A                                                | SO8              |  |  |  |

|           | •           | •                                                                 | •                |  |  |  |

#### 10.1 Board description

#### 10.1.1 Power input (VIN)

This is the input voltage for the power conversion. The high-side MOSFET drain is connected to this input. Supply must be compliant with VIN recommended operating conditions and capacitors rating.

If VIN voltage is compliant also to VCC range listed in recommended operating conditions, it can supply also the device through R16 resistor.

#### 10.1.2 Power output (VOUT)

This is the output voltage of the power conversion. The output voltage is programmed to 1.25 V. It can be changed by replacing R13 (adjusting of compensation network may be needed). R18 allows to adjust OCP threshold.

#### 10.1.3 IC additional supply (VCC)

The controller can be supplied separately from the power conversion through VCC input. In this case, to separate VCC from VIN, R16 resistor must be removed.

#### 10.1.4 Test points

The following test points are provided to allow easy probing of important signals:

- COMP: Output of the error amplifier;

- FB: Inverting input of the error amplifier;

- PH: Phase pin of the device;

- LG: Low-side gate pin of the device;

- UG: High-side gate pin of the device.

#### 10.1.5 Demonstration board efficiency

5 A demonstration board L6726A

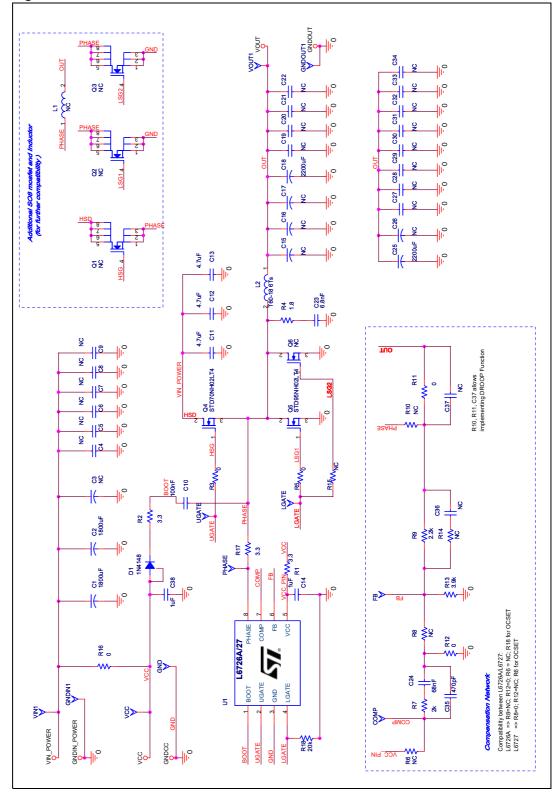

### 11 5 A demonstration board

L6726A demonstration board realizes on a two-layer PCB a step-down DC/DC converter and shows the operation of the device in a general-purpose low-current application. Input voltage can range from 5 V to 12 V bus. Output voltage is programmed at 1.25 V. The application can deliver an output current in excess of 5 A. The switching frequency is 270 kHz.

Figure 18. 5 A demonstration board (left) and components placement (right)

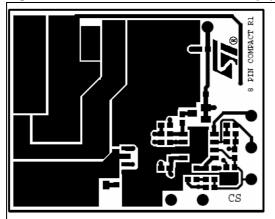

Figure 19. 5 A demonstration board top (left) and bottom (right) layers

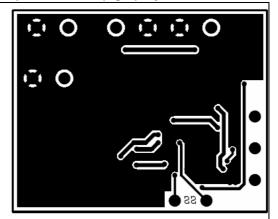

Figure 20. 5 A demonstration board schematic

5 A demonstration board L6726A

Table 7. 5 A demonstration board - bill of material

| Qty       | Reference Description   |                                                     | Package |  |

|-----------|-------------------------|-----------------------------------------------------|---------|--|

| Capacitor | s                       |                                                     |         |  |

| 2         | C12, C51                | SMD1206                                             |         |  |

| 1         | C10                     | MLCC, 100nF, 25V, X7R                               | SMD0603 |  |

| 2         | C14, C38                | MLCC, 1 μF, 16 V, X7R                               | SMD0805 |  |

| 1         | C39                     | MLCC, 22 μF, 6.3 V, X5R<br>Murata GRM31CR60J226ME19 | SMD1206 |  |

| 1         | C30                     | 330 $\mu$ F, 6.3 V, 40 m $\Omega$<br>Sanyo 6TPB330M | SMD7343 |  |

| 1         | C23                     | MLCC, 6.8 nF, X7R                                   |         |  |

| 1         | C24                     | MLCC, 220 nF, X7R                                   | SMD0603 |  |

| 1         | 1 C35 MLCC, 2.2 nF, X7R |                                                     |         |  |

| Resistors |                         |                                                     |         |  |

| 1         | R4                      | Resistor, 1R8, 1/8 W, 1%                            | SMD0805 |  |

| 4         | R3, R5, R10, R16        | Resistor, 0R, 1/16 W, 1%                            | CMDocos |  |

| 3         | R1, R2, R17             | Resistor, 3R3, 1/16 W, 1%                           | SMD0603 |  |

| 1         | R9                      | Resistor, 2K2, 1/16 W, 1%                           |         |  |

| 1         | R13                     | Resistor, 3K9, 1/16 W, 1%                           | SMD0603 |  |

| 1         | R7                      | Resistor, 820R, 1/16 W, 1%                          |         |  |

| Inductor  |                         |                                                     |         |  |

| 1         | L1                      | Inductor, 2.20 μH,<br>Wurth 744324220LF             | na      |  |

| Active Co | mponents                |                                                     |         |  |

| 1         | D1                      | Diode, BAT54                                        | SOT23   |  |

| 1         | Q5                      | Mosfet, STS9D8NH3LL                                 | SO8     |  |

| 1         | U1                      | Controller, L6726A                                  | SO8     |  |

## 11.1 Board description

#### 11.1.1 Power input (VIN)

This is the input voltage for the power conversion. The high-side MOSFET drain is connected to this input. Supply must be compliant with VIN recommended operating conditions and capacitors rating.

If VIN voltage is compliant also to VCC range listed in recommended operating conditions, it can supply also the device through R16 resistor.

#### 11.1.2 Power output (VOUT)

This is the output voltage of the power conversion. The output voltage is programmed to 1.25 V. It can be changed by replacing R13 (adjusting of compensation network may be needed). Adding R18 allows to adjust OCP threshold.

#### 11.1.3 IC additional supply (VCC)

The controller can be supplied separately from the power conversion through VCC input. In this case, to separate VCC from VIN, R16 resistor must be removed.

#### 11.1.4 Test points

The following test points are provided to allow easy probing of important signals:

- COMP: output of the error amplifier;

- FB: inverting input of the error amplifier;

- PH: Phase pin of the device;

- LG: Low-side gate pin of the device;

- UG: High-side gate pin of the device.

#### 11.1.5 Demonstration board efficiency

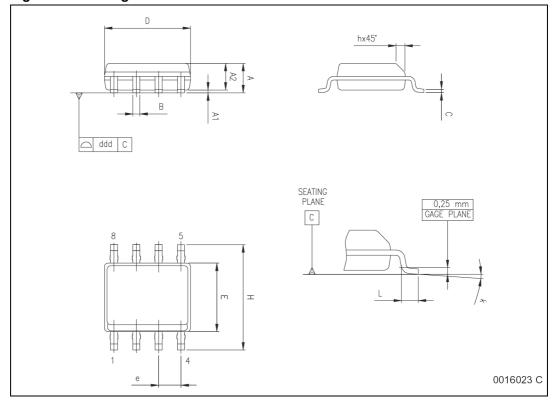

# 12 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

32/35 Doc ID 12754 Rev 4

Table 8. SO-8 mechanical data

| Dim   |      | mm.  |            |           | inch  |       |  |

|-------|------|------|------------|-----------|-------|-------|--|

| Dim.  | Min  | Тур  | Max        | Min       | Тур   | Max   |  |

| Α     | 1.35 |      | 1.75       | 0.053     |       | 0.069 |  |

|       |      |      |            |           |       |       |  |

| A1    | 0.10 |      | 0.25       | 0.004     |       | 0.010 |  |

| A2    | 1.10 |      | 1.65       | 0.043     |       | 0.065 |  |

| В     | 0.33 |      | 0.51       | 0.013     |       | 0.020 |  |

| С     | 0.19 |      | 0.25       | 0.007     |       | 0.010 |  |

| D (1) | 4.80 |      | 5.00       | 0.189     |       | 0.197 |  |

| Е     | 3.80 |      | 4.00       | 0.15      |       | 0.157 |  |

| е     |      | 1.27 |            |           | 0.050 |       |  |

| Н     | 5.80 |      | 6.20       | 0.228     |       | 0.244 |  |

| h     | 0.25 |      | 0.50       | 0.010     |       | 0.020 |  |

| L     | 0.40 |      | 1.27       | 0.016     |       | 0.050 |  |

| k     |      |      | 0° (min.), | 8° (max.) |       |       |  |

| ddd   |      |      | 0.10       |           |       | 0.004 |  |

<sup>1.</sup> D and F does not include mold flash or protrusions. Mold flash or potrusions shall not exceed 0.15mm (.006inch) per side.

Figure 22. Package dimensions

Revision history L6726A

# 13 Revision history

Table 9. Document revision history

| Date        | Revision | Changes                                                                                                    |

|-------------|----------|------------------------------------------------------------------------------------------------------------|

| 16-Oct-2006 | 1        | Initial release.                                                                                           |

| 26-Oct-2006 | 2        | Mechanical data dimensions updated                                                                         |

| 30-Jul-2007 | 3        | Updated Figure 1 on page 4, tables 2, 3, 4, 5                                                              |

| 23-Mar-2010 | 4        | Added:<br>Section 9 on page 21, Section 10 on page 23, Section 11 on page 28<br>Updated: Table 5 on page 7 |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

STMicroelectronics: