Product data sheet

# **General description**

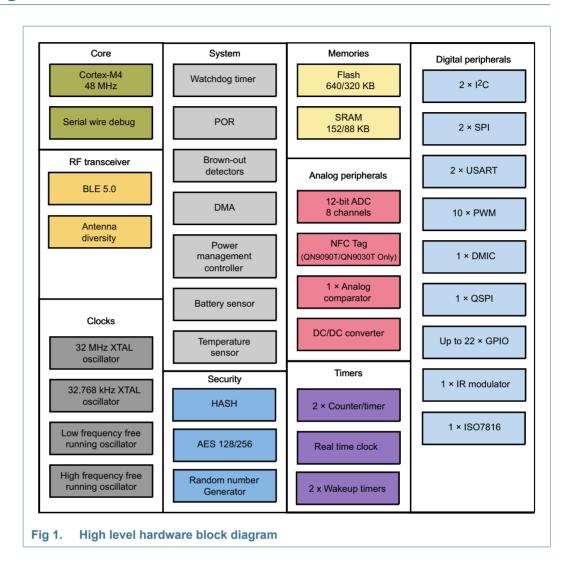

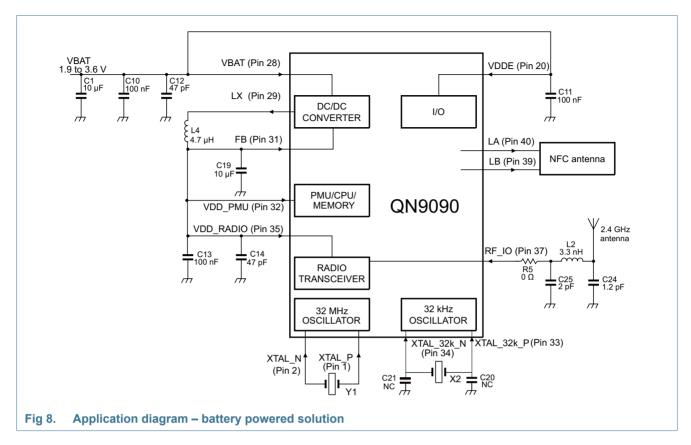

The QN9090 and QN9090T (called QN9090 throughout this document) are ultra-low power, high performance Arm® Cortex®-M4 based wireless microcontrollers supporting Bluetooth Low Energy 5.0 to facilitate the development of Bluetooth Low Energy applications.

The QN9090, supporting eight simultaneous connections, includes a 2.4 GHz Bluetooth Low Energy 5 compliant transceiver and a comprehensive mix of analog and digital peripherals. Ultra-low current consumption in both radio receive and transmit modes and also in the power down modes allow use of coin cell batteries.

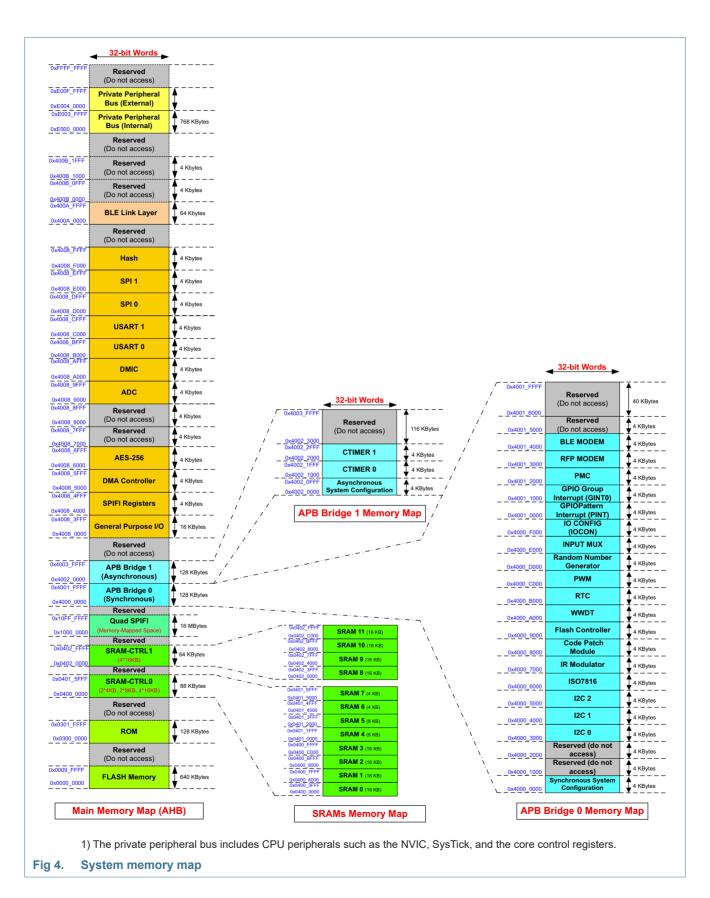

The product has 640 KB embedded Flash, 152 KB RAM memory. The embedded flash can support Over The Air (OTA) code download to applications. The devices include 10-channel PWM, two timers, one RTC/alarm timer, a Windowed Watchdog Timer (WWDT), two USARTs, two SPI interfaces, two I2C interfaces, a DMIC subsystem with dual-channel PDM microphone interface with voice activity detector, one 12-bit ADC, temperature sensor and comparator.

The QN9090T variant has an internal NFC tag with connections to the external NFC antenna.

The QN9030 variant has the same functionality as the QN9090 except for reduced memory sizes of 320 KB embedded Flash, 88 KB RAM. The QN9030T variant has the functionality of the QN9030 with the addition of an embedded NFC tag.

The Arm Cortex-M4 is a 32-bit core that offers system enhancements such as low power consumption, enhanced debug features, and a high level support of the block integration. The Arm Cortex-M4 CPU, operates at up to 48 MHz.

#### Features and benefits 2.

### 2.1 Benefits

- Very low current solution for long battery life

- Single chip device to run stack and application

- System BOM is low in component count and cost

- Flexible sensor interfacing

- Embedded NTAG on QN9090T and QN9030T devices

- Package

- ♦ 6 × 6 mm HVQFN40, 0.5 mm pitch

- ◆ Lead-free and RoHS compliant

- Junction temperature range: -40 °C to +125 °C

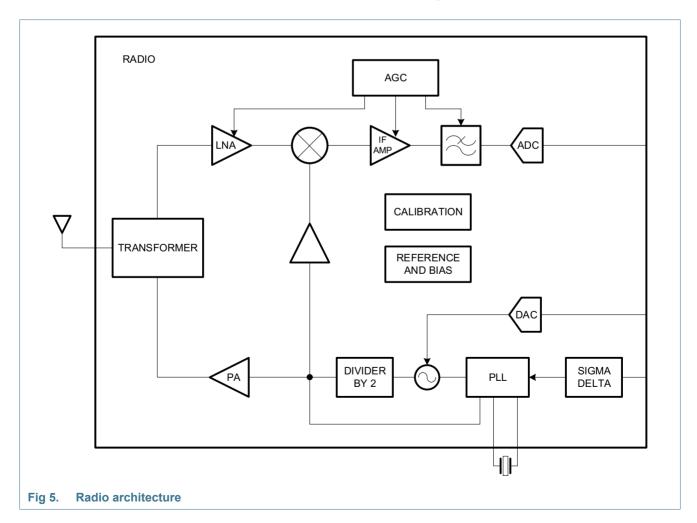

#### 2.2 Radio features

- 2.4 GHz Bluetooth Low Energy 5.0 compliant

- Receiver current 4.3 mA

- Bluetooth Low Energy 5.0 2Mbps high data rate

- Bluetooth Low Energy Receiver sensitivity -97 dBm

- Improved co-existence with WiFi

- Configurable transmit power up to +11 dBm, with 46 dB range

- Transmit power / current +10 dBm / 20.3 mA

- Transmit power / current +3 dBm / 9.4 mA

- Transmit power / current 0 dBm / 7.4 mA

- 1.9 V to 3.6 V supply voltage

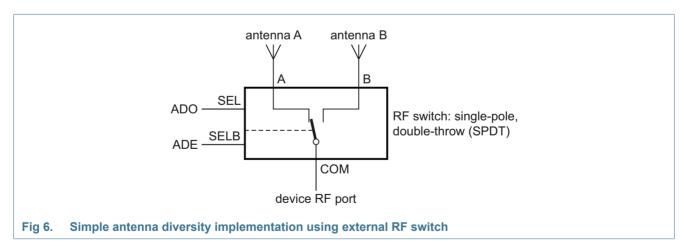

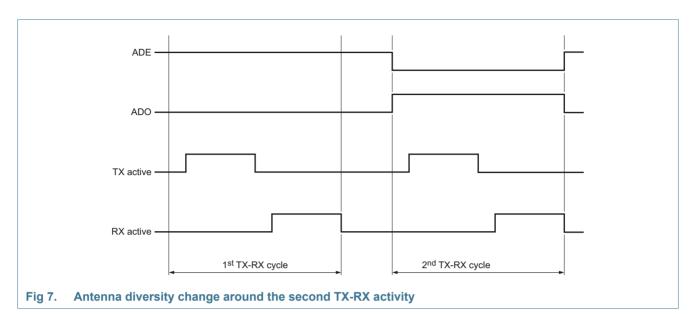

- Antenna Diversity control

- 32 MHz XTAL cell with internal capacitors, able with suitable external XTAL to meet the required accuracy for radio operation over the operating conditions

- Integrated RF balun

- Integrated ultra Low-power sleep oscillator

- Deep Power-down current 350 nA (with wake-up on IO)

- 128-bit, 192-bit or 256-bit AES security processor

#### 2.3 Microcontroller features

- Application CPU, Arm Cortex-M4 CPU:

- ◆ Arm Cortex-M4 processor, running at a frequency of up to 48 MHz.

- Arm built-in Nested Vectored Interrupt Controller (NVIC)

- Memory Protection Unit (MPU)

- ◆ Non-maskable Interrupt (NMI) with a selection of sources

- Serial Wire Debug (SWD) with 8 breakpoints and 4 watchpoints

- System tick timer

- Includes Serial Wire Output for enhanced debug capabilities.

- On-Chip memory

- ◆ 640 KB flash (320 KB for QN9030)

- ◆ 152 KB SRAM (88 KB for QN9030)

- 12 MHz to 48 MHz system clock speed for low-power

- 2 x I2C-bus interface, operate as either master or slave

- 10 x PWM

- 2 x Low-power timers

- 2 x USART, one with flow control

- 2 x SPI-bus, master or slave

- 1 x PDM digital audio interface with a hardware based voice activity detector to reduce power consumption in voice applications. Support for dual-channel microphone interface, flexible decimators, 16 entry FIFOs and optional DC blocking.

- 19-channel DMA engine for efficient data transfer between peripherals and SRAM, or SRAM to SRAM. DMA can operate with fixed or incrementing addresses. Operations can be chained together to provide complex functionality with low CPU overhead.

- Up to four GPIOs can be selected as pin interrupts (PINT), triggered by rising, falling or both input edges.

- Two GPIO grouped interrupts (GINT) enable an interrupt based on a logical (AND/OR) combination of input states.

- 32-bit Real Time clock (RTC) with 1 s resolution. A timer in the RTC can be used to wake from Sleep, Deep-sleep and Power-down, with 1 ms resolution

- Voltage Brown Out with 8 programmable thresholds

- 8-input 12-bit ADC, 190 ksamples/s (Max.). HW support for continuous operation or single conversions, single or multiple inputs can be sampled within a sequence. DMA operation can be linked to achieve low overhead operation.

- 1 x analog comparator

- Battery and temperature sensors

- Watchdog timer and POR

- Standby power controller

- Up to 22 Digital IOs (DIO)

- 1 x Quad SPIFI for accessing an external flash device

- Integrated NTAG I<sup>2</sup>C plus device, NFC Forum Type 2, on QN9090T and QN9030T only

- Random Number Generator engine

- AES engine AES-128 to 256

- Hash hardware accelerator supporting SHA-1, SHA-256

- EFuse:

- 128-bit random AES key

- Configuration modes

- Trimming

- ISO7816 smart card digital interface which with a suitable external analogue device can operate as a smart card reader

### 2.4 Low power features

- Sleep mode supported, the CPU in low power state waiting for interrupt

- Deep-sleep mode supported, the CPU in low power state waiting for interrupt, but extra functionality disabled or in low power state compared to sleep mode

- Power Down mode, main functionality powered down, wakeup possible from IOs, wakeup possible from some peripherals (I2C, USART, SPI) in a limited function mode and low power timers

- Deep -power down, very low power state with option of wake-up triggered by IOs, 350 nA

- 41-bit and 28-bit Low power timers can run in power down mode, clocked by 32 kHz FRO or 32 kHz XTAL. Timers can run for over one year or 2 days

- Dedicated low power timer, clocked by 32 kHz XTAL, closely integrated with the Bluetooth Low Energy link layer to maintain the timing reference through power-down cycles

# 3. Applications

Bluetooth Low Energy 5.0 networks

- Robust and secure Low-power wireless applications

- Lighting and Home automation

- Toys and gaming peripherals

- Activity and wellness monitors

- Personal healthcare devices

- Wireless occupancy sensors

# 4. Ordering information

Table 1. Ordering information

| Type number | Package |                                                                      |          |  |  |  |

|-------------|---------|----------------------------------------------------------------------|----------|--|--|--|

|             | Name    | Description                                                          | Version  |  |  |  |

| QN9090HN    | HVQFN40 | Plastic thermal enhanced very thin quad                              | SOT618-1 |  |  |  |

| QN9090THN   |         | flat package; no leads; 40 terminals; body $6\times 6\times 0.85$ mm |          |  |  |  |

| QN9030HN    |         |                                                                      |          |  |  |  |

| QN9030THN   |         |                                                                      |          |  |  |  |

Table 2. Ordering information details

| Type number | Flash size | SRAM size | NTAG |

|-------------|------------|-----------|------|

| QN9090HN    | 640 KB     | 152 KB    | no   |

| QN9090THN   |            |           | yes  |

| QN9030HN    | 320 KB     | 88 KB     | no   |

| QN9030THN   |            |           | yes  |

# 5. Marking

Table 3. Marking codes

| Type number | Marking code |

|-------------|--------------|

| QN9090HN    | QN9090       |

| QN9090THN   | QN9090T      |

| QN9030HN    | QN9030       |

| QN9030THN   | QN9030T      |

#### **Block diagram** 6.

# 7. Pinning information

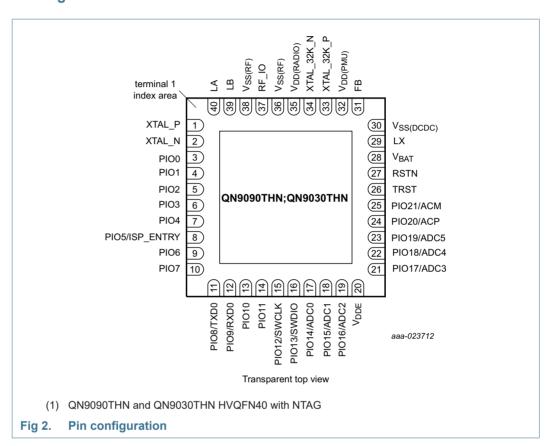

### 7.1 HVQFN40 - with NTAG

# 7.1.1 Pinning

# 7.1.2 Pin description

Table 4. Pin descriptions

| Symbol | Pin  | Туре | Default at reset                                                | Description                                                                                             |

|--------|------|------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| XTAL_P | 1    |      |                                                                 | System crystal oscillator 32 MHz                                                                        |

| XTAL_N | 2    |      |                                                                 | System crystal oscillator 32 MHz                                                                        |

| PIO0   | 3 IO | Ю    | GPIO0[1]                                                        | GPIO0 — General Purpose digital Input/Output 0                                                          |

|        |      |      |                                                                 | <b>USART0_SCK</b> — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 0 - synchronous clock    |

|        |      |      |                                                                 | <b>USART1_TXD</b> — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 1 - transmit data output |

|        |      |      |                                                                 | PWM0 — Pulse Width Modulator output 0                                                                   |

|        |      |      | SPI1_SCK — Serial Peripheral Interface-bus 1 clock input/output |                                                                                                         |

|        |      |      |                                                                 | PDM0_DATA — Pulse Density Modulation Data input from digital microphone (channel 0)                     |

Table 4. Pin descriptions

| Symbol             | Pin | Туре | Default at reset          | Description                                                                                        |

|--------------------|-----|------|---------------------------|----------------------------------------------------------------------------------------------------|

| PIO1               | 4   | Ю    | GPIO1 <sup>[1]</sup>      | GPI01 — General Purpose digital Input/Output 1                                                     |

|                    |     |      |                           | <b>USART1_RXD</b> — Universal Synchronous/Asynchronous Receiver/Transmitter 1 - receive data input |

|                    |     |      |                           | PWM1 — Pulse Width Modulator output 1                                                              |

|                    |     |      |                           | SPI1_MISO — Serial Peripheral Interface-bus 1 master data input                                    |

|                    |     |      |                           | PDM0_CLK — Pulse Density Modulation Clock output to digital microphone (channel 0)                 |

| PIO2               | 5   | Ю    | GPIO2 <sup>[1]</sup>      | GPIO2 — General Purpose digital Input/Output 2                                                     |

|                    |     |      |                           | SPI0_SCK — Serial Peripheral Interface-bus 0 clock input/output                                    |

|                    |     |      |                           | PWM2 — Pulse Width Modulator output 2                                                              |

|                    |     |      |                           | SPI1_MOSI — Serial Peripheral Interface-bus 1 master output slave input                            |

|                    |     |      |                           | USART0_RXD — Universal Synchronous/Asynchronous Receiver/Transmitter 0 - receive data input        |

|                    |     |      |                           | ISO7816_RST — RST signal, output, for ISO7816 interface                                            |

|                    |     |      |                           | MCLK — External clock, can be provided to DMIC IP                                                  |

| PIO3               | 6   | Ю    | GPIO3[1]                  | GPIO3 — General Purpose digital Input/Output 3                                                     |

|                    |     |      |                           | SPI0_MISO — Serial Peripheral Interface-bus 0 master input                                         |

|                    |     |      |                           | PWM3 — Pulse Width Modulator output 3                                                              |

|                    |     |      |                           | SPI1_SSELN0 — Serial Peripheral Interface-bus 1 slave select not 0                                 |

|                    |     |      |                           | USART0_TXD — Universal Synchronous/Asynchronous Receiver/Transmitter 0 - transmit data output      |

|                    |     |      |                           | ISO7816_CLK — Clock output for ISO7816 interface                                                   |

| PIO4               | 7   | Ю    | GPIO4[1][2]               | GPIO4 — General Purpose digital Input/Output 4                                                     |

|                    |     |      |                           | SPI0_MOSI — Serial Peripheral Interface-bus 0 master output slave input                            |

|                    |     |      |                           | PWM4 — Pulse Width Modulator output 4                                                              |

|                    |     |      |                           | SPI1_SSELN1 — Serial Peripheral Interface-bus 1 slave select not 1                                 |

|                    |     |      |                           | USART0_CTS — Universal Synchronous/Asynchronous Receiver/Transmitter 0 - Clear To Send input       |

|                    |     |      |                           | ISO7816_IO — IO of ISO7816 interface                                                               |

|                    |     |      |                           | RFTX — Radio Transmit Control Output                                                               |

|                    |     |      |                           | ISP_SEL — In-System Programming Mode Selection                                                     |

| PIO5/ISP_ENTR<br>Y | 8   | Ю    | GPIO5/ISP_ENT<br>RY[1][3] | GPIO5/ISP_ENTRY — General Purpose digital Input/Output 5;<br>In-System Programming Entry           |

|                    |     |      |                           | SPI0_SSELN — Serial Peripheral Interface-bus 0 slave select not                                    |

|                    |     |      |                           | SPI1_MISO — Serial Peripheral Interface-bus 1 master data input                                    |

|                    |     |      |                           | SPI1_SSELN2 — Serial Peripheral Interface-bus 1 slave select not 2                                 |

|                    |     |      |                           | USART0_RTS — Universal Synchronous/Asynchronous Receiver/Transmitter 0 - Request To Send output    |

|                    |     |      |                           | RFRX — Radio Receiver Control Output                                                               |

Table 4. Pin descriptions

| Symbol    | Pin | Type | Default at reset | Description                                                                                            |

|-----------|-----|------|------------------|--------------------------------------------------------------------------------------------------------|

| PIO6      | 9   | Ю    | GPI06[1]         | GPIO6 — General Purpose digital Input/Output 6                                                         |

|           |     |      |                  | <b>USART0_RTS</b> — Universal Synchronous/Asynchronous Receiver/Transmitter 0 - Request to Send output |

|           |     |      |                  | CT32B1_MAT0 — 32-bit CT32B1 match output 0                                                             |

|           |     |      |                  | PWM6 — Pulse Width Modulator output 6                                                                  |

|           |     |      |                  | <b>I2C1_SCL</b> — I <sup>2</sup> C-bus 1 master/slave SCL input/output                                 |

|           |     |      |                  | <b>USART1_TXD</b> — Universal Synchronous/Asynchronous Receiver/Transmitter 1 - transmit data output   |

|           |     |      |                  | ADE — Antenna Diversity Even output                                                                    |

|           |     |      |                  | SPI0_SCK — Serial Peripheral Interface 0- synchronous clock                                            |

| PIO7      | 10  | Ю    | GPI07[1]         | GPIO7 — General Purpose digital Input/Output 7                                                         |

|           |     |      |                  | USART0_CTS — Universal Synchronous/Asynchronous Receiver/Transmitter 0 - Clear to Send input           |

|           |     |      |                  | CT32B1_MAT1 — 32-bit CT32B1 match output 1                                                             |

|           |     |      |                  | PWM7 — Pulse Width Modulator output 7                                                                  |

|           |     |      |                  | <b>I2C1_SDA</b> — I <sup>2</sup> C-bus 1 master/slave SDA input/output                                 |

|           |     |      |                  | <b>USART1_RXD</b> — Universal Synchronous/Asynchronous Receiver/Transmitter 1 - receive data input     |

|           |     |      |                  | ADO — Antenna Diversity Odd Output                                                                     |

|           |     |      |                  | SPI0_MISO — Serial Peripheral Interface-bus 0 master input                                             |

| PIO8/TXD0 | 11  | Ю    | GPIO8[1][4]      | GPIO8 — General Purpose digital Input/Output 8                                                         |

|           |     |      |                  | <b>USART0_TXD</b> — Universal Synchronous/Asynchronous Receiver/Transmitter 0 - transmit data output   |

|           |     |      |                  | CT32B0_MAT0 — 32-bit CT32B0 match output 0                                                             |

|           |     |      |                  | PWM8 — Pulse Width Modulator output 8                                                                  |

|           |     |      |                  | ANA_COMP_OUT — Analog Comparator digital output                                                        |

|           |     |      |                  | PDM1_DATA — Pulse Density Modulation Data input from digital microphone (channel 1)                    |

|           |     |      |                  | <b>SPI0_MOSI</b> — Serial Peripheral Interface-bus 0 master output slave input                         |

|           |     |      |                  | RFTX — Radio Transmit Control Output                                                                   |

| PIO9/RXD0 | 12  | Ю    | GPIO9[1][5]      | GPIO9 — General Purpose digital Input/Output 9                                                         |

|           |     |      |                  | <b>USART0_RXD</b> — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 0 - receive data input  |

|           |     |      |                  | CT32B1_CAP1 — 32-bit CT32B1 capture input 1                                                            |

|           |     |      |                  | <b>PWM9</b> — Pulse Width Modulator output 9                                                           |

|           |     |      |                  | <b>USART1_SCK</b> — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 1 - synchronous clock   |

|           |     |      |                  | PDM1_CLK — Pulse Density Modulation Clock output                                                       |

|           |     |      |                  | to digital microphone (channel 1)                                                                      |

|           |     |      |                  | SPI0_SSELN — Serial Peripheral Interface-bus 0 slave select not                                        |

|           |     |      |                  | ADO — Antenna Diversity Odd Output                                                                     |

Table 4. Pin descriptions

| Symbol      | Pin | Type | Default at reset      | Description                                                                                          |

|-------------|-----|------|-----------------------|------------------------------------------------------------------------------------------------------|

| PIO10       | 13  | Ю    | GPIO10[1]             | GPIO10 — General Purpose digital Input/Output 10                                                     |

|             |     |      |                       | CT32B0_CAP0 — 32-bit CT32B0 capture input 0                                                          |

|             |     |      |                       | <b>USART1_TXD</b> — Universal Synchronous/Asynchronous Receiver/Transmitter 1 - transmit data output |

|             |     |      |                       | RFTX — Radio Transmit Control Output                                                                 |

|             |     |      |                       | <b>I2C0_SCL</b> — I <sup>2</sup> C-bus 0 master/slave SCL input/output (open drain)                  |

|             |     |      |                       | SPI0_SCK — Serial Peripheral Interface-bus 0 clock input/output                                      |

|             |     |      |                       | <b>PDM0_DATA</b> — Pulse Density Modulation Data input from digital microphone (channel 0)           |

| PIO11       | 14  | Ю    | GPIO11 <sup>[1]</sup> | GPIO11 — General Purpose digital Input/Output 11                                                     |

|             |     |      |                       | CT32B1_CAP0 — 32-bit CT32B1 capture input 0                                                          |

|             |     |      |                       | <b>USART1_RXD</b> — Universal Synchronous/Asynchronous Receiver/Transmitter 1 - receive data input   |

|             |     |      |                       | RFRX — Radio Receiver Control Output                                                                 |

|             |     |      |                       | <b>I2C0_SDA</b> — I <sup>2</sup> C-bus 0 master/slave SDA input/output (open drain)                  |

|             |     |      |                       | <b>SPI0_MISO</b> — Serial Peripheral Interface-bus 0 master input slave output                       |

|             |     |      |                       | PDM0_CLK — Pulse Density Modulation Clock output to digital microphone (channel 0)                   |

| PIO12/SWCLK | 15  | Ю    | SWCLK                 | GPIO12 — General Purpose digital Input/Output 12                                                     |

|             |     |      |                       | SWCLK — Serial Wire Debug Clock                                                                      |

|             |     |      |                       | <b>PWM0</b> — Pulse Width Modulator output 0                                                         |

|             |     |      |                       | <b>I2C1_SCL</b> — I <sup>2</sup> C-bus 1 master/slave SCL input/output (open drain)                  |

|             |     |      |                       | <b>SPI0_MOSI</b> — Serial Peripheral Interface-bus 0 master output slave input                       |

|             |     |      |                       | ANA_COMP_OUT — Analog Comparator digital output                                                      |

|             |     |      |                       | IR_BLASTER — Infra-Red Modulator output                                                              |

| PIO13/SWDIO | 16  | Ю    | SWDIO                 | GPIO13 — General Purpose digital Input/Output 13                                                     |

|             |     |      |                       | <b>SPI1_SSELN2</b> — Serial Peripheral Interface-bus 1, slave select not 2                           |

|             |     |      |                       | SWDIO — Serial Wire Debug Input/Output                                                               |

|             |     |      |                       | PWM2 — Pulse Width Modulator output 2                                                                |

|             |     |      |                       | <b>I2C1_SDA</b> — I <sup>2</sup> C-bus 1 master/slave SDA input/output (open drain)                  |

|             |     |      |                       | SPI0_SSELN — Serial Peripheral Interface-bus 0, slave select not                                     |

Table 4. Pin descriptions

| Symbol     | Pin | Type | Default at reset      | Description                                                                                          |

|------------|-----|------|-----------------------|------------------------------------------------------------------------------------------------------|

| PIO14/ADC0 | 17  | Ю    | GPIO14[1]             | ADC0 — ADC input 0                                                                                   |

|            |     |      |                       | GPIO14 — General Purpose digital Input/Output 14                                                     |

|            |     |      |                       | <b>SPI1_SSELN1</b> — Serial Peripheral Interface-bus 1, slave select not 1                           |

|            |     |      |                       | CT32B0_CAP1 — 32-bit CT32B0 capture input 1                                                          |

|            |     |      |                       | PWM1 — Pulse Width Modulator output 1                                                                |

|            |     |      |                       | SWO — Serial Wire Output                                                                             |

|            |     |      |                       | <b>USART0_SCK</b> — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 0 - synchronous clock |

|            |     |      |                       | MCLK — External clock, can be provided to DMIC IP                                                    |

|            |     |      |                       | RFTX — Radio Transmit Control Output                                                                 |

| PIO15/ADC1 | 18  | Ю    | GPIO15[1]             | ADC1 — ADC input 1                                                                                   |

|            |     |      |                       | GPIO15 — General Purpose digital Input/Output 15                                                     |

|            |     |      |                       | SPI1_SCK — Serial Peripheral Interface-bus 1, clock input/output                                     |

|            |     |      |                       | ANA_COMP_OUT — Analog Comparator digital output                                                      |

|            |     |      |                       | PWM3 — Pulse Width Modulator output 3                                                                |

|            |     |      |                       | <b>PDM1_DATA</b> — Pulse Density Modulation Data input from digital microphone (channel 1)           |

|            |     |      |                       | I2C0_SCL — I2C-bus 0 master/slave SCL input/output (open drain)                                      |

|            |     |      |                       | RFRX — Radio Receiver Control Output                                                                 |

| PIO16/ADC2 | 19  | Ю    | GPIO16 <sup>[1]</sup> | ADC2 — ADC input 2                                                                                   |

|            |     |      |                       | GPIO16 — General Purpose digital Input/Output 16                                                     |

|            |     |      |                       | <b>SPI1_SSELN0</b> — Serial Peripheral Interface-bus 1, slave select not 0                           |

|            |     |      |                       | PWM5 — Pulse Width Modulator output 5                                                                |

|            |     |      |                       | PDM1_CLK — Pulse Density Modulation Clock output to digital microphone (channel 1)                   |

|            |     |      |                       | SPIFI_CSN — Quad-SPI Chip Select Not, output                                                         |

|            |     |      |                       | ISO7816_RST — RST signal, output, for ISO7816 interface                                              |

|            |     |      |                       | I2C0_SDA — I2C-bus 0 master/slave SDA input/output (open drain)                                      |

| $V_{DDE}$  | 20  | Р    |                       | V <sub>DDE</sub> — Supply voltage for IO                                                             |

| PIO17/ADC3 | 21  | Ю    | GPIO17[1]             | ADC3 — ADC input 3                                                                                   |

|            |     |      |                       | GPIO17 — General Purpose digital Input/Output 17                                                     |

|            |     |      |                       | <b>SPI1_MOSI</b> — Serial Peripheral Interface-bus 1, master output slave input                      |

|            |     |      |                       | SWO — Serial Wire Output                                                                             |

|            |     |      |                       | PWM6 — Pulse Width Modulator output 6                                                                |

|            |     |      |                       | SPIFI_IO3 — Quad-SPI Input/Output 3                                                                  |

|            |     |      |                       | ISO7816_CLK — Clock output for ISO7816 interface                                                     |

|            |     |      |                       | CLK_OUT — Clock out                                                                                  |

Table 4. Pin descriptions

| Symbol                |    | Pin | Type                                                                                          | Default at reset      | Description                                                                                             |

|-----------------------|----|-----|-----------------------------------------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------|

| PIO18/ADC             | C4 | 22  | IO                                                                                            | GPIO18[1]             | ADC4 — ADC input 4                                                                                      |

|                       |    |     |                                                                                               |                       | GPI018 — General Purpose digital Input/Output 18                                                        |

|                       |    |     |                                                                                               |                       | SPI1_MISO — Serial Peripheral Interface-bus 1, master data input                                        |

|                       |    |     |                                                                                               |                       | CT32B0_MAT1 — 32-bit CT32B0 match output 1                                                              |

|                       |    |     |                                                                                               |                       | PWM7 — Pulse Width Modulator output 7                                                                   |

|                       |    |     |                                                                                               |                       | SPIFI_CLK — Quad-SPI Clock output                                                                       |

|                       |    |     |                                                                                               |                       | ISO7816_IO — IO of ISO7816 interface                                                                    |

|                       |    |     |                                                                                               |                       | <b>USART0_TXD</b> — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 0 - transmit data output |

| PIO19/ADC             | C5 | 23  | Ю                                                                                             | GPIO19[1]             | ADC5 — ADC input 5                                                                                      |

|                       |    |     |                                                                                               |                       | GPIO19 — General Purpose digital Input/Output 19                                                        |

|                       |    |     |                                                                                               |                       | ADO — Antenna Diversity Odd Output                                                                      |

|                       |    |     |                                                                                               |                       | PWM4 — Pulse Width Modulator output 4                                                                   |

|                       |    |     |                                                                                               |                       | SPIFI_IO0 — Quad-SPI Input/Output 0                                                                     |

|                       |    |     |                                                                                               |                       | USART1_RXD — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 1 - receive data input          |

|                       |    |     |                                                                                               |                       | CLK_IN — External clock                                                                                 |

|                       |    |     |                                                                                               |                       | USART0_RXD — Universal Synchronous/Asynchronous Receiver/Transmitter 0 - receive data input             |

| PIO20/ACF             | )  | 24  | Ю                                                                                             | GPIO20 <sup>[1]</sup> | ACP — Analog Comparator Positive input                                                                  |

|                       |    |     |                                                                                               |                       | GPIO20 — General Purpose digital Input/Output 20                                                        |

|                       |    |     |                                                                                               |                       | IR_BLASTER — Infra-Red Modulator output                                                                 |

|                       |    |     |                                                                                               |                       | PWM8 — Pulse Width Modulator output 8                                                                   |

|                       |    |     |                                                                                               |                       | RFTX — Radio Transmit Control Output                                                                    |

|                       |    |     |                                                                                               |                       | SPIFI_IO2 — Quad-SPI Input/Output 2                                                                     |

|                       |    |     |                                                                                               |                       | USART1_TXD — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 1 - transmit data output        |

| PIO21/ACN             | Л  | 25  | Ю                                                                                             | GPIO21[1]             | ACM — Analog Comparator Negative input                                                                  |

|                       |    |     |                                                                                               |                       | GPIO21 — General Purpose digital Input/Output 21                                                        |

|                       |    |     |                                                                                               |                       | IR_BLASTER — Infra-Red Modulator output                                                                 |

|                       |    |     |                                                                                               |                       | PWM9 — Pulse Width Modulator output 9                                                                   |

|                       |    |     |                                                                                               |                       | RFRX — Radio Receiver Control Output                                                                    |

|                       |    |     |                                                                                               |                       | SWO — Serial Wire Output                                                                                |

|                       |    |     |                                                                                               |                       | SPIFI_IO1 — Quad-SPI Input/Output 1                                                                     |

|                       |    |     | USART1_SCK — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 1 - synchronous clock |                       |                                                                                                         |

| TRST                  |    | 26  | G                                                                                             |                       | TRST — must be connected to GND                                                                         |

| RSTN                  |    | 27  | I                                                                                             |                       | RSTN — Reset Not input                                                                                  |

| V <sub>BAT</sub>      |    | 28  | Р                                                                                             |                       | V <sub>BAT</sub> — Supply voltage DCDC input                                                            |

| LX                    |    | 29  |                                                                                               |                       | LX — DCDC filter                                                                                        |

| V <sub>SS(DCDC)</sub> |    | 30  | G                                                                                             |                       | V <sub>SS(DCDC)</sub> — ground for DCDC section                                                         |

| FB                    |    | 31  |                                                                                               |                       | FB — DCDC Feedback input                                                                                |

11 of 99

Table 4. Pin descriptions

| Symbol                 | Pin | Туре | Default at reset | Description                                                                                                     |

|------------------------|-----|------|------------------|-----------------------------------------------------------------------------------------------------------------|

| V <sub>DD(PMU)</sub>   | 32  | Р    |                  | V <sub>DD(PMU)</sub> — supply voltage for PMU section                                                           |

| XTAL_32K_P             | 33  |      |                  | crystal oscillator 32.768 kHz                                                                                   |

| XTAL_32K_N             | 34  |      |                  | crystal oscillator 32.768 kHz                                                                                   |

| V <sub>DD(RADIO)</sub> | 35  | Р    |                  | V <sub>DD(RADIO)</sub> — supply voltage for radio section                                                       |

| V <sub>SS(RF)</sub>    | 36  | G    |                  | V <sub>SS(RF)</sub> — RF ground                                                                                 |

| RF_IO                  | 37  | Ю    |                  | RF_IO — RF antenna, RF pin which can be considered as RF Input/output. The radio transceiver is connected here. |

| V <sub>SS(RF)</sub>    | 38  | G    |                  | V <sub>SS(RF)</sub> — RF ground                                                                                 |

| LB                     | 39  |      |                  | NFC tag antenna input B                                                                                         |

| LA                     | 40  |      |                  | NFC tag antenna input A                                                                                         |

| exposed die pad        |     | G    |                  | must be connected to RF ground plane                                                                            |

- [1] I: input at reset.

- [2] For standard operation (normal boot or ISP programming mode), this pin should be high during the release of reset. If there is no external driver to this pin, then the internal pull-up will keep this pin high.

- [3] ISP programming mode: leave pin floating high during reset to avoid entering UART programming mode or hold it low to program.

- [4] In ISP mode, it is configured to USART0\_TXD.

- [5] In ISP mode, it is configured to USARTO RXD.

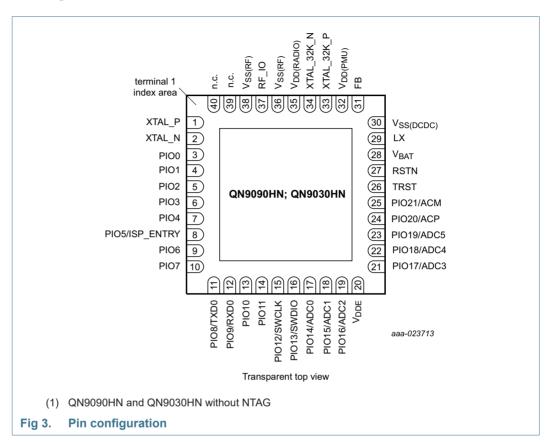

#### 7.2 HVQFN40 - without NTAG

# 7.2.1 Pinning

# 7.2.2 Pin description

Table 5. Pin descriptions

| Symbol    | Pin | Type                                                            | Default at reset                               | Description                                                                                          |                                                                                               |

|-----------|-----|-----------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| XTAL_P    | 1   |                                                                 |                                                | System crystal oscillator 32 MHz                                                                     |                                                                                               |

| XTAL_N    | 2   |                                                                 |                                                | System crystal oscillator 32 MHz                                                                     |                                                                                               |

| PIOO 3 IO | Ю   | GPIO0[1]                                                        | GPIO0 — General Purpose digital Input/Output 0 |                                                                                                      |                                                                                               |

|           |     |                                                                 |                                                | <b>USART0_SCK</b> — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 0 - synchronous clock |                                                                                               |

|           |     |                                                                 |                                                |                                                                                                      | USART1_TXD — Universal Synchronous/Asynchronous Receiver/Transmitter 1 - transmit data output |

|           |     |                                                                 |                                                | PWM0 — Pulse Width Modulator output 0                                                                |                                                                                               |

|           |     | SPI1_SCK — Serial Peripheral Interface-bus 1 clock input/output |                                                |                                                                                                      |                                                                                               |

|           |     |                                                                 |                                                | <b>PDM0_DATA</b> — Pulse Density Modulation Data input from digital microphone (channel 0)           |                                                                                               |

Table 5. Pin descriptions

| Symbol         | Pin | Type | Default at reset          | Description                                                                                               |

|----------------|-----|------|---------------------------|-----------------------------------------------------------------------------------------------------------|

| PIO1           | 4   | Ю    | GPIO1[1]                  | GPI01 — General Purpose digital Input/Output 1                                                            |

|                |     |      |                           | USART1_RXD — Universal Synchronous/Asynchronous Receiver/Transmitter 1 - receive data input               |

|                |     |      |                           | PWM1 — Pulse Width Modulator output 1                                                                     |

|                |     |      |                           | SPI1_MISO — Serial Peripheral Interface-bus 1 master data input                                           |

|                |     |      |                           | PDM0_CLK — Pulse Density Modulation Clock output to digital microphone (channel 0)                        |

| PIO2           | 5   | Ю    | GPIO2 <sup>[1]</sup>      | GPIO2 — General Purpose digital Input/Output 2                                                            |

|                |     |      |                           | SPI0_SCK — Serial Peripheral Interface-bus 0 clock input/output                                           |

|                |     |      |                           | PWM2 — Pulse Width Modulator output 2                                                                     |

|                |     |      |                           | <b>SPI1_MOSI</b> — Serial Peripheral Interface-bus 1 master output slave input                            |

|                |     |      |                           | <b>USART0_RXD</b> — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 0 - receive data input     |

|                |     |      |                           | ISO7816_RST — RST signal, output, for ISO7816 interface                                                   |

|                |     |      |                           | MCLK — External clock, can be provided to DMIC IP                                                         |

| PIO3           | 6   | Ю    | GPIO3[1]                  | GPIO3 — General Purpose digital Input/Output 3                                                            |

|                |     |      |                           | SPI0_MISO — Serial Peripheral Interface-bus 0 master input                                                |

|                |     |      |                           | PWM3 — Pulse Width Modulator output 3                                                                     |

|                |     |      |                           | SPI1_SSELN0 — Serial Peripheral Interface-bus 1 slave select not 0                                        |

|                |     |      |                           | <b>USART0_TXD</b> — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 0 - transmit data output   |

|                |     |      |                           | ISO7816_CLK — Clock output for ISO7816 interface                                                          |

| PIO4           | 7   | IO   | GPIO4[1][2]               | GPIO4 — General Purpose digital Input/Output 4                                                            |

|                |     |      |                           | <b>SPI0_MOSI</b> — Serial Peripheral Interface-bus 0 master output slave input                            |

|                |     |      |                           | PWM4 — Pulse Width Modulator output 4                                                                     |

|                |     |      |                           | SPI1_SSELN1 — Serial Peripheral Interface-bus 1 slave select not 1                                        |

|                |     |      |                           | USART0_CTS — Universal Synchronous/Asynchronous Receiver/Transmitter 0 - Clear To Send input              |

|                |     |      |                           | ISO7816_IO — IO of ISO7816 interface                                                                      |

|                |     |      |                           | RFTX — Radio Transmit Control Output                                                                      |

|                |     |      |                           | ISP_SEL — In-System Programming Mode Selection                                                            |

| PIO5/ISP_ENTRY | 8   | Ю    | GPIO5/ISP_ENT<br>RY[1][3] | GPIO5/ISP_ENTRY — General Purpose digital Input/Output 5;<br>In-System Programming Entry                  |

|                |     |      |                           | SPI0_SSELN — Serial Peripheral Interface-bus 0 slave select not                                           |

|                |     |      |                           | SPI1_MISO — Serial Peripheral Interface-bus 1 master data input                                           |

|                |     |      |                           | SPI1_SSELN2 — Serial Peripheral Interface-bus 1 slave select not 2                                        |

|                |     |      |                           | <b>USART0_RTS</b> — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 0 - Request To Send output |

|                |     |      |                           | RFRX — Radio Receiver Control Output                                                                      |

Table 5. Pin descriptions

| Symbol    | Pin | Type | Default at reset | Description                                                                                            |  |  |  |

|-----------|-----|------|------------------|--------------------------------------------------------------------------------------------------------|--|--|--|

| PIO6      | 9   | Ю    | GPI06[1]         | GPIO6 — General Purpose digital Input/Output 6                                                         |  |  |  |

|           |     |      |                  | <b>USART0_RTS</b> — Universal Synchronous/Asynchronous Receiver/Transmitter 0 - Request to Send output |  |  |  |

|           |     |      |                  | CT32B1_MAT0 — 32-bit CT32B1 match output 0                                                             |  |  |  |

|           |     |      |                  | PWM6 — Pulse Width Modulator output 6                                                                  |  |  |  |

|           |     |      |                  | I2C1_SCL — I <sup>2</sup> C-bus 1 master/slave SCL input/output                                        |  |  |  |

|           |     |      |                  | <b>USART1_TXD</b> — Universal Synchronous/Asynchronous Receiver/Transmitter 1 - transmit data output   |  |  |  |

|           |     |      |                  | ADE — Antenna Diversity Even output                                                                    |  |  |  |

|           |     |      |                  | SPI0_SCK — Serial Peripheral Interface 0- synchronous clock                                            |  |  |  |

| PIO7      | 10  | Ю    | GPI07[1]         | GPIO7 — General Purpose digital Input/Output 7                                                         |  |  |  |

|           |     |      |                  | <b>USART0_CTS</b> — Universal Synchronous/Asynchronous Receiver/Transmitter 0 - Clear to Send input    |  |  |  |

|           |     |      |                  | CT32B1_MAT1 — 32-bit CT32B1 match output 1                                                             |  |  |  |

|           |     |      |                  | <b>PWM7</b> — Pulse Width Modulator output 7                                                           |  |  |  |

|           |     |      |                  | I2C1_SDA — I <sup>2</sup> C-bus 1 master/slave SDA input/output                                        |  |  |  |

|           |     |      |                  | <b>USART1_RXD</b> — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 1 - receive data input  |  |  |  |

|           |     |      |                  | ADO — Antenna Diversity Odd Output                                                                     |  |  |  |

|           |     |      |                  | SPI0_MISO — Serial Peripheral Interface-bus 0 master input                                             |  |  |  |

| PIO8/TXD0 | 11  | Ю    | GPIO8[1][4]      | GPIO8 — General Purpose digital Input/Output 8                                                         |  |  |  |

|           |     |      |                  | <b>USART0_TXD</b> — Universal Synchronous/Asynchronous Receiver/Transmitter 0 - transmit data output   |  |  |  |

|           |     |      |                  | CT32B0_MAT0 — 32-bit CT32B0 match output 0                                                             |  |  |  |

|           |     |      |                  | PWM8 — Pulse Width Modulator output 8                                                                  |  |  |  |

|           |     |      |                  | ANA_COMP_OUT — Analog Comparator digital output                                                        |  |  |  |

|           |     |      |                  | <b>PDM1_DATA</b> — Pulse Density Modulation Data input from digital microphone (channel 1)             |  |  |  |

|           |     |      |                  | <b>SPI0_MOSI</b> — Serial Peripheral Interface-bus 0 master output slave input                         |  |  |  |

|           |     |      |                  | RFTX — Radio Transmit Control Output                                                                   |  |  |  |

| PIO9/RXD0 | 12  | Ю    | GPIO9[1][5]      | GPIO9 — General Purpose digital Input/Output 9                                                         |  |  |  |

|           |     |      |                  | <b>USART0_RXD</b> — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 0 - receive data input  |  |  |  |

|           |     |      |                  | CT32B1_CAP1 — 32-bit CT32B1 capture input 1                                                            |  |  |  |

|           |     |      |                  | <b>PWM9</b> — Pulse Width Modulator output 9                                                           |  |  |  |

|           |     |      |                  | <b>USART1_SCK</b> — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 1 - synchronous clock   |  |  |  |

|           |     |      |                  | PDM1_CLK — Pulse Density Modulation Clock output                                                       |  |  |  |

|           |     |      |                  | to digital microphone (channel 1)                                                                      |  |  |  |

|           |     |      |                  | SPI0_SSELN — Serial Peripheral Interface-bus 0 slave select not                                        |  |  |  |

|           |     |      |                  | ADO — Antenna Diversity Odd Output                                                                     |  |  |  |

Table 5. Pin descriptions

| Symbol      | Pin | Type | Default at reset     | Description                                                                                   |  |  |

|-------------|-----|------|----------------------|-----------------------------------------------------------------------------------------------|--|--|

| PIO10       | 13  | Ю    | GPIO10[1]            | GPIO10 — General Purpose digital Input/Output 10                                              |  |  |

|             |     |      |                      | CT32B0_CAP0 — 32-bit CT32B0 capture input 0                                                   |  |  |

|             |     |      |                      | USART1_TXD — Universal Synchronous/Asynchronous Receiver/Transmitter 1 - transmit data output |  |  |

|             |     |      |                      | RFTX — Radio Transmit Control Output                                                          |  |  |

|             |     |      |                      | <b>I2C0_SCL</b> — I <sup>2</sup> C-bus 0 master/slave SCL input/output (open drain)           |  |  |

|             |     |      |                      | SPI0_SCK — Serial Peripheral Interface-bus 0 clock input/output                               |  |  |

|             |     |      |                      | <b>PDM0_DATA</b> — Pulse Density Modulation Data input from digital microphone (channel 0)    |  |  |

| PIO11       | 14  | Ю    | GPIO11 <sup>11</sup> | GPIO11 — General Purpose digital Input/Output 11                                              |  |  |

|             |     |      |                      | CT32B1_CAP0 — 32-bit CT32B1 capture input 0                                                   |  |  |

|             |     |      |                      | USART1_RXD — Universal Synchronous/Asynchronous Receiver/Transmitter 1 - receive data input   |  |  |

|             |     |      |                      | RFRX — Radio Receiver Control Output                                                          |  |  |

|             |     |      |                      | I2C0_SDA — I <sup>2</sup> C-bus 0 master/slave SDA input/output (open drain)                  |  |  |

|             |     |      |                      | SPI0_MISO — Serial Peripheral Interface-bus 0 master input slave output                       |  |  |

|             |     |      |                      | PDM0_CLK — Pulse Density Modulation Clock output to digital microphone (channel 0)            |  |  |

| PIO12/SWCLK | 15  | Ю    | SWCLK                | GPIO12 — General Purpose digital Input/Output 12                                              |  |  |

|             |     |      |                      | SWCLK — Serial Wire Debug Clock                                                               |  |  |

|             |     |      |                      | PWM0 — Pulse Width Modulator output 0                                                         |  |  |

|             |     |      |                      | <b>I2C1_SCL</b> — I <sup>2</sup> C-bus 1 master/slave SCL input/output (open drain)           |  |  |

|             |     |      |                      | <b>SPI0_MOSI</b> — Serial Peripheral Interface-bus 0 master output slave input                |  |  |

|             |     |      |                      | ANA_COMP_OUT — Analog Comparator digital output                                               |  |  |

|             |     |      |                      | IR_BLASTER — Infra-Red Modulator output                                                       |  |  |

| PIO13/SWDIO | 16  | Ю    | SWDIO                | GPIO13 — General Purpose digital Input/Output 13                                              |  |  |

|             |     |      |                      | <b>SPI1_SSELN2</b> — Serial Peripheral Interface-bus 1, slave select not 2                    |  |  |

|             |     |      |                      | SWDIO — Serial Wire Debug Input/Output                                                        |  |  |

|             |     |      |                      | PWM2 — Pulse Width Modulator output 2                                                         |  |  |

|             |     |      |                      | I2C1_SDA — I <sup>2</sup> C-bus 1 master/slave SDA input/output (open drain)                  |  |  |

|             |     |      |                      | SPI0_SSELN — Serial Peripheral Interface-bus 0, slave select not                              |  |  |

Table 5. Pin descriptions

| Symbol     | Pin | Type | Default at reset      | Description                                                                                          |

|------------|-----|------|-----------------------|------------------------------------------------------------------------------------------------------|

| PIO14/ADC0 | 17  | Ю    | GPIO14[1]             | ADC0 — ADC input 0                                                                                   |

|            |     |      |                       | GPIO14 — General Purpose digital Input/Output 14                                                     |

|            |     |      |                       | <b>SPI1_SSELN1</b> — Serial Peripheral Interface-bus 1, slave select not 1                           |

|            |     |      |                       | CT32B0_CAP1 — 32-bit CT32B0 capture input 1                                                          |

|            |     |      |                       | PWM1 — Pulse Width Modulator output 1                                                                |

|            |     |      |                       | SWO — Serial Wire Output                                                                             |

|            |     |      |                       | <b>USART0_SCK</b> — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 0 - synchronous clock |

|            |     |      |                       | MCLK — External clock, can be provided to DMIC IP                                                    |

|            |     |      |                       | RFTX — Radio Transmit Control Output                                                                 |

| PIO15/ADC1 | 18  | Ю    | GPIO15[1]             | ADC1 — ADC input 1                                                                                   |

|            |     |      |                       | GPIO15 — General Purpose digital Input/Output 15                                                     |

|            |     |      |                       | SPI1_SCK — Serial Peripheral Interface-bus 1, clock input/output                                     |

|            |     |      |                       | ANA_COMP_OUT — Analog Comparator digital output                                                      |

|            |     |      |                       | PWM3 — Pulse Width Modulator output 3                                                                |

|            |     |      |                       | PDM1_DATA — Pulse Density Modulation Data input from digital microphone (channel 1)                  |

|            |     |      |                       | I2C0_SCL — I2C-bus 0 master/slave SCL input/output (open drain)                                      |

|            |     |      |                       | RFRX — Radio Receiver Control Output                                                                 |

| PIO16/ADC2 | 19  | 9 10 | GPIO16 <sup>[1]</sup> | ADC2 — ADC input 2                                                                                   |

|            |     |      |                       | GPIO16 — General Purpose digital Input/Output 16                                                     |

|            |     |      |                       | <b>SPI1_SSELN0</b> — Serial Peripheral Interface-bus 1, slave select not 0                           |

|            |     |      |                       | PWM5 — Pulse Width Modulator output 5                                                                |

|            |     |      |                       | PDM1_CLK — Pulse Density Modulation Clock output to digital microphone (channel 1)                   |

|            |     |      |                       | SPIFI_CSN — Quad-SPI Chip Select Not, output                                                         |

|            |     |      |                       | ISO7816_RST — RST signal, output, for ISO7816 interface                                              |

|            |     |      |                       | <b>I2C0_SDA</b> — I2C-bus 0 master/slave SDA input/output (open drain)                               |

| $V_{DDE}$  | 20  | Р    |                       | V <sub>DDE</sub> — Supply voltage for IO                                                             |

| PIO17/ADC3 | 21  | Ю    | GPIO17[1]             | ADC3 — ADC input 3                                                                                   |

|            |     |      |                       | GPIO17 — General Purpose digital Input/Output 17                                                     |

|            |     |      |                       | <b>SPI1_MOSI</b> — Serial Peripheral Interface-bus 1, master output slave input                      |

|            |     |      |                       | SWO — Serial Wire Output                                                                             |

|            |     |      |                       | PWM6 — Pulse Width Modulator output 6                                                                |

|            |     |      |                       | SPIFI_IO3 — Quad-SPI Input/Output 3                                                                  |

|            |     |      |                       | ISO7816_CLK — Clock output for ISO7816 interface                                                     |

|            |     |      |                       | CLK_OUT — Clock out                                                                                  |

**Product data sheet**

Table 5. Pin descriptions

| Symbol                | Pin | Type | Default at reset | Description                                                                                             |

|-----------------------|-----|------|------------------|---------------------------------------------------------------------------------------------------------|

| PIO18/ADC4            | 22  | Ю    | GPIO18[1]        | ADC4 — ADC input 4                                                                                      |

|                       |     |      |                  | GPIO18 — General Purpose digital Input/Output 18                                                        |

|                       |     |      |                  | SPI1_MISO — Serial Peripheral Interface-bus 1, master data input                                        |

|                       |     |      |                  | CT32B0_MAT1 — 32-bit CT32B0 match output 1                                                              |

|                       |     |      |                  | PWM7 — Pulse Width Modulator output 7                                                                   |

|                       |     |      |                  | SPIFI_CLK — Quad-SPI Clock output                                                                       |

|                       |     |      |                  | ISO7816_IO — IO of ISO7816 interface                                                                    |

|                       |     |      |                  | <b>USART0_TXD</b> — Universal Synchronous/Asynchronous Receiver/Transmitter 0 - transmit data output    |

| PIO19/ADC5            | 23  | Ю    | GPIO19[1]        | ADC5 — ADC input 5                                                                                      |

|                       |     |      |                  | GPIO19 — General Purpose digital Input/Output 19                                                        |

|                       |     |      |                  | ADO — Antenna Diversity Odd Output                                                                      |

|                       |     |      |                  | PWM4 — Pulse Width Modulator output 4                                                                   |

|                       |     |      |                  | SPIFI_IO0 — Quad-SPI Input/Output 0                                                                     |

|                       |     |      |                  | <b>USART1_RXD</b> — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 1 - receive data input   |

|                       |     |      |                  | CLK_IN — External clock                                                                                 |

|                       |     |      |                  | <b>USART0_RXD</b> — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 0 - receive data input   |

| PIO20/ACP             | 24  | Ю    | GPIO20[1]        | ACP — Analog Comparator Positive input                                                                  |

|                       |     |      |                  | GPIO20 — General Purpose digital Input/Output 20                                                        |

|                       |     |      |                  | IR_BLASTER — Infra-Red Modulator output                                                                 |

|                       |     |      |                  | PWM8 — Pulse Width Modulator output 8                                                                   |

|                       |     |      |                  | RFTX — Radio Transmit Control Output                                                                    |

|                       |     |      |                  | SPIFI_IO2 — Quad-SPI Input/Output 2                                                                     |

|                       |     |      |                  | <b>USART1_TXD</b> — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 1 - transmit data output |

| PIO21/ACM             | 25  | Ю    | GPIO21[1]        | ACM — Analog Comparator Negative input                                                                  |

|                       |     |      |                  | GPIO21 — General Purpose digital Input/Output 21                                                        |

|                       |     |      |                  | IR_BLASTER — Infra-Red Modulator output                                                                 |

|                       |     |      |                  | PWM9 — Pulse Width Modulator output 9                                                                   |

|                       |     |      |                  | RFRX — Radio Receiver Control Output                                                                    |

|                       |     |      |                  | SWO — Serial Wire Output                                                                                |

|                       |     |      |                  | SPIFI_IO1 — Quad-SPI Input/Output 1                                                                     |

|                       |     |      |                  | <b>USART1_SCK</b> — Universal Synchronous/Asynchronous<br>Receiver/Transmitter 1 - synchronous clock    |

| TRST                  | 26  | G    |                  | TRST — must be connected to GND                                                                         |

| RSTN                  | 27  | I    |                  | RSTN — Reset Not input                                                                                  |

| V <sub>BAT</sub>      | 28  | Р    |                  | V <sub>BAT</sub> — Supply voltage DCDC input                                                            |

| LX                    | 29  |      |                  | LX — DCDC filter                                                                                        |

| V <sub>SS(DCDC)</sub> | 30  | G    |                  | V <sub>SS(DCDC)</sub> — ground for DCDC section                                                         |

| FB                    | 31  |      |                  | FB — DCDC Feedback input                                                                                |

Table 5. Pin descriptions

| Symbol                 | Pin | Type | Default at reset | Description                                                                                                     |

|------------------------|-----|------|------------------|-----------------------------------------------------------------------------------------------------------------|

| V <sub>DD(PMU)</sub>   | 32  | Р    |                  | V <sub>DD(PMU)</sub> — supply voltage for PMU section                                                           |

| XTAL_32K_P             | 33  |      |                  | crystal oscillator 32.768 kHz                                                                                   |

| XTAL_32K_N             | 34  |      |                  | crystal oscillator 32.768 kHz                                                                                   |

| V <sub>DD(RADIO)</sub> | 35  | Р    |                  | V <sub>DD(RADIO)</sub> — supply voltage for radio section                                                       |

| V <sub>SS(RF)</sub>    | 36  | G    |                  | V <sub>SS(RF)</sub> — RF ground                                                                                 |

| RF_IO                  | 37  | Ю    |                  | RF_IO — RF antenna, RF pin which can be considered as RF Input/output. The radio transceiver is connected here. |

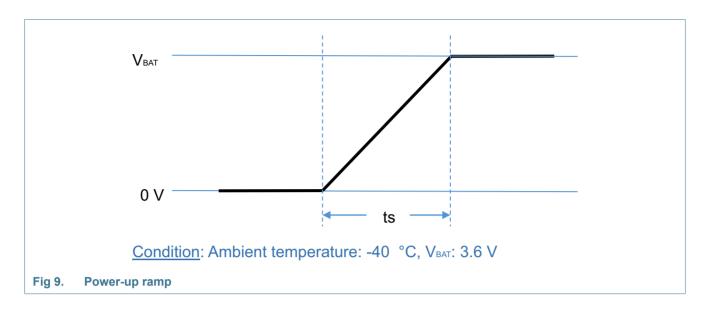

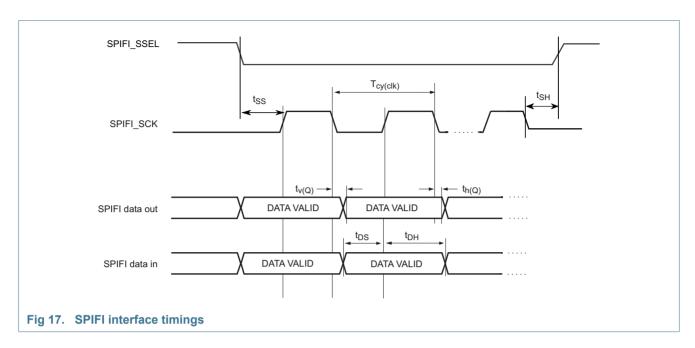

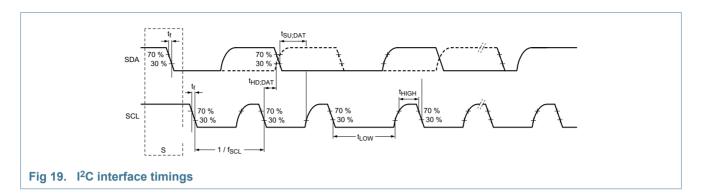

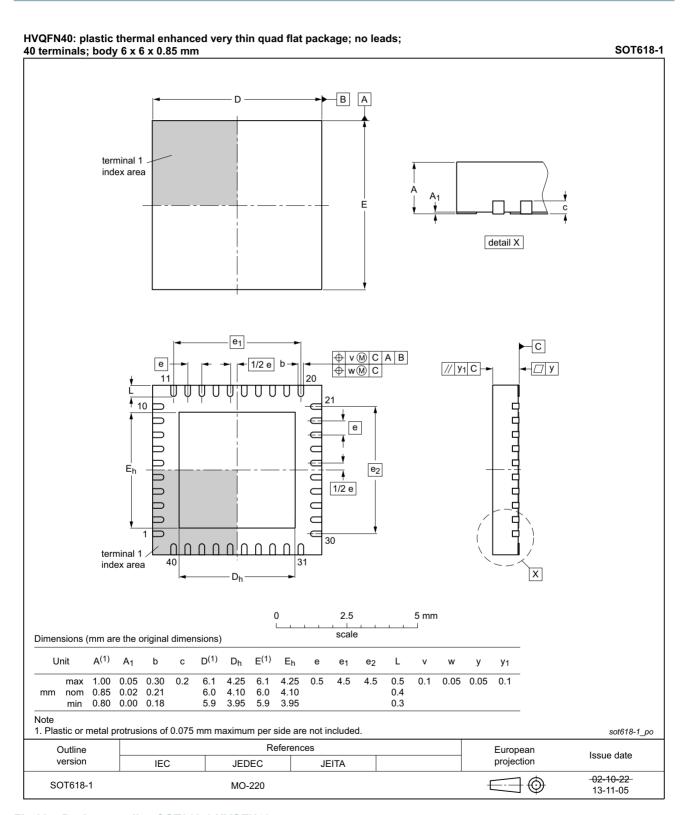

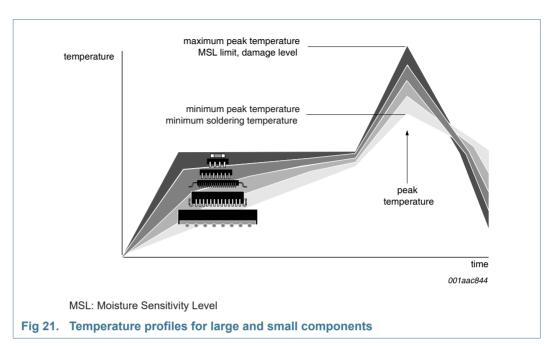

| V <sub>SS(RF)</sub>    | 38  | G    |                  | V <sub>SS(RF)</sub> — RF ground                                                                                 |