# PWM controller for ZVS half bridge

Datasheet - production data

### **Features**

- Complementary PWM control for soft-switched half bridge with programmable deadtime

- Up to 500 kHz operating frequency

- Onboard high-voltage startup

- Advanced light load management

- Adaptive UVLO

- Pulse-by-pulse OCP

- OLP (latched or autorestart)

- Transformer saturation detection

- Interface with PFC controller

- Latched disable input

- Input for power-on sequencing or brownout protection

- Programmable soft-start

- 4% precision external reference

- 600 V-rail compatible high-side gate driver with integrated bootstrap diode and high dV/dt immunity

- SO16N package

### **Applications**

- High power AC-DC adapter/charger

- Desktop PC, entry-level server

- Telecom SMPS

Contents L6591

# **Contents**

| 1  | Desc | cription                                                 |

|----|------|----------------------------------------------------------|

| 2  | Pin  | settings4                                                |

|    | 2.1  | Connection                                               |

|    | 2.2  | Functions                                                |

| 3  | Elec | trical data7                                             |

|    | 3.1  | Maximum ratings 7                                        |

|    | 3.2  | Thermal data 7                                           |

| 4  | Elec | trical characteristics 8                                 |

| 5  | Турі | cal characteristics12                                    |

| 6  | Арр  | lication information                                     |

|    | 6.1  | High-voltage startup generator                           |

|    | 6.2  | Operation at no load or very light load 24               |

|    | 6.3  | PWM control block                                        |

|    | 6.4  | PWM comparator, PWM latch and hiccup mode OCP 26         |

|    | 6.5  | Latched shutdown                                         |

|    | 6.6  | Oscillator and deadtime programming                      |

|    | 6.7  | Adaptive UVLO                                            |

|    | 6.8  | Line sensing function                                    |

|    | 6.9  | Soft-start and delayed latched shutdown upon overcurrent |

| 7  | Sum  | mary of L6591 power management functions 34              |

| 8  | ECO  | PACK <sup>®</sup> 37                                     |

| 9  | Orde | er codes                                                 |

| 10 | Revi | sion history40                                           |

L6591 Description

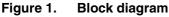

### 1 Description

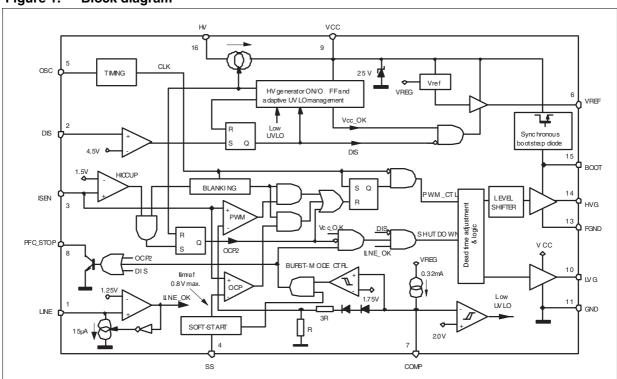

The L6591 is a double-ended PWM controller specific to the soft-switched half bridge topology. It provides complementary PWM control, where the high-side switch is driven ON for a duty cycle D and the low-side switch for a duty cycle 1-D, with D < 50%. An externally programmable deadtime inserted between the turn-off of one switch and the turn-on of the other one guarantees soft-switching and enables high-frequency operation.

To drive the high-side switch with the bootstrap approach, the IC incorporates a high-voltage floating structure able to withstand more than 600 V with a synchronous-driven high-voltage DMOS that replaces the external fast-recovery bootstrap diode.

The IC enables the user to set the operating frequency of the converter by means of an externally programmable oscillator: the maximum duty cycle is digitally clipped at 50% by a T-flip-flop, so that the operating frequency is half that of the oscillator.

At very light load the IC enters a controlled burst mode operation that, along with the built-in non-dissipative high-voltage startup circuit and the low quiescent current, helps keep the consumption from the mains low and is compliant with energy saving recommendations.

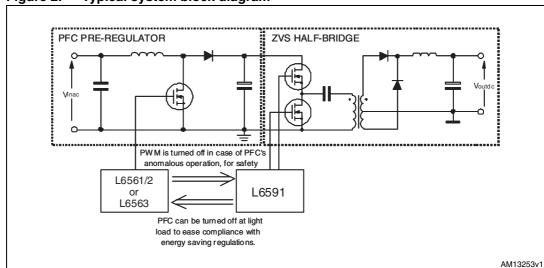

To allow compliance with these standards also in two-stage power-factor-corrected systems, an interface with the PFC controller is provided that enables the pre-regulator to be switched off between one burst and the following one.

An innovative adaptive UVLO helps minimize the issues related to fluctuations of the self-supply voltage with the output load, due to the transformer's parasitic.

IC protection functions include: not-latched input undervoltage (brownout), a first-level OCP with delayed shutdown able to protect the system during overload and short-circuit conditions (either auto-restart or latch mode can be selected) and a second-level OCP that latches off the IC when the transformer saturates or one of the secondary diodes fails short. Finally, a latched disable function allows easy implementation of OTP or OVP.

Programmable soft-start and digital leading-edge blanking on the current sense input pin complete the equipment of the IC.

Figure 2. Typical system block diagram

Pin settings L6591

# 2 Pin settings

### 2.1 Connection

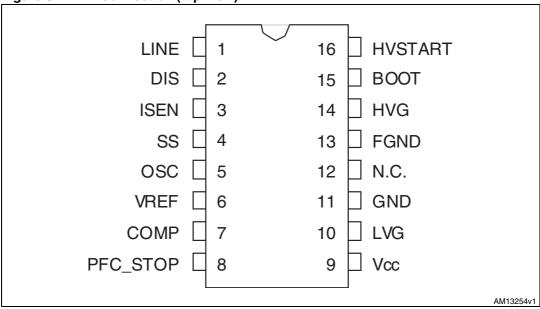

Figure 3. Pin connection (top view)

### 2.2 Functions

Table 1. Pin functions

| Pin N. | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | LINE | Line sensing input. The pin is to be connected to the high-voltage input bus with a resistor divider. A voltage below 1.25 V shuts down the IC, lowers its consumption and discharges the soft-start capacitor. IC operation is reenabled as the voltage exceeds 1.25 V. The comparator is provided with current hysteresis: an internal 15 $\mu A$ current generator is ON as long as the voltage applied at the pin is below 1.25 V, and is OFF if this value is exceeded. Bypass the pin with a capacitor to GND (#11) to reduce noise pick-up. The pin is intended for either power-on sequencing in systems with PFC, or brownout protection. Tie to Vcc (#9) with a 220 to 330 $k\Omega$ resistor if the function is not used. |

| 2      | DIS  | Latched device shutdown. Internally, the pin connects a comparator that, when the voltage on the pin exceeds 4.5 V, shuts the IC down and brings its consumption to a value barely higher than before startup. The information is latched and it is necessary to recycle the input power to restart the IC: the latch is removed as the voltage on the Vcc pin (#9) goes below the UVLO threshold. Connect the pin to GND (#11) if the function is not used.                                                                                                                                                                                                                                                                         |

L6591 Pin settings

Table 1. Pin functions (continued)

| Table 1. | Pin tunci | tions (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin N.   | Name      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3        | ISEN      | Current sense (PWM comparator) input. The voltage on this pin is internally compared with an internal reference derived from the voltage on the COMP pin and, when they are equal, the high-side gate drive output (previously asserted high by the clock signal generated by the oscillator) is driven low to turn off the upper Power MOSFET; the lower MOSFET is turned on after a delay programmed by the timing capacitor at the OSC pin (#5). The pin is equipped with 200 ns blanking time for improved noise immunity. A second comparator, referenced at 0.8 V, turns off the upper MOSFET if the voltage at the pin exceeds the threshold, overriding the PWM comparator (pulse-by-pulse OCP). A third comparison level located at 1.5 V shuts the device down and brings its consumption almost to a "before startup" level (hiccup mode OCP) to prevent uncontrolled current rise. A logic circuit improves sensitivity to temporary disturbances. |

| 4        | SS        | Soft-start. An internal 20 µA generator charges an external capacitor connected between the pin and GND (#11) generating a voltage ramp. During the ramp, the internal reference for pulse-by-pulse OCP (see pin #3, ISEN) rises linearly starting from zero to its final value, therefore causing the duty cycle of the upper MOSFET to rise starting from zero as well, and all the functions monitoring the COMP pin (#7) are disabled. The same capacitor is used to delay IC shutdown (latch-off or auto-restart mode selectable) after detecting an overcurrent condition. The SS capacitor is quickly discharged as the chip goes into UVLO.                                                                                                                                                                                                                                                                                                            |

| 5        | OSC       | Oscillator pin. A resistor to VREF (#6) and a capacitor from the pin to GND (#11) define the oscillator frequency. The maximum duty cycle is limited below 50% by an internal T-flip-flop. As a result, the switching frequency is half that of the oscillator. The capacitor value defines the deadtime separating the conduction state of either MOSFET. This capacitor should not be lower than 220 pF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6        | VREF      | Voltage reference. An internal generator furnishes an accurate voltage reference (5 V±4%, all inclusive) that can be used to supply up to 5 mA to an external circuit. A small film capacitor (0.1 µF typ.), connected between this pin and GND (#11) is recommended to ensure the stability of the generator and to prevent noise from affecting the reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7        | СОМР      | Control input for PWM regulation. The pin is to be driven by the phototransistor (emitter-grounded) of an octocoupler to modulate the voltage by modulating the current sunk from (sourced by) the pin (0.4 mA typ.). It is recommended to place a small filter capacitor between the pin and GND (#11), as close to the IC as possible, to reduce switching noise pick-up, and to set a pole in the output-to-control transfer function. A voltage lower than 1.75 V shuts down the IC and reduces its current consumption. The chip restarts as the voltage exceeds 1.8 V. This function realizes burst mode operation at light load.                                                                                                                                                                                                                                                                                                                        |

| 8        | PFC_STOP  | Open-drain ON/OFF control of PFC controller. This pin is intended for temporarily stopping the PFC controller at light load in systems comprising a PFC pre-regulator, during burst mode operation (see pin COMP, #7). The pin, normally open, goes low if the voltage on COMP is lower than 1.75 V and opens when the voltage on the COMP pin exceeds 1.8 V. Whenever the IC is shut down (SS > 5 V, DIS > 4.5, ISEN > 1.5 V) the pin is low as well, provided the supply voltage of the IC is above the restart threshold (typ. 5 V). It is open during UVLO. Leave the pin open if not used.                                                                                                                                                                                                                                                                                                                                                                |

Pin settings L6591

Table 1. Pin functions (continued)

| Pin N. | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9      | Vcc     | Supply voltage of both the signal part of the IC and the low-side gate driver. The internal high-voltage generator charges an electrolytic capacitor connected between this pin and GND (#11) as long as the voltage on the pin is below the startup threshold of the IC, after that, it is disabled and the chip turns on. Sometimes a small bypass capacitor (0.1 $\mu F$ typ.) to GND may be useful to get a clean bias voltage for the signal part of the IC. The minimum operating voltage (UVLO) is adapted to the loading conditions of the converter to ease burst mode operation, during which the available supply voltage for the IC drops. |

| 10     | LVG     | Low-side gate-drive output. The driver is capable of 0.3 A min. source and 0.8 A min. sink peak current to drive the gate of the lower MOSFET of the half bridge leg. The pin is actively pulled to GND (#11) during UVLO.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11     | GND     | Chip ground. Current return for both the low-side gate-drive current and the bias current of the IC. All of the ground connections of the bias components should be tied to a track going to this pin and kept separate from any pulsed current return.                                                                                                                                                                                                                                                                                                                                                                                                |

| 12     | N.C.    | High-voltage spacer. The pin is not connected internally to isolate the group of high-voltage pins and comply with safety regulations (creepage distance) on the PCB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 13     | FGND    | High-side gate-drive floating ground. Current return for the high-side gate-drive current. Layout carefully the connection of this pin to avoid too large spikes below ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 14     | HVG     | High-side floating gate-drive output. The driver is capable of 0.3 A min. source and 0.8 A min. sink peak current to drive the gate of the upper MOSFET of the half bridge leg. A pull-down resistor between this pin and pin 13 (FGND) makes sure that the gate is never floating during UVLO.                                                                                                                                                                                                                                                                                                                                                        |

| 15     | воот    | High-side gate-drive floating supply voltage. The bootstrap capacitor connected between this pin and pin 13 (FGND) is fed by an internal synchronous bootstrap diode driven in-phase with the low-side gate-drive. This patented structure can replace the normally used external diode.                                                                                                                                                                                                                                                                                                                                                               |

| 16     | HVSTART | High-voltage startup. The pin is to be connected directly to the rectified mains voltage. A 0.8 mA internal current source charges the capacitor connected between pin Vcc (#9) and GND (#11) until the voltage on the Vcc pin reaches the startup threshold. Normally it is re-enabled when the voltage on the Vcc pin falls below 5 V, except under latched shutdown conditions, in which case it is re-enabled as the Vcc voltage falls 1 V below the startup threshold to keep the latch active.                                                                                                                                                   |

L6591 Electrical data

# 3 Electrical data

# 3.1 Maximum ratings

Table 2. Absolute maximum ratings

| Symbol                              | Pin    | Parameter                                        | Value                       | Unit |

|-------------------------------------|--------|--------------------------------------------------|-----------------------------|------|

| V <sub>HVSTART</sub>                | 16     | Voltage range (referred to ground)               | -0.3 to 700                 | V    |

| I <sub>HVS</sub>                    | 16     | Input current                                    | Self-limited                | Α    |

| V <sub>BOOT</sub>                   | 15     | Floating supply voltage                          | -1 to 618                   | ٧    |

| V <sub>FGND</sub>                   | 13     | Floating ground voltage                          | -3 to V <sub>BOOT</sub> -18 | ٧    |

| dV <sub>FGND</sub> /dt              | 13     | Floating ground slew rate                        | 50                          | V/ns |

| V <sub>CC</sub>                     | 9      | IC supply voltage (Icc = 20 mA)                  | Self-limited                | ٧    |

| I <sub>HVG</sub> , I <sub>LVG</sub> | 10, 14 | Gate drive peak current                          | Self-limited                | Α    |

| IPFC_STOP                           | 8      | Max. sink current (V <sub>PFC_STOP</sub> = 25 V) | Self-limited                | Α    |

| V <sub>LINEmax</sub>                | 1      | Maximum pin voltage (Ipin ≤1 mA)                 | Self-limited                | ٧    |

| -                                   | 2 to 7 | Analog inputs and outputs                        | -0.3 to 7                   | ٧    |

| ISEN                                | 3      | Current sense input                              | -3 to 7                     | V    |

| P <sub>TOT</sub>                    |        | Power dissipation @ T <sub>A</sub> = 50 °C       | 0.75                        | W    |

| TJ                                  |        | Junction temperature operating range             | -40 to 150                  | Ô    |

| T <sub>STG</sub>                    |        | Storage temperature                              | -55 to 150                  | °C   |

### 3.2 Thermal data

Table 3. Thermal data

| Symbol            | Parameter                                  | Value | Unit |

|-------------------|--------------------------------------------|-------|------|

| R <sub>thJA</sub> | Thermal resistance junction-to-ambient (1) | 120   | °C/W |

<sup>1.</sup> Value depending on PCB copper area and thickness.

Electrical characteristics L6591

## 4 Electrical characteristics

$T_J$  = 0 to 105 °C, Vcc = 15 V,  $V_{BOOT}$  = 12 V,  $C_{HVG}$  =  $C_{LVG}$  = 1 nF;  $R_T$  = 22 k $\Omega$   $C_T$  = 330 pF; unless otherwise specified.

Table 4. Electrical characteristics

| Symbol               | Parameter Test condition                  |                                                        | Min. | Тур. | Max.     | Unit |  |

|----------------------|-------------------------------------------|--------------------------------------------------------|------|------|----------|------|--|

| IC supply            | voltage                                   | •                                                      | •    | •    | <u> </u> |      |  |

| \/oo                 | Operating range after                     | V <sub>COMP</sub> > V <sub>COMPL</sub>                 | 11.3 |      | 22       | V    |  |

| Vcc                  | turn-on                                   | $V_{COMP} = V_{COMPL}$                                 | 9.2  |      | 22       | v    |  |

| Vcc <sub>On</sub>    | Turn-on threshold                         | (1)                                                    | 13   | 14   | 15       | ٧    |  |

| Voo                  | Turn-off threshold                        | $^{(1)}V_{COMP} > V_{COMPL}$                           | 9.7  | 10.5 | 11.3     | V    |  |

| Vcc <sub>Off</sub>   | Turri-on theshold                         | $^{(1)}V_{COMP} = V_{COMPL}$                           | 8.2  | 8.7  | 9.2      | v    |  |

| Hys                  | Hysteresis                                | V <sub>COMP</sub> > V <sub>COMPL</sub>                 | 3.0  | 3.5  |          | V    |  |

| VZ                   | Vcc clamp voltage                         | Icc = 15 mA                                            | 22   | 25   | 28       | V    |  |

| Supply c             | urrent                                    |                                                        |      |      |          |      |  |

| I <sub>startup</sub> | Startup current                           | Before turn-on,<br>Vcc = 12.5 V                        |      | 190  | 250      | μA   |  |

| Iq                   | Quiescent current                         | After turn-on                                          |      | 2.8  | 3.5      | mA   |  |

| lcc                  | Operating supply current                  |                                                        |      | 5.3  | 8        | mA   |  |

|                      | Shutdown quiescent                        | V <sub>DIS</sub> > 4.5 V,<br>V <sub>ISEN</sub> > 1.5 V |      |      | 0.35     | mA   |  |

| Iq <sub>dis</sub>    | current                                   | V <sub>COMP</sub> = 1.64 V                             |      |      | 2.2      | mA   |  |

|                      |                                           | V <sub>LINE</sub> < 1.25 V                             |      |      | 0.35     | mA   |  |

| High-side            | e floating gate-drive supply              |                                                        |      |      |          |      |  |

| $V_{BOOT}$           | Operating supply voltage                  | Referred to FGND pin                                   |      |      | 17       | V    |  |

| I <sub>qBOOT</sub>   | Quiescent current                         | V <sub>FGND</sub> = 0                                  |      | 500  | 800      | μΑ   |  |

| I <sub>LK</sub>      | High-voltage leakage                      | $V_{FGND} = V_{BOOT} = V_{HVG} = 600 \text{ V}$        |      |      | 10       | μΑ   |  |

| R <sub>DS(on)</sub>  | Synchronous bootstrap diode on-resistance | V <sub>LVG</sub> = HIGH                                |      | 125  |          | Ω    |  |

| High-volt            | age startup generator                     | •                                                      |      |      |          |      |  |

| V <sub>HV</sub>      | Breakdown voltage                         | I <sub>HV</sub> < 100 μA                               | 700  |      |          | V    |  |

| V <sub>HVstart</sub> | Start voltage                             | I <sub>Vcc</sub> < 100 μA                              | 60   | 75   | 90       | V    |  |

| I <sub>charge</sub>  | Vcc charge current                        | V <sub>HV</sub> > V <sub>Hvstart</sub> ,<br>Vcc > 3 V  | 0.55 | 0.75 | 1        | mA   |  |

**Electrical characteristics**

| Symbol                 | Parameter                    | Test condition                                                    | Min. | Тур. | Max. | Unit |

|------------------------|------------------------------|-------------------------------------------------------------------|------|------|------|------|

| I <sub>HV, ON</sub>    | ON-state current             | V <sub>HV</sub> > V <sub>Hvstart</sub> ,<br>Vcc > 3 V             |      |      | 1.6  | mA   |

| 'HV, ON                |                              | V <sub>HV</sub> > V <sub>Hvstart</sub> , Vcc = 0                  |      |      | 0.8  |      |

| I <sub>HV, OFF</sub>   | Leakage current (OFF-state)  | V <sub>HV</sub> = 400 V                                           |      |      | 40   | μΑ   |

| V <sub>CCrestart</sub> | HV generator restart voltage | (1)                                                               | 4.4  | 5    | 5.6  | V    |

|                        |                              | (1) After DIS tripping                                            | 12.2 | 13.2 | 14.2 | V    |

| Reference              | e voltage                    |                                                                   |      |      |      |      |

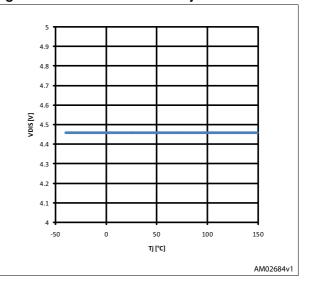

| V <sub>REF</sub>       | Output voltage               | <sup>(1)</sup> T <sub>J</sub> = 25 °C;<br>I <sub>REF</sub> = 1 mA | 4.9  | 5    | 5.1  | V    |

| V <sub>REF</sub>       | Total variation              | Vcc= 9.2 to 22 V,<br>I <sub>REF</sub> = 1 to 5 mA                 | 4.8  |      | 5.2  | ٧    |

| I <sub>REF</sub>       | Short-circuit current        | V <sub>REF</sub> = 0                                              | 10   |      | 30   | mA   |

|                        | Sink capability in UVLO      | Vcc = 6 V;<br>Isink = 0.5 mA                                      |      | 0.2  | 0.5  | ٧    |

| Current s              | ense comparator              |                                                                   |      |      |      |      |

| I <sub>ISEN</sub>      | Input bias current           | V <sub>ISEN</sub> = 0                                             |      |      | -1   | μΑ   |

| t <sub>LEB</sub>       | Leading edge blanking        | After V <sub>HVG</sub> low-to-high transition                     |      | 200  |      | ns   |

| t <sub>d(H-L)</sub>    | Delay to output              |                                                                   |      |      | 170  | ns   |

|                        | Gain                         |                                                                   | 3.8  | 4    | 4.2  | V/V  |

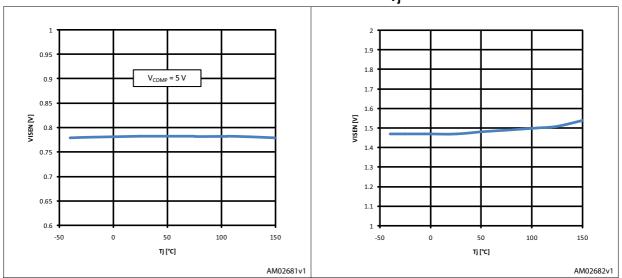

| V <sub>ISENx</sub>     | Maximum signal               | $^{(1)}V_{COMP} = 5 V$                                            | 0.76 | 0.8  | 0.84 | V    |

| V <sub>ISENdis</sub>   | Hiccup mode OCP level        | (1)                                                               | 1.4  | 1.5  | 1.65 | V    |

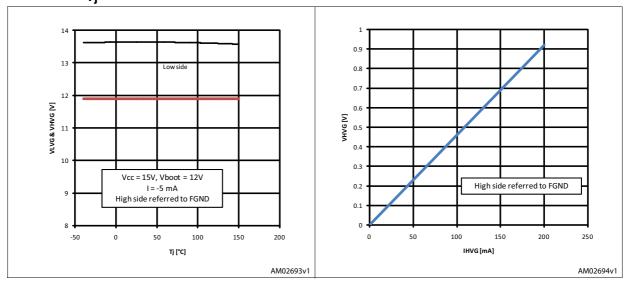

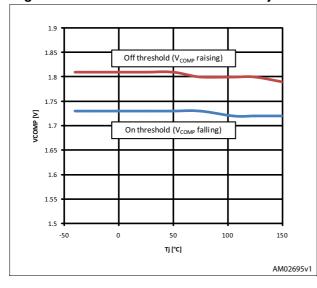

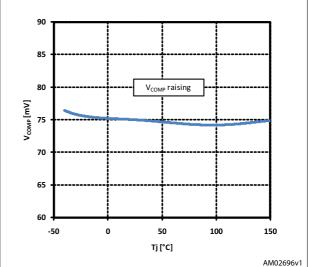

| PWM con                | trol and burst mode control  |                                                                   |      |      |      |      |

| V <sub>COMPH</sub>     | Maximum level                | I <sub>COMP</sub> = 0                                             | 5.5  |      |      | V    |

| I <sub>COMP</sub>      | Source current               | V <sub>COMP</sub> = 2 V                                           | 210  | 300  | 400  | μΑ   |

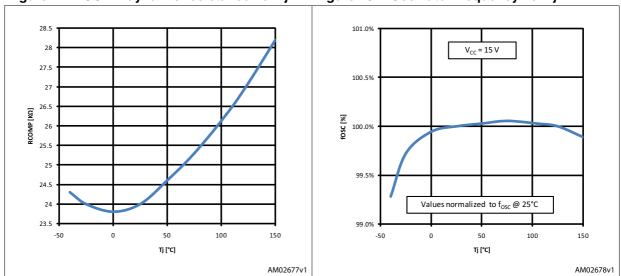

| R <sub>COMP</sub>      | Dynamic resistance           | V <sub>COMP</sub> = 2 to 4 V                                      |      | 25   |      | kΩ   |

| V <sub>COMPBon</sub>   | Burst mode on threshold      | (1) V <sub>COMP</sub> falling                                     | 1.68 | 1.75 | 1.82 | V    |

| Hys                    | Burst mode hysteresis        | V <sub>COMP</sub> rising                                          |      | 70   |      | mV   |

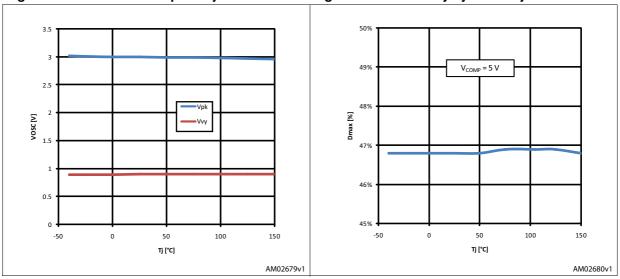

| D <sub>max</sub>       | Maximum duty cycle           | V <sub>COMP</sub> = 5 V                                           | 46   |      | 50   | %    |

| Adaptive               | UVLO                         |                                                                   |      |      |      | I    |

| V <sub>COMPL</sub>     | UVLO shift threshold         | (1)                                                               | 1.9  | 2    | 2.1  | V    |

| Line sens              | sing                         | 1                                                                 | I    |      | I    | I    |

| Vth                    | Threshold voltage            | Voltage rising or falling                                         | 1.22 | 1.25 | 1.28 | V    |

| I <sub>Hys</sub>       | Current hysteresis           | Vcc > 5 V                                                         | 13.2 | 14.7 | 16.2 | μA   |

| 11,5                   | Clamp level                  | I <sub>LINE</sub> = 1 mA                                          | 2.8  | 3    |      | V    |

Electrical characteristics L6591

Table 4. Electrical characteristics (continued)

| Symbol                | Parameter                                                                 | Test condition                                                               | Min.  | Тур.  | Max.  | Unit |  |

|-----------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------|-------|-------|-------|------|--|

| DIS funct             | ion                                                                       |                                                                              |       |       |       |      |  |

| I <sub>OTP</sub>      | Input bias current                                                        | V <sub>DIS</sub> = 0 to Vth                                                  |       |       | -1    | μΑ   |  |

| Vth                   | Disable threshold                                                         |                                                                              | 4.275 | 4.5   | 4.725 | V    |  |

| Oscillato             | r and deadtime programming                                                | 3                                                                            |       |       |       |      |  |

| f <sub>osc</sub>      | Oscillation frequency                                                     | T <sub>J</sub> = 25 °C                                                       | 170   | 180   | 190   | kHz  |  |

|                       |                                                                           | Vcc = 9.2 to 22 V                                                            | 168   | 180   | 192   | kHz  |  |

| Vpk                   | Oscillator peak voltage                                                   | (1)                                                                          | 2.85  | 3     | 3.15  | V    |  |

| Vvy                   | Oscillator valley voltage                                                 | (1)                                                                          | 0.75  | 0.9   | 1.05  | V    |  |

|                       | Deadtime                                                                  |                                                                              |       | 0.42  |       |      |  |

| _                     | (V <sub>HVG</sub> high-to-low to V <sub>LVG</sub> low-to-high transition) | C <sub>T</sub> = 1 nF                                                        |       | 1.0   |       |      |  |

| T <sub>dead</sub>     | Deadtime (V <sub>LVG</sub> high-to-low                                    |                                                                              |       | 0.42  |       | - μs |  |

|                       | to V <sub>HVG</sub> low-to-high transition)                               | C <sub>T</sub> = 1 nF                                                        |       | 1.0   |       |      |  |

| Soft-start            |                                                                           |                                                                              |       |       |       |      |  |

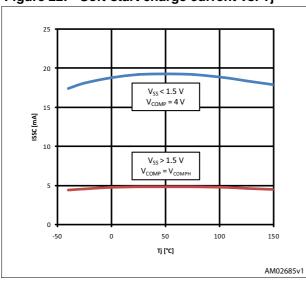

|                       | Charge current                                                            | $T_J = 25 ^{\circ}\text{C},  V_{SS} < 1.5 \text{V}, \ V_{COMP} = 4 \text{V}$ | 14    | 14 18 |       |      |  |

| I <sub>SSC</sub>      | Charge current                                                            | $T_J = 25$ °C, $V_{SS} > 1.5$ V,<br>$V_{COMP} = V_{COMPH}$                   | 3.4   | 4.7   | 5.6   | — μA |  |

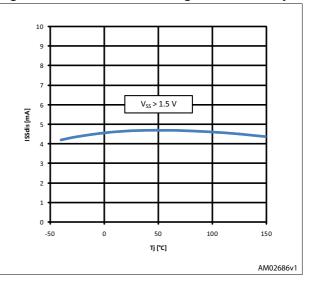

| I <sub>Ssdis</sub>    | Discharge current                                                         | V <sub>SS</sub> > 1.5 V                                                      | 3.4   | 4.7   | 5.6   | μΑ   |  |

| V <sub>Ssclamp</sub>  | High saturation voltage                                                   | V <sub>COMP</sub> = 4 V                                                      |       | 2     |       | ٧    |  |

| V <sub>SSDIS</sub>    | Disable level                                                             | $^{(2)}$ $V_{COMP} = V_{COMPH}$                                              | 4.85  | 5     | 5.15  | V    |  |

| $V_{SSLAT}$           | Latch-off level                                                           | $V_{COMP} = V_{COMPH}$                                                       |       | 6.4   |       | V    |  |

| PFC_STC               | P function                                                                |                                                                              |       |       |       |      |  |

| I <sub>leak</sub>     | High level leakage current                                                | $V_{PFC\_STOP} = Vcc,$<br>$V_{COMP} = 2 V$                                   |       |       | 1     | μΑ   |  |

| V <sub>L</sub>        | Low saturation level                                                      | $I_{PFC\_STOP} = 2 \text{ mA}$ $V_{COMP} = 1.5 \text{ V}$                    |       |       | 0.1   | V    |  |

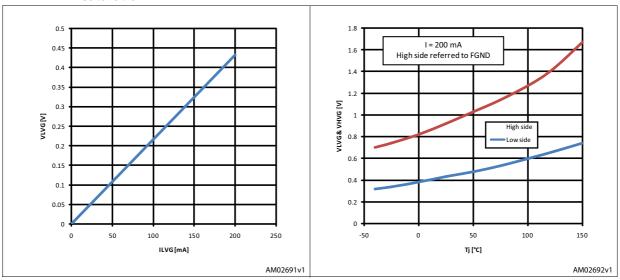

| Low-side              | gate driver (voltages referre                                             | d to GND)                                                                    |       |       | •     |      |  |

| V <sub>LVGL</sub>     | Output low-voltage                                                        | I <sub>sink</sub> = 200 mA                                                   |       |       | 1.0   | V    |  |

| $V_{LVGH}$            | Output high-voltage                                                       | I <sub>source</sub> = 5 mA                                                   | 12.8  | 13.3  |       | ٧    |  |

| I <sub>sourcepk</sub> | Peak source current (2)                                                   |                                                                              | -0.3  |       |       | Α    |  |

| I <sub>sinkpk</sub>   | Peak sink current (2)                                                     |                                                                              | 0.8   |       |       | Α    |  |

|                       |                                                                           | •                                                                            |       |       | •     | •    |  |

Table 4. Electrical characteristics (continued)

| Symbol                | Parameter                                         | Test condition                              | Min. | Тур. | Max. | Unit |  |  |  |  |

|-----------------------|---------------------------------------------------|---------------------------------------------|------|------|------|------|--|--|--|--|

| t <sub>f</sub>        | Fall time                                         |                                             |      | 40   |      | ns   |  |  |  |  |

| t <sub>r</sub>        | Rise time                                         |                                             |      | 80   |      | ns   |  |  |  |  |

|                       | UVLO saturation                                   | $Vcc = 0$ to $Vcc_{On}$ , $I_{sink} = 1$ mA |      |      | 1.1  | V    |  |  |  |  |

| High-side             | High-side gate driver (voltages referred to FGND) |                                             |      |      |      |      |  |  |  |  |

| V <sub>HVGL</sub>     | Output low-voltage                                | I <sub>sink</sub> = 200 mA                  |      |      | 1.5  | V    |  |  |  |  |

| V <sub>HVGH</sub>     | Output high-voltage                               | I <sub>source</sub> = 5 mA                  | 11   | 11.9 |      | V    |  |  |  |  |

| I <sub>sourcepk</sub> | Peak source current (2)                           |                                             | -0.3 |      |      | Α    |  |  |  |  |

| I <sub>sinkpk</sub>   | Peak sink current (2)                             |                                             | 0.8  |      |      | Α    |  |  |  |  |

| t <sub>f</sub>        | Fall time                                         |                                             |      | 40   |      | ns   |  |  |  |  |

| t <sub>r</sub>        | Rise time                                         |                                             |      | 80   |      | ns   |  |  |  |  |

|                       | Pull-down resistor                                |                                             |      | 25   |      | kΩ   |  |  |  |  |

<sup>1.</sup> Parameters tracking each other.

<sup>2.</sup> Parameters guaranteed by design.

# 5 Typical characteristics

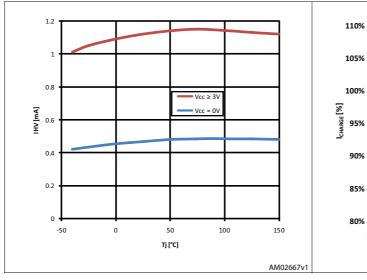

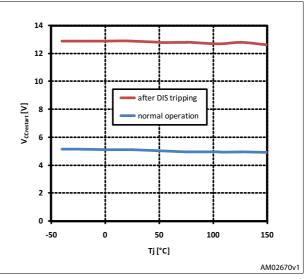

Figure 4. High-voltage generator ON-state Figure 5. sink current vs. Tj

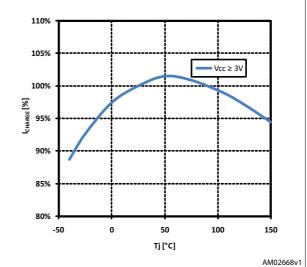

Figure 5. High-voltage generator output (Vcc charge current) vs. Tj

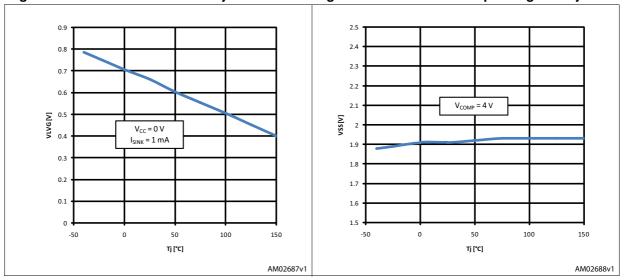

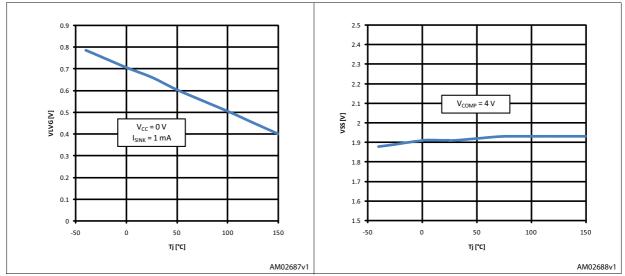

Figure 6. High-voltage generator start voltage vs. Tj

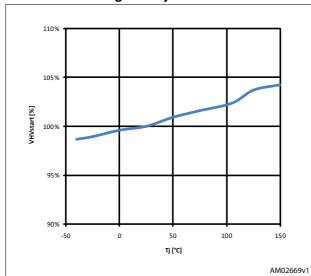

Figure 7. High-voltage generator Vcc restart voltage vs. Tj

12/41 Doc ID 14821 Rev 6

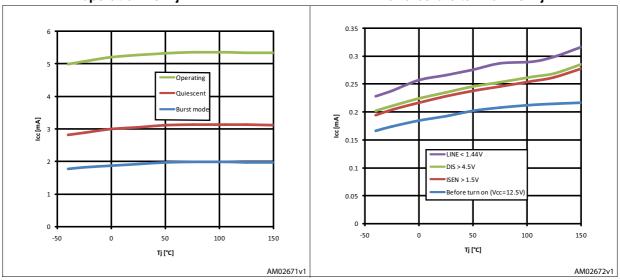

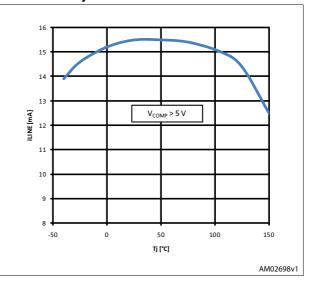

Figure 8. IC consumption during normal operation vs. Tj

Figure 9. IC consumption under protection and before turn-on vs. Tj

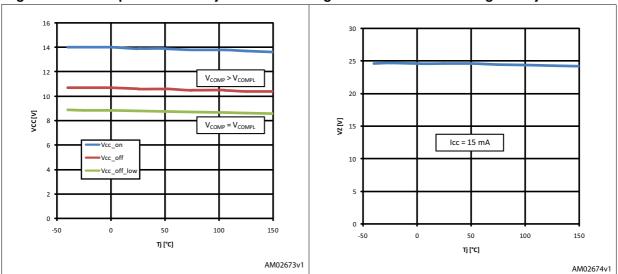

Figure 10. Startup & UVLO vs. Tj

Figure 11. Vcc Zener voltage vs. Tj

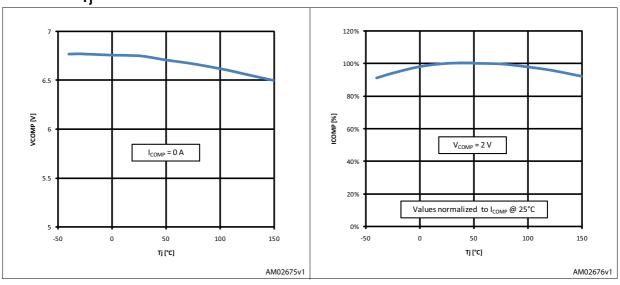

Figure 12. COMP voltage upper clamp level vs. Figure 13. COMP source current vs. Tj

Figure 14. COMP dynamic resistance vs. Tj Figure 15. Oscillator frequency vs. Tj

Figure 16. Oscillator ramp vs. Tj

Figure 17. Max. duty cycle vs. Tj

Figure 18. Current sense clamp vs. Tj

Figure 19. Disable level on current sense vs. Tj

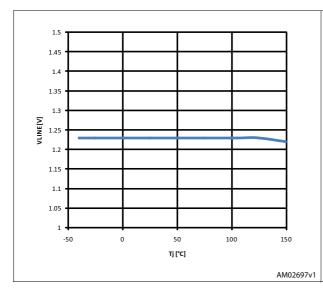

Figure 20. Reference voltage vs. Tj

5.1 5.08 5.04 V<sub>CC</sub> = 15 V I<sub>REF</sub> = 1 mA 5.02 4.98 4.96 4.94 4.92 4.9 -50 0 50 100 150

Tj [°C]

AM02683v1

Figure 21. DIS threshold vs. Tj

Figure 22. Soft-start charge current vs. Tj

Figure 23. Soft-start discharge current vs. Tj

Figure 24. UVLO saturation vs. Tj

Figure 25. Soft-start clamp voltage vs. Tj

Figure 26. UVLO saturation vs. Tj

Figure 27. Soft-start clamp voltage vs. Tj

Figure 28. Low-side gate drive output low saturation

Figure 29. Gate drive output low-voltage vs. Tj

Figure 30. Gate drive output high-voltage vs. Figure 31. High-side pull-down resistor vs. Tj

Figure 32. Burst mode thresholds vs. Tj

Figure 33. Burst mode hysteresis vs. Tj

Figure 34. Line sensing threshold vs. Tj

Figure 35. Line sensing current hysteresis vs. Tj

4

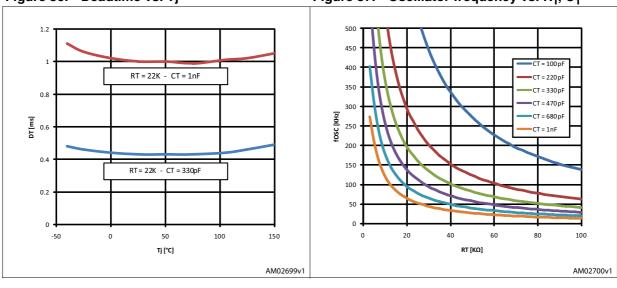

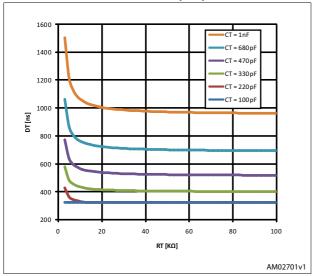

Figure 36. Deadtime vs. Tj

Figure 37. Oscillator frequency vs.  $R_T$ ,  $C_T$

Figure 38. Deadtime vs.  $R_T$ ,  $C_T$

#### **Application information** 6

The L6591 is an advanced current-mode PWM controller specific for fixed-frequency, peakcurrent-mode-controlled ZVS half bridge converters. In these converters the switches (MOSFET) are controlled with complementary duty cycle: the high-side MOSFET is driven ON for a duty cycle D and the low-side MOSFET for a duty cycle 1-D. For a proper operation the maximum allowed duty cycle must be limited below 50%.

An externally programmable deadtime TD inserted between the turn-off of one MOSFET and the turn-on of the other one ensures soft-switching and enables high-frequency operation with high efficiency and low EMI emissions. See Section 6.6: Oscillator and deadtime programming on page 28 section for more information on how to program T<sub>D</sub>.

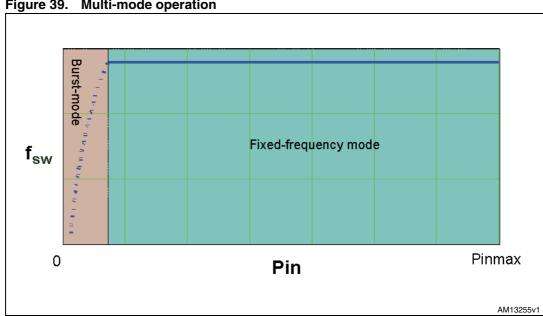

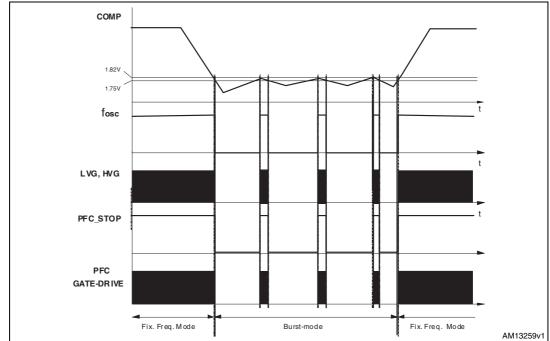

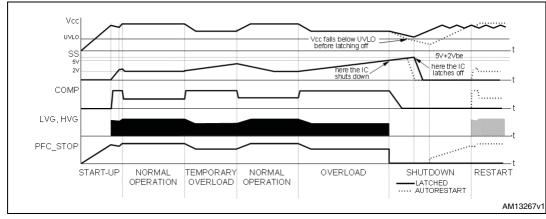

The device is able to operate in different modes (Figure 39), depending on the converter's load conditions:

- Fixed frequency at heavy load. A relaxation oscillator, externally programmable with a capacitor and a resistor generates a sawtooth and releases clock pulses during the falling edges of the sawtooth. In this region the low-side MOSFET is turned off by the even pulses of the clock signal and the high-side MOSFET is turned on after a delay; the high-side MOSFET is turned off and, after a delay, the low-side MOSFET is turned on in response to the control loop.

- Burst mode control with no or very light load. When the load is extremely light or disconnected, the converter enters a controlled on/off operation with fixed duty cycle, where a series of few switching cycles are spaced out by long periods where both MOSFET's are in OFF-state. A load decrease is then translated into a frequency reduction, which can go down even to few hundred hertz, thus minimizing all frequency-related losses and making it easier to comply with energy saving regulations. The peak current is very low and so no issue of audible noise arises.

Figure 39. Multi-mode operation

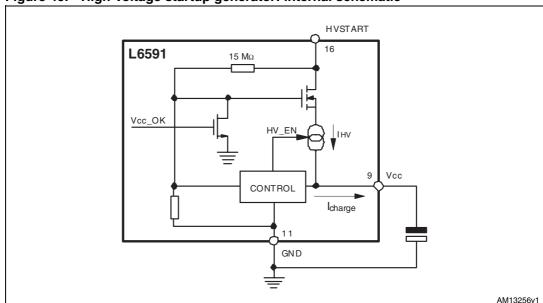

### 6.1 High-voltage startup generator

*Figure 40* shows the internal schematic of the high-voltage startup generator (HV generator). It is made up of a high-voltage N-channel FET, whose gate is biased by a 15 MW resistor, with a temperature-compensated current generator connected to its source.

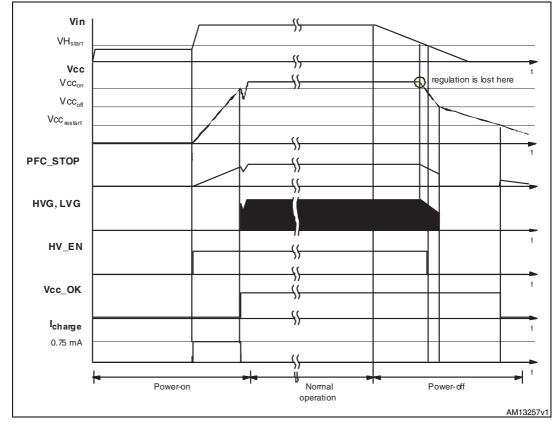

With reference to the timing diagram of *Figure 41*, when power is first applied to the converter the voltage on the bulk capacitor (Vin) builds up and, as it reaches about 80 V, the HV generator is enabled to operate (HV\_EN is pulled high) and draws about 1 mA. This current, diminished by the IC consumption, charges the bypass capacitor connected between pin Vcc (9) and ground and makes its voltage rise almost linearly.

As the Vcc voltage reaches the startup threshold (13.5 V typ.) the IC starts operating and the HV generator is cut off by the Vcc\_OK signal asserted high. The IC is powered by the energy stored in the Vcc capacitor until the self-supply circuit develops a voltage high enough to sustain the operation. The residual consumption of this circuit is just the one on the 15 MW resistor ( $\approx 10$  mW at 400 Vdc), typically 50-70 times lower, under the same conditions, as compared to a standard startup circuit made with an external dropping resistor.

Figure 40. High-voltage startup generator: internal schematic

Figure 41. Timing diagram: normal power-up and power-down sequences

At converter power-down the system loses regulation as soon as the input voltage is so low that either peak current or maximum duty cycle limitation is tripped. Vcc then drops and stops IC activity as it falls below the UVLO threshold (10.5 V typ.). The Vcc\_OK signal is deasserted as the Vcc voltage goes below a threshold Vcc<sub>rest</sub> located at about 5 V. The HV generator can now restart but, if Vin < Vin<sub>start</sub>, as shown in *Figure 41*, HV\_EN is de-asserted too and the HV generator is disabled. This prevents converter restart attempts and ensures monotonic output voltage decay at power-down.

The low restart threshold Vcc<sub>rest</sub> ensures that, during short-circuits, the restart attempts of the L6591 has a very low repetition rate, as shown in the timing diagram of *Figure 42*, and that the converter works safely with extremely low power throughput.

The restart threshold of the HV generator is changed when any latched disable function of the IC is invoked to ensure a real latch-off. For more details see *Section 6.5*.

Figure 42. Timing diagram showing short-circuit behavior (SS pin clamped below 5 V)

### 6.2 Operation at no load or very light load

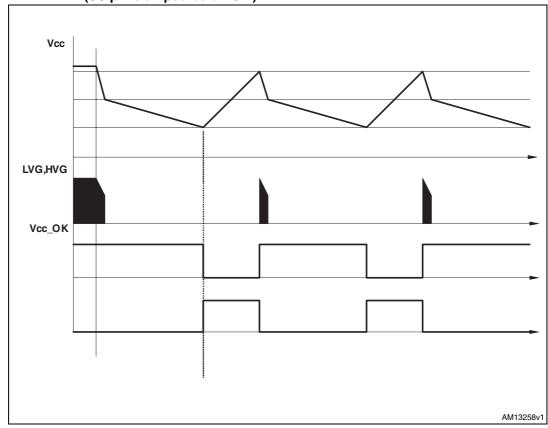

When the PWM control voltage at the COMP pin falls below a threshold located at 1.75 V, the IC is disabled with both the high-side and the low-side MOSFET kept in OFF-state, the oscillator stopped and the quiescent consumption very much reduced to minimize Vcc capacitor discharge.

The control voltage now increases as a result of the feedback reaction to the energy delivery stop and, as it exceeds 1.82 V, the IC restarts switching. After a while, the control voltage goes down again in response to the energy burst and stops the IC. In this way the converter works in a burst mode fashion with a nearly constant peak current. A further load decrease then causes a frequency reduction, which can go down even to few hundred hertz, therefore minimizing all frequency-related losses and making it easier to comply with energy saving regulations. The timing diagram of *Figure 43* illustrates this kind of operation, showing the most significant signals.

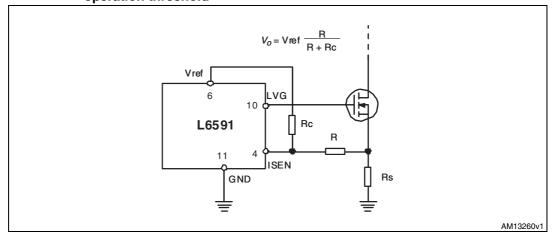

If it is necessary to decrease the intervention threshold of the burst mode operation, this can be done by adding a small DC offset on the current sense pin, as shown in *Figure 44*.

Note:

The offset reduces the available dynamics of the current signal; therefore, the value of the sense resistor must be determined taking this offset into account.

Figure 43. Load-dependent operating modes: timing diagram

Figure 44. Addition of an offset to the current sense lowers the burst mode operation threshold

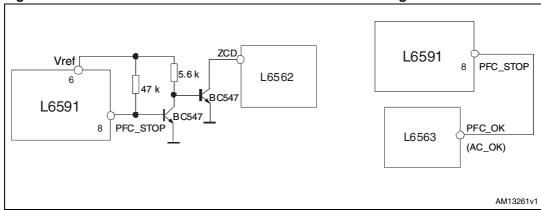

To help the user meet energy saving requirements even in power-factor-corrected systems, where a PFC pre-regulator precedes the DC-DC converter, the L6591 allows that the PFC pre-regulator can be turned off during burst mode operation, therefore eliminating the noload consumption of this stage (0.5÷1 W). There is no compliance issue in that, because EMC regulations on low-frequency harmonic emissions refer to nominal load, no limit is envisaged when the converter operates with light or no load.

To do so, the L6591 provides the PFC\_STOP (#8) pin: it is an open collector output, normally open, that is asserted low when the IC is idle during burst mode operation. This signal is externally used for switching off the PFC controller and the pre-regulator, as shown in *Figure 45*. When the L6591 is in UVLO, the pin is kept open, to let the PFC controller start first.

Figure 45. How the L6591 can switch off a PFC controller at light load

#### 6.3 PWM control block

The device is specific to secondary feedback. Typically, there is a TL431 at the secondary side and an optocoupler that transfers output voltage information to the PWM control at the primary side, crossing the isolation barrier. The PWM control input (pin #7, COMP) is driven directly by the phototransistor's collector (the emitter is grounded) to modulate the duty cycle. It is recommended to place a small filter capacitor between the pin and GND (#11), as close to the IC as possible to reduce switching noise pick-up, to set a pole in the output-to-control transfer function.

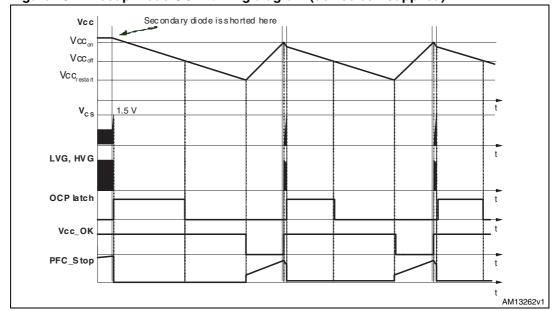

### 6.4 PWM comparator, PWM latch and hiccup mode OCP

The PWM comparator senses the voltage across the current sense resistor (Rs) and, by comparing it with the programming signal derived by the voltage on pin COMP (#7), determines the exact time when the high-side MOSFET is to be switched off. The PWM latch avoids spurious switching, which may be caused by the noise generated ("double-pulse suppression").

A second comparator senses the voltage on the current sense input and shuts the IC down if the voltage at the pin exceeds 1.5 V. Such an anomalous condition is typically generated by either a short-circuit of one of the secondary rectifiers or a shorted secondary winding or a saturated transformer. This condition is latched as long as the IC is supplied; therefore if the IC is supplied by an external source, it is necessary to disconnect the source to restart the IC.

To distinguish an actual malfunction from a disturbance (e.g. induced during ESD tests), the first time the comparator is tripped the protection circuit enters a "warning state". If, in the next switching cycle, the comparator is not tripped, a temporary disturbance is assumed and the protection logic is reset in its idle state; if the comparator is tripped again a real malfunction is assumed and the L6591 is stopped.

If the device is self-supplied, no energy is coming from the self-supply circuit, the voltage on the Vcc capacitor then decays and crosses the UVLO threshold after some time, which clears the latch. The internal startup generator is still off and the Vcc voltage still needs to then go below its restart voltage before the Vcc capacitor is charged again and the IC restarted. Ultimately, either of the above mentioned failures results in a low-frequency intermittent operation (hiccup mode operation), with very low stress on the power circuit. The timing diagram of *Figure 46* illustrates this operation.

26/41 Doc ID 14821 Rev 6

Figure 46. Hiccup mode OCP: timing diagram (device self-supplied)

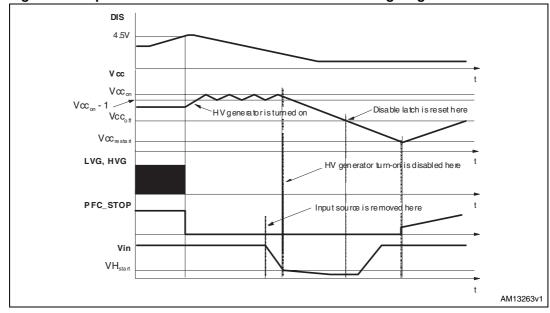

### 6.5 Latched shutdown

The L6591 is equipped with a comparator having the non-inverting input externally available at the DIS pin (#2) and with the inverting input internally referenced to 4.5 V. As the voltage on the pin exceeds the internal threshold, the IC is immediately shut down and its consumption reduced to a low value.

The information is latched and it is necessary to let the voltage on the Vcc pin go below the UVLO threshold to reset the latch and restart the IC. To keep the latch supplied as long as the converter is connected to the input source, the HV generator is activated periodically so that Vcc oscillates between the startup threshold  $V_{\rm ccON}$  and  $V_{\rm ccON}-1$  V. It is then necessary to disconnect the converter from the input source to restart the IC. This operation is shown in the timing diagram of *Figure 47*. Activating the HV generator in this way cuts its power dissipation approximately by three (as compared to the case of continuous conduction) and keeps peak silicon temperature close to the average value.

Figure 47. Operation after latched disable activation: timing diagram

This function is useful to easily implement a latched over temperature protection by biasing the pin with a divider from VREF, where the upper resistor is an NTC physically located close to a heating element like the MOSFET, or the secondary diode or the transformer. An OVP can be implemented as well, e.g. by sensing the output voltage and transferring an overvoltage condition via an optocoupler.

### 6.6 Oscillator and deadtime programming

The oscillator is programmed externally by means of a resistor-capacitor network ( $R_T$ ,  $C_T$ ) connected from pin OSC (#5) to VREF (#6) and to ground respectively. Once the oscillator frequency and the deadtime duration is chosen, the values of RT and CT can be calculated as:

#### **Equation 1**

$$R_{T} = 50 + \frac{1150}{f_{osc} (T_{d} - 125 \cdot 10^{-9})}$$

#### **Equation 2**

$$C_T = 1.39 \cdot \frac{1}{f_{osc}} \cdot \frac{R_T - 1200}{R_T (R_T - 50)}$$

After having selected the commercial values for  $R_T$  and  $C_T$ , the oscillator frequency ( $f_{osc}$ ) can be verified with good approximation using the following formula:

#### **Equation 3**

$$f_{osc} \approx \frac{1.39}{(C_T (R_T + 1150))}$$

**577**

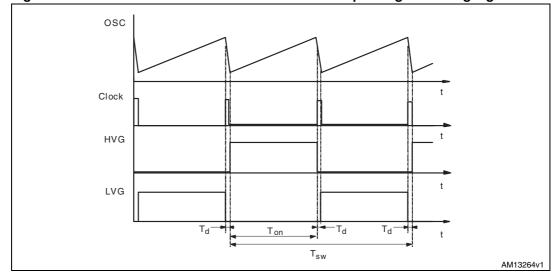

During the negative-going ramp of the sawtooth, a clock pulse is released. A T-flip-flop, along with a logic circuit, separates the odd and the even clock pulses. The even ones turn off the low-side MOSFET first and, after a dead time  $T_d$ , turn on the high-side MOSFET. Normally, the high-side MOSFET is turned off (and the low-side MOSFET turned on after the deadtime  $T_d$ ) in response to the control loop; in the case of overload, it is the overcurrent comparator to do the job or, in the case of open control loop, the odd clock pulses limit the maximum ON-time within one oscillator cycle. In this way, the maximum duty cycle is limited right below 50% and the operating frequency of the converter is half that of the oscillator. Precisely, with reference to the waveforms in *Figure 50*, where  $T_{sw}$ = 2/ $f_{osc}$ , the maximum achievable duty cycle is:

#### **Equation 4**

$$D_{\text{max}} = \frac{\frac{T_{\text{SW}}}{2} - T_{\text{d}}}{T_{\text{SW}}} = 0.5 - \frac{T_{\text{d}}}{T_{\text{SW}}} = 0.5 \left(1 - T_{\text{d}} \, f_{\text{osc}}\right)$$

At startup, the first clock pulse turns on the low-side MOSFET for 10 oscillator cycles to charge the bootstrap capacitor and then the high-side MOSFET switches on. When the IC resumes switching during burst mode operation, the first clock pulse turns on the low-side MOSFET first to charge the bootstrap capacitor, and just after the second clock pulse the high-side MOSFET switches on. In this way the bootstrap capacitor is always charged and ready to supply the high-side floating driver. The oscillator waveforms are illustrated in *Figure 50* as well.

The deadtime  $T_d$  equals the duration of the negative-going ramp of the oscillator sawtooth plus an internal delay of 125 ns; therefore, it depends on the timing capacitor  $C_T$  and the resistor  $R_T$  and is given by the approximate relationship:

#### **Equation 5**

$$T_d = C_T \frac{2.1}{2.54 \cdot 10^{-3} - \frac{3.05}{R_T}} + 125 \cdot 10^{-9}$$

There is an internal 325 ns limit to the minimum  $T_d$  value, to make sure that no hazardous condition of shoot-through can be generated, however it is recommended not to use capacitor values lower than 220 pF.

Oscillator waveforms and their relationship with gate-driving signals

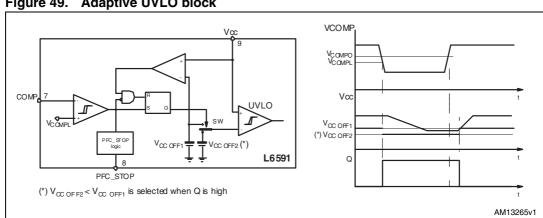

#### 6.7 **Adaptive UVLO**

A major problem when optimizing a converter for minimum no load consumption is that the voltage generated by the self-supply system under these conditions falls considerably as compared even to a few mA load. This very often causes the IC supply voltage Vcc to drop and go below the UVLO threshold of the controller so that the operation becomes intermittent, which is undesired. A low UVLO threshold would be helpful but it may be an issue when driving the MOSFETS with a sufficient gate-drive voltage at heavy load during power-off.

To help overcome this problem, the L6591, besides reducing its own consumption during burst mode operation, also features a proprietary adaptive UVLO function. It consists of shifting the UVLO threshold downwards at light load, namely when the voltage at the COMP pin falls below a threshold  $V_{COMPL}$  internally fixed, so as to provide more headroom. To prevent any malfunctioning during transients from minimum to maximum load, the normal (higher) UVLO threshold is re-established when the voltage at the COMP pin exceeds V<sub>COMPL</sub> (with some mV hysteresis) and Vcc has exceeded the normal UVLO threshold (see Figure 51). The normal UVLO threshold ensures that under heavy load conditions the MOSFET is driven with an appropriate gate voltage.

Figure 49. Adaptive UVLO block

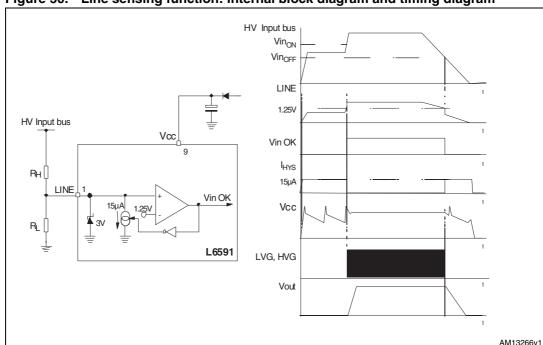

### 6.8 Line sensing function

This function basically stops the IC as the input voltage to the converter falls below the specified range and lets it restart as the voltage goes back within the range. The sensed voltage can be either the rectified and filtered mains voltage, in which case the function acts as a brownout protection, or, in systems with a PFC pre-regulator front-end, the output voltage of the PFC stage, in which case the function serves as a power-on and power-off sequencing.

L6591 shutdown upon input undervoltage is accomplished by means of an internal comparator, as shown in the block diagram of *Figure 52*, whose non-inverting input is available at the LINE pin (#1). The comparator is internally referenced to 1.25 V and disables the IC if the voltage applied at the LINE pin is below the internal reference. Under these conditions the soft-start discharges, the pin PFC\_STOP is open and the consumption of the IC is reduced. PWM operation is re-enabled as the voltage on the pin is above the reference. The comparator is provided with current hysteresis instead of a more usual voltage hysteresis: an internal 15  $\mu$ A current sink is ON as long as the voltage applied at the LINE pin is below the reference and is OFF if the voltage is above the reference.

Figure 50. Line sensing function: internal block diagram and timing diagram

This approach provides an additional degree of freedom: it is possible to set the ON threshold and the OFF threshold separately by properly choosing the resistors of the external divider (see below). With voltage hysteresis, instead, fixing one threshold automatically fixes the other one depending on the built-in hysteresis of the comparator.

With reference to *Figure 52*, the following relationships can be established for the ON  $(V_{inON})$  and OFF  $(V_{inOFF})$  thresholds of the input voltage:

#### **Equation 6**

$$\frac{Vin_{ON} - 1.25}{R_H} = 15 \cdot 10^{-6} + \frac{1.25}{R_L} \qquad \qquad \frac{Vin_{OFF} - 1.25}{R_H} = \frac{1.25}{R_L}$$

which, solved for R<sub>H</sub> and R<sub>L</sub>, yields:

#### **Equation 7**

$$R_{H} = \frac{Vin_{ON} - Vin_{OFF}}{15 \cdot 10^{-6}}; \qquad R_{L} = R_{H} \frac{1.25}{Vin_{OFF} - 1.25}$$

While the line undervoltage is active the startup generator keeps on working but there is no PWM activity, therefore the Vcc voltage continuously oscillates between the startup and the UVLO thresholds, as shown in the timing diagram of *Figure 52*.

The LINE pin, while the device is operating, is a high impedance input connected to high value resistors, it is therefore prone to pick-up noise, which may alter the OFF threshold or give origin to undesired switch-off of the IC during ESD tests. It is possible to bypass the pin to ground with a small film capacitor (e.g. 1-10 nF) to prevent any malfunctioning of this kind. Tie to Vcc (#9) with a 220 to 330 k $\Omega$  resistor if the function is not used.

### 6.9 Soft-start and delayed latched shutdown upon overcurrent

At device startup, a capacitor (Css) connected between the SS pin (#4) and ground is charged by an internal current generator, I<sub>SS1</sub>, from zero up to about 2 V, where it is clamped. During this ramp, the overcurrent setpoint progressively raises from zero the final value (0.8 V). The time needed for the overcurrent setpoint to reach its steady-state value, referred to as soft-start time, is approximately:

#### **Equation 8**

$$T_{SS} = 0.8 \frac{C_{SS}}{I_{SS1}}$$

During the ramp, the MOSFET duty cycle increases progressively, therefore controlling the startup inrush current. Furthermore, all the functions that monitor the voltage on the COMP pin are disabled.

The soft-start pin is also invoked whenever the control voltage (COMP) saturates high, which reveals an open-loop condition for the feedback system. This condition very often occurs at startup, but may also be caused by either a control loop failure or a converter overload/short-circuit.

Figure 51. Soft-start pin operation under different operating conditions

While, in the case of feedback loop failure, the system must be stopped quickly to prevent the output voltage from reaching too high values, an overload or a short-circuit does not generally need such fast intervention. The L6591 makes it easier to handle such conditions: the 2 V clamp on the SS pin is removed and a second internal current generator  $I_{SS2} = I_{SS1}$ /4 keeps on charging Css. If the voltage reaches 5 V, the IC is disabled, if it is allowed to reach 2  $V_{BE}$  over 5 V, the IC is latched off. In the former case the resulting behavior is identical to that under short-circuit illustrated in *Figure 46*; in the latter case the result is identical to that of *Figure 47*. The time delay before stopping switching upon overload is:

#### **Equation 9**

$$T_{delay} = 12 \frac{C_{SS}}{I_{SS1}}$$

If the overload disappears before the SS voltage reaches 5 V, the  $I_{\rm SS2}$  generator is turned off and the voltage gradually brought back down to 2 V. A diode, with the anode to the SS pin and the cathode connected to the VREF pin (#6), allows the user to select either an auto-restart mode or a latch-mode behavior upon overload.

If latch-mode behavior is desired also for converter short-circuit, make sure that the supply voltage of the IC never falls below the UVLO threshold before activating the latch. *Figure 20* shows soft-start pin behavior under different operating conditions.

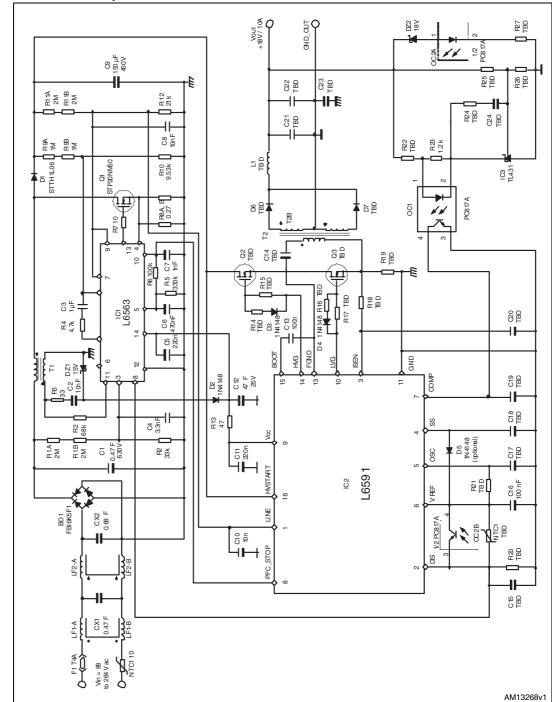

*Figure 52* shows a typical high-power adapter application that uses the L6591 in conjunction with the L6563 PFC controller.

### 7 Summary of L6591 power management functions

It has been shown that the device is provided with a number of power management functions: different operating mode upon loading conditions, protection functions, as well as interaction with the PFC pre-regulator. To help the user familiarize themselves with these functions, in the following tables all of the themes are summarized with their respective activation mechanisms and the resulting status of the most important pins. This can be useful not only for a correct use of the IC but also for diagnostic purposes: especially at prototyping/debugging stage; it is quite common to bump into unwanted activation of some function, and these tables can be used as a sort of quick troubleshooting guide.

Table 5. Light load management

| Feature          | Description                                                                        | Caused by                                 | IC<br>behavior                 | Vcc<br>restart<br>[V] | Consumption [mA]                                                 | PFC_STOP                                                   | SS           | osc                                                            |

|------------------|------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------|-----------------------|------------------------------------------------------------------|------------------------------------------------------------|--------------|----------------------------------------------------------------|

| Burst mode       | Controlled<br>ON-OFF<br>operation for<br>low power<br>consumption<br>at light load | V <sub>COMP</sub> < V <sub>COMPBon</sub>  | Pulse<br>skipping<br>operation | N.A.                  | 2 mA max.<br>when<br>V <sub>COMP</sub> <<br>V <sub>COMPBon</sub> | Active (low) when V <sub>COMP</sub> < V <sub>COMPBon</sub> | No<br>change | Stopped<br>when<br>V <sub>COMP</sub> <<br>V <sub>COMPBon</sub> |

| Adaptive<br>UVLO | Extended<br>Vcc range at<br>light load                                             | V <sub>COMP</sub> <<br>V <sub>COMPL</sub> | UVLO<br>threshold<br>reduction | N.A.                  | N.A.                                                             | No change                                                  | No<br>change | Run                                                            |

Table 6. Protection

| Protection                      | Description                            | Caused by                                                                   | IC<br>behavior                  | Vcc<br>restart<br>[V] | IC Iq<br>[mA] | VREF<br>[V] | SS   | V <sub>COMP</sub><br>[V] | osc<br>[V] | PFC_STOP     |

|---------------------------------|----------------------------------------|-----------------------------------------------------------------------------|---------------------------------|-----------------------|---------------|-------------|------|--------------------------|------------|--------------|

| OLP                             | Output<br>overload<br>protection       | $V_{COMP} = V_{COMPH} $ $V_{SS} > V_{SSDIS}$                                | Auto-<br>restart <sup>(1)</sup> | 5                     | 1.2           | 5           | N.A. | 0                        | Stop       | Active (low) |

|                                 |                                        | $V_{COMP} = V_{COMPH} V_{SS} > V_{SSLAT}$                                   | Latched                         | 13                    | 0.35<br>max.  | 0           | N.A. | 0                        | Stop       | Active (low) |

| Short-<br>circuit<br>protection | Output short-<br>circuit<br>protection | $V_{COMP} = V_{COMPH} $ $V_{SS} > V_{SSDIS}$                                | Auto-<br>restart <sup>(1)</sup> | 5                     | 1.2           | 5           | N.A. | 0                        | Stop       | Active (low) |

|                                 |                                        | V <sub>COMP</sub> = V <sub>COMPH</sub> V <sub>SS</sub> > V <sub>SSLAT</sub> | Latched                         | 13                    | 0.35<br>max.  | 0           | N.A. | 0                        | Stop       | Active (low) |

34/41 Doc ID 14821 Rev 6

Table 6. Protection (continued)

| Protection          | Description                                                                 | Caused by                                                                | IC<br>behavior   | Vcc<br>restart<br>[V] | IC Iq<br>[mA] | VREF<br>[V] | ss | V <sub>COMP</sub><br>[V] | osc<br>[V] | PFC_STOP            |

|---------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------|-----------------------|---------------|-------------|----|--------------------------|------------|---------------------|

| Protection          | Description                                                                 | Caused by                                                                | IC<br>behavior   | Vcc<br>restart<br>[V] | IC Iq<br>[mA] | VREF<br>[V] | ss | V <sub>COMP</sub><br>[V] | osc<br>[V] | PFC_STOP            |

| 2 <sup>nd</sup> OCP | Transformer<br>saturation or<br>shorted<br>secondary<br>diode<br>protection | V <sub>ISEN</sub> ><br>1.5 V for 2<br>consecutive<br>switching<br>cycles | Latched (2)      | 5                     | 0.35<br>max.  | 0           | 0  | 0                        | Stop       | Active (low)        |

| DISABLE             | Externally programmabl e latched protection                                 | V <sub>DIS</sub> > 4.5 V                                                 | Latched          | 13                    | 0.35<br>max.  | 0           | 0  | 0                        | Stop       | Active (low)        |

| Brownout            | Mains<br>undervoltage<br>protection                                         | V <sub>LINE</sub> < 1.25 V                                               | Auto-<br>restart | 5                     | 0.35<br>max.  | 0           | 0  | 0                        | Stop       | Not active (high Z) |

- 1. Use one external diode from SS (#14) to VREF (#10), cathode to VREF.

- 2. The condition is latched as long as the IC is supplied; the HV generator is not invoked.

Note: All values are typical unless otherwise specified.

It is worth remembering that "auto-restart" means that the device works intermittently as long as the condition that is activating the function is not removed; "Latched" means that the device is stopped as long as the unit is connected to the input power source and the unit must be disconnected for some time from the source in order for the device (and the unit) to restart.

Figure 52. L6591 typical application: 180 W, WRM, power-factor-corrected AC-DC adapter

**577**

L6591 ECOPACK®

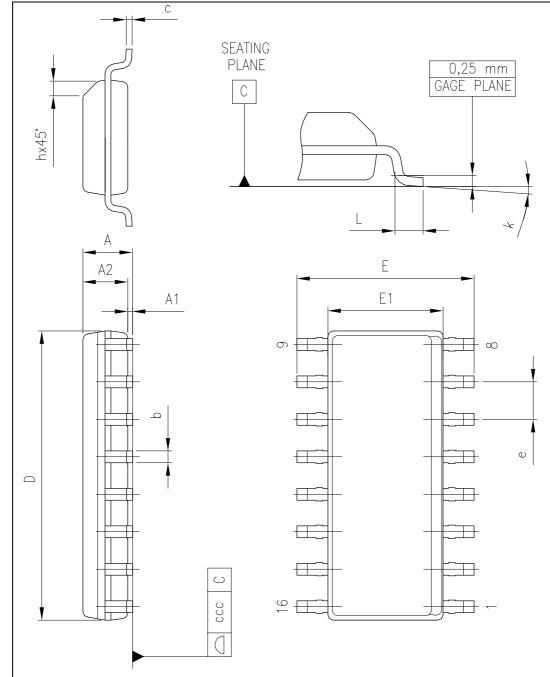

# 8 ECOPACK®

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: <a href="www.st.com">www.st.com</a>. ECOPACK is an ST trademark.

Table 7. SO16 narrow mechanical data

| Dim.   | mm   |      |      |  |  |  |

|--------|------|------|------|--|--|--|

| Dilli. | Min. | Тур. | Max. |  |  |  |

| Α      |      |      | 1.75 |  |  |  |

| A1     | 0.1  |      | 0.25 |  |  |  |

| A2     | 1.25 |      |      |  |  |  |

| b      | 0.31 |      | 0.51 |  |  |  |

| С      | 0.17 |      | 0.25 |  |  |  |

| D      | 9.8  | 9.9  | 10   |  |  |  |

| E      | 5.8  | 6    | 6.2  |  |  |  |

| E1     | 3.8  | 3.9  | 4    |  |  |  |

| е      |      | 1.27 |      |  |  |  |

| h      | 0.25 |      | 0.5  |  |  |  |

| L      | 0.4  |      | 1.27 |  |  |  |

| k      | 0    |      | 8    |  |  |  |

| ccc    |      |      | 0.1  |  |  |  |

Figure 53. SO16 narrow mechanical data

L6591 Order codes

# 9 Order codes

Table 8. Order codes

| Order codes | Package | Packaging     |

|-------------|---------|---------------|

| L6591       | SO16N   | Tube          |

| L6591TR     | SO16N   | Tape and reel |

Revision history L6591

# 10 Revision history

Table 9. Document revision history

| Date          | Revision | Changes                                                                                                                             |

|---------------|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| 19-Jun-2008   | 1        | Initial release                                                                                                                     |

| 17-Oct-2008   | 2        | Updated: Section 1: Description on page 3                                                                                           |

| 24-Mar-2009   | 3        | Updated: Table 4 on page 8                                                                                                          |

| 19-May-2009   | 4        | Updated: Table 4 on page 8, Section 6.7 on page 30                                                                                  |

| 07-Mar-2011   | 5        | Added: Section 5 on page 12 Updated: Figure 1 on page 1, Table 4 on page 8                                                          |

| 26-Jul-2012 6 |          | Modified: I <sub>COMP</sub> value on <i>Table 4: Electrical characteristics on page 8</i> Minor text changes to improve readability |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.