# ST1PS01

### Datasheet

# 400 mA nano-quiescent synchronous step-down converter with digital voltage selection and Power Good

Flip-Chip8 (1.14x1.44 mm)

### Features

- 500 nA input quiescent current at V<sub>IN</sub>=3.6 V (not switching)

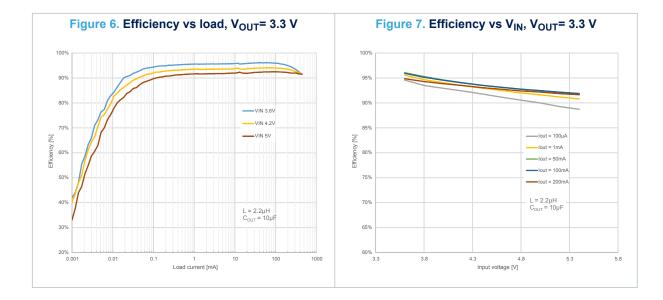

- 94% typical efficiency at 1 mA load (V<sub>IN</sub>=3.6 V, V<sub>OUT</sub>=3.3 V)

- 100% duty cycle

- 1.8 V to 5.5 V input operating range

- Undervoltage lockout: 1.57 V (V<sub>IN</sub> falling, typ.)

- Up to 400 mA output current capability

- Low power control operation for the best efficiency

- Embedded soft-start circuit

- Tiny external components: L=2.2 µH typ.

- Selectable output voltages: 0.625 V to 3.3 V

- Output voltage Power Good

- $\pm 1.5\%$  output voltage accuracy (V<sub>OUT</sub>, T<sub>A</sub> = 25 °C)

- Dynamic output voltage selection (D0, D1)

- Available in Flip-Chip package

### **Applications**

- Wearable applications

- Personal tracking monitors

- Smart watches, sport bands

- Energy harvesting, wireless sensors

- Wearable and fitness accessories

- Industrial sensors, portable low power devices

- Single cell Li-Ion battery applications

- Bluetooth<sup>®</sup> low energy

- Zigbee

lectronics sales office

### Description

The ST1PS01 is a nano-quiescent miniaturized synchronous step-down converter, which is able to provide up to 400 mA output current with an input voltage ranging from 1.8 V to 5.5 V.

This converter is specifically designed for applications where high efficiency, PCB size and thickness are the key factors. The output voltage can be set using two digital control inputs, a V<sub>OUT</sub> from 0.625 V to 3.3 V can be dynamically selected. Thanks to the enhanced PCC (peak current control) the ST1PS01 reaches very high efficiency conversion using just a 2.2  $\mu$ H inductor and two small capacitors. Advanced design circuitry is implemented to minimize the quiescent current. The device is available in Flip-Chip package.

Product status link ST1PS01

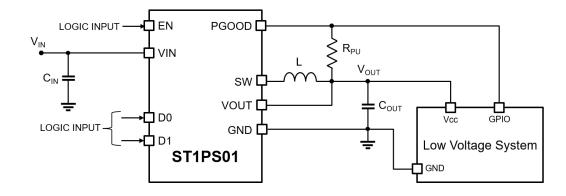

# 1 Application schematic

57

### Figure 1. ST1PS01 application schematic

### Table 1. Typical external components

| Component        | Description                           | Value | Size - imperial (metric) |

|------------------|---------------------------------------|-------|--------------------------|

| C <sub>IN</sub>  | Ceramic capacitor with low ESR values | 10 µF | 0603 (1608)              |

| C <sub>OUT</sub> | Ceramic capacitor with low ESR values |       | 0603 (1608)              |

| L                | Inductor                              |       | 0806 (2016)              |

| R <sub>PU</sub>  | Pull-up resistor                      | 1 MΩ  | 0402 (1005)              |

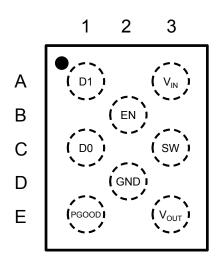

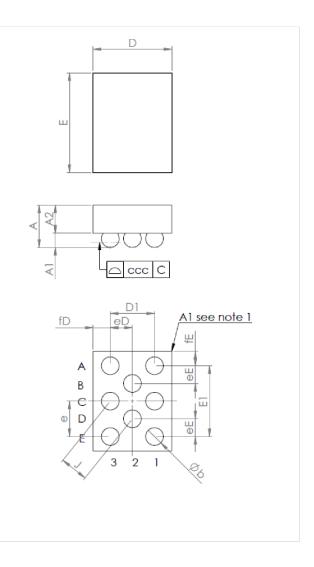

# 2 Pin configuration

57

### Figure 2. Flip-Chip8 package (top through view)

### Table 2. Pin description

| Name             | Bump name | Description                                                                                                     |

|------------------|-----------|-----------------------------------------------------------------------------------------------------------------|

| V <sub>IN</sub>  | A3        | Input supply voltage. Bypass this pin to ground with a 10 $\mu\text{F}$ capacitor                               |

| SW               | C3        | Switching output. Inductor connection                                                                           |

| V <sub>OUT</sub> | E3        | Sense pin used to monitor output voltage                                                                        |

| EN               | B2        | Enable pin. High logic level turns on the IC. $V_{IN}$ referred                                                 |

| GND              | D2        | Ground                                                                                                          |

| D1               | A1        | Output voltage selection inputs (Refer to the Section 5                                                         |

| D0               | C1        | Output voitage selection inputs (relet to the Section 5                                                         |

| PGOOD            | E1        | Open drain output. It is in high impedance when the output voltage reaches 97.5% of the target $V_{\mbox{OUT}}$ |

### 3 Functional pin description

#### GND

Device ground pin.

### VIN

Supply voltage. This pin supplies power to the internal analog and digital circuitries when voltage is higher than  $V_{UVLO}$ . Bypass this pin to GND with a 10  $\mu$ F ceramic capacitor. Input capacitor C<sub>IN</sub> must be chosen with low ESR to reduce the input voltage ripple.

#### SW

Inductor connection to internal PMOS and NMOS switches.

#### VOUT

Output voltage sense input. It provides the feedback voltage level to the regulation circuitry. 10  $\mu$ F output capacitor C<sub>OUT</sub> must be connected close to the pin or through a short trace and should have low ESR to reduce the output voltage ripple.

#### EN

Enable pin. A logic low level on this pin disables the device. High level enables the device. Do not leave this pin floating.

### D0, D1

Output voltage selection pins. See the Section 5 for  $V_{OUT}$  selection. Do not leave these pins floating. These pins can be dynamically changed during operation.

#### PGOOD

Power Good open drain output. If used it requires a pull-up resistor to hold a high level signal. High impedance indicates that  $V_{OUT}$  is above proper good threshold.

# 4 Maximum ratings

| Symbol                | Parameter                                   | Value                         | Unit |

|-----------------------|---------------------------------------------|-------------------------------|------|

| V <sub>IN</sub>       | Power and signal supply voltage             | - 0.3 to + 6.5                | V    |

| EN, D0, D1            | Logic input pins                            | - 0.3 to + 6.5                | V    |

| V <sub>OUT</sub> , SW | Output signal monitoring and switching pins | -0.3 to V <sub>IN</sub> + 0.3 | V    |

| PGOOD                 | Power Good open drain output pin            | - 0.3 to + 6.5                | V    |

| T <sub>AMB</sub>      | Operating ambient temperature               | -40 to 85                     | °C   |

| TJ                    | Junction temperature                        | -40 to 125                    | °C   |

| T <sub>STG</sub>      | Storage temperature                         | -55 to 150                    | °C   |

#### Table 3. Absolute maximum ratings

Note:

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied

### Table 4. Thermal data

| Symbol            | Parameter                           | Flip-Chip8 | Unit |

|-------------------|-------------------------------------|------------|------|

| R <sub>thJA</sub> | Thermal resistance junction-ambient | 60         | °C/W |

### Table 5. Recommended operating conditions

| Symbol          | Parameter            | Min. | Тур. | Max. | Unit |

|-----------------|----------------------|------|------|------|------|

| V <sub>IN</sub> | Input supply voltage | 1.8  |      | 5.5  | V    |

## 5 Electrical characteristics

57

$C_{IN}$ = 10  $\mu$ F,  $C_{OUT}$ = 10  $\mu$ F, L=2.2  $\mu$ H, RPU=1 MOhm,  $V_{IN}$ =3.6 V,  $V_{EN}$ =  $V_{IN},$   $V_{OUT}$ =1.8 V,  $T_A$ =25 °C unless otherwise specified.

| Symbol                                          | Parameter                                                  | Test conditions                                                                                           | Min.  | Тур. | Max. | Uni   |

|-------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------|------|------|-------|

| General                                         | section                                                    | '                                                                                                         |       |      |      |       |

|                                                 |                                                            | EN=V <sub>IN</sub> ,                                                                                      |       |      |      |       |

| IQ                                              | Quiescent current                                          | device does not switch (V <sub>OUT</sub> pin voltage > V <sub>OUT</sub> setting value),                   | -     | 500  | 1000 | nA    |

|                                                 |                                                            | $V_{\text{IN}}\text{=}V_{\text{OUT}\_\text{min.}}\text{+}0.3$ V (1.8 V min.) to 5.5 V                     |       |      |      |       |

| ISD                                             | Shutdown current                                           | EN = GND, shutdown current into $V_{IN}$                                                                  |       | 10   | 200  | nA    |

|                                                 |                                                            | V <sub>IN</sub> rising                                                                                    | -     | 1.63 | 1.72 | V     |

| V <sub>UVLO</sub> Undervoltage lockout threshol |                                                            | V <sub>IN</sub> falling                                                                                   | 1.51  | 1.57 | -    | V     |

|                                                 |                                                            | Hysteresis                                                                                                | -     | 65   | -    | m∖    |

| V <sub>th100%+</sub>                            | 100% mode leave threshold                                  | $V_{\text{IN}}$ rising, 100% mode is disabled with $V_{\text{IN}}$ = $V_{OUTnom}$ + $V_{th100\%^+}$       | -     | 300  | -    |       |

| V <sub>th100%</sub> -                           | 100% mode enter threshold                                  | 100% mode enter threshold $V_{IN}$ falling, 100% mode is entered with $V_{IN} = V_{OUTnom} + V_{th100\%}$ |       | 200  | -    | - m∨  |

| Output v                                        | oltage                                                     |                                                                                                           |       |      |      |       |

| \/                                              | Output voltage range                                       | Output voltages are selected with pins D0, D1                                                             | 0.625 | -    | 3.3  | V     |

| V <sub>OUT</sub>                                | Output voltage accuracy                                    | $V_{IN}$ = 3.6 V, whole $V_{OUT}$ range, $I_{OUT}$ =100 mA                                                |       | -    | 1.5  | %     |

| t <sub>ONmin</sub>                              | Minimum on-time                                            | V <sub>IN</sub> = 3.6 V, V <sub>OUT</sub> = 2 V, I <sub>OUT</sub> = 0 A                                   |       | 200  | -    | ns    |

| t <sub>OFFmin</sub>                             | Minimum off-time                                           | V <sub>IN</sub> =2.3V                                                                                     |       | 50   | -    | ns    |

| t <sub>startupd</sub>                           | Start-up delay time                                        | $V_{\text{EN}}$ from low to high, $V_{\text{IN}}$ = 3.6 V, $V_{\text{OUT}}$ = 1.8 V                       | -     | 1.7  | -    | ms    |

| R <sub>OUTDIS</sub>                             | Output discharge MOSFET on-<br>resistance                  | V <sub>EN</sub> = GND                                                                                     | -     | 30   | -    | Ω     |

| Logic inp                                       | outs (EN, D0, D1)                                          |                                                                                                           |       |      |      |       |

| VIL                                             | Low level input voltage threshold                          | V <sub>IN</sub> =1.8 V to 5.5 V                                                                           | -     | -    | 0.3  | v     |

| V <sub>IH</sub>                                 | High level input voltage threshold                         | VIN-1.0 V to 5.5 V                                                                                        | 1.1   | -    | -    | V     |

| Power sv                                        | vitch                                                      |                                                                                                           |       |      |      |       |

| R <sub>DS(on)</sub>                             | High-side MOSFET on-<br>resistance                         | V <sub>IN</sub> = 3.6 V, I <sub>sw</sub> = 400 mA                                                         | -     | 0.38 | 0.45 | Ω     |

|                                                 | Low-side MOSFET on-resistance                              |                                                                                                           |       | 0.14 | 0.2  |       |

| I <sub>LIM1</sub>                               | High-side MOSFET switch<br>current limit                   | $1.8 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$                                                |       | -    | 1150 | mA    |

| I <sub>LIMSS</sub>                              | High-side MOSFET switch<br>current limit during soft-start | Reduced switch current limit during soft-start period (typ. 400 µs)                                       |       | 280  | 360  | 111/- |

| Power G                                         | ood output (PGOOD)                                         | ·                                                                                                         |       |      |      |       |

| V <sub>thpg</sub>                               | Power Good threshold voltage                               | Rising output voltage on $V_{OUT}$ pin, referred to $V_{OUT}$ selected (D0, D1)                           | 95    | 97.5 | -    | %     |

| V <sub>thpgH</sub>                              |                                                            | Hysteresis                                                                                                | -4    | -3.2 | -2.5 |       |

#### Table 6. Electrical characteristics

| Symbol          | Parameter                | Test conditions                                                                                        | Min. | Тур. | Max. | Unit |

|-----------------|--------------------------|--------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>OL</sub> | Low level output voltage | 1.8 V $\leq$ V <sub>IN</sub> $\leq$ 5.5 V, E <sub>N</sub> = GND, current into PGOOD pin, IPGOOD = 4 mA | -    | -    | 0.23 | V    |

### Table 7. Output voltage settings

| Device     | D1 | D0 | VOUT                  |

|------------|----|----|-----------------------|

|            | 0  | 0  | 1.9 V                 |

| 07/000/010 | 0  | 1  | 2.0 V                 |

| ST1PS01AJR | 1  | 0  | 2.1 V                 |

|            | 1  | 1  | 2.8 V                 |

|            | 0  | 0  | 1.1 V                 |

|            | 0  | 1  | 1.2 V                 |

| ST1PS01BJR | 1  | 0  | 1.5 V <sup>(1)</sup>  |

|            | 1  | 1  | 1.7 V <sup>(1)</sup>  |

|            | 0  | 0  | 1.0 V                 |

|            | 0  | 1  | 1.2 V                 |

| ST1PS01CJR | 1  | 0  | 1.3 V                 |

|            | 1  | 1  | 1.5 V <sup>(1)</sup>  |

|            | 0  | 0  | 1.8 V                 |

|            | 0  | 1  | 2.3 V                 |

| ST1PS01DJR | 1  | 0  | 2.5 V                 |

|            | 1  | 1  | 2.8 V                 |

|            | 0  | 0  | 1.8 V                 |

|            | 0  | 1  | 2.7 V                 |

| ST1PS01EJR | 1  | 0  | 3.0 V                 |

|            | 1  | 1  | 3.3 V                 |

|            | 0  | 0  | 1.05 V                |

|            | 0  | 1  | 1.25 V                |

| ST1PS01FJR | 1  | 0  | 1.35 V                |

|            | 1  | 1  | 1.55 V <sup>(1)</sup> |

|            | 0  | 0  | 0.73 V                |

|            | 0  | 1  | 0.80 V                |

| ST1PS01GJR | 1  | 0  | 0.90 V                |

|            | 1  | 1  | 1.0 V                 |

|            | 0  | 0  | 1.05 V                |

|            | 0  | 1  | 0.90 V                |

| ST1PS01HJR | 1  | 0  | 0.70 V                |

|            | 1  | 1  | 0.625 V               |

1. Vout can be dinamically selected when VIN=Vout selected+300 mV, at least.

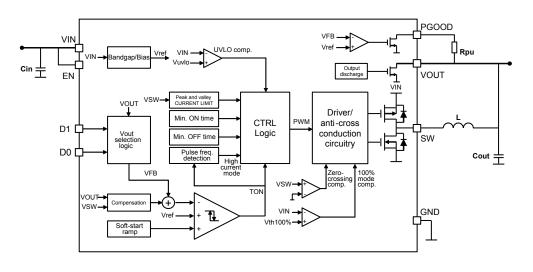

# 6 ST1PS01 block diagram

57

### Figure 3. Block diagram

### 7 Operation description

The ST1PS01 is an ultra-low quiescent new generation buck converter. It targets a very small quiescent current consumption (typical 500 nA) and it guarantees high efficiency operation even down to few microampere loads.

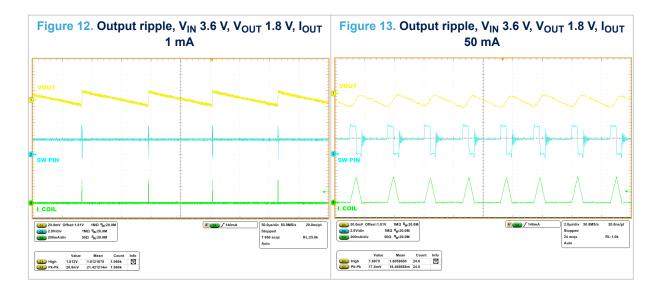

It is based on a hysteretic comparator that senses the coil ripple current that is held constant in all operation modes. The device has seamless transition between PFM (pulse frequency modulation) and PWM (pulse width modulation) mode with low ripple and good load transient response.

In order to maintain constant ripple current on the selected coil, the device changes switching frequency, which also depends on input supply voltage. During PWM mode (heavy load), the device operates in continuous conduction up to 400 mA and switching frequency can reach 2 MHz maximum.

### 7.1 Power save mode

At light load the device enters automatically power save mode with total current consumption from the input power supply of 500 nA typical; during this condition most of the internal blocks are turned off in order to reach ultra-low power consumption. During this time, the load current is supported by the output capacitor.

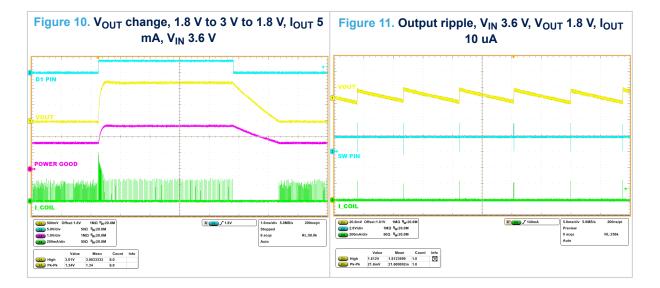

### 7.2 Output voltage

The device allows output voltage selection without external resistor divider. A couple of standard digital inputs are used to configure the device to supply a fixed output voltage according to Section 5. The  $V_{OUT}$  pin **must be connected directly** and **as close as possible to the inductor terminal** to obtain the best performance and get the best output voltage regulation. The output voltage can be dynamically changed to implement voltage scaling.

### 7.3 Output discharge and UVLO

The device embeds a fast output discharge circuitry active when the enable pin is held to ground (EN=gnd) or when the input supply voltage reaches the minimum voltage level set by the UVLO protection circuit (undervoltage lock-out protection circuit). The UVLO rising threshold at 1.63 V (typ.) guarantees a proper device supply voltage operation.

### 7.4 Soft-start and current limitation

The device embeds a fixed soft-start circuit active during a limited time period (few ms). This feature allows the inrush current to be minimized from the power supply in case of weak source. During this period internal circuit reduces to 280 mA the typical switch current limit.

The ST1PS01 embeds also a current limit on high-side MOSFET to protect the device against overload or short-circuit on the output, during normal operation conditions. When the device enters 100% duty cycle operation condition and an overload (or short-circuit) occurs, the output voltage is set in shutdown in order to limit the power dissipation. To restart the device operation, a LOW to HIGH cycle on EN pin is necessary.

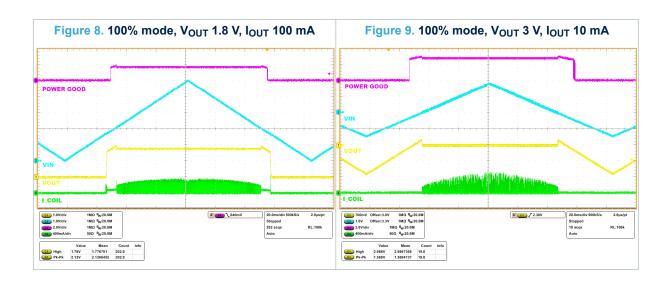

### 7.5 100% duty cycle operation

The device enters 100% duty cycle operation if the input voltage comes close to the selected output voltage. During this mode, the regulator is turned off and output pin is directly connected to the input pin through the high-side MOSFET. The output voltage follows the input level minus the voltage drop across the internal MOSFET and the inductor. Once the input voltage exceeds the 100% duty cyle leave threshold, the device restarts to switch and regulates the select output voltage again.

### 7.6 Power Good flag

The Power Good comparator monitors the selected  $V_{OUT}$  voltage. The Power Good open drain output is in high impedance when the  $V_{OUT}$  reaches the correct voltage level while it switches to low level when  $V_{OUT}$  falls below the normal voltage level.

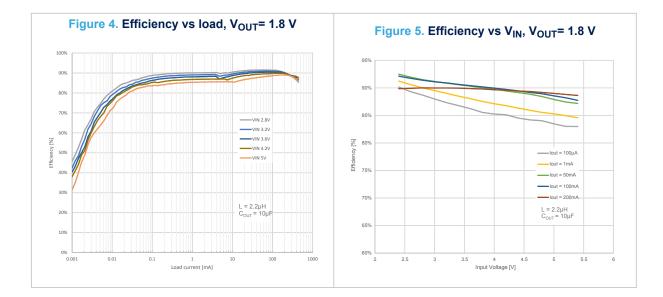

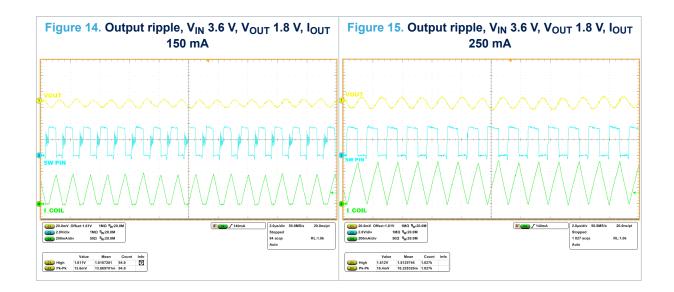

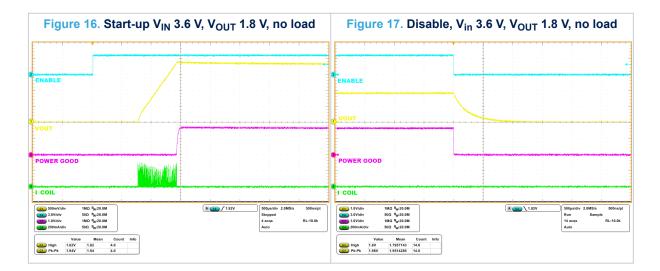

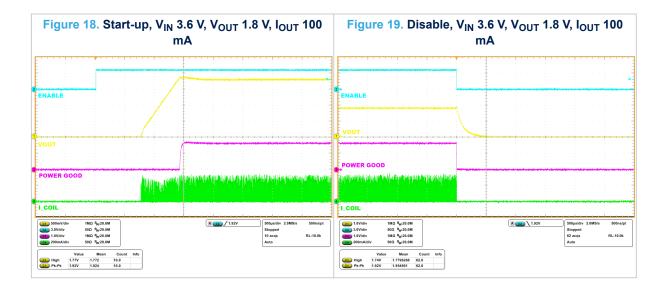

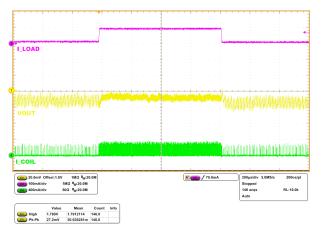

# 8 Typical performance characteristics

| Figure 20                                                                                   |                                                                                           | nt, V <sub>IN</sub> 3.6 V V <sub>O</sub><br>to 10 mA | <sub>UT</sub> 1.8 V,                           | louт                 | T Figure 21. Load transient, V <sub>IN</sub> 3.6 V, V <sub>OUT</sub> 1.8 V,<br>0 to 100 mA                                                                        |                                      |        | I <sub>OU</sub> .                                  |                                        |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------|----------------------------------------------------|----------------------------------------|

| LLOAD                                                                                       |                                                                                           |                                                      |                                                |                      |                                                                                                                                                                   |                                      |        |                                                    |                                        |

|                                                                                             |                                                                                           |                                                      |                                                |                      | I_LOAD                                                                                                                                                            |                                      | I      |                                                    | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

| VOUT                                                                                        |                                                                                           |                                                      |                                                |                      | vout                                                                                                                                                              |                                      |        |                                                    |                                        |

| I_COIL                                                                                      |                                                                                           |                                                      |                                                |                      | LCOIL                                                                                                                                                             | pen da alfalha Osaa shirina ayay far |        |                                                    |                                        |

|                                                                                             | 1MΩ <sup>9</sup> W-20.0M<br>MΩ <sup>9</sup> W-20.0M<br>0Ω <sup>9</sup> W-20.0M            | <b>A 1 1 1 1 1 1 1 1 1 1</b>                         | 200µs/div 5.0MS/s<br>Preview<br>0 acqs<br>Auto | 200ns/pt<br>RL:10.0k | 20.0mV Offset:1.8V         IMΩ B <sub>qx</sub> :20.           T0.0mA/div         IMΩ B <sub>qx</sub> :20.0M           MOMA/div         S0Ω B <sub>qx</sub> :20.0M |                                      | T1.4mA | 200µs/div 5.0MS/s<br>Stopped<br>3 577 acqs<br>Auto | 200ns/p<br>RL:10.0k                    |

| Value           C1         High           1.81V           C1         Pk-Pk           38.4mV | Mean         Count         Info           1.81         1.0         38.400003m         1.0 |                                                      |                                                |                      | Value         Mean           C1         High         1.809V         1.8118393           C5         Pk-Pk         40.0mV         47.577805m                        | Count Info<br>1361k 1361k            |        |                                                    |                                        |

Figure 22. Load transient, V\_IN 3.6 V, V\_OUT 1.8 V, I\_OUT 10 mA to 100 mA

# 9 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

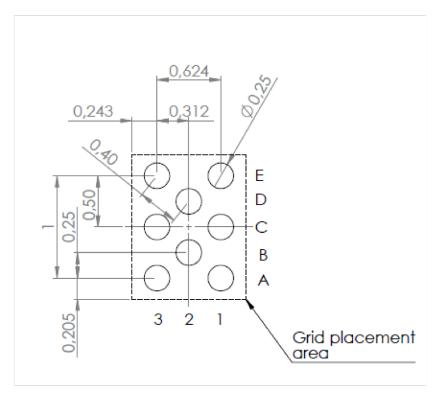

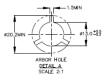

### 9.1 Flip-Chip 8 (1.14x1.44 mm) package information

Figure 23. Flip-Chip 8 (1.14x1.44 mm) package outline

| Quanta al |       | Milimeters |       |

|-----------|-------|------------|-------|

| Symbol    | Min.  | Тур.       | Max.  |

| А         | 0.500 | 0.550      | 0.600 |

| A1        | 0.170 | 0.200      | 0.230 |

| A2        | 0.330 | 0.350      | 0.370 |

| b         | 0.230 | 0.250      | 0.270 |

| D         | 1.08  | 1.11       | 1.14  |

| D1        |       | 0.624      |       |

| E         | 1.38  | 1.41       | 1.44  |

| E1        |       | 1.00       |       |

| fE        |       | 0.205      |       |

| fD        |       | 0.243      |       |

| eE        |       | 0.250      |       |

| eD        |       | 0.312      |       |

| e         |       | 0.50       |       |

| J         |       | 0.40       |       |

| CCC       |       | 0.05       |       |

### Table 8. Flip-Chip 8 (1.14x1.44 mm) mechanical data

### Figure 24. Flip-Chip 8 (1.14x1.44 mm) recommended footprint

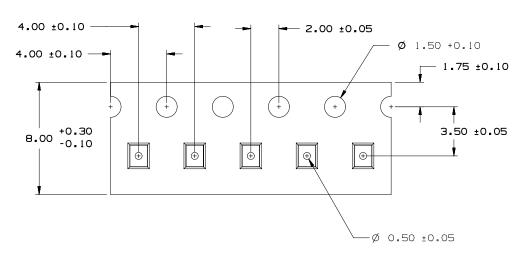

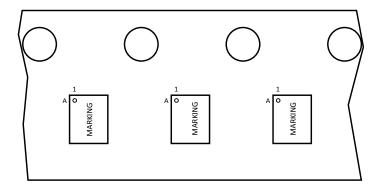

### 9.2 Flip-Chip 8 (1.14x1.44 mm) packing information

57

### Figure 25. Flip-Chip 8 (1.14x1.44 mm) tape outline

### Figure 26. Flip-Chip 8 (1.14x1.44 mm) tape orientation

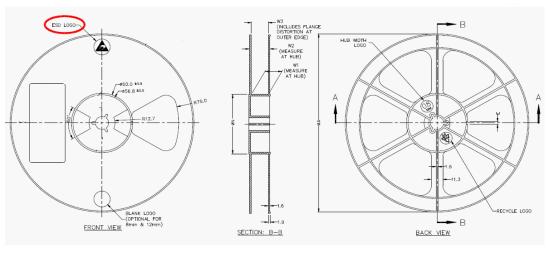

### Figure 27. Flip-Chip 8 (1.14x1.44 mm) reel outline

#### Table 9. Reel mechanical data

| A max. | N min. | W1 max. [mm] | W2 max. [mm] | W3 min./max. [mm] |

|--------|--------|--------------|--------------|-------------------|

| 180    | 60     | 8.4          | 14.4         | 7.9/10.9          |

# **Revision history**

| Date          | Version | Changes                                                                                                                                |

|---------------|---------|----------------------------------------------------------------------------------------------------------------------------------------|

| 31-Oct-2018   | 1       | Initial release.                                                                                                                       |

| 13-Dec-2018   | 2       | Updated Section 8 Typical performance characteristics.                                                                                 |

|               |         | Added Section 9.2 Flip-Chip 8 (1.14x1.44 mm) packing information.                                                                      |

| 13-Dec-2019   | 3       | Updated Figure 22. Load transient, V_IN 3.6 V, V_OUT 1.8 V, I_OUT 10 mA to 100 mA.                                                     |

| 22-Jul-2020   | 4       | Updated the cover page, Section 5 Electrical characteristics,<br>Section 8 Typical performance characteristics.<br>Minor text changes. |

| 22-Sep-2020   | 5       | Updated Section Features.                                                                                                              |

| 28-Jun-2021 6 |         | Updated Figure 1. ST1PS01 application schematic.                                                                                       |

|               | 6       | Updated Section 3 Functional pin description, Section 7.4 Soft-start and current limitation and Table 6. Electrical characteristics.   |

|               |         | Updated Table 7. Output voltage settings.                                                                                              |

### Table 10. Document revision history

# Contents

| 1   | Appl                       | ication schematic                                |  |  |  |

|-----|----------------------------|--------------------------------------------------|--|--|--|

| 2   | Pin configuration          |                                                  |  |  |  |

| 3   | Functional pin description |                                                  |  |  |  |

| 4   | Maxi                       | mum ratings                                      |  |  |  |

| 5   | Electrical characteristics |                                                  |  |  |  |

| 6   | Bloc                       | k diagram                                        |  |  |  |

| 7   | Oper                       | ation description9                               |  |  |  |

|     | 7.1                        | Power save mode                                  |  |  |  |

|     | 7.2                        | Output voltage                                   |  |  |  |

|     | 7.3                        | Output discharge and UVLO9                       |  |  |  |

|     | 7.4                        | Soft-start and current limitation9               |  |  |  |

|     | 7.5                        | 100% duty cycle operation                        |  |  |  |

|     | 7.6                        | Power Good flag                                  |  |  |  |

| 8   | Туріс                      | al performance characteristics10                 |  |  |  |

| 9   | Package information        |                                                  |  |  |  |

|     | 9.1                        | Flip-Chip8 (1.14x1.44 mm) package information    |  |  |  |

|     | 9.2                        | Flip-Chip 8 (1.14x1.44 mm) packing information16 |  |  |  |

| Rev | ision I                    | nistory                                          |  |  |  |

# 57

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved