**S-35770** COUNTER IC

#### www.ablic.com

# **COUNTER IC WITH 2-WIRE (I<sup>2</sup>C-bus) INTERFACE**

© ABLIC Inc., 2019 Rev. 1.0\_00

The counter IC allows for counting externally input clocks.

The counter of the S-35770 is a 24-bit binary-up counter. The counter data can be read via a 2-wire serial interface.

### **■** Features

• External clock signal count function:

• Low current consumption:

• Wide range of operation voltage:

• 2-wire (I<sup>2</sup>C-bus) CPU interface

• Operation temperature range:

• Lead-free (Sn 100%), halogen-free

Countable from 0 to 16,777,215, with output pin for counter loop flag

$0.01~\mu A$  typ. (V<sub>DD</sub> = 3.0~V, Ta =  $+25^{\circ}C$ , out of communication (CLKIN pin = 0~V))

1.5 V to 5.5 V

Ta = -40°C to +85°C

## **■** Applications

- Various measurement equipment

- Infrastructure-related meter

- Amusement equipment

- Life counter

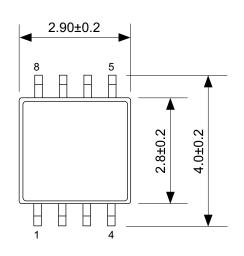

# ■ Package

• TMSOP-8

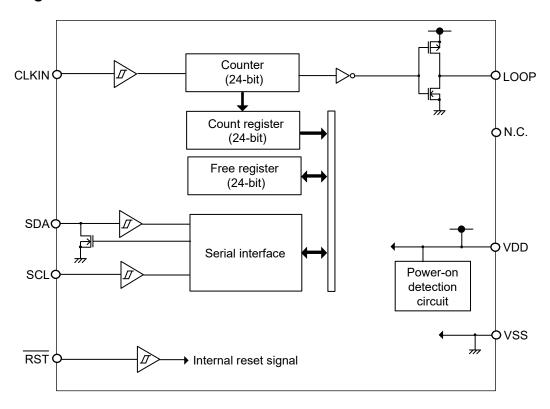

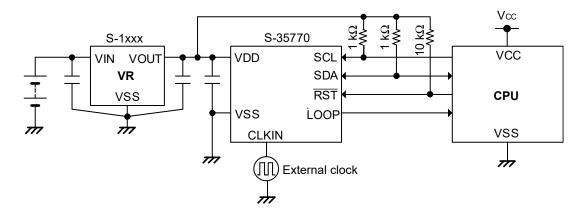

# **■** Block Diagram

Figure 1

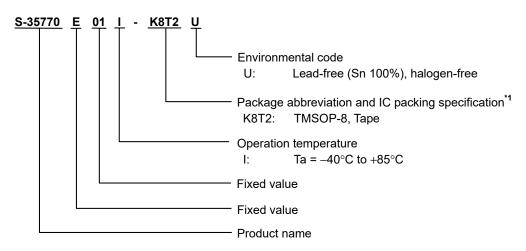

### **■ Product Name Structure**

### 1. Product name

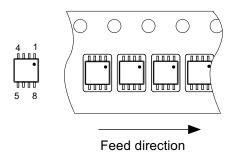

\*1. Refer to the tape drawing.

### 2. Package

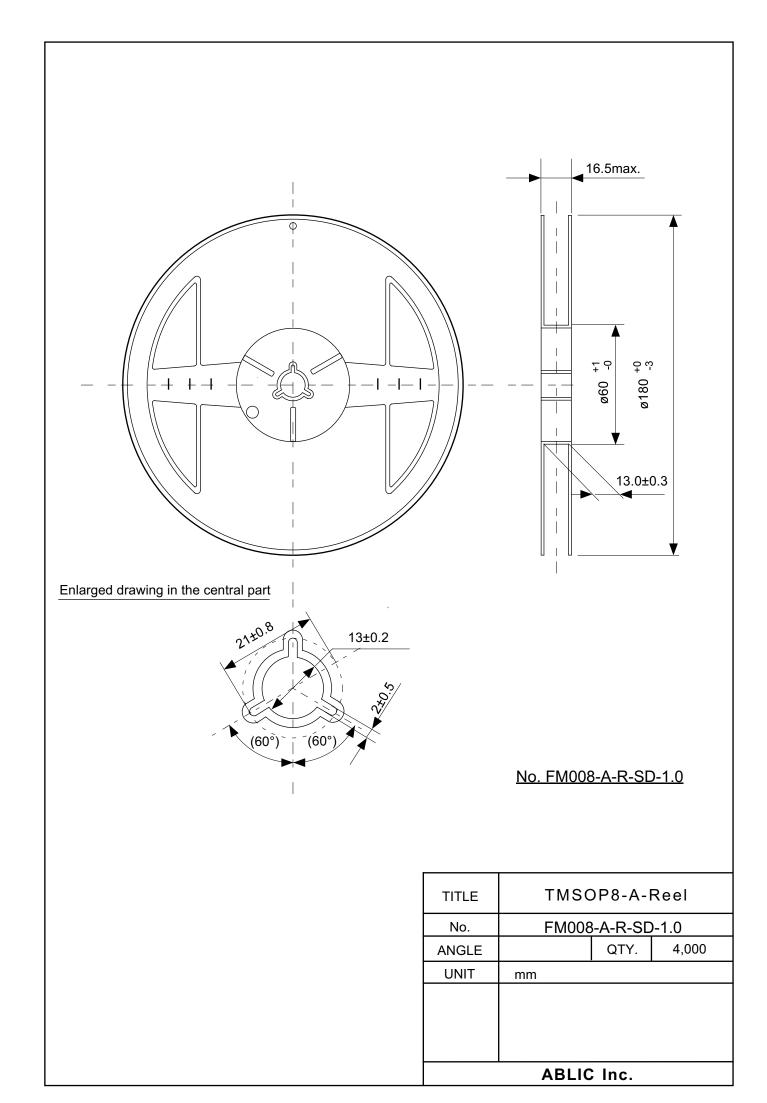

Table 1 Package Drawing Codes

| Package Name | Dimension    | Tape         | Reel         |

|--------------|--------------|--------------|--------------|

| TMSOP-8      | FM008-A-P-SD | FM008-A-C-SD | FM008-A-R-SD |

### 3. Product name list

Table 2

| Product Name      | RST Pin                  | LOOP Pin Output Form | LOOP Pin Output*1 |

|-------------------|--------------------------|----------------------|-------------------|

| S-35770E01I-K8T2U | Without pull-up resistor | CMOS output          | "L"               |

**<sup>\*1.</sup>** The output status at power-on.

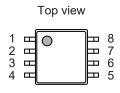

# **■** Pin Configuration

# 1. TMSOP-8

Figure 2

Table 3 List of Pins

| Pin No. | Symbol | Description                      | I/O            | Configuration                         |

|---------|--------|----------------------------------|----------------|---------------------------------------|

| 1       | RST    | Input pin for reset signal       | Input          | CMOS input (without pull-up resistor) |

| 2       | NC*1   | No connection                    | -              | -                                     |

| 3       | CLKIN  | Input pin for external clock     | Input          | CMOS input                            |

| 4       | VSS    | GND pin                          | _              | 1                                     |

| 5       | LOOP   | Output pin for counter loop flag | Output         | CMOS output                           |

| 6       | SDA    | I/O pin for serial data          | Bi-directional | Nch open-drain output,<br>CMOS input  |

| 7       | SCL    | Input pin for serial clock       | Input          | CMOS input                            |

| 8       | VDD    | Pin for positive power supply    | _              | _                                     |

**<sup>\*1.</sup>** The NC pin is electrically open.

Therefore, leave it open or connect it to VDD pin or VSS pin.

#### ■ Pin Functions

### 1. SDA (I/O for serial data) pin

This is a data input / output pin for  $I^2C$ -bus interface. The SDA pin inputs / outputs data by synchronizing with a clock pulse from the SCL pin. This pin has CMOS input and Nch open-drain output. Generally in use, the SDA pin is pulled up to  $V_{DD}$  potential via a resistor, and is used with wired-OR connection of other device of Nch open-drain output or open collector output.

### 2. SCL (Input for serial clock) pin

This is a clock input pin for I2C-bus interface. The SDA pin inputs / outputs data by synchronizing with this clock

## 3. RST (Input for reset signal) pin

This pin inputs the reset signal. The counter is reset when inputting "L" to the  $\overline{RST}$  pin. When inputting "H" to the  $\overline{RST}$  pin, the count-up action of the counter is started.

Besides, the  $\overline{\mathsf{RST}}$  pin has no pull-up resistor.

#### 4. CLKIN (Input for external clock) pin

This pin inputs an external clock. The counter is incremented by 1 when the CLKIN pin input changes from "L" to "H".

### 5. LOOP (Output for counter loop flag) pin

Each time the counter loops back to 0 after reaching 16,777,215, the LOOP pin performs a toggle operation. Regarding the operation of the LOOP pin, refer to "■ LOOP Pin".

Regarding the operation of the LOOP pin, refer to **LOOP**

Besides, the LOOP pin output form is CMOS output.

### 6. VDD (Positive power supply) pin

Connect this pin with a positive power supply. Regarding the values of voltage to be applied, refer to **"Example Recommended Operation Condition"**.

#### 7. VSS pin

Connect this pin to GND.

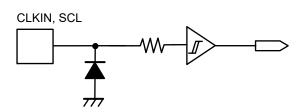

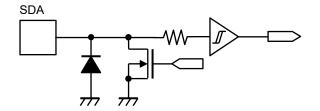

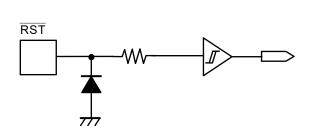

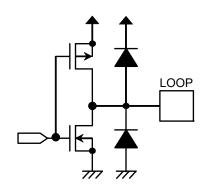

# ■ Equivalent Circuits of Pins

Figure 3 CLKIN Pin and SCL Pin

Figure 4 SDA Pin

Figure 5 RST Pin

Figure 6 LOOP Pin

# ■ Absolute Maximum Ratings

Table 4

| Item                            | Symbol           | Applied Pin Absolute Maximum Rating |                                                   | Unit |

|---------------------------------|------------------|-------------------------------------|---------------------------------------------------|------|

| Power supply voltage            | $V_{DD}$         | _                                   | $V_{SS} - 0.3$ to $V_{SS} + 6.5$                  | V    |

| Input voltage                   | V <sub>IN</sub>  | CLKIN, SDA, SCL, RST                | $V_{SS} - 0.3$ to $V_{SS} + 6.5$                  | V    |

| Outrout walks as                |                  | SDA                                 | $V_{SS} - 0.3$ to $V_{SS} + 6.5$                  | V    |

| Output voltage                  | Vout             | LOOP                                | $V_{SS} - 0.3$ to $V_{DD} + 0.3 \le V_{SS} + 6.5$ | V    |

| Operation ambient temperature*1 | Topr             | _                                   | -40 to +85                                        | °C   |

| Storage temperature             | T <sub>stg</sub> | _                                   | −55 to +150                                       | °C   |

<sup>\*1.</sup> Conditions with no condensation or frost. Condensation or frost causes short-circuiting between pins, resulting in a malfunction.

Caution The absolute maximum ratings are rated values exceeding which the product could suffer physical damage. These values must therefore not be exceeded under any conditions.

# ■ Recommended Operation Condition

Table 5

$(V_{SS} = 0 V)$

|                                |          |                    |      |      |      | (133 01) |

|--------------------------------|----------|--------------------|------|------|------|----------|

| Item                           | Symbol   | Condition          | Min. | Тур. | Max. | Unit     |

| Operation power supply voltage | $V_{DD}$ | Ta = -40°C to +85C | 1.5  | _    | 5.5  | V        |

# **■ DC Electrical Characteristics**

Table 6

$(Ta = -40^{\circ}C \text{ to } +85^{\circ}C, V_{SS} = 0 \text{ V})$

| Item                                | Symbol           | Applied Dip             | Condition                                                                                            | Min.                  |      | May                   | Unit |

|-------------------------------------|------------------|-------------------------|------------------------------------------------------------------------------------------------------|-----------------------|------|-----------------------|------|

| item                                | Symbol           | Applied Pin             | _                                                                                                    | IVIII1.               | Тур. | Max.                  | Unit |

| Current consumption 1               | I <sub>DD1</sub> | -                       | V <sub>DD</sub> = 3.0 V,<br>Out of communication<br>(CLKIN pin = 0 V),<br>LOOP pin = no load         | _                     | 0.01 | 0.1                   | μΑ   |

| Current consumption 2               | I <sub>DD2</sub> | -                       | V <sub>DD</sub> = 3.0 V,<br>f <sub>SCL</sub> = 1 MHz,<br>During communication,<br>LOOP pin = no load | _                     | 170  | 300                   | μΑ   |

| High level input leakage current    | lızh             | CLKIN, SDA, SCL, RST    | V <sub>IN</sub> = V <sub>DD</sub>                                                                    | -0.5                  | ı    | 0.5                   | μΑ   |

| Low level input leakage current     | l <sub>IZL</sub> | CLKIN, SDA, SCL, RST    | V <sub>IN</sub> = V <sub>SS</sub>                                                                    | -0.5                  | I    | 0.5                   | μΑ   |

| High level output leakage current   | lozh             | SDA                     | V <sub>OUT</sub> = V <sub>DD</sub>                                                                   | -0.5                  | ı    | 0.5                   | μΑ   |

| Low level output<br>leakage current | lozL             | SDA                     | V <sub>OUT</sub> = V <sub>SS</sub>                                                                   | -0.5                  | -    | 0.5                   | μΑ   |

| High level input voltage            | V <sub>IH</sub>  | CLKIN, SDA, SCL,<br>RST | _                                                                                                    | $0.7 \times V_{DD}$   | _    | V <sub>SS</sub> + 5.5 | V    |

| Low level input voltage             | VIL              | CLKIN, SDA, SCL, RST    | _                                                                                                    | V <sub>SS</sub> – 0.3 | -    | $0.3 \times V_{DD}$   | V    |

| Low level output voltage            | VoL              | SDA                     | I <sub>OL</sub> = 2.0 mA                                                                             | _                     | _    | 0.4                   | V    |

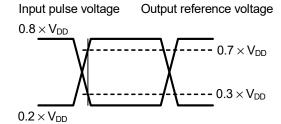

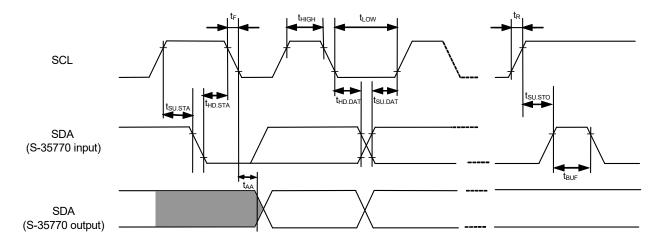

### ■ AC Electrical Characteristics

**Table 7 Measurement Conditions**

| Input pulse voltage          | $V_{IH} = 0.8 \times V_{DD},$<br>$V_{IL} = 0.2 \times V_{DD}$ |

|------------------------------|---------------------------------------------------------------|

| Input pulse rise / fall time | 20 ns                                                         |

| Output reference voltage     | $V_{OH} = 0.7 \times V_{DD},$<br>$V_{OL} = 0.3 \times V_{DD}$ |

| Output load                  | 100 pF                                                        |

Figure 7 Input / Output Waveform during AC Measurement

**Table 8 AC Electrical Characteristics**

$(Ta = -40^{\circ}C \text{ to } +85^{\circ}C)$

| lto-m                       | Cumala al           | V <sub>DD</sub> = 1.5 | V to 2.5 V | V <sub>DD</sub> = 2.5 | V to 5.5 V | l lmit |

|-----------------------------|---------------------|-----------------------|------------|-----------------------|------------|--------|

| Item                        | Symbol              | Min.                  | Max.       | Min.                  | Max.       | Unit   |

| SCL clock frequency         | fscL                | 0                     | 400        | 0                     | 1000       | kHz    |

| SCL clock "L" time          | t <sub>LOW</sub>    | 1.3                   | _          | 0.4                   | _          | μs     |

| SCL clock "H" time          | thigh               | 0.6                   | _          | 0.3                   | _          | μs     |

| SDA output delay time*1     | t <sub>AA</sub>     | _                     | 0.9        | ı                     | 0.5        | μs     |

| Start condition set-up time | tsu.sta             | 0.6                   | _          | 0.25                  | _          | μs     |

| Start condition hold time   | thd.sta             | 0.6                   | _          | 0.25                  | _          | μs     |

| Data input set-up time      | t <sub>SU.DAT</sub> | 100                   | _          | 80                    | _          | ns     |

| Data input hold time        | t <sub>HD.DAT</sub> | 0                     | _          | 0                     | _          | ns     |

| Stop condition set-up time  | tsu.sto             | 0.6                   | _          | 0.25                  | _          | μs     |

| SCL, SDA rise time          | t <sub>R</sub>      | _                     | 0.3        | _                     | 0.3        | μs     |

| SCL, SDA fall time          | t <sub>F</sub>      | _                     | 0.3        | _                     | 0.3        | μs     |

| Bus release time            | t <sub>BUF</sub>    | 1.3                   | _          | 0.5                   | _          | μs     |

| Noise suppression time      | tı                  | _                     | 50         | _                     | 50         | ns     |

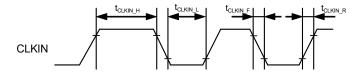

| CLKIN clock frequency       | fclkin              | 0                     | 400        | 0                     | 1000       | kHz    |

| CLKIN clock "L" time        | tclkin_L            | 1.3                   | _          | 0.4                   | _          | μs     |

| CLKIN clock "H" time        | tclkin_h            | 0.6                   | -          | 0.3                   | -          | μs     |

| CLKIN rise time             | tclkin_r            | _                     | 0.3        | ı                     | 0.3        | μs     |

| CLKIN fall time             | tclkin_f            | _                     | 0.3        | _                     | 0.3        | μs     |

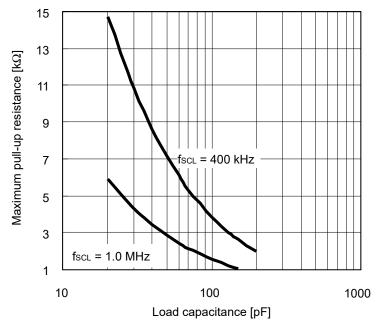

<sup>\*1.</sup> Since the output form of the SDA pin is Nch open-drain output, the SDA output delay time is determined by the values of the load resistance and load capacitance outside the IC. **Figure 9** shows the relationship between the output load values.

Figure 8 Bus Timing

Figure 9 Output Load

Figure 10 CLKIN Pin Clock Timing

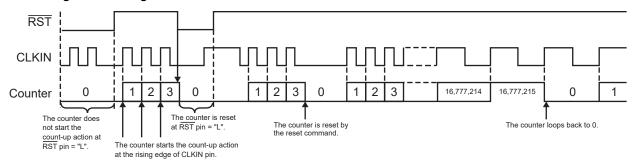

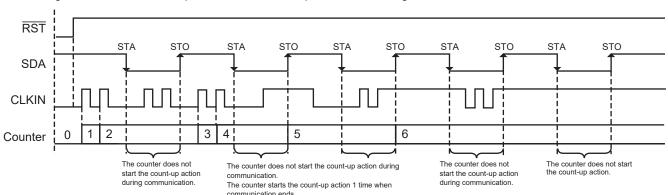

# ■ External Clock Signal Count Function

The S-35770 detects the change of the CLKIN pin from "L" to "H", and then starts the count-up action of the counter. The counter is a 24-bit binary counter which can count from 0 to 16,777,215 (FFFFFF h). After reaching 16,777,215, the S-35770 detects the change of the CLKIN pin from "L" to "H", the counter loops back to 0.

The counter value can be confirmed by reading the count register. To initialize the counter, input "L" to the  $\overline{RST}$  pin or input the reset command to the free register. Regarding the count register and the reset command, refer to " $\blacksquare$  Configuration of registers".

Figure 11 Counter Operation

During communication, the S-35770 does not detect the change of the CLKIN pin from "L" to "H" and maintains the counter data. The duration of the communication is defined as the time period from the start condition to the stop condition. The count-up action of the counter is executed 1 time if the CLKIN pin is "L" when the start condition is recognized and if the CLKIN pin is "H" when the stop condition is recognized.

Figure 12 Counter Operation during Communication

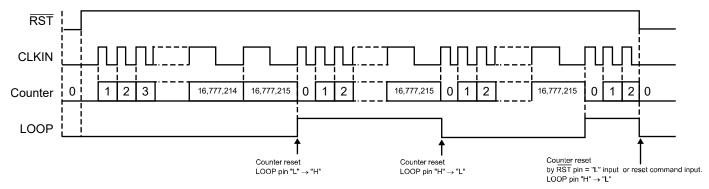

### ■ LOOP Pin

The S-35770 detects the change of the CLKIN pin from "L" to "H", and then starts the count-up action of the counter. The counter loops back to 0 after reaching 16,777,215. At this time, the LOOP pin changes from "L" to "H". To change the LOOP pin to "L", input "L" to the  $\overline{RST}$  pin or input the reset command to the free register.

Furthermore, if the counter loops back to 0 again after reaching 16,777,215 under the condition the LOOP pin maintains "H", the LOOP pin changes from "H" to "L". In other word, each time the counter loops back to 0 after reaching 16,777,215, the LOOP pin performs a toggle operation.

Figure 13 LOOP Pin Operation

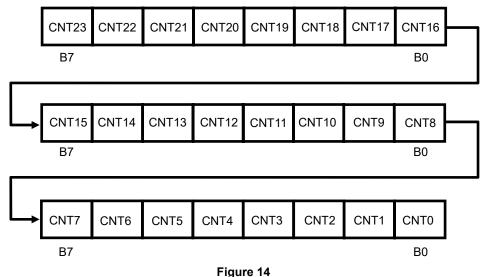

## ■ Configuration of Registers

### 1. Count register

The count register is a 3-byte register that stores the counter value as binary code.

The count register is read-only.

Perform the read operation of the count register in 3-byte unit from CNT23 to CNT0.

Example: 3 (0000\_0000\_0000\_0000\_0000\_0011)

45 (0000\_0000\_0000\_1010\_1000\_1100)

19,800 (0000\_0000\_0100\_1101\_0101\_1000)

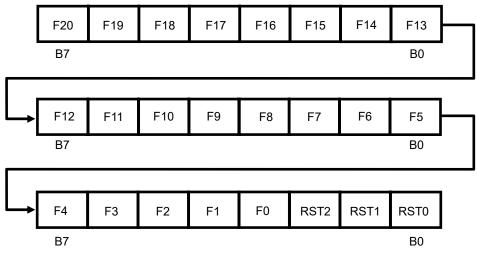

#### 2. Free register

The free register is a 3-byte register that can be freely read and written by the user. The lower 3 bits, RST2 to RST0 are used as a register to input the counter reset command. The counter is reset by writing RST2 = "0", RST1 = "1", and RST0 = "0". The data of F20 to F0 are not reset when inputting the reset command; however, the data when the reset command is input are set.

When only the data of F20 to F0 are rewritten without resetting the counter, write the data except for the above mentioned ones, such as RST2 = "1", RST1 = "1" and RST0 = "1" to the free register.

Perform the write and read operation of the free register in 3-byte unit.

Figure 15

### ■ Serial Interface

The S-35770 transmits and receives various commands via I<sup>2</sup>C-bus serial interface to read / write data.

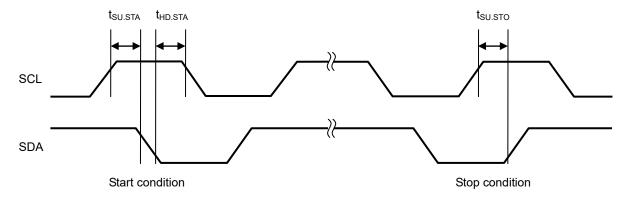

#### 1. Start condition

When SDA changes from "H" to "L" with SCL at "H", the S-35770 recognizes start condition and the access operation is started.

#### 2. Stop condition

When SDA changes from "L" to "H" with SCL at "H", the S-35770 recognizes stop condition and the access operation is completed. The S-35770 enters standby mode, consequently.

Figure 16 Start / Stop Condition

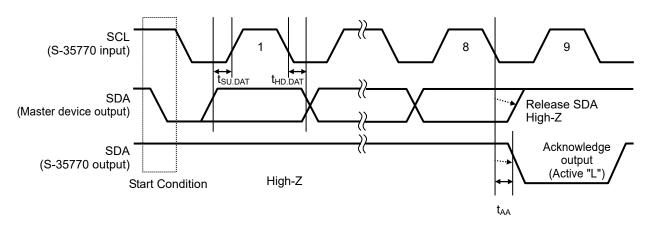

#### 3. Data transmission and acknowledge

The data transmission is performed at every one byte after the start condition detection. Pay attention to the specification of t<sub>SU.DAT</sub> and t<sub>HD.DAT</sub> when changing SDA, and perform the operation when SCL is "L". If SDA changes when SCL is "H", the start / stop condition is recognized even during the data transmission, and the access operation will be interrupted.

Whenever a one-byte data is received during data transimmion, the receiving device returns an acknowledge. For example, as shown in **Figure 17**, assume that the S-35770 is a receiving device, and the master device is a transmitting device. If the clock pulse at the 8th bit falls, the master device releases SDA. Consequently, the S-35770, as an acknowledge, sets SDA to "L" during the 9th bit pulse. The access operation is not performed properly when the S-35770 does not output an acknowledge.

Figure 17 Acknowledge Output Timing

14

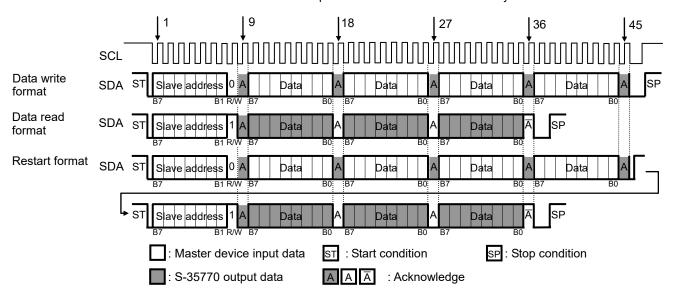

#### 4. Data transmission format

After the start condition transmission, the 1st byte is a slave address and a command (read / write bit) that shows the transmission direction at the 2nd byte or subsequent bytes.

The slave address of the S-35770 is specified to "0110010". The data can be written to the free register when read / write bit is "0", and the data of count register or the free register can be read when read / write bit is "1".

When the data can be written to the free register, input the data from the master device in order of B7 to B0. The acknowledge ("L") is output from the S-35770 whenever a one-byte data is input.

When the data of the count register or the free register can be read, the data from the S-35770 is output in order of B7 to B0 in byte unit. Input the acknowledge ("L") from the master device whenever a one-byte data is input. However, do not input the acknowledge for the last byte (NO ACK). By this, the end of the data read is informed.

After the master device receives / transmits the acknowledge for the last byte data, input the stop condition to the S-35770 to finish the access operation.

When the master device inputs start condition instead of stop condition, the S-35770 becomes restart condition, and can transmit / receive the data if the master device inputs the slave address continuously.

Figure 18 Data Transmission Format of Serial Interface

In the time period from the start condition to the stop condition, the S-35770 does not detect the change of the CLKIN pin from "L" to "H" and maintains the counter data. Therefore, the output data of the count register does not change even if an external clock is input during a read operation of the count register.

Regarding the counter operation during communication, refer to "

External Clock Signal Count Function".

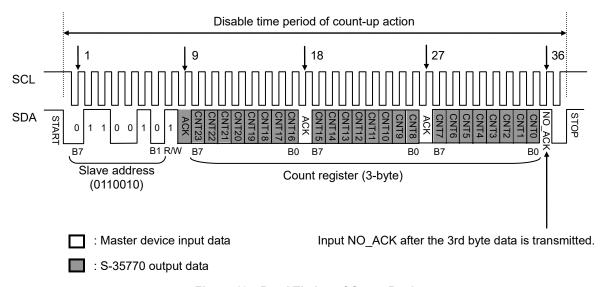

### 5. Read operation of count register

Transmit the start condition and slave address from the master device. The slave address of the S-35770 is specified to "0110010". The data of the count register can be read when the read / write bit is "1".

The 2nd byte to the 4th byte are used as the count register. Each byte from B7 is transmitted.

When the read operation of the count register is finished, transmit "1" (NO\_ACK) to the acknowledge after B0 is output from the master device, and then transmit the stop condition.

The count register is a 3-byte register. "1" is read if the read operation is performed continuously after reading 3 bytes of the count register. Regarding the count register, refer to "**Configuration of Registers**".

Figure 19 Read Timing of Count Register

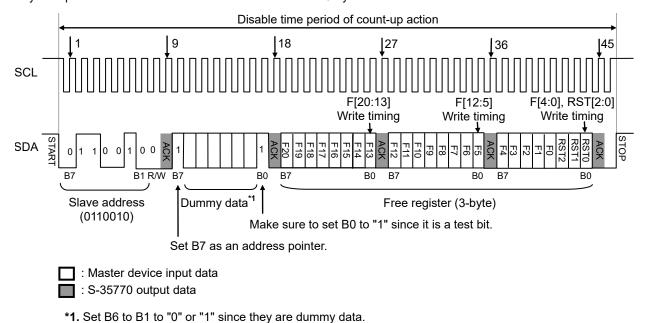

### 6. Write operation of free register

Transmit the start condition and slave address from the master device. The slave address of the S-35770 is specified to "0110010". Next, transmit "0" to the read / write bit.

Transmit the 2nd byte data. Set B7 to "1" since it is an address pointer. Set B6 to B1 to "0" or "1" since they are dummy data. Be sure to set B0 to "1" since it is a test bit.

B7 in the 3rd byte to B3 in the 5th byte are used as the free register.

B2 to B0 (RST2 to RST0) in the 5th byte are used as a register to input the counter reset command. The counter is reset when transmitting RST2 = "0", RST1 = "1" and RST0 = "0". When not resetting the counter, transmit the data except for the above mentioned ones, such as RST2 = "1", RST1 = "1" and RST0 = "1".

Transmit the stop condition from the master device to finish the access operation.

Regarding the free register, refer to "

Configuration of Registers".

Write operation of the free register is performed each byte, so transmit the data in 3-byte unit. Note that the S-35770 may not operate as desired if the data is not transmitted in 3-byte unit.

Figure 20 Write Timing of Free Register

ABLIC Inc.

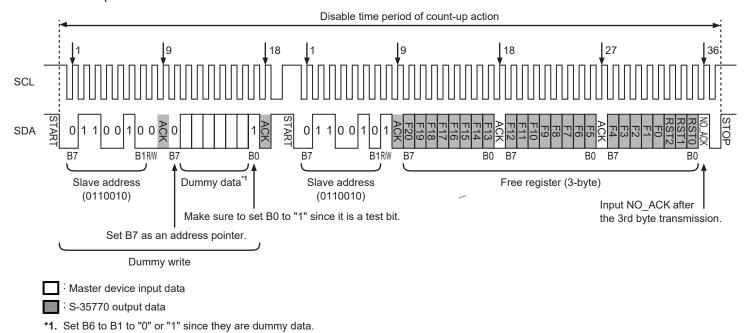

### 7. Read operation of free register

Perform the read operation of the free register with the restart format. Regarding the restart format, refer to "4. Data transmission format".

Transmit the start condition and the slave address from the master device. The slave address of the S-35770 is specified to "0110010". Next, transmit "0" to the read / write bit.

B7 in the 2nd byte is an address pointer. Set B7 to "0" when reading the free register. Next, transmit the dummy data to B6 to B1. Make sure to set B0 to "1" since it is a test bit. This processing is called "dummy write".

Then transmit the start condition, the slave address and the read / write bit. If the read / write bit is set to "1", the S-35770 becomes the mode to read the free register.

Consequently, the data of the free register is output from the S-35770. Each byte from B7 is transmitted.

When the read operation of the free register is finished, transmit "1" (NO\_ACK) to the acknowledge after B0 output from the master device, and then transmit the stop condition.

The free register is a 3-byte register. "1" is read if the read operation is performed continuously after reading 3 bytes of the free register.

Regarding the free register, refer to "

Configuration of Registers".

Moreover, the internal address pointer is reset if recognizing the stop condition. Therefore, do not transmit the stop condition after dummy write operation. The counter data is read when reading the free register after transmission of the stop condition.

Figure 21 Read Timing of Free Register

18 ABLIC Inc.

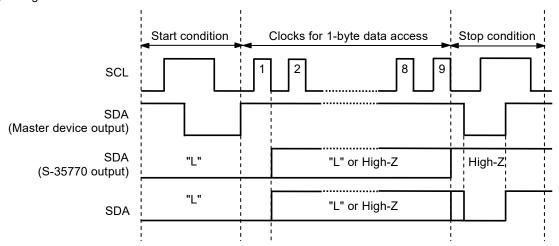

### ■ Release of SDA

The  $\overline{\mathsf{RST}}$  pin of the S-35770 does not perform the reset operation of the communication interface. Therefore, the stop condition is input to reset the internal interface circuit usually.

However, the S-35770 does not accept the stop condition from the master device when in the status that SDA outputs "L" (at the time of acknowledge outputting or reading). Consequently, it is necessary to finish the acknowledge output or the read operation. **Figure 22** shows the SDA release method.

First, input the start condition from the master device (since SDA of the S-35770 outputs "L", the S-35770 can not detect the start condition). Next, input the clocks for 1-byte data access (9 clocks) from SCL. During the time, release SDA of the master device. By this, the SDA input / output before communication interrupt is completed, and SDA of the S-35770 becomes release status. Continuously, if the stop condition is input, the internal circuit resets and the communication returns to normal status.

It is strongly recommended that the SDA release method is performed at the time of system initialization after the power supply voltage of the master device rises.

Figure 22 SDA Release Method

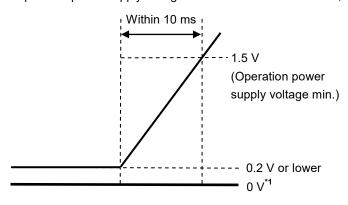

### ■ Power-on Detection Circuit

In order for the power-on detection circuit to operate normally, raise the power supply voltage of the IC from 0.2 V or lower so that it reaches 1.5 V of the operation power supply voltage minimum value within 10 ms, as shown in **Figure 23**.

\*1. 0 V means that there is no potential difference between the VDD pin and the VSS pin of the S-35770.

Figure 23 How to Raise the Power Supply Voltage

# **■** Example of Application Circuit

Figure 24

- Caution 1. Start communication under stable condition after turning on the system power supply.

- 2. The above connection diagrams do not guarantee operation. Set the constants after performing sufficient evaluation using the actual application.

### **■** Precautions

- Do not apply an electrostatic discharge to this IC that exceeds the performance ratings of the built-in electrostatic protection circuit.

- ABLIC Inc. claims no responsibility for any disputes arising out of or in connection with any infringement by products including this IC of patents owned by a third party.

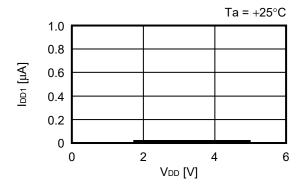

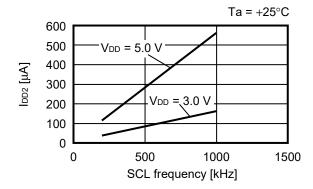

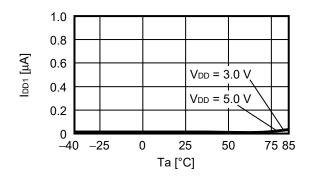

# ■ Characteristics (Typical Data)

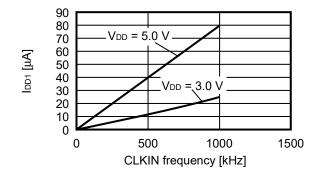

1. Current consumption 1 vs. Power supply voltage characteristics

2. Current consumption 2 vs. SCL frequency characteristics

3. Current consumption 1 vs. Temperature characteristics

4. Current consumption 1 vs. CLKIN frequency characteristics

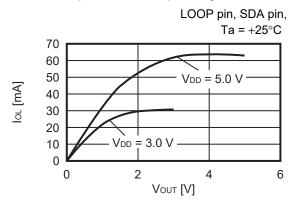

5. Low level output current vs. Output voltage characteristics

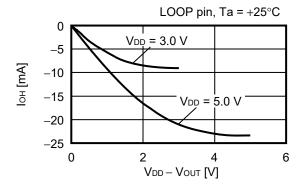

6. High level output current vs. VDD - VOUT characteristics

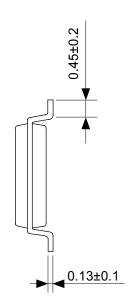

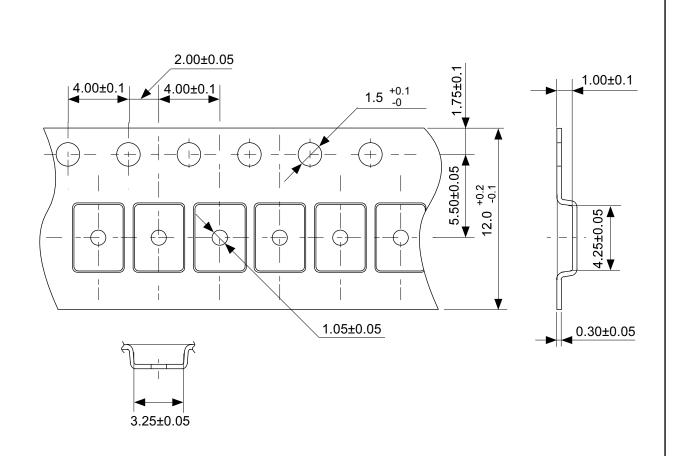

# No. FM008-A-P-SD-1.2

| TITLE      | TMSOP8-A-PKG Dimensions |  |

|------------|-------------------------|--|

| No.        | FM008-A-P-SD-1.2        |  |

| ANGLE      | <b>Q</b>                |  |

| UNIT       | mm                      |  |

|            |                         |  |

|            |                         |  |

|            |                         |  |

| ABLIC Inc. |                         |  |

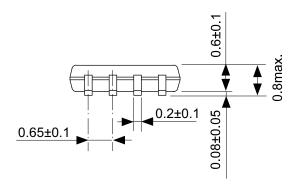

# No. FM008-A-C-SD-2.0

| TITLE      | TMSOP8-A-Carrier Tape |  |

|------------|-----------------------|--|

| No.        | FM008-A-C-SD-2.0      |  |

| ANGLE      |                       |  |

| UNIT       | mm                    |  |

|            |                       |  |

|            |                       |  |

|            |                       |  |

| ABLIC Inc. |                       |  |

# **Disclaimers (Handling Precautions)**

- 1. All the information described herein (product data, specifications, figures, tables, programs, algorithms and application circuit examples, etc.) is current as of publishing date of this document and is subject to change without notice.

- 2. The circuit examples and the usages described herein are for reference only, and do not guarantee the success of any specific mass-production design.

- ABLIC Inc. is not liable for any losses, damages, claims or demands caused by the reasons other than the products described herein (hereinafter "the products") or infringement of third-party intellectual property right and any other right due to the use of the information described herein.

- 3. ABLIC Inc. is not liable for any losses, damages, claims or demands caused by the incorrect information described herein.

- 4. Be careful to use the products within their ranges described herein. Pay special attention for use to the absolute maximum ratings, operation voltage range and electrical characteristics, etc.

- ABLIC Inc. is not liable for any losses, damages, claims or demands caused by failures and / or accidents, etc. due to the use of the products outside their specified ranges.

- 5. Before using the products, confirm their applications, and the laws and regulations of the region or country where they are used and verify suitability, safety and other factors for the intended use.

- 6. When exporting the products, comply with the Foreign Exchange and Foreign Trade Act and all other export-related laws, and follow the required procedures.

- 7. The products are strictly prohibited from using, providing or exporting for the purposes of the development of weapons of mass destruction or military use. ABLIC Inc. is not liable for any losses, damages, claims or demands caused by any provision or export to the person or entity who intends to develop, manufacture, use or store nuclear, biological or chemical weapons or missiles, or use any other military purposes.

- 8. The products are not designed to be used as part of any device or equipment that may affect the human body, human life, or assets (such as medical equipment, disaster prevention systems, security systems, combustion control systems, infrastructure control systems, vehicle equipment, traffic systems, in-vehicle equipment, aviation equipment, aerospace equipment, and nuclear-related equipment), excluding when specified for in-vehicle use or other uses by ABLIC, Inc. Do not apply the products to the above listed devices and equipments.

- ABLIC Inc. is not liable for any losses, damages, claims or demands caused by unauthorized or unspecified use of the products.

- 9. In general, semiconductor products may fail or malfunction with some probability. The user of the products should therefore take responsibility to give thorough consideration to safety design including redundancy, fire spread prevention measures, and malfunction prevention to prevent accidents causing injury or death, fires and social damage, etc. that may ensue from the products' failure or malfunction.

- The entire system in which the products are used must be sufficiently evaluated and judged whether the products are allowed to apply for the system on customer's own responsibility.

- 10. The products are not designed to be radiation-proof. The necessary radiation measures should be taken in the product design by the customer depending on the intended use.

- 11. The products do not affect human health under normal use. However, they contain chemical substances and heavy metals and should therefore not be put in the mouth. The fracture surfaces of wafers and chips may be sharp. Be careful when handling these with the bare hands to prevent injuries, etc.

- 12. When disposing of the products, comply with the laws and ordinances of the country or region where they are used.

- 13. The information described herein contains copyright information and know-how of ABLIC Inc. The information described herein does not convey any license under any intellectual property rights or any other rights belonging to ABLIC Inc. or a third party. Reproduction or copying of the information from this document or any part of this document described herein for the purpose of disclosing it to a third-party is strictly prohibited without the express permission of ABLIC Inc.

- 14. For more details on the information described herein or any other questions, please contact ABLIC Inc.'s sales representative.

- 15. This Disclaimers have been delivered in a text using the Japanese language, which text, despite any translations into the English language and the Chinese language, shall be controlling.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

ABLIC:

S-35770E01I-K8T2U