# **MP2619**

2A, 24V Input, 600kHz 2-3 Cell Switching Li-lon Battery Charger With System Power Path Management

### **DESCRIPTION**

The MP2619 is a monolithic switching charger for 2-3 cell Li-lon battery packs with a built in internal power MOSFET. It achieves up to 2A charge current with current mode control for fast loop response and easy compensation. The charge current can be programmed by sensing the current through an accurate sense resistor.

MP2619 regulates the battery voltage and charge current using two control loops to realize high accuracy CC charge and CV charge.

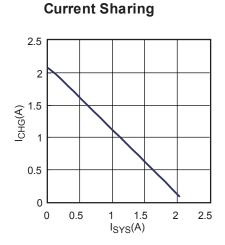

The system power path management function ensures continuous supply to the system by automatically selecting the input or the battery to power the system. Power path management separates charging current from system load. When the MP2619 realizes current sharing of the input current, charge current will drop down according to the increase of the system current.

Fault condition protection includes cycle -by -cycle current limiting, and thermal shutdown. Other safety features include battery temperature charge monitoring. status indication programmable timer to finish the charging cycle.

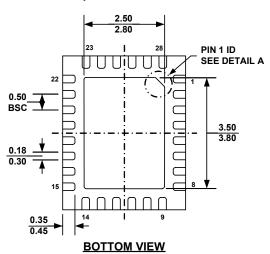

The MP2619 is available in a 28-pin, 4mm x 5mm QFN package.

### **FEATURES**

- Charges 2-3 cell Li-Ion Battery Packs

- Wide Operating Input Range

- Up to 2A Programmable Charging Current

- Power Path Management with Current Sharing

- ±0.75% V<sub>BATT</sub> Accuracy

- 0.2Ω Internal Power MOSFET Switch

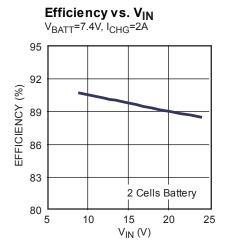

- Up to 90% Efficiency

- Fixed 600kHz Frequency

- Preconditioning for Fully Depleted Batteries

- **Charging Operation Indicator**

- Input Supply and Battery Fault Indicator

- Thermal Shutdown

- Cycle-by-Cycle Over Current Protection

- **Battery Temperature Monitor and Protection**

## **APPLICATIONS**

- Netbook PC

- **Distributed Power Systems**

- Chargers for 2-Cell or 3-Cell Li-lon **Batteries**

- Pre-Regulator for Linear Regulators

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Products, Quality Assurance page.

"MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

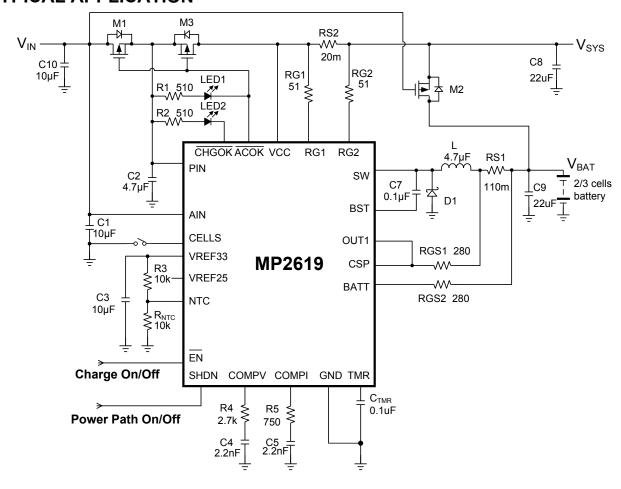

## TYPICAL APPLICATION

#### ORDERING INFORMATION

| Part Number* | Package          | Top Marking |  |

|--------------|------------------|-------------|--|

| MP2619EV     | QFN-28 (4mmx5mm) | MP2619      |  |

\* For Tape & Reel, add suffix –Z (eg. MP2619EV–Z). For RoHS compliant packaging, add suffix –LF (eg. MP2619EV–LF–Z)

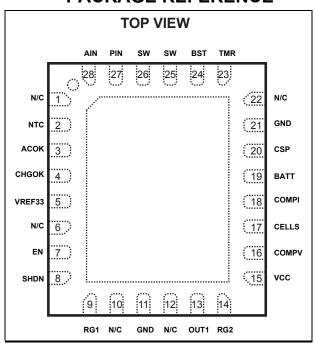

# **PACKAGE REFERENCE**

# ABSOLUTE MAXIMUM RATINGS (1)

# Recommended Operating Conditions (3)

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) = ( $T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB

# **ELECTRICAL CHARACTERISTICS**

$V_{\text{IN}}$  = 19V,  $T_{\text{A}}$  = +25°C, CELLS=0V, unless otherwise noted.

| Parameters                                  | Symbol                              | Condition                                       | Min    | Тур  | Max    | Units         |  |

|---------------------------------------------|-------------------------------------|-------------------------------------------------|--------|------|--------|---------------|--|

| Terminal Pattery Voltage                    | \/                                  | CELLS=0V                                        | 8.337  | 8.4  | 8.463  | V             |  |

| Terminal Battery Voltage                    | $V_{BATT}$                          | CELLS= Float                                    | 12.505 | 12.6 | 12.695 | V             |  |

| CSP, BATT Current                           | I <sub>CSP</sub> ,I <sub>BATT</sub> | Charging disabled                               |        | 1    |        | μΑ            |  |

| Switch On Resistance                        | R <sub>DS(ON)</sub>                 |                                                 |        | 0.2  |        | Ω             |  |

| Switch Leakage                              |                                     | $\overline{EN}$ = 4V, $V_{SW}$ = 0V             |        | 0    | 1      | μΑ            |  |

| Peak Current Limit                          |                                     | CC Mode                                         |        | 4.1  |        | Α             |  |

| Feak Guitent Liniit                         |                                     | Trickle Mode                                    |        | 2    |        | Α             |  |

| CC current                                  | Icc                                 | RS1=100mΩ                                       | 1.8    | 2.0  | 2.2    | Α             |  |

| Trickle charge current                      | ITRICKLE                            |                                                 |        | 10%  |        | Icc           |  |

| Trickle charge voltage threshold            |                                     |                                                 |        | 3.0  |        | V/Cell        |  |

| Trickle charge hysteresis                   |                                     |                                                 |        | 350  |        | mV/Cell       |  |

| Termination current threshold               | I <sub>BF</sub>                     |                                                 | 5%     | 10%  | 15%    | Icc           |  |

| Oscillator Frequency                        | fsw                                 | CELLS=0V,<br>V <sub>BATT</sub> =7V              |        | 600  |        | kHz           |  |

| Fold-back Frequency                         |                                     | V <sub>BATT</sub> = 0V                          |        | 190  |        | kHz           |  |

| Maximum Duty Cycle                          |                                     |                                                 | 90     |      |        | %             |  |

| Maximum current Sense Voltage (CSP to BATT) | V <sub>SENSE</sub>                  |                                                 | 170    | 200  | 230    | mV            |  |

| Under Voltage Lockout Threshold Rising      |                                     |                                                 | 3      | 3.2  | 3.4    | V             |  |

| Under Voltage Lockout Threshold Hysteresis  |                                     |                                                 |        | 200  | 1000   | mV            |  |

| Open-drain sink current                     |                                     | Vdrain=0.3V                                     | 5      |      |        | mA            |  |

| Dead-battery indicator                      |                                     | Stay at trickle charge, C <sub>TMR</sub> =0.1µF |        | 30   |        | min           |  |

| Recharge threshold at Vbatt                 | Vrechg                              |                                                 |        | 4.0  |        | V/cell        |  |

| Recharge Hysteresis                         |                                     |                                                 |        | 100  |        | mV/Cell       |  |

| NTC Low-Temp Rising Threshold               |                                     | R <sub>NTC</sub> =NCP18X103,<br>0°C             | 70.5   | 73.5 | 76.5   | %of<br>VREF33 |  |

| NTC High-Temp Falling Threshold             |                                     | R <sub>NTC</sub> =NCP18X103,<br>50°C            | 27.5   | 29.5 | 31.5   | %of<br>VREF33 |  |

| Vin min head-room (reverse blocking)        |                                     | Vin-Vbatt                                       |        | 180  |        | mV            |  |

| EN Input Low Voltage                        |                                     |                                                 |        |      | 0.4    | V             |  |

| EN Input High Voltage                       |                                     |                                                 | 1.8    |      |        | V             |  |

| EN la 10 mai                                |                                     | <u>EN</u> = 4V                                  |        | 4    |        |               |  |

| EN Input Current                            |                                     | EN = 0V                                         |        | 0.2  |        | μA            |  |

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN}$  = 19V,  $T_A$  = +25°C, CELLS=0V, unless otherwise noted.

| Parameters                      | Symbol                            | Condition                                                                                       | Min | Тур   | Max | Units |

|---------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------|-----|-------|-----|-------|

|                                 |                                   | EN = 4V                                                                                         |     | 0.5   |     | mA    |

| Supply Current (Shutdown)       |                                   | EN = 4V,<br>Consider VREF33 pin<br>output current.<br>R <sub>3</sub> =10k,R <sub>NTC</sub> =10k |     | 0.665 |     | mA    |

| Supply Current (Quiescent)      | I <sub>AIN</sub>                  | EN = 0V,<br>CELLS=0V,<br>VBATT=4.5V                                                             |     |       | 2.0 | mA    |

| Thermal Shutdown <sup>(5)</sup> |                                   |                                                                                                 |     | 150   |     | °C    |

| VREF33 output voltage           |                                   |                                                                                                 |     | 3.3   |     | V     |

| VREF33 load regulation          |                                   | I <sub>LOAD</sub> =0 to 10mA                                                                    |     | 30    |     | mV    |

| Input Current Sense Section     | Input Current Sense Section       |                                                                                                 |     |       |     |       |

| Supply Current                  | Icc                               | $I_{LOAD}$ = 0A, $V_{CC}$ = 40V                                                                 |     | 12    | 30  | μA    |

| OUT1 Input Offset Voltage       | V <sub>OS1</sub>                  |                                                                                                 |     | 0.4   | 2   | mV    |

| OUT1 Current Accuracy           | I <sub>RG1</sub> /I <sub>GS</sub> | V <sub>SENSE</sub> = 100mV                                                                      |     | ±2    | ±5  | %     |

| No-Load OUT1 Error              |                                   | V <sub>SENSE</sub> = 0V                                                                         |     | 0.1   | 1   | μA    |

| Low-Level OUT1 Error            |                                   | V <sub>SENSE</sub> = 5mV                                                                        |     | 0.3   | 2   | μA    |

| Shutdown Supply Current         | Icc(shdn)                         | V <sub>SHDN</sub> = 3V                                                                          |     | 3     | 6   | μA    |

| SHDN Threshold Voltage          | VTH_SHUTD<br>OWN                  | (Low → High)                                                                                    | 0.7 | 0.9   | 1.2 | V     |

| SHDN Hysteresis                 |                                   |                                                                                                 |     | 30    |     | mV    |

#### Notes:

<sup>5)</sup> Guaranteed by design.

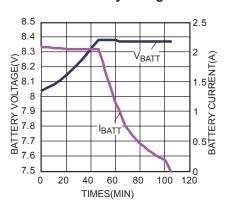

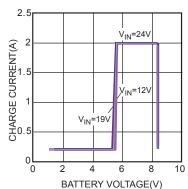

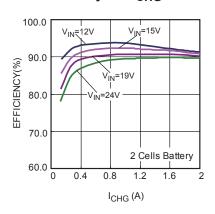

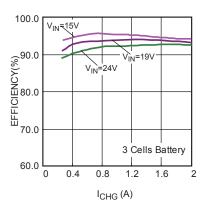

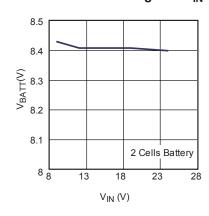

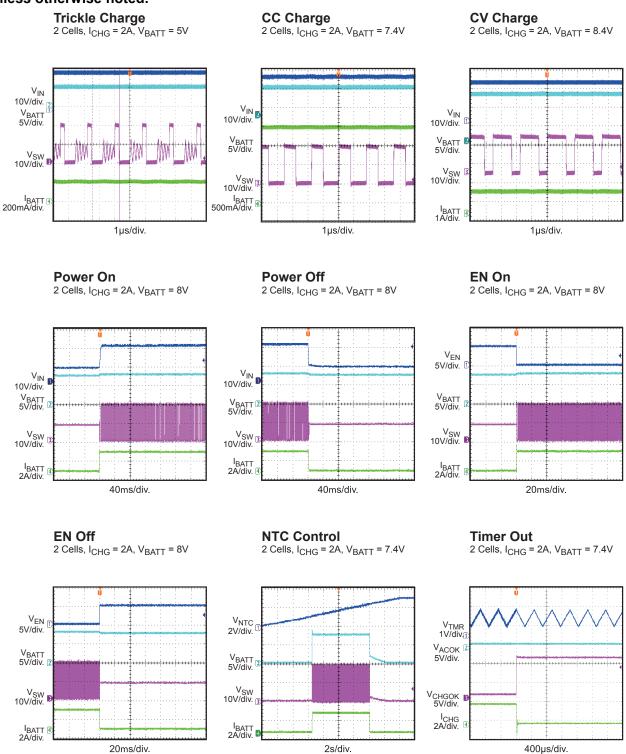

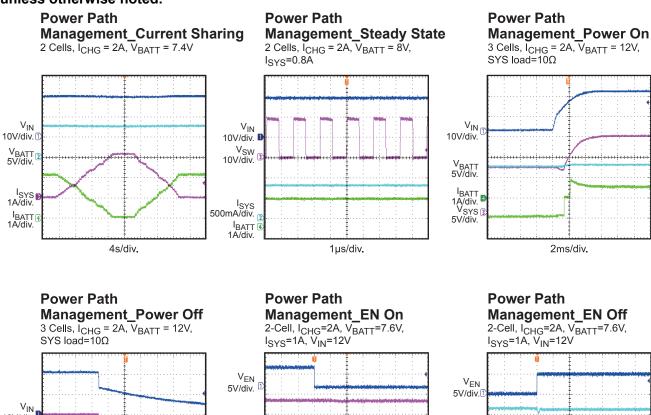

## TYPICAL PERFORMANCE CHARACTERISTICS

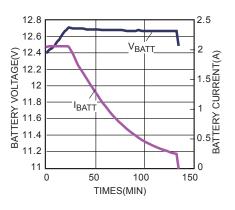

$V_{IN}$ =19V, C1=4.7 $\mu$ F, C2=22 $\mu$ F, L=4.7 $\mu$ H, RS1=110m $\Omega$ , RS2=20m $\Omega$ , Real Battery Load, T<sub>A</sub>=25°C, unless otherwise noted.

2 Cells Battery Charge Curve

2 Cells I<sub>CHG</sub> vs. V<sub>BATT</sub> Curve

3 Cells Battery Charge Curve

3 Cells I<sub>CHG</sub> vs. V<sub>BATT</sub> Curve

Effciency vs. I<sub>CHG</sub>

Effciency vs. I<sub>CHG</sub>

**BATT Float Voltage vs. VIN**

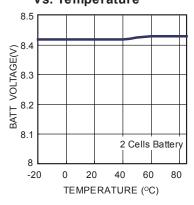

**BATT Float Voltage** vs. Temperature

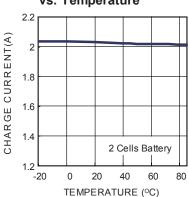

**Charge Current** vs. Temperature

6

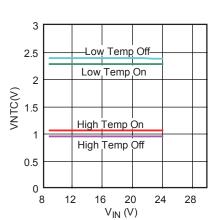

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{\text{IN}}\!=\!19V,~C1\!=\!4.7\mu\text{F},~C2\!=\!22\mu\text{F},~L\!=\!4.7\mu\text{H},~RS1\!=\!110m\Omega,~RS2\!=\!20m\Omega,~Real~Battery~Load,~T_{\text{A}}\!=\!25^{\circ}\text{C},~unless~otherwise~noted.}$

**NTC Control Window**

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{\text{IN}}$ =19V, C1=4.7μF, C2=22μF, L=4.7μH, RS1=110mΩ, RS2=20mΩ, Real Battery Load,  $T_{\text{A}}$ =25°C, unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{\text{IN}}$ =19V, C1=4.7 $\mu$ F, C2=22 $\mu$ F, L=4.7 $\mu$ H, RS1=110m $\Omega$ , RS2=20m $\Omega$ , Real Battery Load, T<sub>A</sub>=25°C, unless otherwise noted.

# **PIN FUNCTIONS**

| Pin#         | Name                   | Description                                                                                                                                                                                                                                                                                                                                       |

|--------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,6,10,12,22 | NC                     | No Connection                                                                                                                                                                                                                                                                                                                                     |

| 2            | NTC                    | Thermistor Input. Connect a resistor from this pin to the pin VREF33 and the Thermistor from this pin to ground.                                                                                                                                                                                                                                  |

| 3            | ACOK                   | Valid Input Supply Indicator. A logic LOW on this pin indicates the presence of a valid input supply.                                                                                                                                                                                                                                             |

| 4            | CHGOK                  | Charging Completion Indicator. A logic LOW indicates charging operation. The pin will become an open drain once the charging is complete.                                                                                                                                                                                                         |

| 5            | VREF33                 | Internal linear regulator 3.3V reference output. Bypass to GND with a 1 $\mu$ F ceramic capacitor.                                                                                                                                                                                                                                                |

| 7            | ĒN                     | On/Off Control Input.                                                                                                                                                                                                                                                                                                                             |

| 8            | SHDN                   | Shutdown control of current sense amplifier. Connect to ground for normal operation.                                                                                                                                                                                                                                                              |

| 9            | RG1                    | Gain Resistor of current sense amplifier.                                                                                                                                                                                                                                                                                                         |

| 11, 21       | GND,<br>Exposed<br>Pad | Ground. This pin is the voltage reference for the regulated output voltage. For this reason care must be taken in its layout. This node should be placed outside of the D1 to C1 ground path to prevent switching current spikes from inducing voltage noise into the part. Connect exposed pad to ground plane for optional thermal performance. |

| 13           | OUT1                   | Output for Driving Resistor Load.                                                                                                                                                                                                                                                                                                                 |

| 14           | RG2                    | Gain Resistor of current sense amplifier.                                                                                                                                                                                                                                                                                                         |

| 15           | VCC                    | Power Input of current sense amplifier.                                                                                                                                                                                                                                                                                                           |

| 16           | COMPV                  | VLOOP Compensation. Decouple this pin with a capacitor and a resistor.                                                                                                                                                                                                                                                                            |

| 17           | CELLS                  | Command Input for the Number of Li-Ion Cells. Connect this pin to VREF33 or keep it float for 3-cell operation or ground the pin for 2-cell operation.                                                                                                                                                                                            |

| 18           | COMPI                  | ILOOP Compensation. Decouple this pin with a capacitor and a resistor.                                                                                                                                                                                                                                                                            |

| 19           | BATT                   | Positive Battery Terminal.                                                                                                                                                                                                                                                                                                                        |

| 20           | CSP                    | Battery Current Sense Positive Input. Connect a resistor RS1 between CSP and BATT.                                                                                                                                                                                                                                                                |

| 23           | TMR                    | Set time constant. 0.1 $\mu$ A current charges and discharges the external cap. DO NOT CONNECT THIS PIN TO GND DIRECTLY.                                                                                                                                                                                                                          |

| 24           | BST                    | Bootstrap. This capacitor is needed to drive the power switch's gate above the supply voltage. It is connected between SW and BST pins to form a floating supply across the power switch driver.                                                                                                                                                  |

| 25, 26       | SW                     | Switch Output.                                                                                                                                                                                                                                                                                                                                    |

| 27           | PIN                    | Power Supply Voltage. The MP2619 operates from a +5.5V to +24V unregulated input. C1 is needed to prevent large voltage spikes from appearing at the input.                                                                                                                                                                                       |

| 28           | AIN                    | Controller Supply Voltage.                                                                                                                                                                                                                                                                                                                        |

## **OPERATION**

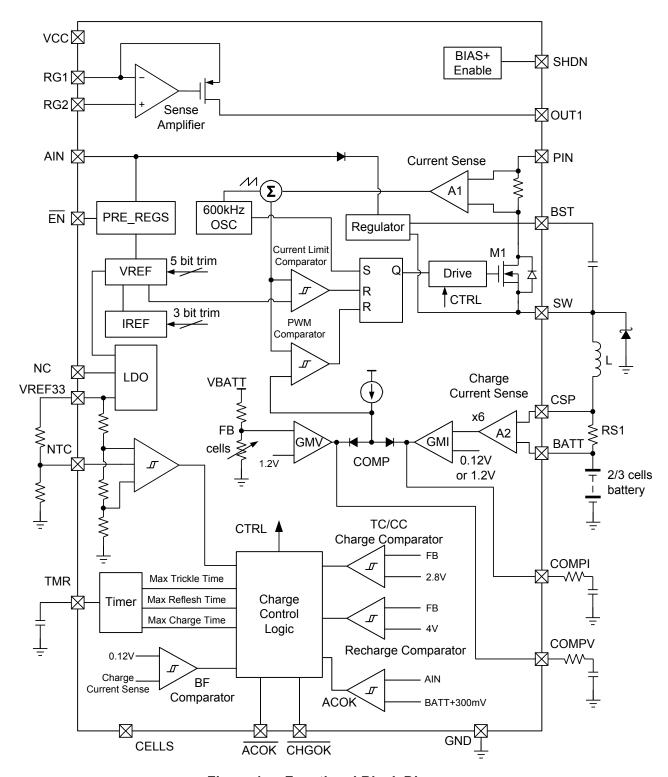

The MP2619 is a peak current mode controlled switching charger for use with Li-lon batteries.

Figure 1 shows the block diagram. At the beginning of a cycle, M1 is off. The COMP voltage is higher than the current sense result from amplifier A1's output and the PWM comparator's output is low. The rising edge of the 600 kHz CLK signal sets the RS Flip-Flop. Its output turns on M1 thus connecting the SW pin and inductor to the input supply.

The increasing inductor current is sensed and amplified by the Current Sense Amplifier A1. Ramp compensation is summed to the output of A1 and compared to COMP by the PWM comparator.

When the sum of A1's output and the Slope Compensation signal exceeds the COMP voltage, the RS Flip-Flop is reset and M1 turns off. The external switching diode D1 then conducts the inductor current.

If the sum of A1's output and the Slope Compensation signal does not exceed the COMP voltage, then the falling edge of the CLK resets the Flip-Flop.

The MP2619 have one internal linear regulators power internal circuit, VREF33. The output of 3.3V reference voltage can also power external circuitry as long as the maximum current (30mA) is not exceeded. A 1uF bypass capacitor is required from VREF33 to GND to ensure stability.

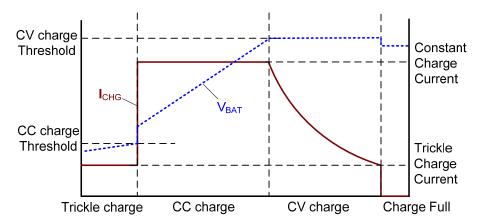

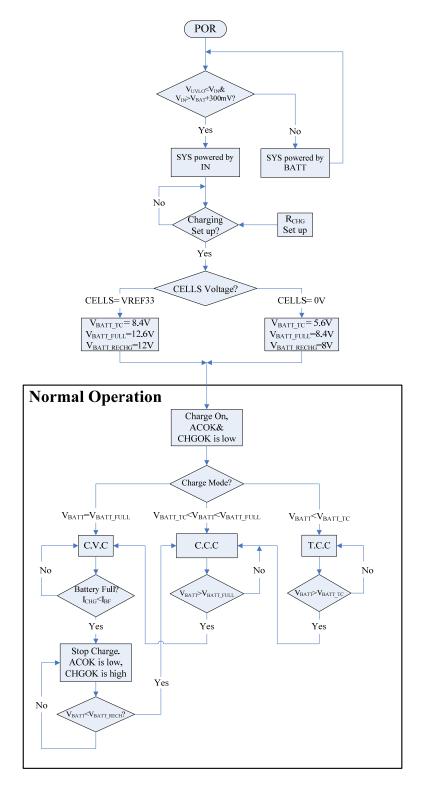

# Charge Cycle (Mode change: Trickle→ CC→ CV)

The battery current is sensed via RS1 (Figure 1) and amplified by A2. The charge will start in "trickle charging mode" (10% of the RS1 programmed current I<sub>CC</sub>) until the battery voltage reaches 3.0V/cell. If the charge stays in the "trickle charging mode" till "timer out" condition triggered, and the charge is terminated. Otherwise, the output of A2 is then regulated to the level set by RS1. The charger is operating at "constant current charging mode." The duty cycle of the switcher is determined by the COMPI voltage that is regulated by the amplifier GMI.

When the battery voltage reaches the "constant voltage mode" threshold, the amplifier GMV will

regulate the COMP pin, and then the duty cycle. The charger will then operate in "constant voltage mode."

#### **Automatic Recharge**

After the battery has completely recharged, the charger disables all blocks except the battery voltage monitor to limit leakage current. If the battery voltage falls below 4.0V/Cell, the chip will begin recharging using soft-start. The timer will then reset to avoid timer-related charging disruptions.

#### **Charger Status Indication**

MP2619 has two open-drain status outputs:

CHGOK and ACOK. The ACOK pin pulls low when an input voltage is greater than battery voltage 300mV and over the under voltage lockout threshold. CHGOK is used to indicate the status of the charge cycle. Table 1 describes the status of the charge cycle based on the CHGOK and ACOK outputs.

**Table 1—Charging Status Indication**

| ACOK | CHGOK | Charger Status                                                                        |

|------|-------|---------------------------------------------------------------------------------------|

| low  | low   | In charging                                                                           |

| low  | high  | End of charge, NTC fault, timer out, thermal shutdown, $\overline{\text{EN}}$ disable |

| high | high  | PIN –V <sub>BATT</sub> <0.3V.<br>AIN <uvlo,< td=""></uvlo,<>                          |

#### **Timer Operation**

MP2619 uses internal timer to terminate the charge if the timer times out. The timer duration is programmed by an external capacitor at the TMR pin.

The trickle mode charge time is:

$$T_{\text{TICKLE\_TMR}} = 30 \text{mins} \times \frac{C_{\text{TMR}}}{0.1 \text{uF}}$$

The total charge time is:

$$T_{TOTAL\_TMR} = 3hours \times \frac{C_{TMR}}{0.1uF}$$

When time-out occurs, charger is suspended. And only refresh the input power or EN signal or auto-recharge (The event that  $V_{BATT}$  falls through 4V/cell) can restart the charge cycle.

#### Negative Thermal Coefficient (NTC) Thermistor

The MP2619 has a built-in NTC resistance window comparator, which allows MP2619 to sense the battery temperature via the thermistor packed internally in the battery pack to ensure a safe operating environment of the battery. A resistor with appropriate value should be connected from VREF33 to NTC pin and the thermistor is connected from NTC pin to GND. The voltage on NTC pin is determined by the resistor divider whose divide ratio depends on the battery temperature. When the voltage of pin NTC falls out of NTC window range, MP2619 will stop the charging. The charger will restart if the temperature goes back into NTC window range.

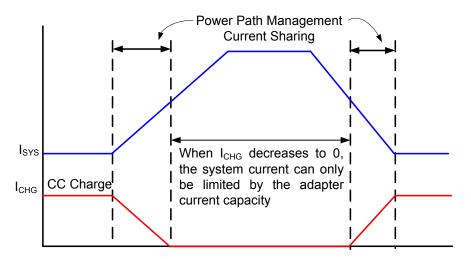

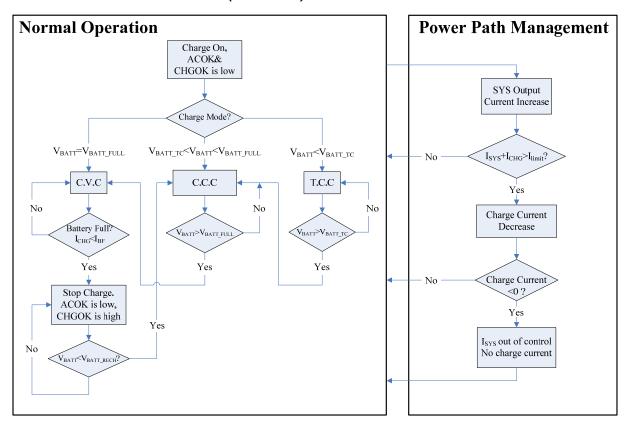

#### **Power Path Management**

MP2619 can implement a switching charger circuit with power path management function, which realizes the current sharing of the charger and system load. In another word, MP2619 senses the system current and feeds it back, then reduces charge current according to the increase of the system current.

However, after the charge current decrease to 0, the system current can only be limited by the adapter.

The system current is satisfied first and always. It chooses the adapter as its power source when the adapter plugs in, and the battery is the backup power source when the adapter is removed.

Figure 2 to 6 shows the charge profile, operation waveform and flow chart, respectively.

## **BLOCK DIAGRAM**

Figure 1 — Functional Block Diagram

## CHARGE PROFILE AND POWER PATH MANAGEMENT FUNCTION

Figure 2 — Li-Ion Battery Charge Profile

Figure 3 — Power Path Management Function- Current Sharing

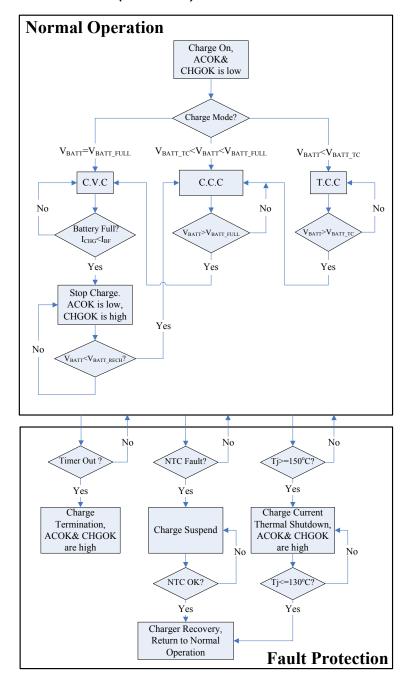

## **OPERATION FLOW CHART**

Figure 4— Normal Charging Operation Flow Chart

# **OPERATION FLOW CHART** (continued)

Figure 5— Power Path Management Operation Flow Chart

# **OPERATION FLOW CHART (continued)**

Figure 6— Fault Protection Flow Chart

#### APPLICATION INFORMATION

#### **Setting the Charge Current**

#### 1. Standalone Switching Charger

The charge current of MP2619 is set by the sense resistor RS1. The charge current programmable formula is as following:

$$I_{CHG}(A) = \frac{200mV}{RS1(m\Omega)}$$

(1)

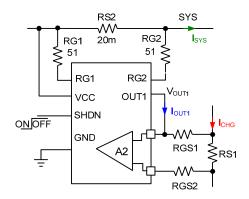

2. Switching Charger with Power Path Management

Figure 7 shows the charge current sharing with the system current.

Figure 7— Charge current sharing with System current

The gain of the system current is set as:

$$Gain = \frac{RGS1}{RG1}$$

(2)

The voltage of OUT1 pin,  $V_{\text{OUT1}}$  can be calculated from:

$$V_{OUT1} = I_{SYS} \times RS2 \times Gain = \frac{I_{SYS} \times RS2 \times RGS1}{RG1} (3)$$

When the system current increased  $\Delta I_{SYS}$ , to satisfy the charge current decreased  $\Delta I_{SYS}$  accordingly. The relationship should be:

$$\Delta I_{BAT} = \frac{\Delta V_{OUT1}}{RS1} = \frac{\Delta I_{SYS} \times RS2 \times RGS1}{RS1 \times RG1}$$

(4)

Because  $\triangle I_{SYS} = \triangle I_{BATT}$ , we can get:

$$\frac{RS1}{RS2} = \frac{RGS1}{RG1}$$

(5)

RGS1/2 causes the charge current sense error as it changes the sense gain of A2, which can be calculated from:

$$G_{A2} = \frac{12.3(k\Omega)}{2(k\Omega) + RGS(k\Omega)}$$

(6)

The charge current is set as:

$$I_{CHG}(A) = \frac{1230}{G_{A2} \times RS1(m\Omega)}$$

(7)

Then the influence of R<sub>GS1</sub> to the charge current is:

$$I_{CHG}(A) = \frac{2000 + RGS(\Omega)}{10 \times RS1(m\Omega)}$$

(8)

To decrease the power loss of the sensing circuit, choose RS2 as small as possible, 20m is recommended. Too small  $R_{\rm G1}$  results in too big current sense error of the system current,  $50\Omega$  is at least.

Substitute these two values into equation (5), then the calibrated charge current set formula in power path application is got from equation (8):

$$I_{CHG}(A) = \frac{2000 + 2.5 \times RS1(m\Omega)}{10 \times RS1(m\Omega)}$$

(9)

Following table is the calculated RS1 and R<sub>GS1</sub> value for setting different charge current.

Table2—I<sub>CHG</sub> Set in Power Path Application

| Icнg(A) | R <sub>GS</sub> (Ω) | RS1(mΩ) |

|---------|---------------------|---------|

| 2       | 280                 | 110     |

| 1.5     | 402                 | 160     |

| 1       | 665                 | 260     |

| 0.8     | 909                 | 360     |

| 0.5     | 2k                  | 800     |

If choose different RS2 and  $R_{\text{G1}}$ , re-calculated from equation (5) and equation (8), then get the different equation (9) and the table.

Also, any relationship between  $\Delta I_{SYS}$  and  $\Delta I_{BATT}$  can be realized by re-calculate equation (4), (5) and (8).

#### Selecting the Inductor

A 1µH to 10µH inductor is recommended for most applications. The inductance value can be derived from the following equation.

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times \Delta I_{L} \times f_{OSC}}$$

(10)

Where  $\Delta I_L$  is the inductor ripple current.  $V_{OUT}$  is the 2/3 cell battery voltage.

Choose inductor current to be approximately 30% if the maximum charge current, 2A. The maximum inductor peak current is:

$$I_{L(MAX)} = I_{CHG} + \frac{\Delta I_L}{2}$$

(11)

Under light load conditions below 100mA, larger inductance is recommended for improved efficiency.

For optimized efficiency, the inductor DC resistance is recommended to be less than  $200m\Omega$ .

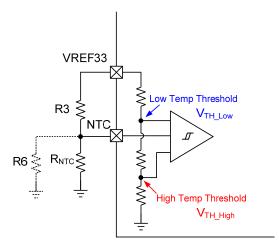

#### **NTC Function**

As Figure 8 shows, the low temperature threshold and high temperature threshold are preset internally via a resistive divider, which are 73%·VREF33 and 30%·VREF33. For a given NTC thermistor, we can select appropriate R3 and R6 to set the NTC window.

In detail, for the thermistor (NCP18XH103) noted in above electrical characteristic,

At 0°C,

$$R_{NTC Cold} = 27.445k$$

;

At 50°C,

$$R_{NTC\_Hot} = 4.1601k$$

.

Assume that the NTC window is between 0°C and 50°C, the following equations could be derived:

$$\frac{R6//R_{NTC\_Cold}}{R3 + R6//R_{NTC\_Cold}} = \frac{V_{TH\_Low}}{VREF33} = 73\%$$

(12)

$$\frac{R6//R_{NTC\_Hot}}{R3 + R6//R_{NTC\_Hot}} = \frac{V_{TH\_High}}{VREF33} = 30\%$$

(13)

According to equation (12) and equation (13), we can find that R3 = 9.63k and R6 = 505k.

To be simple in project, making R3=10k and R6 will approximately meet the connect specification.

Figure 8— NTC function block

#### Selecting the Input Capacitor

The input capacitor reduces the surge current drawn from the input and also the switching noise from the device. The input capacitor impedance at the switching frequency should be less than the input source impedance to prevent high frequency switching current passing to the input. Ceramic capacitors with X5R or X7R dielectrics are highly recommended because of their low ESR and small temperature coefficients. For most applications, a 4.7µF capacitor is sufficient.

#### Selecting the Output Capacitor

The output capacitor keeps output voltage ripple small and ensures regulation loop stability. The output capacitor impedance should be low at the switching frequency. Ceramic capacitors with X5R or X7R dielectrics are recommended.

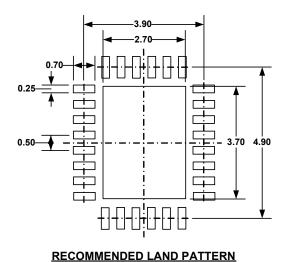

#### **PC Board Layout**

The high frequency and high current paths (GND, IN and SW) should be placed to the device with short, direct and wide traces. The input capacitor needs to be as close as possible to the IN and GND pins. The external feedback resistors should be placed next to the FB pin. Keep the switching node SW short and away from the feedback network.

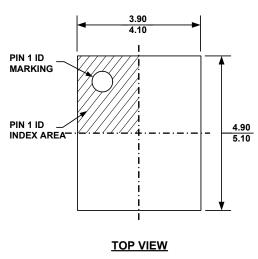

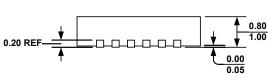

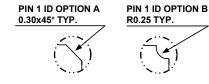

# **PACKAGE INFORMATION**

## **QFN28 (4mm x 5mm)**

SIDE VIEW

**DETAIL A**

# NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

- 3) LEAD COPLANARITY SHALL BE 0.10 MILLIMETER MAX.

4) DRAWING CONFORMS TO JEDEC MO-220, VARIATION VHGD-3.

- 5) DRAWING IS NOT TO SCALE.

NOTICE: The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

$\frac{\text{Monolithic Power Systems (MPS)}}{\text{MP2619EV-LF-Z} \quad \text{MP2619EV-LF-P}}:$