# CMOS, Low Voltage, 2-Wire Serially Controlled, Matrix Switches

## ADG728/ADG729

**FEATURES**

2-Wire Serial Interface

2.7 V to 5.5 V Single Supply

2.5 Ω On Resistance

0.75 Ω On-Resistance Flatness

100 pA Leakage Currents

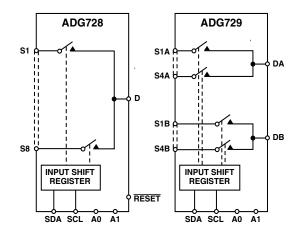

Single 8-to-1 Matrix Switch ADG728

Dual 4-to-1 Matrix Switch ADG729

Power-On Reset

Small 16-Lead TSSOP Package

Qualified for Automotive Applications

APPLICATIONS

Data Acquisition Systems

Communications Systems

Relay Placement

Audio and Video Switching

Automatic Test Equipment

#### **GENERAL DESCRIPTION**

The ADG728 and ADG729 are CMOS analog matrix switches with a serially controlled 2-wire interface. The ADG728 is an 8-channel matrix switch, while the ADG729 is a dual 4-channel matrix switch. On resistance is closely matched between switches and very flat over the full signal range. These parts can operate equally well as either multiplexers, demultiplexers or switch arrays and the input signal range extends to the supplies.

The ADG728 and ADG729 utilize a 2-wire serial interface that is compatible with the  $I^2C^{TM}$  interface standard. Both have two external address pins (A0 and A1). This allows the 2 LSBs of the 7-bit slave address to be set by the user. Four of each of the devices can be connected to the one bus. The ADG728 also has a  $\overline{RESET}$  pin that should be tied high if not in use.

Each channel is controlled by one bit of an 8-bit word. This means that these devices may be used in a number of different configurations; all, any, or none of the channels may be on at any one time.

On power-up of the device, all switches will be in the OFF condition and the internal shift register will contain all zeros.

All channels exhibit break-before-make switching action preventing momentary shorting when switching channels.

The ADG728 and ADG729 are available in 16-lead TSSOP packages.

#### FUNCTIONAL BLOCK DIAGRAMS

## **PRODUCT HIGHLIGHTS**

- 1. 2-Wire Serial Interface.

- 2. Single Supply Operation. The ADG728 and ADG729 are fully specified and guaranteed with 3 V and 5 V supply rails.

- 3. Low On Resistance 2.5  $\Omega$  typical.

- 4. Any configuration of switches may be on at any one time.

- 5. Guaranteed Break-Before-Make Switching Action.

- 6. Small 16-Lead TSSOP Package.

## $ADG728/ADG729 — SPECIFICATIONS^{1} \ (v_{DD} = 5 \ v \ \pm \ 10\%, \ GND = 0 \ v, \ unless \ otherwise \ noted.)$

|                                                 | B Ver                  |                        |                           |                                                                          |

|-------------------------------------------------|------------------------|------------------------|---------------------------|--------------------------------------------------------------------------|

| Parameter                                       | 25°C                   | -40°C<br>to +85°C      | Unit                      | Test Conditions/Comments                                                 |

| ANALOG SWITCH                                   |                        |                        |                           |                                                                          |

| Analog Signal Range                             |                        | 0 V to $V_{DD}$        | V                         |                                                                          |

|                                                 | 2.5                    | U V LU V <sub>DD</sub> |                           | $V_S = 0 \text{ V to } V_{DD}, I_S = 10 \text{ mA};$                     |

| On Resistance (R <sub>ON</sub> )                |                        | 5                      | $\Omega$ typ $\Omega$ max | Test Circuit 1                                                           |

| On-Resistance Match Between                     | 4.5                    | 5                      |                           |                                                                          |

|                                                 |                        | 0.4                    | Ω typ                     | $V_S = 0 \text{ V to } V_{DD}, I_S = 10 \text{ mA}$                      |

| Channels ( $\Delta R_{ON}$ )                    | 0.75                   | 0.8                    | Ω max                     | V = 0 V = V I = 10 ··· A                                                 |

| On-Resistance Flatness (R <sub>FLAT(ON)</sub> ) | 0.75                   | 1.2                    | $\Omega$ typ $\Omega$ max | $V_S = 0 \text{ V to } V_{DD}, I_S = 10 \text{ mA}$                      |

| LEAKAGE CURRENTS                                |                        |                        |                           | V <sub>DD</sub> = 5.5 V                                                  |

| Source OFF Leakage I <sub>S</sub> (OFF)         | ±0.01                  |                        | nA typ                    | $V_D = 4.5 \text{ V/1 V}, V_S = 1 \text{ V/4.5 V}, \text{ Test Circuit}$ |

|                                                 | ±0.1                   | $\pm 0.3$              | nA max                    |                                                                          |

| Drain OFF Leakage I <sub>D</sub> (OFF)          | ±0.01                  |                        | nA typ                    | $V_D = 4.5 \text{ V/1 V}, V_D = 1 \text{ V/4.5 V}, \text{ Test Circuit}$ |

|                                                 | ±0.1                   | ±1                     | nA max                    |                                                                          |

| Channel ON Leakage ID, IS (ON)                  | ±0.01                  |                        | nA typ                    | $V_D = V_S = 4.5 \text{ V/1 V}$ , Test Circuit 4                         |

|                                                 | ±0.1                   | ±1                     | nA max                    |                                                                          |

| LOGIC INPUTS (A0, A1) <sup>2</sup>              |                        |                        |                           |                                                                          |

| Input High Voltage, V <sub>INH</sub>            |                        | 2.4                    | V min                     |                                                                          |

| Input Low Voltage, V <sub>INL</sub>             |                        | 0.8                    | V max                     |                                                                          |

| Input Current                                   |                        |                        |                           |                                                                          |

| I <sub>INL</sub> or I <sub>INH</sub>            | 0.005                  |                        | μA typ                    |                                                                          |

|                                                 |                        | $\pm 0.1$              | μA max                    |                                                                          |

| C <sub>IN</sub> , Input Capacitance             | 6                      |                        | pF typ                    |                                                                          |

| LOGIC INPUTS (SCL, SDA) <sup>2</sup>            |                        |                        |                           |                                                                          |

| Input High Voltage, V <sub>INH</sub>            |                        | $0.7~\mathrm{V_{DD}}$  | V min                     |                                                                          |

| . 0 0, 1111                                     |                        | $V_{DD} + 0.3$         | V max                     |                                                                          |

| Input Low Voltage, V <sub>INL</sub>             |                        | -0.3                   | V min                     |                                                                          |

| . 0, 11.2                                       |                        | $0.3~\mathrm{V_{DD}}$  | V max                     |                                                                          |

| I <sub>IN</sub> , Input Leakage Current         | 0.005                  | DD                     | μA typ                    | $V_{IN} = 0 \text{ V to } V_{DD}$                                        |

|                                                 |                        | $\pm 1.0$              | μA max                    |                                                                          |

| V <sub>HYST</sub> , Input Hysteresis            | $0.05~\mathrm{V_{DD}}$ |                        | V min                     |                                                                          |

| C <sub>IN</sub> , Input Capacitance             | 6                      |                        | pF typ                    |                                                                          |

| LOGIC OUTPUT (SDA) <sup>2</sup>                 |                        |                        |                           |                                                                          |

| V <sub>OL</sub> , Output Low Voltage            |                        | 0.4                    | V max                     | $I_{SINK} = 3 \text{ mA}$                                                |

| OD - with an end of                             |                        | 0.6                    | V max                     | $I_{SINK} = 6 \text{ mA}$                                                |

| DYNAMIC CHARACTERISTICS <sup>2</sup>            |                        |                        |                           |                                                                          |

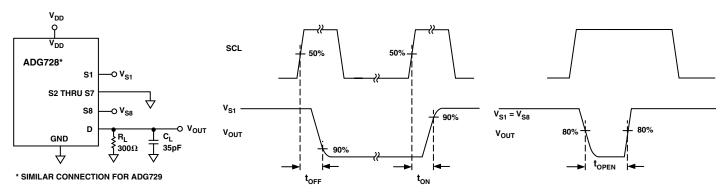

| $t_{ON}$                                        | 95                     |                        | ns typ                    | $R_L = 300 \Omega$ , $C_L = 35 pF$ , Test Circuit 5;                     |

|                                                 |                        | 140                    | ns max                    | $V_{S1} = 3 \text{ V}$                                                   |

| $t_{ m OFF}$                                    | 85                     |                        | ns typ                    | $V_{S1} = 3 \text{ V}, R_L = 300 \Omega, C_L = 35 \text{ pF};$           |

| 011                                             |                        | 130                    | ns max                    | Test Circuit 5                                                           |

| Break-Before-Make Time Delay, t <sub>D</sub>    | 8                      |                        | ns typ                    | $R_L = 300 \Omega, C_L = 35 pF;$                                         |

|                                                 |                        | 1                      | ns min                    | $V_{S1} = V_{S2} = 3 \text{ V}$ , Test Circuit 5                         |

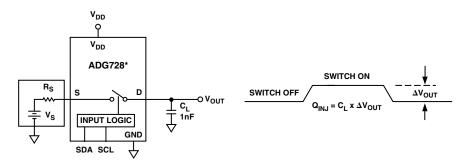

| Charge Injection                                | ±3                     |                        | pC typ                    | $V_S = 2.5 \text{ V}, R_S = 0 \Omega, C_L = 1 \text{ nF};$               |

|                                                 |                        |                        | 1 - 31                    | Test Circuit 6                                                           |

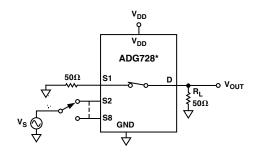

| Off Isolation                                   | -55                    |                        | dB typ                    | $R_L = 50 \Omega, C_L = 5 pF, f = 10 MHz;$                               |

|                                                 | -75                    |                        | dB typ                    | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ;                         |

|                                                 | '3                     |                        | ub typ                    | Test Circuit 8                                                           |

| Channel-to-Channel Crosstalk                    | -55                    |                        | dB typ                    | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 10 MHz$ ;                        |

| Chamier-to-Chamier Grosstaik                    | -75                    |                        | dB typ                    | $R_L = 50 \Omega$ , $C_L = 5 \text{ pF}$ , $f = 1 \text{ MHz}$ ;         |

|                                                 | ,,,                    |                        | ub typ                    | Test Circuit 7                                                           |

| -3 dB Bandwidth                                 |                        |                        |                           |                                                                          |

| ADG728                                          | 65                     |                        | MHz typ                   | $R_L = 50 \Omega$ , $C_L = 5 pF$ , Test Circuit 8                        |

| ADG729                                          | 100                    |                        | MHz typ                   |                                                                          |

| $C_S(OFF)$                                      | 13                     |                        | pF typ                    |                                                                          |

| $C_{\rm D}$ (OFF)                               |                        |                        | _ ,,                      |                                                                          |

| ADG728                                          | 85                     |                        | pF typ                    |                                                                          |

| ADG729                                          | 42                     |                        | pF typ                    |                                                                          |

| $C_D, C_S(ON)$                                  |                        |                        | FJF                       |                                                                          |

| ADG728                                          | 96                     |                        | pF typ                    |                                                                          |

| ADG729                                          | 48                     |                        | pF typ                    |                                                                          |

| POWER REQUIREMENTS                              | -                      |                        | r Jr                      | V <sub>DD</sub> = 5.5 V                                                  |

|                                                 | 10                     |                        | μA typ                    | $V_{DD} = 3.5 \text{ V}$ Digital Inputs = 0 V or 5.5 V                   |

| $I_{ m DD}$                                     | 10                     |                        | MI LVD                    | Digital iliputs – 0 v of 3.3 v                                           |

-2-

<sup>&</sup>lt;sup>1</sup>Temperature range is as follows: B Version: -40°C to +85°C. <sup>2</sup>Guaranteed by design, not subject to production test.

## $SPECIFICATIONS^{1} \ (v_{DD}=3 \ v \pm 10\%, \ GND=0 \ V, \ unless \ otherwise \ noted.)$

|                                                         | B Vers                 | ion<br>–40°C           |         |                                                                                                     |

|---------------------------------------------------------|------------------------|------------------------|---------|-----------------------------------------------------------------------------------------------------|

| Parameter                                               | 25°C                   | to +85°C               | Unit    | Test Conditions/Comments                                                                            |

| ANALOG SWITCH                                           |                        |                        |         |                                                                                                     |

| Analog Signal Range                                     |                        | 0 V to V <sub>DD</sub> | v       |                                                                                                     |

| On Resistance (R <sub>ON</sub> )                        | 6                      | о т со трр             | Ω typ   | $V_S = 0 \text{ V to } V_{DD}, I_S = 10 \text{ mA};$                                                |

| 0 11 110010 turio (11011)                               | 11                     | 12                     | Ω max   | Test Circuit 1                                                                                      |

| On-Resistance Match Between                             |                        | 0.4                    | Ω typ   | $V_S = 0$ V to $V_{DD}$ , $I_S = 10$ mA                                                             |

| Channels $(\Delta R_{ON})$                              |                        | 1.2                    | Ω max   | · 3 · · · · · · · · · · · · · · · · · ·                                                             |

| On-Resistance Flatness (R <sub>FLAT(ON)</sub> )         |                        | 3.5                    | Ω typ   | $V_S = 0 \text{ V to } V_{DD}, I_S = 10 \text{ mA}$                                                 |

| . ,                                                     |                        |                        | -51     |                                                                                                     |

| LEAKAGE CURRENTS Source OFF Leakage Is (OFF)            | +0.01                  |                        |         | $V_{DD} = 3.3 \text{ V}$ $V_{DD} = 3.4 \text{ V}$ $V_{DD} = 3.3 \text{ V}$ $V_{DD} = 3.3 \text{ V}$ |

| Source Off Leakage Is (Off)                             | ±0.01                  | ±0.2                   | nA typ  | $V_S = 3 \text{ V/1 V}, V_D = 1 \text{ V/3 V}, \text{ Test Circuit 2}$                              |

| Durin OFF Loshops L (OFF)                               | ±0.1                   | ±0.3                   | nA max  | V = 2 V/1 V V = 1 V/2 V Test Circuit 2                                                              |

| Drain OFF Leakage I <sub>D</sub> (OFF)                  | ±0.01                  | ⊥1                     | nA typ  | $V_D = 3 \text{ V/1 V}, V_D = 1 \text{ V/3 V}, \text{ Test Circuit 3}$                              |

| Channel ON Leabage I I (ON)                             | ±0.1                   | ±1                     | nA max  | V - V - 2 V/1 V Tast Circuit 4                                                                      |

| Channel ON Leakage I <sub>D</sub> , I <sub>S</sub> (ON) | ±0.01                  | ±1                     | nA typ  | $V_D = V_S = 3 \text{ V/1 V}$ , Test Circuit 4                                                      |

|                                                         | ±0.1                   | ±1                     | nA max  |                                                                                                     |

| LOGIC INPUTS (A0, A1) <sup>2</sup>                      |                        |                        |         |                                                                                                     |

| Input High Voltage, V <sub>INH</sub>                    |                        | 2.0                    | V min   |                                                                                                     |

| Input Low Voltage, V <sub>INL</sub>                     |                        | 0.4                    | V max   |                                                                                                     |

| Input Current                                           |                        |                        |         |                                                                                                     |

| I <sub>INL</sub> or I <sub>INH</sub>                    | 0.005                  |                        | μA typ  |                                                                                                     |

|                                                         |                        | ±0.1                   | μA max  |                                                                                                     |

| C <sub>IN</sub> , Input Capacitance                     | 3                      |                        | pF typ  |                                                                                                     |

| LOGIC INPUTS (SCL, SDA) <sup>2</sup>                    |                        |                        |         |                                                                                                     |

| Input High Voltage, V <sub>INH</sub>                    |                        | $0.7 V_{DD}$           | V min   |                                                                                                     |

| r as a second second                                    |                        | $V_{DD} + 0.3$         | V max   |                                                                                                     |

| Input Low Voltage, V <sub>INL</sub>                     |                        | -0.3                   | V min   |                                                                                                     |

|                                                         |                        | $0.3~\mathrm{V_{DD}}$  | V max   |                                                                                                     |

| I <sub>IN</sub> , Input Leakage Current                 | 0.005                  | *** · DD               | μA typ  | $V_{IN} = 0 \text{ V to } V_{DD}$                                                                   |

| -IIV)P to = to                                          |                        | ±1.0                   | μA max  | · IN · · · · · · · · · · · · · · · · · ·                                                            |

| V <sub>HYST</sub> , Input Hysteresis                    | $0.05~\mathrm{V_{DD}}$ |                        | V min   |                                                                                                     |

| C <sub>IN</sub> , Input Capacitance                     | 3                      |                        | pF typ  |                                                                                                     |

| LOGIC OUTPUT (SDA) <sup>2</sup>                         |                        |                        | 1 31    |                                                                                                     |

| $V_{OL}$ , Output Low Voltage                           |                        | 0.4                    | V max   | $I_{SINK} = 3 \text{ mA}$                                                                           |

| VOL, Output Low Voltage                                 |                        | 0.4                    | V max   | $I_{SINK} = 5 \text{ mA}$                                                                           |

| DIRILING ONLY DI CERRICE COS                            |                        | 0.0                    | VIIIax  | ISINK - 0 IIII I                                                                                    |

| DYNAMIC CHARACTERISTICS <sup>2</sup>                    | 100                    |                        |         | D                                                                                                   |

| $t_{ON}$                                                | 130                    | • • • •                | ns typ  | $R_L = 300 \Omega$ , $C_L = 35 pF$ , Test Circuit 5;                                                |

|                                                         |                        | 200                    | ns max  | $V_{S1} = 2 V$                                                                                      |

| $t_{ m OFF}$                                            | 115                    | 400                    | ns typ  | $R_L = 300 \Omega, C_L = 35 pF;$                                                                    |

| D 1 D C 1/1 / 17: D 1                                   |                        | 180                    | ns max  | $V_S = 2 V$ , Test Circuit 5                                                                        |

| Break-Before-Make Time Delay, t <sub>D</sub>            | 8                      |                        | ns typ  | $R_L = 300 \Omega, C_L = 35 pF;$                                                                    |

|                                                         |                        | 1                      | ns min  | $V_{S1} = V_{S8} = 2 \text{ V}$ , Test Circuit 5                                                    |

| Charge Injection                                        | ±3                     |                        | pC typ  | $V_S = 1.5 \text{ V}, R_S = 0 \Omega, C_L = 1 \text{ nF};$                                          |

| OWI 1                                                   |                        |                        | 100     | Test Circuit 6                                                                                      |

| Off Isolation                                           | -55<br>-55             |                        | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 10 MHz$ ;                                                   |

|                                                         | -75                    |                        | dB typ  | $R_L = 50 \Omega, C_L = 5 pF, f = 1 MHz;$                                                           |

| 0 11                                                    |                        |                        | 170     | Test Circuit 8                                                                                      |

| Crosstalk                                               | -55<br>                |                        | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 10 MHz$ ;                                                   |

|                                                         | -75                    |                        | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ;                                                    |

| 0 ID D 1 111                                            | 1                      |                        |         | Test Circuit 7                                                                                      |

| -3 dB Bandwidth                                         |                        |                        |         | B 5000 5 5 5 5 5 5                                                                                  |

| ADG728                                                  | 65                     |                        | MHz typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ , Test Circuit 8                                                   |

| ADG729                                                  | 100                    |                        | MHz typ |                                                                                                     |

| $C_{S}$ (OFF)                                           | 13                     |                        | pF typ  |                                                                                                     |

| $C_{\rm D}$ (OFF)                                       | 05                     |                        | _       |                                                                                                     |

| ADG728                                                  | 85                     |                        | pF typ  |                                                                                                     |

| ADG729                                                  | 42                     |                        | pF typ  |                                                                                                     |

| $C_D, C_S(ON)$                                          |                        |                        | _       |                                                                                                     |

| ADG728                                                  | 96                     |                        | pF typ  |                                                                                                     |

| ADG729                                                  | 48                     |                        | pF typ  |                                                                                                     |

| POWER REQUIREMENTS                                      |                        |                        |         | $V_{DD} = 3.3 \text{ V}$                                                                            |

| $I_{\mathrm{DD}}$                                       | 10                     |                        | μA typ  | Digital Inputs = 0 V or 3.3 V                                                                       |

|                                                         | 1                      | 20                     | μA max  |                                                                                                     |

NOTES

1 Temperature ranges are as follows: B Versions: -40°C to +85°C.

<sup>&</sup>lt;sup>2</sup>Guaranteed by design, not subject to production test.

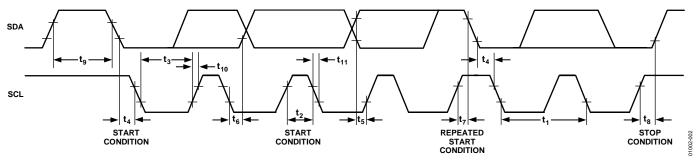

## TIMING CHARACTERISTICS

$V_{\rm DD}$  = 2.7 V to 5.5 V. All specifications -40°C to +85°C, unless otherwise noted. See Figure 1.

| Parameter        | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit    | Test Conditions/Comments                                                 |

|------------------|----------------------------------------------|---------|--------------------------------------------------------------------------|

| f <sub>SCL</sub> | 400                                          | kHz max | SCL clock frequency                                                      |

| $t_1$            | 2.5                                          | μs min  | SCL cycle time                                                           |

| $t_2$            | 0.6                                          | μs min  | SCL high time, t <sub>HIGH</sub>                                         |

| t <sub>3</sub>   | 1.3                                          | μs min  | SCL low time, t <sub>LOW</sub>                                           |

| t <sub>4</sub>   | 0.6                                          | μs min  | Start/repeated start condition hold time, thd, STA                       |

| $t_5$            | 100                                          | ns min  | Data setup time, t <sub>SU, DAT</sub>                                    |

| $t_6^1$          | 0.9                                          | μs max  | Data hold time, t <sub>HD, DAT</sub>                                     |

|                  | 0                                            | μs min  |                                                                          |

| t <sub>7</sub>   | 0.6                                          | μs min  | Setup time for repeated start, t <sub>SU, STA</sub>                      |

| t <sub>8</sub>   | 0.6                                          | μs min  | Stop condition setup time, t <sub>SU, STO</sub>                          |

| t <sub>9</sub>   | 1.3                                          | μs min  | Bus free time between a stop condition and a start condition, tbuf       |

| t <sub>10</sub>  | 300                                          | ns max  | Rise time of both SCL and SDA when receiving, $t_{\mbox{\scriptsize R}}$ |

|                  | 20 + 0.1Cb2                                  | ns min  |                                                                          |

| t <sub>11</sub>  | 250                                          | ns max  | Fall time of SDA when receiving, t <sub>F</sub>                          |

|                  | 300                                          | ns max  | Fall time of SDA when transmitting, t <sub>F</sub>                       |

|                  | 0.1C <sub>b</sub> <sup>2</sup>               | ns min  |                                                                          |

| $C_b^2$          | 400                                          | pF max  | Capacitive load for each bus line                                        |

| $t_{SP}{}^{3}$   | 50                                           | ns max  | Pulse width of spike suppressed                                          |

<sup>&</sup>lt;sup>1</sup> A master device must provide a hold time of at least 300 ns for the SDA signal (referred to the V<sub>H</sub> min of the SCL signal) to bridge the undefined region of the falling edge of SCL. <sup>2</sup>  $C_b$  is the total capacitance of one bus line in pF.  $t_R$  and  $t_F$  measured between 0.3  $V_{DD}$  and 0.7  $V_{DD}$ . <sup>3</sup> Input filtering on both the SCL and SDA inputs suppress noise spikes that are less than 50 ns.

Figure 1. 2-Wire Serial Interface Timing Diagram

REV. C

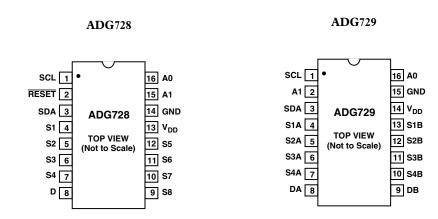

## PIN FUNCTION DESCRIPTIONS

| ADG728        | ADG729         | Mnemonic    | Function                                                                                                                                                                                                                                                                                                                |

|---------------|----------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | 1              | SCL         | Serial Clock Line. This is used in conjunction with the SDA line to clock data into the 8-bit input shift register. Clock rates of up to 400 kbit/s can be accommodated with this 2-wire serial interface.                                                                                                              |

| 2             |                | RESET       | Active low control input that clears the input register and turns all switches to the OFF condition.                                                                                                                                                                                                                    |

| 3             | 3              | SDA         | Serial Data Line. This is used in conjunction with the SCL line to clock data into the 8-bit input shift register during the write cycle and used to read back 1 byte of data during the read cycle. It is a bidirectional open-drain data line which should be pulled to the supply with an external pull-up resistor. |

| 4, 5, 6, 7    | 4, 5, 6, 7     | Sxx         | Source. May be an input or output.                                                                                                                                                                                                                                                                                      |

| 8             | 8, 9           | Dx          | Drain. May be an input or output.                                                                                                                                                                                                                                                                                       |

| 9, 10, 11, 12 | 10, 11, 12, 13 | Sxx         | Source. May be an input or output.                                                                                                                                                                                                                                                                                      |

| 13            | 14             | $V_{ m DD}$ | Power Supply Input. These parts can be operated from a supply of 2.7 V to 5.5 V.                                                                                                                                                                                                                                        |

| 14            | 15             | GND         | Ground Reference.                                                                                                                                                                                                                                                                                                       |

| 15            | 2              | A1          | Address Input. Sets the second least significant bit of the 7-bit slave address.                                                                                                                                                                                                                                        |

| 16            | 16             | A0          | Address Input. Sets the least significant bit of the 7-bit slave address.                                                                                                                                                                                                                                               |

## PIN CONFIGURATIONS

REV. C -5-

## ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| $(T_A = 25^{\circ}C \text{ unless otherwise noted.})$                               |

|-------------------------------------------------------------------------------------|

| $V_{DD}$ to GND $$                                                                  |

| Analog, Digital Inputs <sup>2</sup> $-0.3 \text{ V}$ to $V_{DD} + 0.3 \text{ V}$ or |

| 30 mA, Whichever Occurs First                                                       |

| Peak Current, S or D                                                                |

| (Pulsed at 1 ms, 10% Duty Cycle max)                                                |

| Continuous Current, Each S 30 mA                                                    |

| Continuous Current D, ADG729 80 mA                                                  |

| Continuous Current D, ADG728 120 mA                                                 |

| Operating Temperature Range                                                         |

| Industrial (B Version)40°C to +85°C                                                 |

| Storage Temperature Range65°C to +150°C                                             |

| Junction Temperature 150°C                                                          |

| $\theta_{IA}$ Thermal Impedance          | 150.4°C/W |

|------------------------------------------|-----------|

| $\theta_{JC}$ Thermal Impedance          | 27.6°C/W  |

| Lead Temperature, Soldering As per JEDEC | J-STD-020 |

#### NOTES

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Only one absolute maximum rating may be applied at any one time.

<sup>2</sup>Overvoltages at IN, S or D will be clamped by internal diodes. Current should be limited to the maximum ratings given.

#### **CAUTION** -

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADG728/ADG729 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

## **TERMINOLOGY**

| T.7                           | Mark Daviding Dames County Date of 1                                                         | C (ON)             | "ONI" Secient Committee Manager Local and                                           |  |

|-------------------------------|----------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------|--|

| $V_{ m DD}$                   | Most Positive Power Supply Potential.                                                        | $C_D$ , $C_S$ (ON) | "ON" Switch Capacitance. Measured with reference to ground.                         |  |

| $I_{DD}$                      | Positive Supply Current.                                                                     | $C_{IN}$           | Digital Input Capacitance.                                                          |  |

| GND                           | Ground (0 V) Reference.                                                                      |                    |                                                                                     |  |

| S                             | Source Terminal. May be an input or output.                                                  | $t_{ON}$           | Delay time between the 50% and 90% points of the STOP condition and the switch "ON" |  |

| D                             | Drain Terminal. May be an input or output.                                                   |                    | condition.                                                                          |  |

| $V_D(V_S)$                    | Analog Voltage on Terminals D, S.                                                            | $t_{ m OFF}$       | Delay time between the 50% and 90% points                                           |  |

| $R_{ON}$                      | Ohmic Resistance between D and S.                                                            |                    | of the STOP condition and the switch "OFF"                                          |  |

| $\Delta R_{ON}$               | On Resistance Match Between any Two Chan-                                                    |                    | condition.                                                                          |  |

|                               | nels, i.e., R <sub>ON</sub> max – R <sub>ON</sub> min.                                       | $t_{\mathrm{D}}$   | "OFF" time measured between the 80% points of                                       |  |

| $R_{FLAT\left(ON\right)}$     | Flatness is defined as the difference between the maximum and minimum value of on resistance |                    | both switches when switching from one switch to another.                            |  |

|                               | as measured over the specified analog signal range.                                          | Charge             | A measure of the glitch impulse transferred from                                    |  |

| I <sub>S</sub> (OFF)          | Source Leakage Current with the Switch "OFF."                                                | Injection          | the digital input to the analog output during switching.                            |  |

| $I_D$ (OFF)                   | Drain Leakage Current with the Switch "OFF."                                                 | Off Isolation      | A measure of unwanted signal coupling through                                       |  |

| $I_D$ , $I_S$ (ON)            | Channel Leakage Current with the Switch "ON."                                                | On isolation       | an "OFF" switch.                                                                    |  |

| $V_{INL}$                     | Maximum Input Voltage for Logic "0."                                                         | Crosstalk          | A measure of unwanted signal which is coupled                                       |  |

| $V_{INH}$                     | Minimum Input Voltage for Logic "1."                                                         |                    | through from one channel to another as a result                                     |  |

| $I_{INL}\left(I_{INH}\right)$ | Input Current of the Digital Input.                                                          |                    | of parasitic capacitance.                                                           |  |

| C <sub>S</sub> (OFF)          | "OFF" Switch Source Capacitance. Measured with reference to ground.                          | Bandwidth          | The frequency at which the output is attenuated by 3 dBs.                           |  |

| C <sub>D</sub> (OFF)          | "OFF" Switch Drain Capacitance. Measured                                                     | On Response        | The frequency response of the "ON" switch.                                          |  |

| C <sub>D</sub> (OIT)          | with reference to ground.                                                                    | Insertion          | The loss due to the ON resistance of the switch.                                    |  |

|                               |                                                                                              | Loss               |                                                                                     |  |

-6-

REV. C

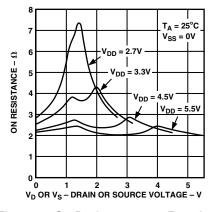

## Typical Performance Characteristics—ADG728/ADG729

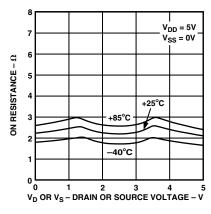

Figure 2. On Resistance as a Function of  $V_D$  ( $V_S$ ) for Single Supply

Figure 3. On Resistance as a Function of  $V_D$  ( $V_S$ ) for Different Temperatures, Single Supply

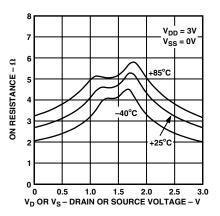

Figure 4. On Resistance as a Function of  $V_D$  ( $V_S$ ) for Different Temperatures, Single Supply

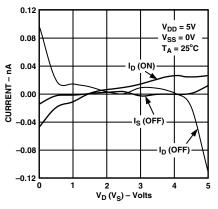

Figure 5. Leakage Currents as a Function of  $V_D$  ( $V_S$ )

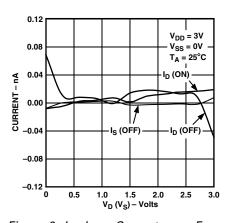

Figure 6. Leakage Currents as a Function of  $V_D$  ( $V_S$ )

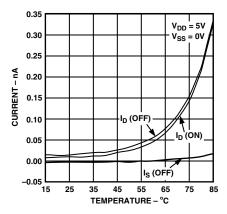

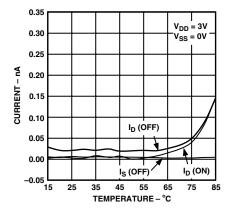

Figure 7. Leakage Currents as a Function of Temperature

Figure 8. Leakage Currents as a Function of Temperature

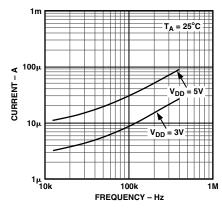

Figure 9. Input Current vs. Switching Frequency

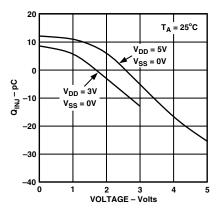

Figure 10. Charge Injection vs. Source Voltage

REV. C -7-

Figure 11.  $T_{ON}/T_{OFF}$  Times vs. Temperature

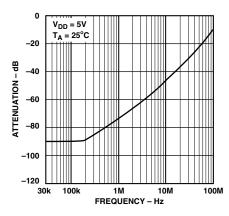

Figure 12. Off Isolation vs. Frequency

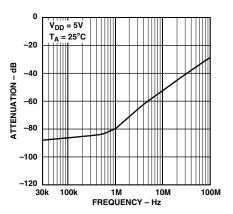

Figure 13. Crosstalk vs. Frequency

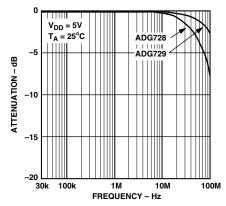

Figure 14. On Response vs. Frequency

-8- REV. C

#### **GENERAL DESCRIPTION**

The ADG728 and ADG729 are serially controlled, 8-channel and dual 4-channel matrix switches respectively. While providing the normal multiplexing and demultiplexing functions, these devices also provide the user with more flexibility as to where their signal may be routed. Each bit of the serial word corresponds to one switch of the device. A Logic 1 in the particular bit position turns on the switch, while a Logic 0 turns the switch off. Because each switch is independently controlled by an individual bit, this provides the option of having any, all, or none of the switches ON. This feature may be particularly useful in the demultiplexing application where the user may wish to direct one signal from the drain to a number of outputs (sources). Care must be taken, however, in the multiplexing situation where a number of inputs may be shorted together (separated only by the small on resistance of the switch).

When changing the switch conditions, a new 8-bit word is written to the input shift register. Some of the bits may be the same as the previous write cycle, as the user may not wish to change the state of some switches. In order to minimize glitches on the output of these switches, the part cleverly compares the state of switches from the previous write cycle. If the switch is already in the ON condition, and is required to stay ON, there will be minimal glitches on the output of the switch.

#### **POWER-ON RESET**

On power-up of the device, all switches will be in the OFF condition and the internal shift register is filled with zeros and will remain so until a valid write takes place.

## **SERIAL INTERFACE**

#### 2-Wire Serial Bus

The ADG728/ADG729 are controlled via an I<sup>2</sup>C compatible serial bus. These parts are connected to this bus as a slave device (no clock is generated by the multiplexer).

The ADG728/ADG729 have different 7-bit slave addresses. The five MSBs of the ADG728 are 10011, while the MSBs of the ADG729 are 10001 and the two LSBs are determined by the state of the A0 and A1 pins.

The 2-wire serial bus protocol operates as follows:

The master initiates data transfer by establishing a START condition which is when a high-to-low transition on the SDA line occurs while SCL is high. The following byte is the address byte, which consists of the 7-bit slave address followed by a R/W bit (this bit determines whether data will be read from or written to the slave device).

The slave whose address corresponds to the transmitted address responds by pulling the SDA line low during the ninth clock pulse (this is termed the Acknowledge bit). At this stage, all other devices on the bus remain idle while the selected device waits for data to be written to or read from its serial register. If the R/W bit is high, the master will read from the slave device. However, if the  $R/\overline{W}$  bit is low, the master will write to the slave device.

- Data is transmitted over the serial bus in sequences of nine clock pulses (eight data bits followed by an acknowledge bit).

The transitions on the SDA line must occur during the low period of SCL and remain stable during the high period of SCL.

- 3. When all data bits have been read or written, a STOP condition is established by the master. A STOP condition is defined as a low-to-high transition on the SDA line while SCL is high. In Write mode, the master will pull the SDA line high during the 10th clock pulse to establish a STOP condition. In Read mode, the master will issue a No Acknowledge for the ninth clock pulse (i.e., the SDA line remains high). The master will then bring the SDA line low before the tenth clock pulse and then high during the tenth clock pulse to establish a STOP condition.

See Figures 18 to 21 below for a graphical explanation of the serial interface.

A repeated write function gives the user flexibility to update the matrix switch a number of times after addressing the part only once. During the write cycle, each data byte will update the configuration of the switches. For example, after the matrix switch has acknowledged its address byte, and receives one data byte, the switches will update after the data byte, if another data byte is written to the matrix switch while it is still the addressed slave device, this data byte will also cause an switch configuration update. Repeat read of the matrix switch is also allowed.

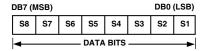

#### INPUT SHIFT REGISTER

The input shift register is eight bits wide. Figure 15 illustrates the contents of the input shift register. Data is loaded into the device as an 8-bit word under the control of a serial clock input, SCL. The timing diagram for this operation is shown in Figure 1. The 8-bit word consists of eight data bits each controlling one switch. MSB (Bit 7) is loaded first.

Figure 15. ADG728/ADG729 Input Shift Register Contents

REV. C \_9\_

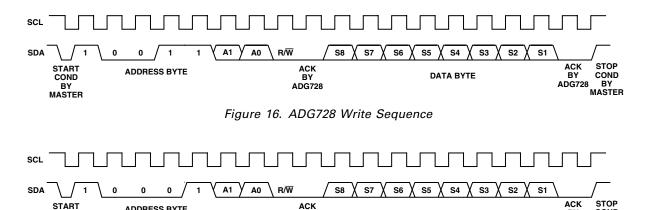

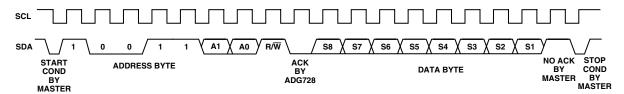

#### WRITE OPERATION

When writing to the ADG728/ADG729, the user must begin with an address byte and  $R/\overline{W}$  bit, after which the switch will acknowledge that it is prepared to receive data by pulling SDA low. This address byte is followed by the 8-bit word. The write operations for each matrix switch are shown in the figures below.

ADDRESS BYTE

Figure 17. ADG729 Write Sequence

DATA BYTE

BY ADG729

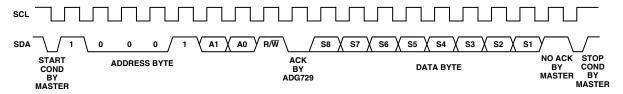

#### READ OPERATION

BY MASTER

When reading data back from the ADG728/ADG729, the user must begin with an address byte and  $R/\overline{W}$  bit, after which the matrix switch will acknowledge that it is prepared to transmit data by pulling SDA low. The readback operation is a single byte that consists of the eight data bits in the input register. The read operations for each part are shown in Figures 18 and 19.

Figure 18. ADG728 Readback Sequence

Figure 19. ADG729 Readback Sequence

REV. C -10-

COND

BY MASTER

BY

ADG729

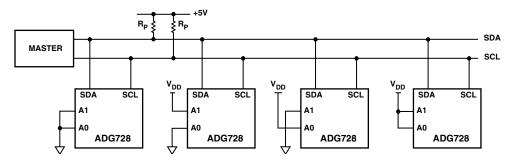

## MULTIPLE DEVICES ON ONE BUS

Figure 20 shows four ADG728s devices on the same serial bus. Each has a different slave address since the state of their A0 and A1 pins is different. This allows each Matrix Switch to be written to or read from independently. Because the ADG729 has a different address to the ADG728, it would be possible for four of each of these devices to be connected to the same bus.

Figure 20. Multiple ADG728s on the Same Bus

## **TEST CIRCUITS**

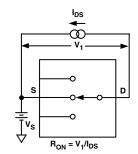

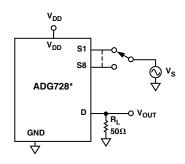

Test Circuit 1. On Resistance

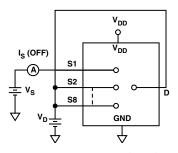

Test Circuit 2. I<sub>D</sub> (OFF)

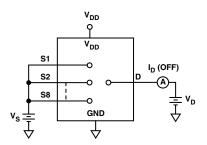

Test Circuit 3. I<sub>S</sub> (OFF)

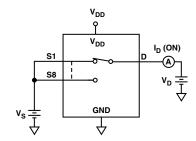

Test Circuit 4. I<sub>D</sub> (ON)

Test Circuit 5. Switching Times and Break-Before-Make Times

\* SIMILAR CONNECTION FOR ADG729

Test Circuit 6. Charge Injection

\* SIMILAR CONNECTION FOR ADG729

CHANNEL-TO-CHANNEL CROSSTALK =  $20LOG_{10}(V_{OUT}/V_S)$

Test Circuit 7. Channel-to-Channel Crosstalk

\*SIMILAR CONNECTION FOR ADG729 S1 IS SWITCHED OFF FOR OFF ISOLATION MEASUREMENTS AND ON FOR BANDWIDTH MEASUREMENTS OFF ISOLATION =  $20\text{LOG}_{10}(\text{V}_{\text{OUT}}/\text{V}_{\text{S}})$

$\label{eq:volt} \text{INSERTION LOSS} = 20 \text{LOG}_{10} \bigg( \frac{\text{V}_{\text{OUT}} \text{ WITH SWITCH}}{\text{V}_{\text{OUT}} \text{ WITHOUT SWITCH}} \bigg)$

Test Circuit 8. Off Isolation and Bandwidth

-12- REV. C

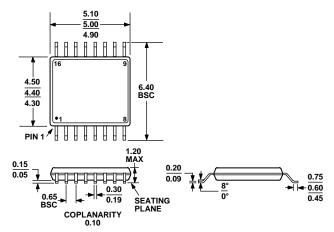

## **OUTLINE DIMENSIONS**

**COMPLIANT TO JEDEC STANDARDS MO-153-AB**

Figure 1. 16-Lead Thin Shrink Small Outline Package [TSSOP] (RU-16) Dimensions shown in millimeters

## **ORDERING GUIDE**

| Model <sup>1, 2</sup> | Temperature Range | Package Description                               | Package Option |

|-----------------------|-------------------|---------------------------------------------------|----------------|

| ADG728BRU             | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADG728BRU-REEL        | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADG728BRU-REEL7       | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADG728BRUZ            | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADG728BRUZ-REEL       | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADG728BRUZ-REEL7      | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADG728WBRUZ-REEL7     | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADG729BRU             | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADG729BRU-REEL        | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADG729BRU-REEL7       | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADG729BRUZ            | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADG729BRUZ-REEL7      | -40°C to +85°C    | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

## **AUTOMOTIVE PRODUCTS**

The ADG728W model is available with controlled manufacturing to support the quality and reliability requirements of automotive applications. Note that this automotive model may have specifications that differ from the commercial models; therefore, designers should review the Specifications section of this data sheet carefully. Only the automotive grade product shown is available for use in automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for this model.

### **REVISION HISTORY**

#### 10/11—Rev. A to Rev. B

| Change to Features Section                  | 1  |

|---------------------------------------------|----|

| Changes to Absolute Maximum Ratings Section | 6  |

| Updated Outline Dimensions                  | 13 |

| Changes to Ordering Guide                   | 13 |

| Added Automotive Products Section           | 13 |

©2012 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

D01002-0-6/12(C)

www.analog.com

<sup>&</sup>lt;sup>2</sup> W = Qualified for Automotive Applications.

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

ADG729BRUZ-REEL7 ADG729BRUZ