## 50 Hz to 6 GHz, 50 dB TruPwr™ Detector

Data Sheet AD8363

#### **FEATURES**

Accurate rms-to-dc conversion from 50 Hz to 6 GHz Single-ended input dynamic range of >50 dB No balun or external input tuning required Waveform and modulation independent RF power detection Linear-in-decibels output, scaled: 52 mV/dB

Log conformance error: <±0.15 dB Temperature stability: <±0.5 dB Voltage supply range: 4.5 V to 5.5 V

Operating temperature range: -40°C to +125°C

Power-down capability to 1.5 mW Small footprint, 4 mm × 4 mm, LFCSP

#### **APPLICATIONS**

Power amplifier linearization/control loops

Multi-Standard, Multi-Carrier Wireless Infrastructure

(MCGSM, CDMA, WCDMA, TD-SCDMA, WiMAX, LTE)

Transmitter power control

Transmitter signal strength indication (TSSI)

RF instrumentation

#### **GENERAL DESCRIPTION**

The AD8363 is a true rms responding power detector that can be directly driven with a single-ended 50  $\Omega$  source. This feature makes the AD8363 frequency versatile by eliminating the need for a balun or any other form of external input tuning for operation up to 6 GHz.

The AD8363 provides an accurate power measurement, independent of waveform, for a variety of high frequency communication and instrumentation systems. Requiring only a single supply of 5 V and a few capacitors, it is easy to use and provides high measurement accuracy. The AD8363 can operate from arbitrarily low frequencies to 6 GHz and can accept inputs that have rms values from less than –50 dBm to at least 0 dBm, with large crest factors exceeding the requirements for accurate measurement of WiMAX, CDMA, W-CDMA, TD-SCDMA, multicarrier GSM, and LTE signals.

The AD8363 can determine the true power of a high frequency signal having a complex low frequency modulation envelope, or it can be used as a simple low frequency rms voltmeter. The highpass corner generated by its internal offset-nulling loop can be lowered by a capacitor added on the CHPF pin.

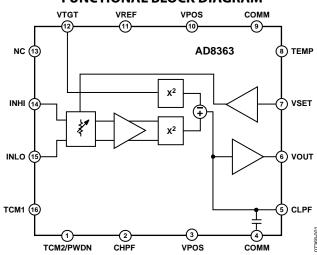

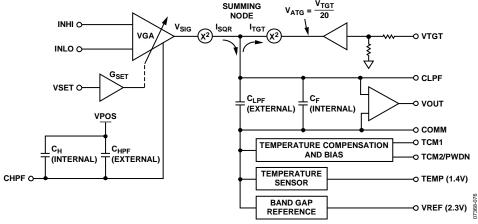

#### **FUNCTIONAL BLOCK DIAGRAM**

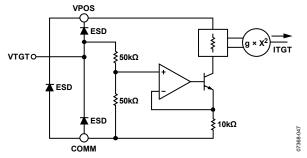

Figure 1. AD8363 Block Diagram

Used as a power measurement device, VOUT is connected to VSET. The output is then proportional to the logarithm of the rms value of the input. The reading is presented directly in decibels and is conveniently scaled to 52 mV/dB, or approximately 1 V per decade; however, other slopes are easily arranged. In controller mode, the voltage applied to VSET determines the power level required at the input to null the deviation from the setpoint. The output buffer can provide high load currents.

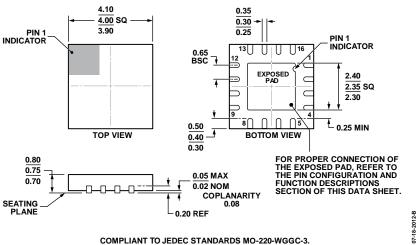

The AD8363 has 1.5 mW power consumption when powered down by a logic high applied to the TCM2/PWDN pin. It powers up within about 30  $\mu$ s to its nominal operating current of 60 mA at 25°C. The AD8363 is available in a 4 mm  $\times$  4 mm 16-lead LFCSP for operation over the -40°C to +125°C temperature range.

A fully populated RoHS compliant evaluation board is also available.

## **TABLE OF CONTENTS**

| Features                                               | 1  |

|--------------------------------------------------------|----|

| Applications                                           | 1  |

| Functional Block Diagram                               | 1  |

| General Description                                    | 1  |

| Revision History                                       | 2  |

| Specifications                                         | 3  |

| Absolute Maximum Ratings                               | 7  |

| ESD Caution                                            | 7  |

| Pin Configuration and Function Descriptions            | 8  |

| Typical Performance Characteristics                    | 9  |

| Theory of Operation                                    | 14 |

| Square Law Detector and Amplitude Target               |    |

| RF Input Interface                                     |    |

| Choice of RF Input Pin                                 |    |

| Small Signal Loop Response                             |    |

| Temperature Sensor Interface                           |    |

| VREF Interface                                         |    |

| Temperature Compensation Interface                     |    |

| Power-Down Interface                                   |    |

| Tower Bown meruee                                      | 17 |

| REVISION HISTORY                                       |    |

| 3/15—Rev. A to Rev. B                                  |    |

| Changes to Figure 2 and Table 3                        | 8  |

| Changes to Controller Mode Basic Connections Section   |    |

| Updated Outline Dimensions                             | 29 |

| Changes to the Ordering Guide                          | 29 |

| 7/11—Rev. 0 to Rev. A                                  |    |

| Changes to Features Section and Applications Section   | 1  |

| Added 3-Point Calibration to Table 1 for All MHz       |    |

| Replaced Typical Performance Characteristics Section;  |    |

| Renumbered Sequentially                                |    |

| Changes to Theory of Operation Section                 |    |

| Changes to Temperature Compensation Interface Section  |    |

| Changes to System Calibration and Error Calculation    |    |

| Section and Changes to Figure 44 and Figure 45         | 19 |

| Deleted Basis for Error Calculations Section           | 20 |

| Changes to Figure 46                                   | 20 |

| Deleted Selecting and Increasing Calibration Points to |    |

| Improve Accuracy over a Reduced Range Section          |    |

| Deleted Altering the Slope Section                     |    |

| Added Output Voltage Scaling Section                   | 23 |

|   | VSET Interface                                                                                  | . 17 |

|---|-------------------------------------------------------------------------------------------------|------|

|   | Output Interface                                                                                | . 17 |

|   | VTGT Interface                                                                                  | . 18 |

|   | Measurement Mode Basic Connections                                                              | . 18 |

|   | System Calibration and Error Calculation                                                        | . 19 |

|   | Operation to 125°C                                                                              | . 19 |

|   | Output Voltage Scaling                                                                          | . 20 |

|   | Offset Compensation, Minimum $C_{\text{LPF}}$ , and Maximum $C_{\text{HPF}}$ Capacitance Values |      |

|   | Choosing a Value for C <sub>LPF</sub>                                                           | . 21 |

|   | RF Pulse Response and VTGT                                                                      | . 23 |

|   | Controller Mode Basic Connections                                                               | . 23 |

|   | Constant Output Power Operation                                                                 | . 24 |

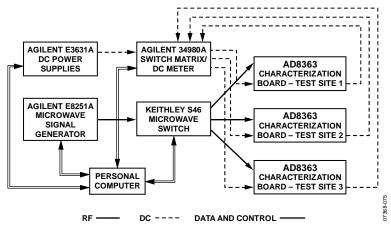

|   | Description of RF Characterization                                                              | . 25 |

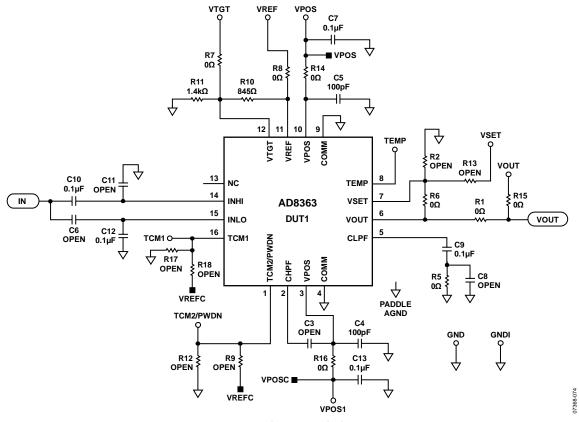

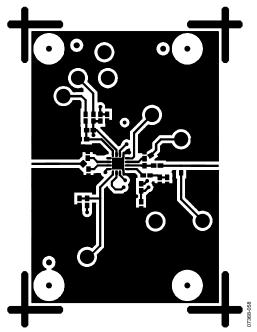

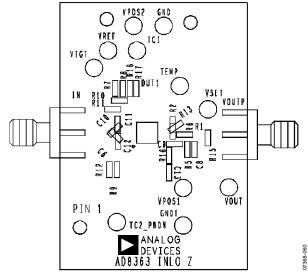

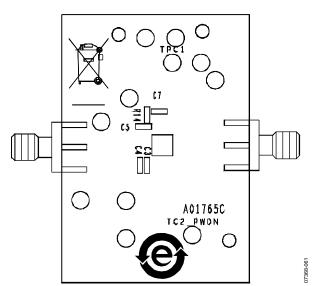

|   | Evaluation and Characterization Circuit Board Layouts                                           | . 26 |

|   | Assembly Drawings                                                                               | . 28 |

| С | Outline Dimensions                                                                              | . 29 |

|   | Ondoning Cuido                                                                                  | 20   |

## **SPECIFICATIONS**

$V_{POS} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ ,  $Z_O = 50 \Omega$ , single-ended input drive, VOUT connected to VSET,  $V_{TGT} = 1.4 \text{ V}$ ,  $C_{LPF} = 3.9 \text{ nF}$ ,  $C_{HPF} = 2.7 \text{ nF}$ , error referred to best-fit line (linear regression) from -20 dBm to -40 dBm, unless otherwise noted.

Table 1.

| Parameter                     | Conditions                                                                              | Min Typ   | Max | Unit  |

|-------------------------------|-----------------------------------------------------------------------------------------|-----------|-----|-------|

| OVERALL FUNCTION              |                                                                                         |           |     |       |

| Maximum Input Frequency       |                                                                                         |           | 6   | GHz   |

| RF INPUT INTERFACE            | INHI (Pin 14), INLO (Pin 15), ac-coupled                                                |           |     |       |

| Input Resistance              | Single-ended drive                                                                      | 50        |     | Ω     |

| Common-Mode DC Voltage        |                                                                                         | 2.6       |     | V     |

| 100 MHz                       | TCM1 (Pin 16) = 0.47 V, TCM2 (Pin 1) = 1.0 V, INHI input                                |           |     |       |

| Output Voltage: High Power In | $P_{IN} = -10 \text{ dBm}$                                                              | 2.47      |     | V     |

| Output Voltage: Low Power In  | $P_{IN} = -40 \text{ dBm}$                                                              | 0.92      |     | V     |

| ±1.0 dB Dynamic Range         | CW input, T <sub>A</sub> = 25°C                                                         |           |     |       |

|                               | 3-point calibration at 0 dBm, -10 dBm, and -40 dBm                                      | 64        |     | dB    |

|                               | Best-fit (linear regression) at -20 dBm and -40 dBm                                     | 65        |     | dB    |

| Maximum Input Level, ±1.0 dB  |                                                                                         | 9         |     | dBm   |

| Minimum Input Level, ±1.0 dB  |                                                                                         | -56       |     | dBm   |

| Deviation vs. Temperature     | Deviation from output at 25°C                                                           |           |     |       |

|                               | $-40^{\circ}$ C < T <sub>A</sub> < $+85^{\circ}$ C; P <sub>IN</sub> = $-10 \text{ dBm}$ | -0.2/+0.  | 3   | dB    |

|                               | $-40^{\circ}$ C < T <sub>A</sub> < +85°C; P <sub>IN</sub> = -40 dBm                     | -0.5/+0.  | 6   | dB    |

| Logarithmic Slope             |                                                                                         | 51.7      |     | mV/dB |

| Logarithmic Intercept         |                                                                                         | -58       |     | dBm   |

| Deviation from CW Response    | 13 dB peak-to-rms ratio (W-CDMA), over 40 dB dynamic range                              | <±0.1     |     | dB    |

|                               | 12 dB peak-to-rms ratio (WiMAX), over 40 dB dynamic range                               | <±0.1     |     | dB    |

|                               | 14.0 dB peak-to-rms ratio (16C CDMA2K), over 40 dB dynamic range                        | <±0.1     |     | dB    |

|                               | 256 QAM, CF = 8 dB, over 40 dB dynamic range                                            | <±0.1     |     | dB    |

| Input Impedance               | Single-ended drive                                                                      | 49 – j0.0 | 9   | Ω     |

| 900 MHz                       | TCM1 (Pin 16) = 0.5 V, TCM2 (Pin 1) = 1.2 V, INHI input                                 |           |     |       |

| Output Voltage: High Power In | $P_{IN} = -15 \text{ dBm}$                                                              | 2.2       |     | V     |

| Output Voltage: Low Power In  | $P_{IN} = -40 \text{ dBm}$                                                              | 0.91      |     | V     |

| ±1.0 dB Dynamic Range         | CW input, T <sub>A</sub> = 25°C                                                         |           |     |       |

|                               | 3-point calibration at 0 dBm, –10 dBm, and –40 dBm                                      | 60        |     | dB    |

|                               | Best-fit (linear regression) at -20 dBm and -40 dBm                                     | 54        |     | dB    |

| Maximum Input Level, ±1.0 dB  |                                                                                         | -2        |     | dBm   |

| Minimum Input Level, ±1.0 dB  |                                                                                         | -56       |     | dBm   |

| Deviation vs. Temperature     | Deviation from output at 25°C                                                           |           |     |       |

|                               | $-40^{\circ}$ C < $T_A$ < $+85^{\circ}$ C; $P_{IN}$ = $-15 \text{ dBm}$                 | +0.6/-0.  | 4   | dB    |

|                               | $-40^{\circ}$ C < T <sub>A</sub> < +85°C; P <sub>IN</sub> = -40 dBm                     | +0.8/-0.  | 6   | dB    |

| Logarithmic Slope             |                                                                                         | 51.8      |     | mV/dB |

| Logarithmic Intercept         |                                                                                         | -58       |     | dBm   |

| Deviation from CW Response    | 13 dB peak-to-rms ratio (W-CDMA), over 40 dB dynamic range                              | <±0.1     |     | dB    |

| •                             | 12 dB peak-to-rms ratio (WiMAX), over 40 dB dynamic range                               | <±0.1     |     | dB    |

|                               | 14.0 dB peak-to-rms ratio (16C CDMA2K), over 40 dB dynamic range                        | <±0.1     |     | dB    |

|                               | 256 QAM, CF = 8 dB, over 40 dB dynamic range                                            | <±0.1     |     | dB    |

| Input Impedance               | Single-ended drive                                                                      | 60 – j3.3 |     | Ω     |

| Parameter                     | Conditions                                                                                                                          | Min | Тур            | Max | Unit  |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|----------------|-----|-------|

| 1.9 GHz                       | TCM1 (Pin 16) = 0.52 V, TCM2 (Pin 1) = 0.51 V, INHI input                                                                           |     |                |     |       |

| Output Voltage: High Power In | $P_{IN} = -15 \text{ dBm}$                                                                                                          |     | 2.10           |     | V     |

| Output Voltage: Low Power In  | $P_{IN} = -40 \text{ dBm}$                                                                                                          |     | 0.8            |     | V     |

| ±1.0 dB Dynamic Range         | CW input, T <sub>A</sub> = 25°C                                                                                                     |     |                |     |       |

| •                             | 3-point calibration at 0 dBm, -10 dBm, and -40 dBm                                                                                  |     | 56             |     | dB    |

|                               | Best-fit (linear regression) at -20 dBm and -40 dBm                                                                                 |     | 48             |     | dB    |

| Maximum Input Level, ±1.0 dB  |                                                                                                                                     |     | -6             |     | dBm   |

| Minimum Input Level, ±1.0 dB  |                                                                                                                                     |     | -53            |     | dBm   |

| Deviation vs. Temperature     | Deviation from output at 25°C                                                                                                       |     |                |     |       |

|                               | $-40^{\circ}\text{C} < \text{T}_{A} < +85^{\circ}\text{C}; P_{IN} = -15 \text{ dBm}$                                                |     | +0.3/-0.5      |     | dB    |

|                               | $-40^{\circ}\text{C} < T_A < +85^{\circ}\text{C}; P_{IN} = -40 \text{ dBm}$                                                         |     | +0.4/-0.4      |     | dB    |

| Logarithmic Slope             |                                                                                                                                     |     | 52             |     | mV/d  |

| Logarithmic Intercept         |                                                                                                                                     |     | -55            |     | dBm   |

| Deviation from CW Response    | 13 dB peak-to-rms ratio (W-CDMA), over 37 dB dynamic range                                                                          |     | ±0.1           |     | dB    |

| Deviation from ew nesponse    | 12 dB peak-to-rms ratio (WiMAX), over 37 dB dynamic range                                                                           |     | ±0.1           |     | dB    |

|                               | 14.0 dB peak-to-rms ratio (16C CDMA2K), over 37 dB dynamic                                                                          |     | ±0.1           |     | dB    |

|                               | range                                                                                                                               |     | ±0.1           |     | ab    |

|                               | 256 QAM, CF = 8 dB, over 37 dB dynamic range                                                                                        |     | ±0.1           |     | dB    |

| Input Impedance               | Single-ended drive                                                                                                                  |     | 118 – j26      |     | Ω     |

| 2.14 GHz                      | TCM1 (Pin 16) = 0.52 V, TCM2 (Pin 1) = 0.6 V, INHI input                                                                            |     | 110 120        |     |       |

| Output Voltage: High Power In | $P_{IN} = -15 \text{ dBm}$                                                                                                          |     | 2.0            |     | V     |

| Output Voltage: Low Power In  | $P_{IN} = -40 \text{ dBm}$                                                                                                          |     | 0.71           |     | V     |

| ±1.0 dB Dynamic Range         | CW input, T <sub>A</sub> = 25°C                                                                                                     |     | 0.71           |     | •     |

| ± 1.0 db Dynamic Range        | 3-point calibration at 0 dBm, -10 dBm and -40 dBm                                                                                   |     | 55             |     | dB    |

|                               | Best-fit (linear regression) at –20 dBm and –40 dBm                                                                                 |     | 44             |     | dВ    |

| Maximum Input Lovel +1.0 dB   | best-fit (lifted) regression) at -20 dbiff and -40 dbiff                                                                            |     | <del>-</del> 8 |     | dBm   |

| Maximum Input Level, ±1.0 dB  |                                                                                                                                     |     |                |     | dBm   |

| Minimum Input Level, ±1.0 dB  | Deviation from output at 25%                                                                                                        |     | <b>-52</b>     |     | abm   |

| Deviation vs. Temperature     | Deviation from output at 25°C                                                                                                       |     | .01/.03        |     | -ID   |

|                               | $-40^{\circ}\text{C} < \text{T}_A < +85^{\circ}\text{C}; P_{\text{IN}} = -15 \text{ dBm}$                                           |     | +0.1/-0.2      |     | dB    |

|                               | $-40^{\circ}\text{C} < \text{T}_{A} < +85^{\circ}\text{C}; P_{IN} = -40 \text{ dBm}$                                                |     | +0.3/-0.5      |     | dB    |

| Logarithmic Slope             |                                                                                                                                     |     | 52.2           |     | mV/d  |

| Logarithmic Intercept         | 12   12   13   14   15   15   15   15   15   15   15                                                                                |     | -54            |     | dBm   |

| Deviation from CW Response    | 13 dB peak-to-rms ratio (W-CDMA), over 35 dB dynamic range                                                                          |     | ±0.1           |     | dB    |

|                               | 12 dB peak-to-rms ratio (WiMAX), over 35 dB dynamic range                                                                           |     | ±0.1           |     | dB    |

|                               | 14.0 dB peak-to-rms ratio (16C CDMA2K), over 35 dB dynamic range                                                                    |     | ±0.1           |     | dB    |

|                               | 256 QAM, CF = 8 dB, over 35 dB dynamic range                                                                                        |     | ±0.1           |     | dB    |

| Rise Time                     | Transition from no input to 1 dB settling at RF <sub>IN</sub> = $-10$ dBm,<br>$C_{LPF} = 390$ pF, $C_{HPF} = open$                  |     | 3              |     | μs    |

| Fall Time                     | Transition from –10 dBm to within 1 dB of final value (that is, no input level), C <sub>LPF</sub> = 390 pF, C <sub>HPF</sub> = open |     | 15             |     | μs    |

| Input Impedance               | Single-ended drive                                                                                                                  |     | 130 – j49      |     | Ω     |

| 2.6 GHz                       | TCM1 (Pin 16) = 0.54 V, TCM2 (Pin 1) = 1.1 V, INHI input                                                                            |     | ,              |     |       |

| Output Voltage: High Power In | $P_{IN} = -15 \text{ dBm}$                                                                                                          |     | 1.84           |     | V     |

| Output Voltage: Low Power In  | $P_{IN} = -40 \text{ dBm}$                                                                                                          |     | 0.50           |     | v     |

| ±1.0 dB Dynamic Range         | CW input, T <sub>A</sub> = 25°C                                                                                                     |     |                |     |       |

| = as synamic hange            | 3-point calibration at 0 dBm, –10 dBm and –40 dBm                                                                                   |     | 50             |     | dB    |

|                               | Best-fit (linear regression) at –20 dBm and –40 dBm                                                                                 |     | 41             |     | dB    |

| Maximum Input Level, ±1.0 dB  | best in filled regression, at -20 abili and -40 abili                                                                               |     | <del>-</del> 7 |     | dBm   |

|                               |                                                                                                                                     |     |                |     | dBm   |

| Minimum Input Level, ±1.0 dB  | Deviation from output at 25°C                                                                                                       |     | <b>-48</b>     |     | ubiii |

| Deviation vs. Temperature     | Deviation from output at 25°C                                                                                                       |     | .0.5/.03       |     | ۲۰    |

|                               | $-40^{\circ}$ C < $T_A$ < $+85^{\circ}$ C; $P_{IN} = -15 \text{ dBm}$                                                               |     | +0.5/-0.2      |     | dB    |

|                               | $-40$ °C < $T_A$ < $+85$ °C; $P_{IN} = -40 \text{ dBm}$                                                                             |     | +0.6/-0.2      |     | dB    |

| Parameter                         | Conditions                                                                              | Min | Тур       | Max    | Unit  |

|-----------------------------------|-----------------------------------------------------------------------------------------|-----|-----------|--------|-------|

| Logarithmic Slope                 |                                                                                         |     | 52.9      |        | mV/dB |

| Logarithmic Intercept             |                                                                                         |     | -49       |        | dBm   |

| <b>Deviation from CW Response</b> | 13 dB peak-to-rms ratio (W-CDMA), over 32 dB dynamic range                              |     | ±0.1      |        | dB    |

|                                   | 12 dB peak-to-rms ratio (WiMAX), over 32 dB dynamic range                               |     | ±0.1      |        | dB    |

|                                   | 14.0 dB peak-to-rms ratio (16C CDMA2K), over 32 dB dynamic range                        |     | ±0.1      |        | dB    |

|                                   | 256 QAM, CF = 8 dB, over 32 dB dynamic range                                            |     | ±0.1      |        | dB    |

| Input Impedance                   | Single-ended drive                                                                      |     | 95 – j65  |        | Ω     |

| 3.8 GHz                           | TCM1 (Pin 16) = 0.56 V, TCM2 (Pin 1) = 1.0 V, INLO input                                |     |           |        |       |

| Output Voltage: High Power In     | $P_{IN} = -20 \text{ dBm}$                                                              |     | 1.54      |        | V     |

| Output Voltage: Low Power In      | $P_{IN} = -40 \text{ dBm}$                                                              |     | 0.54      |        | V     |

| ±1.0 dB Dynamic Range             | CW input, T <sub>A</sub> = 25°C                                                         |     |           |        |       |

| ac c /                            | 3-point calibration at 0 dBm, –10 dBm and –40 dBm                                       |     | 50        |        | dB    |

|                                   | Best-fit (linear regression) at -20 dBm and -40 dBm                                     |     | 43        |        | dB    |

| Maximum Input Level, ±1.0 dB      | 5 cost in (iii.cos. regression, at 25 abin and 16 abin                                  |     | -5        |        | dBm   |

| Minimum Input Level, ±1.0 dB      |                                                                                         |     | -48       |        | dBm   |

| Deviation vs. Temperature         | Deviation from output at 25°C                                                           |     | 10        |        | abiii |

| Deviation vs. Temperature         | $-40^{\circ}\text{C} < T_A < +85^{\circ}\text{C}$ ; $P_{IN} = -20 \text{ dBm}$          |     | +0.1/-0.7 |        | dB    |

|                                   | $-40^{\circ}\text{C} < T_A < +85^{\circ}\text{C}; P_{IN} = -40 \text{ dBm}$             |     | +0.4/-0.5 |        | dB    |

| Logarithmic Slope                 | 10 C ( 1A ( 103 C, 1 IN = 10 dBIII                                                      |     | 50.0      |        | mV/dB |

| Logarithmic Intercept             |                                                                                         |     | -51       |        | dBm   |

| Deviation from CW Response        | 13 dB peak-to-rms ratio (W-CDMA), over 32 dB dynamic range                              |     | ±0.1      |        | dB    |

| Deviation from ew nesponse        | 12 dB peak-to-rms ratio (WiMAX), over 32 dB dynamic range                               |     | ±0.1      |        | dB    |

|                                   | 14.0 dB peak-to-rms ratio (16C CDMA2K), over 32 dB dynamic range                        |     | ±0.1      |        | dB    |

|                                   | 256 QAM, CF = 8 dB, over 32 dB dynamic range                                            |     | ±0.1      |        | dB    |

| Input Impedance                   | Single-ended drive                                                                      |     | 42 – j4.5 |        | Ω     |

| 5.8 GHz                           | TCM1 (Pin 16) = 0.88 V, TCM2 (Pin 1) = 1.0 V, INLO input                                |     | 12 ) 1.3  |        | 1     |

| Output Voltage: High Power In     | $P_{IN} = -20 \text{ dBm}$                                                              |     | 1.38      |        | V     |

| Output Voltage: Low Power In      | $P_{IN} = -40 \text{ dBm}$                                                              |     | 0.36      |        | V     |

| ±1.0 dB Dynamic Range             | CW input, T <sub>A</sub> = 25°C                                                         |     | 0.50      |        |       |

| ab b)aeage                        | 3-point calibration at 0 dBm, –10 dBm and –40 dBm                                       |     | 50        |        | dB    |

|                                   | Best-fit (linear regression) at –20 dBm and –40 dBm                                     |     | 45        |        | dB    |

| Maximum Input Level, ±1.0 dB      | best in (inited) regression, at 25 abin and 16 abin                                     |     | -3        |        | dBm   |

| Minimum Input Level, ±1.0 dB      |                                                                                         |     | -48       |        | dBm   |

| Deviation vs. Temperature         | Deviation from output at 25°C                                                           |     | 10        |        | abiii |

| 2 chance is in temperature        | $-40^{\circ}$ C < T <sub>A</sub> < $+85^{\circ}$ C; P <sub>IN</sub> = $-20 \text{ dBm}$ |     | +0.1/-0.6 |        | dB    |

|                                   | $-40^{\circ}\text{C} < \text{T}_{A} < +85^{\circ}\text{C}; P_{IN} = -40 \text{ dBm}$    |     | +0.3/-0.8 |        | dB    |

| Logarithmic Slope                 | 10 C 11/4 1 100 C/1 IIV                                                                 |     | 51.1      |        | mV/dB |

| Logarithmic Intercept             |                                                                                         |     | -47       |        | dBm   |

| Deviation from CW Response        | 13 dB peak-to-rms ratio (W-CDMA), over 32 dB dynamic range                              |     | ±0.1      |        | dB    |

| Deviation from ew nesponse        | 12 dB peak-to-rms ratio (WiMAX), over 32 dB dynamic range                               |     | ±0.1      |        | dB    |

|                                   | 14.0 dB peak-to-rms ratio (16C CDMA2K), over 32 dB dynamic range                        |     | ±0.1      |        | dB    |

|                                   | 256 QAM, CF = 8 dB, over 32 dB dynamic range                                            |     | ±0.1      |        | dB    |

| Input Impedance                   | Single-ended drive                                                                      |     | 28 + j1.6 |        | Ω     |

| OUTPUT INTERFACE                  | VOUT (Pin 6)                                                                            |     | ,         |        |       |

| Output Swing, Controller Mode     | Swing range minimum, $R_L \ge 500 \Omega$ to ground                                     |     | 0.03      |        | V     |

| - mare made                       | Swing range maximum, $R_L \ge 500 \Omega$ to ground                                     |     | 4.8       |        | v     |

| Current Source/Sink Capability    | Output held at V <sub>POS</sub> /2                                                      |     |           | 10/10  | mA    |

| Voltage Regulation                | I <sub>LOAD</sub> = 8 mA, source/sink                                                   |     | -0.2/+0.1 | 10, 10 | %     |

| Rise Time                         | Transition from no input to 1 dB settling at $RF_{IN} = -10$ dBm,                       | 1   | 3         |        | μs    |

|                                   | $C_{LPF} = 390 \text{ pF, } C_{HPF} = \text{open}$                                      |     |           |        | F-3   |

| Parameter                               | Conditions                                                                                                              | Min | Тур            | Max    | Unit     |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|----------------|--------|----------|

| Fall Time                               | Transition from $-10$ dBm to within 1 dB of final value (that is, no input level), $C_{LPF} = 390$ pF, $C_{HPF} = open$ |     | 15             |        | μs       |

| Noise Spectral Density                  | Measured at 100 kHz                                                                                                     |     | 45             |        | nV/√H    |

| SETPOINT INPUT                          | VSET (Pin 7)                                                                                                            |     |                |        |          |

| Voltage Range                           | Log conformance error ≤ 1 dB, minimum 2.14 GHz                                                                          |     | 2.0            |        | V        |

|                                         | Log conformance error ≤ 1 dB, maximum 2.14 GHz                                                                          |     | 0.7            |        | V        |

| Input Resistance                        |                                                                                                                         |     | 72             |        | kΩ       |

| Logarithmic Scale Factor                | $f = 2.14 \text{ GHz}, -40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$                                           |     | 19.2           |        | dB/V     |

| Logarithmic Intercept                   | $f = 2.14 \text{ GHz}$ , $-40^{\circ}\text{C} \le T_A \le +85^{\circ}\text{C}$ , referred to $50 \Omega$                |     | -54            |        | dBm      |

| TEMPERATURE COMPENSATION                | TCM1 (Pin 16), TCM2 (Pin 1)                                                                                             |     |                |        |          |

| Input Voltage Range                     |                                                                                                                         | 0   |                | 2.5    | V        |

| Input Bias Current, TCM1                | $V_{TCM1} = 0 V$                                                                                                        |     | -140           |        | μΑ       |

| ,                                       | $V_{TCM1} = 0.5 \text{ V}$                                                                                              |     | 80             |        | μΑ       |

| Input Resistance, TCM1                  | $V_{TCM1} > 0.7 \text{ V}$                                                                                              |     | 5              |        | kΩ       |

| Input Current, TCM2                     | $V_{TCM2} = 5 V$                                                                                                        |     | 2              |        | μΑ       |

|                                         | $V_{TCM2} = 4.5 \text{ V}$                                                                                              |     | 750            |        | μΑ       |

|                                         | $V_{TCM2} = 1 V$                                                                                                        |     | -2             |        | μΑ       |

|                                         | $V_{TCM2} = 0 V$                                                                                                        |     | _3             |        | μΑ       |

| Input Resistance, TCM2                  | $0.7 \text{ V} \leq \text{V}_{\text{TCM2}} \leq 4.0 \text{ V}$                                                          |     | 500            |        | kΩ       |

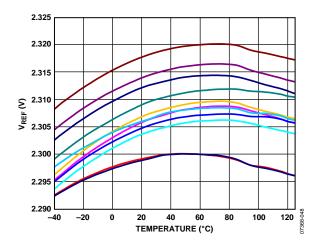

| VOLTAGE REFERENCE                       | VREF (Pin 11)                                                                                                           |     | 300            |        | 102      |

| Output Voltage                          | RF <sub>IN</sub> = -55 dBm                                                                                              |     | 2.3            |        | V        |

| Temperature Sensitivity                 | $25^{\circ}\text{C} \leq T_{A} \leq 70^{\circ}\text{C}$                                                                 |     | 0.04           |        | mV/°C    |

| remperature sensitivity                 | $70^{\circ}\text{C} \leq T_{A} \leq 125^{\circ}\text{C}$                                                                |     | -0.06          |        | mV/°C    |

|                                         | $-40^{\circ}\text{C} \le T_{A} \le +25^{\circ}\text{C}$ $-60^{\circ}\text{C} \le T_{A} \le +25^{\circ}\text{C}$         |     | -0.00<br>-0.18 |        | mV/°C    |

| Current Source/Sink Capability          | $25^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$                                                                  |     | -0.16          | 4/0.05 | mA       |

| Current Source/Sink Capability          | $-40^{\circ}\text{C} \leq \text{T}_{A} \leq +25^{\circ}\text{C}$                                                        |     |                | 3/0.05 | mA       |

| Voltage Regulation                      | $T_A = 25^{\circ}\text{C}$ , $I_{LOAD} = 3 \text{ mA}$                                                                  |     | -0.6           | 3/0.03 | %        |

| TEMPERATURE REFERENCE                   | TEMP (Pin 8)                                                                                                            | 1   | -0.0           |        | 70       |

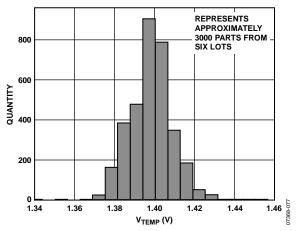

| Output Voltage                          | $T_A = 25^{\circ}\text{C}, R_L \ge 10 \text{ k}\Omega$                                                                  |     | 1.4            |        | V        |

| Temperature Coefficient                 | $-40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}, R_{L} \ge 10 \text{ k}\Omega$                                  |     | 5              |        | mV/°C    |

| Current Source/Sink Capability          | $25^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$                                                                  |     | ,              | 4/0.05 | mA       |

| Current Source/Sink Capability          | $-40^{\circ}\text{C} \leq \text{T}_{A} \leq +25^{\circ}\text{C}$                                                        |     |                | 3/0.05 | mA       |

| Voltage Regulation                      | $T_A = 25^{\circ}C$ , $I_{LOAD} = 3$ mA                                                                                 |     | -0.1           | 3/0.03 | %        |

| RMS TARGET INTERFACE                    | VTGT (Pin 12)                                                                                                           | -   | -0.1           |        | 70       |

| Input Voltage Range                     | VIGI (FIII 12)                                                                                                          | 1.4 |                | 2.5    | V        |

| Input Bias Current                      | V <sub>TGT</sub> = 1.4 V                                                                                                | 1.4 | 14             | 2.3    |          |

| Input Bias Current Input Resistance     | VTGT = 1.4 V                                                                                                            |     | 14             |        | μA<br>kΩ |

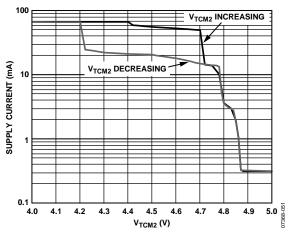

| POWER-DOWN INTERFACE                    | TCM2 (Pin1)                                                                                                             | -   | 100            |        | KLZ      |

|                                         |                                                                                                                         |     | 4.2            |        | V        |

| Logic Level to Enable                   | VPWDN decreasing                                                                                                        |     | 4.2<br>4.7     |        | V        |

| Logic Level to Disable<br>Input Current | VPWDN increasing $V_{TCM2} = 5 V$                                                                                       |     | 4.7<br>2       |        |          |

| input Current                           |                                                                                                                         |     |                |        | μΑ       |

|                                         | $V_{TCM2} = 4.5 \text{ V}$ $V_{TCM2} = 1 \text{ V}$                                                                     |     | 750            |        | μΑ       |

|                                         | 1                                                                                                                       |     | <b>-2</b>      |        | μΑ       |

| For a laboration a                      | $V_{\text{TCM2}} = 0 \text{ V}$                                                                                         |     | -3<br>25       |        | μΑ       |

| Enable Time                             | TCM2 low to $V_{OUT}$ at 1 dB of final value, $C_{LPF} = 470$ pF, $C_{HPF} = 220$ pF, $RF_{IN} = 0$ dBm                 |     | 35             |        | μs       |

| Disable Time                            | TCM2 high to $V_{OUT}$ at 1 dB of final value, $C_{LPF} = 470$ pF, $C_{HPF} = 220$ pF, $RF_{IN} = 0$ dBm                |     | 25             |        | μs       |

| POWER SUPPLY INTERFACE                  | VPOS (Pin 3, Pin 10)                                                                                                    |     |                |        |          |

| Supply Voltage                          |                                                                                                                         | 4.5 | 5              | 5.5    | V        |

| Quiescent Current                       | $T_A = 25$ °C, $RF_{IN} = -55 \text{ dBm}$                                                                              |     | 60             |        | mA       |

|                                         | T <sub>A</sub> = 85°C                                                                                                   |     | 72             |        | mA       |

| Power-Down Current                      | $V_{TCM2} > V_{POS} - 0.3 V$                                                                                            | Ī   | 300            |        | μΑ       |

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

|                                      | D 41            |

|--------------------------------------|-----------------|

| Parameter                            | Rating          |

| Supply Voltage, VPOS                 | 5.5 V           |

| Input Average RF Power <sup>1</sup>  | 21 dBm          |

| Equivalent Voltage, Sine Wave Input  | 2.51 V rms      |

| Internal Power Dissipation           | 450 mW          |

| $\theta_{JC}^2$                      | 10.6°C/W        |

| $\Theta_{JB}^2$                      | 35.3°C/W        |

| $\theta_{JA}^2$                      | 57.2°C/W        |

| $\Psi_{JT}^2$                        | 1.0°C/W         |

| $\Psi_{JB}{}^{2}$                    | 34°C/W          |

| Maximum Junction Temperature         | 150°C           |

| Operating Temperature Range          | −40°C to +125°C |

| Storage Temperature Range            | −65°C to +150°C |

| Lead Temperature (Soldering, 60 sec) | 300°C           |

<sup>&</sup>lt;sup>1</sup> This is for long durations. Excursions above this level, with durations much less than 1 second, are possible without damage.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> No airflow with the exposed pad soldered to a 4-layer JEDEC board.

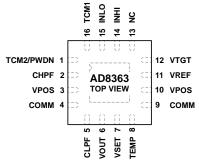

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

- NOTES

1. NC = NO CONNECT. DO NOT CONNECT TO THIS PIN.

2. THE EXPOSED PAD IS THE SYSTEM COMMON CONNECTION AND IT MUST HAVE BOTH A GOOD THERMAL AND GOOD ELECTRICAL CONNECTION TO GROUND.

Figure 2. Pin Configuration

**Table 3. Pin Function Descriptions**

| Pin<br>No. | Mnemonic Description                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                          |                   |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 1          | TCM2/PWDN                                                                                                                                                                                                                                                              | This is a dual function pin used for controlling the amount of nonlinear intercept temperature compensation at voltages <2.5 V and/or for shutting down the device at voltages >4 V. If the shutdown function is not used, this pin can be connected to the VREF pin through a voltage divider.          | See Figure 39     |

| 2          | CHPF                                                                                                                                                                                                                                                                   | Connect this pin to VPOS via a capacitor to determine the -3 dB point of the input signal high-pass filter. Only add a capacitor when operating at frequencies below 10 MHz.                                                                                                                             | See Figure 48     |

| 3, 10      | VPOS                                                                                                                                                                                                                                                                   | Supply for the Device. Connect these pins to a 5 V power supply. Pin 3 and Pin 10 are not internally connected; therefore, both must connect to the source.                                                                                                                                              | Not<br>applicable |

| 4, 9       | COMM                                                                                                                                                                                                                                                                   | System Common Connection. Connect these pins via low impedance to system common.                                                                                                                                                                                                                         | Not<br>applicable |

| 5          | CLPF Connection for Loop Filter Integration (Averaging) Capacitor. Connect a ground-referenced capacitor to this pin. A resistor can be connected in series with this capacitor to improve loop stability and response time. Minimum C <sub>LPF</sub> value is 390 pF. |                                                                                                                                                                                                                                                                                                          | See Figure 41     |

| 6          | VOUT                                                                                                                                                                                                                                                                   | Output Pin in Measurement Mode (Error Amplifier Output). In measurement mode, this pin is connected to VSET. This pin can be used to drive a gain control when the device is used in controller mode.                                                                                                    |                   |

| 7          | VSET                                                                                                                                                                                                                                                                   | The voltage applied to this pin sets the decibel value of the required RF input voltage that results in zero current flow in the loop integrating capacitor pin, CLPF. This pin controls the variable gain amplifier (VGA) gain such that a 50 mV change in VSET reduces the gain by approximately 1 dB. | See Figure 40     |

| 8          | TEMP                                                                                                                                                                                                                                                                   | Temperature Sensor Output.                                                                                                                                                                                                                                                                               | See Figure 35     |

| 11         | VREF                                                                                                                                                                                                                                                                   | General-Purpose Reference Voltage Output of 2.3 V.                                                                                                                                                                                                                                                       | See Figure 36     |

| 12         | VTGT                                                                                                                                                                                                                                                                   | The voltage applied to this pin determines the target power at the input of the RF squaring circuit. The intercept voltage is proportional to the voltage applied to this pin. The use of a lower target voltage increases the crest factor capacity; however, this may affect the system loop response. | See Figure 42     |

| 13         | NC                                                                                                                                                                                                                                                                     | No Connect.                                                                                                                                                                                                                                                                                              | Not<br>applicable |

| 14         | INHI                                                                                                                                                                                                                                                                   | This is the RF input pin for frequencies up to and including 2.6 GHz. The RF input signal is normally ac-coupled to this pin through a coupling capacitor.                                                                                                                                               |                   |

| 15         | INLO                                                                                                                                                                                                                                                                   | This is the RF input pin for frequencies above 2.6 GHz. The RF input signal is normally ac-coupled to this pin through a coupling capacitor.                                                                                                                                                             |                   |

| 16         | TCM1                                                                                                                                                                                                                                                                   | This pin is used to adjust the intercept temperature compensation. Connect this pin to VREF through a voltage divider or to an external dc source.                                                                                                                                                       | See Figure 38     |

|            | EPAD                                                                                                                                                                                                                                                                   | Exposed Pad. The exposed pad is the system common connection and it must have both a good thermal and good electrical connection to ground.                                                                                                                                                              | Not<br>applicable |

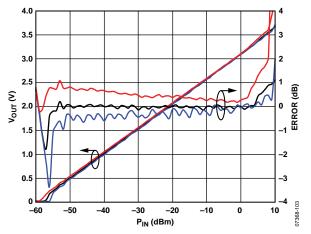

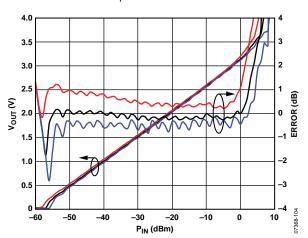

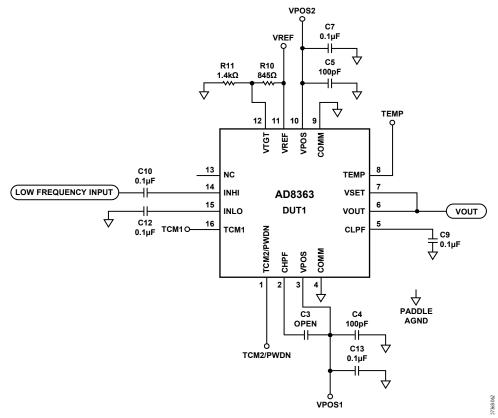

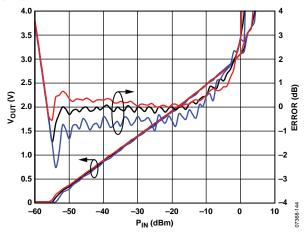

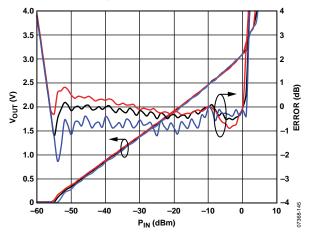

### TYPICAL PERFORMANCE CHARACTERISTICS

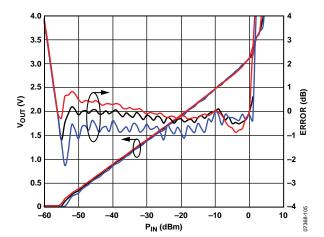

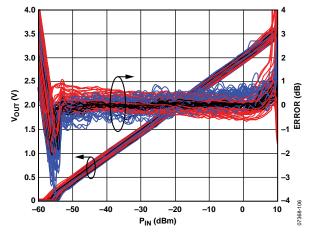

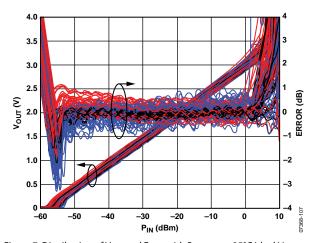

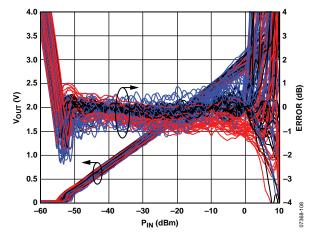

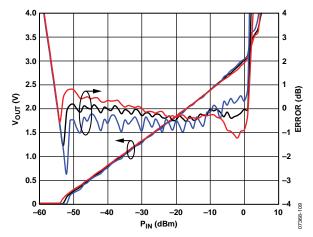

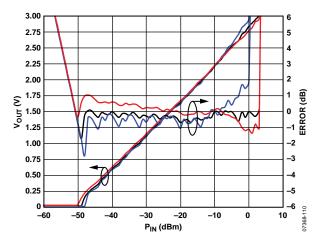

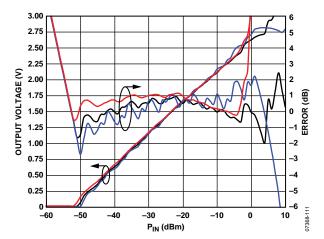

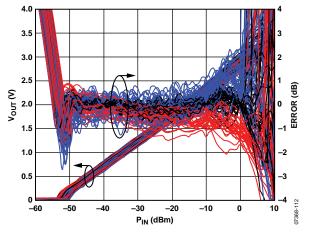

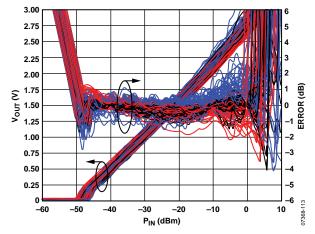

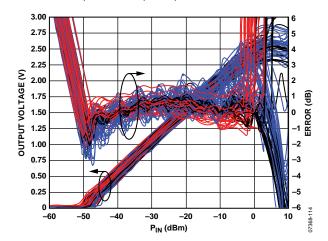

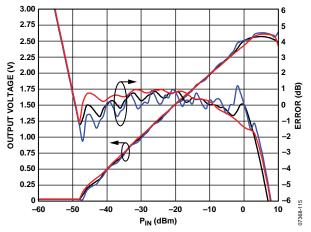

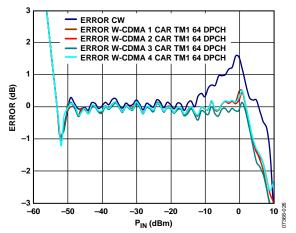

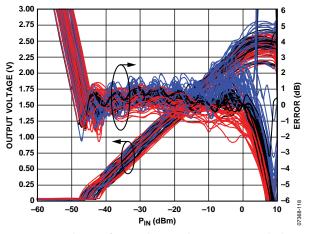

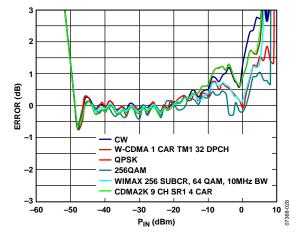

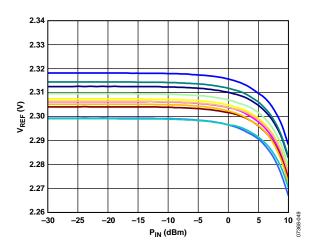

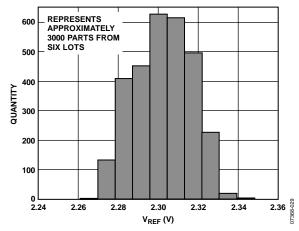

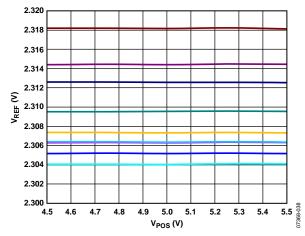

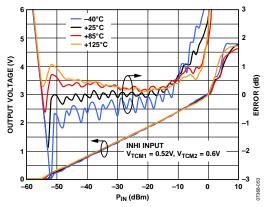

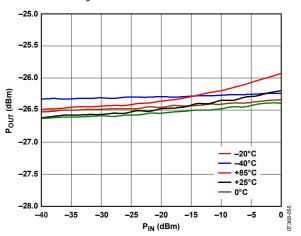

$V_{POS} = 5$  V,  $Z_O = 50$   $\Omega$ , single-ended input drive, VOUT connected to VSET,  $V_{TGT} = 1.4$  V,  $C_{LPF} = 3.9$  nF,  $C_{HPF} = 2.7$  nF,  $T_A = +25$ °C (black), -40°C (blue), +85°C (red), where appropriate. Error calculated using 3-point calibration at 0 dBm, -10 dBm, and -40 dBm, unless otherwise indicated. Input RF signal is a sine wave (CW), unless otherwise indicated.

Figure 3. V<sub>ΟUT</sub> and Log Conformance vs. Input Power and Temperature at 100 MHz

Figure 4.  $V_{OUT}$  and Log Conformance Error with Respect to 25°C Ideal Line over Temperature vs. Input Amplitude at 900 MHz, CW, Typical Device

Figure 5.  $V_{OUT}$  and Log Conformance Error with Respect to 25°C Ideal Line over Temperature vs. Input Amplitude at 1.90 GHz, CW, Typical Device

Figure 6. Distribution of Vou⊤ and Error with Respect to 25°C Ideal Line over Temperature vs. Input Amplitude at 100 MHz, CW

Figure 7. Distribution of  $V_{\text{OUT}}$  and Error with Respect to 25°C Ideal Line over Temperature vs. Input Amplitude at 900 MHz, CW

Figure 8. Distribution of V<sub>OUT</sub> and Error with Respect to 25 ℃ Ideal Line over Temperature vs. Input Amplitude at 1.90 GHz, CW

Figure 9.  $V_{OUT}$  and Log Conformance Error with Respect to 25°C Ideal Line over Temperature vs. Input Amplitude at 2.14 GHz, CW, Typical Device

Figure 10. V<sub>ΟυΤ</sub> and Log Conformance Error with Respect to 25°C Ideal Line over Temperature vs. Input Amplitude at 2.6 GHz, CW, Typical Device

Figure 11. V<sub>OUT</sub> and Log Conformance Error with Respect to 25°C Ideal Line over Temperature vs. Input Amplitude at 3.8 GHz, CW, Typical Device

Figure 12. Distribution of  $V_{OUT}$  and Error with Respect to 25°C Ideal Line over Temperature vs. Input Amplitude at 2.14 GHz, CW

Figure 13. Distribution of  $V_{OUT}$  and Error with Respect to 25°C Ideal Line over Temperature vs. Input Amplitude at 2.6 GHz, CW

Figure 14. Distribution of  $V_{OUT}$  and Error with Respect to 25°C Ideal Line over Temperature vs. Input Amplitude at 3.8 GHz, CW

Figure 15.  $V_{\rm OUT}$  and Log Conformance Error with Respect to 25°C Ideal Line over Temperature vs. Input Amplitude at 5.8 GHz, Typical Device

Figure 16. Error from CW Linear Reference vs. Input Amplitude with Modulation, Frequency at 2.14 GHz,  $C_{LPF} = 0.1 \mu F$ , INHI Input

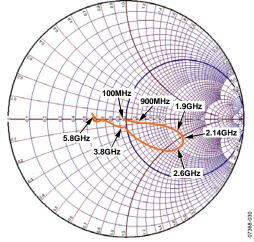

Figure 17. Single-Ended Input Impedance (S11) vs. Frequency;  $Z_0 = 50 \Omega$ , INHI or INLO

Figure 18. Distribution of  $V_{OUT}$  and Error with Respect to 25°C Ideal Line over Temperature vs. Input Amplitude at 5.8 GHz, CW

Figure 19. Error from CW Linear Reference vs. Input Amplitude with Modulation, Frequency at 2.6 GHz, C<sub>LPF</sub> = 0.1 μF, INHI Input

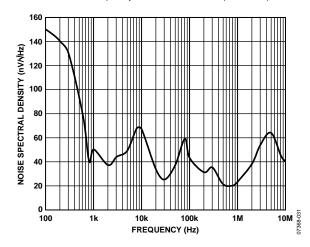

Figure 20. Typical Noise Spectral Density of Vout; All CLPF Values

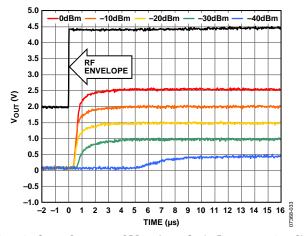

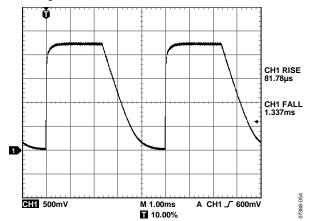

Figure 21. Output Response to RF Burst Input, Carrier Frequency at 2.14 GHz,  $C_{LPF} = 390 \text{ pF}$ ,  $C_{HPF} = Open$ , Rising Edge

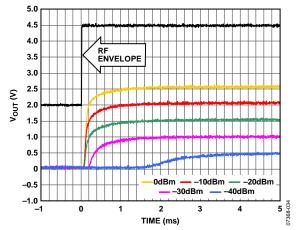

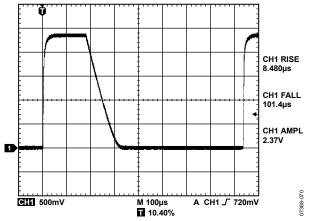

Figure 22. Output Response to RF Burst Input, Carrier Frequency at 2.14 GHz,  $C_{LPF} = 0.1 \ \mu F$ ,  $C_{HPF} = Open$ , Rising Edge

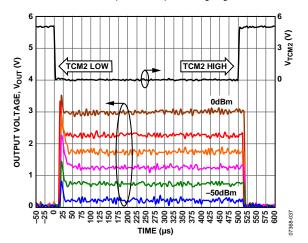

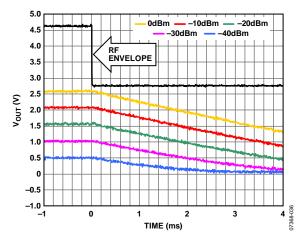

Figure 23. Output Response Using Power-Down Mode for Various RF Input Levels Carrier Frequency at 2.14 GHz,  $C_{LPF} = 470$  pF,  $C_{HPF} = 220$  pF

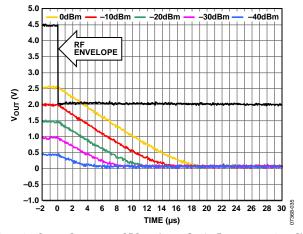

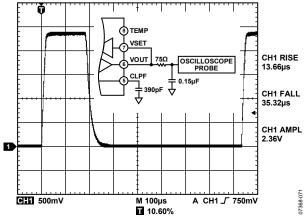

Figure 24. Output Response to RF Burst Input, Carrier Frequency at 2.14 GHz,  $C_{LPF} = 390$  pF,  $C_{HPF} = Open$ , Falling Edge

Figure 25. Output Response to RF Burst Input, Carrier Frequency at 2.14 GHz,  $C_{LPF}=0.1~\mu F, C_{HPF}=Open, Falling Edge$

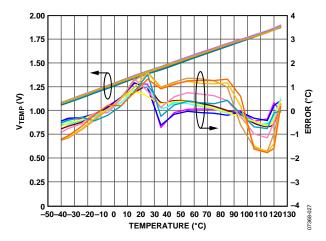

Figure 26. V<sub>TEMP</sub> and Error with Respect to Straight Line vs. Temperature for Eleven Devices

Figure 27. Distribution of V<sub>TEMP</sub> Voltage at 25°C, No RF Input

Figure 28. Supply Current vs. V<sub>TCM2</sub>

Figure 29. Change in V<sub>REF</sub> with Input Amplitude for Eleven Devices

Figure 30. Distribution of V<sub>REF</sub>, 25°C, No RF Input

Figure 31. Change in V<sub>REF</sub> with V<sub>POS</sub> for Nine Devices

Figure 32. Change in  $V_{\textit{REF}}$  with Temperature for Eleven Devices

### THEORY OF OPERATION

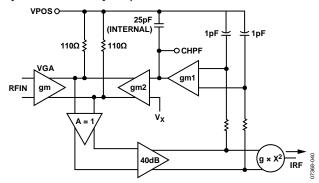

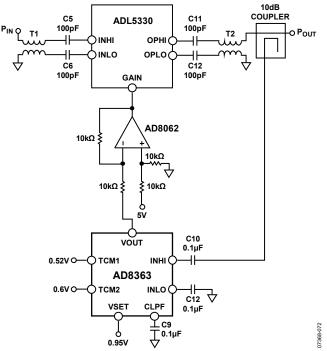

The computational core of the AD8363 is a high performance AGC loop. As shown in Figure 33, the AGC loop comprises a wide bandwidth variable gain amplifier (VGA), square law detectors, an amplitude target circuit, and an output driver. For a more detailed description of the functional blocks, see the AD8362 data sheet.

The nomenclature used in this data sheet to distinguish between a pin name and the signal on that pin is as follows:

- The pin name is all uppercase (for example, VPOS, COMM, and VOUT).

- The signal name or a value associated with that pin is the pin mnemonic with a partial subscript (for example, C<sub>LPF</sub>, C<sub>HPF</sub>, and V<sub>OUT</sub>).

#### **SQUARE LAW DETECTOR AND AMPLITUDE TARGET**

The VGA gain has the form

$$G_{SET} = G_O \exp(-V_{SET}/V_{GNS}) \tag{1}$$

where:

*G*<sup>0</sup> is the basic fixed gain.

$V_{\text{GNS}}$  is a scaling voltage that defines the gain slope (the decibel change per voltage). The gain decreases with increasing  $V_{\text{SET}}$ .

The VGA output is

$$V_{SIG} = G_{SET} \times RF_{IN} = G_O \times RF_{IN} \exp(V_{SET}/V_{GNS})$$

(2)

where  $RF_{IN}$  is the ac voltage applied to the input terminals of the AD8363.

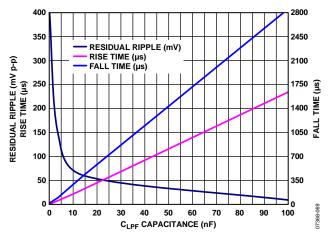

The output of the VGA,  $V_{SIG}$ , is applied to a wideband square law detector. The detector provides the true rms response of the RF input signal, independent of waveform. The detector output,  $I_{SQR}$ , is a fluctuating current with positive mean value. The difference between  $I_{SQR}$  and an internally generated current,  $I_{TGT}$ , is integrated by  $C_F$  and the external capacitor attached to the CLPF pin at the summing node.  $C_F$  is an on-chip 25 pF filter capacitor, and  $C_{LPF}$ , the external capacitance connected to the CLPF pin, can be used to arbitrarily increase the averaging time while trading off with the response time. When the AGC loop is at equilibrium

$$Mean(I_{SQR}) = I_{TGT} \tag{3}$$

This equilibrium occurs only when

$$Mean(V_{SIG}^2) = V_{TGT}^2 \tag{4}$$

where  $V_{TGT}$  is the voltage presented at the VTGT pin. This pin can conveniently be connected to the VREF pin through a voltage divider to establish a target rms voltage  $V_{ATG}$  of ~70 mV rms, when  $V_{TGT} = 1.4$  V.

Because the square law detectors are electrically identical and well matched, process and temperature dependent variations are effectively cancelled.

Figure 33. Simplified Architecture Details

By forcing the previous identity through varying the VGA setpoint, it is apparent that

$$RMS(V_{SIG}) = \sqrt{(Mean(V_{SIG}^2))} = \sqrt{(V_{ATG}^2)} = V_{ATG}$$

(5)

Substituting the value of V<sub>SIG</sub> from Equation 2 results in

$$RMS(G_0 \times RF_{IN} \exp(-V_{SET}/V_{GNS})) = V_{ATG}$$

(6)

When connected as a measurement device,  $V_{SET} = V_{OUT}$ . Solving for  $V_{OUT}$  as a function of  $RF_{IN}$

$$V_{OUT} = V_{SLOPE} \times \log_{10}(RMS(RF_{IN})/V_Z)$$

(7)

where:

V<sub>SLOPE</sub> is 1 V/decade (or 50 mV/dB).

$V_Z$  is the intercept voltage.

When RMS(RF<sub>IN</sub>) =  $V_z$ , because  $log_{10}(1) = 0$ , this implies that  $V_{OUT} = 0$  V, making the intercept the input that forces  $V_{OUT} = 0$  V.  $V_z$  has been fixed to approximately 280  $\mu$ V (approximately –58 dBm, referred to 50  $\Omega$ ) with a CW signal at 100 MHz. In reality, the AD8363 does not respond to signals less than  $\sim$ -56 dBm. This means that the intercept is an extrapolated value outside the operating range of the device.

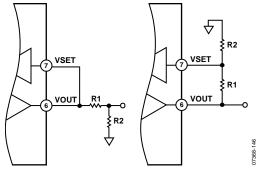

If desired, the effective value of V<sub>SLOPE</sub> can be altered by using a resistor divider between VOUT and VSET. (Refer to the Output Voltage Scaling section for more information.)

In most applications, the AGC loop is closed through the setpoint interface and the VSET pin. In measurement mode, VOUT is directly connected to VSET. (See the Measurement Mode Basic Connections section for more information.) In controller mode, a control voltage is applied to VSET and the VOUT pin typically drives the control input of an amplification or attenuation system. In this case, the voltage at the VSET pin forces a signal amplitude at the RF inputs of the AD8363 that balances the system through feedback. (See the Controller Mode Basic Connections section for more information.)

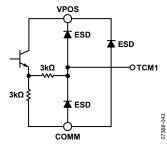

#### RF INPUT INTERFACE

Figure 34 shows the connections of the RF inputs within the AD8363. The input impedance is set primarily by an internal 50  $\Omega$  resistor connected between INHI and INLO. A dc level of approximately half the supply voltage on each pin is established internally. Either the INHI pin or the INLO pin can be used as the single-ended RF input pin. (See the Choice of RF Input Pin section.) If the dc levels at these pins are disturbed, performance is compromised; therefore, signal coupling capacitors must be connected from the input signal to INHI and INLO. The input signal high-pass corner formed by the coupling capacitors and the internal resistances is

$$f_{HIGH-PASS} = 1/(2 \times \pi \times 50 \times C) \tag{8}$$

where C is in farads and  $f_{\text{HIGH-PASS}}$  is in hertz. The input coupling capacitors must be large enough in value to pass the input signal frequency of interest. The other input pin should be RF ac-coupled to common (ground).

Figure 34. RF Inputs Simplified Schematic

Extensive ESD protection is employed on the RF inputs, which limits the maximum possible input amplitude to the AD8363.

#### **CHOICE OF RF INPUT PIN**

The dynamic range of the AD8363 can be optimized by choosing the correct RF input pin for the intended frequency of operation. Using INHI (Pin 14), users can obtain the best dynamic range at frequencies up to 2.6 GHz. Above 2.6 GHz, it is recommended that INLO (Pin 15) be used. At 2.6 GHz, the performance obtained at the two inputs is approximately equal.

The AD8363 was designed with a single-ended RF drive in mind. A balun can be used to drive INHI and INLO differentially, but it is not necessary, and it does not result in improved dynamic range.

#### **SMALL SIGNAL LOOP RESPONSE**

The AD8363 uses a VGA in a loop to force a squared RF signal to be equal to a squared dc voltage. This nonlinear loop can be simplified and solved for a small signal loop response. The low-pass corner pole is given by

$$Freq_{LP} \approx 1.83 \times I_{TGT}/(C_{LPF})$$

(9)

where:

$I_{TGT}$  is in amperes.

$C_{LPF}$  is in farads.

*FreqLP* is in hertz.

$I_{TGT}$  is derived from  $V_{TGT};$  however,  $I_{TGT}$  is a squared value of  $V_{TGT}$  multiplied by a transresistance, namely

$$I_{TGT} = g_m \times V_{TGT}^2 \tag{10}$$

$g_{m}$  is approximately 18.9  $\mu s,$  so with  $V_{TGT}$  equal to the typically recommended 1.4 V,  $I_{TGT}$  is approximately 37  $\mu A.$  The value of this current varies with temperature; therefore, the small signal pole varies with temperature. However, because the RF squaring circuit and dc squaring circuit track with temperature, there is no temperature variation contribution to the absolute value of  $V_{OUT}$ .

For CW signals,

$$Freq_{LP} \approx 67.7 \times 10^{-6} / (C_{LPF}) \tag{11}$$

However, signals with large crest factors include low pseudorandom frequency content that either needs to be filtered out or sampled and averaged out. See the Choosing a Value for CLPF section for more information.

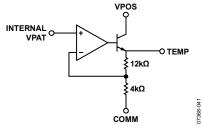

#### **TEMPERATURE SENSOR INTERFACE**

The AD8363 provides a temperature sensor output with an output voltage scaling factor of approximately 5 mV/°C. The output is capable of sourcing 4 mA and sinking 50  $\mu A$  maximum at temperatures at or above 25°C. If additional current sink capability is desired, an external resistor can be connected between the TEMP and COMM pins. The typical output voltage at 25°C is approximately 1.4 V.

Figure 35. TEMP Interface Simplified Schematic

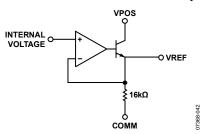

#### **VREF INTERFACE**

The VREF pin provides an internally generated voltage reference. The  $V_{\text{REF}}$  voltage is a temperature stable 2.3 V reference that is capable of sourcing 4 mA and sinking 50  $\mu A$  maximum at temperatures at or above 25°C. An external resistor can be connected between the VREF and COMM pins to provide additional current sink capability. The voltage on this pin can be used to drive the TCM1, TCM2/PWDN, and VTGT pins, if desired.

Figure 36. VREF Interface Simplified Schematic

#### **TEMPERATURE COMPENSATION INTERFACE**

Proprietary techniques are used to maximize the temperature stability of the AD8363. For optimal performance, the output temperature drift must be compensated for using the TCM1 and TCM2/PWDN pins. The absolute value of compensation varies with frequency and  $V_{\rm TGT}.$  Table 4 shows the recommended voltages for the TCM1 and TCM2/PWDN pins to maintain the best temperature drift error over the rated temperature range ( $-40^{\circ}\text{C} < T_{\rm A} < 85^{\circ}\text{C}$ ) when driven single-ended and using a  $V_{\rm TGT} = 1.4~V.$

Table 4. Recommended Voltages for TCM1 and TCM2/PWDN

| · ·       |          |               |  |  |  |

|-----------|----------|---------------|--|--|--|

| Frequency | TCM1 (V) | TCM2/PWDN (V) |  |  |  |

| 100 MHz   | 0.47     | 1.0           |  |  |  |

| 900 MHz   | 0.5      | 1.2           |  |  |  |

| 1.9 GHz   | 0.52     | 0.51          |  |  |  |

| 2.14 GHz  | 0.52     | 0.6           |  |  |  |

| 2.6 GHz   | 0.54     | 1.1           |  |  |  |

| 3.8 GHz   | 0.56     | 1.0           |  |  |  |

| 5.8 GHz   | 0.88     | 1.0           |  |  |  |

The values in Table 4 were chosen to give the best drift performance at the high end of the usable dynamic range over the  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range.

Compensating the device for the temperature drift using TCM1 and TCM2/PWDN allows for great flexibility and the user may wish to modify these values to optimize for another amplitude point in the dynamic range, for a different temperature range, or for an operating frequency other than those shown in Table 4.

To find a new compensation point,  $V_{\text{TCM1}}$  and  $V_{\text{TCM2}}$  can be swept while monitoring  $V_{\text{OUT}}$  over the temperature at the frequency and amplitude of interest. The optimal voltages for  $V_{\text{TCM1}}$  and  $V_{\text{TCM2}}$  to achieve minimum temperature drift at a given power and frequency are the values of  $V_{\text{TCM1}}$  and  $V_{\text{TCM2}}$  where  $V_{\text{OUT}}$  has minimum movement. See the AD8364 and ADL5513 data sheets for more information.

Varying  $V_{TCM1}$  and  $V_{TCM2}$  has only a very slight effect on  $V_{OUT}$  at device temperatures near 25°C; however, the compensation circuit has more and more effect, and is more and more necessary for best temperature drift performance, as the temperature departs farther from 25°C.

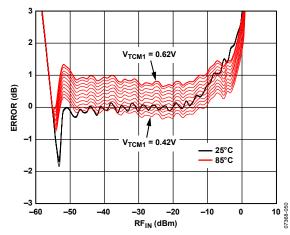

Figure 37 shows the effect on temperature drift performance at  $25^{\circ}$ C and  $85^{\circ}$ C as  $V_{TCM1}$  is varied but  $V_{TCM2}$  is held constant at 0.6 V.

Figure 37. Error vs. Input Amplitude over Stepped  $V_{TCM1}$  Values, 25°C and 85°C, 2.14 GHz,  $V_{TCM2} = 0.6 \text{ V}$

TCM1 primarily adjusts the intercept of the AD8363 at temperature. In this way, TCM1 can be thought of as a coarse adjustment to the compensation. Conversely, TCM2 performs a fine adjustment. For this reason, it is advised that when searching for compensation with  $V_{\rm TCM1}$  and  $V_{\rm TCM2}$ , that  $V_{\rm TCM1}$  be adjusted first, and when best performance is found,  $V_{\rm TCM2}$  can then be adjusted for optimization.

It is evident from Figure 37 that the temperature compensation circuit can be used to adjust for the lowest drift at any input amplitude of choice. Though not shown in Figure 37, a similar analysis can simultaneously be performed at  $-40^{\circ}$ C, or any other temperature within the operating range of the AD8363.

Performance varies slightly from device to device; therefore, optimal  $V_{\text{TCM1}}$  and  $V_{\text{TCM2}}$  values must be arrived at statistically

over a population of devices to be useful in mass production applications.

The TCM1 and TCM2 pins have high input impedances, approximately 5 k $\Omega$  and 500 k $\Omega$ , respectively, and can be conveniently driven from an external source or from a fraction of VREF by using a resistor divider. VREF does change slightly with temperature and RF input amplitude (see Figure 32 and Figure 29); however, the amount of change is unlikely to result in a significant effect on the final temperature stability of the RF measurement system.

Figure 38 shows a simplified schematic representation of TCM1. See the Power-Down Interface section for the TCM2 interface.

Figure 38. TCM1 Interface Simplified Schematic

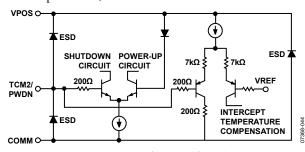

#### **POWER-DOWN INTERFACE**

The quiescent and disabled currents for the AD8363 at 25°C are approximately 60 mA and 300 µA, respectively. The dual function pin, TCM2/PWDN, is connected to a temperature compensation circuit as well as a power-down circuit. Typically, when PWDN is greater than  $V_{POS} - 0.1$  V, the device is fully powered down. Figure 28 shows this characteristic as a function of V<sub>PWDN</sub>. Note that because of the design of this section of the AD8363, as  $V_{TCM2}$  passes through a narrow range at ~4.5 V (or ~ $V_{POS}$  – 0.5 V), the TCM2/PWDN pin sinks approximately 750 µA. The source used to disable the AD8363 must have a sufficiently high current capability for this reason. Figure 23 shows the typical response times for various RF input levels. The output reaches within 0.1 dB of its steady-state value in approximately 35 µs; however, the reference voltage is available to full accuracy in a much shorter time. This wake-up response varies depending on the input coupling and the capacitances, CHPF and CLPF.

Figure 39. PWDN Interface Simplified Schematic

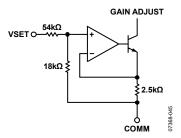

#### **VSET INTERFACE**

The VSET interface has a high input impedance of 72 k $\Omega$ . The voltage at VSET is converted to an internal current used to set the internal VGA gain. The VGA attenuation control is approximately 19 dB/V.

Figure 40. VSET Interface Simplified Schematic

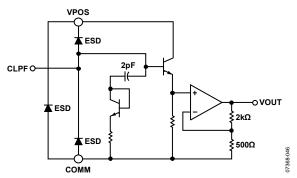

#### **OUTPUT INTERFACE**

The output driver used in the AD8363 is different from the output stage on the AD8362. The AD8363 incorporates rail-to-rail output drivers with pull-up and pull-down capabilities. The closed-loop -3 dB bandwidth of the VOUT buffer with no load is approximately 58 MHz with a single-pole roll-off of -20 dB/dec. The output noise is approximately 45 nV/ $\sqrt{\rm Hz}$  at 100 kHz, which is independent of C<sub>LPF</sub> due to the architecture of the AD8363. VOUT can source and sink up to 10 mA. There is an internal load between VOUT and COMM of 2.5 k $\Omega$ .

Figure 41. VOUT Interface Simplified Schematic

#### **VTGT INTERFACE**

The target voltage can be set with an external source or by connecting the VREF pin (nominally 2.3 V) to the VTGT pin through a resistive voltage divider. With 1.4 V on the VTGT pin, the rms voltage that must be provided by the VGA to balance the AGC feedback loop is  $1.4~{\rm V}\times0.05=70~{\rm mV}$  rms. Most of the characterization information in this data sheet was collected at  ${\rm V}_{\rm TGT}=1.4~{\rm V}$ . Voltages higher and lower than this can be used; however, doing so increases or decreases the gain at the internal squaring cell, which results in a corresponding increase or decrease in intercept. This in turn affects the sensitivity and the usable measurement range. Because the gain of the squaring cell varies with temperature, oscillations or a loss in measurement range can result. For these reasons, do not reduce  ${\rm V}_{\rm TGT}$  below 1.3 V.

Figure 42. VTGT Interface Simplified Schematic

#### MEASUREMENT MODE BASIC CONNECTIONS