# ANALOG 8-Channel, 16-Bit, Simultaneous Sampling DEVICES ADC with Power Scaling 110 8 kHz RW ADC with Power Scaling, 110.8 kHz BW

**AD7761 Data Sheet**

#### **FEATURES**

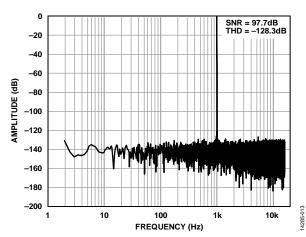

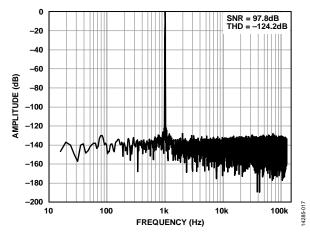

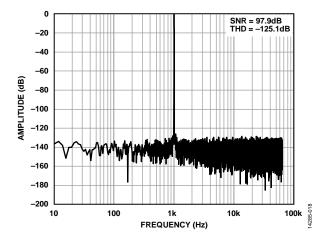

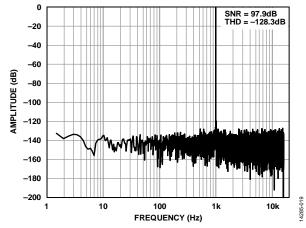

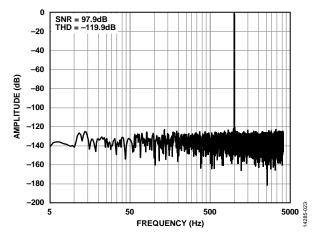

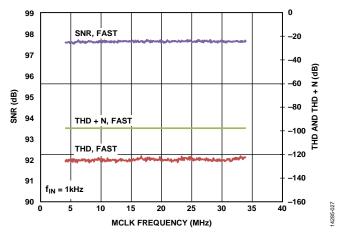

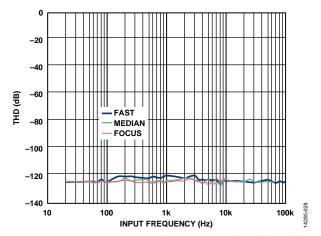

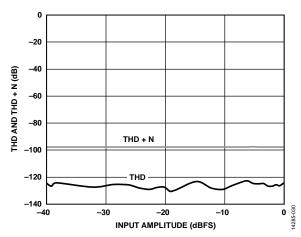

Precision ac and dc performance 8-channel simultaneous sampling 256 kSPS ADC ODR per channel 97.7 dB dynamic range 110.8 kHz input bandwidth (-3 dB BW) -120 dB THD, typical

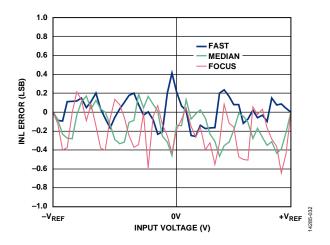

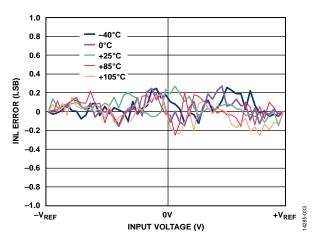

±1 LSB INL, ±1 LSB offset error, ±5 LSB gain error

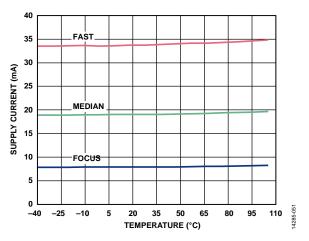

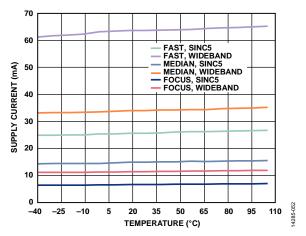

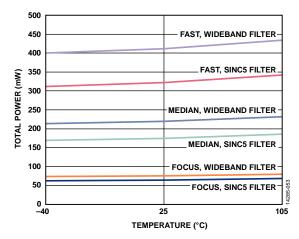

Optimized power dissipation vs. noise vs. input bandwidth Selectable power, speed, and input bandwidth

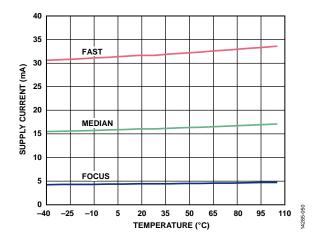

Fast (highest speed): 110.8 kHz BW, 51.5 mW per channel Median (half speed): 55.4 kHz BW, 27.5 mW per channel Low power (lowest power): 13.8 kHz BW, 9.375 mW per channel

Input BW range: dc to 110.8 kHz Programmable input bandwidth/sampling rates CRC error checking on data interface **Daisy-chaining**

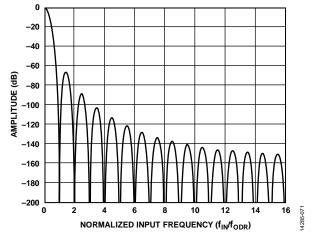

Linear phase digital filter

Low latency sinc5 filter

Wideband brick wall filter: ±0.005 dB ripple to 102.4 kHz

**Analog input precharge buffers**

**Power supply**

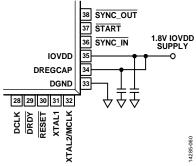

AVDD1 = 5 V, AVDD2 = 2.25 V to 5.0 V IOVDD = 2.5 V to 3.3 V or IOVDD = 1.8 V 64-lead LQFP package, no exposed pad

Temperature range: -40°C to +105°C

#### **APPLICATIONS**

Data acquisition systems: USB/PXI/Ethernet Instrumentation and industrial control loops **Audio testing and measurement** Vibration and asset condition monitoring 3-phase power quality analysis

High precision medical electroencephalogram (EEG)/ electromyography (EMG)/electrocardiogram (ECG)

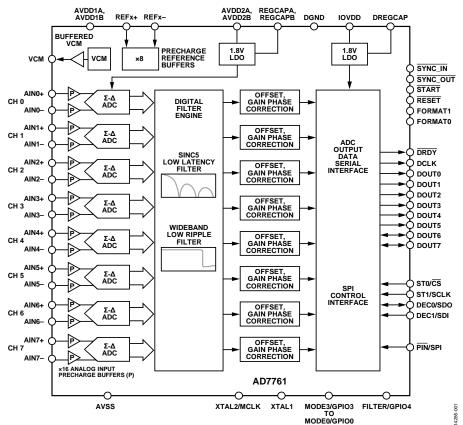

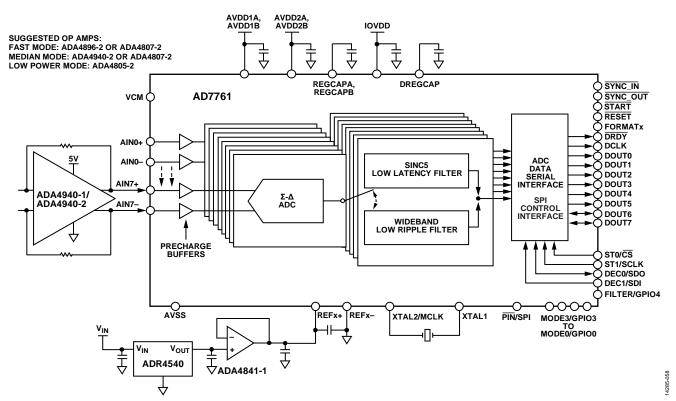

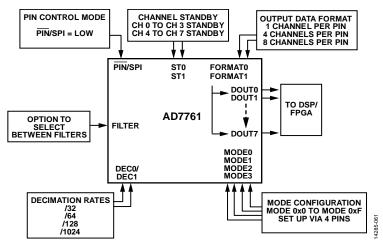

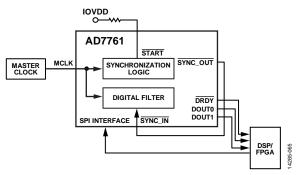

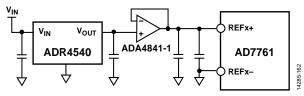

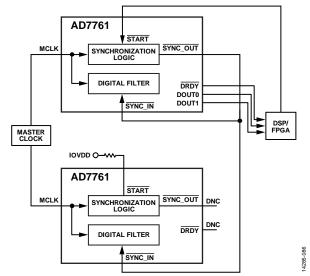

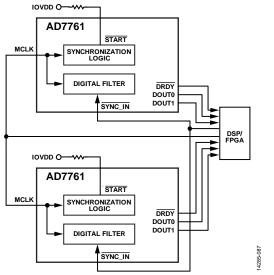

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

**Document Feedback** Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2016–2017 Analog Devices, Inc. All rights reserved. **Technical Support** www.analog.com

# AD7761\* PRODUCT PAGE QUICK LINKS

Last Content Update: 09/12/2017

# COMPARABLE PARTS 🖵

View a parametric search of comparable parts.

# **EVALUATION KITS**

· AD7761 Evaluation Board

# **DOCUMENTATION**

#### **Data Sheet**

AD7761: 8-Channel, 16-Bit, Simultaneous Sampling ADC with Power Scaling, 110.8 kHz BW Data Sheet

#### **User Guides**

UG-949: Evaluation Board for the AD7761 16-Bit, 8-Channel, Simultaneous Sampling, 256 kSPS, Sigma-Delta ADC with Power Scaling

# REFERENCE MATERIALS $\Box$

#### **Press**

Sigma-Delta A/D Converters Improve Signal Quality Monitoring in Instrumentation, Energy and Healthcare Applications

# **DESIGN RESOURCES**

- AD7761 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- Symbols and Footprints

### **DISCUSSIONS**

View all AD7761 EngineerZone Discussions.

# SAMPLE AND BUY 🖳

Visit the product page to see pricing options.

# **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

This page is dynamically generated by Analog Devices, Inc., and inserted into this data sheet. A dynamic change to the content on this page will not trigger a change to either the revision number or the content of the product data sheet. This dynamic page may be frequently modified.

**Data Sheet**

# **AD7761**

# **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| Functional Block Diagram                    | 1  |

| Revision History                            | 3  |

| General Description                         | 4  |

| Specifications                              | 5  |

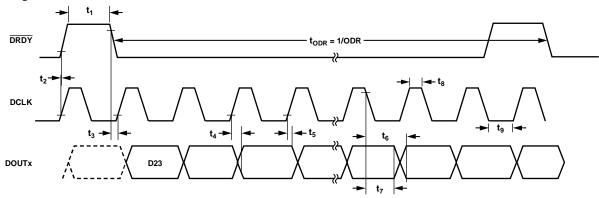

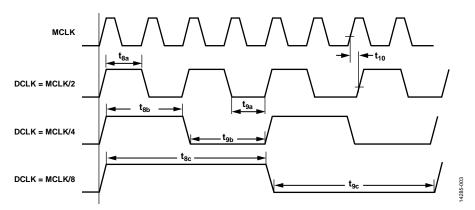

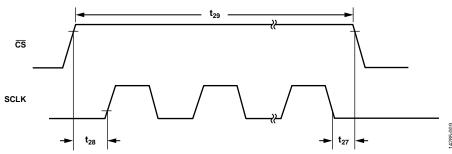

| Timing Specifications                       | 10 |

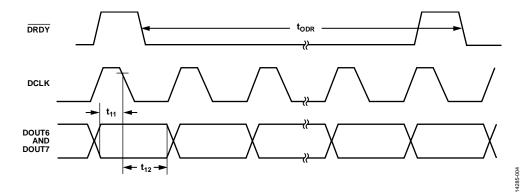

| 1.8 V IOVDD Timing Specifications           | 11 |

| Absolute Maximum Ratings                    | 15 |

| Thermal Resistance                          | 15 |

| ESD Caution                                 | 15 |

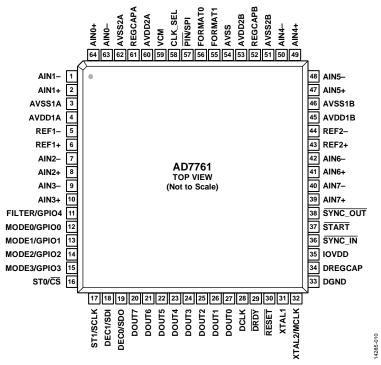

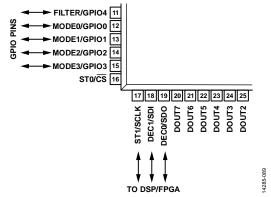

| Pin Configuration and Function Descriptions | 16 |

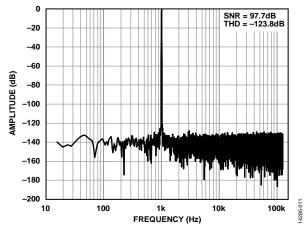

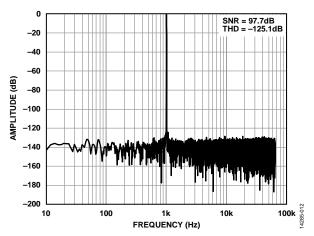

| Typical Performance Characteristics         | 20 |

| Terminology                                 | 26 |

| Theory of Operation                         | 27 |

| Clocking, Sampling Tree, and Power Scaling  | 27 |

| Noise Performance and Resolution            | 28 |

| Applications Information                    | 30 |

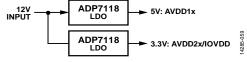

| Power Supplies                              | 31 |

| Device Configuration                        | 32 |

| Pin Control Mode                            | 32 |

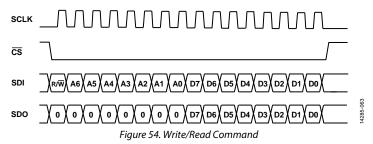

| SPI Control                                 | 35 |

| SPI Control Functionality                   | 36 |

| SPI Control Mode Extra Diagnostic Features  | 38 |

| Circuit Information                         | 39 |

| Core Signal Chain                           | 39 |

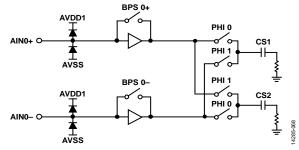

| Analog Inputs                               | 40 |

| VCM                                         | 41 |

| Reference Input                             | 42 |

| Clock Selection                             | 42 |

| Digital Filtering                           | 42 |

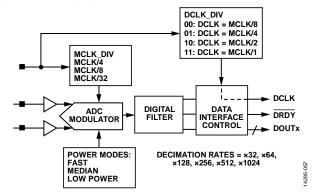

| Decimation Rate Control                     | 46 |

| Antialiasing                                | 46 |

| Calibration                                 | 48 |

| Data Interface                              | 49 |

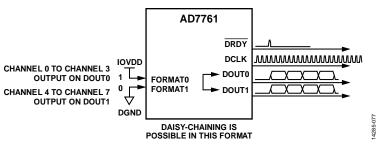

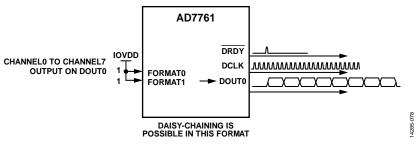

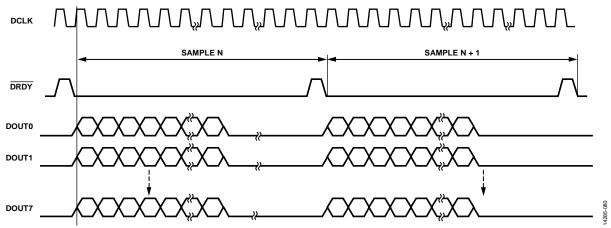

| Setting the Format of Data Output43                                  | 7 |

|----------------------------------------------------------------------|---|

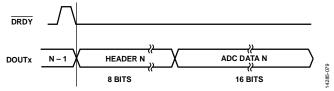

| ADC Conversion Output: Header and Data 50                            | 0 |

| Functionality                                                        | 9 |

| GPIO Functionality59                                                 | 9 |

| Register Map Details (SPI Control)                                   | 0 |

| Register Map60                                                       | 0 |

| Channel Standby Register                                             | 2 |

| Channel Mode A Register                                              | 3 |

| Channel Mode B Register                                              | 3 |

| Channel Mode Select Register64                                       | 4 |

| Power Mode Select Register64                                         | 4 |

| General Device Configuration Register                                | 5 |

| Data Control: Soft Reset, Sync, and Single-Shot Control Register     | 6 |

| Interface Configuration Register                                     | 6 |

| Digital Filter RAM Built in Self Test (BIST) Register 67             | 7 |

| Status Register67                                                    | 7 |

| Revision Identification Register                                     | 8 |

| GPIO Control Register                                                | 8 |

| GPIO Write Data Register69                                           | 9 |

| GPIO Read Data Register69                                            | 9 |

| Analog Input Precharge Buffer Enable Register Channel 0 to Channel 3 | 9 |

| Analog Input Precharge Buffer Enable Register Channel 4 to Channel 7 | 0 |

| Positive Reference Precharge Buffer Enable Register                  | 0 |

| Negative Reference Precharge Buffer Enable Register 71               | 1 |

| Offset Registers7                                                    | 1 |

| Gain Registers72                                                     | 2 |

| Sync Phase Offset Registers                                          | 2 |

| ADC Diagnostic Receive Select Register72                             | 2 |

| ADC Diagnostic Control Register                                      | 3 |

| Modulator Delay Control Register74                                   | 4 |

| Chopping Control Register                                            | 4 |

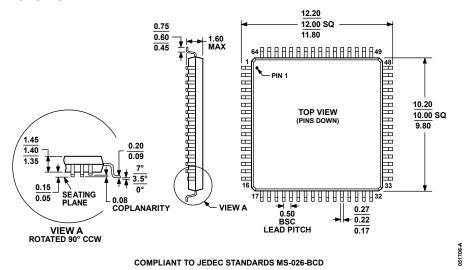

| Outline Dimensions                                                   | 5 |

| Ordering Guide75                                                     | 5 |

# **REVISION HISTORY**

| 9/2017—Rev. 0 to Rev. A                           |          |

|---------------------------------------------------|----------|

| Changed Focus Mode to Low Power Mode T            | hroughou |

| Changes to Table 1                                |          |

| Changes to Figure 2                               | 13       |

| Changes to Thermal Resistance Section and Table 7 | 1        |

| Changes to Table 8                                | 10       |

| Changes to Figure 47                              | 27       |

| Changes to Figure 48                              | 30       |

| Changes to MCLK Source Selection Section          | 37       |

| Changes to Analog Input Precharge Buffers Section | 38       |

| Changes to Analog Inputs Section                  | 40       |

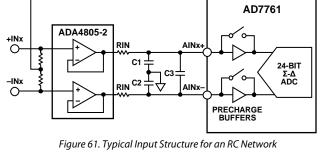

| Added Figure 61; Renumbered Sequentially          | 4        |

| Changes to Table 24                               | 4        |

| Changes to Reference Input Section                | 42       |

| Added Figure 62                                   | 42       |

| Added Filter Settling Time Section                | 43       |

| Changes to Wideband Low Ripple Filter Section     |          |

| Moved Table 25                                    | 44       |

4/2016—Revision 0: Initial Version

# **GENERAL DESCRIPTION**

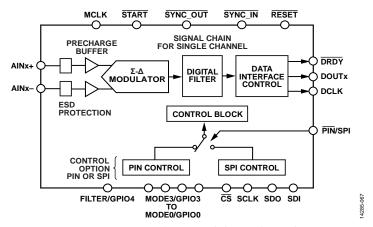

The AD7761 is an 8-channel, simultaneous sampling sigma-delta  $(\Sigma - \Delta)$  analog-to-digital converter (ADC) with a  $\Sigma - \Delta$  modulator and digital filter per channel, enabling synchronized sampling of ac and dc signals.

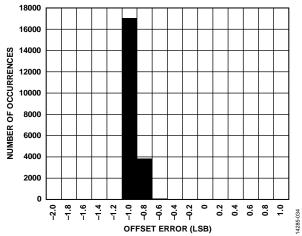

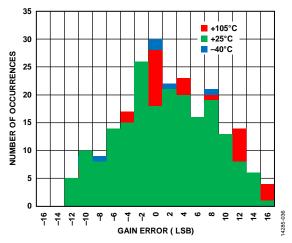

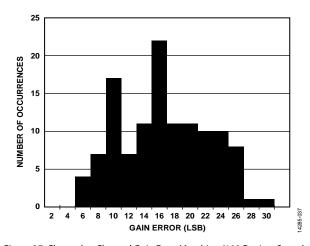

The AD7761 achieves 97.7 dB dynamic range at a maximum input bandwidth of 110.8 kHz, combined with typical performance of  $\pm 1$  LSB integral nonlinearity (INL),  $\pm 1$  LSB offset error, and  $\pm 5$  LSB gain error.

The AD7761 user can trade off input bandwidth, output data rate, and power dissipation. Select one of three power modes to optimize the device for noise targets and power consumption. The flexibility of the AD7761 allows it to become a reusable platform for low power dc and high performance ac measurement modules.

The AD7761 has three modes: fast mode (256 kSPS maximum, 110.8 kHz input bandwidth, 51.5 mW per channel), median mode (128 kSPS maximum, 55.4 kHz input bandwidth, 27.5 mW per channel) and low power mode (32 kSPS maximum, 13.8 kHz input bandwidth, 9.375 mW per channel).

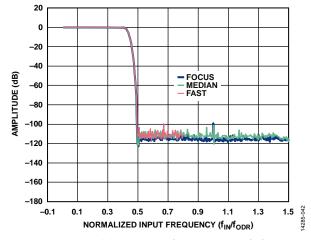

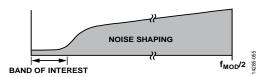

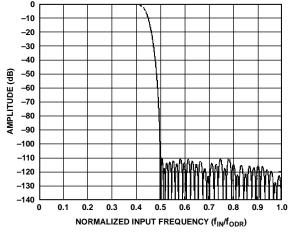

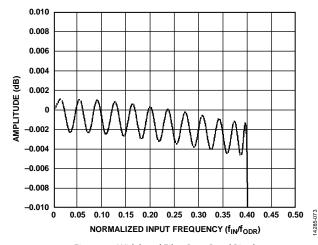

The AD7761 offers extensive digital filtering capabilities, such as a wideband, low  $\pm 0.005$  dB pass-band ripple, antialiasing low-pass filter with sharp roll-off, and 105 dB attenuation at the Nyquist frequency.

Frequency domain measurements can use the wideband linear phase filter. This filter has a flat pass band ( $\pm 0.005$  dB ripple) from dc to 102.4 kHz at 256 kSPS, from dc to 51.2 kHz at 128 kSPS, or from dc to 12.8 kHz at 32 kSPS.

The AD7761 also offers sinc response via a sinc5 filter, a low latency path for low bandwidth, and low noise measurements.

The wideband and sinc5 filters can be selected and run on a per channel basis.

Within these filter options, the user can improve the dynamic range by selecting from decimation rates of  $\times 32$ ,  $\times 64$ ,  $\times 128$ ,  $\times 256$ ,  $\times 512$ , and  $\times 1024$ . The ability to vary the decimation filtering optimizes noise performance to the required input bandwidth.

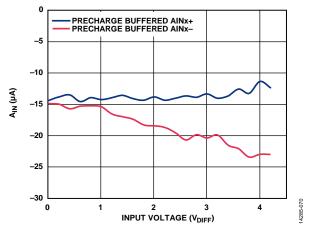

Embedded analog functionality on each ADC channel makes design easier, such as a precharge buffer on each analog input that reduces analog input current and a precharge reference buffer per channel reduces input current and glitches on the reference input terminals.

The device operates with a 5 V AVDD1A and AVDD1B supply, a 2.25 V to 5.0 V AVDD2A and AVDD2B supply, and a 2.5 V to 3.3 V or 1.8 V IOVDD supply (see the 1.8 V IOVDD Operation section for specific requirements for operating at 1.8 V IOVDD).

The device requires an external reference; the absolute input reference voltage range is 1 V to AVDD1 – AVSS.

For the purposes of clarity within this data sheet, the AVDD1A and AVDD1B supplies are referred to as AVDD1 and the AVDD2A and AVDD2B supplies are referred to as AVDD2. For the negative supplies, AVSS refers to the AVSS1A, AVSS1B, AVSS2A, AVSS2B, and AVSS pins.

The specified operating temperature range is  $-40^{\circ}$ C to  $+105^{\circ}$ C. The device is housed in a 10 mm  $\times$  10 mm 64-lead LQFP package with a 12 mm  $\times$  12 mm printed circuit board (PCB) footprint.

Throughout this data sheet, multifunction pins, such as XTAL2/MCLK, are referred to either by the entire pin name or by a single function of the pin, for example MCLK, when only that function is relevant.

# **SPECIFICATIONS**

$AVDD1A = AVDD1B = 4.5 \text{ V to } 5.5 \text{ V, } AVDD2A = AVDD2B = 2.0 \text{ V to } 5.5 \text{ V, } IOVDD = 1.72 \text{ V to } 1.88 \text{ V and } 2.25 \text{ V to } 3.6 \text{ V, } AVSS = DGND = 0 \text{ V, } REFx+ = 4.096 \text{ V and } REFx- = 0 \text{ V, } MCLK = 32.768 \text{ MHz, } analog input precharge buffers on, reference precharge buffers off, wideband filter, <math>f_{CHOP} = f_{MOD}/32$ ,  $T_A = -40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$ , unless otherwise noted.

Table 1.

| Parameter                                           | Test Conditions/Comments                                                                                  | Min        | Тур                 | Max           | Unit    |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------|---------------------|---------------|---------|

| ADC SPEED AND PERFORMANCE                           |                                                                                                           |            |                     |               |         |

| Output Data Rate (ODR), per<br>Channel <sup>1</sup> | Fast                                                                                                      | 8          |                     | 256           | kSPS    |

|                                                     | Median                                                                                                    | 4          |                     | 128           | kSPS    |

|                                                     | Low power                                                                                                 | 1          |                     | 32            | kSPS    |

| −3 dB Bandwidth (BW)                                | Fast, wideband filter                                                                                     |            |                     | 110.8         | kHz     |

|                                                     | Median, wideband filter                                                                                   |            |                     | 55.4          | kHz     |

|                                                     | Low power, wideband filter                                                                                |            |                     | 13.8          | kHz     |

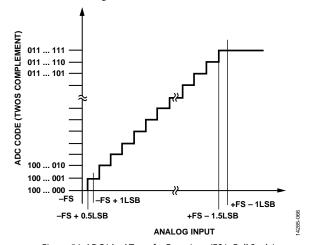

| Data Output Coding                                  |                                                                                                           |            | Twos complemen      | nt, MSB first |         |

| No Missing Codes <sup>2</sup>                       |                                                                                                           | 16         |                     |               | Bits    |

| DYNAMIC PERFORMANCE                                 |                                                                                                           |            |                     |               |         |

|                                                     | Decimation by 32, 256 kSPS ODR                                                                            |            |                     |               |         |

| Dynamic Range                                       | Shorted input, wideband filter                                                                            | 97.3       | 97.7                |               | dB      |

| Signal-to-Noise Ratio (SNR)                         | 1 kHz, –0.5 dBFS, sine wave input                                                                         |            |                     |               |         |

|                                                     | Sinc5 filter                                                                                              | 97.3       | 97.9                |               | dB      |

|                                                     | Wideband filter                                                                                           | 97.3       | 97.7                |               | dB      |

| Signal-to-Noise-and-Distortion<br>Ratio (SINAD)     | 1 kHz, –0.5 dBFS, sine wave input                                                                         | 97.3       | 97.7                |               | dB      |

| Total Harmonic Distortion (THD)                     | 1 kHz, –0.5 dBFS, sine wave input                                                                         |            | -120                | -107          | dB      |

| Spurious-Free Dynamic Range (SFDR)                  |                                                                                                           |            | 126                 |               | dBc     |

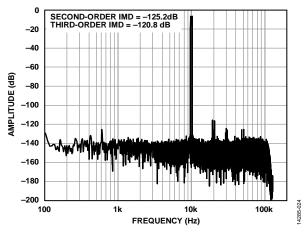

| INTERMODULATON DISTORTION (IMD)                     | f <sub>INA</sub> = 9.7 kHz, f <sub>INB</sub> = 10.3 kHz                                                   |            |                     |               |         |

|                                                     | Second order                                                                                              |            | -125                |               | dB      |

|                                                     | Third order                                                                                               |            | -124                |               | dB      |

| ACCURACY                                            |                                                                                                           |            |                     |               |         |

| INL <sup>3</sup>                                    | Endpoint method                                                                                           |            | ±1                  | ± 1.5         | LSB     |

| Offset Error⁴                                       |                                                                                                           |            | ±1                  | ±2            | LSB     |

| Gain Error⁴                                         | T <sub>A</sub> = 25°C                                                                                     |            | ±5                  | ±40           | LSB     |

| Gain Drift vs. Temperature <sup>2</sup>             |                                                                                                           |            | ±0.01               | ±0.02         | LSB/°C  |

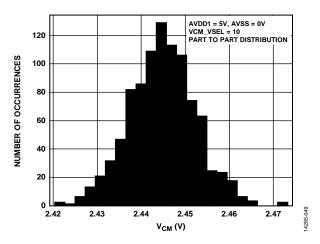

| VCM PIN                                             |                                                                                                           |            |                     |               |         |

| Output                                              | With respect to AVSS                                                                                      |            | (AVDD1 –<br>AVSS)/2 |               | V       |

| Load Regulation                                     | ΔV <sub>OUT</sub> /ΔΙ <sub>L</sub>                                                                        |            | 400                 |               | μV/mA   |

| Voltage Regulation                                  | Applies to the following VCM output                                                                       |            | 5                   |               | μV/V    |

|                                                     | options only: $V_{CM} = \Delta V_{OUT}/\Delta (AVDD1 - AVSS)/2$ , $V_{CM} = 1.65$ V, and $V_{CM} = 2.5$ V |            |                     |               |         |

| Short-Circuit Current                               |                                                                                                           |            | 30                  |               | mA      |

| ANALOG INPUTS                                       | See the Analog Inputs section                                                                             |            |                     |               |         |

| Differential Input Voltage Range                    | $V_{REF} = (REFx+) - (REFx-)$                                                                             | $-V_{REF}$ |                     | $+V_{REF}$    | V       |

| Input Common-Mode Range <sup>2</sup>                |                                                                                                           | AVSS       |                     | AVDD1         | V       |

| Absolute Analog Input Voltage Limits <sup>2</sup>   |                                                                                                           | AVSS       |                     | AVDD1         | V       |

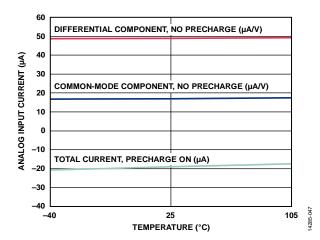

| Analog Input Current                                |                                                                                                           |            |                     |               |         |

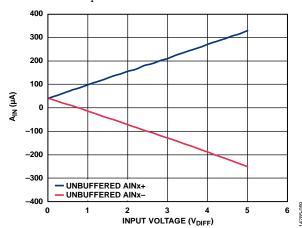

| Unbuffered                                          | Differential component                                                                                    |            | ±48                 |               | μA/V    |

|                                                     | Common-mode component                                                                                     |            | ±17                 |               | μA/V    |

| Precharge Buffer On⁵                                |                                                                                                           |            | -20                 |               | μΑ      |

| Input Current Drift                                 |                                                                                                           |            |                     |               |         |

| Unbuffered                                          |                                                                                                           |            | ±5                  |               | nA/V/°C |

| Precharge Buffer On                                 |                                                                                                           |            | ±31                 |               | nA/°C   |

| Parameter                                          | Test Conditions/Comments                                                 | Min            | Тур                | Max          | Unit          |

|----------------------------------------------------|--------------------------------------------------------------------------|----------------|--------------------|--------------|---------------|

| EXTERNAL REFERENCE                                 |                                                                          |                |                    |              |               |

| Reference Voltage                                  | $V_{REF} = (REFx+) - (REFx-)$                                            | 1              |                    | AVDD1 – AVSS | V             |

| Absolute Reference Voltage Limits <sup>2</sup>     | Precharge reference buffers off                                          | AVSS –<br>0.05 |                    | AVDD1 + 0.05 | V             |

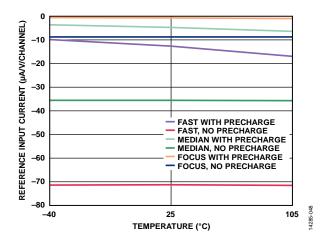

| Average Reference Current                          | Precharge reference buffers on Fast mode                                 | AVSS           |                    | AVDD1        | V             |

| Average Neierence Current                          | Precharge reference buffers off                                          |                | ±72                |              | μΑ/V/channe   |

|                                                    | Precharge reference buffers on                                           |                | ±16                |              | μΑ/V/channe   |

| Average Reference Current Drift                    | Fast mode                                                                |                | ±10                |              | μΑ/V/Cilarine |

| Average helerence Current Dilit                    | Precharge reference buffers off                                          |                | ±1.7               |              | nA/V/°C       |

|                                                    | Precharge reference buffers on                                           |                | ±1.7<br>±49        |              | nA/V/°C       |

| Common-Mode Rejection                              | riecharge reference buriers on                                           |                | ±49<br>95          |              | dB            |

| DIGITAL FILTER RESPONSE                            |                                                                          |                | 93                 |              | db            |

| Low Ripple Wideband Filter                         | FILTER = 0                                                               |                |                    |              |               |

| Decimation Rate                                    | Up to six selectable decimation rates                                    | 32             |                    | 1024         |               |

| Group Delay                                        | Latency                                                                  | 32             | 34/ODR             | 1024         | sec           |

| Settling Time                                      | Complete settling                                                        |                | 68/ODR             |              | sec           |

| Pass-Band Ripple <sup>2</sup>                      | Complete setting                                                         |                | 00/ODN             | ±0.005       | dB            |

| Pass Band                                          | ±0.005 dB bandwidth                                                      |                | 0.4 × ODR          | ±0.005       | Hz            |

| rass ballu                                         | -0.1 dB bandwidth                                                        |                | 0.409 × ODR        |              | Hz            |

|                                                    | -3 dB bandwidth                                                          |                | 0.433 × ODR        |              | Hz            |

| Stop Band Frequency                                | Attenuation > 105 dB                                                     |                | 0.499 × ODR        |              | Hz            |

| Stop Band Attenuation                              | Attenuation > 105 db                                                     |                | 0.499 X ODK<br>105 |              | dB            |

| Sinc5 Filter                                       | FILTER = 1                                                               |                | 103                |              | ав            |

| Decimation Rate                                    |                                                                          | 32             |                    | 1024         |               |

|                                                    | Up to six selectable decimation rates                                    | 32             | 3/ODR              | 1024         |               |

| Group Delay                                        | Latency                                                                  |                | 7/ODR              |              | sec           |

| Settling Time<br>Pass Band                         | Complete settling  –3 dB bandwidth                                       |                |                    |              | sec<br>Hz     |

| REJECTION                                          | -3 dB balldwidth                                                         |                | 0.204 × ODR        |              | П             |

|                                                    | V = 0.1 V AVDD1 = 5 V AVDD3 =                                            |                |                    |              |               |

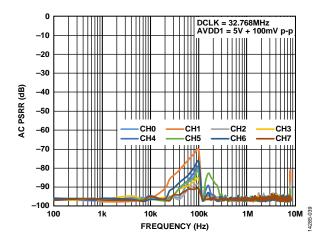

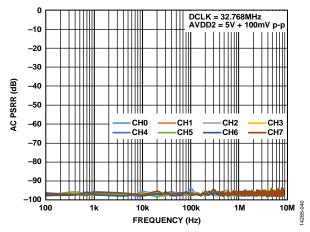

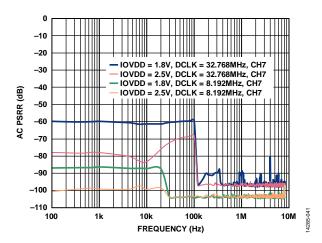

| AC Power Supply Rejection Ratio (PSRR)             | V <sub>IN</sub> = 0.1 V, AVDD1 = 5 V, AVDD2 = 5 V, IOVDD = 2.5 V         |                |                    |              |               |

| AVDD1                                              |                                                                          |                | 90                 |              | dB            |

| AVDD2                                              |                                                                          |                | 100                |              | dB            |

| IOVDD                                              |                                                                          |                | 75                 |              | dB            |

| DC PSRR                                            | $V_{IN} = 1 V$                                                           |                |                    |              |               |

| AVDD1                                              |                                                                          |                | 100                |              | dB            |

| AVDD2                                              |                                                                          |                | 118                |              | dB            |

| IOVDD                                              |                                                                          |                | 90                 |              | dB            |

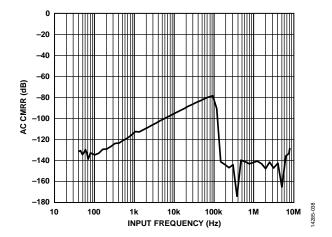

| Analog Input Common-Mode<br>Rejection Ratio (CMRR) |                                                                          |                |                    |              |               |

| DC                                                 | $V_{IN} = 0.1 V$                                                         |                | 95                 |              | dB            |

| AC                                                 | Up to 10 kHz                                                             |                | 95                 |              | dB            |

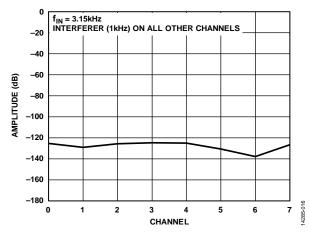

| Crosstalk                                          | -0.5 dBFS input on adjacent channels                                     |                | -120               |              | dB            |

| CLOCK                                              | See the Clock Selection section for data sheet performance functionality |                |                    |              |               |

| Crystal Frequency                                  | ,                                                                        | 8              | 32.768             | 34           | MHz           |

| External Clock (MCLK)                              |                                                                          |                | 32.768             |              | MHz           |

| Duty Cycle                                         |                                                                          |                | 50:50              |              | %             |

| MCLK Pulse Width <sup>2</sup>                      |                                                                          |                |                    |              |               |

| Logic Low                                          |                                                                          | 12.2           |                    |              | ns            |

| Logic High                                         |                                                                          | 12.2           |                    |              | ns            |

| CMOS Clock Input Voltage                           | See the Logic Inputs parameter                                           |                |                    |              |               |

| High, V <sub>INH</sub>                             | e 203.2pato parameter                                                    |                |                    |              |               |

| Low, V <sub>INL</sub>                              |                                                                          |                |                    |              |               |

| Parameter                                  | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Min                  | Тур         | Max                   | Unit      |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------|-----------------------|-----------|

| LVDS Clock <sup>2</sup>                    | $R_L = 100 \Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |             |                       |           |

| Differential Input Voltage                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 100                  |             | 650                   | mV        |

| Common-Mode Input Voltage                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 800                  |             | 1575                  | mV        |

| Absolute Input Voltage                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |             | 1.88                  | V         |

| ADC RESET <sup>2</sup>                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |             |                       |           |

| ADC Start-Up Time After Reset <sup>6</sup> | Time to first DRDY, fast mode, decimation by 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      | 1.58        | 1.66                  | ms        |

| Minimum RESET Low Pulse Width              | t <sub>MCLK</sub> = 1/MCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $2 \times t_{MCLK}$  |             |                       |           |

| LOGIC INPUTS                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |             |                       |           |

| Input Voltage <sup>2</sup>                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |             |                       |           |

| High, V <sub>INH</sub>                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.65 ×<br>IOVDD      |             |                       | V         |

| Low, V <sub>INL</sub>                      | 2.25 V < IOVDD < 3.6 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |             | 0.7                   | V         |

|                                            | 1.72 V < IOVDD < 1.88 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |             | 0.4                   | V         |

| Hysteresis <sup>2</sup>                    | 2.25 V < IOVDD < 3.6 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.04                 |             | 0.09                  | V         |

|                                            | 1.72 V < IOVDD < 1.88 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.04                 |             | 0.2                   | V         |

| Leakage Current                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -10                  | +0.03       | +10                   | μΑ        |

|                                            | RESET pin <sup>7</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -10                  |             | +10                   | μΑ        |

| LOGIC OUTPUTS                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |             |                       |           |

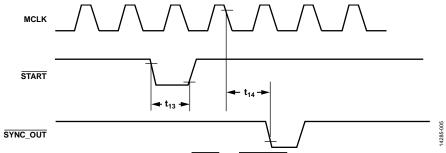

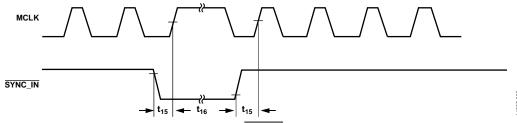

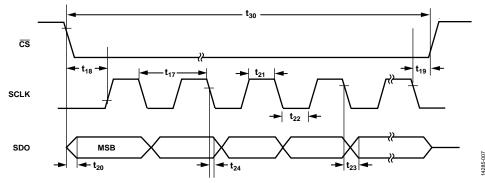

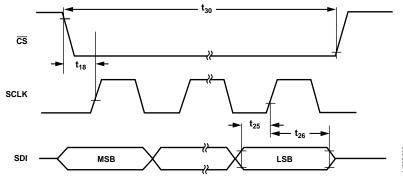

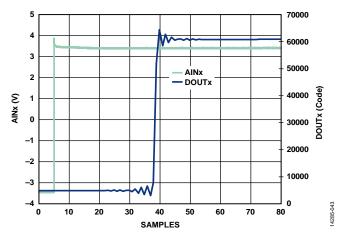

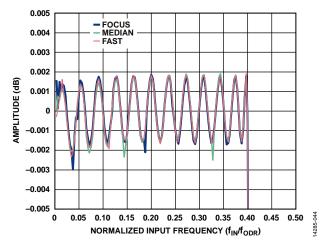

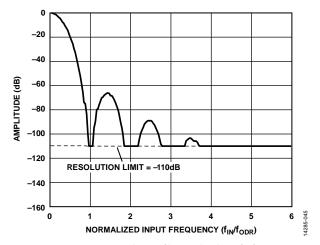

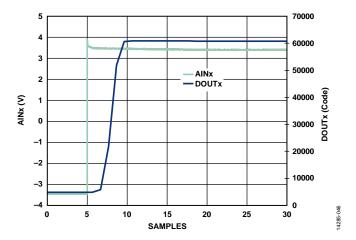

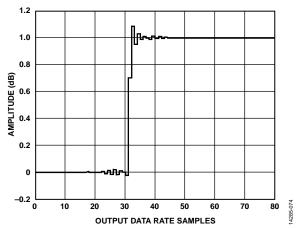

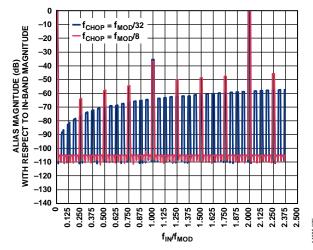

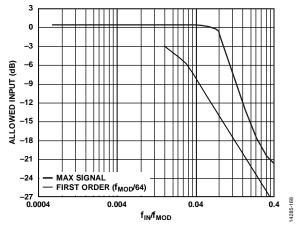

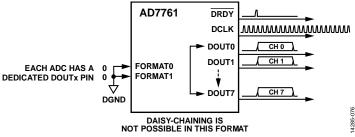

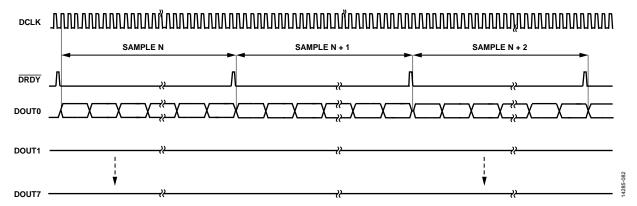

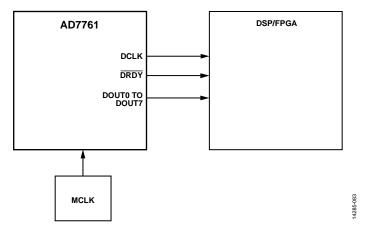

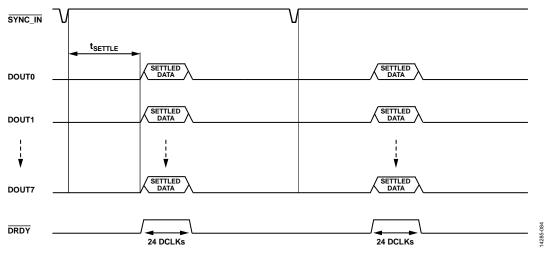

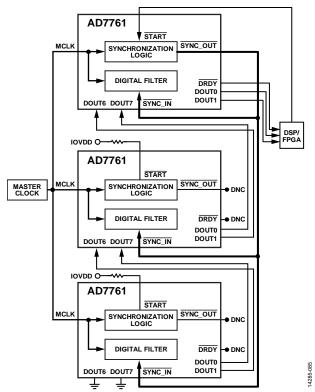

| Output Voltage <sup>2</sup>                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |             |                       |           |