# **ANALOG** Low Voltage 1.15 V to 5.5 V, Single-Channel Bidirectional Logic Level Translator

# ADG3301

### **FEATURES**

Bidirectional level translation Operates from 1.15 V to 5.5 V Low quiescent current < 5 μA No direction pin

### **APPLICATIONS**

SPI®, MICROWIRE® level translation Low voltage ASIC level translation Smart card readers Cell phones and cell phone cradles Portable communication devices Telecommunications equipment Network switches and routers Storage systems (SAN/NAS) Computing/server applications GPS Portable POS systems Low cost serial interfaces

### **GENERAL DESCRIPTION**

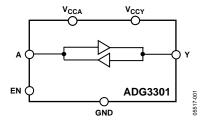

The ADG3301 is a single-channel, bidirectional logic level translator. It can be used in multivoltage digital system applications such as data transfer between a low voltage DSP/controller and a higher voltage device. The internal architecture allows the device to perform bidirectional logic level translation without an additional signal to set the direction in which the translation takes place.

The voltage applied to  $V_{CCA}$  sets the logic levels on the A side of the device, while  $V_{CCY}$  sets the levels on the Y side. For proper operation,  $V_{CCA}$  must always be less than  $V_{CCY}$ . The  $V_{CCA}$ compatible logic signals applied to the A pin appear as  $V_{CCY}$ compatible levels on the Y pin. Similarly,  $V_{CCY}$ -compatible logic levels applied to the Y pin appear as  $V_{CCA}$ -compatible logic levels on the A pin. The enable pin (EN) provides three-state operation on both the A pin and the Y pin. When the device enable pin is pulled low, the terminals on both sides of the device are in the high impedance state. The EN pin is referred to the  $V_{CCA}$  supply voltage and driven high for normal operation.

The ADG3301 is available in a compact 6-lead SC70 package and is guaranteed to operate over the 1.15 V to 5.5 V supply voltage range and extended  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range.

### Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change withhout notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

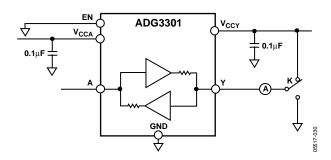

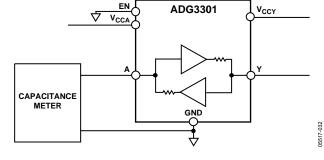

### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

### **PRODUCT HIGHLIGHTS**

- 1. Bidirectional level translation.

- 2. Fully guaranteed over the 1.15 V to 5.5 V supply range.

- 3. No direction pin.

- 4. Compact 6-lead SC70 package.

# **TABLE OF CONTENTS**

| Features                                     |

|----------------------------------------------|

| Applications1                                |

| Functional Block Diagram 1                   |

| General Description 1                        |

| Product Highlights 1                         |

| Specifications                               |

| Absolute Maximum Ratings                     |

| ESD Caution                                  |

| Pin Configuration and Function Descriptions7 |

| Typical Performance Characteristics          |

| Test Circuits                                |

| Terminology15                                |

# Theory of Operation 16 Level Translator Architecture 16 Input Driving Requirements 16 Output Load Requirements 16 Enable Operation 16 Power Supplies 16 Data Rate 17 Applications 18 Layout Guidelines 19 Ordering Guide 19

### **REVISION HISTORY**

12/05—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_{CCY}$  = 1.65 V to 5.5 V,  $V_{CCA}$  = 1.15 V to  $V_{CCY}$ , GND = 0 V. All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

### Table 1.

| Parameter <sup>1</sup>                                             | Symbol                                 | Conditions                                                                                                                            | Min                    | Typ <sup>2</sup> | Max                   | Unit |

|--------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------|-----------------------|------|

| LOGIC INPUTS/OUTPUTS                                               |                                        |                                                                                                                                       |                        |                  |                       |      |

| A Side                                                             |                                        |                                                                                                                                       |                        |                  |                       |      |

| Input High Voltage <sup>3</sup>                                    | VIHA                                   | V <sub>CCA</sub> = 1.15 V                                                                                                             | V <sub>CCA</sub> – 0.3 |                  |                       | V    |

|                                                                    | VIHA                                   | $V_{CCA} = 1.2 V \text{ to } 5.5 V$                                                                                                   | $0.65 \times V_{CCA}$  |                  |                       |      |

| Input Low Voltage <sup>3</sup>                                     | VILA                                   |                                                                                                                                       |                        |                  | $0.35 \times V_{CCA}$ | V    |

| Output High Voltage                                                | V <sub>OHA</sub>                       | $V_{\rm Y} = V_{\rm CCY}$ , $I_{\rm OH} = 20 \mu A$ , see Figure 27                                                                   | $V_{CCA} - 0.4$        |                  |                       | V    |

| Output Low Voltage                                                 | Vola                                   | $V_{\rm Y}$ = 0 V, $I_{\rm OL}$ = 20 $\mu$ A, see Figure 27                                                                           |                        |                  | 0.4                   | V    |

| Capacitance <sup>3</sup>                                           | C <sub>A</sub>                         | f = 1 MHz, $EN = 0$ , see Figure 32                                                                                                   |                        | 9                |                       | pF   |

| Leakage Current                                                    | I <sub>LA, Hi</sub> z                  | $V_A = 0 V/V_{CCA}$ , EN = 0, see Figure 29                                                                                           |                        |                  | ±1                    | μΑ   |

| Y Side                                                             |                                        |                                                                                                                                       |                        |                  |                       |      |

| Input High Voltage <sup>3</sup>                                    | VIHY                                   |                                                                                                                                       | $0.65 \times V_{CCY}$  |                  |                       | V    |

| Input Low Voltage <sup>3</sup>                                     | VILY                                   |                                                                                                                                       |                        |                  | $0.35 \times V_{CCY}$ | V    |

| Output High Voltage                                                | VOHY                                   | $V_A = V_{CCA}$ , $I_{OH} = 20 \ \mu A$ , see Figure 28                                                                               | V <sub>CCY</sub> - 0.4 |                  |                       | V    |

| Output Low Voltage                                                 | VOLY                                   | $V_A = 0 V$ , $I_{OL} = 20 \mu A$ , see Figure 28                                                                                     |                        |                  | 0.4                   | V    |

| Capacitance <sup>3</sup>                                           | Cy                                     | f = 1 MHz, $EN = 0$ , see Figure 33                                                                                                   |                        | 6                |                       | pF   |

| Leakage Current                                                    | ILY, HIZ                               | $V_{\rm Y} = 0  V/V_{\rm CCY}$ , EN = 0, see Figure 30                                                                                |                        |                  | ±1                    | μΑ   |

| Enable (EN)                                                        |                                        |                                                                                                                                       |                        |                  |                       |      |

| Input High Voltage <sup>3</sup>                                    | VIHEN                                  | V <sub>CCA</sub> = 1.15 V                                                                                                             | V <sub>CCA</sub> – 0.3 |                  |                       | v    |

|                                                                    | VIHEN                                  | $V_{CCA} = 1.2 \text{ V to } 5.5 \text{ V}$                                                                                           | $0.65 \times V_{CCA}$  |                  |                       | V    |

| Input Low Voltage <sup>3</sup>                                     | VILEN                                  |                                                                                                                                       |                        |                  | $0.35 \times V_{CCA}$ | V    |

| Leakage Current                                                    | ILEN                                   | $V_{EN} = 0 V/V_{CCA}$ , $V_A = 0 V$ , see Figure 31                                                                                  |                        |                  | ±1                    | μA   |

| Capacitance <sup>3</sup>                                           | CEN                                    |                                                                                                                                       |                        | 3                |                       | pF   |

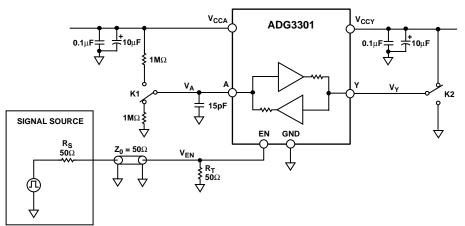

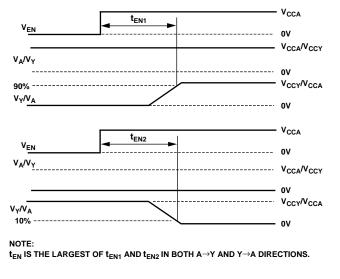

| Enable Time <sup>3</sup>                                           | t <sub>EN</sub>                        | $R_{S} = R_{T} = 50 \Omega, V_{A} = 0 V/V_{CCA} (A \rightarrow Y),$<br>$V_{Y} = 0 V/V_{CCY} (Y \rightarrow A), \text{ see Figure 34}$ |                        | 1                | 1.8                   | μs   |

| SWITCHING CHARACTERISTICS <sup>3</sup>                             |                                        |                                                                                                                                       |                        |                  |                       |      |

| $3.3 V \pm 0.3 V \le V_{CCA} \le V_{CCY}, V_{CCY} = 5 V \pm 0.5 V$ |                                        |                                                                                                                                       |                        |                  |                       |      |

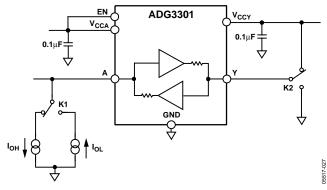

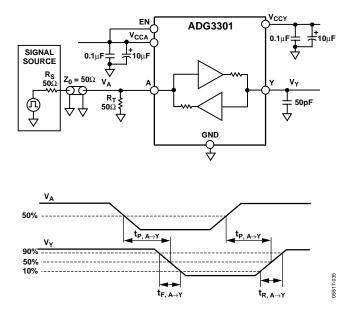

| $A \rightarrow Y$ Level Translation                                |                                        | $R_s = R_T = 50 \Omega$ , $C_L = 50 pF$ , see Figure 35                                                                               |                        |                  |                       |      |

| Propagation Delay                                                  | t <sub>P, A→Y</sub>                    |                                                                                                                                       |                        | 6                | 10                    | ns   |

| RiseTime                                                           | $t_{R,A\rightarrow Y}$                 |                                                                                                                                       |                        | 2                | 3.5                   | ns   |

| Fall Time                                                          | t <sub>F, A→Y</sub>                    |                                                                                                                                       |                        | 2                | 3.5                   | ns   |

| Maximum Data Rate                                                  | D <sub>MAX, A→Y</sub>                  |                                                                                                                                       | 50                     |                  |                       | Mb   |

| Part-to-Part Skew                                                  | $t_{\text{PPSKEW}, A \rightarrow Y}$   |                                                                                                                                       |                        |                  | 3                     | ns   |

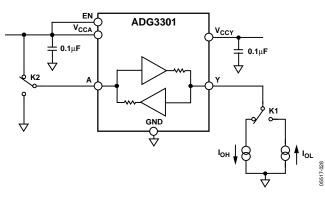

| $Y \rightarrow A$ Level Translation                                |                                        | $R_s = R_T = 50 \Omega$ , $C_L = 15 pF$ , see Figure 36                                                                               |                        |                  |                       |      |

| Propagation Delay                                                  | t <sub>P,Y→A</sub>                     | _                                                                                                                                     |                        | 4                | 7                     | ns   |

| Rise Time                                                          | t <sub>R,Y→A</sub>                     |                                                                                                                                       |                        | 1                | 3                     | ns   |

| Fall Time                                                          | t <sub>F,Y→A</sub>                     |                                                                                                                                       |                        | 3                | 7                     | ns   |

| Maximum Data Rate                                                  |                                        |                                                                                                                                       | 50                     | 5                | ,                     | Mb   |

| Part-to-Part Skew                                                  |                                        |                                                                                                                                       | 50                     |                  | 2                     | ns   |

| $1.8V \pm 0.15V \le V_{CCA} \le V_{CCY}, V_{CCY} = 3.3V \pm 0.3V$  | <b>t</b> ppskew, y→A                   |                                                                                                                                       |                        |                  | <u> </u>              | 113  |

| A $\rightarrow$ Y Translation                                      |                                        | $R_s = R_T = 50 \Omega$ , $C_L = 50 pF$ , see Figure 35                                                                               |                        |                  |                       |      |

| Propagation Delay                                                  | t                                      |                                                                                                                                       |                        | 8                | 11                    | ns   |

| Rise Time                                                          | t <sub>P, A→Y</sub>                    |                                                                                                                                       |                        |                  |                       |      |

|                                                                    | t <sub>R, A→Y</sub>                    |                                                                                                                                       |                        | 2                | 5                     | ns   |

| Fall Time                                                          | t <sub>F, A→Y</sub>                    |                                                                                                                                       | 50                     | 2                | 5                     | ns   |

| Maximum Data Rate                                                  | $D_{MAX, A \rightarrow Y}$             |                                                                                                                                       | 50                     |                  |                       | Mbj  |

| Part-to-Part Skew                                                  | $\mathbf{t}_{PPSKEW, A \rightarrow Y}$ |                                                                                                                                       |                        |                  | 4                     | ns   |

| arameter <sup>1</sup>                                                                                                                           | Symbol                                                                          | Conditions                                                 | Min | Typ <sup>2</sup> | Max  | Uni |

|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------|-----|------------------|------|-----|

| Y→A Translation                                                                                                                                 |                                                                                 | $R_s = R_T = 50 \Omega, C_L = 15 pF,$                      |     |                  |      |     |

|                                                                                                                                                 | .                                                                               | see Figure 36                                              |     | -                | 0    |     |

| Propagation Delay                                                                                                                               | t <sub>P,Y→A</sub>                                                              |                                                            |     | 5                | 8    | ns  |

| RiseTime                                                                                                                                        | t <sub>R,Y→A</sub>                                                              |                                                            |     | 2                | 3.5  | ns  |

| Fall Time                                                                                                                                       | t <sub>F,Y→A</sub>                                                              |                                                            |     | 2                | 3.5  | ns  |

| Maximum Data Rate                                                                                                                               | $D_{MAX,Y \rightarrow A}$                                                       |                                                            | 50  |                  | -    | Mb  |

| Part-to-Part Skew                                                                                                                               | $\mathbf{t}_{PPSKEW, Y \to A}$                                                  |                                                            |     |                  | 3    | ns  |

| $1.15 \text{ V to } 1.3 \text{ V} \le \text{V}_{\text{CCA}} \le \text{V}_{\text{CCY}}, \text{V}_{\text{CCY}} = 3.3 \text{ V} \pm 0.3 \text{ V}$ |                                                                                 |                                                            |     |                  |      |     |

| $A \rightarrow Y$ Translation                                                                                                                   |                                                                                 | $R_s = R_T = 50 \Omega$ , $C_L = 50 pF$ ,<br>see Figure 35 |     |                  |      |     |

| Propagation Delay                                                                                                                               | t <sub>P,A→Y</sub>                                                              | see light ss                                               |     | 9                | 18   | ns  |

| Rise Time                                                                                                                                       | t <sub>R, A→Y</sub>                                                             |                                                            |     | 3                | 5    | ns  |

| Fall Time                                                                                                                                       | t <sub>F,A→Y</sub>                                                              |                                                            |     | 2                | 5    | ns  |

| Maximum Data Rate                                                                                                                               |                                                                                 |                                                            | 40  | -                | 0    | Mb  |

| Part-to-Part Skew                                                                                                                               |                                                                                 |                                                            |     |                  | 10   | ns  |

| $Y \rightarrow A$ Translation                                                                                                                   | <rr> <rr> <rr> <rr> <rr> <rr> <rr> <rr></rr></rr></rr></rr></rr></rr></rr></rr> | $R_s = R_T = 50 \Omega, C_L = 15 pF,$                      |     |                  |      |     |

|                                                                                                                                                 |                                                                                 | see Figure 36                                              |     |                  |      |     |

| Propagation Delay                                                                                                                               | t <sub>P,Y→A</sub>                                                              |                                                            |     | 5                | 9    | ns  |

| Rise Time                                                                                                                                       | $t_{\text{R,Y}\rightarrow\text{A}}$                                             |                                                            |     | 2                | 4    | ns  |

| Fall Time                                                                                                                                       | $t_{F,Y \longrightarrow A}$                                                     |                                                            |     | 2                | 4    | ns  |

| Maximum Data Rate                                                                                                                               | $D_{MAX,Y \rightarrow A}$                                                       |                                                            | 40  |                  |      | Mb  |

| Part-to-Part Skew                                                                                                                               | $t_{\text{PPSKEW}, Y \rightarrow A}$                                            |                                                            |     |                  | 4    | ns  |

| $1.15 \text{ V}$ to $1.3 \text{ V} \le V_{CCA} \le V_{CCY}, V_{CCY} = 1.8 \text{ V} \pm 0.3 \text{ V}$                                          |                                                                                 |                                                            |     |                  |      |     |

| $A \rightarrow Y$ Translation                                                                                                                   |                                                                                 | $R_s = R_T = 50 \Omega$ , $C_L = 50 pF$ , see Figure 35    |     |                  |      |     |

| Propagation Delay                                                                                                                               | $t_{P\!\!\!,A\to Y}$                                                            |                                                            |     | 12               | 25   | ns  |

| Rise Time                                                                                                                                       | $t_{\text{R,}\text{A}\rightarrow\text{Y}}$                                      |                                                            |     | 7                | 12   | ns  |

| Fall Time                                                                                                                                       | $t_{F\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$  |                                                            |     | 3                | 5    | ns  |

| Maximum Data Rate                                                                                                                               | DMAX, A-Y                                                                       |                                                            | 25  |                  |      | Mb  |

| Part-to-Part Skew                                                                                                                               | $t_{\text{PPSKEW},A \to Y}$                                                     |                                                            |     |                  | 15   | ns  |

| $Y \rightarrow A$ Translation                                                                                                                   |                                                                                 | $R_s = R_T = 50 \Omega$ , $C_L = 15 pF$ , see Figure 36    |     |                  |      |     |

| Propagation Delay                                                                                                                               | t <sub>P,Y→A</sub>                                                              |                                                            |     | 14               | 35   | ns  |

| Rise Time                                                                                                                                       | t <sub>R,Y→A</sub>                                                              |                                                            |     | 5                | 16   | ns  |

| Fall Time                                                                                                                                       | t <sub>F,Y→A</sub>                                                              |                                                            |     | 2.5              | 6.5  | ns  |

| Maximum Data Rate                                                                                                                               | $D_{MAX,Y\to A}$                                                                |                                                            | 25  |                  |      | Mb  |

| Part-to-Part Skew                                                                                                                               | $t_{\text{PPSKEW}, Y \rightarrow A}$                                            |                                                            |     |                  | 23.5 | ns  |

| $2.5 V \pm 0.2 V \le V_{CCA} \le V_{CCY}, V_{CCY} = 3.3 V \pm 0.3 V$                                                                            |                                                                                 |                                                            |     |                  |      |     |

| $A \rightarrow Y$ Translation                                                                                                                   |                                                                                 | $R_s = R_T = 50 \Omega$ , $C_L = 50 pF$ , see Figure 35    |     |                  |      |     |

| Propagation Delay                                                                                                                               | $t_{P\!\!,A \to Y}$                                                             |                                                            |     | 7                | 10   | ns  |

| RiseTime                                                                                                                                        | $t_{\text{R},\text{A}\rightarrow\text{Y}}$                                      |                                                            |     | 2.5              | 4    | ns  |

| Fall Time                                                                                                                                       | $t_{F\!,A\to Y}$                                                                |                                                            |     | 2                | 5    | ns  |

| Maximum Data Rate                                                                                                                               | Dмах, а→Y                                                                       |                                                            | 60  |                  |      | Mb  |

| Part-to-Part Skew                                                                                                                               | $t_{\text{PPSKEW}, A \rightarrow Y}$                                            |                                                            |     |                  | 4    | ns  |

| $Y \rightarrow A$ Translation                                                                                                                   |                                                                                 | $R_s = R_T = 50 \Omega$ , $C_L = 15 pF$ ,<br>see Figure 36 |     |                  |      |     |

| Propagation Delay                                                                                                                               | t <sub>P,Y→A</sub>                                                              |                                                            |     | 5                | 8    | ns  |

| Rise Time                                                                                                                                       | t <sub>R,Y→A</sub>                                                              |                                                            |     | 1                | 4    | ns  |

| Fall Time                                                                                                                                       | t <sub>F,Y→A</sub>                                                              |                                                            |     | 3                | 5    | ns  |

| Maximum Data Rate                                                                                                                               | D <sub>мах, у→А</sub>                                                           |                                                            | 60  |                  |      | Mb  |

| Part-to-Part Skew                                                                                                                               | $t_{\text{PPSKEW}, Y \rightarrow A}$                                            |                                                            |     |                  | 3    | ns  |

| Parameter <sup>1</sup>                | Symbol            | Conditions                                                                | Min  | Typ <sup>2</sup> | Max | Unit |

|---------------------------------------|-------------------|---------------------------------------------------------------------------|------|------------------|-----|------|

| POWER REQUIREMENTS                    |                   |                                                                           |      |                  |     |      |

| Power Supply Voltages                 | VCCA              | V <sub>CCA</sub> ≤ V <sub>CCY</sub>                                       | 1.15 |                  | 5.5 | V    |

|                                       | Vccy              |                                                                           | 1.65 |                  | 5.5 | V    |

| Quiescent Power Supply Current        | ICCA              | $V_A = 0 V/V_{CCA}, V_Y = 0 V/V_{CCY}, V_{CCA} = V_{CCY} = 5.5 V, EN = 1$ |      | 0.17             | 5   | μΑ   |

|                                       | Іссч              | $V_A = 0 V/V_{CCA}, V_Y = 0 V/V_{CCY}, V_{CCA} = V_{CCY} = 5.5 V, EN = 1$ |      | 0.27             | 5   | μΑ   |

| Three-State Mode Power Supply Current | I <sub>HiZA</sub> | $V_{CCA} = V_{CCY} = 5.5 \text{ V}, \text{ EN} = 0$                       |      | 0.1              | 5   | μA   |

|                                       | <b>I</b> HiZY     | $V_{CCA} = V_{CCY} = 5.5 \text{ V}, \text{ EN} = 0$                       |      | 0.1              | 5   | μΑ   |

<sup>1</sup> Temperature range for the B version is  $-40^{\circ}$ C to  $+85^{\circ}$ C. <sup>2</sup> All typical values are at T<sub>A</sub> = 25°C, unless otherwise noted. <sup>3</sup> Guaranteed by design, not subject to production test.

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

### Table 2.

| Parameter                                       | Rating                             |

|-------------------------------------------------|------------------------------------|

| V <sub>CCA</sub> to GND                         | –0.3 V to +7 V                     |

| V <sub>CCY</sub> to GND                         | V <sub>CCA</sub> to +7 V           |

| Digital Inputs (A)                              | $-0.3$ V to V_{CCA} + 0.3 V        |

| Digital Inputs (Y)                              | -0.3 V to V <sub>CCY</sub> + 0.3 V |

| EN to GND                                       | –0.3 V to +7 V                     |

| Operating Temperature Range                     |                                    |

| Industrial (B Version)                          | -40°C to +85°C                     |

| Storage Temperature Range                       | –65°C to +150°C                    |

| Junction Temperature                            | 150°C                              |

| $\theta_{JA}$ Thermal Impedance (4-Layer Board) |                                    |

| 6-Lead SC70                                     | 494.1°C/W                          |

| Lead Temperature, Soldering (10 sec)            | 300°C                              |

| IR Reflow, Peak Temperature (< 20 sec)          | 260(+0/-5)°C                       |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Only one absolute maximum rating may be applied at any one time.

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

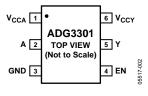

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 2. Pin Configuration

### **Table 3. Pin Function Descriptions**

| Pin No. | Mnemonic         | Description                                                                                             |

|---------|------------------|---------------------------------------------------------------------------------------------------------|

| 1       | V <sub>CCA</sub> | Power Supply Voltage Input for the A I/O Pin (1.15 V $\leq$ V <sub>CCA</sub> $\leq$ V <sub>CCY</sub> ). |

| 2       | А                | Input/Output A. Referenced to V <sub>CCA</sub> .                                                        |

| 3       | GND              | Ground (0 V).                                                                                           |

| 4       | EN               | Active High Enable Input.                                                                               |

| 5       | Y                | Input/Output Y. Referenced to V <sub>CCY</sub> .                                                        |

| 6       | Vccy             | Power Supply Voltage Input for the Y I/O Pin (1.65 V $\leq$ V <sub>CCY</sub> $\leq$ 5.5V).              |

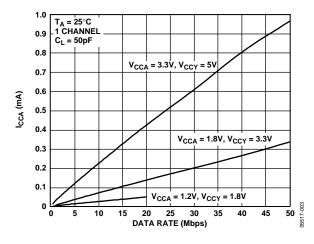

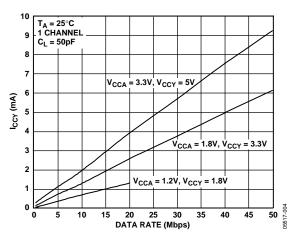

# **TYPICAL PERFORMANCE CHARACTERISTICS**

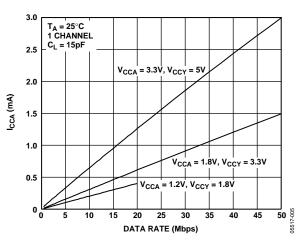

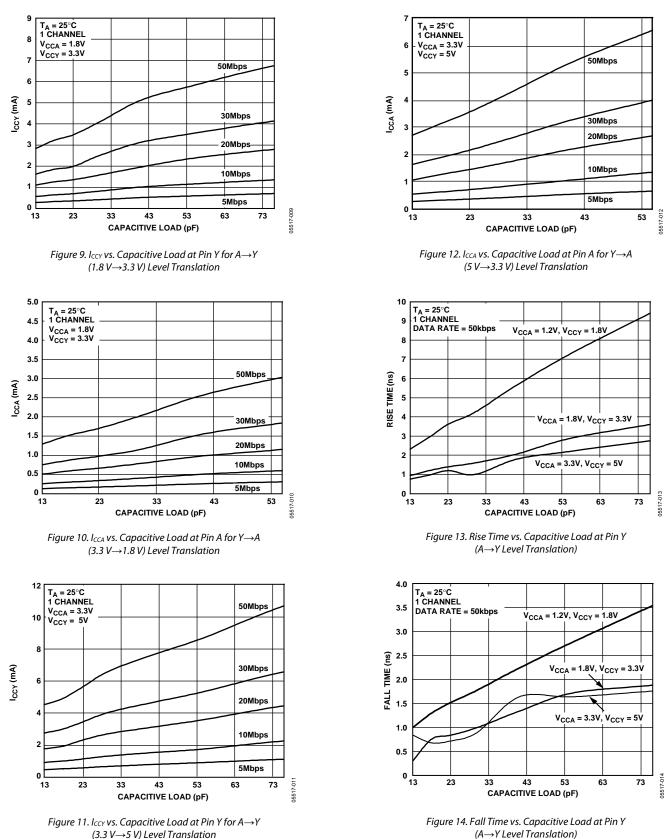

Figure 3.  $I_{CCA}$  vs. Data Rate (A $\rightarrow$ Y Level Translation)

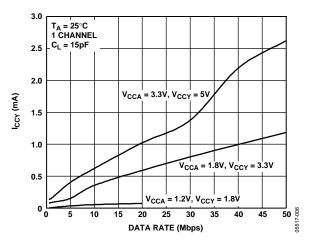

Figure 4.  $I_{CCY}$  vs. Data Rate (A $\rightarrow$ Y Level Translation)

Figure 5.  $I_{CCA}$  vs. Data Rate (Y $\rightarrow$ A Level Translation)

Figure 6.  $I_{CCY}$  vs. Data Rate (Y $\rightarrow$ A Level Translation)

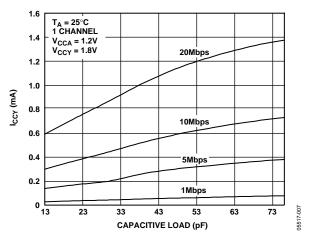

Figure 7.  $I_{CCY}$  vs. Capacitive Load at Pin Y for  $A \rightarrow Y$ (1.2  $V \rightarrow$  1.8 V) Level Translation

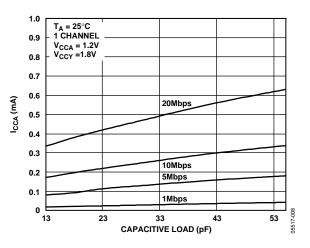

Figure 8. I<sub>CCA</sub> vs. Capacitive Load at Pin A for Y $\rightarrow$ A (1.8 V $\rightarrow$ 1.2 V) Level Translation

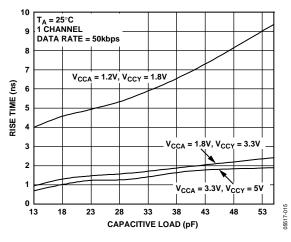

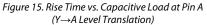

$(3.3 V \rightarrow 5 V)$  Level Translation

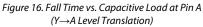

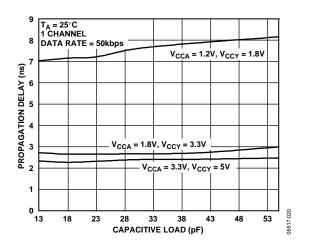

Figure 17. Propagation Delay  $(t_{PLH})$  vs. Capacitive Load at Pin Y  $(A \rightarrow Y Level Translation)$

Figure 18. Propagation Delay  $(t_{PHL})$  vs. Capacitive Load at Pin Y  $(A \rightarrow Y Level Translation)$

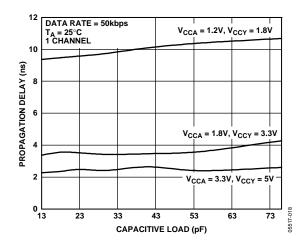

Figure 19. Propagation Delay  $(t_{PLH})$  vs. Capacitive Load at Pin A (Y $\rightarrow$ A Level Translation)

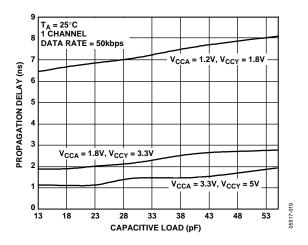

Figure 20. Propagation Delay  $(t_{PHL})$  vs. Capacitive Load at Pin A  $(Y \rightarrow A \text{ Level Translation})$

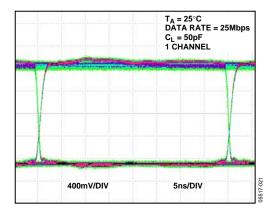

Figure 21. Eye Diagram at Y Output (1.2 V to 1.8 V Level Translation, 25 Mbps)

Figure 22. Eye Diagram at A Output (1.8 V to 1.2 V Level Translation, 25 Mbps)

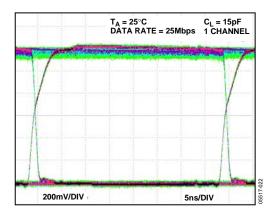

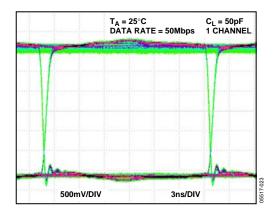

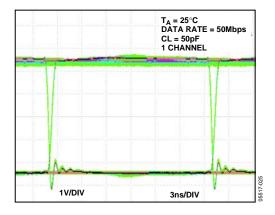

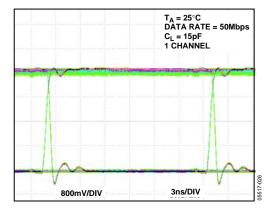

Figure 23. Eye Diagram at Y Output (1.8 V to 3.3 V Level Translation, 50 Mbps)

Figure 24. Eye Diagram at A Output (3.3 V to 1.8 V Level Translation, 50 Mbps)

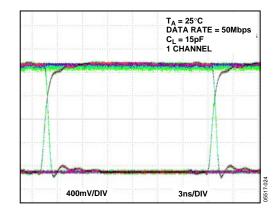

Figure 25. Eye Diagram at Y Output (3.3 V to 5 V Level Translation, 50 Mbps)

Figure 26. Eye Diagram at A Output (5 V to 3.3 V Level Translation, 50 Mbps)

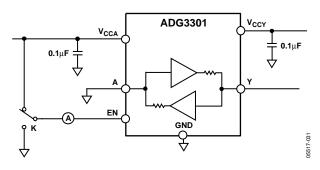

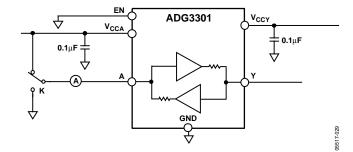

# **TEST CIRCUITS**

Figure 27. VOH/VOL Voltages at Pin A

Figure 28. VOH/VOL Voltages at Pin Y

Figure 30. Three-State Leakage Current at Pin Y

Figure 31. EN Pin Leakage Current

Figure 29. Three-State Leakage Current at Pin A

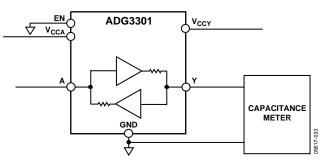

Figure 33. Capacitance at Pin Y

Figure 32. Capacitance at Pin A

### A→Y DIRECTION VCCA V<sub>CCY</sub> ADG3301 <u></u>+<sup>‡</sup>10μF **#**10μF **0.1**μ **0.1**μF **1M**Ω q VA A **K**1 K2 50pF Ĵ ↓ 1ΜΩ ↓ ↓ SIGNAL SOURCE 4 GND EN R<sub>S</sub> 50Ω **50**Ω VEN $\diamond$ $\nabla$ **(П**) $\uparrow$

Figure 34. Enable Time

05517-034

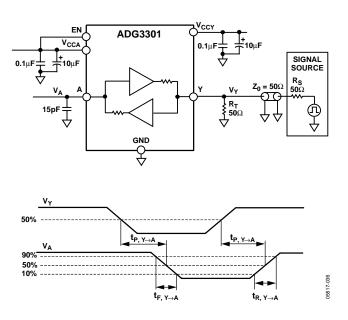

Figure 35. Switching Characteristics ( $A \rightarrow Y$  Level Translation)

Figure 36. Switching Characteristics ( $Y \rightarrow A$  Level Translation)

## TERMINOLOGY

V<sub>IHA</sub> Logic input high voltage at Pin A.

VILA Logic input low voltage at Pin A.

Vона Logic output high voltage at Pin A.

Vola Logic output low voltage at Pin A.

$C_A$ Capacitance measured at Pin A (EN = 0).

$I_{LA, HiZ}$ Leakage current at Pin A when EN = 0 (Pin A three-stated).

V<sub>IHY</sub> Logic input high voltage at Pin Y.

V<sub>ILY</sub> Logic input low voltage at Pin Y.

V<sub>ону</sub> Logic output high voltage at Pin Y.

V<sub>OLY</sub> Logic output low voltage at Pin Y.

$C_{Y}$ Capacitance measured at Pin Y (EN = 0).

$I_{LY, HiZ}$ Leakage current at pin and when EN = 0 (Pin A three-stated).

$\ensuremath{\mathbf{V}}_{\ensuremath{\mathsf{IHEN}}}$  Logic input high voltage at the EN pin.

$V_{\mbox{\scriptsize ILEN}}$  Logic input low voltage at the EN pin.

$C_{\mbox{\scriptsize EN}}$  Capacitance measured at EN pin.

I<sub>LEN</sub> Enable (EN) pin leakage current.

t<sub>EN</sub> Three-state enable time for Pin A and Pin Y.

$\mathbf{t}_{P,A \rightarrow Y}$ Propagation delay when translating logic levels in the A $\rightarrow$ Y direction.  $t_{R,\,A \rightarrow Y}$  Rise time when translating logic levels in the A—Y direction.

$t_{F,\,A \rightarrow Y}$  Fall time when translating logic levels in the A—Y direction.

### $\mathbf{D}_{\text{MAX}, A \rightarrow Y}$

Guaranteed data rate when translating logic levels in the  $A \rightarrow Y$  direction under the driving and loading conditions specified in Table 1.

### $\mathbf{t}_{\text{PPSKEW, A} \rightarrow Y}$

Difference in propagation delay between any one channel and the same channel on a different part (under same driving/loading conditions) when translating in the  $A \rightarrow Y$  direction.

$t_{P,\,Y \rightarrow A}$  Propagation delay when translating logic levels in the Y  ${\rightarrow}\,A$  direction.

$t_{R, \, Y \not \rightarrow A}$  Rise time when translating logic levels in the Y  $\longrightarrow A$  direction.

$t_{F,\,Y \ni A}$  Fall time when translating logic levels in the Y  $\rightarrow$  A direction.

$D_{MAX, Y \rightarrow A}$ Guaranteed data rate when translating logic levels in the Y $\rightarrow$ A direction under the driving and loading conditions specified in Table 1.

### **t**<sub>PPSKEW, Y→A</sub> Difference in propagation delay between any one channel and the same channel on a different part (under the same driving/ loading conditions) when translating in the Y→A direction.

$I_{CCA}$ V<sub>CCA</sub> supply current.

$I_{CCY}$ V<sub>CCY</sub> supply current.

$I_{HiZA}$ V<sub>CCA</sub> supply current during three-state mode (EN = 0).

$I_{\rm HiZY}$   $V_{\rm CCY}$  supply current during three-state mode (EN = 0).

# THEORY OF OPERATION

The ADG3301 level translator allows the level shifting necessary for data transfer in a system where multiple supply voltages are used. The device requires two supplies,  $V_{CCA}$  and  $V_{CCY}$  ( $V_{CCA} \leq V_{CCY}$ ). These supplies set the logic levels on each side of the device. When driving the A pin, the device translates the  $V_{CCA}$ -compatible logic levels to  $V_{CCY}$ -compatible logic levels to  $V_{CCY}$ -compatible logic levels to  $V_{CCA}$ -compatible logic levels available at the Y pin. Similarly, because the device is capable of bidirectional translation, when driving the Y pin the  $V_{CCY}$ -compatible logic levels are translated to  $V_{CCA}$ -compatible logic levels available at the A pin. When EN = 0, the A pin and the Y pin are three-stated. When EN is driven high, the ADG3301 goes into normal operation mode and performs level translation.

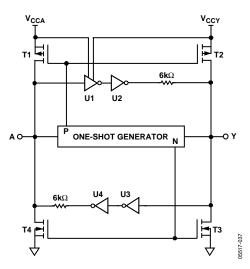

### LEVEL TRANSLATOR ARCHITECTURE

The ADG3301 consists of a single bidirectional channel that can translate logic levels in either the  $A \rightarrow Y$  or the  $Y \rightarrow A$  direction. It uses a one-shot accelerator architecture that ensures excellent switching characteristics. Figure 37 shows a simplified block diagram of the ADG3301 level translator.

Figure 37. Simplified Block Diagram of an ADG3301 Channel

The logic level translation in the  $A \rightarrow Y$  direction is performed using a level translator (U1) and an inverter (U2), while the translation in the  $Y \rightarrow A$  direction is performed using the inverters U3 and U4. The one-shot generator detects a rising or falling edge present on either the A side or the Y side of the channel. It sends a short pulse that turns on the PMOS transistors (T1 and T2) for a rising edge, or the NMOS transistors (T3 and T4) for a falling edge. This charges/discharges the capacitive load faster, which results in fast rise and fall times.

### **INPUT DRIVING REQUIREMENTS**

To ensure correct operation of the ADG3301, the circuit that drives the input of an ADG3301 channel must have an output impedance of less than or equal to 150  $\Omega$  and a minimum peak current driving capability of 36 mA.

### **OUTPUT LOAD REQUIREMENTS**

The ADG3301 level translator is designed to drive CMOScompatible loads. If current driving capability is required, it is recommended to use buffers between the ADG3301 outputs and the load.

### **ENABLE OPERATION**

The ADG3301 provides three-state operation at the A I/O pin and Y I/O pin by using the enable (EN) pin as shown in Table 4.

Table 4. Truth Table

| EN | Y I/O Pin                     | A I/O Pin                     |

|----|-------------------------------|-------------------------------|

| 0  | Hi-Z <sup>1</sup>             | Hi-Z <sup>1</sup>             |

| 1  | Normal operation <sup>2</sup> | Normal operation <sup>2</sup> |

<sup>1</sup> High impedance state.

<sup>2</sup> In normal operation, the ADG3301 performs level translation.

While EN = 0, the ADG3301 enters into tri-state mode. In this mode, the current consumption from both the  $V_{CCA}$  and  $V_{CCY}$  supplies is reduced, allowing the user to save power, which is critical especially on battery-operated systems. The EN input pin can be driven with either  $V_{CCA}$ - or  $V_{CCY}$ -compatible logic levels.

### **POWER SUPPLIES**

For proper operation of the ADG3301, the voltage applied to the  $V_{CCA}$  must be always less than or equal to the voltage applied to  $V_{CCY}$ . To meet this condition, the recommended power-up sequence is  $V_{CCY}$  first and then  $V_{CCA}$ . The ADG3301 operates properly only after both supply voltages reach their nominal values. It is not recommended to use the part in a system where, during power-up,  $V_{CCA}$  may be greater than  $V_{CCY}$  due to a significant increase in the current taken from the  $V_{CCA}$  supply For optimum performance, the  $V_{CCA}$  and  $V_{CCY}$  pins should be decoupled to GND, and placed as close as possible to the device.

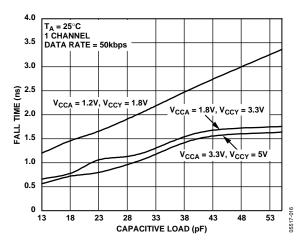

### DATA RATE

The maximum data rate at which the device is guaranteed to operate is a function of the  $V_{\rm CCA}$  and  $V_{\rm CCY}$  supply voltage combination and the load capacitance. It represents the maximum frequency of a square wave that can be applied to the I/O pins, which ensures that the device operates within the datasheet specifications in terms of output voltage ( $V_{\rm OL}$  and  $V_{\rm OH}$ ) and

power dissipation (the junction temperature does not exceed the value specified under the Absolute Maximum Ratings section).

Table 5 shows the guaranteed data rates at which the ADG3301 can operate in both directions (A $\rightarrow$ Y or Y $\rightarrow$ A level translation) for various V<sub>CCA</sub> and V<sub>CCY</sub> supply combinations.

### Table 5. Guaranteed Data Rate (Mbps)<sup>1</sup>

|                          | Vccy                        |                           |                           |                         |  |  |

|--------------------------|-----------------------------|---------------------------|---------------------------|-------------------------|--|--|

| Vcca                     | 1.8 V<br>(1.65 V to 1.95 V) | 2.5 V<br>(2.3 V to 2.7 V) | 3.3 V<br>(3.0 V to 3.6 V) | 5 V<br>(4.5 V to 5.5 V) |  |  |

| 1.2 V (1.15 V to 1.3 V)  | 25                          | 30                        | 40                        | 40                      |  |  |

| 1.8 V (1.65 V to 1.95 V) | -                           | 45                        | 50                        | 50                      |  |  |

| 2.5 V (2.3 V to 2.7 V)   | _                           | -                         | 60                        | 50                      |  |  |

| 3.3 V (3.0 V to 3.6 V)   | -                           | -                         | -                         | 50                      |  |  |

| 5 V (4.5 V to 5.5 V)     | -                           | -                         | -                         | -                       |  |  |

$^{1}$  The load capacitance used is 50 pF when translating in the A $\rightarrow$ Y direction and 15 pF when translating in the Y $\rightarrow$ A direction.

# **APPLICATIONS**

The ADG3301 is designed for digital circuits that operate at different supply voltages; therefore, logic level translation is required. The lower voltage logic signals are connected to the A pin, and the higher voltage logic signals are connected to the Y pin. The ADG3301 can provide level translation in both directions from  $A \rightarrow Y$  or  $Y \rightarrow A$ , eliminating the need for a level translator IC for each direction. The internal architecture allows the ADG3301 to perform bidirectional level translation without an additional signal to set the direction in which the translation is made. This simplifies the design by eliminating the timing requirements for the direction signal and reduces the number of ICs used for level translation.

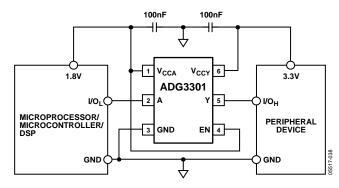

Figure 38 shows an application where a 1.8 V microprocessor transfers data to or from a 3.3 V peripheral device using the ADG3301 level translator.

Figure 38 1.8 V to 3.3 V Level Translation Circuit

### LAYOUT GUIDELINES

As with any high speed digital IC, the printed circuit board layout is important for the overall performance of the circuit. Care should be taken to ensure proper power supply bypass and return paths for the high speed signals. Each  $V_{CC}$  pin ( $V_{CCA}$  and  $V_{CCY}$ ) should be bypassed using low effective series resistance (ESR) and effective series inductance (ESI) capacitors placed as close as possible to the  $V_{CCA}$  and  $V_{CCY}$  pins. The parasitic inductance of the high-speed signal track might cause significant overshoot. This effect can be reduced by keeping the length of the tracks as short as possible. A solid copper plane for the return path (GND) is also recommended.

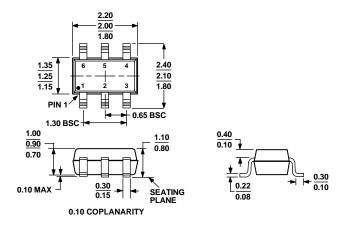

# **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-203-AB

Figure 39. 6-Lead Thin Shrink Small Outline Transistor Package [SC70] (KS-6) Dimensions shown in millimeters

### **ORDERING GUIDE**

| Model                          | Temperature Range | Package Description                                 | Branding <sup>1</sup> | Package Option |

|--------------------------------|-------------------|-----------------------------------------------------|-----------------------|----------------|

| ADG3301BKSZ-REEL <sup>2</sup>  | -40°C to +85°C    | 6-Lead Thin Shrink Small Outline Transistor Package | SOH                   | KS-6           |

| ADG3301BKSZ-REEL7 <sup>2</sup> | -40°C to +85°C    | 6-Lead Thin Shrink Small Outline Transistor Package | SOH                   | KS-6           |

<sup>1</sup> Branding on this package is limited to three characters due to space constraints.

$^{2}$  Z = Pb-free part.

# NOTES

© 2005 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D05517-0-12/05(0)

www.analog.com

Downloaded from Arrow.com.