Data sheet

# **BMM150**Geomagnetic Sensor

**Bosch Sensortec**

#### BMM150: Data sheet

Document revision 1.3

Document release date October 2019

Document number BST-BMM150-DS001-04

Technical reference code(s) 0 273 141 157

Notes Data in this document are subject to change without notice. Product

photos and pictures are for illustration purposes only and may differ from

the real product's appearance.

Page 2

#### **BMM150**

#### THREE-AXIS GEOMAGNETIC SENSOR

#### **Key features**

Three-axis magnetic field sensor

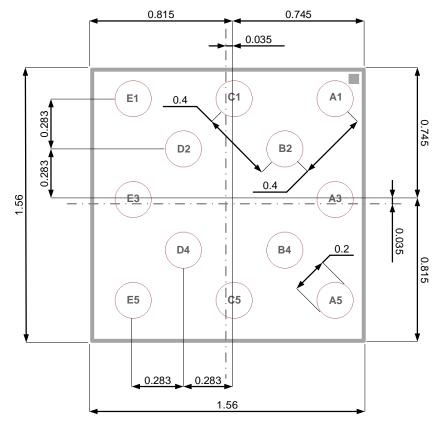

• Ultra-Small package Wafer Level Chip Scale Package

(12 pins, 0.4mm diagonal ball pitch) footprint 1.56 x 1.56 mm<sup>2</sup>, height 0.6 mm

Digital interface

SPI (4-wire, 3-wire), I<sup>2</sup>C, 4, 2 interrupt pins

Low voltage operation

V<sub>DD</sub> supply voltage range: 1.62V to 3.6V

V<sub>DDIO</sub> interface voltage range: 1.2V to 3.6V

Flexible functionality

Magnetic field range typical:

±1300μT (x, y-axis), ±2500μT (z-axis) Magnetic field resolution of ~0.3μT

On-chip interrupt controller

Interrupt-signal generation for

- new data

- magnetic Low-/High-Threshold detection

Ultra-low power

Low current consumption (170μA @ 10 Hz in low power

preset), short wake-up time, advanced features for system

power management

Temperature range -40 °C ... +85 °C

· RoHS compliant, halogen-free

#### **Typical applications**

- Magnetic heading information

- Tilt-compensated electronic compass for map rotation, navigation and augmented reality

- Gyroscope calibration in 9-DoF applications for mobile devices

- In-door navigation, e.g. step counting in combination accelerometer

- Gaming

Page 3

#### **General Description**

The BMM150 is a standalone geomagnetic sensor for consumer market applications. It allows measurements of the magnetic field in three perpendicular axes. Based on Bosch's proprietary FlipCore technology, performance and features of BMM150 are carefully tuned and perfectly match the demanding requirements of all 3-axis mobile applications such as electronic compass, navigation or augmented reality.

An evaluation circuitry (ASIC) converts the output of the geomagnetic sensor to digital results which can be read out over the industry standard digital interfaces (SPI and I2C).

Package and interfaces of the BMM150 have been designed to match a multitude of hardware requirements. As the sensor features an ultra-small footprint and a flat package, it is ingeniously suited for mobile applications. The wafer level chip scale package (WLCSP) with dimensions of only  $1.56 \times 1.56 \times 0.6 \text{ mm}^3$  ensures high flexibility in PCB placement.

The BMM150 offers ultra-low voltage operation ( $V_{DD}$  voltage range from 1.62V to 3.6V,  $V_{DDIO}$  voltage range 1.2V to 3.6V) and can be programmed to optimize functionality, performance and power consumption in customer specific applications. The programmable interrupt engine gives design flexibility to the developer.

The BMM150 senses the three axis of the terrestrial field in cell phones, handhelds, computer peripherals, man-machine interfaces, virtual reality features and game controllers.

## **Index of Contents**

| 1 | . SPECIFICATION                                                                  | 6                    |

|---|----------------------------------------------------------------------------------|----------------------|

|   | 1.1 ELECTRICAL OPERATION CONDITIONS                                              | 6                    |

|   | 1.2 MAGNETOMETER OUTPUT SIGNAL SPECIFICATION                                     | 7                    |

| 2 | . ABSOLUTE MAXIMUM RATINGS                                                       | 9                    |

| 3 | . BLOCK DIAGRAM                                                                  | 10                   |

| 4 | . FUNCTIONAL DESCRIPTION                                                         | 11                   |

|   | 4.1 POWER MANAGEMENT                                                             | . 11                 |

|   | 4.2 POWER MODES                                                                  | . 11                 |

|   | 4.2.1 POWER OFF MODE 4.2.2 SUSPEND MODE 4.2.3 SLEEP MODE 4.2.4 ACTIVE MODE       | 11<br>12             |

|   | 4.3 Sensor output data                                                           | . 14                 |

|   | 4.3.1 Magnetic field data                                                        |                      |

|   | 4.4 Self-test                                                                    | . 16                 |

|   | 4.4.1 NORMAL SELF TEST                                                           |                      |

|   | 4.5 Non-volatile memory                                                          | . 17                 |

|   | 4.6 MAGNETOMETER INTERRUPT CONTROLLER                                            | . 17                 |

|   | 4.6.1 GENERAL FEATURES                                                           | 18<br>19<br>19<br>21 |

| 5 | . REGISTER DESCRIPTION                                                           | 22                   |

|   | 5.1 GENERAL REMARKS                                                              | . 22                 |

|   | 5.2 REGISTER MAP                                                                 | . 22                 |

|   | 5.3 CHIP ID                                                                      | . 23                 |

|   | 5.4 MAGNETIC FIELD DATA                                                          | . 23                 |

|   | 5.5 Interrupt status register                                                    | . 26                 |

|   | 5.6 POWER AND OPERATION MODES, SELF-TEST AND DATA OUTPUT RATE CONTROL REGISTERS. | . 26                 |

|   | 5.7 Interrupt and axis enable settings control registers                         | . 28                 |

|   | 5.8 Number of repetitions control registers                                      | .30                  |

Page 5

| 6. DIGITAL INTERFACES                           | 32 |

|-------------------------------------------------|----|

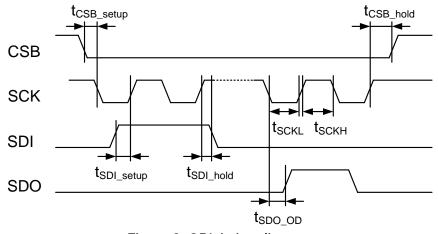

| 6.1 SERIAL PERIPHERAL INTERFACE (SPI)           | 33 |

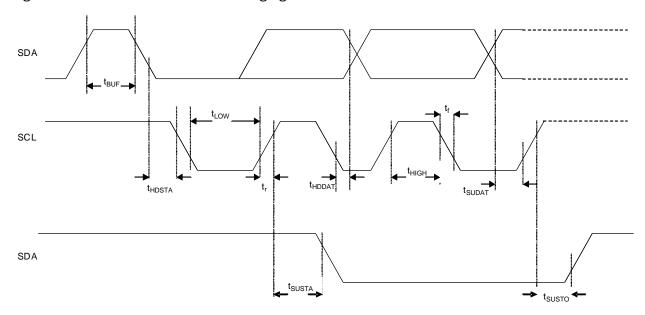

| 6.2 Inter-Integrated Circuit (I <sup>2</sup> C) | 36 |

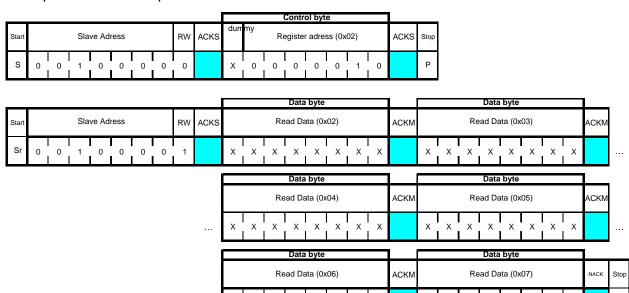

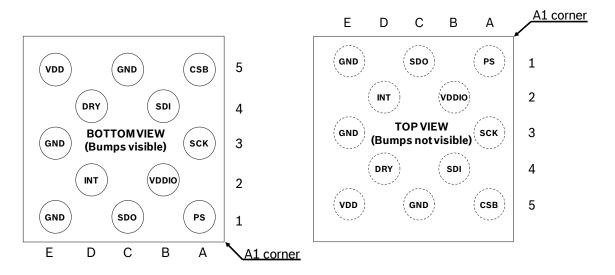

| 7. PIN-OUT AND CONNECTION DIAGRAM               | 41 |

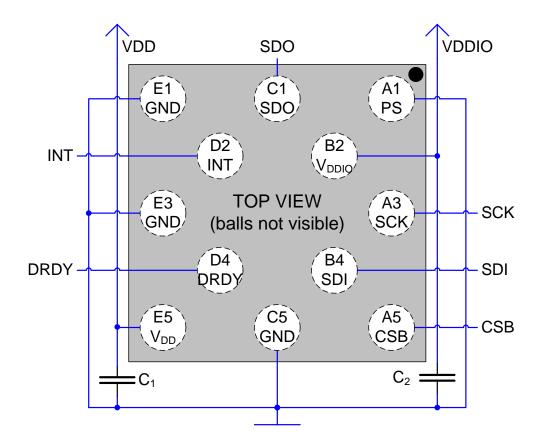

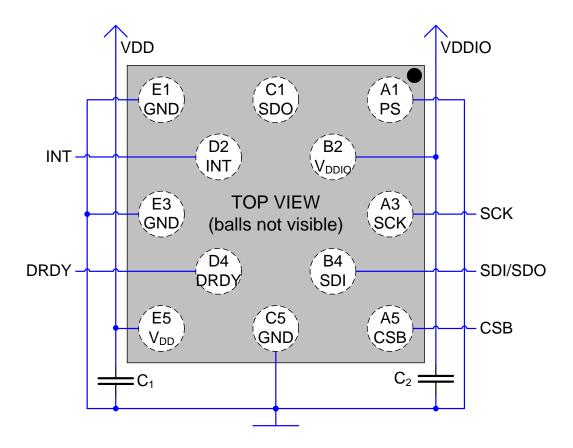

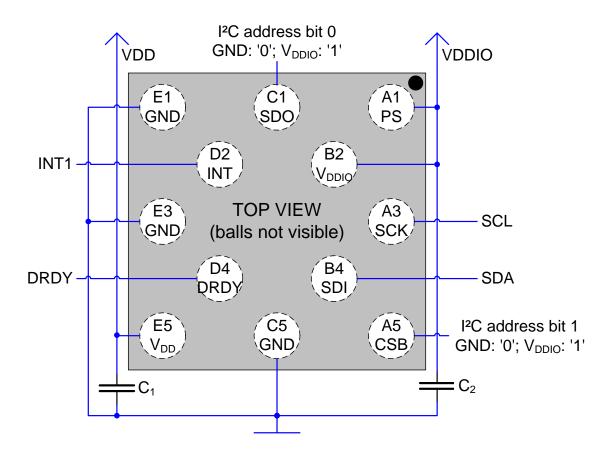

| 7.1 PIN-OUT                                     | 41 |

| 7.2 CONNECTION DIAGRAM 4-WIRE SPI               | 42 |

| 7.3 CONNECTION DIAGRAM 3-WIRE SPI               | 43 |

| 7.4 CONNECTION DIAGRAM I <sup>2</sup> C         | 44 |

| 8. PACKAGE                                      | 45 |

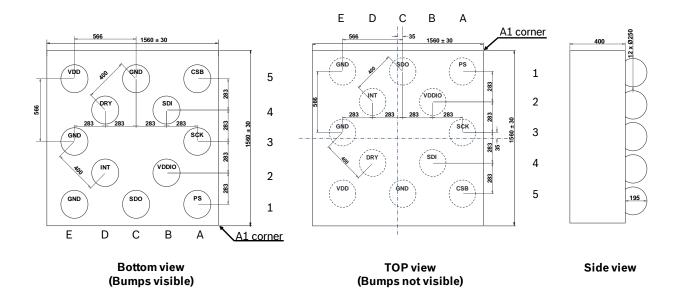

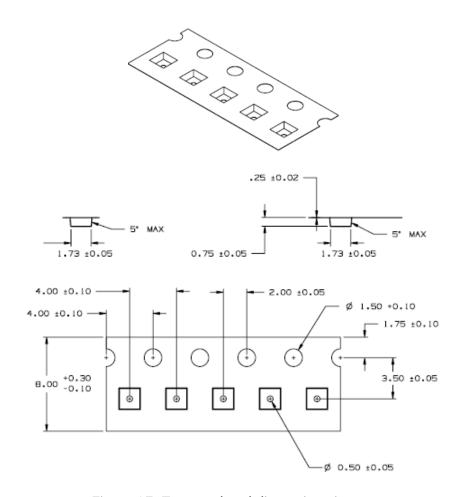

| 8.1 OUTLINE DIMENSIONS                          | 45 |

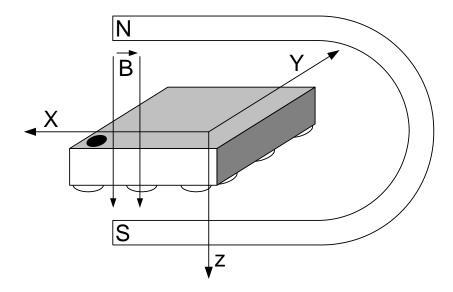

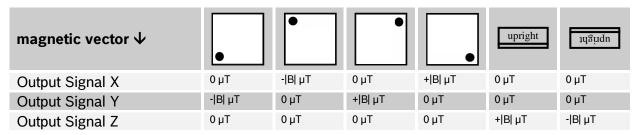

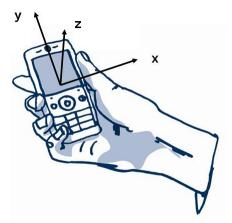

| 8.2 SENSING AXES ORIENTATION                    | 46 |

| 8.3 Android axes orientation                    | 47 |

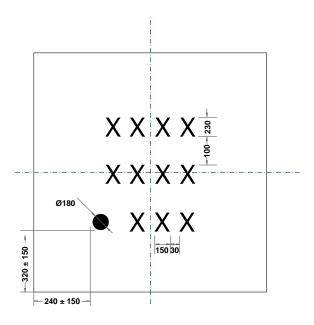

| 8.4 LANDING PATTERN RECOMMENDATION              | 48 |

| 8.5 Marking                                     | 49 |

| 8.5.1 Mass production devices                   |    |

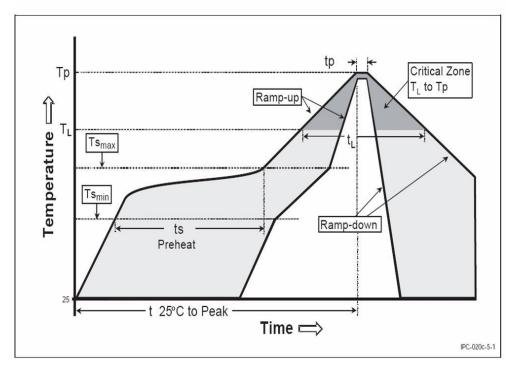

| 8.6 SOLDERING GUIDELINES                        | 51 |

| 8.7 HANDLING INSTRUCTIONS                       | 52 |

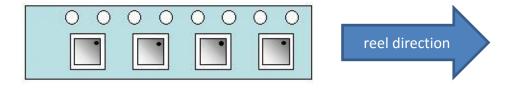

| 8.8 TAPE AND REEL SPECIFICATION                 | 53 |

| 8.8.1 Tape and reel dimensions                  |    |

| 8.9 Environmental safety                        | 54 |

| 8.9.1 HALOGEN CONTENT                           |    |

| 9. LEGAL DISCLAIMER                             | 55 |

| 9.1 Engineering samples                         | 55 |

| 9.2 PRODUCT USE                                 | 55 |

| 9.3 APPLICATION EXAMPLES AND HINTS              | 55 |

| 10. DOCUMENT HISTORY AND MODIFICATION           | 56 |

Page 6

## 1. Specification

If not stated otherwise, the given values are over lifetime and full performance temperature and voltage ranges, minimum/maximum values are  $\pm 3\sigma$ .

#### 1.1 Electrical operation conditions

Table 1: Electrical parameter specification

| OPERATING CONDITIONS                                       |                        |                                                                                   |                      |       |                      |      |  |

|------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------|----------------------|-------|----------------------|------|--|

|                                                            |                        |                                                                                   |                      |       |                      |      |  |

| Parameter                                                  | Symbol                 | Condition                                                                         | Min                  | Тур   | Max                  | Unit |  |

| Supply Voltage<br>Internal Domains                         | $V_{DD}$               |                                                                                   | 1.62                 | 2.4   | 3.6                  | V    |  |

| Supply Voltage I/O Domain                                  | $V_{DDIO}$             |                                                                                   | 1.2                  | 1.8   | 3.6                  | V    |  |

| Voltage Input<br>Low Level                                 | $V_{IL,a}$             | SPI & I <sup>2</sup> C                                                            |                      |       | 0.3V <sub>DDIO</sub> | -    |  |

| Voltage Input<br>High Level                                | $V_{IH,a}$             | SPI & I <sup>2</sup> C                                                            | $0.7V_{DDIO}$        |       |                      | -    |  |

| Voltage Output<br>Low Level                                | V <sub>OL</sub>        | $V_{DDIO} = 1.2V$<br>$I_{OL} = 3mA, SPI \& I^2C$                                  |                      |       | 0.2V <sub>DDIO</sub> | -    |  |

| Voltage Output<br>High Level                               | $V_{OH}$               | $V_{DDIO}$ = 1.62V $I_{OH}$ = 2mA, SPI & I <sup>2</sup> C                         | 0.8V <sub>DDIO</sub> |       |                      | -    |  |

| Magnetic field                                             | $B_{rg,xy}$            | $T_A=25^{\circ}C^1$                                                               | ±1200                | ±1300 |                      | μΤ   |  |

| range                                                      | $B_{rg,z}$             |                                                                                   | ±2000                | ±2500 |                      | μΤ   |  |

| Magnetometer heading accuracy                              | ACheading              | 30µT horizontal<br>geomagnetic field<br>component,<br>T <sub>A</sub> =25°C        |                      |       | ±2.5                 | deg  |  |

|                                                            | $I_{\mathrm{DD,lp,m}}$ | Low power preset Nominal $V_{DD}$ supplies $T_A$ =25°C, ODR=10Hz                  |                      | 170   |                      | μА   |  |

| Supply Current in<br>Active Mode<br>(average) <sup>3</sup> | $I_{\mathrm{DD,rg,m}}$ | Regular preset  Nominal V <sub>DD</sub> supplies  T <sub>A</sub> =25°C,  ODR=10Hz |                      | 0.5   |                      | mA   |  |

|                                                            | I <sub>DD,eh,m</sub>   | Enhanced regular<br>preset<br>Nominal V <sub>DD</sub><br>supplies                 |                      | 0.8   |                      | mA   |  |

<sup>&</sup>lt;sup>1</sup> Full linear measurement range considering sensor offsets.

-

<sup>&</sup>lt;sup>2</sup> The heading accuracy depends on hardware and software. A fully calibrated sensor and ideal tilt compensation are assumed.

<sup>&</sup>lt;sup>3</sup> For details on magnetometer current consumption calculation refer to chapter 4.2.1 and 4.2.2.

Page 7

|                                          |                       | T <sub>A</sub> =25°C,<br>ODR=10Hz                                                                    |     |     |    |

|------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------|-----|-----|----|

|                                          | I <sub>DD,ha,m</sub>  | High accuracy<br>preset<br>Nominal V <sub>DD</sub><br>supplies<br>T <sub>A</sub> =25°C,<br>ODR=20Hz  | 4.9 |     | mA |

| Supply Current in<br>Suspend Mode        | I <sub>DDsm,m</sub>   | Nominal $V_{DD}/V_{DDIO}$ supplies, $T_A$ =25°C                                                      | 1   | 3   | μΑ |

| Peak supply<br>current in Active<br>Mode | $I_{\mathrm{DDpk,m}}$ | In measurement<br>phase<br>Nominal V <sub>DD</sub><br>supplies<br>T <sub>A</sub> =25°C               | 18  | 20  | mA |

| Peak logic supply current in active mode | $I_{ m DDIOpk,m}$     | Only during<br>measurement<br>phase<br>Nominal V <sub>DDIO</sub><br>supplies<br>T <sub>A</sub> =25°C | 210 | 270 | μА |

| POR time                                 | t <sub>w_up,m</sub>   | from OFF to Suspend; time starts when VDD>1.5V and VDDIO>1.1V                                        |     | 1.0 | ms |

| Start-Up Time                            | t <sub>s_up,m</sub>   | from Suspend to sleep                                                                                |     | 3.0 | ms |

## 1.2 Magnetometer output signal specification

| MAGNETOMETER OUTPUT SIGNAL          |                    |                                                                                                            |     |       |       |      |  |  |

|-------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------|-----|-------|-------|------|--|--|

| Parameter                           | Symbol             | Condition                                                                                                  | Min | Тур   | Max   | Unit |  |  |

| Device<br>Resolution                | D <sub>res,m</sub> | T <sub>A</sub> =25°C                                                                                       |     | 0.3   |       | μΤ   |  |  |

| Gain error <sup>4</sup>             | G <sub>err,m</sub> | After API compensation $T_A=25^{\circ}C$ Nominal $V_{DD}$ supplies                                         |     | ±2    | ±5    | %    |  |  |

| Sensitivity<br>Temperature<br>Drift | TCS <sub>m</sub>   | After API compensation $-40^{\circ}\text{C} \leq T_{A} \leq +85^{\circ}\text{C}$ Nominal $V_{DD}$ supplies |     | ±0.01 | ±0.03 | %/K  |  |  |

| Zero-B offset                       | OFFm               | T <sub>A</sub> =25°C                                                                                       |     | ±40   |       | μΤ   |  |  |

<sup>&</sup>lt;sup>4</sup> Definition: gain error = ( (measured field after API compensation) / (applied field) ) - 1

BST-BMM150-DS001-04 | Revision 1.3 | October 2019

Bosch Sensortec

Page 8

| Zero-B offset                  | OFF <sub>m,cal</sub>     | After software calibration with Bosch Sensortec eCompass software <sup>5</sup> $-40^{\circ}\text{C} \leq T_{A} \leq +85^{\circ}\text{C}$ |     | ±2   |      | μΤ   |

|--------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| ODR (data                      | $odr_{lp}$               | Low power preset                                                                                                                         |     | 10   |      | Hz   |

| output rate),<br>normal mode   | $odr_{rg}$               | Regular preset                                                                                                                           | 9.2 | 10   | 10.8 | Hz   |

|                                | odr <sub>eh</sub>        | Enhanced regular preset                                                                                                                  |     | 10   |      | Hz   |

|                                | $odr_{ha}$               | High accuracy preset                                                                                                                     |     | 20   |      | Hz   |

| ODR (data                      | $odr_{lp}$               | Low power preset                                                                                                                         | 0   |      | >300 | Hz   |

| output rate),<br>forced mode   | odr <sub>rg</sub>        | Regular preset                                                                                                                           | 0   |      | 100  | Hz   |

|                                | odr <sub>eh</sub>        | Enhanced regular preset                                                                                                                  | 0   |      | 60   | Hz   |

|                                | $odr_{ha}$               | High accuracy preset                                                                                                                     | 0   |      | 20   | Hz   |

| Full-scale<br>Nonlinearity     | NL <sub>m, FS</sub>      | best fit straight line                                                                                                                   |     |      | 1    | %FS  |

| Output Noise                   | $n_{\text{rms,lp,m,xy}}$ | Low power preset $x$ , $y$ -axis, $T_A$ =25°C Nominal $V_{DD}$ supplies                                                                  |     | 1.0  |      | μТ   |

|                                | n <sub>rms,lp,m,z</sub>  | Low power preset<br>z-axis, T <sub>A</sub> =25°C<br>Nominal V <sub>DD</sub> supplies                                                     |     | 1.4  |      | μТ   |

|                                | n <sub>rms,rg,m</sub>    | Regular preset<br>T <sub>A</sub> =25°C<br>Nominal V <sub>DD</sub> supplies                                                               |     | 0.6  |      | μТ   |

|                                | n <sub>rms,eh,m</sub>    | Enhanced regular<br>preset<br>T <sub>A</sub> =25°C<br>Nominal V <sub>DD</sub> supplies                                                   |     | 0.5  |      | μТ   |

|                                | n <sub>rms,ha,m</sub>    | High accuracy preset  T <sub>A</sub> =25°C  Nominal V <sub>DD</sub> supplies                                                             |     | 0.3  |      | μТ   |

| Power Supply<br>Rejection Rate | PSRR <sub>m</sub>        | $T_A=25^{\circ}C$<br>Nominal V <sub>DD</sub> supplies                                                                                    |     | ±0.5 |      | μT/V |

-

<sup>&</sup>lt;sup>5</sup>Magnetic zero-B offset assuming calibration with Bosch Sensortec eCompass software. Typical value after applying calibration movements containing various device orientations (typical device usage).

Page 9

## 2. Absolute maximum ratings

The absolute maximum ratings are provided in Table 2. At or above these maximum ratings operability is not given. The specification limits in Chapter 1 only apply under normal operating conditions.

Table 2: Absolute maximum ratings

| Parameter                                  | Condition                       | Min  | Max            | Unit |

|--------------------------------------------|---------------------------------|------|----------------|------|

| Voltage at Supply Pin                      | $V_{DD}$ Pin                    | -0.3 | 4.0            | V    |

|                                            | V <sub>DDIO</sub> Pin           | -0.3 | 4.0            | V    |

| Voltage at any Logic Pad                   | Non-Supply Pin                  | -0.3 | VDDIO +<br>0.3 | V    |

| Operating Temperature, T <sub>A</sub>      | Active operation                | -40  | +85            | °C   |

| Passive Storage Temp. Range                | ≤ 65% rel. H.                   | -50  | +150           | °C   |

| None-volatile memory (NVM)  Data Retention | T = 85°C                        | 10   |                | year |

| Mechanical Shock according to              | Duration ≤ 200µs                |      | 10,000         | g    |

| JESD22-B111                                | Duration ≤ 1.0ms                |      | 2,000          | g    |

|                                            | Free fall onto hard<br>surfaces |      | 1.8            | m    |

| ESD                                        | HBM, at any Pin                 |      | 2              | kV   |

|                                            | CDM                             |      | 500            | V    |

| Magnetic field                             | Any direction                   |      | > 7            | T    |

#### Note:

Stress above these limits may cause damage to the device. Exceeding the specified limits may affect the device reliability or cause malfunction.

## 3. Block diagram

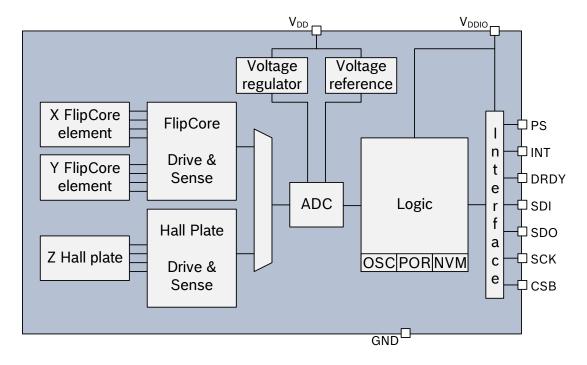

Figure 1 shows the basic building blocks of the BMM150:

Figure 1: Block diagram of BMM150

Page 11

### 4. Functional description

BMM150 is a triaxial standalone geomagnetic sensor (Sensing element and ASIC) in chip scale wafer level package and can be operated via I2C or SPI as a slave device.

#### 4.1 Power management

The BMM150 has two distinct power supply pins:

- V<sub>DD</sub> is the main power supply for all internal analog and digital functional blocks;

- $\bullet$  V<sub>DDIO</sub> is a separate power supply pin, used for the supply of the digital interface as well as the digital logic.

The device can be completely switched off ( $V_{DD} = 0V$ ) while keeping the  $V_{DDIO}$  supply on ( $V_{DDIO} > 0V$ ) or vice versa.

It is absolutely prohibited to keep any interface at a logical high level when  $V_{DDIO}$  is switched off. Such a configuration will permanently damage the device (i.e. if  $V_{DDIO} = 0 \rightarrow [SDI \& SDO \& SCK \& CSB] \neq high)$ .

The device contains a power on reset (POR) generator. It resets the logic part and the register values of the concerned ASIC after powering-on  $V_{DD}$  and  $V_{DDIO}$ . Please note, that all application specific settings which are not equal to the default settings (refer to register maps in chapter 5.2), must be re-set to its designated values after POR.

In case the  $I^2C$  interface is used, a direct electrical connection between  $V_{DDIO}$  supply and the PS pin is recommended in order to ensure reliable protocol selection.

#### 4.2 Power modes

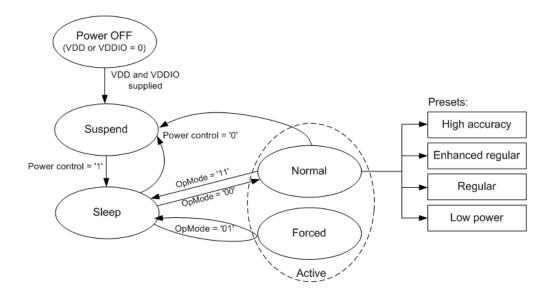

The BMM150 features configurable power modes. The BMM150 magnetometer part has four power modes: In the following chapters, power modes are described.

#### 4.2.1 Power off mode

In Power off mode,  $V_{DD}$  and/or  $V_{DDIO}$  are unpowered and the device does not operate. When only one of  $V_{DD}$  or  $V_{DDIO}$  is supplied, the magnetic sensor will still be in Power off mode. Power on reset is performed after both  $V_{DD}$  and  $V_{DDIO}$  raised above their detection thresholds.

#### 4.2.2 Suspend mode

Suspend mode is the default power mode of BMM150 after the chip is powered. When  $V_{DD}$  and  $V_{DDIO}$  are turned on the POR (power on reset) circuits operate and the device's registers are initialized. After POR becomes inactive, a start up sequence is executed. In this sequence NVM content is downloaded to shadow registers located in the device core. After the start up sequence the device is put in the Suspend mode. In this mode only registers which store power control bit information and SPI3 wire enable can be accessed by the user. No other registers can be accessed in Suspend mode. All registers lose their content, except the control register (0x4B). In particular, in this mode a Chip ID read (register 0x40) returns "0x00" ( $1^2$ C) or high-Z (SPI).

#### 4.2.3 Sleep mode

The user puts device from suspend into Sleep mode by setting the Power bit to "1", or from active modes (normal or forced) by setting OpMode bits to "11". In this state the user has full access to the device registers. In particular, the Chip ID can be read. Setting the power control bit to "0" (register 0x4B bit0) will bring the device back into Suspend mode. From the Sleep mode the user can put the device back into Suspend mode or into Active mode.

#### 4.2.4 Active mode

The device can switch into Active mode from Sleep mode by setting OpMode bits (register 0x4C). In this mode the magnetic field measurements are performed and all registers are accessible. In active mode, two operation modes can be distinguished:

- Normal mode: selected channels are periodically measured according to settings set in user registers. After measurements are completed, output data is put into data registers and the device waits for the next measurement period, which is set by programmed output data rate (ODR). From normal mode, the user can return to sleep mode by setting OpMode to "11" or by performing a soft reset (see chapter 5.6). Suspend mode can be entered by setting power control bit to "0".

- Forced mode (single measurement): When set by the host, the selected channels are measured according to settings programmed in user registers. After measurements are completed, output data is put into data registers, OpMode register value returns to "11" and the device returns to sleep mode. The forced mode is useful to achieve synchronized operation between host microcontroller and BMM150. Also, different data output rates from the ones selectable in normal mode can be achieved using forced mode.

Figure 2: Magnetometer power mode transition diagram

In Active Mode and normal operation, in principle any desired balance between output noise and active time (hence power consumption) can be adjusted by the repetition settings for x/y-axis and z-axis and the output data rate ODR. The average power consumption depends on the ratio of high current phase time (during data acquisition) and low current phase time (between data acquisitions). Hence, the more repetitions are acquired to generate one magnetic field data point, the longer the active time ratio in one sample phase, and the higher the average current. Thanks

Page 13

to longer internal averaging, the noise level of the output data reduces with increasing number of repetitions.

By using forced mode, it is possible to trigger new measurements at any rate. The user can therefore trigger measurements in a shorter interval than it takes for a measurement cycle to complete. If a measurement cycle is not allowed to complete, the resulting data will not be written into the data registers. To prevent this, the manually triggered measurement intervals must not be shorter than the active measurement time which is a function of the selected number of repetitions. The maximum selectable read-out frequency in forced mode can be calculated as follows:

$$f_{\text{max}, ODR} \approx \frac{1}{145\mu s \times nXY + 500\mu s \times nZ + 980\mu s}$$

Hereby nXY is the number of repetitions on X/Y-axis (not the register value) and nZ the number of repetitions on Z-axis (not the register value) (see description of XY\_REP and Z\_REP registers in chapter 5).

Although the repetition numbers for X/Y and Z axis and the ODR can be adjusted independently and in a wide range, there are four recommended presets (High accuracy preset, Enhanced regular preset, Regular preset, Low power preset) which reflect the most common usage scenarios, i.e. required output accuracy at a given current consumption, of the BMM150.

The four presets consist of the below register configurations, which are automatically set by the BMM150 API or driver provided by Bosch Sensortec when a preset is selected. Table 3 shows the recommended presets and the resulting magnetic field output noise and current consumption:

Table 3: Recommended presets for repetitions and output data rates:

| Preset                  | Rep.<br>X/Y<br>nXY | Rep.<br>Z<br>nZ | recommended<br>ODR<br>[Hz] | Max<br>ODR in<br>forced<br>mode<br>fmax,OD<br>R | RMS Noise<br>x/y/z<br>[µT] | Average current consumption at recommended ODR [mA] |

|-------------------------|--------------------|-----------------|----------------------------|-------------------------------------------------|----------------------------|-----------------------------------------------------|

| Low power preset        | 3                  | 3               | 10                         | >300                                            | 1.0/1.0/1.4                | 0.17                                                |

| Regular<br>preset       | 9                  | 15              | 10                         | 100                                             | 0.6/0.6/0.6                | 0.5                                                 |

| Enhanced regular preset | 15                 | 27              | 10                         | 60                                              | 0.5/0.5/0.5                | 0.8                                                 |

| High accuracy preset    | 47                 | 83              | 20                         | 20                                              | 0.3/0.3/0.3                | 4.9                                                 |

Page 14

#### 4.3 Sensor output data

#### 4.3.1 Magnetic field data

The representation of magnetic field data is different between X/Y-axis and Z-axis. The width of X- and Y-axis magnetic field data is 13 bits each and stored in two's complement. DATAX\_LSB (0x42) contains 5-bit LSB part [4:0] of the 13 bit output data of the X-channel. DATAX\_MSB (0x43) contains 8-bit MSB part [12:5] of the 13 bit output data of the Y-channel. DATAY\_LSB (0x44) contains 5-bit LSB part [4:0] of the 13 bit output data of the Y-channel. DATAY\_MSB (0x45) contains 8-bit MSB part [12:5] of the 13 bit output data of the Y-channel.

The width of the Z-axis magnetic field data is 15 bit word stored in two's complement. DATAZ\_LSB (0x46) contains 7-bit LSB part [6:0] of the 15 bit output data of the Z-channel. DATAZ\_MSB (0x47) contains 8-bit MSB part [14:7] of the 15 bit output data of the Z-channel.

For all axes, temperature compensation on the host is used to get ideally matching sensitivity over the full temperature range. The temperature compensation is based on a resistance measurement of the hall sensor plate. The resistance value is represented by a 14 bit unsigned output word.

RHALL\_LSB (0x48) contains 6-bit LSB part [5:0] of the 14 bit output data of the RHALL-channel. RHALL\_MSB (0x49) contains 8-bit MSB part [13:6] of the 14 bit output data of the RHALL-channel.

All signed register values are in two's complement representation. Bits which are marked "reserved" can have different values or can in some cases not be read at all (read will return 0x00 in I<sup>2</sup>C mode and high-Z in SPI mode).

Data register readout and shadowing is implemented as follows:

After all enabled axes have been measured; complete data packages consisting of DATAX, DATAY, DATAZ and RHALL are updated at once in the data registers. This way, it is prevented that a following axis is updated while the first axis is still being read (axis mix-up) or that MSB part of an axis is updated while LSB part is being read.

While reading from any data register, data register update is blocked. Instead, incoming new data is written into shadow registers which will be written to data registers after the previous read sequence is completed (i.e. upon stop condition in  $I^2C$  mode, or CSB going high in SPI mode, respectively). Hence, it is recommended to read out at all data at once (0x42 to 0x49 or 0x4A if status bits are also required) with a burst read.

Single bytes or axes can be read out, while in this case it is not assured that adjacent registers are not updated during readout sequence.

The "Data ready status" bit (register 0x48 bit0) is set "1" when the data registers have been updated but the data was not yet read out over digital interface. Data ready is cleared (set "0") directly after completed read out of any of the data registers and subsequent stop condition (I<sup>2</sup>C) or lifting of CSB (SPI).

In addition, when enabled the "Data overrun" bit (register *0x4A bit7*) turns "1" whenever data registers are updated internally, but the old data was not yet read out over digital interface (i.e. data ready bit was still high). The "Data overrun" bit is cleared when the interrupt status register *0x4A* is read out. This function needs to be enabled separately by setting the "Data overrun En" bit (register *0x4D bit7*)).

Page 15

#### Note:

Please also see chapter 5 for detailed register descriptions.

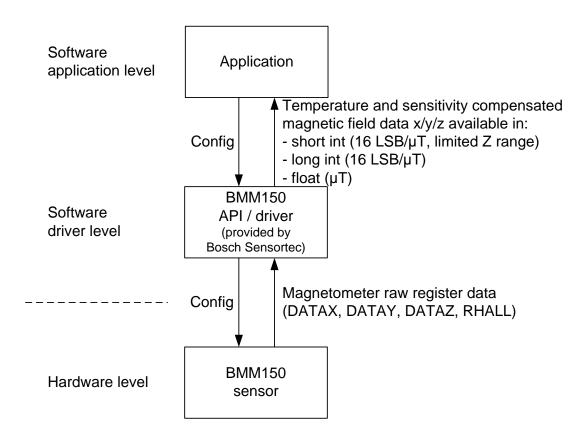

#### 4.3.2 Magnetic field data temperature compensation

The raw register values DATAX, DATAY, DATAZ and RHALL are read out from the host processor using the BMM150 API/driver which is provided by Bosch Sensortec. The API/driver performs an off-chip temperature compensation and outputs x/y/z magnetic field data in 16 LSB/ $\mu$ T to the upper application layer:

Figure 3: Calculation flow of magnetic field data from raw BMM150 register data

The API/driver performs all calculations using highly optimized fixed-point C-code arithmetic. For platforms that do not support C code, a floating-point formula is available as well.

Page 16

#### 4.4 Self-test

BMM150 supports two self-tests modes: Normal self-test and advanced self-test.

#### 4.4.1 Normal self test

During normal self-test, the following verifications are performed:

FlipCore signal path is verified by generating signals on-chip. These are processed through the signal path and the measurement result is compared to known thresholds.

- FlipCore (X and Y) connection to ASIC are checked for connectivity and short circuits

- Hall sensor connectivity is checked for open and shorted connections

- Hall sensor signal path and hall sensor element offset are checked for overflow.

To perform a self test, the sensor must first be put into sleep mode (OpMode = "11"). Self-test mode is then entered by setting the bit "Self test" (register 0x4C bit0) to "1". After performing self test, this bit is set back to "0". When self-test is successful, the corresponding self-test result bits are set to "1" ("X-Self-Test" register 0x42 bit0, "Y-Self-Test" register 0x44 bit0, "Z-Self-Test" register 0x46 bit0). If self-test fails for an axis, the corresponding result bit returns "0".

#### 4.4.2 Advanced self test

Advanced self test performs a verification of the Z channel signal path functionality and sensitivity. An on-chip coil wound around the hall sensor can be driven in both directions with a calibrated current to generate a positive or negative field of around 100 µT.

Advanced self test is an option that is active in parallel to the other operation modes. The only difference is that during the active measurement phase, the coil current is enabled. The recommended usage of advanced self test is the following:

- 1. Set sleep mode

- 2. Disable X, Y axis

- 3. Set Z repetitions to desired level

- 4. Enable positive advanced self test current

- 5. Set forced mode, readout Z and R channel after measurement is finished

- 6. Enable negative advanced self test current

- 7. Set forced mode, readout Z and R channel after measurement is finished

- 8. Disable advanced self test current (this must be done manually)

- 9. Calculate difference between the two compensated field values. This difference should be around 200  $\mu T$  with some margins.

- 10. Perform a soft reset of manually restore desired settings

Please refer to the corresponding application note for the exact thresholds to evaluate advanced self-test.

The table below describes how the advanced self-test is controlled:

Page 17

Table 4: Magnetometer advanced self-test control

| (0x4C)<br>Adv.ST <1:0> | Configuration                              |

|------------------------|--------------------------------------------|

| 00b                    | Normal operation (no self-test), default   |

| 01b                    | Reserved, do not use                       |

| 10b                    | Negative on-chip magnetic field generation |

| 11b                    | Positive on-chip magnetic field generation |

The BMM150 API/driver provided by Bosch Sensortec provides a comfortable way to perform both self-tests and to directly obtain the result without further calculations. It is recommended to use this as a reference.

#### 4.5 Non-volatile memory

Some of the memory of the BMM150 magnetometer is non-volatile memory (NVM). This NVM is pre-programmed in Bosch Sensortec fabrication line and cannot be modified afterwards. It contains trimming data which are required for sensor operation and sensor data compensation, thus it is read out by the BMM150 API/driver during initialization.

#### 4.6 Magnetometer interrupt controller

Four magnetometer based interrupt engines are integrated in the BMM150: Low-Threshold, High-Threshold, Overflow and Data Ready (DRDY). Each interrupt can be enabled independently.

When enabled, an interrupt sets the corresponding status bit in the interrupt status register (0x4A) when its condition is satisfied.

When the "Interrupt Pin Enable" bit (register 0x4E bit6) is set, any occurring activated interrupts are flagged on the BMM150's INT output pin. By default, the interrupt pin is disabled (high-Z status).

Low-Threshold, High-Threshold and Overflow interrupts are mapped to the INT pin when enabled, Data Ready (DRDY) interrupt is mapped to the DRDY pin of BMM150 when enabled. For Highand Low-Threshold interrupts each axis X/Y/Z can be enabled separately for interrupt detection in the registers "High Int Z en", "High Int Y en", "High Int X en", "Low Int Z en", "Low Int Y En" and "Low Int X En" in register 0x4D bit5-bit0. Overflow interrupt is shared for X, Y and Z axis.

When the "Data Ready Pin En" bit (register 0x4E bit7) is set, the Data Ready (DRDY) interrupt event is flagged on the BMM150's DRDY output pin (by default the "Data Ready Pin En" bit is not set and DRDY pin is in high-Z state).

The interrupt status registers are updated together with writing new data into the magnetic field data registers. The status bits for Low-/High-Threshold interrupts are located in register 0x4A, the Data Ready (DRDY) status flag is located at register 0x48 bit0.

If an interrupt is disabled, all active status bits and pins are reset after the next measurement was performed.

Page 18

#### 4.6.1 General features

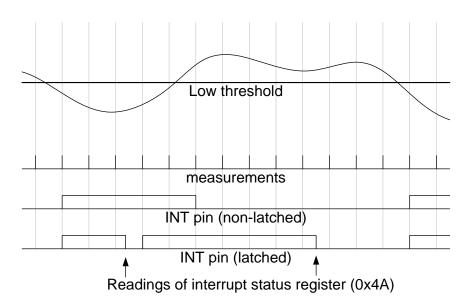

An interrupt is cleared depending on the selected interrupt mode, which is common to all interrupts. There are two different interrupt modes: non-latched and latched. All interrupts (except Data Ready) can be latched or non-latched. Data Ready (DRDY) is always cleared after readout of data registers ends.

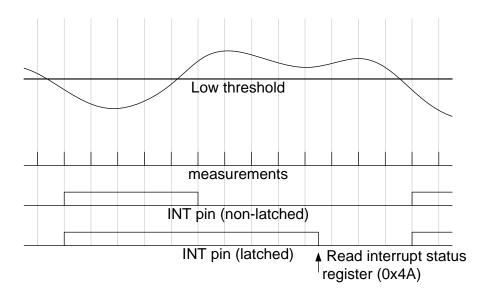

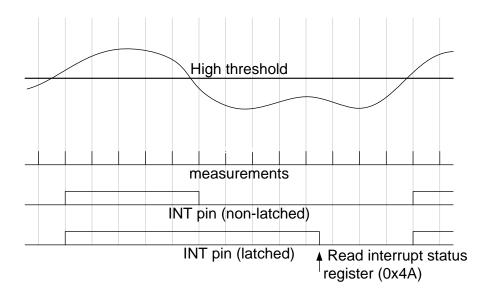

A non-latched interrupt will be cleared on a new measurement when the interrupt condition is not valid anymore, whereas a latched interrupt will stay high until the interrupts status register (0x4A) is read out. After reading the interrupt status, both the interrupt status bits and the interrupt pin are reset. The mode is selected by the "Interrupt latch" bit (register 0x4A bit1), where the default setting of "1" means latched. Figure 4 shows the difference between the modes for the example Low-Threshold interrupt.

INT and DRDY pin polarity can be changed by the "Interrupt polarity" bit (register 0x4E bit0) and "DR polarity" (register 0x4E bit2), from the default high active ("1") to low active ("0").

Figure 4: Interrupt latched and non-latched mode

#### 4.6.2 Electrical behavior of magnetic interrupt pins

Both interrupt pins INT and DRDY are push/pull when the corresponding interrupt pin enable bit is set, and are floating (High-Z) when the corresponding interrupt pin enable bit is disabled (default).

Page 19

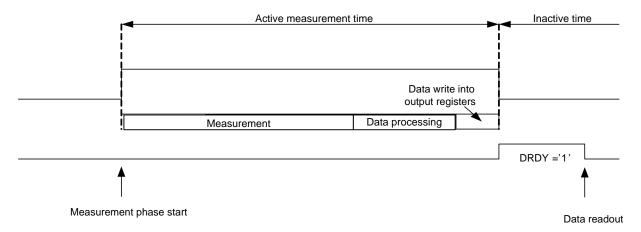

#### 4.6.3 Data ready / DRDY interrupt

This interrupt serves for synchronous reading of magnetometer data. It is generated after storing a new set of values (DATAX, DATAY, DATAZ, RHALL) in the data registers:

Figure 5: Data acquisition and DRDY operation (DRDY in "high active" polarity)

The interrupt mode of the Data Ready (DRDY) interrupt is fixed to non-latched. It is enabled (disabled) by writing "1" ("0") to "Data Ready pin En" in register 0x4E bit7.

DRDY pin polarity can be changed by the "DR polarity" bit (register 0x4E bit2), from the default high active ("1") to low active ("0").

#### 4.6.4 Low-threshold interrupt

When the data registers' (DATAX, DATAY and DATAZ) values drop below the threshold level defined by the "Low Threshold register (0x4F), the corresponding interrupt status bits for those axes are set ("Low Int X", "Low Int Y" and "Low Int Z" in register 0x4A). This is done for each axis independently. Please note that the X and Y axis value for overflow is -4096. However, no interrupt is generated on these values. See chapter 4.6.6 for more information on overflow.

Hereby, one bit in "Low Threshold" corresponds to roughly  $6\mu T$  (not exactly, as the raw magnetic field values DATAX, DATAY and DATAZ are not temperature compensated).

The Low-threshold interrupt is issued on INT pin when one or more values of the data registers DATAX, DATAY and DATAZ drop below the threshold level defined by the "Low Threshold" register (0x4F), and when the axis where the threshold was exceeded is enabled for interrupt generation:

Note: Threshold interrupt enable bits ("Low INT [XYZ] en") are active low and "1" (disabled) by default.

Figure 6: Low-threshold interrupt function

Page 21

#### 4.6.5 High-threshold interrupt

When the data registers' (DATAX, DATAY and DATAZ) values exceed the threshold level defined by the "High Threshold register (0x50), the corresponding interrupt status bits for those axes are set ("High Int X", "High Int Y" and "High Int Z" in register 0x4A). This is done for each axis independently.

Hereby, one bit in "High Threshold" corresponds to roughly  $6\mu T$  (not exactly, as the raw magnetic field values DATAX, DATAY and DATAZ are not temperature compensated).

The High-threshold interrupt is issued on INT pin when one or more values of the data registers DATAX, DATAY and DATAZ exceed the threshold level defined by the "High Threshold" register (0x50), and when the axis where the threshold was exceeded is enabled for interrupt generation:

Result = (DATAX > "High Threshold" x 16) AND "High Int X en" is "0" OR (DATAY > "High Threshold" x 16) AND "High Int Y en" is "0" OR (DATAZ > "High Threshold" x 16) AND "High Int Z en" is "0"

#### Note:

Threshold interrupt enable bits ("High INT [XYZ] en") are active low and "1" (disabled) by default.

Figure 7: High-threshold interrupt function

#### 4.6.6 Overflow

When a measurement axis had an overflow, the corresponding data register is saturated to the most negative value. For X and Y axis, the data register is set to the value -4096. For the Z axis, the data register is set to the value -16384.

The "Overflow" flag (register 0x4A bit6) indicates that the measured magnetic field raw data of one or more axes exceeded maximum range of the device. The overflow condition can be flagged on the INT pin by setting the bit "overflow int enable" (register 0x4D bit6, active high, default value "0"). The channel on which overflow occurred can by determined by assessing the DATAX/Y/Z registers.

## 5. Register Description

#### 5.1 General Remarks

The entire communication with the device's magnetometer part is performed by reading from and writing to registers. Registers have a width of 8 bits; they are mapped to a common space of 50 addresses from (0x40) up to (0x71). Within the used range there are several registers which are marked as 'reserved'. Any reserved bit is ignored when it is written and no specific value is guaranteed when read. Especially, in SPI mode the SDO pin may stay in high-Z state when reading some of these registers.

Registers with addresses from (0x40) up to (0x4A) are read-only. Any attempt to write to these registers is ignored.

#### 5.2 Register map

| Register Address | Default Value | bit7                                                   | bit6                                                     | bit5             | bit4                     | bit3                          | bit2         | bit1            | bit0               |

|------------------|---------------|--------------------------------------------------------|----------------------------------------------------------|------------------|--------------------------|-------------------------------|--------------|-----------------|--------------------|

| 0x71             | N/A           | DILI                                                   | Dito                                                     | DILO             | DIL4                     | DIIJ                          | UILE         | DILI            | DILO               |

| 0x71             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x6F             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x6F             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x6D             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x6C             | N/A<br>N/A    |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x6B             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x6A             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x69             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x68             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x67             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x67<br>0x66     | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x65             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x65<br>0x64     | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x63             | N/A<br>N/A    |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x62             | N/A<br>N/A    |                                                        |                                                          |                  | 7004                     | erved                         |              |                 |                    |

| 0x62<br>0x61     | N/A           |                                                        |                                                          |                  | 1626                     | oi vou                        |              |                 |                    |

| 0x60             | N/A<br>N/A    |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x5F             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x5E             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x5D             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x5D<br>0x5C     | N/A<br>N/A    |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x5B             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x5A             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x5A<br>0x59     | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x58             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x57             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x56             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x55             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x54             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x53             | N/A           |                                                        |                                                          |                  |                          |                               |              |                 |                    |

| 0x52             | 0x00          |                                                        |                                                          |                  | PED7 Number Of Pen       | etitions (valid for Z) [7:0]  |              |                 |                    |

| 0x52<br>0x51     | 0x00          |                                                        |                                                          |                  |                          | etitions (valid for XY) [7:0] |              |                 |                    |

| 0x50             | 0x00          |                                                        |                                                          |                  |                          | eshold [7:0]                  |              |                 |                    |

| 0x4F             | 0x00          |                                                        |                                                          |                  |                          | eshold [7:0]                  |              |                 |                    |

| 0x4E             | 0x07          | Data Ready Pin En                                      | Interrupt Pin En                                         | Channel Z        | Channel Y                | Channel X                     | DR Polarity  | Interrupt Latch | Interrupt Polarity |

| 0X4D             | 0x3F          | Data Overrun En                                        | Overflow Int En                                          | High Int Z en    | High Int Y en            | High Int X en                 | Low Int Z en | Low Int Y en    | Low Int X en       |

| 0x4C             | 0x06          |                                                        | T [1:0]                                                  |                  | Data Rate [2:0]          |                               |              | de [1:0]        | Self Test          |

| 0x4B             | 0x01          | Soft Reset '1'                                         | fixed '0'                                                | fixed '0'        | fixed '0'                | fixed '0'                     | SPI3en       | Soft Reset '1'  | Power Control Bit  |

| 0x4A             | 0x00          | Data Overrun                                           | Overflow                                                 | High Int Z       | High Int Y               | High Int X                    | Low Int Z    | Low Int Y       | Low Int X          |

| 0x49             | N/A           | Data Overruit                                          | Overnow                                                  | riigiriitez      |                          | 13:6] MSB                     | LOWING       | LOWING          | LOWINGA            |

| 0x48             | N/A           |                                                        | RHALL [5:0] LSB fixed '0' Data Ready Status              |                  |                          |                               |              |                 |                    |

| 0x47             | N/A           |                                                        | NAME [3.0] ESB INCO Data Ready Status  DATA Z [14:7] MSB |                  |                          |                               |              |                 |                    |

| 0x46             | N/A           | DATA Z (6.0) LSB Z-Self-Test                           |                                                          |                  |                          |                               |              |                 |                    |

| 0x45             | N/A           | DATA 2 (0.0) LSB                                       |                                                          |                  |                          |                               |              |                 |                    |

| 0x44             | N/A           | DATA Y [4:0] LSB   fixed '0'   fixed '0'   Y-Self-Test |                                                          |                  |                          |                               |              |                 |                    |

| 0x43             | N/A           | DATA X [12:5] MSB  DATA X [12:5] MSB                   |                                                          |                  |                          |                               |              |                 |                    |

| 0x42             | N/A           |                                                        |                                                          | DATA X [4:0] LSB | 2.11/K/                  |                               | fixed '0'    | fixed '0'       | X-Self-Test        |

| 0x42<br>0x41     | N/A           |                                                        | DATA X (4:0) LSB TIXEG U TIXEG U X-Self-Test reserved    |                  |                          |                               |              |                 |                    |

| 0x40             | 0x32          |                                                        |                                                          | Ch               |                          | read if power control bit =   | :"1")        |                 |                    |

| 0,40             | 0.02          |                                                        |                                                          | Cil              | PID - ONOE (Call Olly be | Toda ii postoi control bit =  | .,           |                 |                    |

Page 23

#### 5.3 Chip ID

**Register** (0x40) Chip ID contains the magnetometer chip identification number, which is 0x32. This number can only be read if the power control bit (register 0x4B bit0) is enabled.

Table 5: Chip identification number, register (0x40)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 1     | 1     | 0     | 0     | 1     | 0     |

Register (0x41) is reserved

#### 5.4 Magnetic field data

**Register (0x42)** contains the LSB part of x-axis magnetic field data and the self-test result flag for the x-axis.

Table 6: LSB part of x-axis magnetic field, register (0x42)

| (0x42) Bit | Name          | Description                                      |

|------------|---------------|--------------------------------------------------|

| Bit 7      | DATAX_lsb <4> | Bit 4 of x-axis magnetic field data              |

| Bit 6      | DATAX_lsb <3> | Bit 3 of x-axis magnetic field data              |

| Bit 5      | DATAX_lsb <2> | Bit 2 of x-axis magnetic field data              |

| Bit 4      | DATAX_lsb <1> | Bit 1 of x-axis magnetic field data              |

| Bit 3      | DATAX_lsb <0> | Bit 0 of x-axis magnetic field data = x LSB      |

| Bit 2      | -             | (fixed to 0)                                     |

| Bit 1      | -             | (fixed to 0)                                     |

| Bit 0      | SelfTestX     | Self-test result flag for x-axis, default is "1" |

**Register (0x43)** contains the MSB part of x-axis magnetic field data.

Table 7: MSB part of x-axis magnetic field, register (0x43)

| (0x43) Bit | Name           | Description                                  |

|------------|----------------|----------------------------------------------|

| Bit 7      | DATAX_msb <12> | Bit 12 of x-axis magnetic field data = x MSB |

| Bit 6      | DATAX_msb <11> | Bit 11 of x-axis magnetic field data         |

| Bit 5      | DATAX_msb <10> | Bit 10 of x-axis magnetic field data         |

| Bit 4      | DATAX_msb <9>  | Bit 9 of x-axis magnetic field data          |

| Bit 3      | DATAX_msb <8>  | Bit 8 of x-axis magnetic field data          |

| Bit 2      | DATAX_msb <7>  | Bit 7 of x-axis magnetic field data          |

| Bit 1      | DATAX_msb <6>  | Bit 6 of x-axis magnetic field data          |

| Bit 0      | DATAX_msb <5>  | Bit 5 of x-axis magnetic field data          |

Page 24

**Register (0x44)** contains the LSB part of y-axis magnetic field data and the self-test result flag for the y-axis.

Table 8: LSB part of y-axis magnetic field, register (0x44)

| (0x44) Bit | Name          | Description                                      |

|------------|---------------|--------------------------------------------------|

| Bit 7      | DATAY_lsb <4> | Bit 4 of y-axis magnetic field data              |

| Bit 6      | DATAY_lsb <3> | Bit 3 of y-axis magnetic field data              |

| Bit 5      | DATAY_lsb <2> | Bit 2 of y-axis magnetic field data              |

| Bit 4      | DATAY_lsb <1> | Bit 1 of y-axis magnetic field data              |

| Bit 3      | DATAY_lsb <0> | Bit 0 of y-axis magnetic field data = y LSB      |

| Bit 2      | -             | (fixed to 0)                                     |

| Bit 1      | -             | (fixed to 0)                                     |

| Bit 0      | SelfTestY     | Self-test result flag for y-axis, default is "1" |

Register (0x45) contains the MSB part of y-axis magnetic field data.

Table 9: MSB part of y-axis magnetic field, register (0x45)

| (0x45) Bit | Name           | Description                                  |

|------------|----------------|----------------------------------------------|

| Bit 7      | DATAY_msb <12> | Bit 12 of y-axis magnetic field data = y MSB |

| Bit 6      | DATAY_msb <11> | Bit 11 of y-axis magnetic field data         |

| Bit 5      | DATAY_msb <10> | Bit 10 of y-axis magnetic field data         |

| Bit 4      | DATAY_msb <9>  | Bit 9 of y-axis magnetic field data          |

| Bit 3      | DATAY_msb <8>  | Bit 8 of y-axis magnetic field data          |

| Bit 2      | DATAY_msb <7>  | Bit 7 of y-axis magnetic field data          |

| Bit 1      | DATAY_msb <6>  | Bit 6 of y-axis magnetic field data          |

| Bit 0      | DATAY_msb <5>  | Bit 5 of y-axis magnetic field data          |

**Register (0x46)** contains the LSB part of z-axis magnetic field data and the self-test result flag for the z-axis.

Table 10: LSB part of z-axis magnetic field, register (0x46)

| (0x46) Bit | Name          | Description                                      |

|------------|---------------|--------------------------------------------------|

| Bit 7      | DATAZ_lsb <6> | Bit 6 of z-axis magnetic field data              |

| Bit 6      | DATAZ_lsb <5> | Bit 5 of z-axis magnetic field data              |

| Bit 5      | DATAZ_lsb <4> | Bit 4 of z-axis magnetic field data              |

| Bit 4      | DATAZ_lsb <3> | Bit 3 of z-axis magnetic field data              |

| Bit 3      | DATAZ_lsb <2> | Bit 2 of z-axis magnetic field data              |

| Bit 2      | DATAZ_lsb <1> | Bit 1 of z-axis magnetic field data              |

| Bit 1      | DATAZ_lsb <0> | Bit 0 of z-axis magnetic field data = z LSB      |

| Bit 0      | SelfTestZ     | Self-test result flag for z-axis, default is "1" |

Page 25

Register (0x47) contains the MSB part of z-axis magnetic field data.

Table 11: MSB part of z-axis magnetic field, register (0x47)

| (0x47) Bit | Name           | Description                                  |

|------------|----------------|----------------------------------------------|

| Bit 7      | DATAZ_msb <14> | Bit 14 of y-axis magnetic field data = z MSB |

| Bit 6      | DATAZ_msb <13> | Bit 13 of y-axis magnetic field data         |

| Bit 5      | DATAZ_msb <12> | Bit 12 of y-axis magnetic field data         |

| Bit 4      | DATAZ_msb <11> | Bit 11 of y-axis magnetic field data         |

| Bit 3      | DATAZ_msb <10> | Bit 10 of y-axis magnetic field data         |

| Bit 2      | DATAZ_msb <9>  | Bit 9 of y-axis magnetic field data          |

| Bit 1      | DATAZ_msb <8>  | Bit 8 of y-axis magnetic field data          |

| Bit 0      | DATAZ_msb <7>  | Bit 7 of y-axis magnetic field data          |

Register (0x48) contains the LSB part of hall resistance and the Data Ready (DRDY) status bit.

Table 12: LSB part of hall resistance, register (0x48)

| (0x48) Bit | Name              | Description                          |

|------------|-------------------|--------------------------------------|

| Bit 7      | RHALL_lsb <5>     | Bit 5 of hall resistance             |

| Bit 6      | RHALL_lsb <4>     | Bit 4 of hall resistance             |

| Bit 5      | RHALL_lsb <3>     | Bit 3 of hall resistance             |

| Bit 4      | RHALL_lsb <2>     | Bit 2 of hall resistance             |

| Bit 3      | RHALL_lsb <1>     | Bit 1 of hall resistance             |

| Bit 2      | RHALL_lsb <0>     | Bit 0 of hall resistance = RHALL LSB |

| Bit 1      | -                 | (fixed to 0)                         |

| Bit 0      | Data Ready Status | Data ready (DRDY) status bit         |

Register (0x49) contains the MSB part of hall resistance.

Table 13: MSB part of hall resistance, register (0x49)

| (0x49) Bit | Name           | Description                           |

|------------|----------------|---------------------------------------|

| Bit 7      | RHALL_msb <13> | Bit 13 of hall resistance = RHALL MSB |

| Bit 6      | RHALL_msb <12> | Bit 12 of hall resistance             |

| Bit 5      | RHALL_msb <11> | Bit 11 of hall resistance             |

| Bit 4      | RHALL_msb <10> | Bit 10 of hall resistance             |

| Bit 3      | RHALL_msb <9>  | Bit 9 of hall resistance              |

| Bit 2      | RHALL_msb <8>  | Bit 8 of hall resistance              |

| Bit 1      | RHALL_msb <7>  | Bit 7 of hall resistance              |

| Bit 0      | RHALL_msb <6>  | Bit 6 of hall resistance              |

Page 26

#### 5.5 Interrupt status register

**Register** (0x4A) contains the states of all interrupts.

Table 14: Interrupt status, register (0x4A)

| (0x4A) Bit | Name         | Description                                 |

|------------|--------------|---------------------------------------------|

| Bit 7      | Data overrun | Data overrun status flag                    |

| Bit 6      | Overflow     | Overflow status flag                        |

| Bit 5      | High Int Z   | High-Threshold interrupt z-axis status flag |

| Bit 4      | High Int Y   | High-Threshold interrupt y-axis status flag |

| Bit 3      | High Int X   | High-Threshold interrupt x-axis status flag |

| Bit 2      | Low Int Z    | Low-Threshold interrupt z-axis status flag  |

| Bit 1      | Low Int Y    | Low-Threshold interrupt y-axis status flag  |

| Bit 0      | Low Int X    | Low-Threshold interrupt x-axis status flag  |

#### 5.6 Power and operation modes, self-test and data output rate control registers

**Register** (0x4B) contains control bits for power control, soft reset and interface SPI mode selection. This special control register is also accessible in suspend mode.

Soft reset is executed when both bits (register 0x4B bit7 and bit1) are set "1". Soft reset does not execute a full POR sequence, but all registers are reset except for the "trim" registers above register 0x54 and the power control register (0x4B). Soft reset always brings the device into sleep mode. When device is in the suspend mode, soft reset is ignored and the device remains in suspend mode. The two "Soft Reset" bits are reset to "0" automatically after soft reset was completed. To perform a full POR reset, bring the device into suspend and then back into sleep mode.

When SPI mode is selected, the "SPI3En" bit enables SPI 3-wire mode when set "1". When "SPI3En" is set "0" (default), 4-wire SPI mode is selected.

Setting the "Power Control bit" to "1" brings the device up from Suspend mode to Sleep mode, when "Power Control bit" is set "0" the device returns to suspend mode (see chapter 4.2 for details of magnetometer power modes).

Table 15: Power control, soft reset and SPI mode control register (0x4B)

| (0x4B) Bit | Name              | Description                               |

|------------|-------------------|-------------------------------------------|

| Bit 7      | Soft Reset '1'    | One of the soft reset trigger bits.       |

| Bit 6      |                   | (fixed to 0)                              |

| Bit 5      | -                 | (fixed to 0)                              |

| Bit 4      | -                 | (fixed to 0)                              |

| Bit 3      |                   | (fixed to 0)                              |

| Bit 2      | SPI3en            | Enable bit for SPI3 mode                  |

| Bit 1      | Soft Reset '1'    | One of the soft reset trigger bits.       |

| Bit 0      | Power Control bit | When set to "0", suspend mode is selected |

Page 27

Register (0x4C) contains control bits for operation mode, output data rate and self-test.

The two "Adv. ST" bits control the on-chip advanced self-test (see chapter 4.4.2 for details of the magnetometer advanced self-test).

The three "Data rate" bits control the magnetometer output data rate according to below Table 17.

The two "Opmode" bits control the operation mode according to below Table 18 (see chapter 4.2 for a detailed description of magnetometer power modes).

Table 16: Operation mode, output data rate and self-test control register (0x4C)

| (0x4C) Bit | Name          | Description                      |

|------------|---------------|----------------------------------|

| Bit 7      | Adv. ST <1>   | Advanced self-test control bit 1 |

| Bit 6      | Adv. ST <0>   | Advanced self-test control bit 0 |

| Bit 5      | Data rate <2> | Data rate control bit 2          |

| Bit 4      | Data rate <1> | Data rate control bit 1          |

| Bit 3      | Data rate <0> | Data rate control bit 0          |

| Bit 2      | Opmode <1>    | Operation mode control bit 1     |

| Bit 1      | Opmode <0>    | Operation mode control bit 0     |

| Bit 0      | Self Test     | Normal self-test control bit     |

Three "Data rate" bits control the output data rate (ODR) of the BMM150 magnetometer part:

Table 17: Output data rate (ODR) setting (0x4C)

| (0x4C) Data rate <2:0> | Magnetometer output data rate (ODR) [Hz] |

|------------------------|------------------------------------------|

| 000b                   | 10 (default)                             |

| 001b                   | 2                                        |

| 010b                   | 6                                        |

| 011b                   | 8                                        |

| 100b                   | 15                                       |

| 101b                   | 20                                       |

| 110b                   | 25                                       |

| 111b                   | 30                                       |

Two "Opmode" bits control the operation mode of the BMM150 magnetometer part:

Table 18: Operation mode setting (0x4C)

| (0x4C)<br>Opmode <1:0> | Magnetometer operation mode <sup>6</sup> |

|------------------------|------------------------------------------|

| 00b                    | Normal mode                              |

| 01b                    | Forced mode                              |

| 10b                    | Reserved, do not use                     |

| 11b                    | Sleep Mode                               |

<sup>&</sup>lt;sup>6</sup> See chapter 4.2 for a detailed description of magnetometer power modes.

.

Page 28

## 5.7 Interrupt and axis enable settings control registers

**Register** (0x4D) contains control bits for interrupt settings. (Also refer to chapter 4.6 for the details of magnetometer interrupt operation).

Table 19: Interrupt settings control register (0x4D)

| (0x4D) Bit | Name            | Description                                                                                       |

|------------|-----------------|---------------------------------------------------------------------------------------------------|

| Bit 7      | Data Overrun En | Enables data overrun indication in the "Data Overrun" flag (active high, default is "0" disabled) |

| Bit 6      | Overflow Int En | Activates mapping of Overflow flag status to the INT pin (active high, default is "0" disabled)   |

| Bit 5      | High Int Z En   | Enables the z-axis detection for High-Threshold interrupts (active low, default is "1" disabled)  |

| Bit 4      | High Int Y En   | Enables the y-axis detection for High-Threshold interrupts (active low, default is "1" disabled)  |

| Bit 3      | High Int X En   | Enables the x-axis detection for High-Threshold interrupts (active low, default is "1" disabled)  |

| Bit 2      | Low Int Z En    | Enables the z-axis detection for Low-Threshold interrupts (active low, default is "1" disabled)   |

| Bit 1      | Low Int Y En    | Enables the y-axis detection for Low-Threshold interrupts (active low, default is "1" disabled)   |

| Bit 0      | Low Int X En    | Enables the x-axis detection for Low-Threshold interrupts (active low, default is "1" disabled)   |

**Register** (0x4E) contains control bits interrupt settings and axes enable bits. (Also refer to chapter 0 for the details of magnetometer interrupt operation). If a magnetic measurement channel is disabled, its last measured magnetic output values will remain in the data registers. If the Z channel is disabled, the resistance measurement will also be disabled and the resistance output value will be set to zero. If interrupts are set to trigger on an axis that has been disabled, these interrupts will still be asserted based on the last measured value.

Table 20: Interrupt settings and axes enable bits control register (0x4E)

| (0x4E) Bit | Name               | Description                                                                                                                                                                                                          |

|------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 7      | Data Ready Pin En  | Enables data ready status mapping on DRDY pin (active high, default is "0" disabled)                                                                                                                                 |

| Bit 6      | Interrupt Pin En   | Enables interrupt status mapping on INT pin (active high, default is "0" disabled)                                                                                                                                   |

| Bit 5      | Channel Z          | Enable z-axis and resistance measurement (active low, default is "0" enabled)                                                                                                                                        |