**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

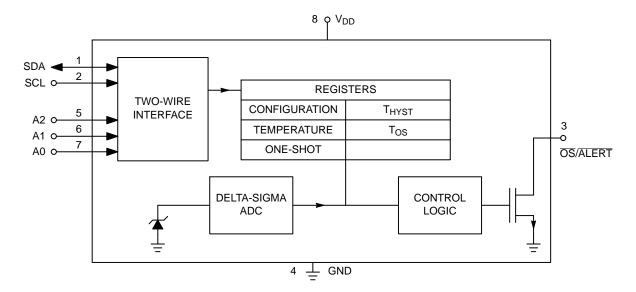

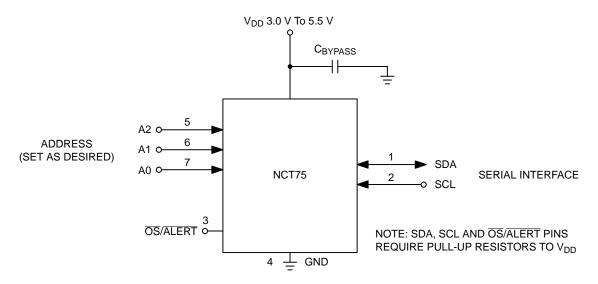

# Industry Standard Digital Temperature Sensor with 2-wire Interface

The NCT75 is a two-wire serially programmable temperature sensor with an over-temperature/interrupt output pin to signal out of limit conditions. This is an open-drain pin and can operate in either comparator or interrupt mode. Temperature measurements are converted into digital form using a high resolution (12 bit), sigma-delta, analog-to-digital converter (ADC). The device operates over the  $-55^{\circ}$ C to  $+125^{\circ}$ C temperature range.

Communication with the NCT75 is accomplished via the SMBus/I<sup>2</sup>C interface. Three address selection pins, A2, A1 and A0, can be used to connect up to 8 NCT75s to a single bus. Through this interface the NCT75s internal registers may be accessed. These registers allow the user to read the current temperature, change the configuration settings and adjust the temperature limits.

The NCT75 has a wide supply voltage range of 3.0 V to 5.5 V. The average supply current is 575  $\mu$ A at 3.3 V. It also offers a shutdown mode to conserve power. The typical shutdown current is 3  $\mu$ A.

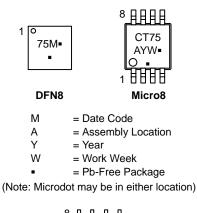

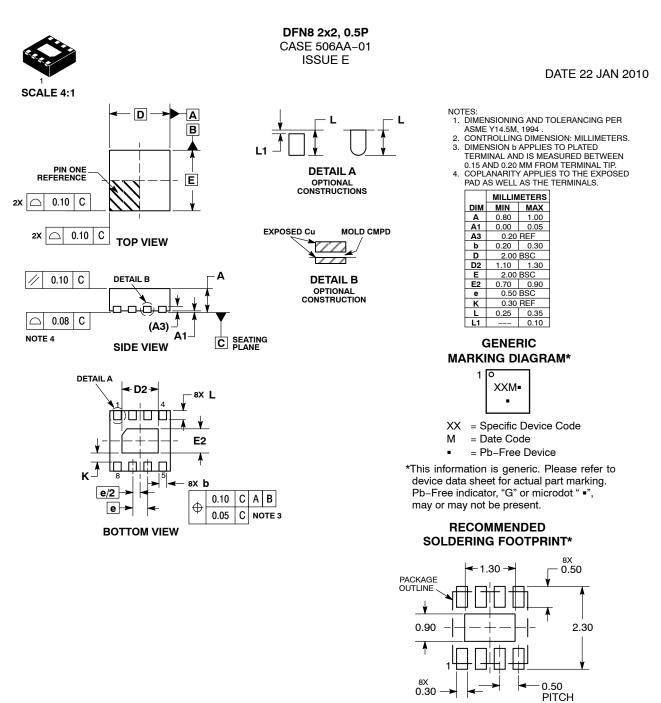

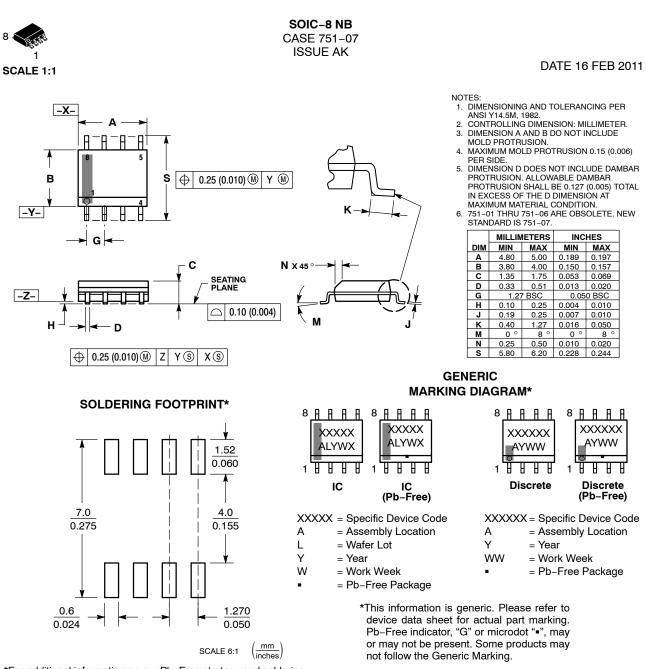

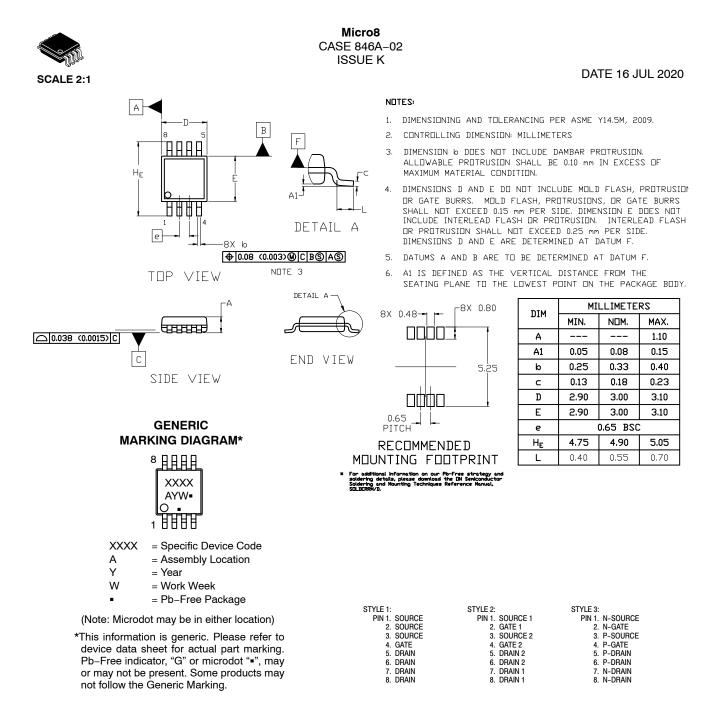

The NCT75 is available in three, space saving packages – 8-lead DFN, 8-lead Micro8 and 8-lead SOIC and is also fully pin and register compatible with the LM75 and TCN75.

#### Features

- 12-bit Temperature-to-Digital Converter

- Input Voltage Range from 3.0 V to 5.5 V

- Temperature Range from -55°C to +125°C

- SMBus/I<sup>2</sup>C Interface

- Overtemperature Indicator

- Support for SMBus/ALERT

- Shutdown Mode for Low Power Consumption

- One-shot Mode

- Available in 8-pin DFN, 8-pin Micro8 and SOIC Packages

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant

#### Applications

- Computer Thermal Monitoring

- Thermal Protection

- Isolated Sensors

- Battery Management

- Office Electronics

- Electronic Test Equipment

- Thermostat Controls

- System Thermal Management

# **ON Semiconductor®**

www.onsemi.com

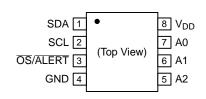

#### **PIN ASSIGNMENT**

MARKING DIAGRAMS

= Pb-Free Package

A

L

Υ

W

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 12 of this data sheet.

# Table 1. PIN FUNCTION DESCRIPTION

| Pin No. | Pin Name        | Description                                                                                                                             |

|---------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SDA             | SMBus/I <sup>2</sup> C Serial Bi-directional Data Input/Output. Open-drain pin; needs a pull-up resistor.                               |

| 2       | SCL             | Serial Clock Input. Open-drain pin; needs a pull-up resistor.                                                                           |

| 3       | OS/ALERT        | Over-temperature Indicator. Open-drain output; needs a pullup resistor. Active Low output.                                              |

| 4       | GND             | Power Supply Ground.                                                                                                                    |

| 5       | A2              | SMBus/I <sup>2</sup> C Serial Bus Address Selection Pin. Connect to GND or V <sub>DD</sub> to set the desired I <sup>2</sup> C address. |

| 6       | A1              | SMBus/I <sup>2</sup> C Serial Bus Address Selection Pin. Connect to GND or V <sub>DD</sub> to set the desired I <sup>2</sup> C address. |

| 7       | A0              | SMBus/I <sup>2</sup> C Serial Bus Address Selection Pin. Connect to GND or V <sub>DD</sub> to set the desired I <sup>2</sup> C address. |

| 8       | V <sub>DD</sub> | Positive Supply Voltage, 3.0 V to 5.5 V. Bypass to ground with a 0.1 $\mu$ F bypass capacitor.                                          |

#### **Table 2. ABSOLUTE MAXIMUM RATINGS**

| Rating                                              | Symbol              | Value                         | Unit |

|-----------------------------------------------------|---------------------|-------------------------------|------|

| Supply Voltage                                      | V <sub>DD</sub>     | -0.3 to +7                    | V    |

| Input Voltage on SCL, SDA, A2, A1, A0 and OS/ALERT. |                     | –0.3 to V <sub>DD</sub> + 0.3 | V    |

| Input Current on SDA, A2, A1, A0 and OS/ALERT.      | l <sub>IN</sub>     | –1 to +50                     | mA   |

| Maximum Junction Temperature                        | T <sub>J(max)</sub> | 150.7                         | °C   |

| Operating Temperature Range                         | T <sub>OP</sub>     | -55 to 125                    | °C   |

| Storage Temperature Range                           | T <sub>STG</sub>    | -65 to 160                    | °C   |

| ESD Capability, Human Body Model (Note 1)           | ESD <sub>HBM</sub>  | 2,000                         | V    |

| ESD Capability, Machine Model (Note 1)              | ESD <sub>MM</sub>   | 400                           | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

#### **Table 3. OPERATING RANGES**

| Rating                              | Symbol          | Min | Max | Unit |

|-------------------------------------|-----------------|-----|-----|------|

| Operating Supply Voltage            | V <sub>IN</sub> | 3.0 | 5.5 | V    |

| Operating Ambient Temperature Range | T <sub>A</sub>  | -55 | 125 | °C   |

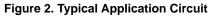

#### **Table 4. SMBus TIMING SPECIFICATIONS**

| Parameter                                          | Symbol              | Test Conditions          | Min | Тур | Max | Unit |

|----------------------------------------------------|---------------------|--------------------------|-----|-----|-----|------|

| Serial Clock Frequency                             | f <sub>SCL</sub>    |                          | DC  | -   | 400 | kHz  |

| Start Condition Hold Time                          | t <sub>HD:STA</sub> |                          | 0.6 | -   | -   | μs   |

| Stop Condition Setup Time                          | t <sub>SU:STO</sub> | 90% of SCL to 10% of SDA | 100 | -   | -   | ns   |

| Clock Low Period                                   | t <sub>LOW</sub>    |                          | 1.3 | -   | -   | μs   |

| Clock High Period                                  | t <sub>HIGH</sub>   |                          | 0.6 | -   | -   | μs   |

| Start Condition Setup Time                         | t <sub>SU:STA</sub> | 90% of SCL to 90% of SDA | 100 | -   | -   | ns   |

| Data Setup Time                                    | t <sub>SU:DAT</sub> | 10% of SDA to 10% of SCL | 100 | -   | -   | ns   |

| Data Hold Time (Note 2)                            | t <sub>HD:DAT</sub> | 10% of SCL to 10% of SDA | 0   | -   | 76  | ns   |

| SDA/SCL Rise Time                                  | t <sub>R</sub>      |                          | -   | 300 | -   | ns   |

| SDA/SCL Fall Time                                  | t <sub>F</sub>      |                          | -   | 300 | -   | ns   |

| Bus Free Time Between STOP<br>and START Conditions | t <sub>BUF</sub>    |                          | 1.3 | -   | _   | μs   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.This refers to the hold time when the NCT75 is writing data to the bus.

Figure 3. Serial Interface Timing

## **Table 5. ELECTRICAL CHARACTERISTICS**

(T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, V<sub>DD</sub> = 3.0 V to 5.5 V. All specifications for  $-55^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted.)

| Parameter                             | Test Conditions                                                                                                                                             | Min                 | Тур         | Max                   | Unit |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------|-----------------------|------|

| TEMPERATURE SENSOR AND ADC            |                                                                                                                                                             |                     |             |                       |      |

| Accuracy at $V_{DD}$ = 3.0 V to 5.5 V | $ \begin{array}{l} T_{A} = 0^{\circ}C \ to +70^{\circ}C \\ T_{A} = -25^{\circ}C \ to +100^{\circ}C \\ T_{A} = -55^{\circ}C \ to +125^{\circ}C \end{array} $ | -<br>-<br>-         | -<br>-<br>- | ±1<br>±2<br>±3        | °C   |

| ADC Resolution                        |                                                                                                                                                             | -                   | 12          | -                     | Bits |

| Temperature Resolution                |                                                                                                                                                             | -                   | 0.0625      | -                     | °C   |

| Temperature Conversion Time           | One-shot Mode                                                                                                                                               | -                   | 48.5        | -                     | ms   |

| Update Rate                           |                                                                                                                                                             | -                   | 80          | -                     | ms   |

| POWER REQUIREMENTS                    |                                                                                                                                                             |                     |             |                       |      |

| Supply Voltage                        |                                                                                                                                                             | 3.0                 | -           | 5.5                   | V    |

| POR Threshold                         |                                                                                                                                                             | 2.75                | -           | -                     | V    |

| Supply Current                        | Peak Current while Converting and I <sup>2</sup> C<br>Interface Inactive                                                                                    | -                   | _           | 0.8                   | mA   |

| Average Current                       | Average Current over 1 Conversion Cycle                                                                                                                     | -                   | 0.44        | 0.575                 | mA   |

| Shutdown Mode at 3.3 V                | Supply Current in Shutdown Mode                                                                                                                             | -                   | 3           | 12                    | μΑ   |

| OS/ALERT OUTPUT (OPEN DRAIN)          |                                                                                                                                                             |                     |             |                       |      |

| Output Low Voltage, V <sub>OL</sub>   | I <sub>OL</sub> = 4 mA                                                                                                                                      | -                   | 0.15        | 0.4                   | V    |

| Pin Capacitance                       |                                                                                                                                                             | -                   | 10          | -                     | pF   |

| High Output Leakage Current, IOH      | OS/ALERT Pin Pulled Up to 5.5 V                                                                                                                             | -                   | 0.1         | 5                     | μA   |

| DIGITAL INPUTS (SDA, SCL)             |                                                                                                                                                             |                     |             |                       |      |

| Input Current                         | $V_{IN} = 0 V$ to $V_{DD}$                                                                                                                                  | -                   | -           | 1                     | μΑ   |

| Input Low Voltage, V <sub>IL</sub>    | V <sub>DD</sub> = 3.3 V (Note 3)                                                                                                                            | -                   | -           | 0.3 x V <sub>DD</sub> | V    |

| Input High Voltage, V <sub>IH</sub>   | V <sub>DD</sub> = 3.3 V (Note 3)                                                                                                                            | 0.7xV <sub>DD</sub> | -           | -                     | V    |

| SCL, SDA Glitch Rejection             | Input Filtering Suppresses Noise Spikes of Less than 50 ns                                                                                                  | -                   | -           | 50                    | ns   |

| Pin Capacitance                       |                                                                                                                                                             | _                   | 3           | _                     | pF   |

| DIGITAL OUTPUT (SDA) (OPEN DRA        | IN)                                                                                                                                                         |                     |             |                       |      |

| Output High Current, I <sub>OH</sub>  | V <sub>OH</sub> = 5 V                                                                                                                                       | -                   | _           | 1                     | μA   |

| Output Low Voltage, V <sub>OL</sub>   | I <sub>OL</sub> = 3 mA                                                                                                                                      | -                   | -           | 0.4                   | V    |

| Output Capacitance, C <sub>OUT</sub>  |                                                                                                                                                             | -                   | 3           | -                     | pF   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 3. Guaranteed by characterization, not production tested.

#### APPLICATION INFORMATION

#### **Functional Description**

The NCT75 temperature sensor converts an analog temperature measurement to a digital representation by using an on-chip measurement transistor and a 12 bit Delta-Sigma ADC.

The device includes an open drain ALERT output which can be used to signal that the programmed temperature limit has been exceeded.

The two main modes of operation are normal and shutdown mode. In normal mode the NCT75 performs a new temperature conversion every 80 ms. This new value is then updated to the temperature value register (address 0x00) and also compared to the  $T_{OS}$  register limit (default = 80°C). If the temperature value register is read during the conversion sequence the value returned is the previously stored value. A bus read does not affect the conversion that is in progress.

In shutdown mode temperature conversion is disabled and the temperature value register holds the last valid temperature reading. The NCT75 can still be communicated with in this mode as the interface is still active. The device mode is controlled via bit 0 of the configuration register.

While in shutdown mode a conversion can be initiated by writing an arbitrary value to the one-shot register (0x04). This has the effect of powering up the NCT75, performing a conversion, comparing the new temperature with the programmed limit and then going back into shutdown mode.

The  $\overline{OS}/\overline{ALERT}$  pin can be configured in many ways to allow it to be used in many different system configurations.

The overtemperature output can be configured to operate as a comparator type output (which is self clearing once the temperature has returned below the hysteresis value) or an interrupt type output (which requires the master to read an internal register AND the temperature to return below the hysteresis value before going into an inactive state). The <u>ALERT</u> pin can also be configured as an active high or active low output.

#### **Temperature Measurement Results**

The results of the on chip temperature measurements are stored in the temperature value register and compared with the  $T_{OS}$  and  $T_{HYST}$  limit register.

The temperature value,  $T_{OS}$  and  $T_{HYST}$  registers are 16 bits wide and have a resolution of 0.0625°C. The data is stored as a 12 bit 2s complement word. The data is left justified, D15 is the MSB and is the sign bit. The four LSBs (D3 to D0) are always 0 as they are not part of the result.

While the ADC of the NCT75 can theoretically measure temperatures in the range of  $-128^{\circ}$ C to  $127^{\circ}$ C, the NCT75 is guaranteed to measure from  $-55^{\circ}$ C to  $+125^{\circ}$ C.

Table 6 shows the relevant temperature bits for a 12 bit temperature reading. A 2-byte read is required to obtain the full 12 bit temperature reading. If an 8 bit (1°C resolution) reading is required then a single byte read is sufficient.

| Temperature | Binary Value<br>D15 to D4 | Hex Value |

|-------------|---------------------------|-----------|

| –55°C       | 1100 1001 0000            | 0xC90     |

| –25°C       | 1110 0111 0000            | 0xE70     |

| –0.0625°C   | 1111 1111 1111            | 0xFFF     |

| 0°C         | 0000 0000 0000            | 0x000     |

| +0.0625°C   | 0000 0000 0001            | 0x001     |

| +25°C       | 0001 1001 0000            | 0x190     |

| +75.25°C    | 0100 1011 0100            | 0x4B4     |

| +100°C      | 0110 0100 0000            | 0x640     |

| +125°C      | 0111 1101 0000            | 0x7D0     |

Table 6. 12-BIT TEMPERATURE DATA FORMAT

#### **Temperature Data Conversion**

#### **12-bit Temperature Data Format**

- Positive Temperature = ADC Code (decimal)/16 Example  $190h = 400d/16 = +25^{\circ}C$

- Negative Temperature = (ADC Code(decimal) 4096)/16Example E70h =  $(3696d - 4096)/16 = -25^{\circ}C$

#### **One-shot Mode**

One of the features of the NCT75 is a One-shot Temperature Measurement Mode. This mode is useful if reduced power consumption is a design requirement.

To enable one-shot mode bit 5 of the configuration register needs to be set. Once, enabled, the NCT75 goes immediately into shutdown mode. Here, the current consumption is reduced to a typical value of 3  $\mu$ A. Writing address 0x04 to the address pointer register initiates a one-shot temperature measurement. This powers up the NCT75, carries out a temperature measurement, and then powers down again. The data written to this register is irrelevant and is not stored. It is the write operation that causes the one-shot conversion.

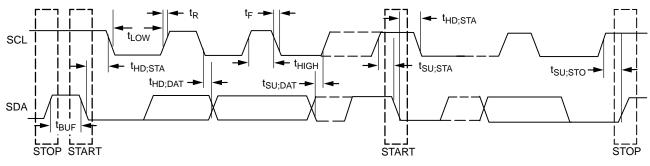

Figure 4. One-shot OS/ALERT Pin Operation

#### **Fault Queue**

A fault is defined as when the temperature exceeds a pre-defined temperature limit. This limit can be programmed in the  $T_{HYST}$  and the  $T_{OS}$  setpoint registers. Bits 3 and 4 of the configuration register determine the number of faults necessary to trigger the  $\overline{OS}/\overline{ALERT}$  pin. Up to six faults can be programmed to prevent false tripping when the NCT75 is used in a noisy temperature environment. In order for the  $\overline{OS}/\overline{ALERT}$  output to be set these faults must occur consecutively.

## Registers

The NCT75 contains six registers for configuring and reading the teperature: the address pointer register, 4 data registers and a one-shot register. The configuration register, the address pointer register and the one-shot register are all 8 bits wide while the temperature register,  $T_{HYST}$  and  $T_{OS}$  registers are all 16 bits wide. All registers, except for the temperature register, can be be read from and written to (the temperature register is read only). The power on state and address of each register are listed in Table 9.

#### Address Pointer Register

The address pointer register is used to select which register is to respond to a read or write operation. The three LSBs (P2, P1 & P0) of this write only register are used to select the appropriate register. On power up this register is loaded with a value of 0x00 and so points to the temperature register. Table 7 shows the bits of the address pointer register and Table 8 shows the pointer address selecting each of the registers available.

#### Table 7. ADDRESS POINTER REGISTER

|         | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|---------|----|----|----|----|----|----|----|----|

| Default | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

#### Table 8. REGISTER ADDRESSES SELECTION

| P2 | P1 | P0 | Register Selected          |

|----|----|----|----------------------------|

| 0  | 0  | 0  | Stored Temperature         |

| 0  | 0  | 1  | Configuration              |

| 0  | 1  | 0  | T <sub>HYST</sub> Setpoint |

| 0  | 1  | 1  | T <sub>OS</sub> Setpoint   |

| 1  | 0  | 0  | One-shot                   |

# Table 9. NCT75 REGISTER SET

| Register   |                          | Power-on<br>Default Value |    |  |  |  |

|------------|--------------------------|---------------------------|----|--|--|--|

| Address    | Register Name            | Hex                       | °C |  |  |  |

| 0x00 (R)   | Stored Temperature Value | 0x0000                    | 0  |  |  |  |

| 0x01 (R/W) | Configuration            | 0x00                      | -  |  |  |  |

| 0x02 (R/W) | T <sub>HYST</sub>        | 0x4B00                    | 75 |  |  |  |

| 0x03 (R/W) | T <sub>OS</sub>          | 0x5000                    | 80 |  |  |  |

| 0x04 (R/W) | One-shot                 | 0xXX                      | -  |  |  |  |

#### **Temperature Register**

The temperature measured by the parts internal sensor is stored in this 16-bit read only register. The data is stored in

#### Table 10. TEMPERATURE VALUE REGISTER

#### MSB

| MSB |     |     |     |     |     |    |    |    |    |    |    |    |    |    | LSB |

|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|-----|

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

| 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | Х  | Х  | Х  | Х   |

#### **Configuration Register**

This 8-bit read/write register is used to configure the NCT75 into its various modes of operation. The different modes are listed in Table 11 and explained in more detail below.

#### **Table 11. CONFIGURATION REGISTER**

| Bit | Configuration         | Default Value |

|-----|-----------------------|---------------|

| D7  | Reserved              | 0             |

| D6  | Reserved              | 0             |

| D5  | One-shot Mode         | 0             |

| D4  | Fault-queue           | 0             |

| D3  | Fault-queue           | 0             |

| D2  | OS/ALERT Pin Polarity | 0             |

| D1  | Cmp/Int Mode          | 0             |

| D0  | Shutdown Mode         | 0             |

#### D7: Reserved

Write 0 to this bit.

#### D6: Reserved

Write 0 to this bit.

#### D5: One-shot Mode

D5 = 0 Part is in normal mode and converting every 60 ms. (Default)

D5 = 1 Setting this bit puts the part into one-shot mode. The part is normally powered down in this mode until the one shot register is written to. Once this register is written to one conversion is performed and the part returns to its shutdown state.

#### Table 12. T<sub>HYST</sub> REGISTER

#### MSB

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| 0   | 1   | 0   | 0   | 1   | 0   | 1  | 1  | 0  | 0  | 0  | 0  | Х  | Х  | Х  | Х  |

#### T<sub>OS</sub> Register

This register stores the temperature limit at which the part asserts an  $\overline{OS}/\overline{Alert}$ . Once the measured temperature reaches this value an alert or overtemperature output is generated.

## Table 13. Tos REGISTER

MSB

| mob |     |     |     |     |     |    |    |    |    |    |    |    |    |    | 202 |

|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|-----|

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

| 0   | 1   | 0   | 1   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | Х  | Х  | Х  | Х   |

twos complement format with the MSB as the sign bit. The 8 MSBs must be read frist followed by the 8 LSBs.

D4 D3 These two bits determine how many overtemperature conditions occur before the OS/Alert pin is triggered. This helps to prevent false triggering of the output.

- $0 \quad 0 = 1$  Fault (Default)

- $0 \quad 1 = 2$  Faults

- 1 0 = 4 Faults

- 2 1 = 6 Faults

#### D2: OS/Alert pin polarity

This selects the polarity of the  $\overline{OS}/\overline{Alert}$  output pin.

- D2 = 0 Output is active low. (Default)

- D2 = 1 Output is active high.

#### D1: Cmp/Int

D1 = 0 Comparator mode. (Default)

D1 = 1 Interrupt mode.

#### D0: Shutdown

D0 = 0 Normal mode – part is fully powered. (Default) D0 = 1 Shutdown mode – all circuitry except for the SMBus interface is powered down. Write a 0 to this bit to power up again.

#### T<sub>HYST</sub> Register

The T<sub>HYST</sub> register stores the temperature hysteresis value for the overtemperature output. This value is picked to stop the OS/Alert pin from being asserted and de-asserted in noisy temperature environments. This limit is stored in the 16 bit register in twos complement format. The MSB is the temperature sign bit. The 8 MSBs must be read first followed by the 8 LSBs. The default value is +75°C.

The data is stored in twos complement format with the MSB as the sign bit. The 8 MSBs must be read frist followed by the 8 LSBs. The default limit +80°C.

LSB

|  | LSB |

|--|-----|

|  |     |

# **Serial Interface**

Control of the NCT75 is carried out via the SMBus/I<sup>2</sup>C compatible serial interface. The NCT75 is connected to this bus as a slave device, under the control of a master device.

#### Serial Bus Address

Control of the NCT75 is carried out via the serial bus. The NCT75 is connected to this bus as a slave device under the control of a master device. The NCT75 has a 7-bit serial address. The four MSBs are fixed and set to 1001 while the 3 LSBs can be configured by the user using pins 5, 6 and 7 (A2, A1 and A0). Each of these pins can be configured in one of two ways low or high. This gives eight different address options listed in Table 14 below. The state of these pins is continually sampled and so can be changed after power up.

|    | MS | Bs |    | LSBs |    |    | Address |

|----|----|----|----|------|----|----|---------|

| A6 | A5 | A4 | A3 | A2   | A1 | A0 | Hex     |

| 1  | 0  | 0  | 1  | 0    | 0  | 0  | 0x48    |

| 1  | 0  | 0  | 1  | 0    | 0  | 1  | 0x49    |

| 1  | 0  | 0  | 1  | 0    | 1  | 0  | 0x4A    |

| 1  | 0  | 0  | 1  | 0    | 1  | 1  | 0x4B    |

| 1  | 0  | 0  | 1  | 1    | 0  | 0  | 0x4C    |

| 1  | 0  | 0  | 1  | 1    | 0  | 1  | 0x4D    |

| 1  | 0  | 0  | 1  | 1    | 1  | 0  | 0x4E    |

| 1  | 0  | 0  | 1  | 1    | 1  | 1  | 0x4F    |

Table 14. SERIAL BUS ADDRESS OPTIONS

The NCT75 also features a SMBus/I<sup>2</sup>C timeout function whereby the SMBus/I<sup>2</sup>C interface times out after 22.5 ms of no activity on the SDA line. After this time, the NCT75 resets the SDA line back to its idle state (high impedance) and waits for the next start condition. Note that the timeout function is only active when the SDA line is held low. If the SDA line is held high with no activity for an extended period of time during a transaction, the timeout will not engage and the NCT75 will remain for the remainder of the command. The activity for an extended period

The serial bus protocol operates as follows:

1. The master initiates data transfer by establishing a start condition, defined as a high to low transition on the serial data line SDA, while the serial clock line SCL remains high. This indicates that an address/data stream is going to follow. All slave peripherals connected to the serial bus respond to the start condition and shift in the next eight bits, consisting of a 7-bit address (MSB first) plus a read/write  $(R/\overline{W})$  bit, which deternimes the direction of the data transfer i.e. whether data is written to, or read from, the slave device. The peripheral with the address corresponding to the transmitted address responds by pulling the data line low during the low period before the ninth clock pulse, known as the acknowledge bit. All other devices on the bus now remain idle while the selected device waits for data to be read from or written to it. If the  $R/\overline{W}$  bit is a zero then the master writes to the slave device. If the  $R/\overline{W}$  bit is a one then the master reads from the slave device.

- 2. Data is sent over the serial bus in sequences of nine clock pulses, eight bits of data followed by an acknowledge bit from the receiver of data. Transitions on the data line must occur during the low period of the clock signal and remain stable during the high period, since a low-to-high transition when the clock is high can be interpreted as a stop signal.

- 3. When all data bytes have been read or written, stop conditions are established. In write mode, the master pulls the data line high during the tenth clock pulse to assert a stop condition. In read mode, the master overrides the acknowledge bit by pulling the data line high during the low period before the ninth clock pulse. This is known as no acknowledge. The master takes the data line low during the low period before the tenth clock pulse, then high during the tenth clock pulse to assert a stop condition.

Any number of bytes of data can be transferred over the serial bus in one operation. However, it is not possible to mix read and write in one operation because the type of operation is determined at the beginning and cannot subsequently be changed without starting a new operation.

#### Writing Data

There are two types of writes used in the NCT75:

# Setting up the Address Pointer Register for a Register Read

To read data from a particular register, the address pointer register must hold the address of the register being read. To configure the address pointer register a single write operation (shown in Figure 5). It consists of the device address followed by the address being written to the address pointer register. This will then be followed by a read operation.

#### Writing Data to a Register

Due to the different size registers used by the NCT75, there are two types of write operations. One is for the 8 bit wide configuration register and the other for the 16 bit wide limit registers.

Figure 6 shows the sequence required to write to the configuration register. It consists of the device address, the data register being written to and the data being written the selected register.

The two temperature limit registers ( $T_{HYST}$  and  $T_{OS}$ ) are 16 bits wide and require two data bytes to be written to these registers. This sequence is shown in Figure 7. It consists of the device address, the data register being written to and the two data byes being written to the selected register.

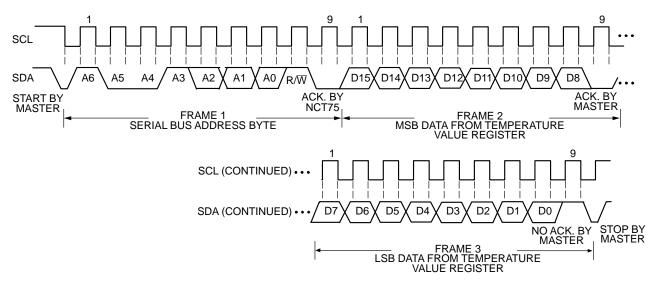

Figure 9. Reading Data from the Temperature Value Register with Preset Pointer Register

Figure 10. Typical Pointer Set followed by Two Bytes Register Read

# **Reading Data**

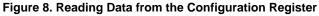

Reading data from the NCT75 is done in two different ways depending on the register being read. The configuration register is only 8 bits wide so a single byte read is used for this (shown in Figure 8). This consists of the device address followed by the data from the register.

Reading the data in the temperature value register requires a two byte read (shown in Figure 9). This consists of the device address, followed by two bytes of data from the temperature register (the first byte is the MSB). In both cases the address pointer register of the register being read must be written to prior to performing a read operation.

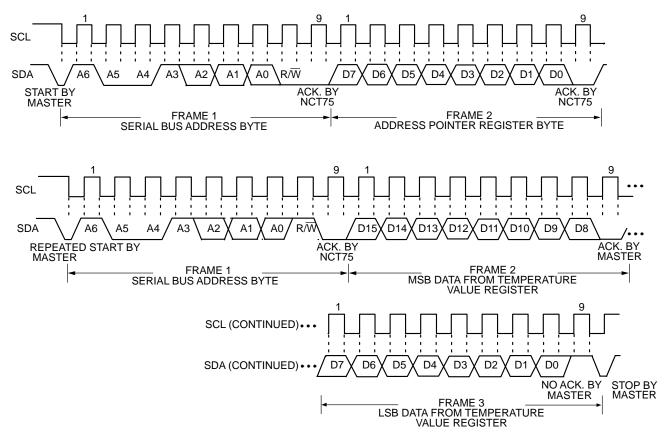

## **OS/ALERT** Output Overtemperature Modes

The  $\overline{OS}/\overline{ALERT}$  output pin can operate in two different modes – overtemperature mode and SMBus alert mode. The pin defaults to overtemperature mode on power up. This means that it becomes active when the measured temperature meets or exceeds the limit stored in the  $T_{OS}$ setpoint register. At this point it can deal with the event in one of two ways which depends on the mode it is in. The two overtemperature modes are: comparator mode and interrupt mode. Comparator mode is the default mode on power up. More information on comparator and interrupt modes alsong with the SMBus alert mode are explained below.

#### **Comparator Mode**

In Comparator Mode, the  $\overline{OS}/\overline{ALERT}$  pin becomes active when the measured temperature equals or exceeds the limit stored in the  $T_{OS}$  setpoint register. The pin returns to its inactive status when the temperature drops below the  $T_{HYST}$ setpoint register value.

NOTE: Shutdown mode does not reset the output state for comparator mode.

## Interrupt Mode

In the interrupt mode, the  $\overline{OS}/\overline{ALERT}$  pin becomes active when the temperature equals or exceeds the T<sub>OS</sub> limit for a consecutive number of faults. It can be reset by performing a read operation on any register in the NCT75. The output can only become active again when the T<sub>OS</sub> limit has been equalled or exceeded.

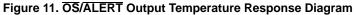

Figure 11 shows how both the interrupt and comparator modes operate in relation to the output pin  $(\overline{OS}/\overline{ALERT})$ . It also shows the operation of the polarity bit in the configuration register.

#### Table 15. ORDERING INFORMATION

| Model Number* | Temperature Range | Temperature Accuracy | Package Description | Package Option <sup>†</sup> |

|---------------|-------------------|----------------------|---------------------|-----------------------------|

| NCT75DMR2G    | –55°C to +125°C   | ±1°C                 | 8-lead Micro8       | 3,000 / Tape & Reel         |

| NCT75DR2G     | –55°C to +125°C   | ±1°C                 | 8-lead SOIC         | 2,500 / Tape & Reel         |

| NCT75MNR2G    | –55°C to +125°C   | ±1°C                 | 8-lead DFN (2x2)    | 3,000 / Tape & Reel         |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*The "G" suffix indicates Pb-Free package.

DIMENSIONS: MILLIMETERS

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER:                                                                  | 98AON18658D Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |  |  |  |  |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| DESCRIPTION: DFN8, 2.0X2.0, 0.5MM PITCH PAGE 1 C                                  |                                                                                                                                                                                                 |  |  |  |  |  |

| ON Semiconductor reserves the right<br>the suitability of its products for any pa | ON Semiconductor and                                                                                                                                                                            |  |  |  |  |  |

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

## STYLES ON PAGE 2

| DOCUMENT NUMBER: 98ASB42564B Electronic versions are uncontrolled except when accessed directly from the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONTROLLED OF the Printed versions are uncontrolled except when stamped "CONT |                                                                                             |                                                                                                                                                                                                                                                                                                               |                                                       |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SOIC-8 NB                                                                                   |                                                                                                                                                                                                                                                                                                               | PAGE 1 OF 2                                           |  |  |

| ON Semiconductor reserves the right<br>the suitability of its products for any pa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | to make changes without further notice to an<br>articular purpose, nor does ON Semiconducto | stries, LLC dba ON Semiconductor or its subsidiaries in the United States<br>y products herein. ON Semiconductor makes no warranty, representation<br>r assume any liability arising out of the application or use of any product or<br>ncidental damages. ON Semiconductor does not convey any license under | or guarantee regarding<br>r circuit, and specifically |  |  |

© Semiconductor Components Industries, LLC, 2019

#### SOIC-8 NB CASE 751-07 **ISSUE AK**

STYLE 1: PIN 1. EMITTER COLLECTOR 2. COLLECTOR З. 4. EMITTER EMITTER 5. 6. BASE 7 BASE 8. EMITTER STYLE 5: PIN 1. DRAIN 2. DRAIN З. DRAIN DRAIN 4. 5. GATE 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6. BASE, DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3. SOURCE GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. 4. TXE 5. RXE 6. VFF GND 7. 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 З. CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C З. REXT 4. GND 5. IOUT 6. IOUT 7. IOUT 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. EMITTER, #1 BASE, #2 2. З. EMITTER, #2 4. 5 COLLECTOR, #2 COLLECTOR, #2 6.

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 З. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: PIN 1. GROUND BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND BIAS 2 INPUT 6. 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE P-SOURCE 3 P-GATE 4. 5. P-DRAIN 6. P-DRAIN N-DRAIN 7. 8. N-DRAIN STYLE 18: PIN 1. ANODE 2. ANODE SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. 8. CATHODE STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3 COMMON CATHODE/VCC I/O LINE 3 4. 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND STYLE 26: PIN 1. GND 2 dv/dt ENABLE З. 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: PIN 1. DRAIN 1 DRAIN 1 2 GATE 2 З. SOURCE 2 4. SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5. 6.

| STYLE 3:<br>PIN 1. DRAIN, DIE #1<br>2. DRAIN, #1<br>3. DRAIN, #2<br>4. DRAIN, #2<br>5. GATE, #2<br>6. SOURCE, #2<br>7. GATE, #1<br>8. SOURCE, #1                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 7:<br>PIN 1. INPUT<br>2. EXTERNAL BYPASS<br>3. THIRD STAGE SOURCE<br>4. GROUND<br>5. DRAIN<br>6. GATE 3<br>7. SECOND STAGE Vd<br>8. FIRST STAGE Vd                    |

| STYLE 11:<br>PIN 1. SOURCE 1<br>2. GATE 1<br>3. SOURCE 2<br>4. GATE 2<br>5. DRAIN 2<br>7. DRAIN 1<br>8. DRAIN 1                                                             |

| STYLE 15:<br>PIN 1. ANODE 1<br>2. ANODE 1<br>3. ANODE 1<br>4. ANODE 1<br>5. CATHODE, COMMON<br>6. CATHODE, COMMON<br>7. CATHODE, COMMON<br>8. CATHODE, COMMON               |

| STYLE 19:<br>PIN 1. SOURCE 1<br>2. GATE 1<br>3. SOURCE 2<br>4. GATE 2<br>5. DRAIN 2<br>6. MIRROR 2<br>7. DRAIN 1<br>8. MIRROR 1                                             |

| STYLE 23:<br>PIN 1. LINE 1 IN<br>2. COMMON ANODE/GND<br>3. COMMON ANODE/GND<br>4. LINE 2 IN<br>5. LINE 2 OUT<br>6. COMMON ANODE/GND<br>7. COMMON ANODE/GND<br>8. LINE 1 OUT |

| STYLE 27:<br>PIN 1. ILIMIT<br>2. OVLO<br>3. UVLO<br>4. INPUT+<br>5. SOURCE<br>6. SOURCE<br>7. SOURCE<br>8. DRAIN                                                            |

#### DATE 16 FEB 2011

STYLE 4: ANODE ANODE PIN 1. 2. ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 BASE, #2 З. COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE SOURCE 2. 3. 4. GATE 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE 2. EMITTER З. COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE CATHODE COLLECTOR/ANODE 6. 7. COLLECTOR/ANODE 8. STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET З. 4. GND 5. 6. V MON VBULK 7. VBULK 8. VIN

| DOCUMENT NUMBER:                                                                  | 98ASB42564B Electronic versions are uncontrolled except when accessed directly from the Document Reposite<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |                                                                                                                                                                                                                                                                                                             |                                                       |  |  |  |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| DESCRIPTION: SOIC-8 NB PAGE                                                       |                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                             |                                                       |  |  |  |

| ON Semiconductor reserves the right<br>the suitability of its products for any pa | to make changes without further notice to an<br>articular purpose, nor does ON Semiconducto                                                                                                  | stries, LLC dba ON Semiconductor or its subsidiaries in the United States<br>y products herein. ON Semiconductor makes no warranty, representation<br>r assume any liability arising out of the application or use of any product o<br>cidental damages. ON Semiconductor does not convey any license under | or guarantee regarding<br>r circuit, and specifically |  |  |  |

SOURCE 1/DRAIN 2

7.

8. GATE 1

7.

8

rights of others.

COLLECTOR, #1

COLLECTOR, #1

| DOCUMENT NUMBER:                                                                  | UMBER: 98ASB14087C Electronic versions are uncontrolled except when accessed directly from the Document R<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |                                                                                                                                                                                                                                                                                                              |                                                       |  |  |  |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| DESCRIPTION: MICRO8                                                               |                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                              |                                                       |  |  |  |

| ON Semiconductor reserves the right<br>the suitability of its products for any pa | to make changes without further notice to an<br>articular purpose, nor does ON Semiconducto                                                                                                  | stries, LLC dba ON Semiconductor or its subsidiaries in the United States<br>y products herein. ON Semiconductor makes no warranty, representation<br>r assume any liability arising out of the application or use of any product o<br>acidental damages. ON Semiconductor does not convey any license under | or guarantee regarding<br>r circuit, and specifically |  |  |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor date sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use a a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor houteds for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

ON Semiconductor Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Phone: 011 421 33 790 2910 Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

onsemi:

NCT75DMR2G NCT75DR2G NCT75MNR2G