## Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

## **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

## **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

## CY8CKIT-040

# PSoC 4000 Pioneer Kit Guide

Doc. # 001-91316 Rev. \*G

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 www.cypress.com

#### Copyrights

© Cypress Semiconductor Corporation, 2014–2019. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PUR-POSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress does not assume any liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

# Contents

|    | Sarety        | Information                                                   | 5  |

|----|---------------|---------------------------------------------------------------|----|

|    | Regu          | ulatory Compliance                                            | 5  |

|    | Gene          | eral Safety Instructions                                      | 6  |

| 1. | Introdu       | ction                                                         | 7  |

|    | 1.1           | Kit Contents                                                  | 7  |

|    | 1.2           | PSoC Creator                                                  |    |

|    |               | 1.2.1 PSoC Creator Code Examples                              |    |

|    |               | 1.2.2 Kit Code Example                                        |    |

|    |               | 1.2.3 PSoC Creator Help                                       |    |

|    | 1.3           | Getting Started                                               |    |

|    | 1.4           | Additional Learning Resources                                 | 12 |

|    | 1.5           | Technical Support                                             | 13 |

|    | 1.6           | Documentation Conventions                                     | 13 |

| 2. | Softwa        | re Installation                                               | 14 |

|    | 2.1           | Before You Begin                                              | 14 |

|    | 2.2           | Install Software                                              |    |

|    | 2.3           | Install Hardware                                              | 16 |

|    | 2.4           | Uninstall Software                                            | 17 |

| 3. | Kit Operation |                                                               | 18 |

|    | 3.1           | Kit Overview                                                  | 18 |

|    | 3.2           | Kit USB Connection                                            | 20 |

|    | 3.3           | Programming and Debugging PSoC 4000                           | 21 |

|    |               | 3.3.1 Using the Onboard PSoC 5LP Programmer and Debugger      | 21 |

|    |               | 3.3.2 Using the CY8CKIT-002 MiniProg3 Programmer and Debugger | 22 |

|    | 3.4           | USB-I2C Bridge                                                |    |

|    | 3.5           | USB-UART Bridge                                               |    |

|    | 3.6           | Updating the Onboard Programmer Firmware                      | 26 |

| 4. | Hardwa        | ire                                                           | 28 |

|    | 4.1           | Board Details                                                 | 28 |

|    | 4.2           | Block Diagram                                                 | 31 |

|    | 4.3           | Kit Component Details                                         |    |

|    |               | 4.3.1 CY8CKIT-040 Baseboard Components                        |    |

|    |               | 4.3.2 CY8CKIT-040 CapSense Trackpad Shield Board              | 46 |

| 5. | Code E        | xamples                                                       | 48 |

|    | 5.1           | Using the Kit Code Examples                                   | 48 |

|    | 5.2           | Project: Blinking LED                                         |    |

|    |           | 5.2.1 Project Overview                                    | 53  |

|----|-----------|-----------------------------------------------------------|-----|

|    |           | 5.2.2 Project Description                                 | 54  |

|    |           | 5.2.3 Verify Output                                       | 55  |

|    | 5.3       | Project: CapSense Proximity and UART                      |     |

|    |           | 5.3.1 Project Overview                                    | 56  |

|    |           | 5.3.2 Project Description                                 | 57  |

|    |           | 5.3.3 Verify Output                                       | 66  |

|    | 5.4       | Project: CapSense Touchpad with I2C Tuner                 | 73  |

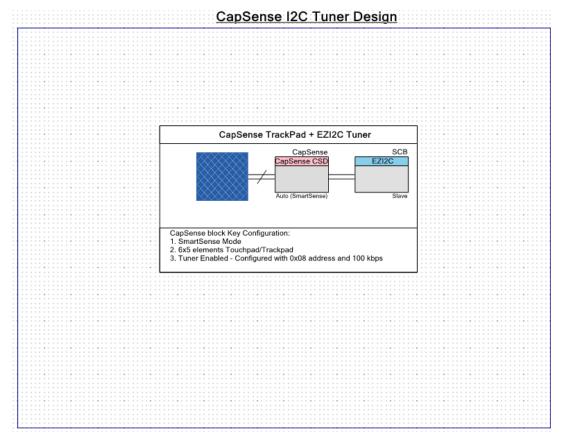

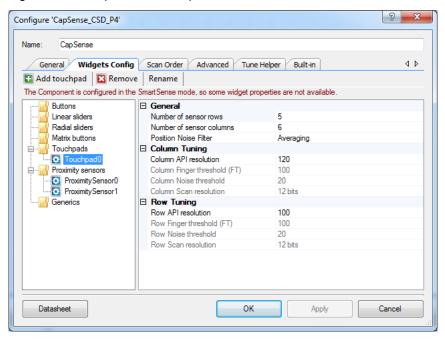

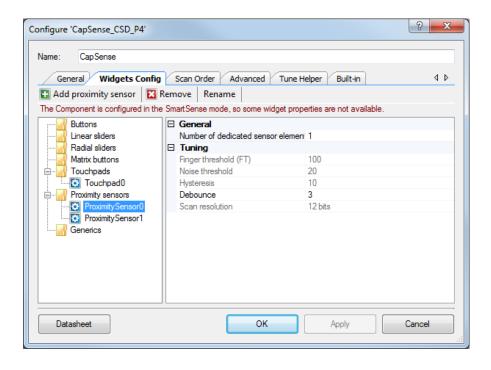

|    |           | 5.4.1 Project Overview                                    | 73  |

|    |           | 5.4.2 Project Description                                 | 75  |

|    |           | 5.4.3 Verify Output                                       | 78  |

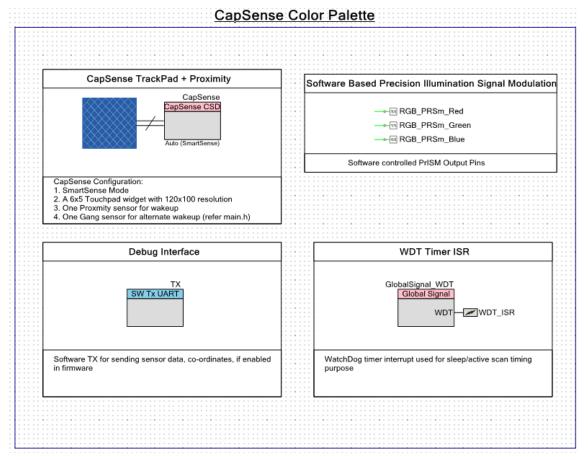

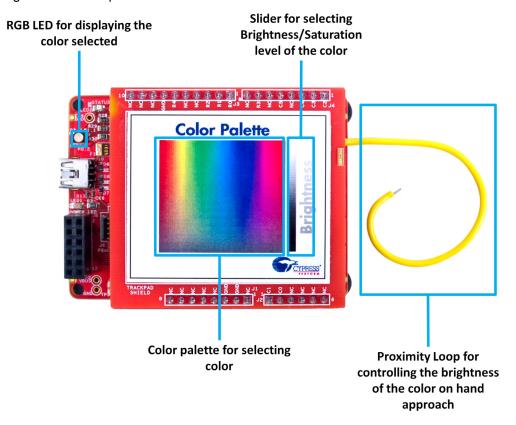

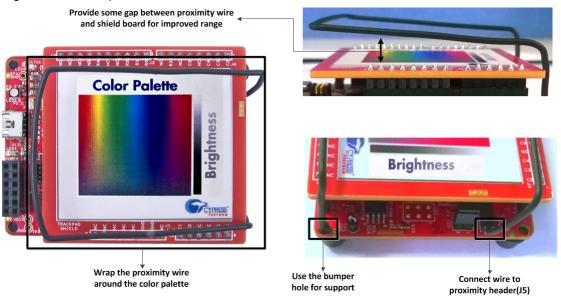

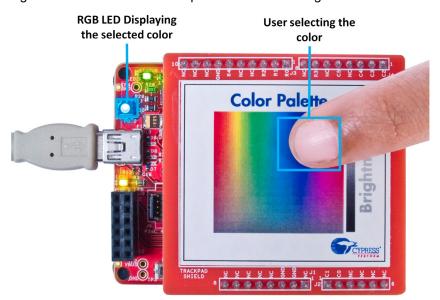

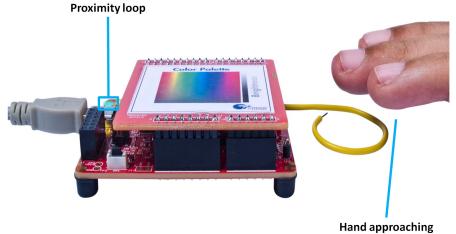

|    | 5.5       | Project: Color Palette                                    | 83  |

|    |           | 5.5.1 Project Overview                                    | 83  |

|    |           | 5.5.2 Project Description                                 | 83  |

|    |           | 5.5.3 Verify Output                                       | 100 |

| 6. | Advanc    | ced Topics                                                | 102 |

|    | 6.1       | Using PSoC 5LP as a USB-I2C Bridge                        | 102 |

|    | 6.2       | Using FM24W256 F-RAM                                      |     |

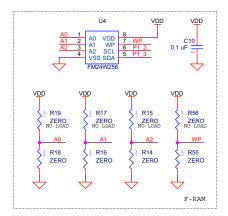

|    |           | 6.2.1 Address Selection                                   | 111 |

|    |           | 6.2.2 Write/Read Operation                                | 112 |

|    |           | 6.2.3 Example Firmware                                    |     |

|    | 6.3       | Using PSoC 5LP as a USB-UART Bridge                       | 115 |

|    | 6.4       | Developing Applications for PSoC 5LP                      | 126 |

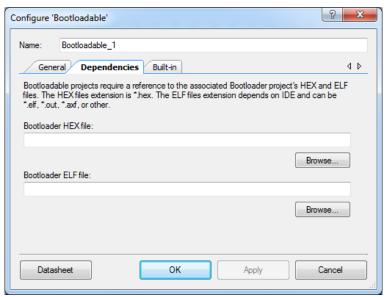

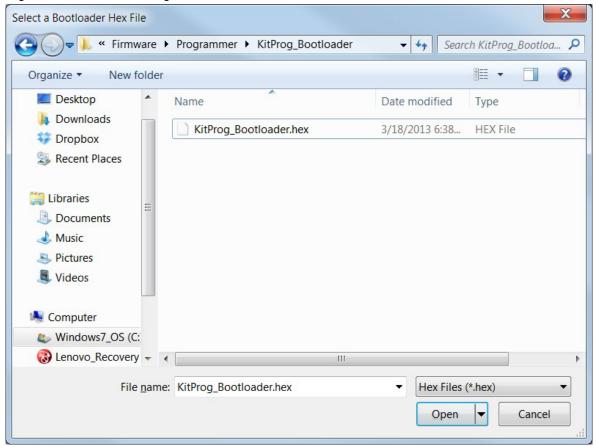

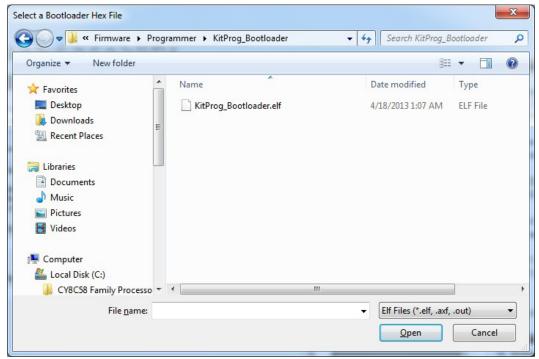

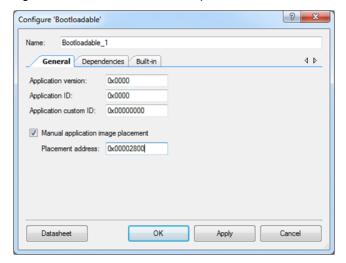

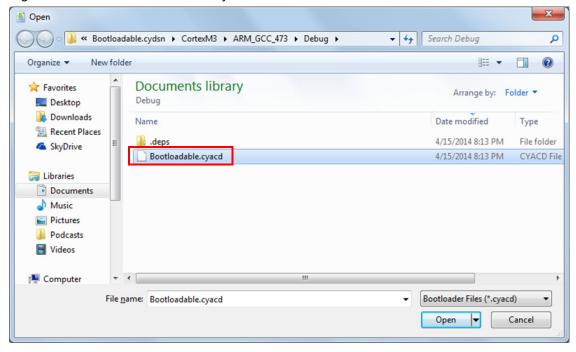

|    |           | 6.4.1 Building a Bootloadable Project for PSoC 5LP        | 127 |

|    |           | 6.4.2 Building a Normal Project for PSoC 5LP              | 135 |

|    | 6.5       | PSoC 5LP Factory Program Restore Instructions             | 136 |

|    |           | 6.5.1 PSoC 5LP Programmed with a Bootloadable Application | 136 |

|    |           | 6.5.2 PSoC 5LP Programmed with a Standard Application     | 140 |

| Α. | Append    | lix                                                       | 143 |

|    | A.1       | CY8CKIT-040 Schematics                                    | 143 |

|    | A.2       | Pin Assignment Table                                      | 148 |

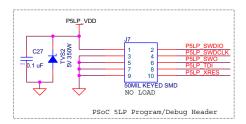

|    | A.3       | Program and Debug Headers                                 |     |

|    | A.4       | Use of Zero-ohm Resistors and No Load                     |     |

|    | A.5       | KitProg Status LED States                                 | 152 |

|    | A.6       | Bill of Materials                                         | 153 |

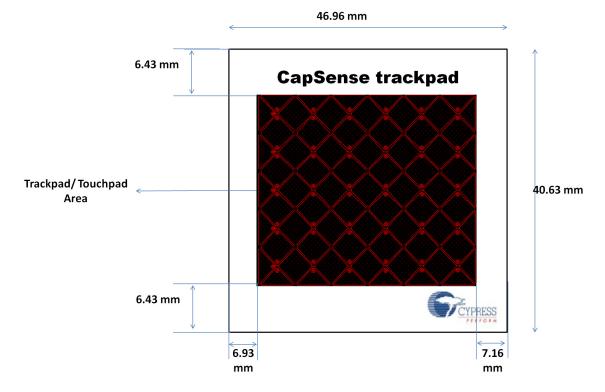

|    | A.7       | Trackpad/Touchpad Sticker Details                         | 156 |

|    | A.8       | Regulatory Compliance Information                         |     |

|    | A.9       | Migrating Projects Across Different Pioneer Series Kits   | 157 |

| Re | evision H | istory                                                    | 161 |

|    | Docu      | ument Revision History                                    | 161 |

|    |           |                                                           |     |

# Safety Information

## **Regulatory Compliance**

The CY8CKIT-040 PSoC® 4000 Pioneer Kit is intended for use as a development platform for hardware or software in a laboratory environment. The board is an open system design, which does not include a shielded enclosure. For this reason, the board may cause interference to other electrical or electronic devices in close proximity. In a domestic environment, this product may cause radio interference. In such cases, the user may be required to take adequate preventive measures. Also, this board should not be used near any medical equipment or RF devices.

Attaching additional wiring to this product or modifying the product operation from the factory default may affect its performance and cause interference with other apparatus in the immediate vicinity. If such interference is detected, suitable mitigating measures should be taken.

The CY8CKIT-040 as shipped from the factory has been verified to meet with requirements of CE as a Class A product.

The CY8CKIT-040 contains electrostatic discharge (ESD) sensitive devices. Electrostatic charges readily accumulate on the human body and any equipment, and can discharge without detection. Permanent damage may occur to devices subjected to high-energy discharges. Proper ESD precautions are recommended to avoid performance degradation or loss of functionality. Store unused CY8CKIT-040 boards in the protective shipping package.

End-of-Life/Product Recycling

The end of life for this kit is five years from the date of manufacture mentioned on the back of the box. Contact your nearest recycler to discard the kit.

## **General Safety Instructions**

### **ESD Protection**

ESD can damage boards and associated components. Cypress recommends that the user perform procedures only at an ESD workstation. If an ESD workstation is not available, use appropriate ESD protection by wearing an antistatic wrist strap attached to the chassis ground (any unpainted metal surface) on the board when handling parts.

## **Handling Boards**

CY8CKIT-040 boards are sensitive to ESD. Hold the board only by its edges. After removing the board from its box, place it on a grounded, static free surface. Use a conductive foam pad if available. Do not slide the board over any surface.

## 1. Introduction

Thank you for your interest in the PSoC<sup>®</sup> 4000 Pioneer Kit. The kit is designed as an easy-to-use and inexpensive development kit, highlighting the unique flexibility of the PSoC 4000 architecture. Designed for flexibility, this kit offers footprint compatibility with several third-party Arduino™ shields. In addition, the board features an RGB LED, integrated USB programmer/debugger, a program/debug header, USB-UART/I<sup>2</sup>C bridges, a proximity header, and an Arduino-compatible CapSense<sup>®</sup> Trackpad shield. This kit supports either 5 V or 3.3 V as power supply voltages.

The PSoC 4000 Pioneer Kit is based on the PSoC 4000 device family, delivering a programmable platform for a wide range of embedded applications. The PSoC 4000 is the smallest member of the PSoC 4 platform with support for CapSense, timer, counter, and pulse width modulator (TCPWM), I<sup>2</sup>C master or slave, and up to 20 GPIOs. PSoC 4000 is a cost-optimized, entry-level PSoC 4 device targeted as socket replacements for obsolete and/or proprietary 8-bit and 16-bit MCUs. PSoC 4000 with its ARM Cortex-M0 core provides 32 programmable peripherals including CapSense.

## 1.1 Kit Contents

The CY8CKIT-040 PSoC 4000 Pioneer Kit contains the following (see Figure 1-1):

- PSoC 4000 Pioneer board

- Trackpad shield board with a color palette sticker

- Quick Start Guide

- USB Standard-A to Mini-B cable

- Six jumper wires

**Note:** Trackpad and Touchpad denote the same in the context of this document and can be used interchangeably.

Figure 1-1. Kit Contents

Inspect the contents of the kit; if you find any part missing, contact your nearest Cypress sales office for help: www.cypress.com/support.

Download the latest version of the kit setup file from www.cypress.com/CY8CKIT-040.

## 1.2 PSoC Creator

PSoC Creator™ is a state-of-the-art, easy-to-use integrated design environment (IDE). It introduces revolutionary hardware and software co-design, powered by a library of preverified and precharacterized PSoC Components. With PSoC Creator, you can:

- 1. Drag and drop Components to build your hardware system design in the main design workspace

- 2. Co-design your application firmware with the PSoC hardware

- 3. Configure Components using configuration tools

- 4. Explore the library of 100+ Components

- 5. Access Component datasheets

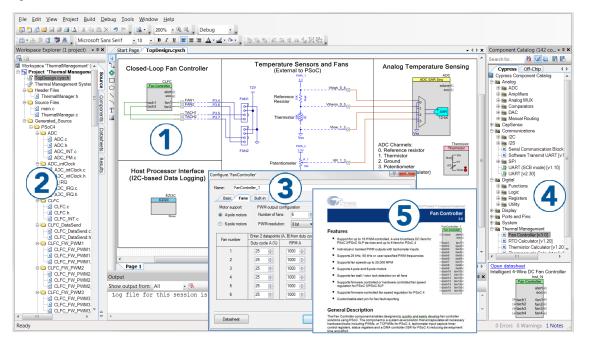

Figure 1-2. PSoC Creator Features

PSoC Creator also enables you to tap into an entire tool ecosystem with integrated compiler chains and production programmers for PSoC devices.

For more information, visit www.cypress.com/psoccreator. Visit PSoC Creator training page for video tutorials on learning and using PSoC Creator.

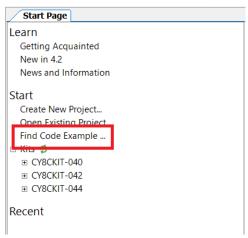

## 1.2.1 PSoC Creator Code Examples

PSoC Creator includes a large number of code examples. These examples are accessible from the PSoC Creator Start Page, as Figure 1-3 shows.

Code examples can speed up your design process by starting you off with a complete design, instead of a blank page. The code examples also show how PSoC Creator Components can be used for various applications.

In the **Find Code Example** dialog, you have several options:

- Filter for examples based on architecture or device family or keyword.

- Select from the menu of examples offered based on the Filter Options.

- View the example project's description (on the **Documentation** tab).

- View the code from the **Sample Code** tab. You can copy the code from this window and paste to your project, which can help speed up code development.

- Create new workspace for the example project. This can speed up your design process by starting you off with a complete, basic design. You can then adapt that design to your application.

Figure 1-3. Code Examples in PSoC Creator

## 1.2.2 Kit Code Example

In addition to the examples built into PSoC Creator, this kit includes a simple example, which can be used to quickly evaluate the functionality of this kit. The example is described in the Code Examples chapter on page 48. In addition, the chapter also includes a section explaining how to use PSoC Creator code examples with the kit by taking one example.

## 1.2.3 PSoC Creator Help

Visit the PSoC Creator home page to download the latest version of PSoC Creator. Then, launch PSoC Creator and navigate to the following items:

- Quick Start Guide: Choose Help > Documentation > Quick Start Guide. This guide gives you the basics for developing PSoC Creator projects.

- Simple Component code examples: Choose File > Code Example. These code examples demonstrate how to configure and use PSoC Creator Components.

- System Reference Guide: Choose Help > System Reference Guides. This guide lists and describes the system functions provided by PSoC Creator.

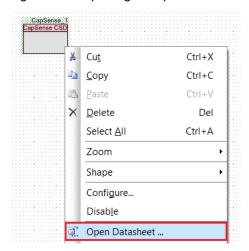

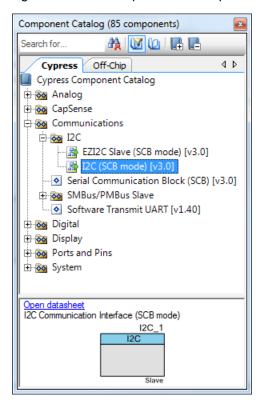

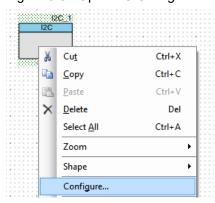

- Component datasheets: Right-click a Component and select Open Datasheet, as shown in Figure 1-4 on page 11. Visit the PSoC 4 Component Datasheets page for a list of all PSoC 4 Component datasheets.

Figure 1-4. Opening Component Datasheet

## 1.3 Getting Started

This guide helps acquaint you with the PSoC 4000 Pioneer Kit.

- The Software Installation chapter on page 14 describes the installation of the kit software.

- The Kit Operation chapter on page 18 explains how to program the PSoC 4 with a programmer and debugger, either the onboard PSoC 5LP or the external MiniProg3 (CY8CKIT-002).

- The Hardware chapter on page 28 details the hardware operation.

- The Code Examples chapter on page 48 describes the code examples that are provided with the kit.

- The Advanced Topics chapter on page 102 deals with topics such as building projects for PSoC 5LP, using onboard F-RAM, USB-UART functionality, and USB-I<sup>2</sup>C functionality of PSoC 5LP.

- The Appendix on page 143 provides schematics, pin assignments, information on the use of zero-ohm resistors, troubleshooting details, and the bill of materials (BOM).

## 1.4 Additional Learning Resources

Cypress provides a wealth of information at <a href="https://www.cypress.com">www.cypress.com</a> to help you to select the right PSoC device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see KBA86521, How to Design with PSoC 3, PSoC 4, and PSoC 5LP. The following is an abbreviated list for PSoC 4:

- Overview: PSoC Portfolio and PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, or PSoC 5LP. In addition, PSoC Creator includes a device selection tool.

- Datasheets: Describe and provide electrical specifications for the PSoC 4000 device family.

- CapSense Design Guide: Learn how to design capacitive touch-sensing applications with the PSoC 4 family of devices.

- Application Notes and Code Examples: Cover a broad range of topics, from basic to advanced level. Many of the application notes include code examples. Visit the PSoC 3/4/5 Code Examples webpage for a list of all available PSoC Creator code examples. To access code examples from within PSoC Creator, see PSoC Creator Code Examples on page 10.

- Technical Reference Manuals (TRM): Provide detailed descriptions of the architecture and registers in each PSoC 4 device family.

- Development Kits:

- CY8CKIT-040, CY8CKIT-042, and CY8CKIT-044 are easy-to-use and inexpensive development platforms. These kits include connectors for Arduino-compatible shields and Digilent Pmod peripheral modules.

- CY8CKIT-049 and CY8CKIT-043 are very low-cost prototyping platforms for sampling PSoC 4 devices.

- The MiniProg3 kit provides an interface for flash programming and debug.

- Knowledge Base Articles (KBA): Provide design and application tips from experts on using the device.

- PSoC Creator Training: Visit www.cypress.com/training for a comprehensive list of video trainings on PSoC Creator.

- Learning From Peers: Visit www.cypress.com/forums to meet enthusiastic PSoC developers discussing the next generation embedded systems on Cypress Developer Community Forums.

## 1.5 Technical Support

If you have any questions, you can create a support request at the Cypress Technical Support page.

If you are in the United States, you can talk to our technical support team by calling our toll-free number: +1-800-541-4736. Select option 3 at the prompt. If you are outside United States, you can talk to our technical support team by calling: +1 (408) 943-2600 Ext. 3.

You can also use the following support resources if you need quick assistance.

- Self-help

- Local Sales Office Locations

## 1.6 Documentation Conventions

Table 1-1. Document Conventions for Guides

| Convention         | Usage                                                                                                                   |

|--------------------|-------------------------------------------------------------------------------------------------------------------------|

| Courier New        | Displays file locations, user-entered text, and source code: C:\cd\icc\                                                 |

| Italics            | Displays file names and reference documentation: Read about the sourcefile.hex file in the PSoC Creator User Guide.     |

| [Bracketed, Bold]  | Displays keyboard commands in procedures: [Enter] or [Ctrl] [C]                                                         |

| File > Open        | Represents menu paths: File > Open > New Project                                                                        |

| Bold               | Displays commands, menu paths, and icon names in procedures:<br>Click the <b>File</b> icon and then click <b>Open</b> . |

| Times New Roman    | Displays an equation: $2 + 2 = 4$                                                                                       |

| Text in gray boxes | Describes cautions or a unique functionality of the product.                                                            |

# 2. Software Installation

This section describes the installation of the CY8CKIT-040 PSoC 4000 Pioneer Kit software and the prerequisites.

## 2.1 Before You Begin

All Cypress software installations require administrator privileges. However, this is not the case for installed software. Before you install the kit software, close any other Cypress software that is currently running.

## 2.2 Install Software

Follow these steps to install the CY8CKIT-040 PSoC 4000 Pioneer Kit software:

1. Download the CY8CKIT-040 software.

The CY8CKIT-040 software is available in three different formats for download:

- a. CY8CKIT-040 Kit Only: This executable file installs only the kit contents, which include kit code examples, hardware files, and user documents. This package can be used if all the software prerequisites listed in step 5 are installed on your PC.

- b. **CY8CKIT-040 Kit Setup**: This installation package contains all kit contents along with PSoC Creator, Cypress Document Manager, and PSoC Programmer. However, it does not include the Windows Installer or Microsoft .NET framework packages. If these packages are not on your computer, the installer directs you to download and install them from the Internet.

- c. CY8CKIT-040 CD ISO: This file is a complete package, stored in a CD-ROM image format that you can use to create a CD or extract using ISO extraction programs, such as WinRAR. The file can also be mounted like a virtual CD using virtual drive programs such as Virtual CloneDrive or MagicISO. This file includes all the required software, utilities, drivers, hardware files, and user documents.

- 2. If you have downloaded the ISO file, mount it in a virtual drive. Extract the ISO contents if you do not have a virtual drive to mount. Double-click *cyautorun.exe* in the root directory of the extracted content or mounted ISO if 'Autorun from CD/DVD' is not enabledd in the PC. The installation window shown in Figure 2-1 will appear automatically. Note: If you are using the 'Kit Setup' or 'Kit Only' file, then go to step 4 for installation.

- 3. Click Install CY8CKIT-040 to start the kit installation, as shown in Figure 2-1.

Figure 2-1. Kit Installer Startup Screen

- Select the folder in which you want to install the CY8CKIT-040 kit-related files. Choose the directory and click Next.

- 5. When you click **Next**, the CY8CKIT-040 ISO installer automatically installs the required software, if it is not present on your computer.

Following is the required software:

- a. PSoC Creator 4.2 or later: Download the latest version from www.cypress.com/psoccreator.

- b. PSoC Programmer 3.27.1 or later: Download the latest version from www.cypress.com/programmer.

6. Choose the **Typical/Custom/Complete** installation type in the Product Installation Overview window, as shown in Figure 2-2. Click **Next** after you select the installation type.

Figure 2-2. Product Installation Overview Window

- Read and Accept the End-User License Agreement and click **Next** to proceed with the installation.

- 8. When the installation begins, a list of packages appears on the installation page. A green check mark appears next to each package after successful installation.

- 9. Enter your contact information or select the check box **Continue Without Contact Information**. Click **Finish** to complete the CY8CKIT-040 kit installation.

- 10. After the installation is complete, the kit contents are available at the following location:

<Install\_Directory>\CY8CKIT-040 PSoC 4000 Pioneer Kit\<version>

#### Default location:

#### Windows 7 (64-bit):

C:\Program Files (x86)\Cypress\CY8CKIT-040 PSoC 4000 Pioneer Kit\<version> Windows 7 (32-bit):

C:\Program Files\Cypress\CY8CKIT-040 PSoC 4000 Pioneer Kit\<version>

**Note:** For Windows 7/8/8.1/10 users, the installed files and the folder are read-only. To use the installed code examples, follow the steps outlined in the Code Examples chapter on page 48. These steps will create an editable copy of the example in a path that you choose so the original installed example is not modified.

## 2.3 Install Hardware

There is no additional hardware installation required for this kit.

## 2.4 Uninstall Software

You can uninstall the CY8CKIT-040 PSoC 4000 Pioneer Kit software using one of the following methods:

- Go to Start > All Programs > Cypress > Cypress Update Manager > Cypress Update Manager. Select the Uninstall button that corresponds to the kit software.

- Go to Start > Control Panel > Programs and Features (or Add/Remove Programs for Windows XP). Select the Uninstall/Change button that corresponds to the kit software.

# 3. Kit Operation

## 3.1 Kit Overview

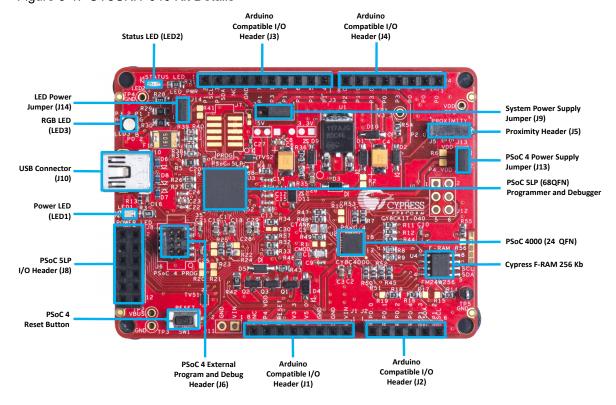

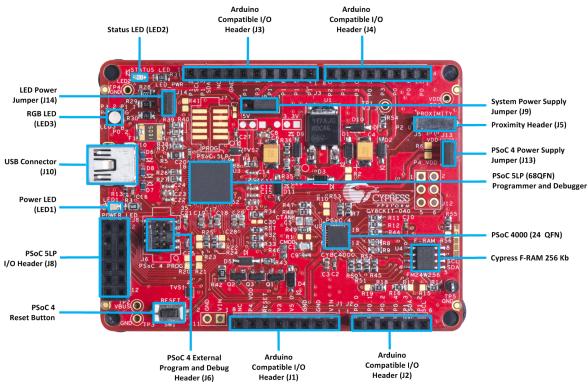

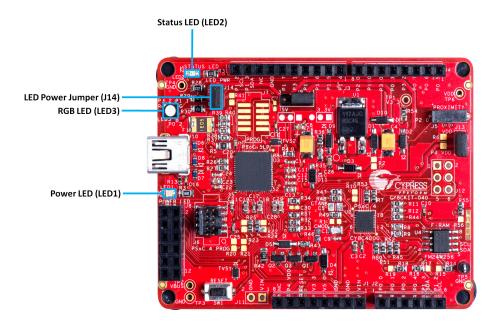

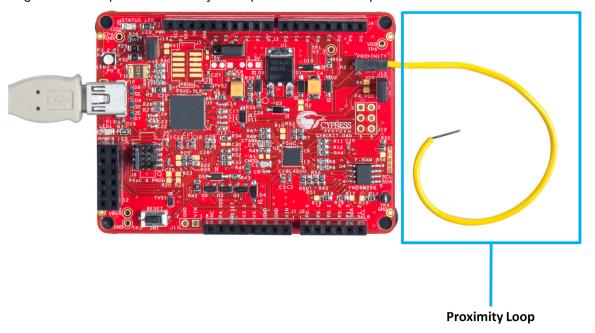

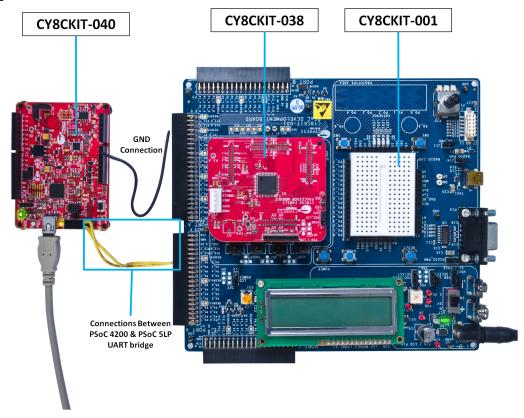

The PSoC 4000 Pioneer Kit can be used to develop applications using the PSoC 4000 family of devices. The kit includes two boards – an Arduino-compatible baseboard and a CapSense-based Trackpad shield board. Figure 3-1 is an image of the PSoC 4000 Pioneer Kit baseboard and shield board with a markup of the onboard components.

Figure 3-1. CY8CKIT-040 Kit Details

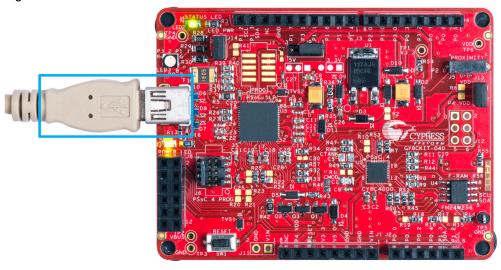

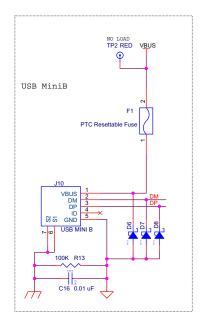

## 3.2 Kit USB Connection

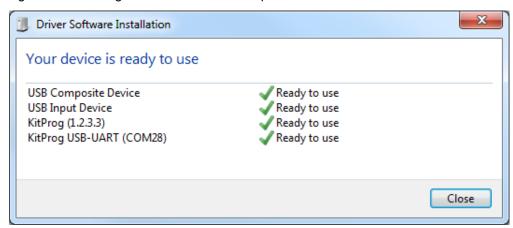

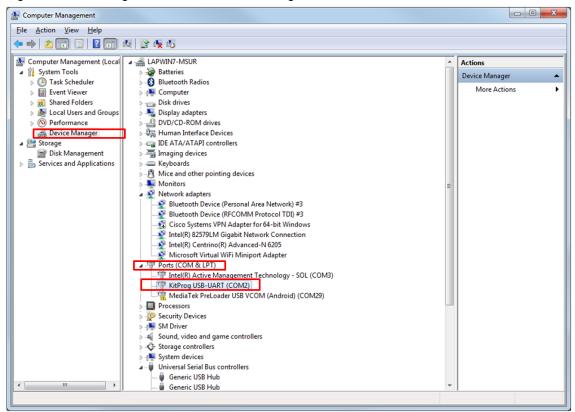

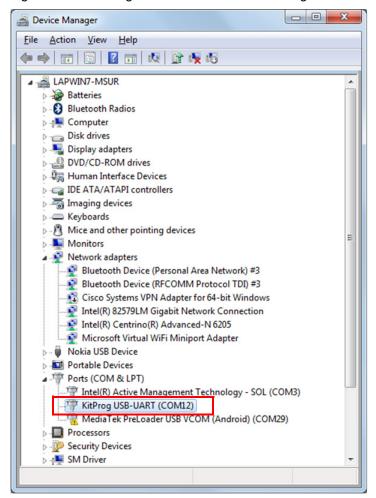

The PSoC 4000 Pioneer Kit connects to the PC over a USB interface (see Figure 3-2). The kit enumerates as a composite device and three separate devices appear under the **Device Manager** in the Windows operating system. See Table 3-1, and Figure 3-3.

Figure 3-2. Kit USB Connection

Table 3-1. PSoC 4000 Pioneer Kit in Device Manager After Enumeration

| Port                 | Description                                            |

|----------------------|--------------------------------------------------------|

| USB Composite Device | Composite device                                       |

| USB Input Device     | USB-I <sup>2</sup> C bridge, KitProg command interface |

| KitProg              | Programmer and debugger                                |

| KitProg USB-UART     | USB-UART bridge, which appears as the COM# port        |

Figure 3-3. KitProg Driver Installation Complete

## 3.3 Programming and Debugging PSoC 4000

The kit allows programming and debugging of the PSoC 4 device in two modes:

- Using the Onboard PSoC 5LP Programmer and Debugger on page 21

- Using the CY8CKIT-002 MiniProg3 Programmer and Debugger on page 22

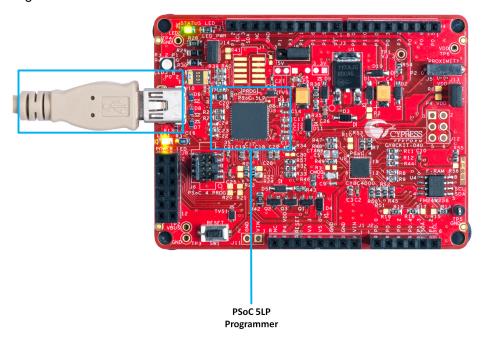

## 3.3.1 Using the Onboard PSoC 5LP Programmer and Debugger

The default programming interface for the kit is a USB-based, onboard programming interface. Before trying to program the device, PSoC Creator and PSoC Programmer must be installed. See Install Software on page 14 for information on installing the kit software.

1. To program the device, plug the USB cable into the programming USB connector J10, as shown in Figure 3-4. The kit will enumerate as a composite device. See Kit USB Connection on page 20 for details.

Figure 3-4. Connect USB Cable to J10

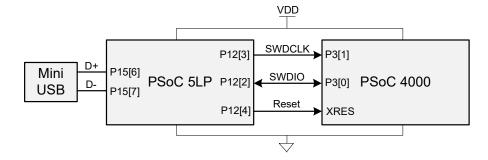

2. The onboard PSoC 5LP uses serial wire debug (SWD) to program the PSoC 4 device. See Figure 3-5.

Note: Figure 3-5 is provided only for reference, all connections are hardwired on the board itself.

Figure 3-5. SWD Programming of PSoC 4000 Using PSoC 5LP

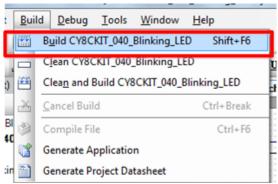

3. The kit's onboard programmer will enumerate on the PC and in the software tools as KitProg. Open an example project in PSoC Creator (such as Project: Blinking LED on page 53) and initiate the build by choosing Build > Build Project or pressing [Shift] [F6]. See Figure 3-6.

Figure 3-6. Build Project in PSoC Creator

4. After the project is built without errors and warnings, choose **Debug > Program** or press **[Ctrl] [F5]** to program the device. See Figure 3-7.

Figure 3-7. Program Device From PSoC Creator

The onboard programmer supports only the RESET programming mode. When using the onboard programmer, the board can either be powered by the USB (VBUS) or by an external source such as an Arduino shield (see Power Supply System on page 35). If the board is already powered from another source, plugging in the USB programmer does not damage the board.

## 3.3.2 Using the CY8CKIT-002 MiniProg3 Programmer and Debugger

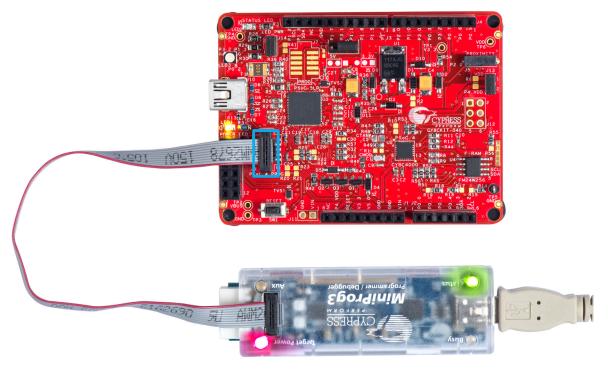

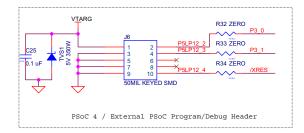

The PSoC 4 on the kit can also be programmed using a MiniProg3 (CY8CKIT-002). To use Mini-Prog3 for programming, use the J6 connector on the board, as shown in Figure 3-8.

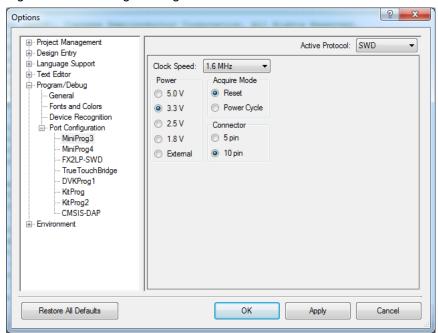

The board can also be powered from the MiniProg3. To do so, choose **Tool > Options** in PSoC Creator. In the Options window, expand **Program/Debug > Port Configuration**; click **MiniProg3** and select the settings shown in Figure 3-9. Choose **Debug > Program** to program and power the board.

**Note** The CY8CKIT-002 MiniProg3 is not part of the PSoC 4000 Pioneer Kit contents. It can be purchased from the Cypress Online Store.

Figure 3-8. PSoC 4 Programming/Debugging Using MiniProg3

Figure 3-9. MiniProg3 Configuration in PSoC Creator

**Note:** Ensure that both MiniProg3 (with or without power) on header J6 and KitProg are not connected to the onboard PSoC 4 at the same time. This will result in failed device acquisition from both.

## 3.4 USB-I<sup>2</sup>C Bridge

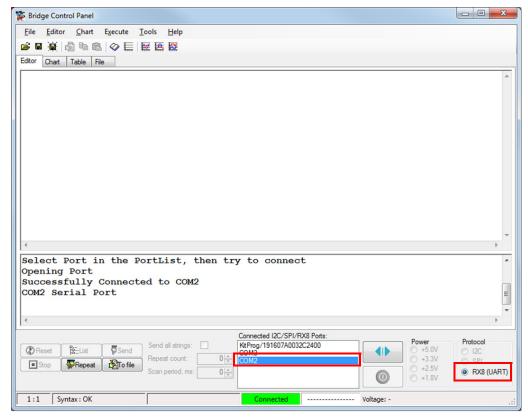

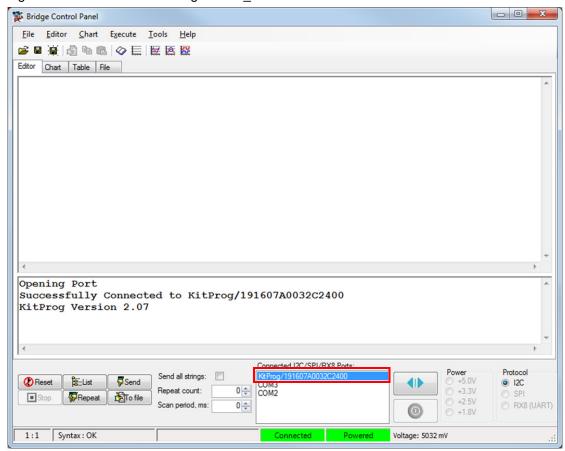

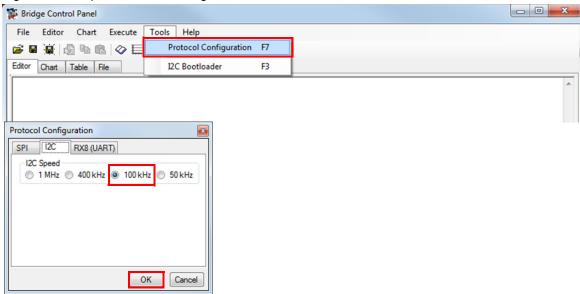

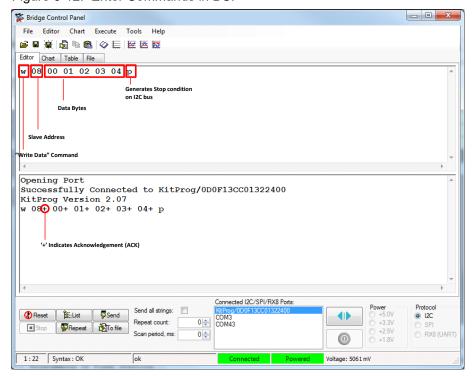

The PSoC 5LP also functions as a USB-I<sup>2</sup>C bridge. The PSoC 4 communicates with the PSoC 5LP using an I<sup>2</sup>C interface, and the PSoC 5LP transfers the data over the USB to the USB-I<sup>2</sup>C software utility on the PC called the Bridge Control Panel (BCP).

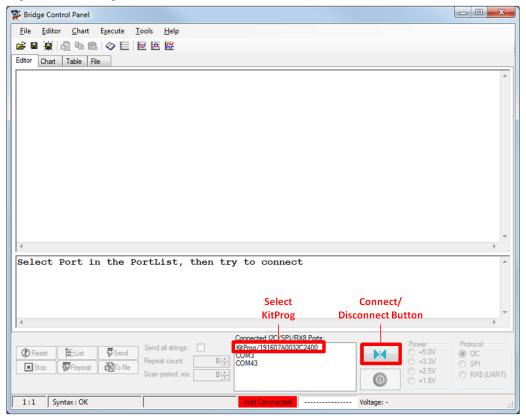

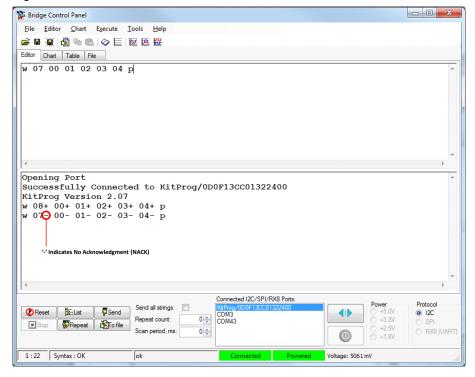

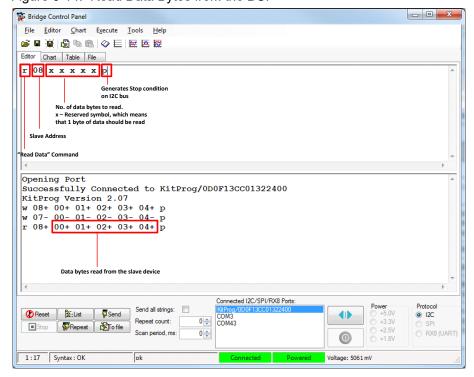

The BCP is available as part of the PSoC Programmer installation. This software can be used to send and receive USB-I<sup>2</sup>C data from the PSoC 5LP. When the USB Mini-B cable is connected to header J10 on the PSoC 4000 Pioneer Kit, the **KitProg/<Serial\_Number>** is available under **Connected I2C/SPI/RX8 Ports** in the BCP, as shown in Figure 3-10.

Figure 3-10. Bridge Control Panel

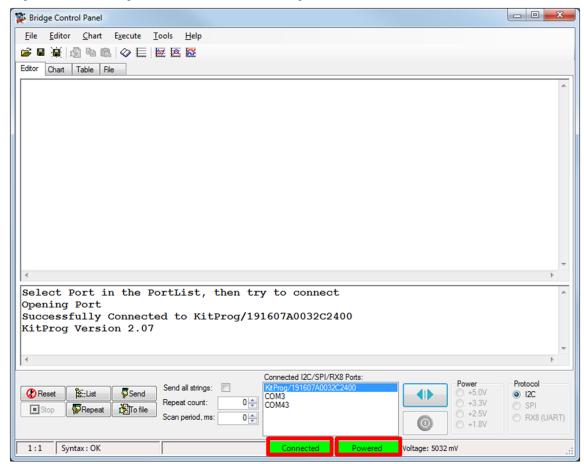

To use the USB-I<sup>2</sup>C functionality, select the **KitProg/<Serial\_Number>** in the BCP (Figure 3-10). On successful connection, the **Connected** and **Powered** status boxes turn green (Figure 3-11).

Figure 3-11. KitProg USB-I<sup>2</sup>C Connected in Bridge Control Panel

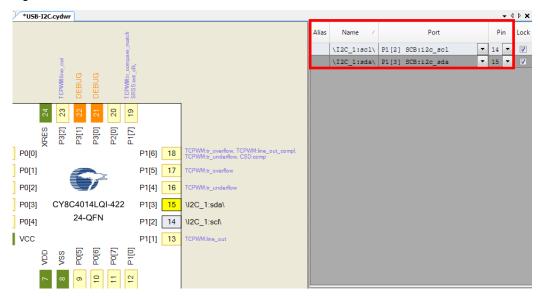

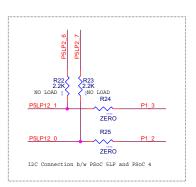

USB-I $^2$ C is implemented using the USB and I $^2$ C components of PSoC 5LP. The SCL (P12\_0) and SDA (P12\_1) lines from the PSoC 5LP are connected to the SCL (P1\_2) and SDA (P1\_3) lines of the PSoC 4 I $^2$ C. The USB-I $^2$ C bridge currently supports I $^2$ C speed of 50 kHz, 100 kHz, 400 kHz, and 1 MHz.

See Using PSoC 5LP as a USB-I2C Bridge on page 102 for building a project that uses the USB-I<sup>2</sup>C bridge functionality.

## 3.5 USB-UART Bridge

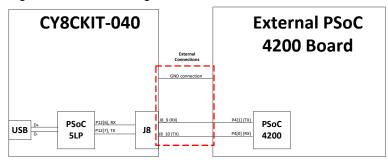

The onboard PSoC 5LP can also act as a USB-UART bridge to transfer and receive data from the PSoC 4 device to the PC via the COM terminal software. When the USB Mini-B cable is connected to J10 of the PSoC 4000 Pioneer Kit, a device named **KitProg USB-UART** is available under **Ports** (**COM & LPT**) in the Device Manager. For more information about the USB-UART functionality, see Using PSoC 5LP as a USB-UART Bridge on page 115.

To use the USB-UART functionality in the COM terminal software, select the corresponding COM port as the communication port for transferring data to and from the COM terminal software.

The UART lines from PSoC 5LP are brought to the P12[6] (J8\_9) and P12[7] (J8\_10) pins of header J8. This interface can be used to send or receive data from any design/device that has a UART by connecting the pins on header J8 to the RX and TX pins available on the connecting device.

**Note:** The PSoC 4000 family that is featured in the kit does not support a full-duplex UART; it can support only a software-based UART transmit on any pin. On the board, P3[0] of the PSoC 4000 device is hardwired to the UART bridge's RX line through zero-ohm resistor R57.

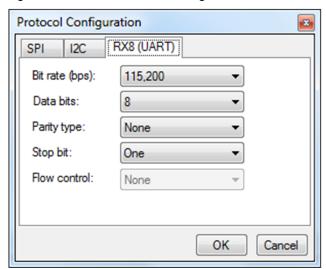

Table 3-2 lists the specifications supported by the USB-UART bridge.

Table 3-2. Specifications Supported by USB-UART Bridge

| ianie e zi. oposinostanie osppostostoj e oz est. ziruge |                                                                                     |  |  |  |

|---------------------------------------------------------|-------------------------------------------------------------------------------------|--|--|--|

| Parameter                                               | Supported Values                                                                    |  |  |  |

| Baud rate                                               | 1200, 2400, 4800, 9600, 19200, 38400, 57600, and 115200                             |  |  |  |

| Data bits                                               | 8                                                                                   |  |  |  |

| Parity                                                  | None                                                                                |  |  |  |

| Stop bits                                               | 1                                                                                   |  |  |  |

| Flow control                                            | None                                                                                |  |  |  |

| File transfer protocols supported                       | Xmodem, 1K Xmodem, Ymodem, Kermit, and Zmodem (only speeds greater than 2400 baud). |  |  |  |

## 3.6 Updating the Onboard Programmer Firmware

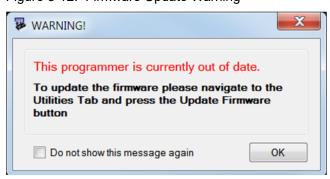

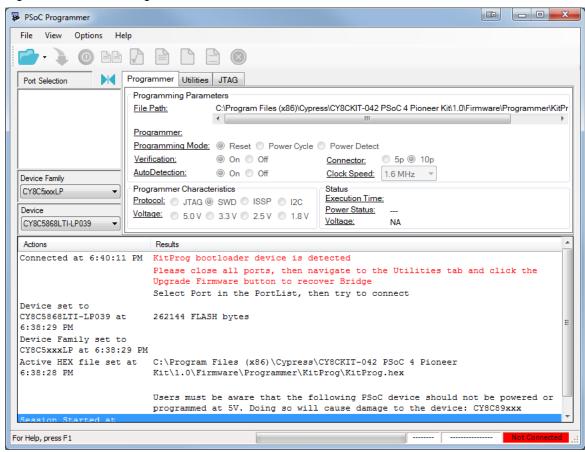

The firmware of the onboard programmer and debugger (KitProg), PSoC 5LP, can be updated from PSoC Programmer. When a new firmware is available or when the KitProg firmware is corrupt (see KitProg Status LED States on page 152), PSoC Programmer displays a warning indicating that new firmware is available.

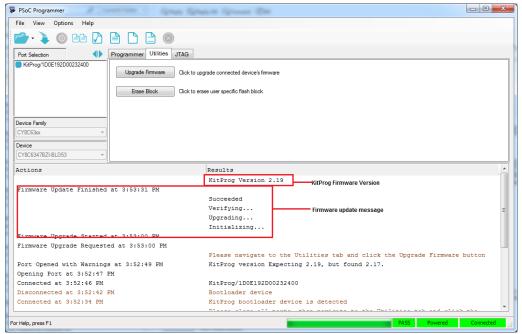

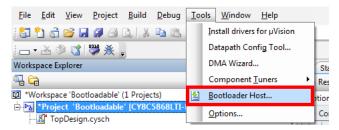

Open PSoC Programmer from **Start > All Programs > Cypress > PSoC Programmer<version>**. When PSoC Programmer opens, a WARNING! window pops up saying that the programmer is currently out of date, as shown in Figure 3-12.

Figure 3-12. Firmware Update Warning

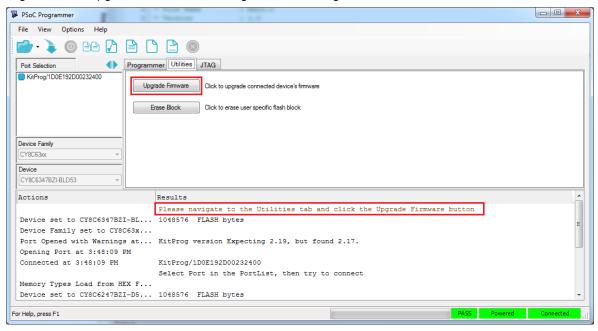

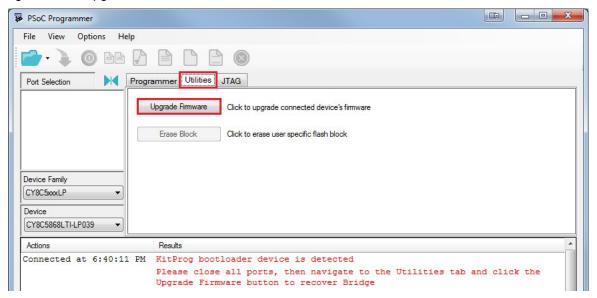

Click **OK** to close the window. On closing the warning window, the **Actions** and **Results** window displays **Please navigate to the Utilities tab and click the Upgrade Firmware button**, as shown in Figure 3-13.

Figure 3-13. Upgrade Firmware Message in PSoC Programmer

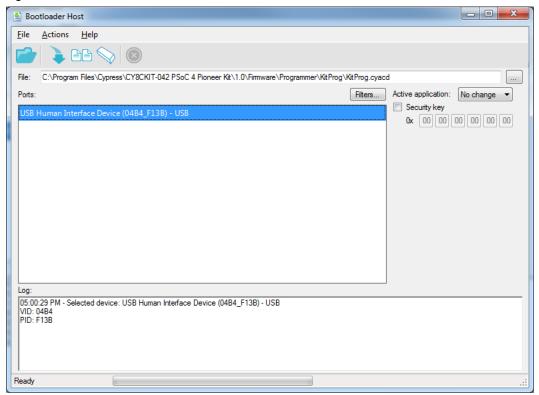

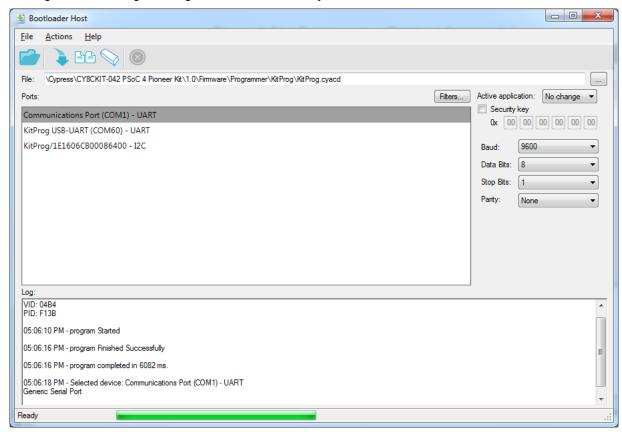

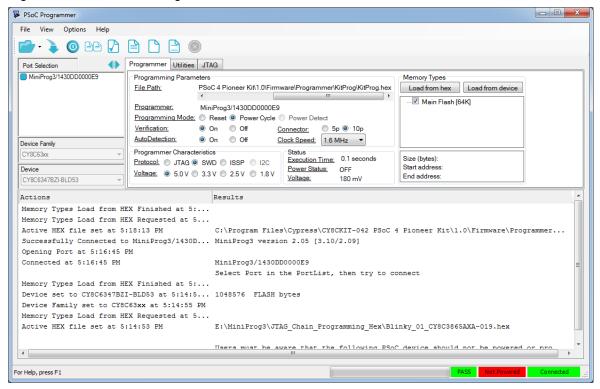

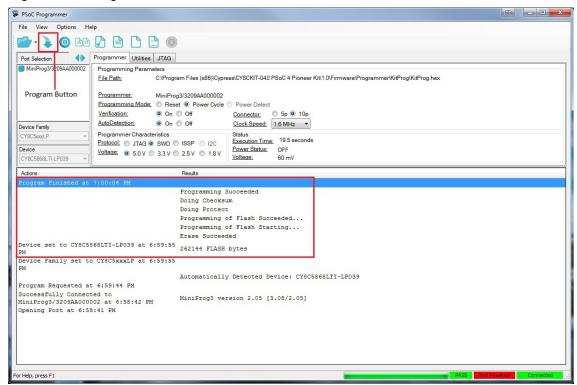

Click the **Utilities** tab and then click the **Upgrade Firmware** button. On successful upgrade, the **Actions** and **Results** window displays the firmware update message with the KitProg version, as shown in Figure 3-14.

Figure 3-14. Firmware Updated in PSoC Programmer

# 4. Hardware

## 4.1 Board Details

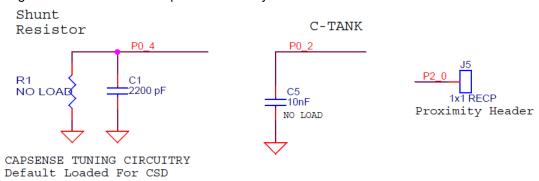

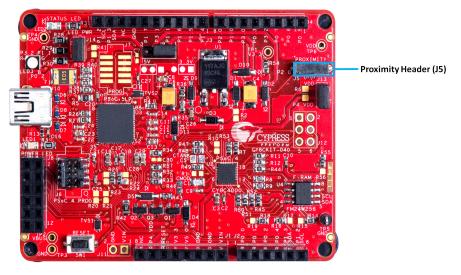

The PSoC 4000 Pioneer Kit consists of the following blocks:

- CY8CKIT-040 baseboard (see Figure 4-1) -

- PSoC 4 (4000 family)

- □ PSoC 5LP

- Power supply system

- □ Coin cell battery holder (BT1)

- Programming interfaces (J6, and J10)

- □ Arduino-compatible headers (J1, J2, J3, J4, and J12)

- □ PSoC 5LP GPIO header (J8)

- □ Proximity header (J5)

- Pioneer board LEDs

- □ Push button (Reset button)

- □ Cypress ferroelectric RAM (F-RAM)

- CY8CKIT-040 CapSense Trackpad shield board (see Figure 4-2)

Note: Programming header J7 is not populated by default.

Figure 4-1. CY8CKIT-040 - Baseboard Details

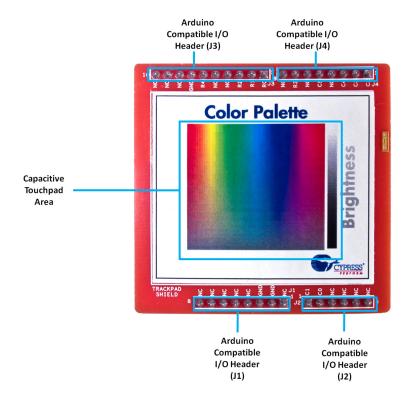

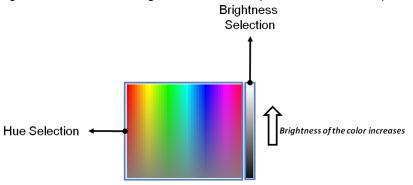

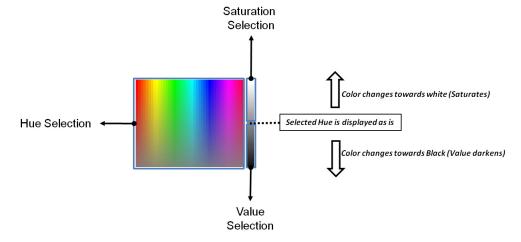

Arduino Arduino Compatible I/O Compatible I/O Header (J3) Header (J4) **Color Palette** ghtness Capacitive Touchpad Area Arduino Arduino Compatible Compatible I/O Header I/O Header (J1) (J2)

Figure 4-2. CY8CKIT-040 CapSense Trackpad Shield Board Details

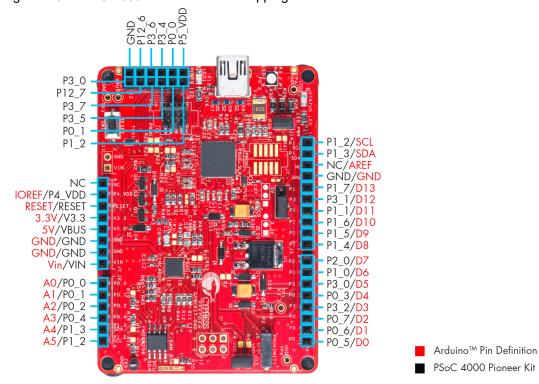

Figure 4-3. PSoC 4000 Pioneer Kit Pin Mapping

## 4.2 Block Diagram

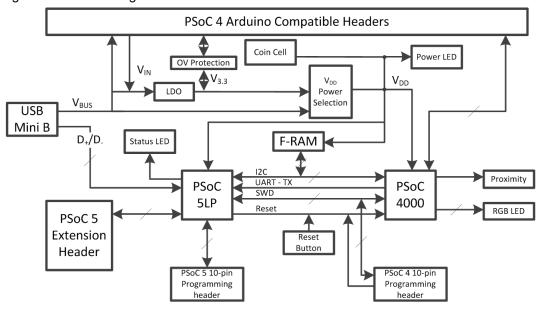

This section provides the block-level description of the PSoC 4000 Pioneer Kit, as illustrated in Figure 4-4.

Figure 4-4. Block Diagram

PSoC 4 is a new generation of programmable system-on-chip devices from Cypress for embedded applications. The PSoC 4000 family is the smallest member of the PSoC 4 platform with CapSense, TCPWM, I<sup>2</sup>C master or slave, and up to 20 GPIOs support. PSoC 4000 is a cost-optimized, entry-level PSoC4 device targeted as socket replacements for obsolete and/or proprietary 8-bit and 16-bit MCUs. PSoC 4000 with its ARM Cortex-M0 core brings 32 CapSense and programmable peripherals.

The kit features an onboard PSoC 5LP, which communicates through the USB to program and debug the PSoC 4 using SWD. The PSoC 5LP also functions as a USB-I<sup>2</sup>C bridge and USB-UART bridge. It can also be used to develop PSoC 5LP based applications (see Developing Applications for PSoC 5LP on page 126).

The kit includes an RGB LED, a status LED, and a power LED. The RGB LED is connected to the PSoC 4000, and the status LED is connected to the PSoC 5LP. This kit also includes a Reset button that connects to the PSoC 4000 XRES, a CapSense proximity header, and a 6x5 elements Trackpad board that is Arduino shield-compatible and can be used to develop touch-based applications. The PSoC 4 pins are brought out onto headers J1 to J4 on the kit to support Arduino shields. The PSoC 5LP pins are brought out onto header J8 to enable using the onboard PSoC 5LP to develop custom applications.

The PSoC 4000 Pioneer Kit can be powered from the USB Mini-B, the Arduino compatible header, an external power supply, or an optional coin cell battery. The input voltage is regulated by a low drop out (LDO) regulator to 3.3 V. You can select between VBUS (5 V) and 3.3 V by suitably plugging the jumper onto the voltage selection header J9. VDD can also be supplied by a coin cell battery placed in the BT1 coin cell holder. The voltage supplied by the coin cell is directly connected to the VDD line through a diode, D11. Make sure that VDD does not exceed the device's VDD specification (1.8 V to 5.5 V).

## 4.3 Kit Component Details

## 4.3.1 CY8CKIT-040 Baseboard Components

#### 4.3.1.1 PSoC 4

This kit uses the PSoC 4000 family device. PSoC 4 is the architecture of programmable embedded system controllers with an ARM Cortex-M0 CPU. PSoC 4 delivers a programmable platform for embedded applications. The CY8C40 family is the smallest member of the PSoC 4 family of devices and is upward compatible with larger members of PSoC 4.

For more information, refer to the PSoC 4 webpage and the PSoC 4000 family datasheet.

#### **Features**

#### ■ 32-bit MCU Subsystem

- □ 16-MHz ARM Cortex-M0 CPU

- Up to 16 KB of flash with read accelerator

- □ Up to 2 KB of SRAM

#### ■ Programmable Analog

- Two current DACs (IDACs) for general-purpose or capacitive sensing applications

- One low-power comparator with internal reference

#### ■ Low Power 1.71-V to 5.5-V Operation

□ Deep Sleep mode with wake-up on interrupt and I<sup>2</sup>C address detect

#### ■ Capacitive Sensing

- Cypress Capacitive Sigma-Delta (CSD) provides best-in-class signal-to-noise ratio (SNR) and water tolerance

- Cypress-supplied software component makes capacitive sensing design easy

- □ Automatic hardware tuning (SmartSense™)

#### ■ Serial Communication

☐ Multimaster I<sup>2</sup>C block with the ability to do address matching during Deep Sleep and generate a wake-up on match

#### Timing and Pulse-Width Modulation

- One 16-bit Timer/Counter/Pulse-Width Modulator (TCPWM) block

- □ Center-aligned, Edge, and Pseudo-Random modes

- Comparator-based triggering of Kill signals for motor drive and other high-reliability digital logic applications

#### ■ Up to 20 Programmable GPIO Pins

- 24-pin QFN, 16-pin SOIC, 16-pin QFN, and 8-pin SOIC packages

- ☐ GPIO pins on Ports 0, 1, and 2 can be CapSense or have other functions

- Drive modes, strengths, and slew rates are programmable

#### ■ PSoC Creator Design Environment

- □ Integrated design environment (IDE) provides schematic design entry and build (with analog and digital automatic routing)

- Applications programming interface (API) component for all fixed-function and programmable peripherals

#### ■ Industry-Standard Tool Compatibility

After schematic entry, development can be done with ARM-based industry-standard development tools

#### 4.3.1.2 PSoC 5LP

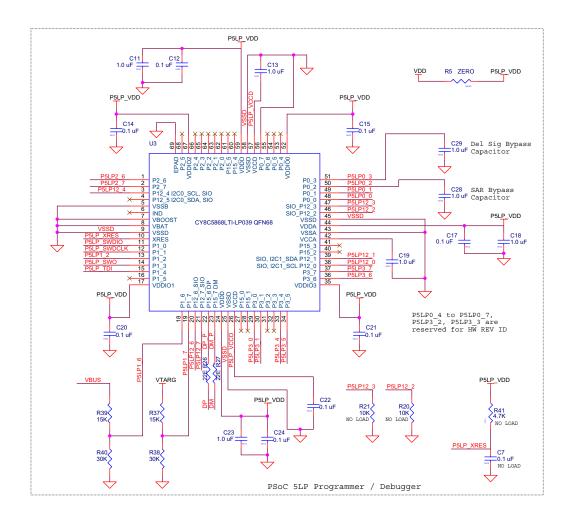

An onboard PSoC 5LP (CY8C5868LTI-LP039) is used to program and debug PSoC 4. The PSoC 5LP connects to the USB port of the PC through a USB Mini-B connector and to the SWD interface of the PSoC 4 device.

PSoC 5LP is a true system-level solution providing MCU, memory, analog, and digital peripheral functions in a single chip. The CY8C58LPxx family offers a modern method of signal acquisition, signal processing, and control with high accuracy, high bandwidth, and high flexibility. Analog capability spans the range from thermocouples (near DC voltages) to ultrasonic signals. For more information, refer to the PSoC 5LP webpage.

#### **Features**

- 32-bit ARM Cortex-M3 CPU core

- DC to 67-MHz operation

- □ Flash program memory up to 256 KB, 100,000 write cycles, 20-year retention, and multiple security features

- Up to 32-KB flash error correcting code (ECC) or configuration storage

- □ Up to 64-KB SRAM

- □ 2-KB electrically erasable programmable read-only memory (EEPROM) memory, 1M cycles, and 20 years' retention

- 24-channel direct memory access (DMA) with multilayer AHB bus access

Programmable chained descriptors and priorities

High-bandwidth 32-bit transfer support

- Low voltage, ultralow power

- Wide operating voltage range: 0.5 V to 5.5 V

- High-efficiency boost regulator from 0.5-V input to 1.8-V to 5.0-V output

- □ 3.1 mA at 6 MHz (2.7 V to 5.5 V)

- Low-power modes including:

- 2-μA sleep mode with real-time clock (RTC) and low-voltage detect (LVD) interrupt 300-nA hibernate mode with RAM retention

- Versatile I/O system

- 28 to 72 I/Os (62 GPIOs, 8 SIOs, 2 USBIOs)

- Any GPIO to any digital or analog peripheral routability

- □ LCD direct drive from any GPIO, up to 46×16 segments

- CapSense support on any GPIO

- 1.2-V to 5.5-V I/O interface voltages, up to four domains

- Maskable, independent IRQ on any pin or port

- Schmitt-trigger transistor-transistor logic (TTL) inputs

- All GPIOs configurable as open drain high/low, pull-up/pull-down, High-Z, or strong output

- Configurable GPIO pin state at power-on reset (POR)

- □ 25-mA sink on SIO

- Digital peripherals

- □ 20 to 24 programmable logic device (PLD)-based universal digital blocks (UDBs)

- □ Full CAN 2.0b 16 RX, 8 TX buffers

- □ Full-Speed (FS) USB 2.0 12 Mbps using internal oscillator

- □ Four 16-bit configurable timers, counters, and PWM blocks

- □ 67-MHz, 24-bit fixed point digital filter block (DFB) to implement finite impulse response (FIR) and infinite impulse response (IIR) filters

- Library of standard peripherals

- 8-, 16-, 24-, and 32-bit timers, counters, and PWMs

Serial peripheral interface (SPI), universal asynchronous transmitter receiver (UART), and I<sup>2</sup>C Many others available in Component catalog available in PSoC Creator IDE

Library of advanced peripherals

Cyclic redundancy check (CRC)

Pseudo random sequence (PRS) generator

Local interconnect network (LIN) bus 2.0

Quadrature decoder

- Analog peripherals (1.71 V ≤ VDDA ≤ 5.5 V)

- □ 1.024 V ±0.1 percent internal voltage reference across –40 °C to +85 °C

- □ Configurable delta-sigma ADC with 8- to 20-bit resolution

Sample rates up to 192 ksps

Programmable gain stage: ×0.25 to ×16

12-bit mode, 192 ksps, 66-dB signal-to-noise and distortion ratio (SINAD), ±1-bit INL/DNL 16-bit mode, 48 ksps, 84-dB SINAD, ±2-bit INL, ±1-bit DNL

- Up to two SAR ADCs, each 12-bit at 1 Msps

- ☐ Four 8-bit 8 Msps current IDACs or 1 Msps voltage VDACs

- Four comparators with 95 ns response time

- □ Four uncommitted opamps with 25 mA drive capability

- □ Four configurable multifunction analog blocks; example configurations are programmable gain amplifier (PGA), transimpedance amplifier (TIA), mixer, and sample and hold

- CapSense support

- Programming, debug, and trace

- JTAG (4-wire), SWD (2-wire), single-wire viewer (SWV), and TRACEPORT interfaces

- Cortex-M3 flash patch and breakpoint (FPB) block

- □ Cortex-M3 Embedded Trace Macrocell™ (ETM™) that generates an instruction trace stream

- Cortex-M3 data watchpoint and trace (DWT) that generates data trace information

- Cortex-M3 Instrumentation Trace Macrocell (ITM) that can be used for printf-style debugging

- DWT, ETM, and ITM blocks that communicate with off-chip debug and trace systems via the SWV or TRACEPORT

- Bootloader programming supportable through I<sup>2</sup>C, SPI, UART, USB, and other interfaces

- Precision, programmable clocking

- 3- to 62-MHz internal oscillator over full temperature and voltage range

- 4- to 25-MHz crystal oscillator for crystal PPM accuracy

- Internal PLL clock generation up to 67 MHz

- □ 32.768-kHz watch crystal oscillator

- □ Low-power internal oscillator at 1, 33, and 100 kHz

For more information, see the CY8C58LPxxx family datasheet.

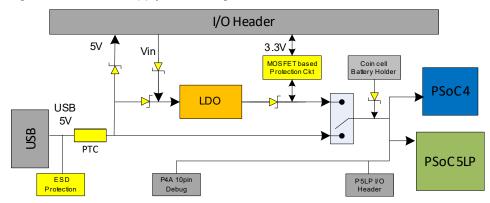

### 4.3.1.3 Power Supply System

The power supply system on this board is versatile, allowing the input supply to come from the following sources:

- 5-V power from onboard USB programming header J10

- 5-V to 12-V power from Arduino shield using J1 01 (VIN on J1) header

- VTARG power from the onboard SWD programming using J6 or J7 (not populated by default)

- VIN J11 (not populated by default)

- Coin cell battery BT1 (not populated by default)

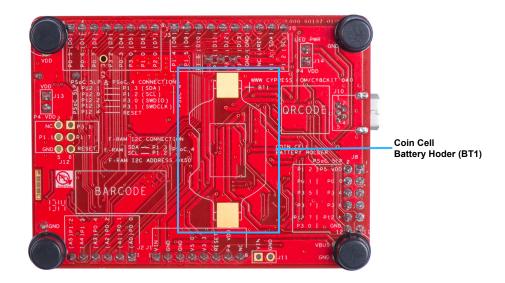

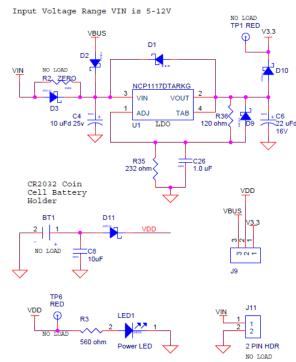

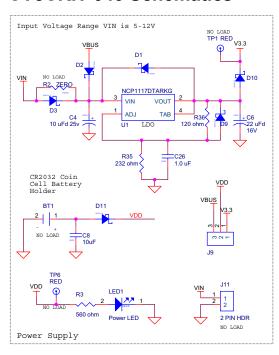

The PSoC 4 and PSoC 5LP are powered with either a 3.3 V or 5 V source. The selection between 3.3 V and 5 V is made through the J9 jumper. The board can supply 3.3 V and 5 V to the I/O headers and receive 3.3 V from the I/O headers (J9 should select 3.3 V for this). The board can also be powered with an external power supply through the VIN (J11) header; the allowed voltage range for the VIN is 5 V to 12 V. The LDO regulator regulates the VIN down to 3.3 V. Figure 4-5 shows the power supply block diagram and circuitry. In addition, there is a coin cell battery holder (BT1), which can power the VDD line directly. The allowed voltage range supported through the coin cell battery is between 1.8 V and 5.5 V (VDD specification of PSoC 4000 family). The BT1 holder is not populated on the board by default. BU2032SM-BT-GTR (from Keystone Electronics) can be used for BT1. This part supports CR2032 type coin cell batteries. See the Bill of Materials on page 153 for details on other parts that can be used for BT1.

**Note:** The 5-V domain is directly powered by the USB (VBUS). For this reason, this domain is unregulated.

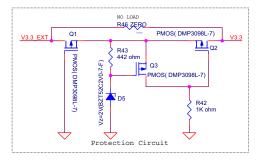

Figure 4-5. Power Supply Block Diagram and Schematic with Protection Circuits

Power Supply

#### **Protection Circuit**

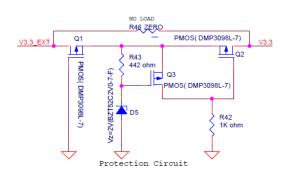

The power supply rail has reverse-voltage, overvoltage, short circuits, and excess current protection features, as seen in Figure 4-5.

- The Schottky diode (D4) ensures power cannot be supplied to the 5-V domain of the board from the I/O header.

- The series protection diode (D3) ensures VIN (power supply from the I/O header) does not back power the USB.

- The Schottky diode (D10) ensures 3.3 V from I/O header does not back power the LDO.

- The series protection diode (D3) ensures that the reverse voltage cannot be supplied from the VIN to the regulator input.

- A PTC resettable fuse is connected to protect the computer's USB ports from shorts and over current.

- The MOSFET-based protection circuit provides overvoltage and reverse-voltage protection to the 3.3-V rail. The PMOS Q1 protects the board components from a reverse-voltage condition. The PMOS Q2 protects the PSoC from an overvoltage condition. The PMOS Q2 will turn off when a voltage greater than 3.6 V is applied, protecting the PSoC 4.

- The output voltage of the LDO is adjusted such that it takes into account the voltage drop across the Schottky diode and provides 3.3 V.

- Populating R46 with a zero-ohm resistor will bypass the MOSFET-based protection circuitry.

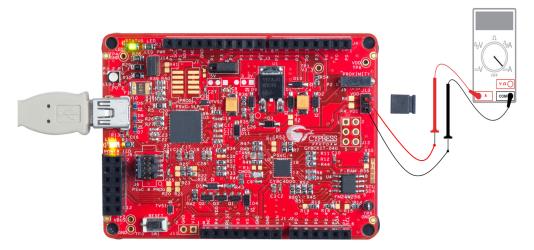

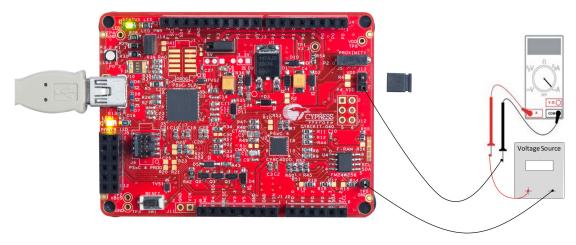

#### **Procedure to Measure PSoC 4 Current Consumption**

The following two methods are supported for measuring current consumption of the PSoC 4 device.

■ When the board is powered through the USB port (J10), remove jumper J13 and connect an ammeter, as shown in Figure 4-6.

Figure 4-6. PSoC 4 Current Measurement When Powered From USB Port

■ When using a separate power supply for the PSoC 4 with USB powering (regulator output on the USB supply must be within 0.5 V of the separate power supply), remove jumper J13. Connect the positive terminal of voltage supply to the positive terminal of the ammeter and the negative terminal of the ammeter to the lower pin (P4.VDD) of J13. Figure 4-7 shows the required connections.

Figure 4-7. PSoC 4 Current Measurement When Powered Separately

**Note:** The RGB tricolor LED is powerd from PSoC 4 VDD only. Remove jumper J14 to measure power consumed by PSoC 4 alone.

### 4.3.1.4 Programming Interface

The kit allows programming and debugging of the PSoC 4 in two modes:

- Using the Onboard PSoC 5LP Programmer and Debugger on page 21

- Using the CY8CKIT-002 MiniProg3 Programmer and Debugger on page 22

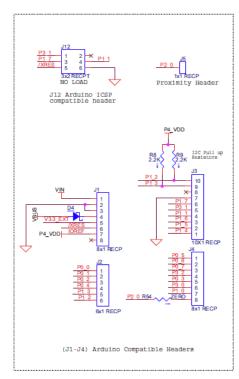

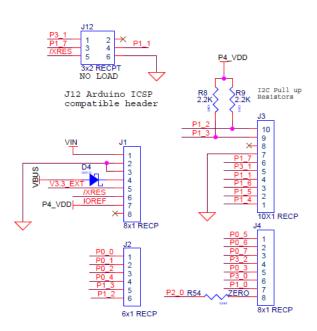

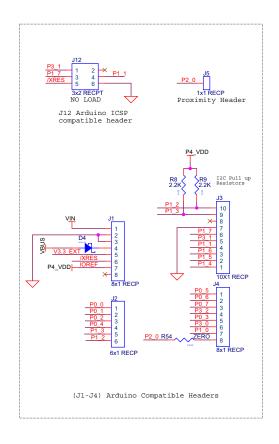

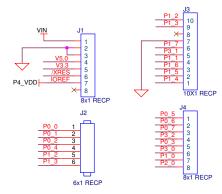

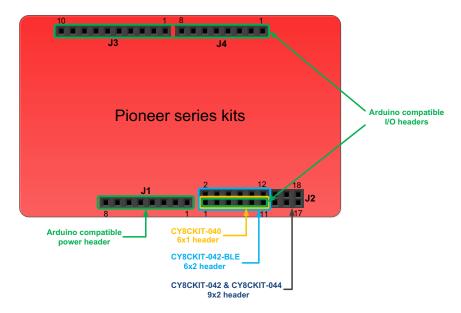

### 4.3.1.5 Arduino Compatible Headers (J1, J2, J3, J4, and J12)

This kit has five Arduino compatible headers: J1, J2, J3, J4, and J12. You can develop applications based on the Arduino shield's hardware. An Arduino shield compatible Trackpad board is also supplied with the kit.

Figure 4-8. Arduino Header

Note: The graphic LCD shield in Figure 4-8 is shown for reference only and not part of the kit.

- The J1 header contains I/O pins for reset and power supply line.

- The J2 header is an analog port. Because of limited analog support in PSoC 4000 family, it contains general-purpose digital I/O pins only.

- The J3 header is primarily a digital port. It contains I/O pins for PWM, I<sup>2</sup>C and general-purpose digital.

- The J4 header is also a digital port.

- The J12 header is an Arduino ICSP-compatible header for the SPI interface. This header is not populated. Refer to the "No Load Components" section of Bill of Materials for the header part number.

**Note:** The PSoC 4000 family does not support SPI in hardware, but SPI master can be implemented on any pin using firmware bit banging.

Arduino

Compatible I/O

Header (J3)

Arduino

Compatible I/O

Header (J12)

Arduino

Compatible I/O

Header (J12)

Arduino

Compatible I/O

Header (J1)

Figure 4-9. Arduino Compatible Headers

(J1-J4) Arduino Compatible Headers

### **Functionality of Unpopulated Header J12**

The J12 header is a 2×3 header that supports Arduino shields. This header is used on a small subset of shields and is unpopulated on the PSoC 4000 Pioneer Kit.

**Note:** The J12 header functions only in 5 V mode. For proper shield functionality, ensure the power jumper (J9) is connected in 5 V mode.

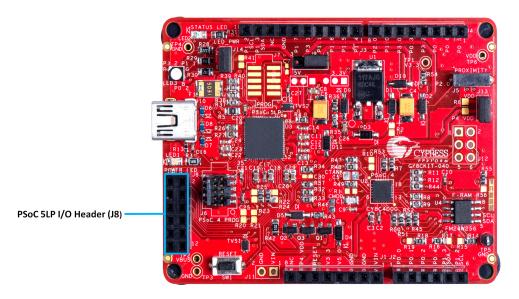

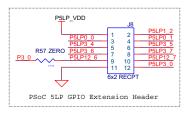

### 4.3.1.6 PSoC 5LP GPIO Header (J8)

A limited set of PSoC 5LP pins are brought to this header. Refer to Developing Applications for PSoC 5LP on page 126 for details on how to develop custom applications. See Pin Assignment Table on page 148 for pin details.

Figure 4-10. PSoC 5LP GPIO Header (J8)

PSoC 5LP GPIO Extension Header

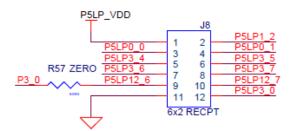

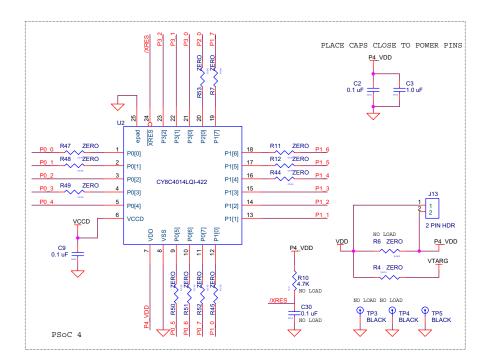

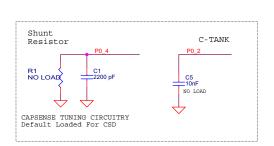

#### 4.3.1.7 CapSense Circuit

The baseboard contains a header (J5) for CapSense proximity wire connection (see Figure 4-12). A 2.2-nF capacitor (C1) is present on CMOD pin, P0[4], for CapSense operation. An optional resistor R1 can be loaded to convert the current output from IDAC to a voltage output in non-CapSense applications.

The board optionally supports CapSense designs that require waterproofing. Any pin that supports CapSense in the device can be configured as a shield signal to enable waterproof operation. However, if a shield tank capacitor is required in the design, Capacitor C5 (CTANK) on the board needs to be populated with the desired tank capacitor value and R30 connecting the Blue LED to P0\_2 needs to be removed. Refer to the CapSense Design Guide for further details related to CapSense.

**Note:** The kit does not demonstrate the waterproof feature using the Trackpad shield board that ships with the kit because of limited I/O availability after Trackpad and RGB LED implementation. However, a custom shield board can be designed to use the feature.

Figure 4-11. Baseboard CapSense Circuitry

Figure 4-12. Proximity Header (J5)

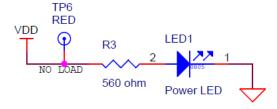

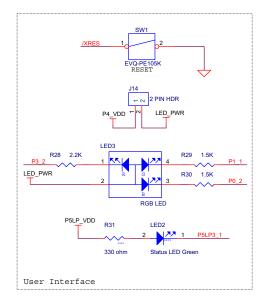

#### 4.3.1.8 Board LEDs

The PSoC 4000 Pioneer board has three LEDs. A green LED (LED2) indicates the status of the programmer. See KitProg Status LED States on page 152 for a detailed list of LED indications. An amber LED (LED1) indicates the status of power supplied to the board. The kit also has a general-purpose tricolor (RGB) LED (LED3) for user applications that connect to specific PSoC 4 pins. Jumper J14 is provided to enable/disable power to the RGB LED (LED3). The RGB LED is powered from PSoC 4 VDD, so jumper J14 needs to be removed to measure PSoC 4 power accurately without leakage and LED power.

Figure 4-13 shows the indication of all these LEDs on the board. Figure 4-14 and Figure 4-15 detail the LED schematic.

Figure 4-13. Board LEDs

Figure 4-14. Power LED

Figure 4-15. Status LED and RGB LED

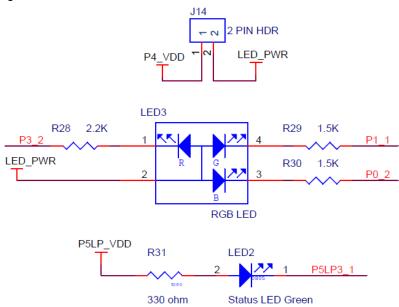

### 4.3.1.9 Push Buttons

The kit contains only a Reset push button, as shown in Figure 4-16. The Reset button is connected to the XRES pin of PSoC 4 and is used to reset the onboard PSoC 4 device. The push button connects to ground on activation (active low).

Figure 4-16. Reset Push Button

**Note:** The PSoC 4 Reset pin (XRES) has an internal pull-up resistor. However, an external pull-up resistor R10 and capacitor C30 are connected to the PSoC 4 Reset pin on the kit, which is optional and required only in a noisy system.

#### 4.3.1.10 Cypress Ferroelectric RAM (F-RAM)

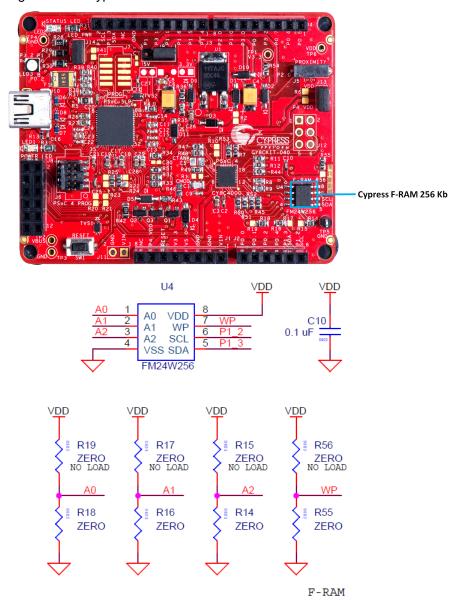

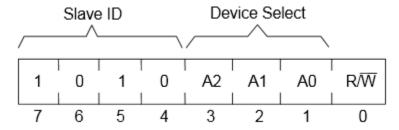

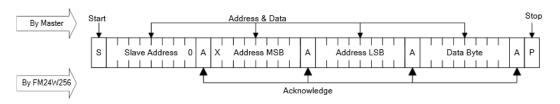

The baseboard contains an F-RAM device (FM24W256); see Figure 4-17, which can be accessed through I<sup>2</sup>C lines by either of the PSoC devices – PSoC 5LP or PSoC 4 – or by both. The F-RAM is 256 Kb (32 KB) in size with the I<sup>2</sup>C speed up to 1 Mbps. The I<sup>2</sup>C slave address of the F-RAM device is 7-bit wide, and the LSB three bits are configurable through physical pins and are hardwired to 000 on the board. By default, the address of the F-RAM device used on the board is 0x50. This can be modified by changing the R19/R18, R17/R16, and R15/R14 pairs. Refer to Use of Zero-ohm Resistors and No Load on page 151 for details on how to change the F-RAM address using these resistors. Using FM24W256 F-RAM on page 111 provides an example implementation showing how to use this F-RAM device with PSoC 4 and share it between Bridge Control Panel over the PSoC 5LP USB-I<sup>2</sup>C bridge.

Figure 4-17. Cypress F-RAM

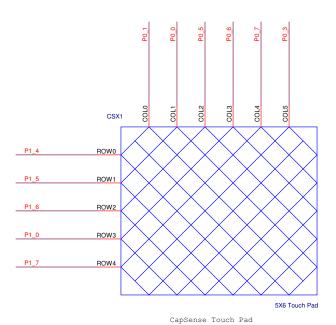

### 4.3.2 CY8CKIT-040 CapSense Trackpad Shield Board

The kit also includes an Arduino-compatible CapSense Trackpad shield board. The Trackpad in the kit is a 6x5 elements capacitive sensing array. Figure 4-18 shows the pin mapping of the Trackpad.

The modulation capacitor (Cmod) used for CapSense is connected to pin P0[4], and an optional bleeder resistor (R1) can be connected across the Cmod. The Trackpad shield is Arduino-compatible and can also be used with the PSoC 4 Pioneer Kit (CY8CKIT-042). The sticker on the Trackpad shield can be redesigned according to user requirement and can be pasted on top of the Trackpad to implement any custom, application-specific UI. The Trackpad/Touchpad Sticker Details on page 156 provides the sticker template.

Refer to the CapSense Design Guide for further details related to CapSense.

Arduino Compatible I/O Compatible I/O Header (J3) Header (J4) 6666666<u>8686868686888</u> **Color Palette** Capacitive Touchpad Area Arduino Arduino Compatible Compatible I/O Header I/O Header (J1) (J2) COL5 COL4 % 1-1 CSX1 P1\_5 ROW1 ROW2 ROW3 ROW4 6x1 RECP

5X6 Touch Pad

CapSense Touch Pad

Figure 4-18. CapSense Trackpad Shield Board

(J1-J4) Arduino Compatible Headers

# 5. Code Examples

The code examples described in this chapter introduce the functionality of the PSoC 4000 device and the onboard components. To access the examples, download and install the CD ISO image or setup files from the kit webpage as explained in Install Software on page 14. After installation, the code examples will be available from **Start** > **Kits** on the PSoC Creator Start Page.

For more code examples, visit the PSoC 3, PSoC 4, and PSoC 5 code examples page. This webpage lists all PSoC Creator code examples available across application notes, kits, and PSoC Creator.

### 5.1 Using the Kit Code Examples

Follow these steps to open and program an example project:

- Launch PSoC Creator from the Windows Start menu (Start > All Programs > Cypress > PSoC Creator <version> > PSoC Creator <version>).

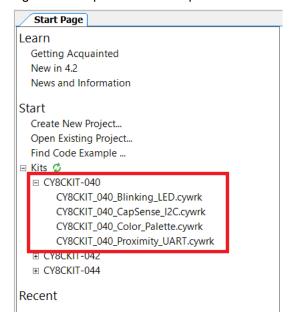

- 2. On the Start page, click **CY8CKIT-040** under **Start > Kits**. A list of code examples appears, as shown in Figure 5-1.

Figure 5-1. Open Code Example from PSoC Creator

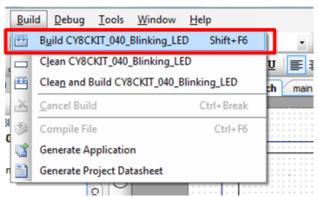

3. Build the code example by choosing **Build > Build <Project Name>**. After the build process is successful, a .hex file is generated.

Figure 5-2. Build Project from PSoC Creator

- 4. To program, connect the PSoC 4000 Pioneer Kit to the computer using the USB cable connected to port J10, as described in Kit USB Connection on page 20. The board is detected as KitProg.

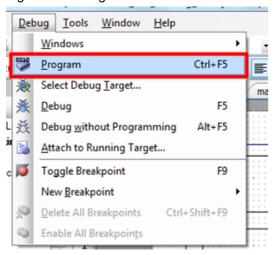

- 5. Choose **Debug > Program** from PSoC Creator, as shown in Figure 5-3.

Figure 5-3. Program Device from PSoC Creator

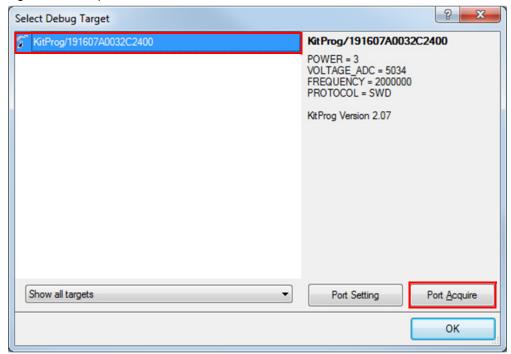

6. If the device is not yet acquired, PSoC Creator will open the **Select Debug Target** window. Select **KitProg/<Serial\_Number>** and click the **Port Acquire** button, as shown in Figure 5-4.

Figure 5-4. Acquire Device from PSoC Creator

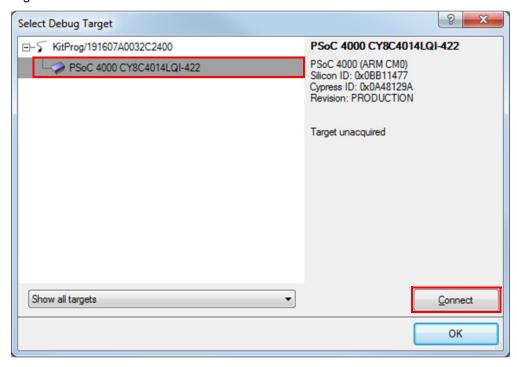

7. After the device is acquired, it is listed in a tree structure below the **KitProg/<Serial\_Number>** (see Figure 5-5). Click the **Connect** button.

Figure 5-5. Connect Device from PSoC Creator

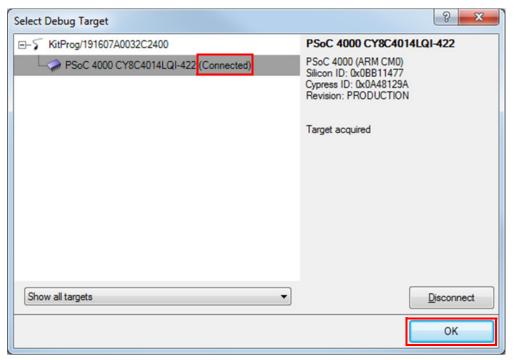

8. Click **OK** to exit the window and start programming, as shown in Figure 5-6.

Figure 5-6. Program Device from PSoC Creator

#### Notes:

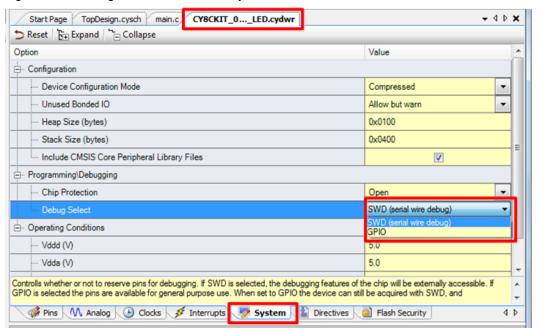

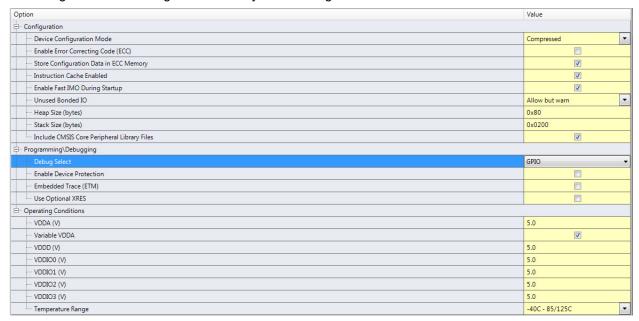

- The Debug port is disabled by default in one of the code examples (Project: CapSense Proximity and UART on page 56) because it uses the P3[0] (SWDIO) pin for software TX output. If debug is required, then change the **Debug Select** setting in the *cydwr* file to SWD, as shown in Figure 5-8. Disable software TX in the project by commenting out the TX\_ENABLE macro present in the *main.h* file. The Project: Color Palette on page 83 example project includes a software TX, but the TX port is disabled by default. To enable the TX port, change the **Debug Select** setting in the *cydwr* file to **GPIO** and uncomment the TX\_ENABLE macro in the *main.h* file. If TX is required along with SWD debug, then follow these steps:

- a. Route TX pin to any other available pin by modifying the TX\_PORT/TX\_PIN macro available in the main.h file of the projects.

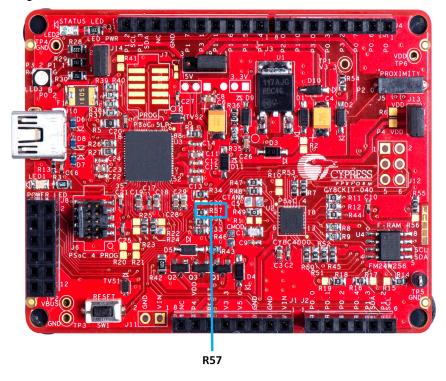

- b. Remove resistor R57 (Figure 5-7) on the board.

- c. Route the TX pin selected in step 1 to pin J8 9 (P12[6]/RX line of PSoC 5LP available in J8).

- Reset the device after plugging in the USB cable for the first time (if kit drivers are installing, then after driver installation) when using SmartSense Auto-tuning in the project. This is because SmartSense tunes the sensors during power-on and the presence of hand or power fluctuations during the USB plugging will affect the tuning algorithm; it can render stuck or insensitive touch sensors.

- By default, when the code examples are opened for the first time, an inline error can pop up in the main.c or main.h file against the '#include <project.h>' line. This error is temporary and will go off when the project is built. The project.h file is generated only when the project is built, hence the error is shown before building the project.

Figure 5-7. R57 Location on the Board

Figure 5-8. Debug Port Pin Functionality Selection

## 5.2 Project: Blinking LED

### 5.2.1 Project Overview

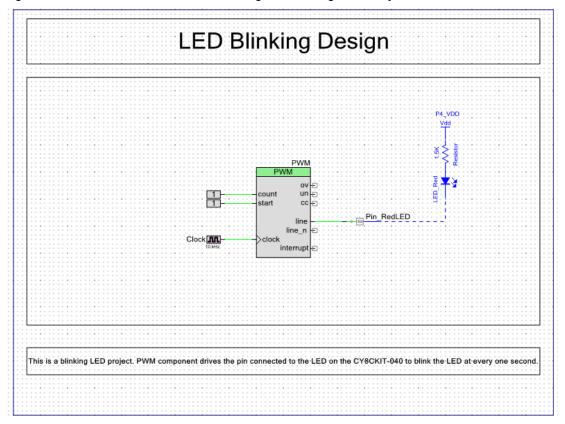

The CY8CKIT\_040\_Blinking\_LED.cyprj example uses a PWM block to blink the red LED of the RGB LED, as shown in Figure 5-9. The PWM output is connected to pin P3\_2 (red) of the RGB LED. The PWM block is configured as a digital clock signal generator with a frequency of 1 Hz. The blinking rate can be varied by changing the period and compare value of the PWM.

Figure 5-9. PSoC Creator Schematic Design of Blinking LED Project

### 5.2.2 Project Description

### 5.2.2.1 PSoC Creator Component Configuration

### **PWM (TCPWM mode)**

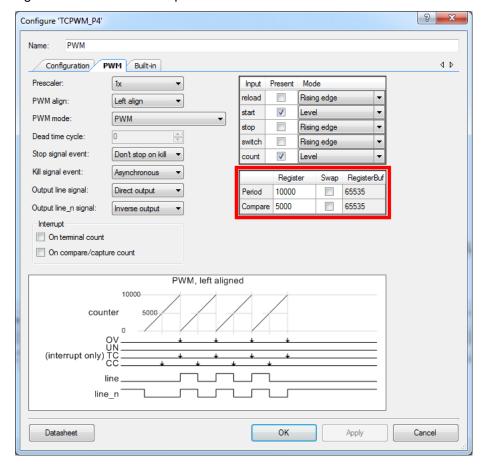

The TCPWM Component is configured as a PWM with the parameters shown in Figure 5-10.

Figure 5-10. TCPWM Component Parameters

#### 5.2.2.2 Firmware Details

Figure 5-11 shows the flow chart of code implemented in main.c.

Figure 5-11. Blinking LED Project Flow Chart

#### 5.2.2.3 Hardware Connections

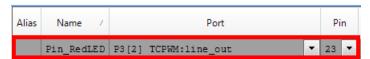

No specific hardware connections are required for this project because all connections are hardwired on the board. Open CY8CKIT\_040\_Blinking\_LED.cydwr under the **Source** vertical tab in the **Workspace Explorer** and select the suitable pin, as shown in Figure 5-12.

Table 5-1. Pin Connection

| Pin Name | Port Name  |  |  |

|----------|------------|--|--|

| PWM      | P3_2 (Red) |  |  |

Figure 5-12. Pin Selection for Blinking LED Project

### 5.2.3 Verify Output

Build and program the code example onto the device. Observe the frequency and duty cycle of the blinking LED. Change the period and compare value in the PWM Component, as shown in Figure 5-10. Rebuild and reprogram the device to change the blinking rate.

### 5.3 Project: CapSense Proximity and UART

### 5.3.1 Project Overview

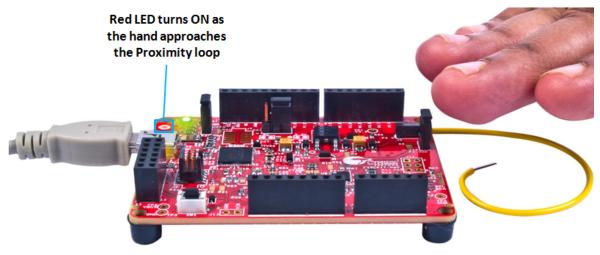

The project CY8CKIT\_040\_Proximity\_UART.cyprj implements a capacitive proximity sensor controlling the brightness of a LED. The project configures the sensor as a CapSense proximity widget with SmartSense Auto-tuning. Firmware Details on page 60 presents the firmware flow and explains the firmware blocks in detail.

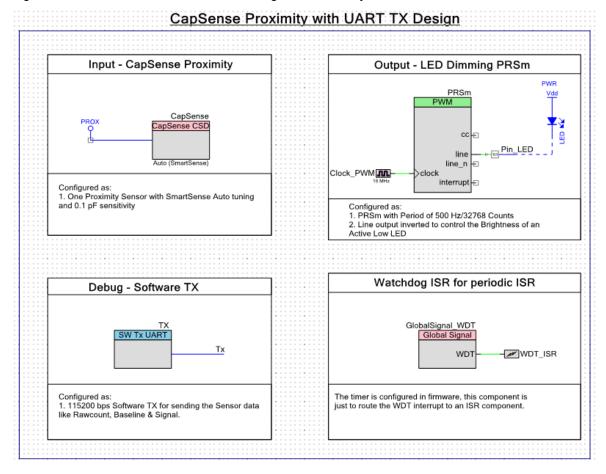

Figure 5-13. PSoC Creator Schematic Design of PWM Project

### 5.3.2 Project Description

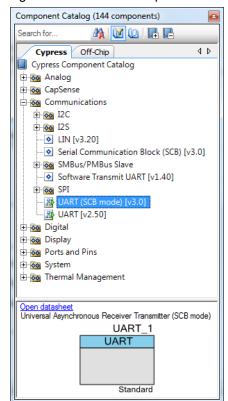

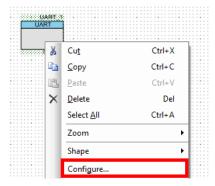

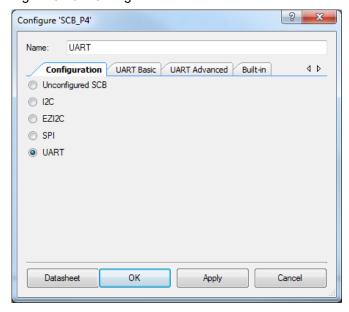

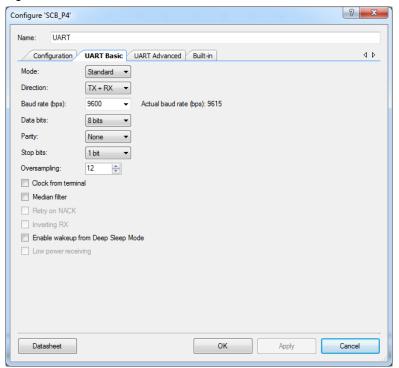

### 5.3.2.1 PSoC Creator Component Configuration

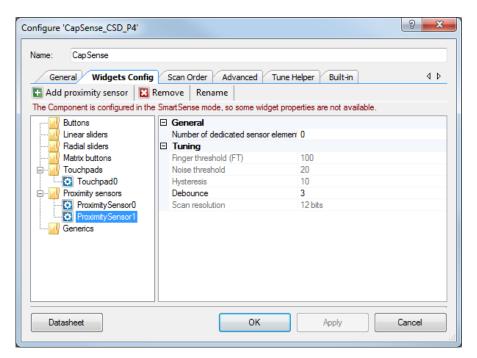

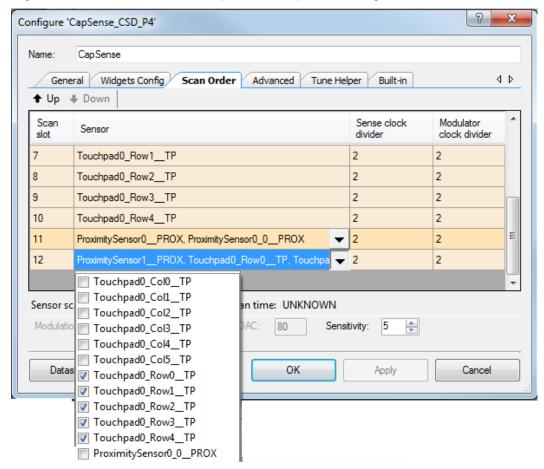

### **CapSense**

The CapSense Component is configured in SmartSense Auto-tuning mode with one proximity sensor for the design with the parameters shown in Table 5-2.

Table 5-2. CapSense Component Parameters

| Parameter                       | Tab Present      | Value                    | Rationale                                                                                                                                                                                                                                                          |  |  |

|---------------------------------|------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Tuning method                   |                  | Auto (Smart-<br>Sense)   | Automatically adjust sensitivity for different system environments.                                                                                                                                                                                                |  |  |

| Threshold mode                  | General          | Automatic                | To enable runtime threshold calculation for a 5:1 SNR                                                                                                                                                                                                              |  |  |

| Raw data noise filter           |                  | First Order IIR 1/4      | Filter out noise or unwanted spikes in raw count. This setting can be tweaked based on requirement.                                                                                                                                                                |  |  |

| ProximitySensor0                | Widgets Config - |                          | Add a proximity sensor by clicking <b>Proximity Sensors</b> and then clicking <b>Add Proximity Sensor</b> . The only parameter that is available to modify in this tab is debounce. This can be set or adjusted based on system requirements.                      |  |  |

| Analog switch drive source      |                  | PRS-12b                  | Reduce EMI emission and enhance EMC immunity.                                                                                                                                                                                                                      |  |  |

| Sensor auto-reset               |                  | Disabled                 | Not required in the design. Add if required by the application.                                                                                                                                                                                                    |  |  |

| Low baseline reset              |                  | 5                        | System dependent number. Configure according to user needs.                                                                                                                                                                                                        |  |  |

| Inactive sensor con-<br>nection | Advanced         | Ground                   | Make the proximity loop not pick up any charge when not scanned                                                                                                                                                                                                    |  |  |

| Shield                          |                  | Disabled                 | Not used in the design.                                                                                                                                                                                                                                            |  |  |

| Guard sensor                    |                  | Disabled                 | Not used in the design.                                                                                                                                                                                                                                            |  |  |

| Cmod precharge                  |                  | Precharge by Vref buffer | Vref is enough for precharging, as there is only one sensor. Cmod voltage will not drop too low for a fast GPIO precharge.                                                                                                                                         |  |  |

| Sensitivity                     | Scan Order       | 1                        | Obtain the maximum possible sensitivity using SmartSense. The parameter controls the scan time, so for a lower number sensitivity setting, the scan rate will be higher. This parameter can be adjusted depending on the response rate and proximity range needed. |  |  |

| Enable tuner helper             | Tuner helper     | Unchecked                | No tuner used.                                                                                                                                                                                                                                                     |  |  |

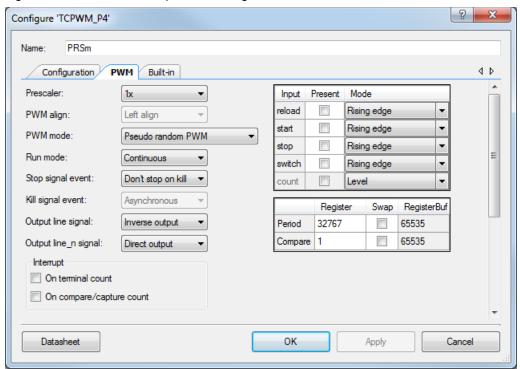

### PRSm (TCPWM Mode)

The TCPWM Component is used to control the LED brightness. The CapSense proximity sensor's signal output is used to deduce the LED brightness. Figure 5-14 shows the parameters for the TCPWM Component. The TCPWM block is configured as a PWM in Pseudo Random Sequence modulator (PRSm) mode with a resolution of 15 bits (fixed by the TCPWM block architecture). This 15-bit resolution of the PRSm along with a 16-MHz input clock generates a period of 500 Hz (PRS repeat period). The output line is inverted to drive the Active Low LED. A period of 32767 is set in the

Component to generate the proper period macro for the 15-bit PRSm. Though the output of PRSm has a variable frequency with a maximum frequency of 8 MHz (16 MHZ/2), the repeat rate of PRSm is considered to be the period in this context.

Note: The Compare value should be a minimum of '1'; '0' will leave the LED on.

Figure 5-14. TCPWM Component Configuration - 'PWM' Tab

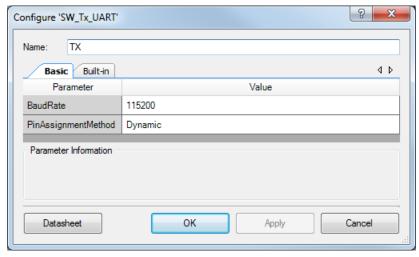

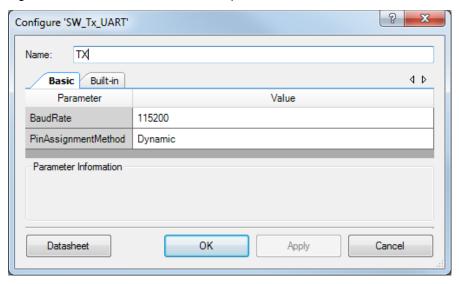

### TX (Software TX UART)

The software transmit TX is used to send out proximity sensor related data for debugging. The configuration for the component is shown in Figure 5-15. The TX pin is selected in firmware through the TX\_PORT/TX\_PIN macros defined in the *main.h* file. The SW TX data can be sent to the computer using either an RS232 connector (with a voltage level translator in between) or through the USB-UART bridge available in the CY8CKIT-040 PSoC 5LP UART bridge, or the CY3240 bridge configured as a UART bridge as documented in AN2397.

Figure 5-15. Software UART TX Component Parameters

### Pin\_LED (Digital Output Pin)

The digital output pin is used to drive the PWM output to the LED. It is a standard strong drive output pin.

#### Clock\_PWM (Cy\_Clock)

Clock\_PWM provides the clock that drives the PWM block. The clock is configured to be the maximum possible or allowed (16 MHz), so that the repeat rate of the PRSm is as high as possible for reduced LED flickers.

### GlobalSignal\_WDT (Global Signal Reference with ISR)

Component used to route the WDT ISR to an ISR Component. This ISR is then configured in firmware to generate periodic wakeup signal using WDT during Sleep Scan mode.

#### 5.3.2.2 Firmware Details

#### **Firmware Structure**

The firmware is written in a modular format, with different aspects of the functionality provided as separate functions for easy understanding. The header provides a list of handy macros for configuring the project's key aspects according to user requirements. The comments in the header file provide the details on the macro.

Table 5-3. Source Files and Header Files in the CapSense Proximity Project

| File Names | Purpose                                                                                                                                          |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| main.c     | This file contains all the function definitions used in the firmware.                                                                            |  |  |

| main.h     | This file contains all the macros used in the firmware. The details of the macros and their usage can be found in the comments above each macro. |  |  |

#### **Firmware Flow Chart**

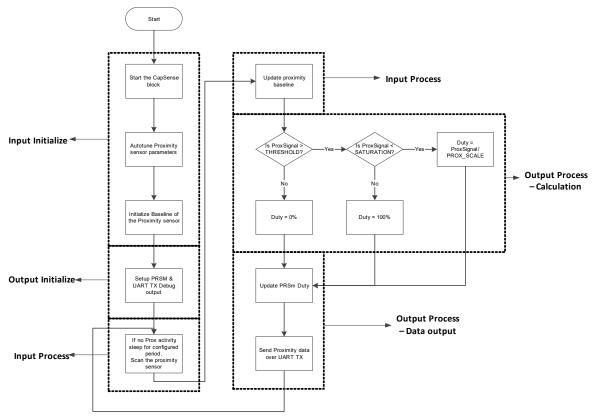

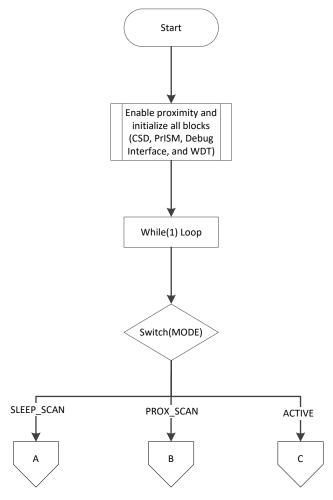

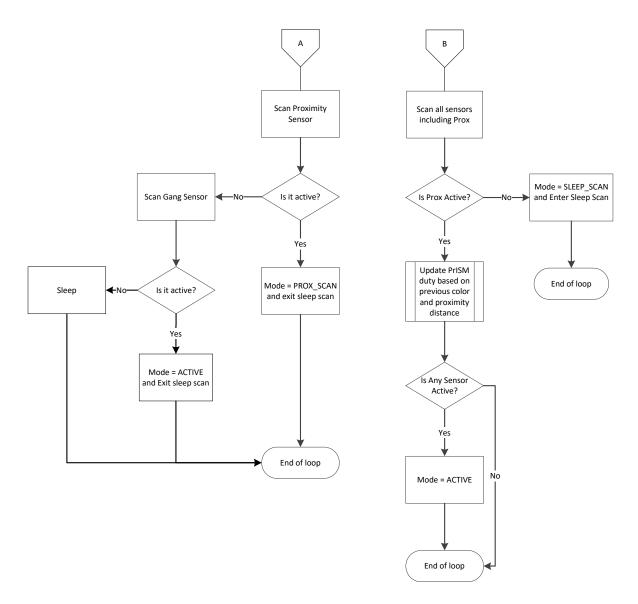

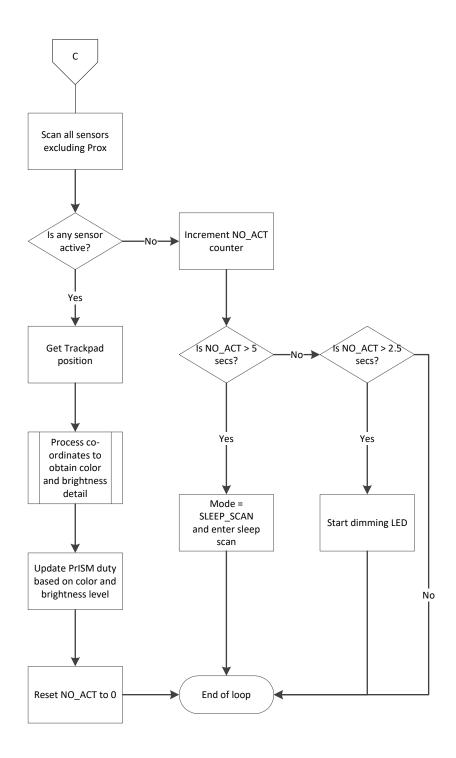

Figure 5-16 shows the flow chart of code implemented in main.c.

Figure 5-16. CapSense Proximity and UART Project Flow Chart

The firmware does the following:

- The CapSense/input initialization part tunes the CapSense system parameters using Smart-Sense.

- The output initialization part configures the PWM and the software UART TX output.

- The infinite loop code is divided into two phases: input process and output process.

- ☐ The input process phase scans the proximity sensor and processes the sensor signal, such as applying filter, calculating baseline, and signal.

- ☐ The output process phase is also split into two phases: the data calculation and data output subphases.

- i. The data calculation subphase compares the proximity signal with a minimum and maximum threshold defined for an approaching hand. The LED brightness is then calculated based on the sensor's signal value relative to the thresholds. The minimum threshold generates the lowest LED brightness, and the maximum threshold generates the highest LED brightness.

- ii. The data output subphase updates the PWM compare value with the calculated brightness. The system data such as sensor raw data, baseline, signal, and calculated LED brightness are sent over the UART TX line.

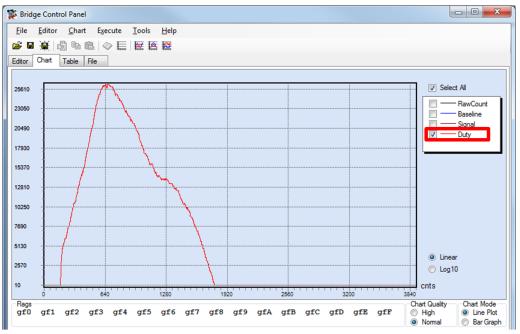

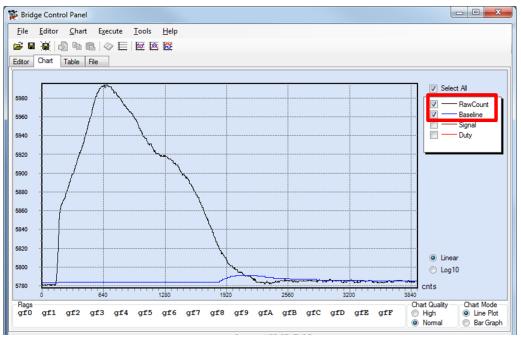

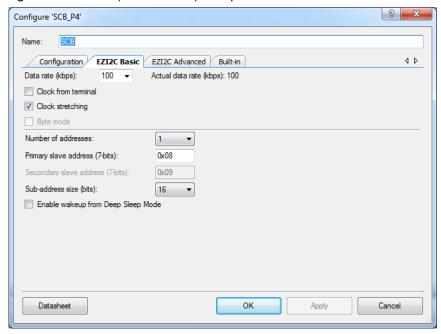

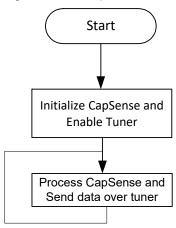

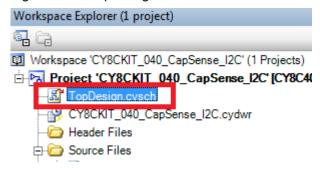

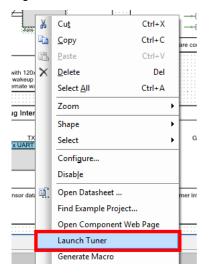

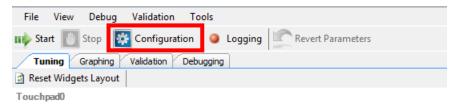

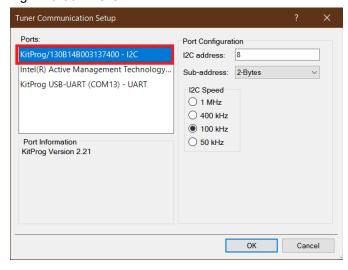

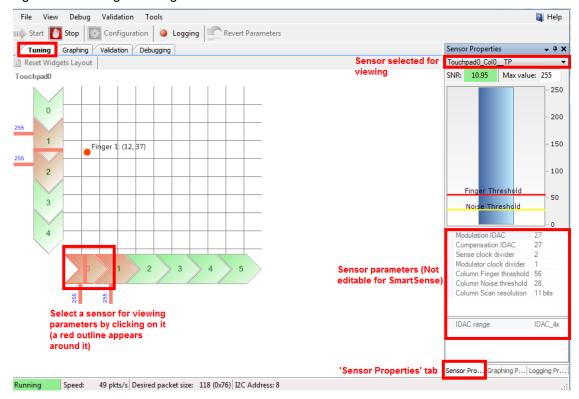

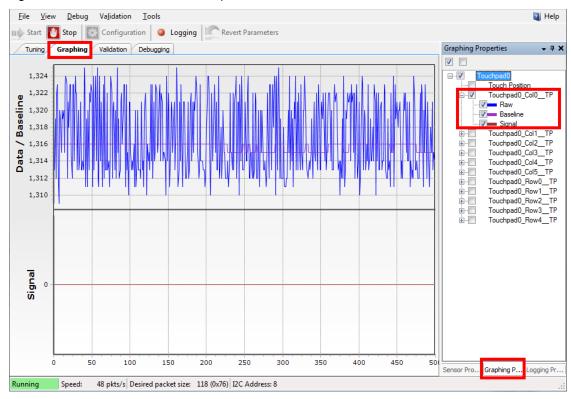

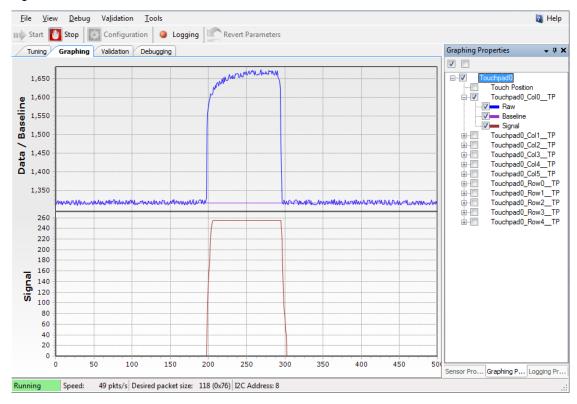

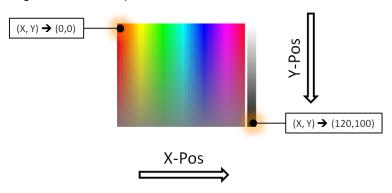

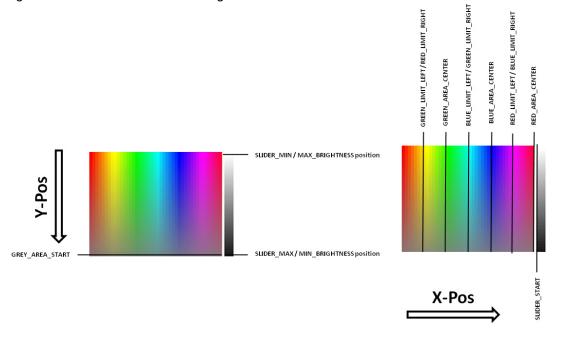

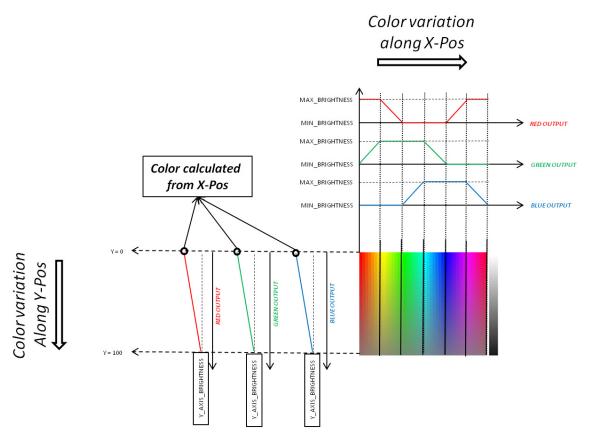

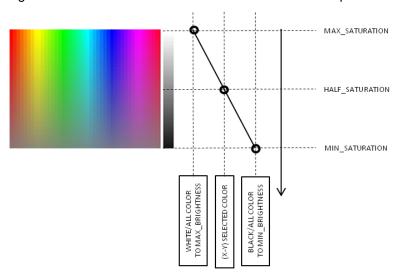

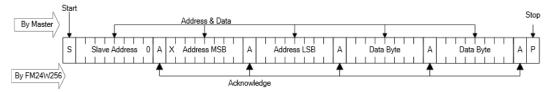

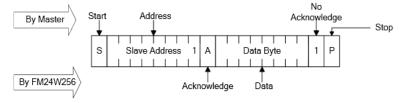

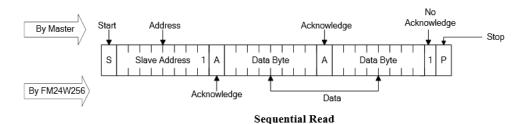

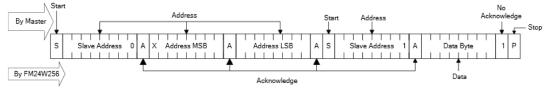

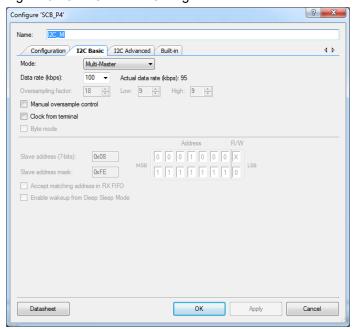

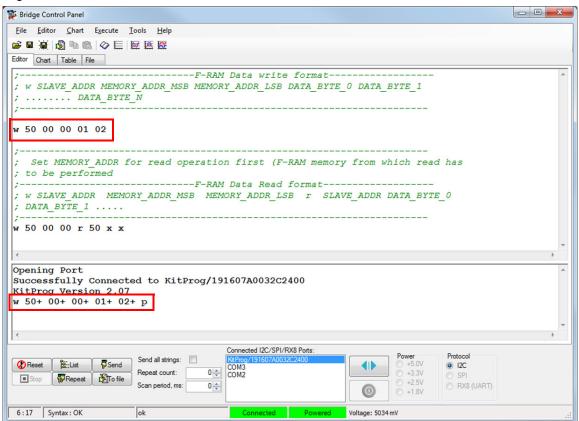

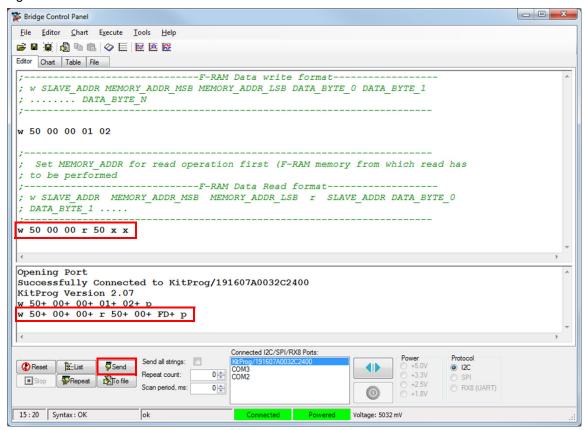

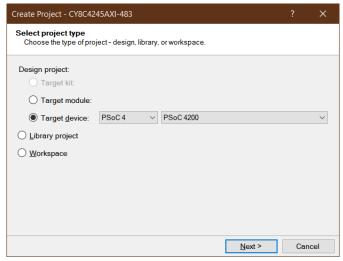

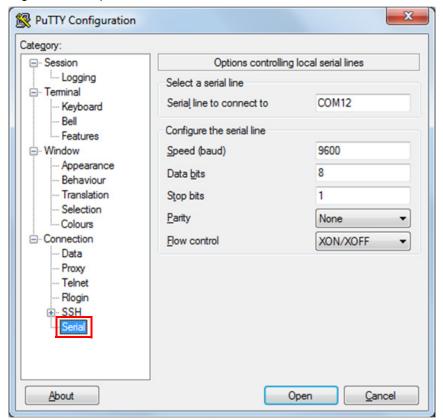

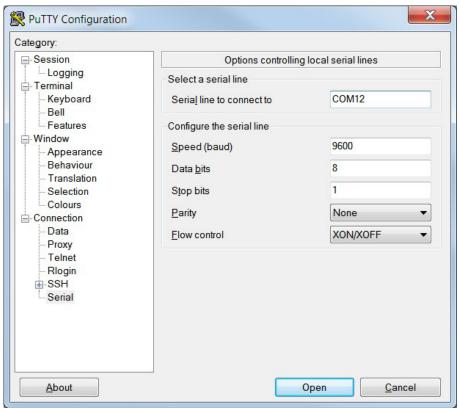

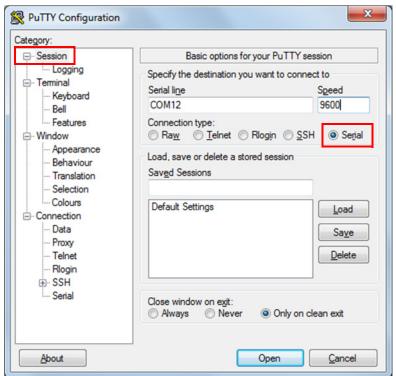

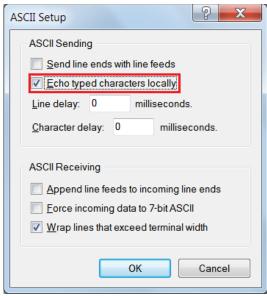

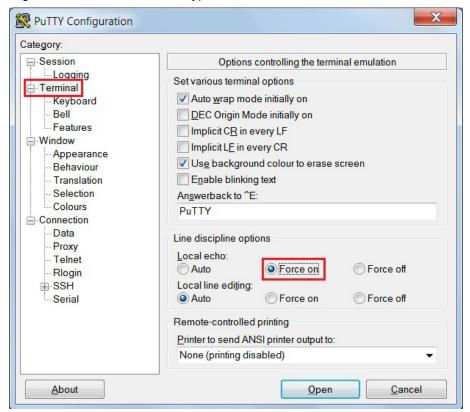

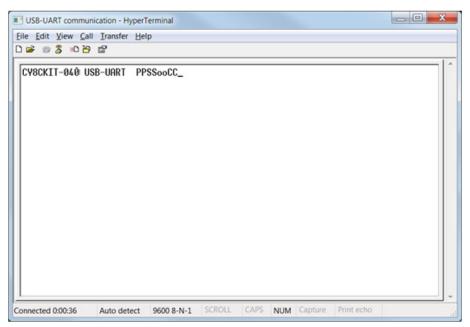

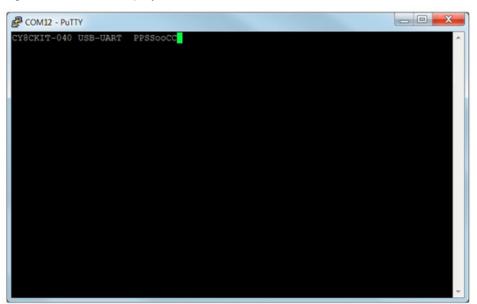

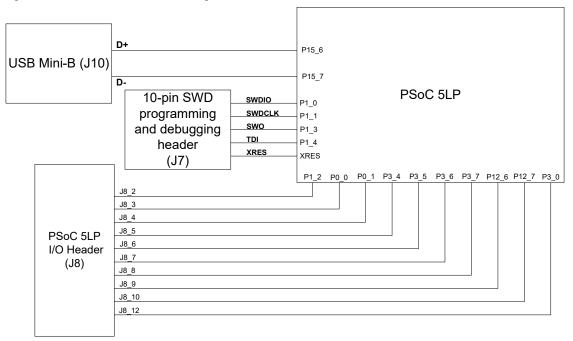

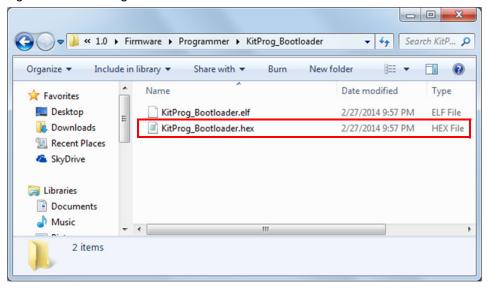

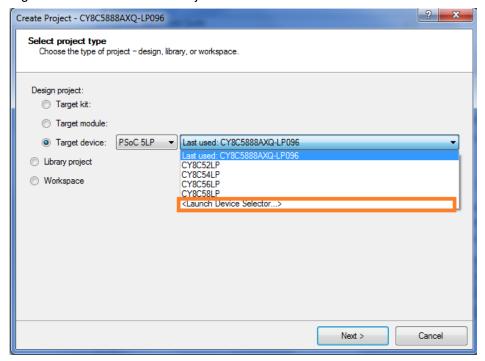

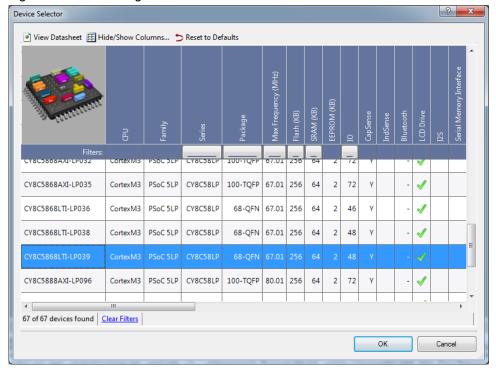

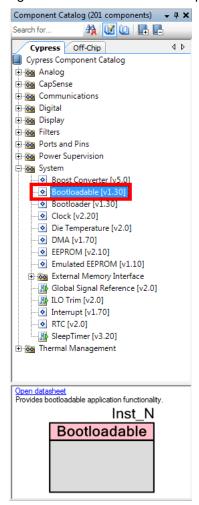

The device monitors the activity on the proximity sensor, and if there is no activity, that is, if the hand is out of range of the proximity, then the device enters a sleep-scan mode. The time for which the device checks for a no activity on the sensor before entering sleep-scan mode is set to 5 seconds and is configurable in the project (ENTER\_SLEEP\_COUNTS macro in *main.h*). In the sleep-scan mode, the device wakes up every 100 ms and checks for any activity on the proximity sensor. This wakeup rate is configurable by modifying the WATCHDOG\_TIMER\_COUNT macro in the *main.h* file.