# SA6880-S - Isolated 3.5 A / 1200 V IGBT Driver

## 1 Features

- Single-channel 1200 V isolated driver optimized for industrial and automotive applications

- 3.5 A peak output current

- 3.75 kV<sub>rms</sub> input to output isolated voltage

- High common-mode transient immunity: higher than 50 kV/μs

- Less than 115 ns propagation delay

- Less than  $\pm 20$  ns pulse width distortion

- Integrated IGBT protection functions:

- IGBT soft turn-off

- Desaturation detection (DESAT)

- o Active Miller-Current clamp

- High Side undervoltage lockout (UVLO) protection with feedback

- Fault sensing/reporting to system controller (DESAT & UVLO)

- TTL compatible inputs

- Automotive temperate range

- Bipolar or unipolar supply operation

- Wide 30 V output supply range

- UL1577 certified to  $V_{ISO} = 3750 V_{RMS}$  for 60 seconds.

- IEC60747-17 and VDE 0884-10 compliant

## 2 Applications

- AC/DC motor drives

- Air-conditioning inverters

- Welding/plasma equipment

- Uninterruptible power supplies

- Battery charging systems

- Automotive OBC and traction inverters

- Auxiliary inverters for HEV and EV

- PV solar inverters and optimizers

## 3 Description

The SA6880-S is a full-featured, galvanically isolated, 3.5 A / 1200 V-rated gate driver IC. This single-chip solution integrates features that improve performance and ensure long-life in harsh environments. It can be used for fast-switching drive and protection of power IGBT's, Si and SiC MOSFETs. The driver incorporates Solantro's on-chip coreless transformer technology to enable 3.75 kV<sub>rms</sub> input to output isolated voltage and high transient immunity (>50 kV/ $\mu$ s) as required in industrial and automotive applications.

The driver is suitable for motor control, switch mode power supply (SMPS), PFC, UPS, EV-OBC, industrial pumps, and traction inverter applications. Its short propagation delay and small timing-skew help achieve optimum performance at higher switching speeds when compared with other driver solutions available in the market. All logic pins are TTL compatible for easy interface to standard controllers and MCUs.

The SA6880-S architecture includes several control features protecting the device in harsh industrial and automotive environments. These integrated features include over-current (desaturation) sensing with soft-shutdown protection, high-side undervoltage lockout, active Miller-Current clamping and fault reporting.

The driver supports bipolar and unipolar supply voltage configurations. In a bipolar configuration, the driver is typically supplied with voltages of +18 V and -5 V. For unipolar configuration, the driver is typically supplied with a positive 18 V (max 32 V).

To meet UL isolation, creepage and clearance requirements the SA6880-S is available in a standard SOIC-16W (wide-body) package.

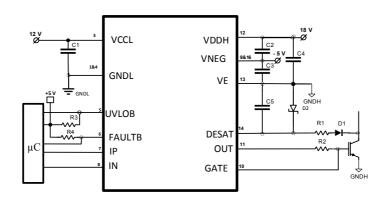

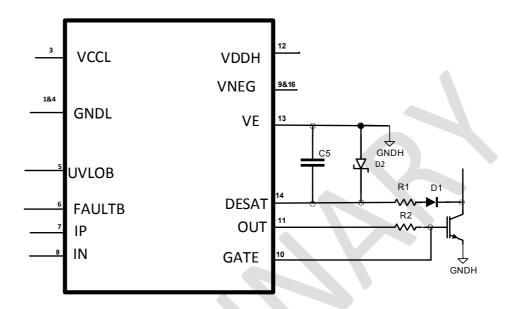

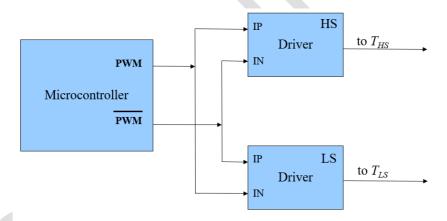

Figure 1- Typical application configuration

## **Content**

| 1    |         |           |                                     |    |

|------|---------|-----------|-------------------------------------|----|

| 2    | Applic  | cations   |                                     | 1  |

| 3    | Descri  | iption    |                                     | 1  |

| 4    | Pin Co  | onfigurat | ion and Functional Diagram          | 3  |

| 5    |         | _         |                                     |    |

|      | 5.1     |           | te maximum rating                   |    |

|      | 5.2     |           | mended operating conditions         |    |

|      | 5.3     |           | cal characteristics                 |    |

|      |         | 5.3.1     | Power supply                        | 5  |

|      |         | 5.3.2     | Logic inputs and outputs            |    |

|      |         | 5.3.3     | Gate Driver output characteristics  | 6  |

|      |         | 5.3.4     | Active Miller clamp                 | 7  |

|      |         | 5.3.5     | Desaturation protection             | 7  |

|      |         | 5.3.6     | Package characteristics             | 8  |

|      | 5.4     | Insulat   | ion characteristics                 | 8  |

|      |         | 5.4.1     | Compliance with UL1577              | 8  |

| 6    | Detail  | ed Desci  | ription                             | 9  |

|      | 6.1     | Power     | Supplies                            | 9  |

|      | 6.2     | Input 8   | k Output                            | 9  |

|      |         | 6.2.1     | Non-Inverting and Inverting Inputs  | 9  |

|      |         | 6.2.2     | Rise and fall and propagation delay | 10 |

|      |         | 6.2.3     | FAULTB and UVLOB outputs            | 10 |

|      |         | 6.2.4     | Driver output                       | 10 |

|      | 6.3     | Interna   | l protection function               | 10 |

|      |         | 6.3.1     | Undervoltage lockout (UVLO)         | 10 |

|      | 6.4     | Externa   | al Protection                       | 12 |

|      |         | 6.4.1     | Desaturation Protection (DESAT)     | 12 |

|      |         | 6.4.2     | Active Miller clamping              | 14 |

| 7 Is | olation |           |                                     | 15 |

|      |         |           |                                     |    |

# 4 Pin Configuration and Functional Diagram

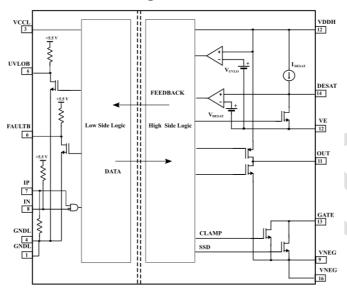

Figure 2- Functional block diagram

| PIN | Name   | Description                                                                                    |

|-----|--------|------------------------------------------------------------------------------------------------|

| 1   | GNDL   | Low side (LS) ground                                                                           |

| 2   | NC     | No connect – (note: <u>connecting to GND or other signals can result in damage to the IC</u> ) |

| 3   | VCCL   | Low side (LS) power supply                                                                     |

| 4   | GNDL   | Low side (LS) ground                                                                           |

| 5   | UVLOB  | Undervoltage lockout, open drain active LOW output                                             |

| 6   | FAULTB | Desaturation (Over-current protection) Fault, open Drain active LOW output                     |

| 7   | IP     | Non-inverting driver input. <sup>1</sup>                                                       |

| 8   | IN     | Inverting driver input. <sup>2</sup>                                                           |

| 9   | VNEG   | High side (HS) negative supply voltage (Ref. VNEG)                                             |

| 10  | GATE   | IGBT Gate connection for Miller current clamp and SSD (soft-shutdown) pull-down                |

| 11  | OUT    | Driver output                                                                                  |

| 12  | VDDH   | High side (HS) positive supply                                                                 |

| 13  | VE     | Connected to IGBT emitter                                                                      |

| 14  | DESAT  | Desaturation (overcurrent) sensing input                                                       |

| 15  | NC     | No connect, for factory test only                                                              |

| 16  | VNEG   | High side negative supply voltage (Ref. VNEG)                                                  |

#### Note:

- 1) IP input controls signal for the driver output while IN is set to low. The IGBT is turned on if IP is set to high and IN is set to low, otherwise is turned off. A minimum pulse width is required to suppress glitches while controlling the IGBT. An internal pull-down resistor ensures that the IGBT is kept in off-state if terminal IP is left unconnected.

- 2) IN input control signals for the driver output while IP is set to high. The IGBT is turned on if IN- is set to low, and is turned off if IN- is set to high, while IN is kept high.

# 5 Specifications

## 5.1 Absolute maximum rating

Absolute maximum ratings are defined as ratings, which when being exceeded may lead to destruction of the integrated circuit. Unless otherwise specified, all voltages at input IC reference to GNDL, all voltages at output IC reference to VE.

| Parameter                                                     | Symbol                  | Min      | Max      | Unit |

|---------------------------------------------------------------|-------------------------|----------|----------|------|

| Low side power supply                                         | VCCL                    | -0.3     | 18       | V    |

| Positive power supply of high side                            | VDDH                    | -0.3     | 30       | V    |

| Negative power supply of high side                            | VNEG                    | -15      | 0.3      | V    |

| Maximum power supply voltage high side (VDDH-VNEG)            | V <sub>MAX_OUT</sub>    |          | 36       | V    |

| Gate driver output voltage                                    | V <sub>OUT</sub>        | VNEG-0.3 | VDDH+0.3 | V    |

| Peak source output current <sup>1</sup>                       | I <sub>OUT_SOURCE</sub> | /        | 3.5      | Α    |

| Peak sink output current <sup>2</sup>                         | I <sub>OUT_SINK</sub>   | 3.5      |          | Α    |

| Gate clamping sinking current <sup>3</sup>                    | I <sub>CLAMP_SINK</sub> | 1        | 1.2      | Α    |

| Logic interface at input side (pins UVLOB, FAULTB, IN and IP) | $V_{LOGIC}$             | -0.3     | 6.5      | V    |

| Pin DESAT voltage                                             | V <sub>DESAT</sub>      | -0.3     | VDDH+0.3 | V    |

| Pin GATE voltage                                              | V <sub>CLAMP</sub>      | -0.3     | VDDH+0.3 | V    |

| Driver junction temperature                                   | T <sub>J</sub>          | -40      | 150      |      |

| Storage temperature                                           | Ts                      | -40      | 150      |      |

| Operating temperature                                         | T <sub>A</sub>          | -40      | 125      |      |

| Max switching frequency <sup>4</sup>                          | f <sub>MAX</sub>        |          | 400      | kHz  |

| Low side power dissipation                                    | $P_{D_{\_IN}}$          |          | 150      | mW   |

| High side power dissipation                                   | $P_{D\_OUT}$            |          | 580      | mW   |

| ESD capability ( Human Body Model )                           | $V_{ESD\_HBM}$          | /        | 2.5      | kV   |

| ESD capability ( Machine model )                              | V <sub>ESD_HBM</sub>    | /        | 200      | V    |

| ESD capability (charged device model)                         | V <sub>ESD_CDM</sub>    | /        | 500      | ٧    |

| Isolation voltage RMS (1 s testing time)                      | V <sub>ISO_RMS</sub>    |          | 4.5      | kV   |

#### Note:

- 1) The peak output current is measured at maximum pulse width equal to 2.5 µs, maximum duty cycle 1%

- 2) The sink output current is measured at maximum OFF time equal to 2.5 µs, maximum duty cycle 99%

- 3) The gate clamp sink current is measured at Maximum OFF time equal to 2.5  $\mu$ s, maximum duty cycle 99% and voltage between GATE and VNEG equal to 2 V.

- 4) The load is 1 nF and a 10  $\Omega$  resistor.

- 5) The LS pins are shorted and HS pins are shorted and  $V_{IO}$  = 500 V

# 5.2 Recommended operating conditions

| Parameter                              | Symbol          | Min | TYP | Max | Unit |

|----------------------------------------|-----------------|-----|-----|-----|------|

| Low side power supply                  | VCCL            | 8   | 12  | 18  | V    |

| High side positive power supply        | VDDH-VE         | 12  | -   | 24  | V    |

| High side negative power supply        | VNEG-VE         | -12 | -   | 0   | V    |

| High side bipolar power supply         | VDDH-VNEG       | -   | -   | 28  | V    |

| Inputs witching frequency <sup>1</sup> | f <sub>sw</sub> |     |     | 150 | kHz  |

| Operating temperature                  | T <sub>A</sub>  | -40 |     | 125 | °C   |

| Input voltage (ON)                     | $V_{in\_ON}$    |     | 3.3 | 5.5 | V    |

| Input voltage (OFF)                    | $V_{in\_OFF}$   |     | 0   | 0.5 | V    |

| Input minimum pulse width <sup>1</sup> | t <sub>on</sub> | 250 |     |     | ns   |

#### Note:

## **5.3** Electrical characteristics

Unless otherwise specified, all Min/Max specification parameters are at recommended operating conditions, all voltages at input IC are referenced to GNDL, all voltages at output IC referenced to  $V_{NEG}$ . All typical values at TA = 25 °C, VCCL = 12 V, VDDH- $V_{NEG}$  = 20 V, VE- $V_{NEG}$  = 0 V

## 5.3.1 Power supply

| Parameters                                             | Symbol                       | MIN  | TYP  | MAX  | Unit |

|--------------------------------------------------------|------------------------------|------|------|------|------|

|                                                        |                              |      |      |      |      |

| Low side quiescent current driver set to OFF           | I <sub>Q_LS_OFF</sub>        |      | 8    | 9    | mA   |

| Low side quiescent current driver set to ON            | I <sub>Q_LS_ON</sub>         |      | 13.5 | 14.5 | mA   |

| High side quiescent current driver set to OFF          | I <sub>Q_HS_OFF</sub>        |      | 16   | 17   | mA   |

| High side quiescent current driver set to ON           | I <sub>Q_HS_ON</sub>         |      | 16.5 | 18   | mA   |

| UVLO threshold high (rising)                           | $V_{UVLO\_H}$                | 11.8 | 11.9 | 12.2 | V    |

| UVLO threshold low (falling)                           | $V_{UVLO\_L}$                | 11.1 | 11.4 | 11.7 | V    |

| UVLO hysteresis                                        | $V_{\text{UVLO\_HYS}}$       |      | 0.5  |      | V    |

| Minimum duration for UVLO report <sup>1</sup>          | t <sub>MIN_UVLO_REPORT</sub> |      |      | 100  | μs   |

| VDDH UVLO to OUT go low delay <sup>1</sup>             | t <sub>UVLO_ON</sub>         |      | 5    |      | μs   |

| VDDH UVLO to OUT go high delay <sup>1</sup>            | t <sub>UVLO_OFF</sub>        |      | 5    |      | μs   |

| OUT to UVLOB high low communication delay <sup>1</sup> | t <sub>HL_UVLO_COM_DEL</sub> |      |      | 5    | μs   |

| OUT to UVLOB low high communication delay <sup>1</sup> | t <sub>lH_UVLO_COM_DEL</sub> |      |      | 5    | μs   |

#### Note:

1) Guaranteed by design. (see Figure 6 thru Figure 8 for definition of the times.)

<sup>1)</sup> Tested with a load of 10 nF capacitor and a 10  $\Omega$  resistor.

**Preliminary Datasheet** – DPD1181

## 5.3.2 Logic inputs and outputs

VCCL-GNDL= 12 V; VDDH-VE= 20 V; VNEG-VE= 0 V; -40°<T<sub>J</sub><150°

| Parameters                                      | Symbol                    | MIN | TYP | MAX | Unit |

|-------------------------------------------------|---------------------------|-----|-----|-----|------|

| IN inputs current when set to high <sup>1</sup> | I <sub>IN_H</sub>         |     | -5  |     | μΑ   |

| IP inputs current when set to high <sup>1</sup> | I <sub>IP_H</sub>         |     | 45  |     | μΑ   |

| IN inputs current when set to low <sup>2</sup>  | I <sub>IN_L</sub>         |     | -50 |     | μΑ   |

| IP inputs current when set to low <sup>2</sup>  | I <sub>IP_L</sub>         |     | 0   |     | μΑ   |

| IN input voltage when driver turns OFF          | V <sub>IN_OFF</sub>       |     | 2.4 |     | V    |

| IN input voltage when driver turns ON           | $V_{IN_{ON}}$             |     | 2.2 |     | V    |

| IN inputs threshold voltage hysteresis          | $V_{\text{IN\_THR\_HYS}}$ |     | 0.2 |     | V    |

| IP input voltage when driver turns OFF          | $V_{IP_OFF}$              |     | 2.2 |     | V    |

| IP input voltage when driver turns ON           | $V_{IP_{ON}}$             |     | 2.5 |     | V    |

| IP inputs threshold voltage hysteresis          | $V_{\text{IP\_THR\_HYS}}$ |     | 0.3 |     | V    |

| FAULTB and UVLOB current when high <sup>1</sup> | I <sub>DIG_HIGH</sub>     |     | -5  |     | μΑ   |

| FAULTB and UVLOB current when low <sup>2</sup>  | I <sub>DIG_LOW</sub>      |     | -50 |     | μΑ   |

| Voltage of UVLOB(FAULTB) pin when sinking 4 mA  | $V_{DIG\_LOW}$            |     |     | 300 | mV   |

Note:

## 5.3.3 Gate Driver output characteristics

VCCL-GNDL= 12 V; VDDH-VE= 20 V; VNEG-VE= 0 V;  $C_L$ = 100 pF; -40°< $T_J$ <150°

| Parameters                              | Symbol                  | Conditions                         | MIN | TYP      | MAX | Unit |

|-----------------------------------------|-------------------------|------------------------------------|-----|----------|-----|------|

| High level output voltage <sup>1</sup>  | V <sub>OUT_H</sub>      |                                    |     | VDDH-0.2 |     | V    |

| Low level output voltage <sup>2</sup>   | $V_{OUT\_L}$            |                                    |     | VNEG+0.1 |     | V    |

| Peak source output current <sup>3</sup> | I <sub>OUT SOURCE</sub> |                                    |     | 7.2      |     | Α    |

| Peak sink output current⁴               | I <sub>OUT_SINK</sub>   |                                    |     | 7.6      |     | Α    |

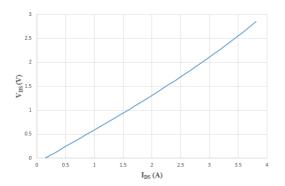

| Source output current at                | I <sub>OUT_P_3V</sub>   | $V_{DS\_P-FET} = 3 V^5$            |     | -2       |     | Α    |

|                                         | I <sub>OUT_P_15V</sub>  | $V_{DS_P-FET} = 15 V^5$            |     | -7       |     | Α    |

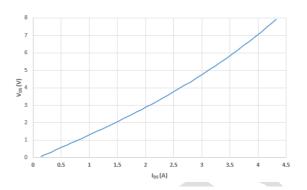

| Sink output current at                  | I <sub>OUT_N_2.5V</sub> | $V_{DS_{N-FET}} = 2.5 \text{ V}^6$ |     | 3.5      |     | Α    |

|                                         | I <sub>OUT_N_6V</sub>   | $V_{DS_N-FET} = 6 V^6$             |     | 6.5      |     | Α    |

| Output voltage rise time (10 % to 90%)  | t <sub>r</sub>          | C <sub>L</sub> = 10 nF             |     | 90       |     | ns   |

| Output voltage fall time (90% to10%)    | t <sub>f</sub>          | C <sub>L</sub> = 10 nF             |     | 70       |     | ns   |

| Turn ON propagation delay (50% to 50%)  | t <sub>D_ON</sub>       |                                    |     | 115      | 150 | ns   |

<sup>1)</sup> Pin set to 5 V.

<sup>2)</sup> Pin set to 1 V.

**Preliminary Datasheet** – DPD1181

| Turn OFF propagation delay (50% to 50%)                | t <sub>D_OFF</sub> |     | 90 | 125 | ns    |

|--------------------------------------------------------|--------------------|-----|----|-----|-------|

| Pulsed width distortion <sup>7</sup>                   |                    | -20 |    | +20 | ns    |

| Dead time distortion <sup>8</sup>                      |                    | -30 |    | +30 | ns    |

| Common mode transient immunity Logic High <sup>9</sup> | CMTI_LH            |     | 50 |     | kV/μs |

| Common mode transient immunity Logic Low <sup>9</sup>  | CMTI_LL            |     | 50 |     | kV/μs |

#### Note

- 1) Set voltage on pins IP to 5 V and IN to 0 V and  $I_{OUT}$  =-100 mA.

- 2) Set voltage on pins IP and IN to 0 V and  $I_{OUT} = 100$  mA.

- 3) The peak output current is measured at maximum pulse width equal to 2.5 µs, maximum duty cycle 1%.

- 4) The sink output current is measured at maximum OFF time equal to 2.5  $\mu$ s, maximum duty cycle 99% .

- 5) See Figure 3

- 6) see Figure 4

- 7) Pulse width distortion (PWD) is defined as  $(t_{D\_ON} t_{D\_OFF})$  of any given unit.

- 8) Dead time Distortion (DTD) is defined as  $(t_{D OFF} t_{D ON})$  between any two parts under the same test conditions.

- 9)  $V_{CM} = 1500 \text{ V}$

#### 5.3.4 Active Miller clamp

VCCL-GNDL= 12 V; VDDH-VE= 20 V; VNEG-VE= 0 V; C<sub>L</sub>= 100 pF; -40°<T<sub>J</sub><150°

| Parameters                                    | Symbol               | MIN | TYP        | MAX | Unit |

|-----------------------------------------------|----------------------|-----|------------|-----|------|

| Soft shutdown current during fault conditions | I <sub>OUT_FLT</sub> |     | 130        |     | mA   |

| Clamp threshold voltage                       | $V_{CLP\_TH}$        | 1.6 | 1.8        | 2.4 | V    |

| Low level clamp sinking current <sup>1</sup>  | I <sub>CLAMP</sub>   |     | 1.7        |     | Α    |

| Low level clamp voltage <sup>2</sup>          | V <sub>CLP</sub>     |     | VNEG + 0.3 |     | V    |

#### Note:

- 1) The gate clamp sink current is measured at V<sub>out</sub> = VE+3 V

- 2) The voltage is measured at I =100 mA.

## 5.3.5 Desaturation protection

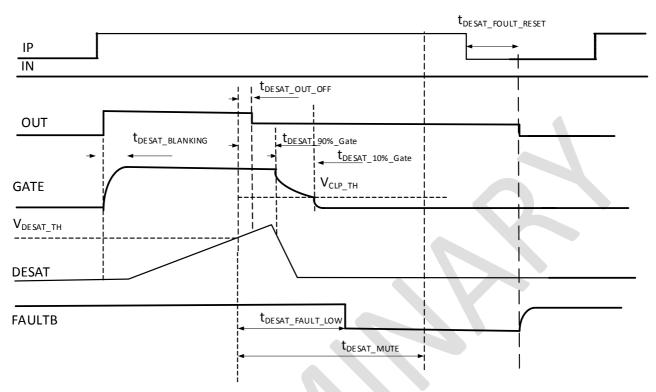

VCCL-GNDL= 12 V; VDDH-VE= 20 V; VNEG-VE= 0 V;  $C_L$ = 100 pF; -40°< $T_J$ <150° (see Figure 10)

| Parameters                                             | Symbol                          | MIN | ТҮР | MAX | Unit |

|--------------------------------------------------------|---------------------------------|-----|-----|-----|------|

| DESAT threshold voltage                                | V <sub>DESAT_TH</sub>           |     | 6.5 |     | V    |

| DESAT charging current <sup>1</sup>                    | I <sub>DESAT_CH</sub>           |     | 0.9 |     | mA   |

| DESAT soft turn-OFF current <sup>2</sup>               | I <sub>DESAT_SOFT_OFF</sub>     |     | 18  |     | mA   |

| Initial DESAT blanking time <sup>3</sup>               | t <sub>DESAT_BLANKING</sub>     |     | 0.6 |     | μs   |

| DESAT output mute time                                 | t <sub>DESAT_MUTE</sub>         |     | 3.2 |     | ms   |

| DESAT to FAULTB low delay <sup>3</sup>                 | t <sub>DESAT_FAULTB_LOW</sub>   | -   | 5   |     | μs   |

| DESAT to 90% GATE delay <sup>4</sup>                   | t <sub>DESAT_90%_GATE</sub>     |     | 0.3 |     | μs   |

| DESAT to 10% GATE delay <sup>4</sup>                   | t <sub>DESAT_10%_GATE</sub>     |     | 0.1 |     | μs   |

| DESAT sense to start turn OFF                          | t <sub>DESAT_OUT</sub>          | -   | -   | 150 | ns   |

| Input kept low before FAULTB go high time <sup>3</sup> | t <sub>DESAT_FAULTB_RESET</sub> |     | 3.2 |     | ms   |

**Preliminary Datasheet** – DPD1181

#### Notes:

- 1)  $V_{DESAT} = 0 V$ .

- 2)  $V_{DESAT} = 3 V$ .

- 3) Guaranteed by design.

- 4)  $C_{GATE} = 1 \text{ nF}.$

## 5.3.6 Package characteristics

| Parameters                                | Symbol              | MIN | TYP              | MAX | Unit |

|-------------------------------------------|---------------------|-----|------------------|-----|------|

| Input to output resistance <sup>1</sup>   | R <sub>IN_OUT</sub> |     | 10 <sup>12</sup> |     | Ω    |

| Input to output capacitance and 2         | $C_{IN\_OUT}$       |     | 1                |     | pF   |

| IC junction to case thermal resistance    | $\Theta_{JC}$       |     | TBD              |     | °C/W |

| IC junction to ambient thermal resistance | $\Theta_{JA}$       |     | 75               | V   | °C/W |

#### Note:

- 1) The driver is treated as a two-terminal device. Pin 1 through pin 8 are shorted together and pin 9 through pin 16 are shorted together.

- 2) f =1 MHz.

## 5.4 Insulation characteristics

## 5.4.1 Compliance with UL1577

| Parameters                                         | Symbol                 | Conditions                                                         | Value | Unit      |

|----------------------------------------------------|------------------------|--------------------------------------------------------------------|-------|-----------|

| External clearance                                 | CLR                    | Shortest terminal-to-terminal distance through air                 | >8    | mm        |

| External creepage                                  | CPG                    | Shortest terminal-to-terminal distance across the package surface  | >8    | mm        |

| Distance through the insulation                    | DTI                    | Minimum internal gap (Internal clearance) of the double insulation | >17   | μm        |

| Insulation withstand voltage for 1min <sup>1</sup> | VI <sub>ISO_1MIN</sub> |                                                                    | 3750  | $V_{rms}$ |

| Insulation withstand voltage for 1sec <sup>1</sup> | V <sub>ISO_1SEC</sub>  |                                                                    |       | $V_{rms}$ |

#### Note:

1) The driver is treated as a two-terminal device. Pin 1 through pin 8 are shorted together and pin 9 through pin 16 are shorted together.

**Preliminary Datasheet** – DPD1181

Figure 3 P-FET output characteristics

Figure 4 N-FET output characteristics

## 6 Detailed Description

The SA6880-S is a single channel, galvanically-isolated, 3.5 A / 1200 V gate driver in a SO-16 package. It can be used for fast-switching drive and control of current generation power IGBT's, Si and SiC MOSFETs. Reinforced galvanic isolation is provided by Solantro's on-chip coreless transformer technology. The SA6880-S architecture includes several control features that protect an IGBT in harsh industrial and automotive environments. These integrated features include IGBT desaturation (over-current) sensing with soft-shutdown protection, high-side undervoltage lockout, active Miller-Current clamping and fault reporting to the system controller.

## **6.1 Power Supplies**

Separate power supplies are required for the low and high sides due to the input and output of the SA6880-S being galvanically isolated from each other. The low side power supply is connected to VCCL and GNDL. Its voltage can be between 8 and 18 V. The driver supports bipolar and unipolar supply voltage configurations. For unipolar configuration, VE and VNEG pins are shorted. The driver is typically supplied with a positive 18 V (max 32 V). In a bipolar configuration, the driver is typically supplied with voltages of +18 V on VDDH and VE pins and -5 V on VNEG and VE pins.

#### 6.1.1 Input & Output

#### 6.1.2 Non-Inverting and Inverting Inputs

There are two possible input modes to control an IGBT:

- 1) Non-inverting mode (IP controls the driver output while IN is set to low).

- 2) Inverting mode (IN controls the driver output while IP is set to high).

A minimum input pulse width is defined to filter occasional glitches. Any glitch on IP or IN shorter than 40 ns would be ignored.

The truth table for input and output signals is shown below:

| IP | IN | OUT |

|----|----|-----|

| 0  | 0  | 0   |

| 0  | 1  | 0   |

| 1  | 0  | 1   |

| 1  | 1  | 0   |

**Preliminary Datasheet** – DPD1181

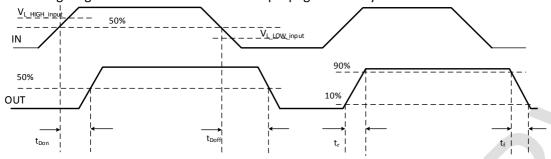

#### 6.1.3 Rise and fall and propagation delay

The timing diagram for rise and fall time and propagation delay is shown below.

Figure 5 - Propagation delay and rise and fall time

#### 6.1.4 FAULTB and UVLOB outputs

The device has default open-drain FAULTB and UVLOB outputs. The FAULTB input will transition to LOW when an IGBT over-current DESAT fault condition occurs. The UVLOB input will transition to LOW when an UVLO event occurs at the high side power supply. To ensure the low side outputs are HIGH when no faults are detected, pull-up resistors are used.

#### 6.1.5 Driver output

The output driver section provides a rail-to-rail output, it clamps to LOW default. During normal operation, V<sub>OUT</sub> drives the IGBT gate high or LOW according to the signals applied to IP and IN. The driver provides max 3.5 A sink & source currents.

## 6.2 Internal protection function

#### 6.2.1 Undervoltage lockout (UVLO)

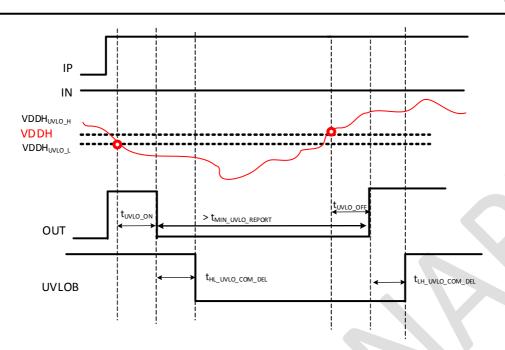

To ensure correct switching of the power devices, an undervoltage lockout (UVLO) function is integrated in the driver high side. If the high side power supply, VDDH, falls below VDDH<sub>UVLO\_L</sub>, the IGBT is turned OFF and the input signals at IP and IN are ignored until VDDH rises above VDDH<sub>UVLO\_H</sub>. The driver does not turn OFF and ON immediately. The time between UVLO detection until the driver output goes low is "VDDH UVLO to OUT go low delay", t<sub>UVLO\_ON</sub>. The time between VDDH rising above VDDH<sub>UVLO\_H</sub> to the driver output going high is "VDDH UVLO to OUT go high delay", t<sub>UVLO\_OFF</sub>.

When an UVLO event happens, a report is sent to low side pin UVLOB. The time between the driver output going low to the time pin UVLOB goes low is "OUT to UVLOB high low communication delay", t<sub>HL\_UVLO\_COM\_DEL</sub>. The time between the driver output going high to the time pin UVLOB goes high is "OUT to UVLOB low high communication delay<sup>3</sup>", t<sub>LH UVLO COM DEL</sub>. Figure 6 shows the SA6880-S during UVLO condition for time higher than t<sub>MIN UVLO REPORT</sub>.

Figure 6 – The SA6880-S during UVLO for time higher than  $t_{\text{MIN\_UVLO\_REPORT}}$ .

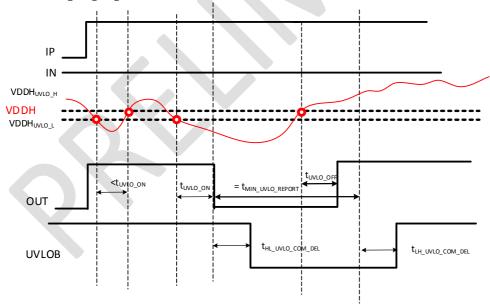

When the driver power supply voltage, VDDH, falls below the threshold voltage VDDH $_{UVLO\_L}$  for time smaller than the time  $t_{UVLO\_ON}$ , the driver is not turned OFF as it is shown in Figure 7. When UVLO is reported and soon after that the driver power supply voltage, VDDH, rises above VDDH $_{UVLO\_H}$ , the driver output goes high after time  $t_{UVLO\_OFF}$ . The report to the low side UVLOB pin is sent after the time  $t_{MIN\_UVLO\_REPORT}$  expires, and the pin becomes high after time  $t_{HL\_UVLO\_COM\_DEL}$  as shown in Figure 7.

Figure 7 - The SA6880-S during UVLO for time smaller than  $t_{\text{UVLO\_ON}}$  and when the UVLO report is expanded to at least time  $t_{\text{MIN\_UVLO\_REPORT}}$ .

Preliminary Datasheet - DPD1181

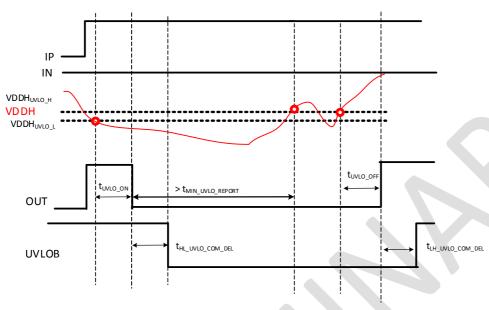

When the SA6880-S is under UVLO condition and VDDH goes high but is not stable, the driver output will not go high until the driver power supply voltage rises above VDDH $_{UVLO\_H}$  for a time longer than  $t_{UVLO\_OFF}$ . This is shown in Figure 8.

Figure 8 - The SA6880-S under UVLO condition and VDDH goes high but is not stable

#### 6.3 External Protection

#### 6.3.1 Desaturation Protection (DESAT)

The driver has a DESAT input and a de-saturation (over-current) protection function for monitoring the IGBT collector emitter saturation voltage (VCE). The DESAT circuitry must remain disabled for a short time period. The time for the driver to response to DESAT condition is known as blanking time, t<sub>DESAT\_BLANKING</sub>. The blanking time is controlled internally and externally. The blanking time depends on the internal charge current, I<sub>DESAT\_CH</sub>, the DESAT reference threshold voltage, V<sub>DESAT\_TH</sub>, and the DESAT capacitor.

The capacitor,  $C_5$ , between the DESAT and VE pins start to charge with current  $I_{DESAT\_CH}$ . A Zener diode,  $D_2$ , is pleased in parallel with the capacitor  $C_5$  to avoid any voltage overshoot between DESAT and VE pins.

When the voltage at DESAT pin becomes higher than  $V_{DESAT\_TH}$ , soft turn OFF of the IGBT occurs. The capacitor value determines the blanking time  $t_{DESAT\_BLANKING}$ .

$$t_{DESAT\_BLANKING} = \frac{c_5 V_{DESAT\_TH}}{I_{DEASAT\_CH}}$$

The DESAT pin is connected to the IGBT collector by a diode,  $D_1$ , and a resistor  $R_1$  as shown in Figure 9. The diode blocks the voltage across the IGBT during its off state. The diode should be fast, to respond to the fault, and have minimum reverse recovery time to prevent a false trip. For very high IGBT blocking voltages, in the kilovolt range, multiple diodes in series could be used. Multiple diodes can also be used to adjust the actual DESAT threshold voltage.

where n is number of diodes and  $V_{\text{F}}$  is a diode forward voltage drop.

Figure 9 - DESAT circuitry

The propagation delay from DESAT sense to starting soft turn OFF,  $t_{DESAT\_OUT}$ , is less than 150 ns (max). The soft turn OFF current,  $I_{DESAT\_SOFT\_OFF}$  is 53 mA typically. When the GATE voltage becomes equal to  $V_{CLP\_TH}$ , the GATE pin is shorted to VNEG.

When desaturation protection is activated, the FAULTB pin on the low side should be set to LOW. The time from the DESAT sense and setting the FAULTB pin to LOW,  $t_{DESAT\_FAULTB\_LOW}$ , is less than 2  $\mu$ s (typical). During DESAT, the input of the driver is muted. The time from when DESAT exceeds the threshold value to the time the input is muted is  $t_{DESAT\_MUTE}$ . When the mute time expires, the input signal should be kept LOW for the fault status to return high. This time is  $t_{DESAT\_FAULTB\_RESET}$ . The time from exceeding the threshold value to 90 % of the GATE voltage and the time from exceeding the threshold value to 10 % of the GATE voltage depends on the gate capacitance,  $C_{GATE}$ .

**Preliminary Datasheet** – DPD1181

Figure 10- Driver time diagram during DESAT conditions (the timescale is not proportional)

## 6.3.2 Active Miller clamping

When the IGBT is turned off and the gate voltage is reduced to the Miller clamp threshold voltage,  $V_{CLP\_TH}$ , the active Miller clamp circuit monitoring the IGBT gate voltage, connects the IGBT gate to the emitter. The Miller clamp threshold voltage is typically 2.1 V relative to VNEG (max 2.4 V). The clamping current is typically 0.9 A.

Figure 11- Voltages on pins IP, OUT and GATE during driver turn ON and OFF.

**Preliminary Datasheet** – DPD1181

#### 7 Isolation

SA6880-S utilizes a magnetically coupled, galvanically isolated, barrier that electrically isolates circuitry between the low side and the high side. The on-chip coreless transformers prevent unwanted AC or DC signals from traveling from one side to the other. They also transmit the switching information between the input chip and output chip and other signals (DESAT and UVLO). The coreless transformer technology provides short propagation delays, excellent delay matching, and strong robustness for driving IGBTs and SiC MOSFETs.

## 8 Common mode transient immunity

Common mode transient immunity (CMTI) is a key specification parameter of isolated drivers. CMTI is the maximum tolerable rate of the rise or fall of the common mode voltage,  $V_{CM}$ . SA6880-S is implemented in an advanced Silicon-on-Insulator high-voltage process (SOI-BCD) which allows the driver to operate latch-up free (by design), even in the presence of large over/under-shoot voltage excursions. As a result, the driver is immune to the noise generated by large dv/dt and di/dt variations during IGBTs or SiC MOSFETs switching.

## 9 Interlock protection and glitch filtering

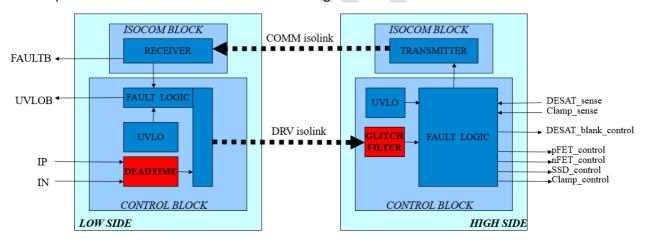

The SA6880-S integrates two functions (interlock protection and glitch filtering) to protect from undesired shoot through operation. Figure 12 shows the SA6880-S digital top block diagram. The DEADTIME block is used for interlock protection and GLITCH Filter block for filtering.

Figure 12 - SA6880-S digital top block diagram

### 9.1 Interlock protection

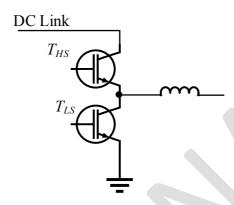

IGBTs are mostly used in three-phase applications such as variable-frequency drives, uninterruptible power supply, solar inverters, and other similar inverter applications. To ensure proper operation of an inverter, the switches of an inverter leg should not switch simultaneously. Dead time is used before the transition of high and low-side switch operation to avoid shoot-through. Interlock protection is integrated in SA6880-S drivers to prevent shoot-through. Avoiding shoot-through operation prevents unwanted additional losses or even failure

**Preliminary Datasheet** – DPD1181

of power devices. The interlock protection will prevent both switches from being ON if there is an error in calculation of the programmed dead time.

Figure 13 shows one leg of three-phase converter. Each IGBT has its own driver. When the drivers are connected according to Figure 14, a minimum dead time of  $0.8~\mu s$  will be introduced before the switches change state. This feature prevents a shoot-through condition.

Figure 13 A leg of three-phase inverter

Figure 14 High and low side drivers' connections for interlock protection

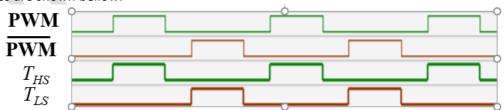

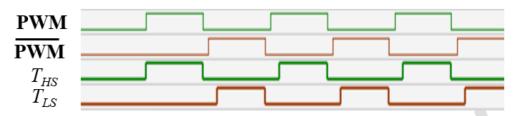

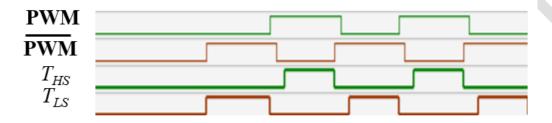

Three examples are shown bellow:

Figure 15 Driver inputs have enough deadtime. Original deadtime from the inputs preserved by the driver.

# **Preliminary Datasheet** – DPD1181

Figure 16 Driver inputs have some deadtime, but less than the minimum deadtime of the driver. Minimum deadtime ensured by the driver.

Figure 17 Driver inputs overlapping. Minimum deadtime ensured by the driver.

#### 9.2 Glitch filtering

High-power applications are susceptible to noise from the large voltage and current transients in the power switches. This noise could propagate to the gate drivers' control signals causing the driver to turn ON when it should be OFF. The spike may be so small and insufficient to fully turn ON the power device, due to the power switch input capacitance and gate resistance causing high conduction loss. If in a half-bridge configuration, the two power devices are switching complementary and therefore, shoot-through is a concern if they are accidentally ON at the same time. During shoot-through, high current flows through the devices which can damage the power switches. The SA6880-S has an input glitch filter that rejects the high frequency noise, so the driver output does not see glitches shorter than 30 - 40 ns. This corresponds to a 30 MHz switching frequency, which is significantly higher than the switching frequency in most IGBT or SiC MOSFET -based applications. The glitch filter rejects positive and negative pulses preventing the accidental turning ON or OFF of the switch. The glitch filter integrated within the gate driver improves driver performance in noisy environments and protects the device from possible failure.

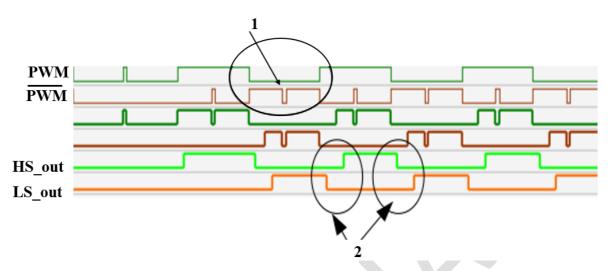

Figure 18 shows the input drivers' signals when glitches with 1-clock (20 ns) duration are present. Also, there is no dead time between the input signals. In the output signal the glitches (1) are removed and the dead time is introduced (2).

Figure 18 Input and output drivers' signals when 1-clock (20 ns) glitches are present and not dead time of the input signal.

# 10 SA6880-S - Recommended Application Circuit

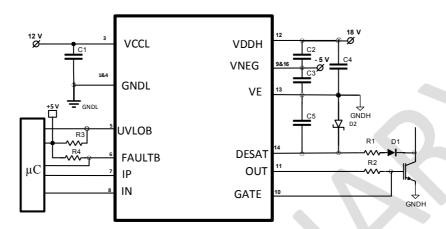

Figure 19 shows a recommended application circuit for the SA6880-S.

Figure 19- SA6880-S recommended application circuit.

Capacitors C1 and C2 are decoupling capacitors (recommended value = 1  $\mu$ F). Capacitors C3 and C4 are decoupling capacitors (recommended value = 10  $\mu$ F). The DESAT circuit includes a high voltage diode (D<sub>1</sub>), a 1  $k\Omega$  resistor (R<sub>1</sub>) and 220 nF capacitor (C<sub>5</sub>). Diode D<sub>2</sub> prevents the voltage on the DESAT pin from falling 0.4 V below the voltage on VE pin.

The gate resistor ( $R_2$ ) limits the gate charge current and indirectly controls the IGBT collector voltage rise and fall times. Its value depends on the IGBT type. The recommended value is 5  $\Omega$ .

The pull-up resistors, R4 and R5 ensure the low side outputs are high when no faults are detected. Their recommended value is  $3.3~k\Omega$ .

# 11 Package Outline Drawings

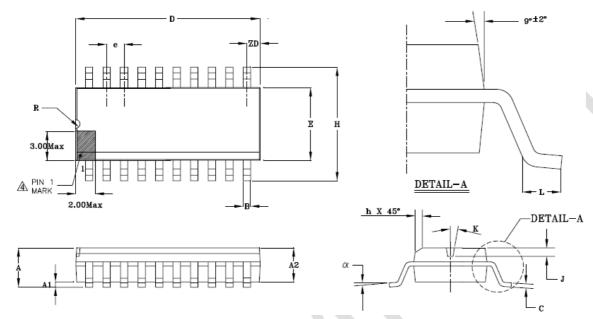

The SA6880-S uses an SOIC16 Wide-Body package as shown below:

#### SOICW 16LD

| SOIC-16LD   |                                                                                       |

|-------------|---------------------------------------------------------------------------------------|

| MILLIMETERS |                                                                                       |

| MIN         | MAX                                                                                   |

| 2.44        | 2.64                                                                                  |

| 0.10        | 0.30                                                                                  |

| 2.24        | 2.44                                                                                  |

| 0.36        | 0.46                                                                                  |

| 0.23        | 0.32                                                                                  |

| 10.11       | 10.31                                                                                 |

| 7.40        | 7.60                                                                                  |

| 1.27 BSC    |                                                                                       |

| 10.11       | 10.51                                                                                 |

| 0.31        | 0.71                                                                                  |

| 0.53        | 0.73                                                                                  |

| 7° BSC      |                                                                                       |

| 0.51        | 1.01                                                                                  |

| 0.63        | 0.89                                                                                  |

| 0.66 REF    |                                                                                       |

| 0°          | 8°                                                                                    |

|             | MILLIM MIN 2.44 0.10 2.24 0.36 0.23 10.11 7.40 1.27 10.11 0.31 0.53 7° 0.51 0.63 0.66 |

#### NOTES :

- 2. PACKAGE SURFACE FINISHING : (2.1) TOP : MATTE (CHARMILLES  $\#18\sim30$ ). (2.2) BOTTOM : SMOOTH OR MATTE (CHARMILLES  $\#12\sim27$ ).

- 3. ALL DIMENSIONS EXCLUDING MOLD FLASHES AND END FLASH FROM THE PACKAGE BODY SHALL NOT EXCEED 0.25MM (.010") PER SIDE(D).

A DETAIL OF PIN \$1 IDENTIFIER ARE OPTIONAL BUT MUST BE LOCATED WITHIN THE ZONE INDICATED.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Solantro Semiconductor: