# 32-Bit Flash Microcontroller with MIPS32 $^{\circledR}$ microAptiv $^{TM}$ UC Core, Low Power and USB

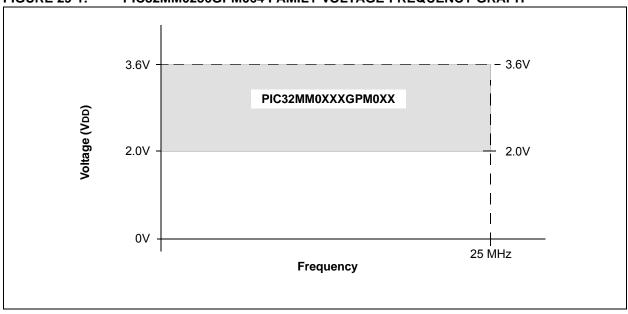

#### **Operating Conditions**

• 2.0V to 3.6V, -40°C to +85°C, DC to 25 MHz

#### **Low-Power Modes**

- · Low-Power modes:

- Idle CPU off, peripherals run from system clock

- Sleep CPU and peripherals off:

- Fast wake-up Sleep with retention

- Low-power Sleep with retention

- 0.65 μA Sleep current for RAM Retention Regulator mode and 5 μA for Regulator Standby mode

- On-Chip 1.8V Voltage Regulator (VREG)

- · On-Chip Ultra Low-Power Retention Regulator

#### **High-Performance 32-Bit RISC CPU**

- microAptiv™ UC 32-Bit Core with 5-Stage Pipeline

- microMIPS™ Instruction Set for 35% Smaller Code and 98% Performance compared to MIPS32 Instructions

- 1.53 DMIPS/MHz (37 DMIPS) (Dhrystone 2.1) Performance

- 3.17 CoreMark®/MHz (79 CoreMark) Performance

- 16-Bit/32-Bit Wide Instructions with 32-Bit Wide Data Path

- Two Sets of 32 Core Register Files (32-bit) to Reduce Interrupt Latency

- · Single-Cycle 32x16 Multiply and Two-Cycle 32x32 Multiply

- 64-Bit, Zero Wait State Flash with ECC to Maximize Endurance/Retention

#### **Microcontroller Features**

- · Up to 256K Flash Memory

- 20,000 Erase/Write Cycle Endurance

- 20 Years Minimum Data Retention

- Self-Programmable under Software Control

- · Up to 32K SRAM Memory

- Multiple Interrupt Vectors with Individually Programmable Priority

- · Fail-Safe Clock Monitor mode

- Configurable Watchdog Timer with On-Chip, Low-Power RC Oscillator

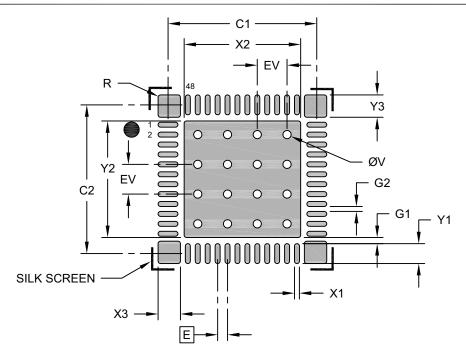

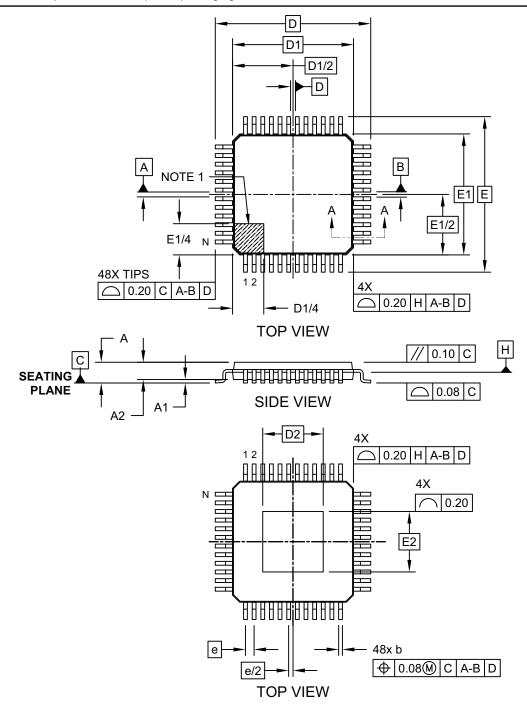

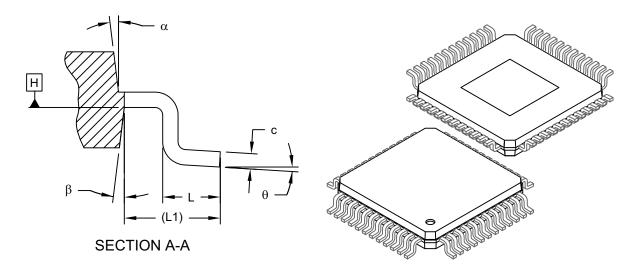

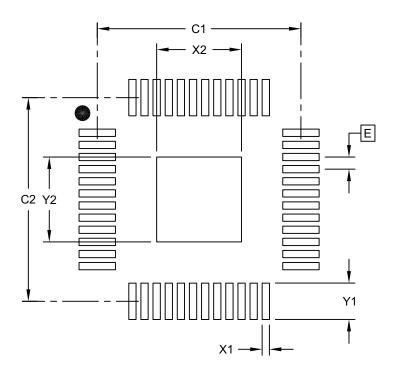

- Programmable Code Protection

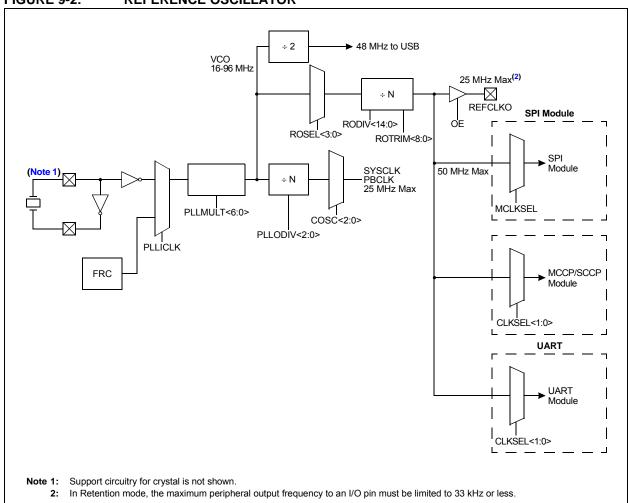

- · Selectable Oscillator Options Including:

- High-precision, 8 MHz (FRC) internal RC oscillator – 2x/3x/4x/6x/12x/24x PLL, which can be clocked from FRC or the Primary Oscillator

- Primary high-speed, crystal/resonator oscillator or external clock

#### **Peripheral Features**

- USB 2.0 Compliant Full-Speed and Low-Speed Device, Host and On-The-Go (OTG) Controller:

- Dedicated DMA

- Device mode operation from FRC oscillator; no crystal oscillator required

- Atomic Set, Clear and Invert Operation on Select Peripheral Registers

- · High-Current Sink/Source

- · Independent, Low-Power 32 kHz Timer Oscillator

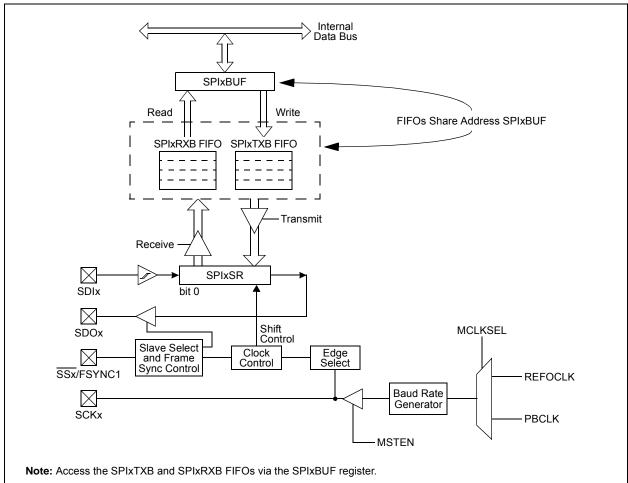

- · Three 4-Wire SPI modules:

- 16-byte FIFO

- Variable width

- I<sup>2</sup>S mode

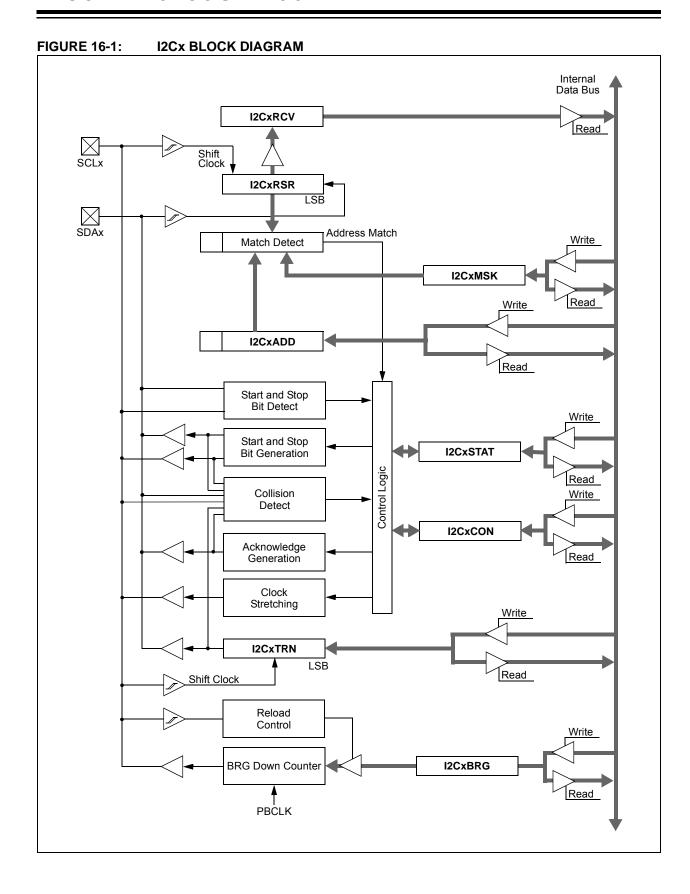

- Three I<sup>2</sup>C Master and Slave w/Address Masking and IPMI Support

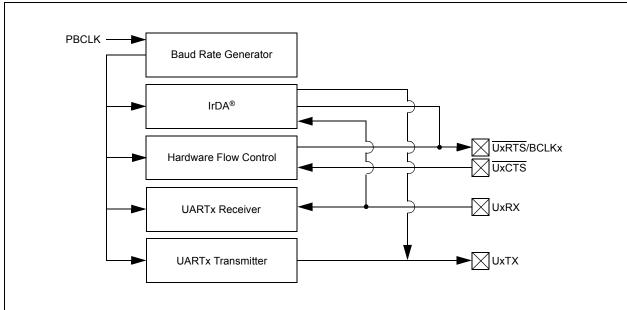

- · Three Enhanced Addressable UARTs:

- RS-232, RS-485 and LIN/J2602 support

- IrDA® with on-chip hardware encoder and decoder

- · External Edge and Level Change Interrupt on All Ports

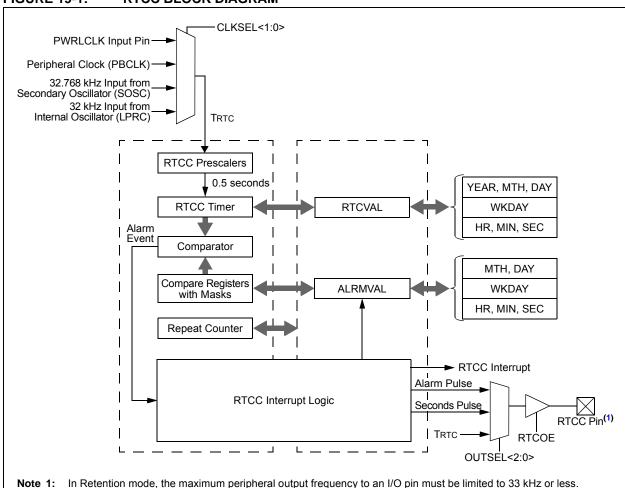

- Hardware Real-Time Clock and Calendar (RTCC)

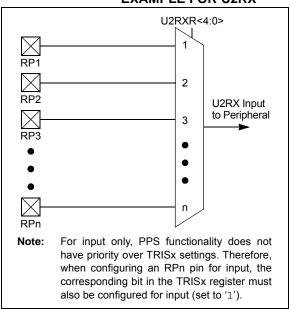

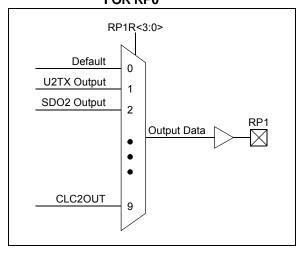

- Up to 24 Peripheral Pin Select (PPS) Remappable Pins

- 21 Total 16-Bit Timers:

- Three dedicated 16-bit timers/counters

- Two can be concatenated to form a 32-bit timer

- Two additional 16-bit timers in each MCCP and SCCP module, totaling 18

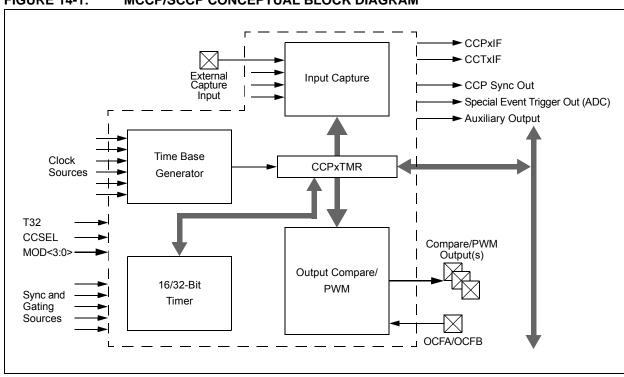

- · Capture/Compare/PWM/Timer modules:

- Two 16-bit timers or one 32-bit timer in each module

- PWM resolution down to 21 ns

- Three Multiple Output (MCCP) modules:

- Flexible configuration as PWM, input capture, output compare or timers

- Six PWM outputs

- Programmable dead time

- Auto-shutdown

- Six Single Output (SCCP) modules:

- Flexible configuration as PWM, input capture, output compare or timers

- Single PWM output

- Reference Clock Output (REFO)

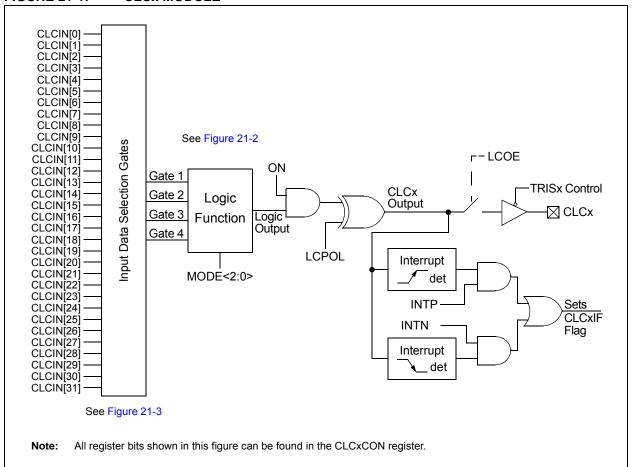

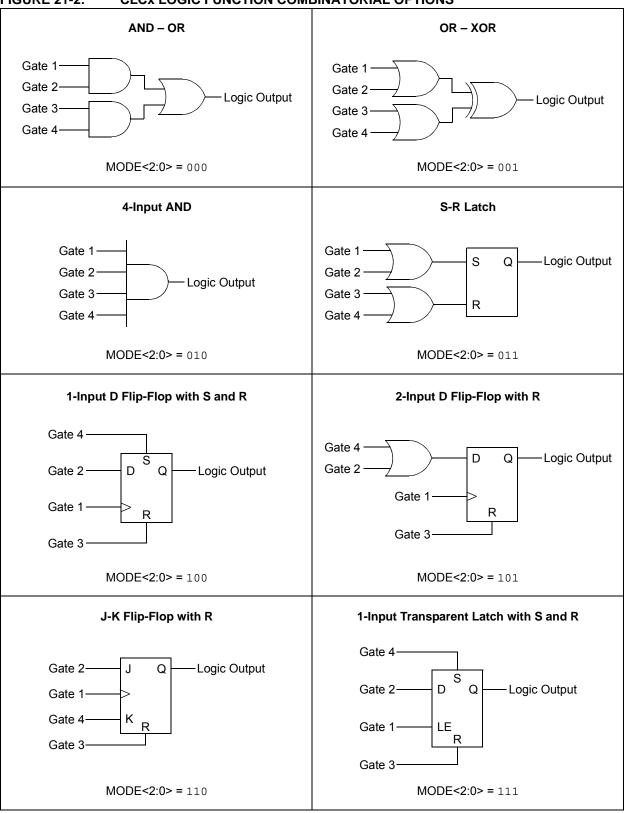

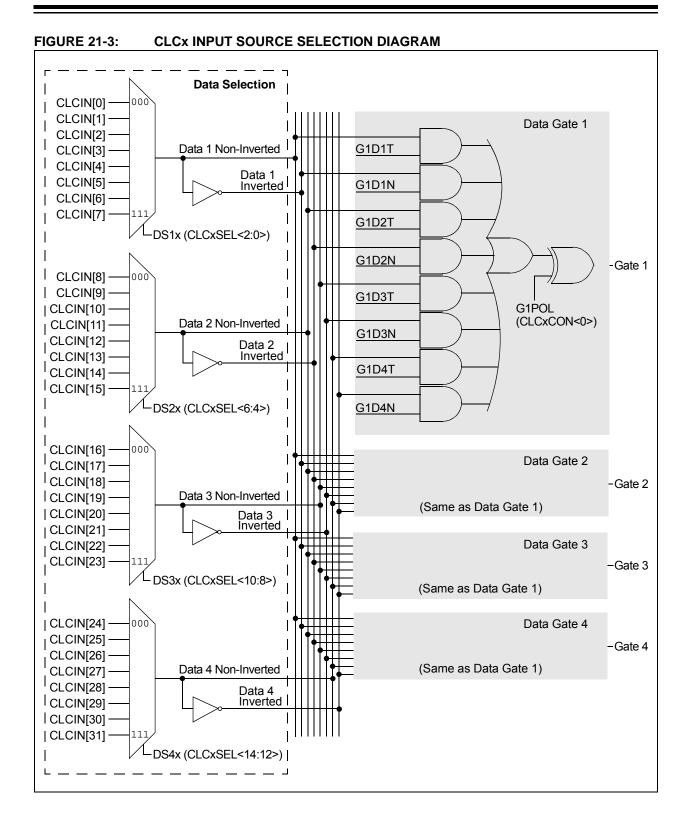

- Four Configurable Logic Cells (CLC) with Internal Connections to Select Peripherals and PPS

- 4-Channel Hardware DMA with Automatic Data Size Detection and CRC Engine

#### **Debug Features**

- · Two Programming and Debugging Interfaces:

- 2-wire ICSP™ interface with non-intrusive access and real-time data exchange with application

- 4-wire MIPS® standard Enhanced JTAG interface

- IEEE Standard 1149.2 Compatible (JTAG) Boundary Scan

#### **Analog Features**

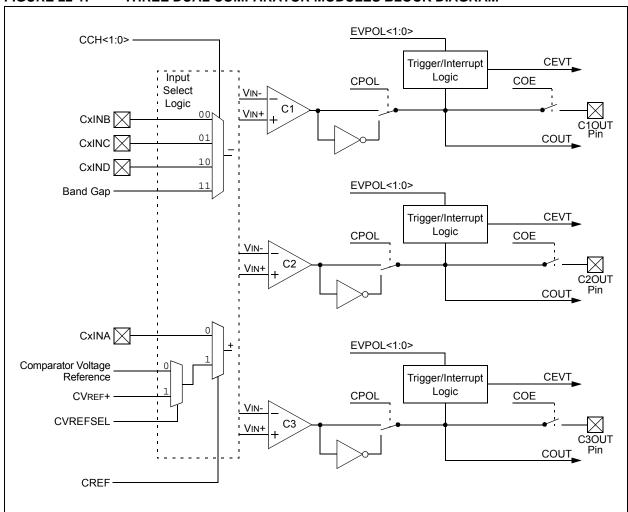

- Three Analog Comparators with Input Multiplexing

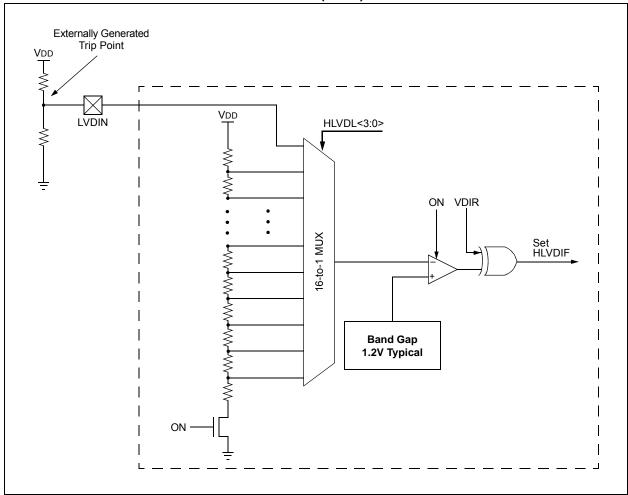

- Programmable High/Low-Voltage Detect (HLVD)

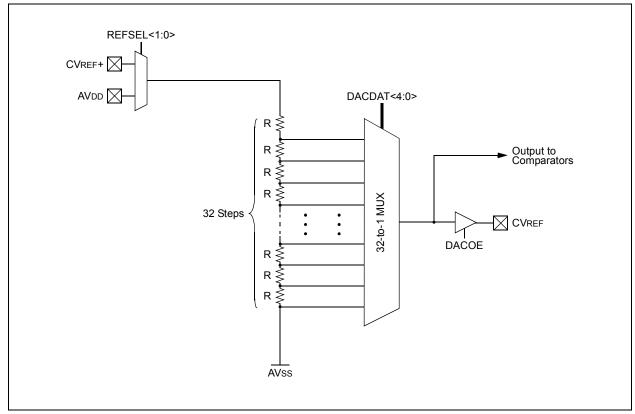

- 5-Bit Comparator Voltage Reference DAC with Pin Output

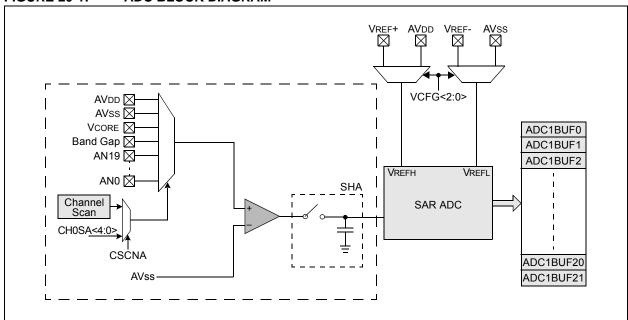

- Up to 24-Channel, Software-Selectable 10/12-Bit SAR Analog-to-Digital Converter (ADC):

- 12-bit 200K samples/second conversion rate (single Sample-and-Hold)

- 10-bit 300k samples/second conversion rate (single Sample-and-Hold)

- Sleep mode operation

- Low-voltage boost for input

- Band gap reference input feature

- Windowed threshold compare feature

- Auto-scan feature

- Brown-out Reset (BOR)

#### TABLE 1: PIC32MM0256GPM064 FAMILY DEVICES

|                   |       | (se                     |                      | Sc                      | r                     | <b>E</b>            |                         |                                |                     | ppab<br>hera        |     |                                      | Channels)                   |             |     |      |     |     |                   |

|-------------------|-------|-------------------------|----------------------|-------------------------|-----------------------|---------------------|-------------------------|--------------------------------|---------------------|---------------------|-----|--------------------------------------|-----------------------------|-------------|-----|------|-----|-----|-------------------|

| Device            | Pins  | Program Memory (Kbytes) | Data Memory (Kbytes) | General Purpose I/O/PPS | 16-Bit Timers Maximum | PWM Outputs Maximum | Dedicated 16-Bit Timers | UART <sup>(1)</sup> /LIN/J2602 | MCCP <sup>(4)</sup> | SCCP <sup>(3)</sup> | כרכ | SPI <sup>(2)</sup> /I <sup>2</sup> S | 10/12-Bit ADC (External Cha | Comparators | CRC | RTCC | ე₅I | USB | Packages          |

| PIC32MM0064GPM028 | 28    | 64                      | 16                   | 21/18                   | 21                    | 18                  | 3                       | 3                              | 3                   | 6                   | 4   | 3                                    | 12                          | 3           | Yes | Yes  | 3   | Yes | SSOP/QFN/<br>UQFN |

| PIC32MM0128GPM028 | 28    | 128                     | 16                   | 21/18                   | 21                    | 18                  | 3                       | 3                              | 3                   | 6                   | 4   | 3                                    | 12                          | 3           | Yes | Yes  | 3   | Yes | SSOP/QFN/<br>UQFN |

| PIC32MM0256GPM028 | 28    | 256                     | 32                   | 21/18                   | 21                    | 18                  | 3                       | 3                              | 3                   | 6                   | 4   | 3                                    | 12                          | 3           | Yes | Yes  | 3   | Yes | SSOP/QFN/<br>UQFN |

| PIC32MM0064GPM036 | 36/40 | 64                      | 16                   | 27/20                   | 21                    | 20                  | 3                       | 3                              | 3                   | 6                   | 4   | 3                                    | 15                          | 3           | Yes | Yes  | 3   | Yes | VQFN/UQFN         |

| PIC32MM0128GPM036 | 36/40 | 128                     | 16                   | 27/20                   | 21                    | 20                  | 3                       | 3                              | 3                   | 6                   | 4   | 3                                    | 15                          | 3           | Yes | Yes  | 3   | Yes | VQFN/UQFN         |

| PIC32MM0256GPM036 | 36/40 | 256                     | 32                   | 27/20                   | 21                    | 20                  | 3                       | 3                              | 3                   | 6                   | 4   | 3                                    | 15                          | 3           | Yes | Yes  | 3   | Yes | VQFN/UQFN         |

| PIC32MM0064GPM048 | 48    | 64                      | 16                   | 38/24                   | 21                    | 24                  | 3                       | 3                              | 3                   | 6                   | 4   | 3                                    | 17                          | 3           | Yes | Yes  | 3   | Yes | UQFN/TQFP         |

| PIC32MM0128GPM048 | 48    | 128                     | 16                   | 38/24                   | 21                    | 24                  | 3                       | 3                              | 3                   | 6                   | 4   | 3                                    | 17                          | 3           | Yes | Yes  | 3   | Yes | UQFN/TQFP         |

| PIC32MM0256GPM048 | 48    | 256                     | 32                   | 38/24                   | 21                    | 24                  | 3                       | 3                              | 3                   | 6                   | 4   | 3                                    | 17                          | 3           | Yes | Yes  | 3   | Yes | UQFN/TQFP         |

| PIC32MM0064GPM064 | 64    | 64                      | 16                   | 52/24                   | 21                    | 24                  | 3                       | 3                              | 3                   | 6                   | 4   | 3                                    | 20                          | 3           | Yes | Yes  | 3   | Yes | QFN/TQFP          |

| PIC32MM0128GPM064 | 64    | 128                     | 16                   | 52/24                   | 21                    | 24                  | 3                       | 3                              | 3                   | 6                   | 4   | 3                                    | 20                          | 3           | Yes | Yes  | 3   | Yes | QFN/TQFP          |

| PIC32MM0256GPM064 | 64    | 256                     | 32                   | 52/24                   | 21                    | 24                  | 3                       | 3                              | 3                   | 6                   | 4   | 3                                    | 20                          | 3           | Yes | Yes  | 3   | Yes | QFN/TQFP          |

- Note 1: UART1 has assigned pins. UART2 and UART3 are remappable.

- 2: SPI1 and SPI3 have assigned pins. SPI2 is remappable.

- 3: SCCP can be configured as a PWM with 1 output, input capture, output compare, 2 x 16-bit timers or 1 x 32-bit timer.

- **4:** MCCP can be configured as a PWM with up to 6 outputs, input capture, output compare, 2 x 16-bit timers or 1 x 32-bit timer.

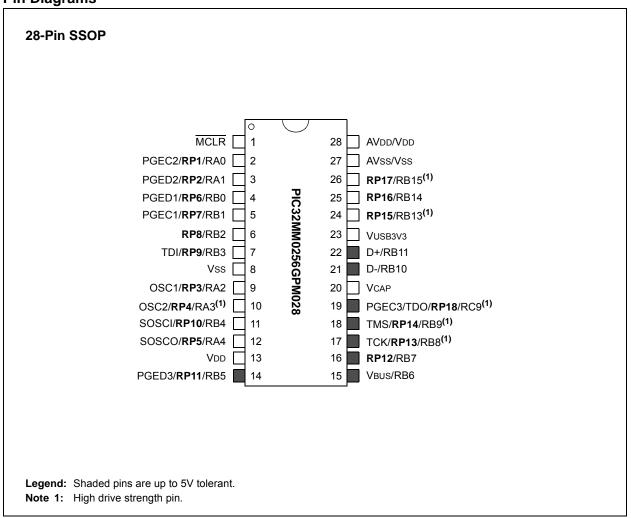

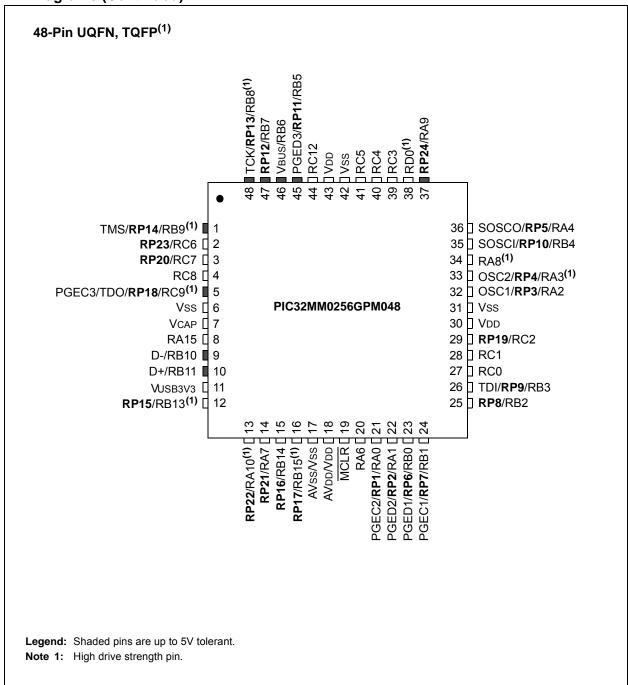

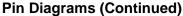

#### **Pin Diagrams**

TABLE 2: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 28-PIN SSOP DEVICES

| Pin | Function                                                                              | Pin | Function                                                                                                      |

|-----|---------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------|

| 1   | MCLR                                                                                  | 15  | VBUS/RB6                                                                                                      |

| 2   | PGEC2/VREF+/CVREF+/AN0/RP1/OCM1E/INT3/RA0                                             | 16  | RP12/SDA3/SDI3/OCM3F/RB7                                                                                      |

| 3   | PGED2/VREF-/AN1/ <b>RP2</b> /OCM1F/RA1                                                | 17  | TCK/RP13/SCL1/U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup>                                                             |

| 4   | PGED1/AN2/C1IND/C2INB/C3INC/RP6/OCM2C/RB0                                             | 18  | TMS/REFCLKI/ <b>RP14</b> /SDA1/T1CK/T1G/T2CK/T2G/ <del>U1RTS</del> /U1BCLK/SDO1/OCM1B/INT2/RB9 <sup>(1)</sup> |

| 5   | PGEC1/AN3/C1INC/C2INA/RP7/OCM2D/RB1                                                   | 19  | PGEC3/TDO/RP18/ASCL1 <sup>(2)</sup> /T3CK/T3G/USBOEN/SDO3/OCM2A/RC9 <sup>(1)</sup>                            |

| 6   | AN4/C1INB/RP8/SDA2/OCM2E/RB2                                                          | 20  | VCAP                                                                                                          |

| 7   | TDI/AN11/C1INA/RP9/SCL2/OCM2F/RB3                                                     | 21  | D-/RB10                                                                                                       |

| 8   | Vss                                                                                   | 22  | D+/RB11                                                                                                       |

| 9   | OSC1/CLKI/AN5/RP3/OCM1C/RA2                                                           | 23  | VUSB3V3                                                                                                       |

| 10  | OSC2/CLKO/AN6/C3IND/RP4/OCM1D/RA3 <sup>(1)</sup>                                      | 24  | AN8/LVDIN/RP15/SCL3/SCK3/OCM3A/RB13 <sup>(1)</sup>                                                            |

| 11  | SOSCI/AN7/RP10/OCM3C/RB4                                                              | 25  | CVREF/AN9/C3INB/RP16/RTCC/U1TX/VBUSON/SDI1/OCM3B/INT1/RB14                                                    |

| 12  | SOSCO/SCLKI/RP5/PWRLCLK/OCM3D/RA4                                                     | 26  | AN10/C3INA/REFCLKO/RP17/U1RX/SS1/FSYNC1/OCM2B/INT0/RB15 <sup>(1)</sup>                                        |

| 13  | VDD                                                                                   | 27  | AVss/Vss                                                                                                      |

| 14  | PGED3/ <b>RP11</b> /ASDA1 <sup>(2)</sup> /USBID/ <del>SS3</del> /FSYNC3/<br>OCM3E/RB5 | 28  | AVDD/VDD                                                                                                      |

Note 1: High drive strength pin.

2: Alternate pin assignments for I2C1 as determined by the I2C1SEL Configuration bit.

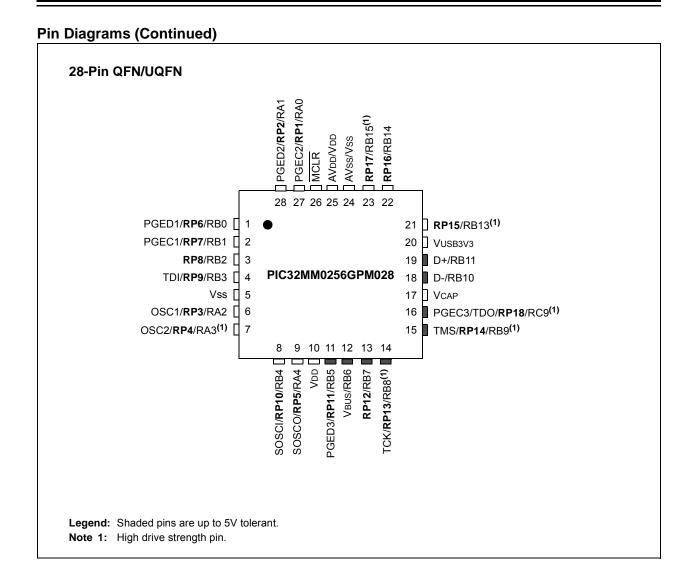

TABLE 3: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 28-PIN QFN/UQFN DEVICES

| Pin | Function                                                                          | Pin | Function                                                                                                      |

|-----|-----------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------|

| 1   | PGED1/AN2/C1IND/C2INB/C3INC/RP6/OCM2C/RB0                                         | 15  | TMS/REFCLKI/ <b>RP14</b> /SDA1/T1CK/T1G/T2CK/T2G/ <del>U1RTS</del> /U1BCLK/SDO1/OCM1B/INT2/RB9 <sup>(1)</sup> |

| 2   | PGEC1/AN3/C1INC/C2INA/RP7/OCM2D/RB1                                               | 16  | PGEC3/TDO/RP18/ASCL1 <sup>(2)</sup> /T3CK/T3G/USBOEN/SDO3/OCM2A/RC9 <sup>(1)</sup>                            |

| 3   | AN4/C1INB/RP8/SDA2/OCM2E/RB2                                                      | 17  | VCAP                                                                                                          |

| 4   | TDI/AN11/C1INA/ <b>RP9</b> /SCL2/OCM2F/RB3                                        | 18  | D-/RB10                                                                                                       |

| 5   | Vss                                                                               | 19  | D+/RB11                                                                                                       |

| 6   | OSC1/CLKI/AN5/RP3/OCM1C/RA2                                                       | 20  | Vusb3v3                                                                                                       |

| 7   | OSC2/CLKO/AN6/C3IND/RP4/OCM1D/RA3 <sup>(1)</sup>                                  | 21  | AN8/LVDIN/ <b>RP15</b> /SCL3/SCK3/OCM3A/RB13 <sup>(1)</sup>                                                   |

| 8   | SOSCI/AN7/RP10/OCM3C/RB4                                                          | 22  | CVREF/AN9/C3INB/RP16/RTCC/U1TX/VBUSON/SDI1/OCM3B/INT1/RB14                                                    |

| 9   | SOSCO/SCLKI/RP5/PWRLCLK/OCM3D/RA4                                                 | 23  | AN10/C3INA/REFCLKO/RP17/U1RX/SS1/FSYNC1/OCM2B/INT0/RB15 <sup>(1)</sup>                                        |

| 10  | VDD                                                                               | 24  | AVss/Vss                                                                                                      |

| 11  | PGED3/ <b>RP11</b> /ASDA1 <sup>(2)</sup> /USBID/ <del>SS3</del> /FSYNC3/OCM3E/RB5 | 25  | AVDD/VDD                                                                                                      |

| 12  | VBus/RB6                                                                          | 26  | MCLR                                                                                                          |

| 13  | RP12/SDA3/SDI3/OCM3F/RB7                                                          | 27  | PGEC2/VREF+/CVREF+/AN0/RP1/OCM1E/INT3/RA0                                                                     |

| 14  | TCK/RP13/SCL1/U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup>                                 | 28  | PGED2/VREF-/AN1/RP2/OCM1F/RA1                                                                                 |

Note 1: High drive strength pin.

<sup>2:</sup> Alternate pin assignments for I2C1 as determined by the I2C1SEL Configuration bit.

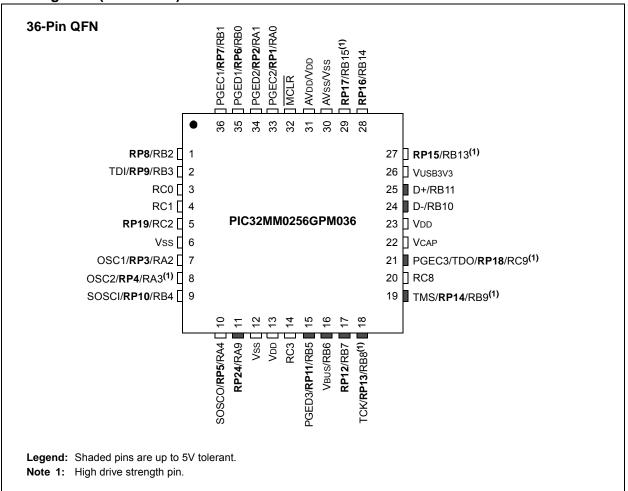

#### Pin Diagrams (Continued)

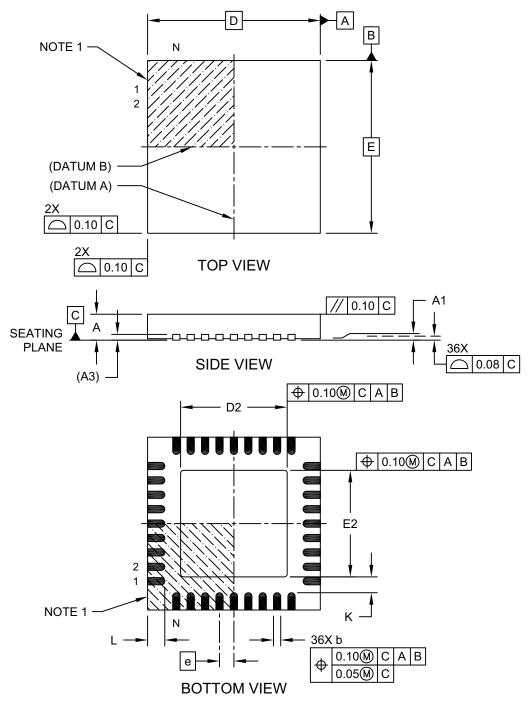

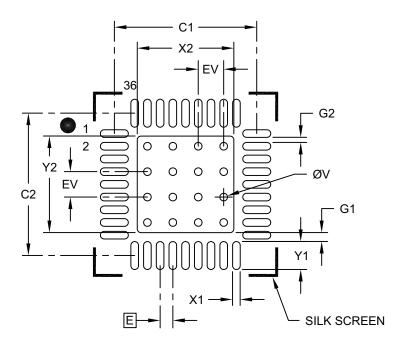

TABLE 4: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 36-PIN QFN DEVICES

| Pin | Function                                          | Pin | Function                                                                       |

|-----|---------------------------------------------------|-----|--------------------------------------------------------------------------------|

| 1   | AN4/C1INB/RP8/SDA2/OCM2E/RB2                      | 19  | TMS/REFCLKI/RP14/SDA1/T1CK/T1G/U1RTS/U1BCLK/SDO1/OCM1B/INT2/RB9 <sup>(1)</sup> |

| 2   | TDI/AN11/C1INA/RP9/SCL2/OCM2F/RB3                 | 20  | AN14/LVDIN/C2INC/RC8                                                           |

| 3   | AN12/C2IND/T2CK/T2G/RC0                           | 21  | PGEC3/TDO/RP18/ASCL1 <sup>(2)</sup> /USBOEN/SDO3/RC9 <sup>(1)</sup>            |

| 4   | AN13/T3CK/T3G/RC1                                 | 22  | VCAP                                                                           |

| 5   | RP19/OCM2A/RC2                                    | 23  | VDD                                                                            |

| 6   | Vss                                               | 24  | D-/RB10                                                                        |

| 7   | OSC1/CLKI/AN5/RP3/OCM1C/RA2                       | 25  | D+/RB11                                                                        |

| 8   | OSC2/CLKO/AN6/C3IND/RP4/OCM1D/RA3 <sup>(1)</sup>  | 26  | Vusb3v3                                                                        |

| 9   | SOSCI/AN7/RP10/OCM3C/RB4                          | 27  | AN8/ <b>RP15</b> /SCL3/SCK3/RB13 <sup>(1)</sup>                                |

| 10  | SOSCO/SCLKI/RP5/PWRLCLK/OCM3D/RA4                 | 28  | CVREF/AN9/C3INB/RP16/RTCC/U1TX/VBUSON/SDI1/OCM3B/INT1/RB14                     |

| 11  | RP24/OCM3A/RA9                                    | 29  | AN10/C3INA/REFCLKO/RP17/U1RX/SS1/FSYNC1/OCM2B/INT0/RB15 <sup>(1)</sup>         |

| 12  | Vss                                               | 30  | AVss/Vss                                                                       |

| 13  | VDD                                               | 31  | AVDD/VDD                                                                       |

| 14  | RC3                                               | 32  | MCLR                                                                           |

| 15  | PGED3/RP11/ASDA1(2)/USBID/SS3/FSYNC3/OCM3E/RB5    | 33  | PGEC2/VREF+/CVREF+/AN0/RP1/OCM1E/INT3/RA0                                      |

| 16  | VBus/RB6                                          | 34  | PGED2/VREF-/AN1/RP2/OCM1F/RA1                                                  |

| 17  | RP12/SDA3/SDI3/OCM3F/RB7                          | 35  | PGED1/AN2/C1IND/C2INB/C3INC/RP6/OCM2C/RB0                                      |

| 18  | TCK/RP13/SCL1/U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup> | 36  | PGEC1/AN3/C1INC/C2INA/RP7/OCM2D/RB1                                            |

Note 1: High drive strength pin.

2: Alternate pin assignments for I2C1 as determined by the I2C1SEL Configuration bit.

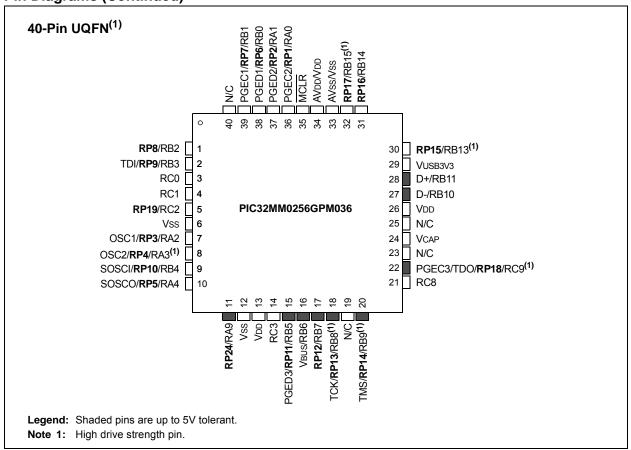

#### Pin Diagrams (Continued)

TABLE 5: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 40-PIN UQFN DEVICES

| Pin | Function                                                                                                 | Pin | Function                                                               |

|-----|----------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------|

| 1   | AN4/C1INB/RP8/SDA2/OCM2E/RB2                                                                             | 21  | AN14/LVDIN/C2INC/RC8                                                   |

| 2   | TDI/AN11/C1INA/RP9/SCL2/OCM2F/RB3                                                                        | 22  | PGEC3/TDO/RP18/ASCL1 <sup>(2)</sup> /SDO3/USBOEN/RC9 <sup>(1)</sup>    |

| 3   | AN12/C2IND/T2CK/T2G/RC0                                                                                  | 23  | N/C                                                                    |

| 4   | AN13/T3CK/T3G/RC1                                                                                        | 24  | VCAP                                                                   |

| 5   | RP19/OCM2A/RC2                                                                                           | 25  | N/C                                                                    |

| 6   | Vss                                                                                                      | 26  | VDD                                                                    |

| 7   | OSC1/CLKI/AN5/RP3/OCM1C/RA2                                                                              | 27  | D-/RB10                                                                |

| 8   | OSC2/CLKO/AN6/C3IND/RP4/OCM1D/RA3 <sup>(1)</sup>                                                         | 28  | D+/RB11                                                                |

| 9   | SOSCI/AN7/RP10/OCM3C/RB4                                                                                 | 29  | Vusb3v3                                                                |

| 10  | SOSCO/SCLKI/RP5/PWRLCLK/OCM3D/RA4                                                                        | 30  | AN8/ <b>RP15</b> /SCL3/SCK3/RB13 <sup>(1)</sup>                        |

| 11  | RP24/OCM3A/RA9                                                                                           | 31  | CVREF/AN9/C3INB/RP16/RTCC/U1TX/VBUSON/SDI1/OCM3B/INT1/RB14             |

| 12  | Vss                                                                                                      | 32  | AN10/C3INA/REFCLKO/RP17/U1RX/SS1/FSYNC1/OCM2B/INT0/RB15 <sup>(1)</sup> |

| 13  | VDD                                                                                                      | 33  | AVss/Vss                                                               |

| 14  | RC3                                                                                                      | 34  | AVDD/VDD                                                               |

| 15  | PGED3/RP11/ASDA1(2)/USBID/SS3/FSYNC3/OCM3E/RB5                                                           | 35  | MCLR                                                                   |

| 16  | VBUS/RB6                                                                                                 | 36  | PGEC2/VREF+/CVREF+/AN0/RP1/OCM1E/INT3/RA0                              |

| 17  | RP12/SDA3/SDI3/OCM3F/RB7                                                                                 | 37  | PGED2/VREF-/AN1/RP2/OCM1F/RA1                                          |

| 18  | TCK/RP13/SCL1/U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup>                                                        | 38  | PGED1/AN2/C1IND/C2INB/C3INC/RP6/OCM2C/RB0                              |

| 19  | N/C                                                                                                      | 39  | PGEC1/AN3/C1INC/C2INA/RP7/OCM2D/RB1                                    |

| 20  | TMS/REFCLKI/ <b>RP14</b> /SDA1/T1CK/T1G/ <del>U1RTS</del> /U1BCLK/<br>SDO1/OCM1B/INT2/RB9 <sup>(1)</sup> | 40  | N/C                                                                    |

Note 1: High drive strength pin.

2: Alternate pin assignments for I2C1 as determined by the I2C1SEL Configuration bit.

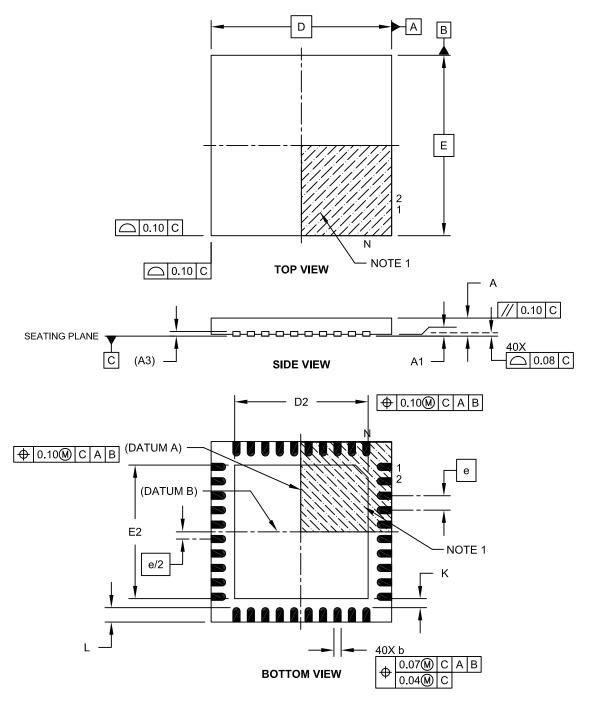

#### **Pin Diagrams (Continued)**

#### **TABLE 6:** COMPLETE PIN FUNCTION DESCRIPTIONS FOR 48-PIN UQFN/TQFP DEVICES

| Pin | Function                                                    | Pin | Function                                          |

|-----|-------------------------------------------------------------|-----|---------------------------------------------------|

| 1   | TMS/RP14/SDA1/OCM1B/INT2/RB9 <sup>(1)</sup>                 | 25  | AN4/C1INB/RP8/SDA2/OCM2E/RB2                      |

| 2   | RP23/RC6                                                    | 26  | TDI/AN11/C1INA/RP9/SCL2/OCM2F/RB3                 |

| 3   | RP20/RC7                                                    | 27  | AN12/C2IND/T2CK/T2G/RC0                           |

| 4   | AN14/LVDIN/C2INC/RC8                                        | 28  | AN13/T3CK/T3G/RC1                                 |

| 5   | PGEC3/TDO/RP18/ASCL1(2)/USBOEN/RC9(1)                       | 29  | RP19/OCM2A/RC2                                    |

| 6   | Vss                                                         | 30  | VDD                                               |

| 7   | VCAP                                                        | 31  | Vss                                               |

| 8   | RTCC/RA15                                                   | 32  | OSC1/CLKI/AN5/RP3/OCM1C/RA2                       |

| 9   | D-/RB10                                                     | 33  | OSC2/CLKO/AN6/C3IND/RP4/RA3 <sup>(1)</sup>        |

| 10  | D+/RB11                                                     | 34  | SD03/RA8 <sup>(1)</sup>                           |

| 11  | Vusb3v3                                                     | 35  | SOSCI/AN7/RP10/OCM3C/RB4                          |

| 12  | AN8/ <b>RP15</b> /SCL3/RB13 <sup>(1)</sup>                  | 36  | SOSCO/SCLKI/RP5/PWRLCLK/OCM3D/RA4                 |

| 13  | RP22/SCK3/RA10 <sup>(1)</sup>                               | 37  | RP24/OCM3A/RA9                                    |

| 14  | RP21/SDI3/RA7                                               | 38  | REFCLKI/T1CK/T1G/U1RTS/U1BCLK/SDO1/RD0(1)         |

| 15  | CVREF/AN9/C3INB/RP16/VBUSON/SDI1/OCM3B/INT1/RB14            | 39  | OCM2B/RC3                                         |

| 16  | AN10/C3INA/REFCLKO/RP17/SS1/FSYNC1/INT0/RB15 <sup>(1)</sup> | 40  | OCM1E/INT3/RC4                                    |

| 17  | AVss/Vss                                                    | 41  | AN15/OCM1D/RC5                                    |

| 18  | AVDD/VDD                                                    | 42  | Vss                                               |

| 19  | MCLR                                                        | 43  | VDD                                               |

| 20  | AN19/U1RX/RA6                                               | 44  | U1TX/RC12                                         |

| 21  | PGEC2/VREF+/CVREF+/AN0/RP1/RA0                              | 45  | PGED3/RP11/ASDA1(2)/USBID/SS3/FSYNC3/OCM3E/RB5    |

| 22  | PGED2/VREF-/AN1/ <b>RP2</b> /OCM1F/RA1                      | 46  | VBUS/RB6                                          |

| 23  | PGED1/AN2/C1IND/C2INB/C3INC/RP6/OCM2C/RB0                   | 47  | RP12/SDA3/OCM3F/RB7                               |

| 24  | PGEC1/AN3/C1INC/C2INA/ <b>RP7</b> /OCM2D/RB1                | 48  | TCK/RP13/SCL1/U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup> |

Note 1: High drive strength pin.

2: Alternate pin assignments for I2C1 as determined by the I2C1SEL Configuration bit.

#### TABLE 7: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 64-PIN QFN/TQFP DEVICES

| Pin | Function                                            | Pin | Function                                                       |

|-----|-----------------------------------------------------|-----|----------------------------------------------------------------|

| 1   | RP21/SDI3/RA7                                       | 33  | OCM3B/RD3                                                      |

| 2   | CVREF/AN9/C3INB/RP16/VBUSON/RB14                    | 34  | REFCLKI/T1CK/T1G/U1RTS/U1BCLK/SDO1/RD0(1)                      |

| 3   | AN10/C3INA/REFCLKO/RP17/RB15 <sup>(1)</sup>         | 35  | OCM2B/RC3                                                      |

| 4   | AVss                                                | 36  | OCM1E/INT3/RC4                                                 |

| 5   | AVDD                                                | 37  | AN15/OCM1D/RC5                                                 |

| 6   | AN16/U1CTS/RA13                                     | 38  | Vss                                                            |

| 7   | AN17/OCM1A/RA12                                     | 39  | VDD                                                            |

| 8   | AN18/RA11                                           | 40  | U1TX/RC12                                                      |

| 9   | MCLR                                                | 41  | OCM3D/RC14                                                     |

| 10  | AN19/U1RX/RA6                                       | 42  | OCM3E/RC15                                                     |

| 11  | PGEC2/VREF+/CVREF+/AN0/RP1/RA0                      | 43  | PGED3/RP11/ASDA1 <sup>(2)</sup> /USBID/RB5                     |

| 12  | PGED2/VREF-/AN1/RP2/OCM1F/RA1                       | 44  | VBus/RB6                                                       |

| 13  | PGED1/AN2/C1IND/C2INB/C3INC/RP6/OCM2C/RB0           | 45  | OCM3F/RC10                                                     |

| 14  | PGEC1/AN3/C1INC/C2INA/RP7/OCM2D/RB1                 | 46  | RP12/SDA3/RB7                                                  |

| 15  | AN4/C1INB/RP8/SDA2/OCM2E/RB2                        | 47  | SCK1/RC13 <sup>(1)</sup>                                       |

| 16  | TDI/AN11/C1INA/ <b>RP9</b> /SCL2/OCM2F/RB3          | 48  | TCK/RP13/SCL1/RB8 <sup>(1)</sup>                               |

| 17  | VDD                                                 | 49  | TMS/RP14/SDA1/INT2/RB9 <sup>(1)</sup>                          |

| 18  | Vss                                                 | 50  | RP23/RC6                                                       |

| 19  | AN12/C2IND/T2CK/T2G/RC0                             | 51  | <b>RP20</b> /RC7                                               |

| 20  | AN13/T3CK/T3G/RC1                                   | 52  | AN14/LVDIN/C2INC/RC8                                           |

| 21  | RP19/OCM2A/RC2                                      | 53  | OCM1B/RD1                                                      |

| 22  | SS3/FSYNC3/RC11                                     | 54  | OCM3A/RA5                                                      |

| 23  | VDD                                                 | 55  | PGEC3/TDO/RP18/ASCL1 <sup>(2)</sup> /USBOEN/RC9 <sup>(1)</sup> |

| 24  | Vss                                                 | 56  | VCAP                                                           |

| 25  | OSC1/CLKI/AN5/RP3/OCM1C/RA2                         | 57  | VDD                                                            |

| 26  | OSC2/CLKO/AN6/C3IND/ <b>RP4</b> /RA3 <sup>(1)</sup> | 58  | RTCC/RA15                                                      |

| 27  | SD03/RA8 <sup>(1)</sup>                             | 59  | OCM3C/RA14                                                     |

| 28  | SOSCI/AN7/RP10/RB4                                  | 60  | D-/RB10                                                        |

| 29  | SOSCO/SCLKI/RP5/PWRLCLK/RA4                         | 61  | D+/RB11                                                        |

| 30  | RP24/RA9                                            | _   | Vusb3v3                                                        |

| 31  | SDI1/INT1/RD4                                       | 63  | AN8/ <b>RP15</b> /SCL3/RB13 <sup>(1)</sup>                     |

| 32  | SS1/FSYNC1/INT0/RD2                                 | 64  | RP22/SCK3/RA10 <sup>(1)</sup>                                  |

Note 1: High drive strength pin.

2: Alternate pin assignments for I2C1 as determined by the I2C1SEL Configuration bit.

#### **Table of Contents**

| 1.0   | Device Overview                                                         | 15  |

|-------|-------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 32-Bit Microcontrollers             | 23  |

| 3.0   | CPU                                                                     | 29  |

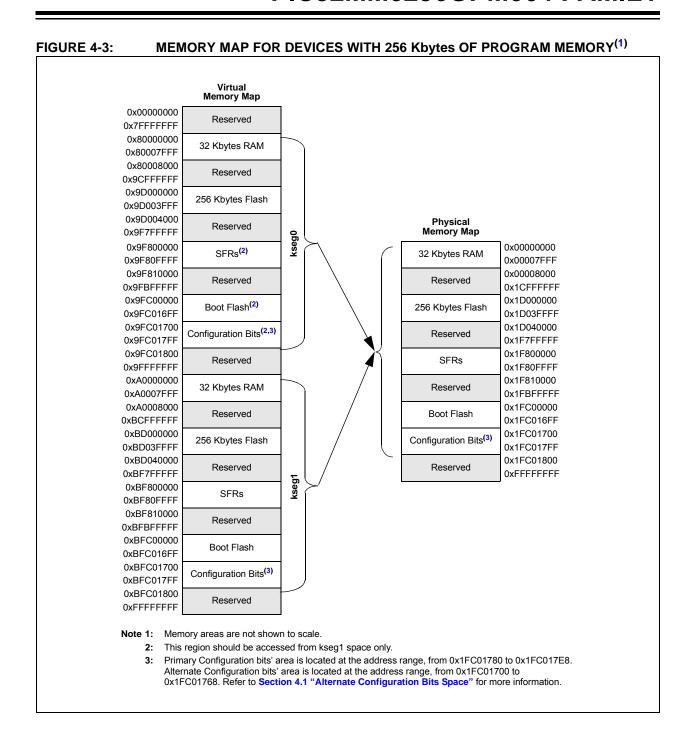

| 4.0   | Memory Organization                                                     | 39  |

| 5.0   | Flash Program Memory                                                    | 45  |

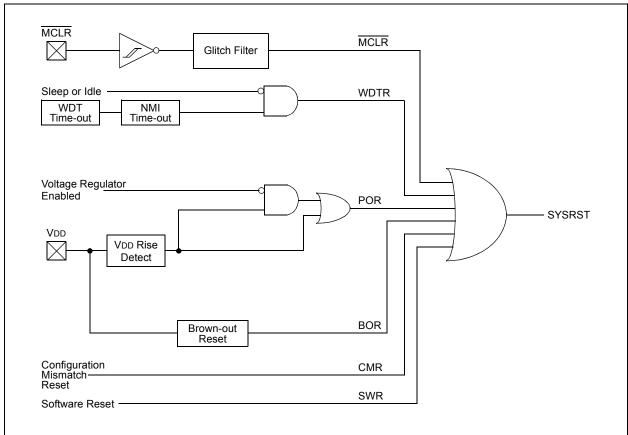

| 6.0   | Resets                                                                  | 53  |

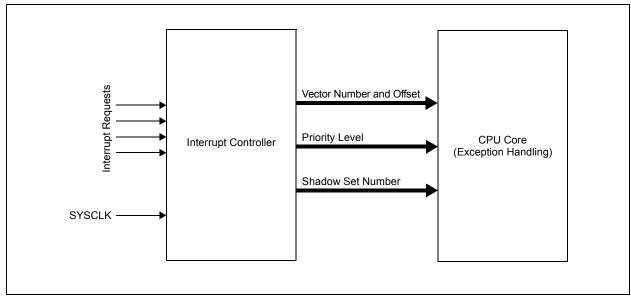

| 7.0   | CPU Exceptions and Interrupt Controller                                 | 59  |

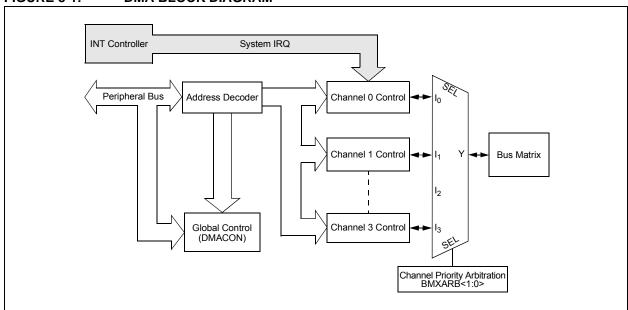

| 8.0   | Direct Memory Access (DMA) Controller                                   | 77  |

| 9.0   | Oscillator Configuration                                                | 97  |

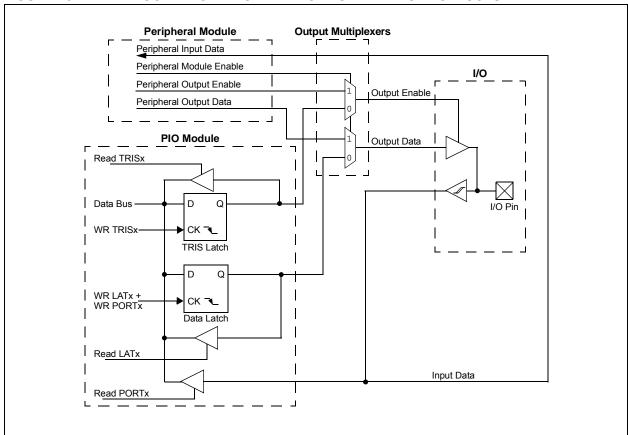

| 10.0  | I/O Ports                                                               | 113 |

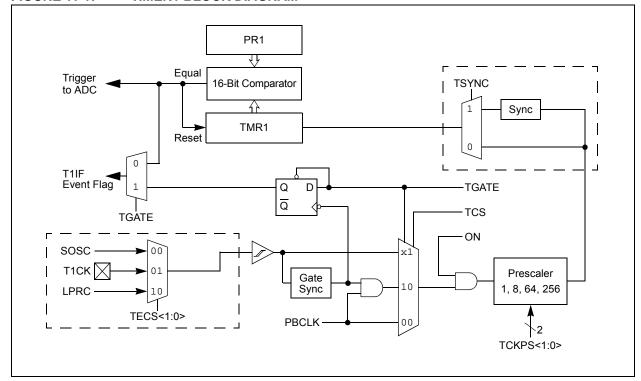

| 11.0  | Timer1                                                                  | 127 |

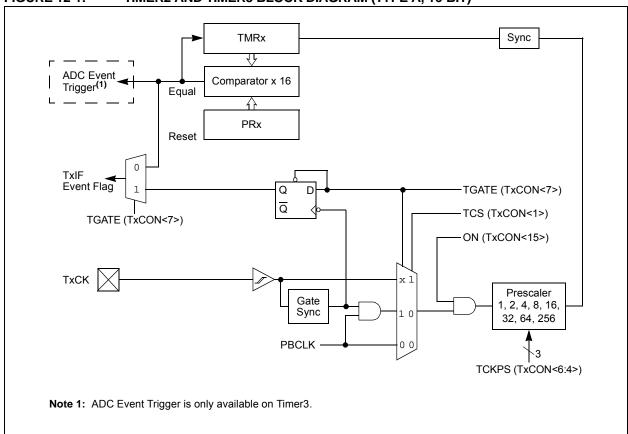

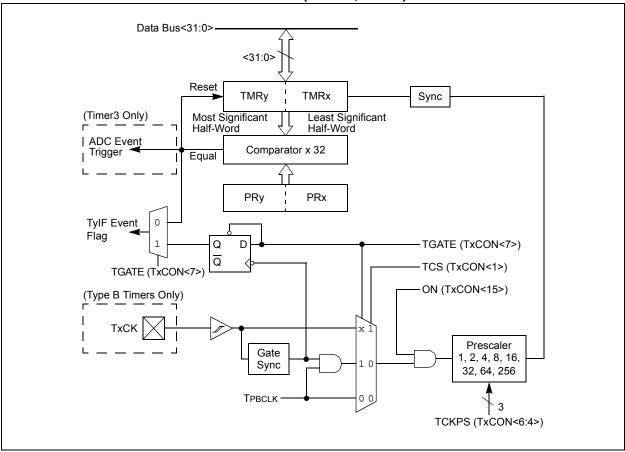

| 12.0  | Timer2 and Timer3                                                       | 131 |

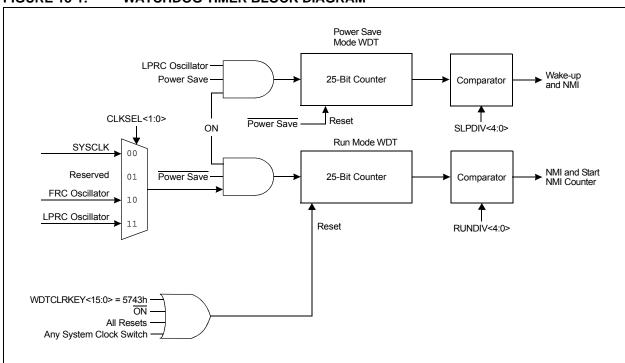

| 13.0  | Watchdog Timer (WDT)                                                    | 137 |

| 14.0  | Capture/Compare/PWM/Timer Modules (MCCP and SCCP)                       | 141 |

| 15.0  | Serial Peripheral Interface (SPI) and Inter-IC Sound (I <sup>2</sup> S) | 159 |

| 16.0  | Inter-Integrated Circuit (I <sup>2</sup> C)                             | 167 |

|       | Universal Asynchronous Receiver Transmitter (UART)                      |     |

| 18.0  | USB On-The-Go (OTG)                                                     | 181 |

| 19.0  | Real-Time Clock and Calendar (RTCC)                                     | 209 |

| 20.0  | 12-Bit ADC Converter with Threshold Detect                              | 217 |

| 21.0  | Configurable Logic Cell (CLC)                                           | 229 |

| 22.0  | Comparator                                                              | 243 |

| 23.0  | Voltage Reference (CVREF)                                               | 249 |

| 24.0  | High/Low-Voltage Detect (HLVD)                                          | 253 |

| 25.0  | Power-Saving Features                                                   | 257 |

| 26.0  | Special Features                                                        | 263 |

| 27.0  | Instruction Set                                                         | 281 |

| 28.0  | Development Support                                                     | 283 |

| 29.0  | Electrical Characteristics                                              | 287 |

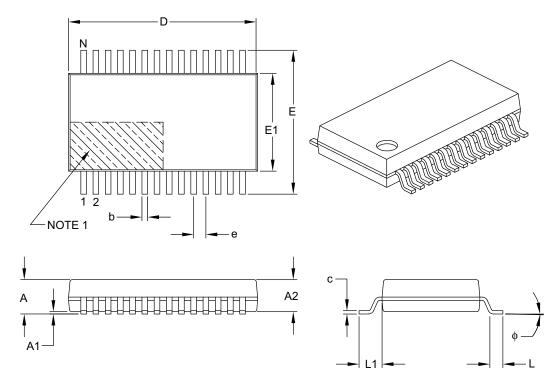

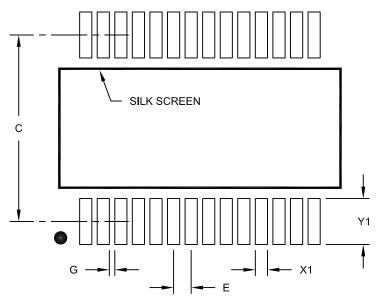

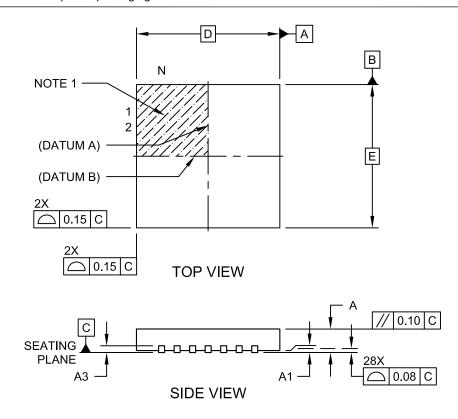

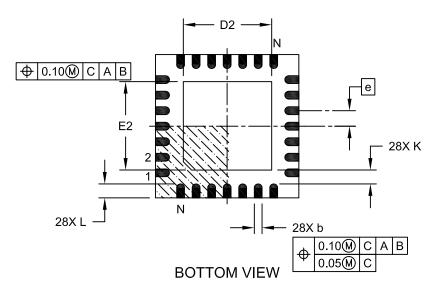

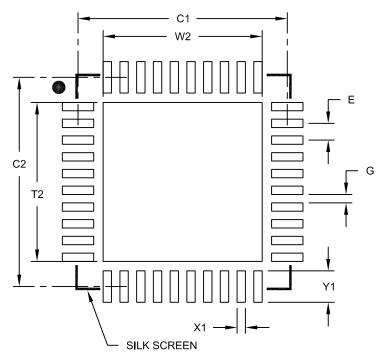

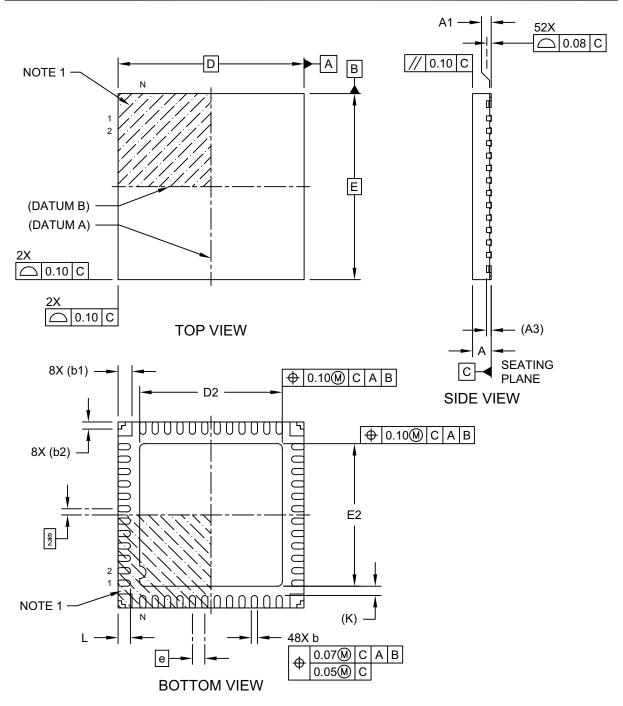

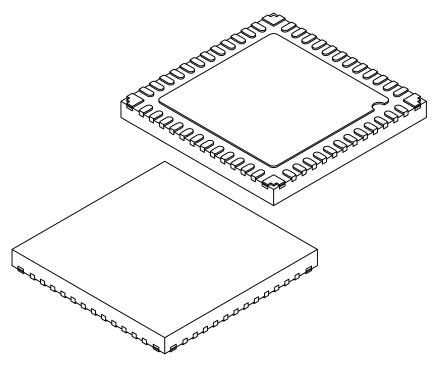

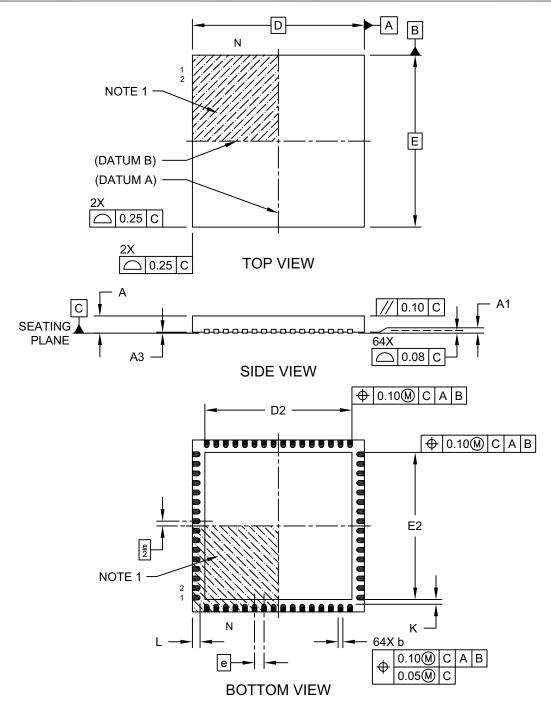

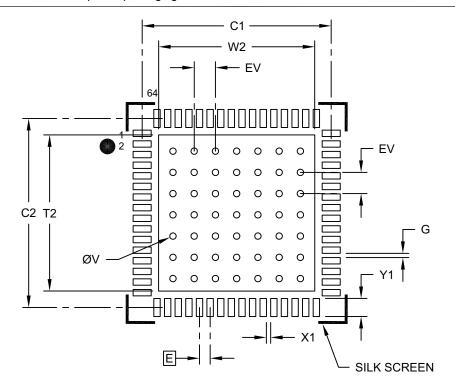

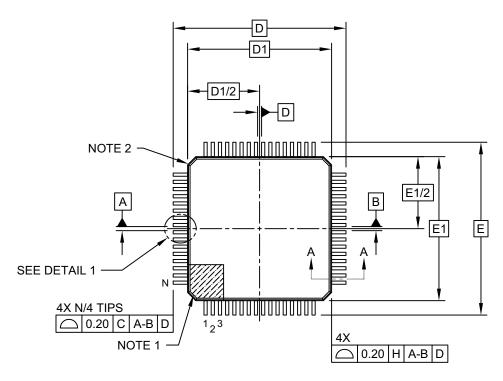

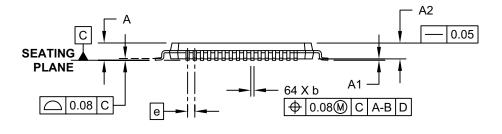

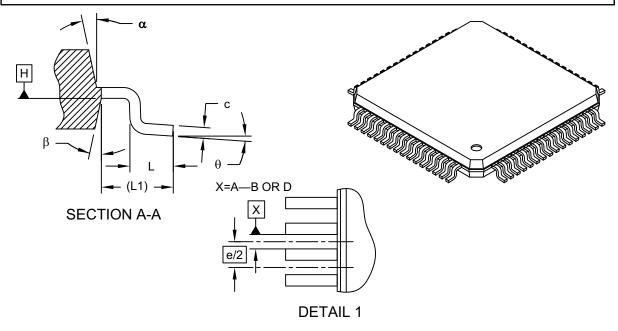

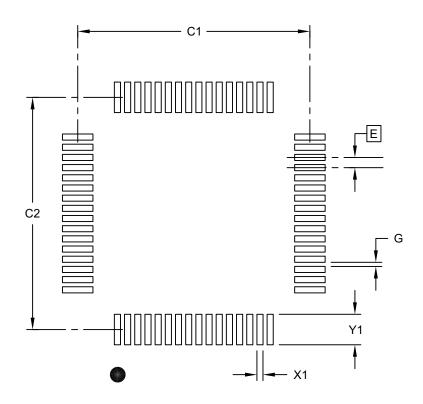

| 30.0  | Packaging Information                                                   | 319 |

| Appe  | endix A: Revision History                                               | 347 |

| Index | x                                                                       | 349 |

| The I | Microchip Web Site                                                      | 353 |

| Custo | omer Change Notification Service                                        | 353 |

| Custo | omer Support                                                            | 353 |

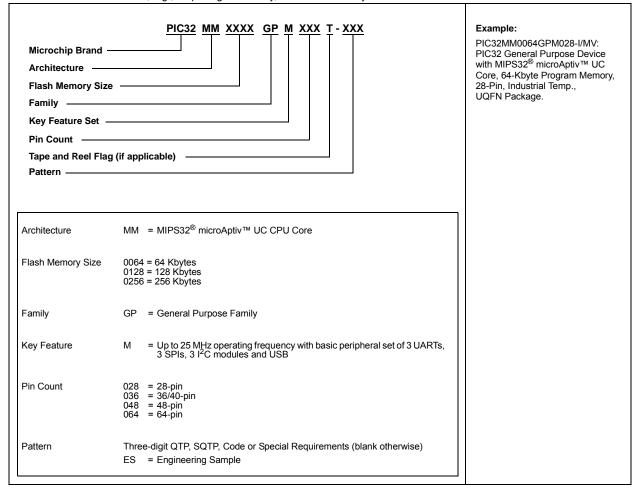

| Prod  | luct Identification System                                              | 355 |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### **Referenced Sources**

This device data sheet is based on the following individual sections of the "PIC32 Family Reference Manual". These documents should be considered as the general reference for the operation of a particular module or device feature.

**Note:** To access the documents listed below, browse the documentation section of the Microchip web site (www.microchip.com).

- Section 1. "Introduction" (DS60001127)

- Section 5. "Flash Programming" (DS60001121)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupts" (DS61108)

- Section 10. "Power-Saving Modes" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 14. "Timers" (DS60001105)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference" (DS61109)

- Section 21. "UART" (DS61107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS61106)

- Section 24. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS61116)

- · Section 25. "12-Bit Analog-to-Digital Converter (ADC) with Threshold Detect" (DS60001359)

- Section 27. "USB On-The-Go (OTG)" (DS61126)

- Section 28. "RTCC with Timestamp" (DS60001362)

- Section 30. "Capture/Compare/PWM/Timer (MCCP and SCCP)" (DS60001381)

- Section 31. "DMA Controller" (DS60001117)

- Section 33. "Programming and Diagnostics" (DS61129)

- Section 36. "Configurable Logic Cell" (DS60001363)

- Section 48. "Memory Organization and Permissions" (DS60001214)

- Section 50. "CPU for Devices with MIPS32® microAptiv™ and M-Class Cores" (DS60001192)

- Section 59. "Oscillators with DCO" (DS60001329)

- Section 62. "Dual Watchdog Timer" (DS60001365)

| NOTES: |  |  |  |

|--------|--|--|--|

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

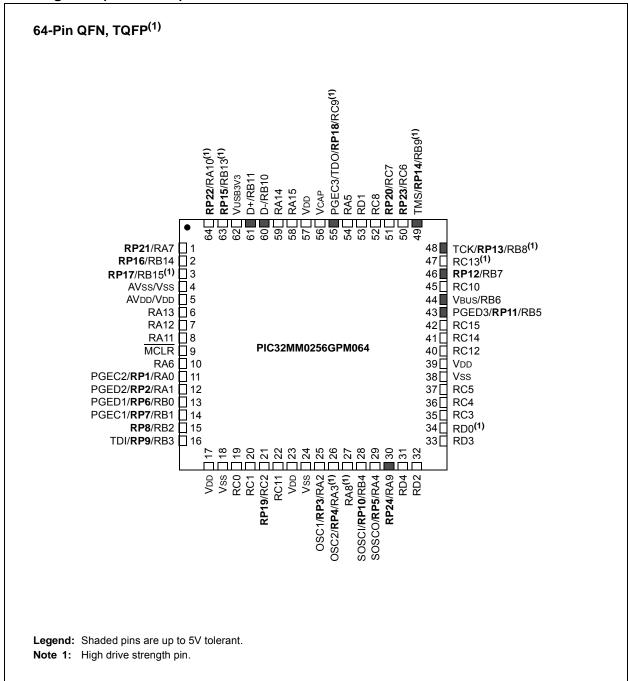

#### 1.0 **DEVICE OVERVIEW**

Note:

This data sheet summarizes the features of the PIC32MM0256GPM064 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

This data sheet contains device-specific information for the PIC32MM0256GPM064 family devices.

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MM0256GPM064 family of devices.

Table 1-1 lists the pinout I/O descriptions for the pins shown in the device pin tables.

TABLE 1-1: PIC32MM0256GPM064 FAMILY PINOUT DESCRIPTION

|          |                |                        | Pin Nu        | ımber          |                        |                        |             |                |                                             |  |  |

|----------|----------------|------------------------|---------------|----------------|------------------------|------------------------|-------------|----------------|---------------------------------------------|--|--|

| Pin Name | 28-Pin<br>SSOP | 28-Pin<br>QFN/<br>UQFN | 36-Pin<br>QFN | 40-Pin<br>UQFN | 48-Pin<br>QFN/<br>TQFP | 64-Pin<br>QFN/<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                 |  |  |

| AN0      | 2              | 27                     | 33            | 36             | 21                     | 11                     | I           | ANA            | Analog-to-Digital Converter input channels  |  |  |

| AN1      | 3              | 28                     | 34            | 37             | 22                     | 12                     | I           | ANA            |                                             |  |  |

| AN2      | 4              | 1                      | 35            | 38             | 23                     | 13                     | I           | ANA            |                                             |  |  |

| AN3      | 5              | 2                      | 36            | 39             | 24                     | 14                     | I           | ANA            |                                             |  |  |

| AN4      | 6              | 3                      | 1             | 1              | 25                     | 15                     | I           | ANA            |                                             |  |  |

| AN5      | 9              | 6                      | 7             | 7              | 32                     | 25                     | I           | ANA            |                                             |  |  |

| AN6      | 10             | 7                      | 8             | 8              | 33                     | 26                     | _           | ANA            |                                             |  |  |

| AN7      | 11             | 8                      | 9             | 9              | 35                     | 28                     | _           | ANA            |                                             |  |  |

| AN8      | 24             | 21                     | 27            | 30             | 12                     | 63                     | I           | ANA            |                                             |  |  |

| AN9      | 25             | 22                     | 28            | 31             | 15                     | 2                      | I           | ANA            |                                             |  |  |

| AN10     | 26             | 23                     | 29            | 32             | 16                     | 3                      | I           | ANA            |                                             |  |  |

| AN11     | 7              | 4                      | 2             | 2              | 26                     | 16                     | I           | ANA            |                                             |  |  |

| AN12     | _              | _                      | 3             | 3              | 27                     | 19                     | I           | ANA            |                                             |  |  |

| AN13     | _              | _                      | 4             | 4              | 28                     | 20                     | I           | ANA            |                                             |  |  |

| AN14     | _              | _                      | 20            | 21             | 4                      | 52                     | I           | ANA            |                                             |  |  |

| AN15     | _              | _                      | _             | _              | 41                     | 37                     | I           | ANA            |                                             |  |  |

| AN16     | _              | _                      | _             | _              | _                      | 6                      | I           | ANA            |                                             |  |  |

| AN17     | _              | _                      | _             | _              | _                      | 7                      | I           | ANA            |                                             |  |  |

| AN18     | _              | _                      | _             | _              | _                      | 8                      | I           | ANA            |                                             |  |  |

| AN19     | _              | _                      | _             | _              | _                      | 10                     | I           | ANA            |                                             |  |  |

| AVDD     | 28             | 25                     | 31            | 34             | 18                     | 5                      | Р           | _              | Analog modules power supply                 |  |  |

| AVss     | 27             | 24                     | 30            | 33             | 17                     | 4                      | Р           | _              | Analog modules ground                       |  |  |

| C1INA    | 7              | 4                      | 2             | 2              | 26                     | 16                     | I           | ANA            | Comparator 1 Input A                        |  |  |

| C1INB    | 6              | 3                      | 1             | 1              | 25                     | 15                     | I           | ANA            | Comparator 1 Input B                        |  |  |

| C1INC    | 5              | 2                      | 36            | 39             | 24                     | 14                     | I           | ANA            | Comparator 1 Input C                        |  |  |

| C1IND    | 4              | 1                      | 35            | 38             | 23                     | 13                     | I           | ANA            | Comparator 1 Input D                        |  |  |

| C2INA    | 5              | 2                      | 36            | 39             | 24                     | 14                     | I           | ANA            | Comparator 2 Input A                        |  |  |

| C2INB    | 4              | 1                      | 35            | 38             | 23                     | 13                     | I           | ANA            | Comparator 2 Input B                        |  |  |

| C2INC    | _              | _                      | 20            | 21             | 4                      | 52                     | Ι           | ANA            | Comparator 2 Input C                        |  |  |

| C2IND    | _              | _                      | 3             | 3              | 27                     | 19                     | I           | ANA            | Comparator 2 Input D                        |  |  |

| C3INA    | 26             | 23                     | 29            | 32             | 16                     | 3                      | Ι           | ANA            | Comparator 3 Input A                        |  |  |

| C3INB    | 25             | 22                     | 28            | 31             | 15                     | 2                      | I           | ANA            | Comparator 3 Input B                        |  |  |

| C3INC    | 4              | 1                      | 35            | 38             | 23                     | 13                     | I           | ANA            | Comparator 3 Input C                        |  |  |

| C3IND    | 10             | 7                      | 8             | 8              | 33                     | 26                     | _           | ANA            | Comparator 3 Input D                        |  |  |

| CLKI     | 9              | 6                      | 7             | 7              | 32                     | 25                     | _           | ST             | External Clock source input (EC mode)       |  |  |

| CLKO     | 10             | 7                      | 8             | 8              | 33                     | 26                     | 0           | DIG            | System clock output                         |  |  |

| CVREF    | 25             | 22                     | 28            | 31             | 15                     | 2                      | 0           | ANA            | Comparator voltage reference output         |  |  |

| CVREF+   | 2              | 27                     | 33            | 36             | 21                     | 11                     | I           | ANA            | Positive comparator voltage reference input |  |  |

| D+       | 22             | 19                     | 25            | 28             | 10                     | 61                     | I/O         | _              | USB transceiver differential plus line      |  |  |

| D-       | 21             | 18                     | 24            | 27             | 9                      | 60                     | I/O         | _              | USB transceiver differential minus line     |  |  |

| FSYNC1   | 26             | 23                     | 29            | 32             | 16                     | 32                     | I/O         | ST/DIG         | SPI1 frame signal input or output           |  |  |

| FSYNC3   | 14             | 11                     | 15            | 15             | 45                     | 22                     | I/O         | ST/DIG         | SPI3 frame signal input or output           |  |  |

**Legend:** ST = Schmitt Trigger input buffer  $I2C = I^2C/SMBus$  input buffer

DIG = Digital input/output ANA = Analog level input/output

TABLE 1-1: PIC32MM0256GPM064 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          |                |                        | Pin Nu        | ımber          |                        |                        |             |                |                                      |  |

|----------|----------------|------------------------|---------------|----------------|------------------------|------------------------|-------------|----------------|--------------------------------------|--|

| Pin Name | 28-Pin<br>SSOP | 28-Pin<br>QFN/<br>UQFN | 36-Pin<br>QFN | 40-Pin<br>UQFN | 48-Pin<br>QFN/<br>TQFP | 64-Pin<br>QFN/<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                          |  |

| INT0     | 26             | 23                     | 29            | 32             | 16                     | 32                     | - 1         | ST             | External Interrupt 0                 |  |

| INT1     | 25             | 22                     | 28            | 31             | 15                     | 31                     | - 1         | ST             | External Interrupt 1                 |  |

| INT2     | 18             | 15                     | 19            | 20             | 1                      | 49                     | I           | ST             | External Interrupt 2                 |  |

| INT3     | 2              | 27                     | 33            | 36             | 40                     | 36                     | I           | ST             | External Interrupt 3                 |  |

| LVDIN    | 24             | 21                     | 20            | 21             | 4                      | 52                     | I           | ANA            | High/Low-Voltage Detect input        |  |

| MCLR     | 1              | 26                     | 32            | 35             | 19                     | 9                      | - 1         | ST             | Master Clear (device Reset)          |  |

| OCM1A    | 17             | 14                     | 18            | 18             | 48                     | 7                      | 0           | DIG            | MCCP1 Output A                       |  |

| OCM1B    | 18             | 15                     | 19            | 20             | 1                      | 53                     | 0           | DIG            | MCCP1 Output B                       |  |

| OCM1C    | 9              | 6                      | 7             | 7              | 32                     | 25                     | 0           | DIG            | MCCP1 Output C                       |  |

| OCM1D    | 10             | 7                      | 8             | 8              | 41                     | 37                     | 0           | DIG            | MCCP1 Output D                       |  |

| OCM1E    | 2              | 27                     | 33            | 36             | 40                     | 36                     | 0           | DIG            | MCCP1 Output E                       |  |

| OCM1F    | 3              | 28                     | 34            | 37             | 22                     | 12                     | 0           | DIG            | MCCP1 Output F                       |  |

| OCM2A    | 19             | 16                     | 5             | 5              | 29                     | 21                     | 0           | DIG            | MCCP2 Output A                       |  |

| OCM2B    | 26             | 23                     | 29            | 32             | 39                     | 35                     | 0           | DIG            | MCCP2 Output B                       |  |

| OCM2C    | 4              | 1                      | 35            | 38             | 23                     | 13                     | 0           | DIG            | MCCP2 Output C                       |  |

| OCM2D    | 5              | 2                      | 36            | 39             | 24                     | 14                     | 0           | DIG            | MCCP2 Output D                       |  |

| OCM2E    | 6              | 3                      | 1             | 1              | 25                     | 15                     | 0           | DIG            | MCCP2 Output E                       |  |

| OCM2F    | 7              | 4                      | 2             | 2              | 26                     | 16                     | 0           | DIG            | MCCP2 Output F                       |  |

| OCM3A    | 24             | 21                     | 11            | 11             | 37                     | 54                     | 0           | DIG            | MCCP3 Output A                       |  |

| ОСМ3В    | 25             | 22                     | 28            | 31             | 15                     | 33                     | 0           | DIG            | MCCP3 Output B                       |  |

| OCM3C    | 11             | 8                      | 9             | 9              | 35                     | 59                     | 0           | DIG            | MCCP3 Output C                       |  |

| OCM3D    | 12             | 9                      | 10            | 10             | 36                     | 41                     | 0           | DIG            | MCCP3 Output D                       |  |

| OCM3E    | 14             | 11                     | 15            | 15             | 45                     | 42                     | 0           | DIG            | MCCP3 Output E                       |  |

| OCM3F    | 16             | 13                     | 17            | 17             | 47                     | 45                     | 0           | DIG            | MCCP3 Output F                       |  |

| OSC1     | 9              | 6                      | 7             | 7              | 32                     | 25                     | _           |                | Primary Oscillator crystal           |  |

| OSC2     | 10             | 7                      | 8             | 8              | 33                     | 26                     | _           | _              | Primary Oscillator crystal           |  |

| PGEC1    | 5              | 2                      | 36            | 39             | 24                     | 14                     | I           | ST             | ICSP™ Port 1 programming clock input |  |

| PGEC2    | 2              | 27                     | 33            | 36             | 21                     | 11                     | I           | ST             | ICSP Port 2 programming clock input  |  |

| PGEC3    | 19             | 16                     | 21            | 22             | 5                      | 55                     | I           | ST             | ICSP Port 3 programming clock input  |  |

| PGED1    | 4              | 1                      | 35            | 38             | 23                     | 13                     | I/O         | ST/DIG         | ICSP Port 1 programming data         |  |

| PGED2    | 3              | 28                     | 34            | 37             | 22                     | 12                     | I/O         | ST/DIG         | ICSP Port 2 programming data         |  |

| PGED3    | 14             | 11                     | 15            | 15             | 45                     | 43                     | I/O         | ST/DIG         | ICSP Port 3 programming data         |  |

| PWRLCLK  | 12             | 9                      | 10            | 10             | 36                     | 29                     | I           | ST             | Real-Time Clock 50/60 Hz clock input |  |

**Legend:** ST = Schmitt Trigger input buffer  $12C = 1^2C/SMBus$  input buffer

DIG = Digital input/output ANA = Analog level input/output

TABLE 1-1: PIC32MM0256GPM064 FAMILY PINOUT DESCRIPTION (CONTINUED)

|          | Pin Nu         |                        | ımber         |                |                        |                        |             |                |                    |  |

|----------|----------------|------------------------|---------------|----------------|------------------------|------------------------|-------------|----------------|--------------------|--|

| Pin Name | 28-Pin<br>SSOP | 28-Pin<br>QFN/<br>UQFN | 36-Pin<br>QFN | 40-Pin<br>UQFN | 48-Pin<br>QFN/<br>TQFP | 64-Pin<br>QFN/<br>TQFP | Pin<br>Type | Buffer<br>Type | Description        |  |

| RA0      | 2              | 27                     | 33            | 36             | 21                     | 11                     | I/O         | ST/DIG         | PORTA digital I/Os |  |

| RA1      | 3              | 28                     | 34            | 37             | 22                     | 12                     | I/O         | ST/DIG         |                    |  |

| RA2      | 9              | 6                      | 7             | 7              | 32                     | 25                     | I/O         | ST/DIG         |                    |  |

| RA3      | 10             | 7                      | 8             | 8              | 33                     | 26                     | I/O         | ST/DIG         |                    |  |

| RA4      | 12             | 9                      | 10            | 10             | 36                     | 29                     | I/O         | ST/DIG         |                    |  |

| RA5      | _              | _                      | _             | _              | _                      | 54                     | I/O         | ST/DIG         |                    |  |

| RA6      | _              | _                      | _             | _              | 20                     | 10                     | I/O         | ST/DIG         |                    |  |

| RA7      | _              | _                      | _             | _              | 14                     | 1                      | I/O         | ST/DIG         |                    |  |

| RA8      | _              | _                      | _             | _              | 34                     | 27                     | I/O         | ST/DIG         |                    |  |

| RA9      | _              | _                      | 11            | 11             | 37                     | 30                     | I/O         | ST/DIG         |                    |  |

| RA10     | _              | _                      | _             | _              | 13                     | 64                     | I/O         | ST/DIG         |                    |  |

| RA11     | _              | _                      | _             | _              | _                      | 8                      | I/O         | ST/DIG         |                    |  |

| RA12     | _              | _                      | _             | _              | _                      | 7                      | I/O         | ST/DIG         |                    |  |

| RA13     | _              | _                      | _             | _              | _                      | 6                      | I/O         | ST/DIG         |                    |  |

| RA14     | _              | _                      | _             | _              | _                      | 59                     | I/O         | ST/DIG         |                    |  |

| RA15     | _              | _                      | _             | _              | 8                      | 58                     | I/O         | ST/DIG         |                    |  |

| RB0      | 4              | 1                      | 35            | 38             | 23                     | 13                     | I/O         | ST/DIG         | PORTB digital I/Os |  |

| RB1      | 5              | 2                      | 36            | 39             | 24                     | 14                     | I/O         | ST/DIG         |                    |  |

| RB2      | 6              | 3                      | 1             | 1              | 25                     | 15                     | I/O         | ST/DIG         |                    |  |

| RB3      | 7              | 4                      | 2             | 2              | 26                     | 16                     | I/O         | ST/DIG         |                    |  |

| RB4      | 11             | 8                      | 9             | 9              | 35                     | 28                     | I/O         | ST/DIG         |                    |  |

| RB5      | 14             | 11                     | 15            | 15             | 45                     | 43                     | I/O         | ST/DIG         |                    |  |

| RB6      | 15             | 12                     | 16            | 16             | 46                     | 44                     | I/O         | ST/DIG         |                    |  |

| RB7      | 16             | 13                     | 17            | 17             | 47                     | 46                     | I/O         | ST/DIG         |                    |  |

| RB8      | 17             | 14                     | 18            | 18             | 48                     | 48                     | I/O         | ST/DIG         |                    |  |

| RB9      | 18             | 15                     | 19            | 20             | 1                      | 49                     | I/O         | ST/DIG         |                    |  |

| RB10     | 21             | 18                     | 24            | 27             | 9                      | 60                     | I/O         | ST/DIG         |                    |  |

| RB11     | 22             | 19                     | 25            | 28             | 10                     | 61                     | I/O         | ST/DIG         |                    |  |

| RB13     | 24             | 21                     | 27            | 30             | 12                     | 63                     | I/O         | ST/DIG         |                    |  |

| RB14     | 25             | 22                     | 28            | 31             | 15                     | 2                      | I/O         | ST/DIG         |                    |  |

| RB15     | 26             | 23                     | 29            | 32             | 16                     | 3                      | I/O         | ST/DIG         |                    |  |

**Legend:** ST = Schmitt Trigger input buffer  $12C = 1^2C/SMBus$  input buffer

DIG = Digital input/output ANA = Analog level input/output

**TABLE 1-1:** PIC32MM0256GPM064 FAMILY PINOUT DESCRIPTION (CONTINUED)

| TABLE 1-1 |                |                        | AMILI FINOUI DESCRIFT |                |                        |                        | ,           |                |                                          |

|-----------|----------------|------------------------|-----------------------|----------------|------------------------|------------------------|-------------|----------------|------------------------------------------|

| Pin Name  | 28-Pin<br>SSOP | 28-Pin<br>QFN/<br>UQFN | 36-Pin<br>QFN         | 40-Pin<br>UQFN | 48-Pin<br>QFN/<br>TQFP | 64-Pin<br>QFN/<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                              |

| RC0       | _              | _                      | 3                     | 3              | 27                     | 19                     | I/O         | ST/DIG         | PORTC digital I/Os                       |

| RC1       | _              | _                      | 4                     | 4              | 28                     | 20                     | I/O         | ST/DIG         |                                          |

| RC2       | _              | _                      | 5                     | 5              | 29                     | 21                     | I/O         | ST/DIG         |                                          |

| RC3       | _              | _                      | 14                    | 14             | 39                     | 35                     | I/O         | ST/DIG         |                                          |

| RC4       | _              | _                      | _                     | _              | 40                     | 36                     | I/O         | ST/DIG         |                                          |

| RC5       | _              | _                      | _                     | _              | 41                     | 37                     | I/O         | ST/DIG         |                                          |

| RC6       | _              | _                      | _                     | _              | 2                      | 50                     | I/O         | ST/DIG         |                                          |

| RC7       | _              | _                      | _                     | _              | 3                      | 51                     | I/O         | ST/DIG         |                                          |

| RC8       | _              | _                      | 20                    | 21             | 4                      | 52                     | I/O         | ST/DIG         |                                          |

| RC9       | 19             | 16                     | 21                    | 22             | 5                      | 55                     | I/O         | ST/DIG         |                                          |

| RC10      | _              | _                      | _                     | _              | _                      | 45                     | I/O         | ST/DIG         |                                          |

| RC11      | _              | _                      | _                     | _              | _                      | 22                     | I/O         | ST/DIG         |                                          |

| RC12      | _              | _                      | _                     | _              | 44                     | 40                     | I/O         | ST/DIG         |                                          |

| RC13      | _              | _                      | _                     | _              | _                      | 47                     | I/O         | ST/DIG         |                                          |

| RC14      | _              | _                      | _                     | _              | _                      | 41                     | I/O         | ST/DIG         |                                          |

| RC15      | _              | _                      | _                     | _              | _                      | 42                     | I/O         | ST/DIG         |                                          |

| RD0       | _              | _                      | _                     | _              | 38                     | 34                     | I/O         |                | PORTD digital I/Os                       |

| RD1       | _              | _                      | _                     | _              | _                      | 53                     | I/O         | ST/DIG         | 3 4 4                                    |

| RD2       | _              | _                      | _                     | _              | _                      | 32                     | I/O         | ST/DIG         |                                          |

| RD3       | _              | _                      | _                     | _              | _                      | 33                     | I/O         | ST/DIG         |                                          |

| RD4       | _              | _                      | _                     | _              | _                      | 31                     | I/O         | ST/DIG         |                                          |

| REFCLKI   | 18             | 15                     | 19                    | 20             | 38                     | 34                     | 1           | ST             | External reference clock input           |

| REFCLKO   | 26             | 23                     | 29                    | 32             | 16                     | 3                      | O           | ST             | External reference clock output          |

| RP1       | 2              | 27                     | 33                    | 36             | 21                     | 11                     | I/O         |                | Remappable peripherals (input or output) |

| RP2       | 3              | 28                     | 34                    | 37             | 22                     | 12                     | I/O         | ST/DIG         | (input of cutput)                        |

| RP3       | 9              | 6                      | 7                     | 7              | 32                     | 25                     | I/O         | ST/DIG         |                                          |

| RP4       | 10             | 7                      | 8                     | 8              | 33                     | 26                     | I/O         | ST/DIG         |                                          |

| RP5       | 12             | 9                      | 10                    | 10             | 36                     | 29                     | I/O         | ST/DIG         |                                          |

| RP6       | 4              | 1                      | 35                    | 38             | 23                     | 13                     | I/O         | ST/DIG         |                                          |

| RP7       | 5              | 2                      | 36                    | 39             | 24                     | 14                     | I/O         | ST/DIG         |                                          |

| RP8       | 6              | 3                      | 1                     | 1              | 25                     | 15                     | I/O         | ST/DIG         |                                          |

| RP9       | 7              | 4                      | 2                     | 2              | 26                     | 16                     | I/O         | ST/DIG         |                                          |

| RP10      | 11             | 8                      | 9                     | 9              | 35                     | 28                     | I/O         | ST/DIG         |                                          |

| RP11      | 14             | 11                     | 15                    | 15             | 45                     | 43                     | I/O         | ST/DIG         |                                          |

| RP12      | 16             | 13                     | 17                    | 17             | 47                     | 46                     | I/O         | ST/DIG         |                                          |

| RP13      | 17             | 14                     | 18                    | 18             | 48                     | 48                     | I/O         | ST/DIG         |                                          |

| RP14      | 18             | 15                     | 19                    | 20             | 1                      | 49                     | 1/0         | ST/DIG         |                                          |

| RP15      | 24             | 21                     | 27                    | 30             | 12                     | 63                     | 1/0         | ST/DIG         |                                          |

| RP16      | 25             | 22                     | 28                    | 31             | 15                     | 2                      | 1/0         | ST/DIG         |                                          |

| RP17      | 26             | 23                     | 29                    | 32             | 16                     | 3                      | 1/0         | ST/DIG         |                                          |

| RP18      | 19             | 16                     | 29                    | 22             | 5                      | 55                     | 1/0         | ST/DIG         |                                          |

| RP19      | 18             | -                      | 5                     | 5              | 29                     | 21                     | 1/0         | ST/DIG         |                                          |

| RP20      | <del>-</del>   |                        | _                     |                | 3                      | 51                     | 1/0         | ST/DIG         |                                          |

|           |                |                        | input buf             | _              | l                      | igital innu            | l           |                | D = Power                                |

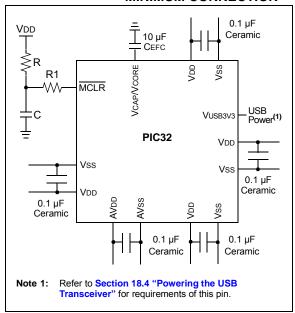

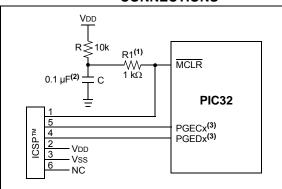

ST = Schmitt Trigger input buffer  $I2C = I^2C/SMBus$  input buffer Legend: