#### **MAX25606**

## 6-Switch Matrix Manager for Automotive Lighting

## **General Description**

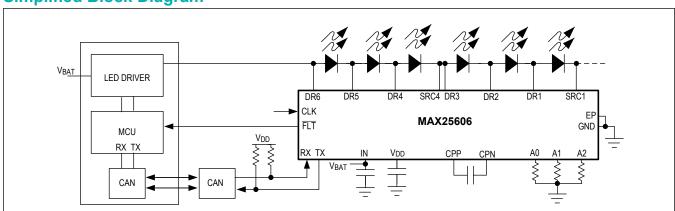

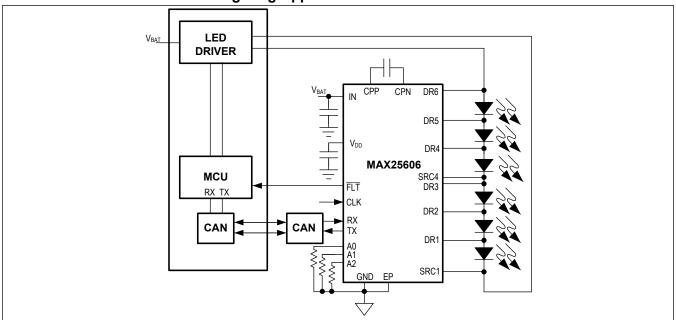

The MAX25606 6-switch matrix manager IC for automotive lighting applications includes a 6-switch array for bypassing individual LEDs in a single- or dual-string application. It features six individually controlled n-channel MOSFET switches with each switch having an on-resistance of  $0.2\Omega$  and rated to withstand 16V. A single current source can be used to power all the LEDs connected in series. Individual LEDs can be dimmed by turning on and off the bypass switches across each LED. The device can also be configured in two string applications with three switches in series per string. Each switch can be connected across one, two, or three LEDs in series. It also allows for parallel connection of two switches to bypass high-current LEDs. The IC also includes an internal charge pump that provides power for the gate drive for the LED bypass switches.

The IC features a universal asynchronous receiver-transmitter (UART) communication interface. Each switch can be turned on, turned off, or PWM modulated with 12 bits of PWM duty cycle adjustment. Transitions between two different PWM settings can either happen instantly or a logarithmic fade transition can be applied. The logarithmic fade algorithm is built into the device and only requires a single software command. The IC features open-LED protection as well as open and short LED fault reporting through the serial interface. The device is available in a 20-pin 4x4mm side wettable TQFN and a 20-pin thin shrink small-outline package (TSSOP) with exposed pad. The device is AEC-Q100 grade 1 qualified and designed to operate over the full -40°C to +125°C temperature range.

#### **Applications**

Automotive Matrix LED Systems and Adaptive Drive Beam Lights

#### **Benefits and Features**

- Automotive Ready: AEC-Q100 Qualified

- Six-Switch Matrix Manager Allows for Flexible Configuration

- · Single and Dual-String Configurations

- · Up to 6 Switches in Series for Single String

- · Up to 3 Switches in Series in Dual-String

- · Up to 3 LEDs per Switch

- Robust Serial Interface

- · Multidrop UART Communication Interface

- Up to 64 Addressable Devices

- Compatible with CAN Physical Layer

- Optimal PWM Dimming Arrangement Provides Excellent Dimming Performance

- Programmable 12-Bit PWM Dimming

- Fade Transition Between PWM Dimming States

- Internal Clock Generator or External Clock for PWM Dimming

- EMI Mitigation

- · Programmable Slew Rate for EMI Control

- Integrated Spread Spectrum Frequency Dithering

- Protection Features and Package Improve Reliability

- Open-LED Protection

- Programmable Open and Short-LED Threshold

- Open and Shorted-LED Fault Reporting

- · Open Trace Fault Reporting

- Thermally Enhanced 20-Pin Side Wettable TQFN and 20-Pin TSSOP with Exposed Pad

Ordering Information appears at end of datasheet.

## **Simplified Block Diagram**

## **TABLE OF CONTENTS**

| General Description.                                      |    |

|-----------------------------------------------------------|----|

| Applications                                              |    |

| Benefits and Features                                     |    |

| Simplified Block Diagram                                  |    |

| Absolute Maximum Ratings                                  |    |

| Package Information                                       |    |

| 20 TQFN-EP* (SW)                                          |    |

| 20 TSSOP-EP*                                              |    |

| Electrical Characteristics                                | 6  |

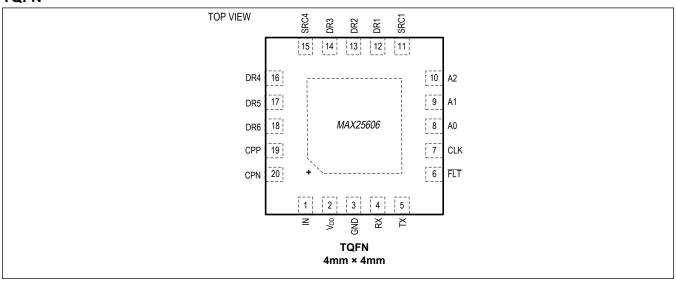

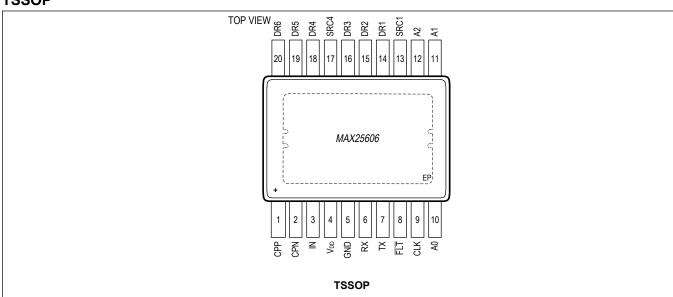

| Pin Configurations                                        |    |

| TQFN                                                      |    |

| TSSOP                                                     |    |

| Pin Description                                           |    |

| Functional Diagrams                                       |    |

| MAX25606 Block Diagram                                    |    |

| Detailed Description                                      |    |

| Power-On Reset and VDD UVLO                               |    |

| Internal Switches                                         | 11 |

| Charge Pump                                               |    |

| Programming Options                                       |    |

| MAX25606 Pin Resistor Decode Table                        |    |

| Resistor Programming Table                                |    |

| PWM Clock and Synchronous Operation with Multiple Devices |    |

| Parallel Operation for Higher Current Applications        |    |

| PWM Dimming                                               |    |

| Dimming With and Without Fade                             |    |

| LED Fault Detection and Protection                        |    |

| LED Short Threshold                                       |    |

| UART Serial Interface                                     |    |

| Overview                                                  |    |

| Device Connections                                        |    |

| UART Frame Format                                         |    |

| Synchronization and Acknowledge Frames                    |    |

| Device ID and Address Frame Format                        |    |

| Write Transactions                                        |    |

| CRC Error Checking                                        |    |

| UART Watchdog Function                                    |    |

| UART Communication Error Handling                         |    |

| Thermal Protection                                        | 18 |

# TABLE OF CONTENTS (CONTINUED)

| PWM Clock and Synchronous Operation with Multiple Devices |    |

|-----------------------------------------------------------|----|

| Register Map                                              |    |

| MAX25606                                                  |    |

| Register Details                                          | 21 |

| Applications Information                                  | 42 |

| Configuration                                             | 42 |

| Synchronized PWM Phase                                    | 42 |

| Recommended LED Drivers                                   | 42 |

| Thermal Considerations                                    | 42 |

| Layout Considerations                                     | 42 |

| Typical Application Circuits                              | 43 |

| MAX25606 in 6-Channel Matrix Lighting Application         | 43 |

| Ordering Information                                      | 43 |

| Revision History                                          | 44 |

## MAX25606

# 6-Switch Matrix Manager for Automotive Lighting

| LIST OF FIGURES                                |    |  |  |  |

|------------------------------------------------|----|--|--|--|

| Figure 1. PWM Phase and Duty Cycle Definitions | 14 |  |  |  |

| Figure 2. SYNC Frame                           | 16 |  |  |  |

| Figure 3. ACK Frame                            | 16 |  |  |  |

Figure 5. SYNC Frame

17

Figure 6. SYNC Frame

17

## **Absolute Maximum Ratings**

| IN to GND               | 0.3V to +65V  |

|-------------------------|---------------|

| V <sub>DD</sub> to GND  | 0.3V to +2.5V |

| CPN to GND              | 0.3V to +65V  |

| CPP to GND              | 0.3V to +70V  |

| CPP to CPN              | 0.3V to +6V   |

| CPP to DR6              | 0.3V to +70V  |

| DR6 to GND              | 0.3V to +65V  |

| DRx to DR(x-1) (Note 1) | 0.3V to +16V  |

| SRCx to GND             | 0.3V to +65V  |

| DR6 to SRC4             | 0.3V to +48V  |

| DR4 to SRC4             | 0.3V to +16V  |

| DR3 to SRC1             | 0.3V to +48V  |

| DR1 to SRC1             | 0.3V to +16V  |

| Continuous Current on DRx, SRCx        | 750mA                          |

|----------------------------------------|--------------------------------|

| FLT, CLK to GND                        | 0.3V to +6V                    |

| RX, TX to GND                          | 0.3V to +6V                    |

| A0, A1, A2 to GND                      | 0.3V to V <sub>DD</sub> + 0.3V |

| Continuous Power Dissipation (20-Pin T | QFN SW) $(T_A = +70^{\circ}C,$ |

| derate 25.6mW/°C above +70°C)          | 2050mW                         |

| Continuous Power Dissipation (20-Pin   | TSSOP) $(T_A = +70^{\circ}C,$  |

| derate 26mW/°C above +70°C)            | 2122mW                         |

| Operating Temperature Range            | 40°C to +125°C                 |

| Junction Temperature                   | +150°C                         |

| Storage Temperature Range              | 40°C to +150°C                 |

| Soldering Temperature (reflow)         | +260°C                         |

|                                        |                                |

#### Note 1: Does not apply to DR4 to DR3.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

### 20 TQFN-EP\* (SW)

| Package Code                            | T2044Y+3C        |  |  |

|-----------------------------------------|------------------|--|--|

| Outline Number                          | <u>21-100068</u> |  |  |

| Land Pattern Number                     | <u>90-0037</u>   |  |  |

| Thermal Resistance, Single-Layer Board: |                  |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | 59°C/W           |  |  |

| Junction to Case (θ <sub>JC</sub> )     | 6°C/W            |  |  |

| Thermal Resistance, Four-Layer Board:   |                  |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | 39°C/W           |  |  |

| Junction to Case (θ <sub>JC</sub> )     | 6°C/W            |  |  |

#### 20 TSSOP-EP\*

| Package Code                            | U20E+3C          |  |  |

|-----------------------------------------|------------------|--|--|

| Outline Number                          | <u>21-100132</u> |  |  |

| Land Pattern Number                     | <u>90-100049</u> |  |  |

| Thermal Resistance, Single-Layer Board: |                  |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | 46°C/W           |  |  |

| Junction to Case (θ <sub>JC</sub> )     | 2°C/W            |  |  |

| Thermal Resistance, Four-Layer Board:   |                  |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | 37°C/W           |  |  |

| Junction to Case (θ <sub>JC</sub> )     | 2°C/W            |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

## **Electrical Characteristics**

(Input Voltage = IN = 5V,  $T_A = T_J = -40^{\circ}\text{C}$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. (Note 2)

| PARAMETER                                              | SYMBOL              | CONDITIONS                                                                                | MIN  | TYP    | MAX  | UNITS |

|--------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------|------|--------|------|-------|

| Supply Voltages                                        |                     |                                                                                           |      |        |      |       |

| Supply Voltage                                         | V <sub>IN</sub>     | Operating Voltage Range                                                                   | 4.0  |        | 60   | V     |

| Input Current                                          | I <sub>IN</sub>     |                                                                                           |      | 2      | 5    | mA    |

| Input Power-On Reset (POR) Threshold                   | V <sub>IN-POR</sub> | V <sub>IN</sub> Rising                                                                    | 3.6  |        | 3.9  | V     |

| Charge-Pump Operating Voltage                          | V <sub>CPP</sub>    |                                                                                           |      |        | 65   | V     |

| V <sub>DD</sub> Regulator                              |                     |                                                                                           |      |        |      |       |

| V <sub>DD</sub> Output                                 | V <sub>DD</sub>     | $2.2\mu F$ Capacitor Placed between V <sub>DD</sub> and GND Pins. I <sub>VDD</sub> = 10mA | 1.71 | 1.8    | 1.89 | V     |

| VDD undervoltage<br>lockout (UVLO) Rising<br>Threshold | UVLO_R_TH           |                                                                                           | 1.61 |        | 1.69 | V     |

| VDD UVLO Falling<br>Threshold                          | UVLO_F_TH           |                                                                                           | 1.54 |        | 1.63 | V     |

| LED Dimming                                            |                     |                                                                                           |      |        |      |       |

| Internal Oscillator<br>Frequency                       | F <sub>OSC</sub>    | Used for Charge Pump and PWM Dimming of LEDs                                              |      | 16.384 |      | MHz   |

| LED Switches                                           |                     |                                                                                           |      |        |      |       |

| Single-Switch On-<br>Resistance                        | R <sub>DSON</sub>   |                                                                                           |      | 0.2    |      | Ω     |

| On-Resistance with<br>Series Switches 3-1 On           |                     |                                                                                           |      | 0.6    | 1.2  | Ω     |

| On-Resistance with<br>Series Switches 6-4 On           |                     |                                                                                           |      | 0.6    | 1.2  | Ω     |

| Open LED Threshold                                     | V <sub>OTH</sub>    |                                                                                           | 12.5 | 13.75  | 15   | V     |

| Open Trace Threshold                                   | ILED_MIN            | Minimum Current Required to Detect<br>Open Trace                                          |      | 45     | 100  | mA    |

|                                                        |                     | VSTH[2:0] = 0b000, Rising V <sub>DS</sub>                                                 | 1.26 | 1.40   | 1.54 |       |

|                                                        |                     | VSTH[2:0] = 0b001, Rising V <sub>DS</sub>                                                 | 3.24 | 3.6    | 3.96 |       |

|                                                        |                     | VSTH[2:0] = 0b010, Rising V <sub>DS</sub>                                                 | 3.6  | 4.00   | 4.4  |       |

| Short LED Threshold                                    | V                   | VSTH[2:0] = 0b011, Rising V <sub>DS</sub>                                                 | 4.95 | 5.5    | 6.05 | V     |

| SHOIL LED THIESHOLD                                    | V <sub>STH</sub>    | VSTH[2:0] = 0b100, Rising V <sub>DS</sub>                                                 | 5.4  | 6.0    | 6.6  | ]     |

|                                                        |                     | VSTH[2:0] = 0b101, Rising V <sub>DS</sub>                                                 | 5.94 | 6.6    | 7.26 |       |

|                                                        |                     | VSTH[2:0] = 0b110, Rising V <sub>DS</sub> 6.48                                            | 7.2  | 7.92   | 7    |       |

|                                                        |                     | VSTH[2:0] = 0b111, Rising V <sub>DS</sub>                                                 | 6.93 | 7.70   | 8.47 | ]     |

| FLT Flag                                               |                     |                                                                                           |      |        |      |       |

| FLT Output Low Voltage                                 |                     | I <sub>SINK</sub> = 2 mA                                                                  |      | 0.06   | 0.4  | V     |

| FLT Output High<br>Leakage Current                     |                     | FLT = 5V                                                                                  |      |        | 1    | μА    |

| Clock External Sync<br>Input, Clock Frequency          | fCLK                |                                                                                           | 0.3  |        | 18   | MHz   |

## **Electrical Characteristics (continued)**

(Input Voltage = IN = 5V,  $T_A = T_J = -40^{\circ}\text{C}$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. (Note 2)

| PARAMETER                            | SYMBOL                   | CONDITIONS                                                    | MIN | TYP | MAX | UNITS |  |

|--------------------------------------|--------------------------|---------------------------------------------------------------|-----|-----|-----|-------|--|

| DIGITAL INPUTS (CLK,                 | DIGITAL INPUTS (CLK, RX) |                                                               |     |     |     |       |  |

| Input High Voltage                   | V <sub>IH</sub>          |                                                               | 1.4 |     |     | V     |  |

| Input Low Voltage                    | V <sub>IL</sub>          |                                                               |     |     | 0.4 | V     |  |

| DIGITAL OUTPUTS (CLI                 | K, TX)                   |                                                               |     |     |     |       |  |

| Output Low Voltage                   | V <sub>OL</sub>          | I <sub>SINK</sub> = 2mA                                       |     |     | 0.4 | V     |  |

| THERMAL SHUTDOWN                     |                          |                                                               | ·   |     |     |       |  |

| Thermal-Warning<br>Threshold         | TH_WARN                  | Rising Temperature                                            |     | 140 |     | °C    |  |

| Thermal-Warning<br>Hysteresis        | HYS_WARN                 |                                                               |     | 15  |     | °C    |  |

| Thermal-Shutdown<br>Threshold        | TH_SHDN                  | Rising Temperature                                            |     | 165 |     | °C    |  |

| Thermal-Shutdown<br>Hysteresis       | HYS_SHDN                 |                                                               |     | 15  |     | °C    |  |

| CHARGE PUMP                          |                          |                                                               |     |     |     |       |  |

| Charge-Pump Output<br>Voltage        | Vo                       | V <sub>CPP</sub> - V <sub>CPN,</sub> I <sub>CPP</sub> = 190μA | 3.8 |     | 5.8 | V     |  |

| Charge-Pump Power-<br>Good Threshold | V <sub>CPP_OK</sub>      | Rising Threshold                                              |     | 4.0 |     | V     |  |

| <b>UART Timing</b>                   | UART Timing              |                                                               |     |     |     |       |  |

| UART Bit Rate                        | F <sub>UART</sub>        |                                                               | 10  |     | 500 | kbps  |  |

Note 2: Limits are 100% production tested at TA = +25°C. Limits over the operating temperature range and relevant supply voltage are guaranteed by design and characterization.

# **Pin Configurations**

## **TQFN**

## **TSSOP**

## **Pin Description**

| PI   | IN    | NAME    | EUNCTION                                                                                                                                     |  |

|------|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| TQFN | TSSOP | INAIVIE | FUNCTION                                                                                                                                     |  |

| 1    | 3     | IN      | Input Supply. Connect to external power supply to provide power to the device. Connect a minimum 0.1µF ceramic capacitor between IN and GND. |  |

# **Pin Description (continued)**

| Р    | PIN   |                 |                                                                                                                                                                                                             |  |

|------|-------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TQFN | TSSOP | NAME            | FUNCTION                                                                                                                                                                                                    |  |

| 2    | 4     | V <sub>DD</sub> | LDO Output. Nominal voltage is 1.8V. Connect a minimum 2.2 $\mu$ F ceramic capacitor between V <sub>DD</sub> and GND.                                                                                       |  |

| 3    | 5     | GND             | Ground Connection                                                                                                                                                                                           |  |

| 4    | 6     | RX              | UART Receive Input                                                                                                                                                                                          |  |

| 5    | 7     | TX              | UART Transmit Output                                                                                                                                                                                        |  |

| 6    | 8     | FLT             | Open-Drain Fault Indicator. Goes low when a fault condition is present.                                                                                                                                     |  |

| 7    | 9     | CLK             | Sequence Period Programming Input. Connect a resistor from CLK to GND to set the sequence period.                                                                                                           |  |

| 8    | 10    | A0              | A0 programming input. Connect a resistor from A0 to GND to set the 4 least-significant bytes (LSBs) of the UART device ID.                                                                                  |  |

| 9    | 11    | A1              | A1 programming input. Connect a resistor from A1 to GND to set the 2 most-significant bytes (MSBs) of the UART device ID.                                                                                   |  |

| 10   | 12    | A2              | A2 programming input. Connect a resistor from A2 to GND to use as a general purpose decode, such as for a binning resistor. The corresponding A2 code can be read through the UART interface after powerup. |  |

| 11   | 13    | SRC1            | Source of Internal Switch 1                                                                                                                                                                                 |  |

| 12   | 14    | DR1             | Drain of Internal Switch 1                                                                                                                                                                                  |  |

| 13   | 15    | DR2             | Drain of Internal Switch 2                                                                                                                                                                                  |  |

| 14   | 16    | DR3             | Drain of Internal Switch 3                                                                                                                                                                                  |  |

| 15   | 17    | SRC4            | Source of Internal Switch 4                                                                                                                                                                                 |  |

| 16   | 18    | DR4             | Drain of Internal Switch 4                                                                                                                                                                                  |  |

| 17   | 19    | DR5             | Drain of Internal Switch 5                                                                                                                                                                                  |  |

| 18   | 20    | DR6             | Drain of Internal Switch 6                                                                                                                                                                                  |  |

| 19   | 1     | CPP             | Charge Pump Capacitor Positive Connection. Connect a 0.1µF ceramic capacitor from CPP to CPN.                                                                                                               |  |

| 20   | 2     | CPN             | Charge Pump Capacitor Negative Connection. Connect a 0.1µF ceramic capacitor from CPP to CPN.                                                                                                               |  |

| -    |       | EP              | Exposed Pad Connection. Connect this pad to a contiguous ground plane.                                                                                                                                      |  |

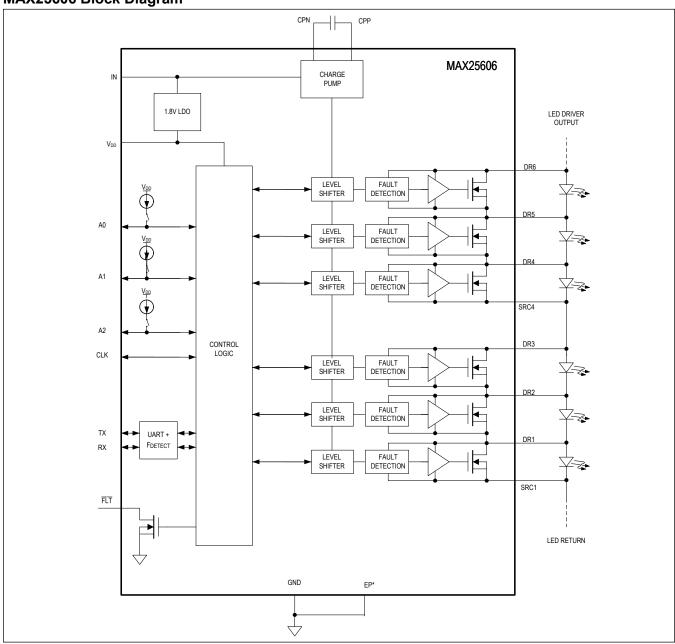

## **Functional Diagrams**

## MAX25606 Block Diagram

### **Detailed Description**

The MAX25606 6-switch matrix manager IC for automotive lighting applications includes a 6-switch array for bypassing individual LEDs in single- or dual-string applications. It features six individually controlled n-channel MOSFET switches, each switch having an  $RD_{SON}$  of  $0.2\Omega$  and rated to withstand 16V. Each group of three cascoded switches can withstand up to 48V. The low on-resistance of the switches minimizes conduction loss and power dissipation.

For single-string applications a single current source can be used to power all the LEDs connected in series. Dual-string applications use a separate current source for each string, with three switches in series per string. For high-current applications, the two sets of three switches can be connected in parallel with a single current source. Each switch can be connected across one, two, or three LEDs in series.

The IC features a serial peripheral interface (UART) for serial communication. The MAX25606 is a slave device that uses the UART to communicate with an external micro-controller ( $\mu$ C), which acts as the master. The serial interface supports the use of CAN transceivers for a robust physical layer. Up to 64 separate devices can be connected using a star topology. Each of the six switches can be independently programmed to bypass the LEDs in the string. Each switch can be turned on, turned off, or PWM modulated with 12 bits of PWM duty cycle adjustment. Transitions between two different PWM settings can either happen instantly or a logarithmic fade transition can be applied. The logarithmic fade algorithm is built into the device and only requires a single software command. The  $\mu$ C can assign device Cluster IDs to allow for simultaneous programming of multiple devices. The serial interface allows the user to program the slew rate to minimize EMI. The PWM frequency can be set by an internal oscillator or synchronized to an external clock source. The IC features built-in open circuit protection, as well as detailed open- and short-LED fault reporting and open trace fault reporting through the serial interface. The short LED fault threshold is programmable to accommodate a wide variety of LED diodes. The IC also includes an internal charge pump that provides power for the gate drive of each of the LED bypass switches.

The device is available in a 20-pin 4x4mm side wettable TQFN and a 20-pin TSSOP package with exposed pad. The device is AEC-Q100 Grade 1 qualified and designed to operate over the -40°C to +125°C temperature range.

#### Power-On Reset and VDD UVLO

Once the IC is powered, an internal power-on reset (POR) signal sets all the registers to their default states. All six switches are in the on-state upon a POR (all LEDs are off). The LEDs remain off until a command is received by the UART. To ensure reliable operation, the IN supply voltage ( $V_{IN}$ ) must be greater than  $V_{IN-POR}$ . If  $V_{IN}$  falls below  $V_{IN-POR}$  and the VDD regulator output falls below VDD\_UVLO, the registers reset to their default state. The IN voltage must be greater than  $V_{IN-POR}$  and VDD must be above VDD\_UVLO for proper operation. The bypass switches remain in their default on-state until the UART is used to enable LED dimming.

#### **Internal Switches**

#### **Charge Pump**

The MAX25606 integrates a charge pump that provides the voltage rails for each switch gate driver and level shifter. The charge pump requires a single  $0.1\mu\text{F}$  capacitor connected between CPP and CPN for operation. The charge pump includes spread spectrum, which dithers the switching frequency by  $\pm 6\%$  around the fundamental of 16.384MHz. The input power for the charge pump is taken from the higher voltage of IN, DR6, or DR3. Therefore, IN and DR6 should have an external decoupling capacitor of at least  $0.01\mu\text{F}$  as close as possible to the device, assuming DR6 is always a greater voltage than DR3. If the DR6 and DR3 segments are controlling two different LED strings, then DR3 should also have a close decoupling capacitor.

A status flag CP\_NOT\_RDY indicates that the charge pump is not yet powered up. When the charge pump is not powered up, the switches inside the IC are off, allowing any current from the LED driver to flow through the LEDs.

Register configurations for LED short detection threshold and switch slew rate in address 0x02 gets level shifted to each switch. Since the level-shift circuit uses the charge pump supply, these registers can only be updated if the charge pump is ready. If the charge pump loses power, these level-shifted registers are reset to 0. The level-shifted registers for each switch only get updated if the charge pump supply is good and a new value is written to the logic level register map. Therefore, if a nonzero value is used for the slew rate or short threshold setting, it is recommended to write 0 and rewrite

the correct value to these registers any time the charge pump supply is interrupted. Make sure the SW\_GO\_EN bit is set to 0 whenever updating the register 0x02 configuration bits.

#### **Programming Options**

#### MAX25606 Pin Resistor Decode Table

Multiple MAX25606 devices can be used in a multidrop UART bus with an external uC acting as the master. The resistors on pins A0 and A1 are used to program the UART Device ID of the MAX25606. The first two LSBs of the A1 code are concatenated with the 4 bits of the A0 code to produce the device ID. For example, a value of  $309\Omega$  on A1 (code x2) and a value of  $1050\Omega$  on A0 (code x8) result in a Device ID of x28.

Table 1. Device ID and A0/A1 Inputs

| {A1[1:0], A0[3:0]} | DEVICE ID |  |  |  |

|--------------------|-----------|--|--|--|

| x00                | x00       |  |  |  |

| x01                | x01       |  |  |  |

|                    |           |  |  |  |

| x3F                | x3F       |  |  |  |

The remaining unused bits {A1[3:2], A2[3:0]} can be used for as general purpose indicators, for example, a binning resistor and/or a hardware revision identifier. The MAX25606 stores the coded value of the resistors on A0, A1, and A2 in the STAT\_RES\_CODE register, address 0x0C, and thus the information is available to the microcontroller through the UART bus.

#### **Resistor Programming Table**

The IC provides 16 levels of detection between 0 and 1.2V on the A0, A1, and A2 pins, which are used to configure the MAX25606 device ID. The pins source 400  $\mu$ A, allowing the use of an external resistor between A0/A1/A2 and GND to set the voltage level. See Table 2 for recommended resistor values.

Table 2. A0/A1/A2 Recommended Values

| A0/A1/A2[3:0] DECODE VALUE | A0/A1 RESISTOR VALUE<br>(Ω, 1%) |

|----------------------------|---------------------------------|

| 0000                       | 95.3                            |

| 0001                       | 200                             |

| 0010                       | 309                             |

| 0011                       | 422                             |

| 0100                       | 536                             |

| 0101                       | 649                             |

| 0110                       | 768                             |

| 0111                       | 909                             |

| 1000                       | 1050                            |

| 1001                       | 1210                            |

| 1010                       | 1400                            |

| 1011                       | 1620                            |

| 1100                       | 1870                            |

| 1101                       | 2150                            |

| 1110                       | 2490                            |

| 1111                       | 2870                            |

A0 sets the four LSBs of the 6-bit device ID. A1 sets the two MSBs of the 6-bit device ID.

#### **PWM Clock and Synchronous Operation with Multiple Devices**

The PWM clock for the IC can be selected from the internal oscillator or from an external clock source driving the CLK pin. The CLK pin is bidirectional, allowing a single device to be the master clock, providing a common clock source to multiple devices. The PWM clock source and CLK pin direction are configured through PWM\_CLK[1:0] in the CNFG\_GEN (0x03) register. The default value is internal oscillator with the CLK pin disabled. For synchronous operation with multiple devices, use the PWM\_CLK\_SEL bits in the CNFG\_GEN (0x03) register to set the master with internal oscillator and CLK pin output, and the slave devices with external oscillator and CLK pin input.

The PWM dimming frequency is programmable by setting the value of the DIV[1:0] bits in the CNFG\_GEN (0x03) register, which sets the divide ratio for both the internal (16.384 MHz) and external clock sources.

The CLK output mode requires a pullup resistor from CLK to VDD because the CLK output is an open-drain output. The pullup strength depends on the desired UART frequency. A  $10k\Omega$  resistor pullup works for most frequencies. If 500k baud rate is needed, then a stronger pullup resistor, on the order of  $1k\Omega$ , is most likely required.

#### **Parallel Operation for Higher Current Applications**

The switches in the IC can handle current up to 0.75A (max); however, for applications that require higher currents, the switches can be configured in parallel. For example, if the current capability needs to be doubled with three LEDs, connect switch SW0 in parallel to SW3, SW1 in parallel to SW4, and SW2 in parallel to SW5. Make sure the switches connected in parallel have the same phase shift and PWM dimming duty cycles.

### **PWM Dimming**

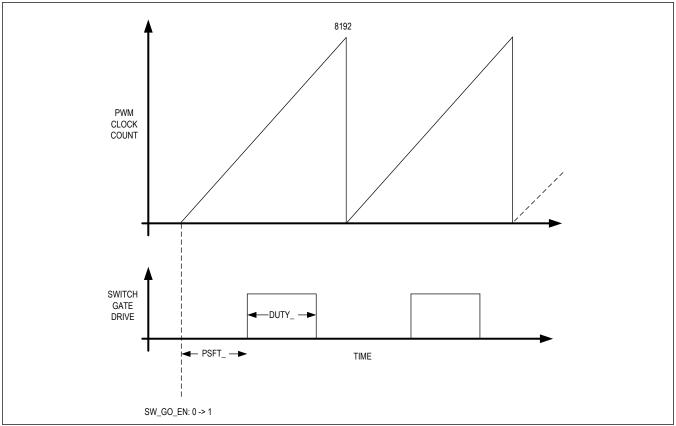

The IC provides 12-bit programmable dimming on each individual switch. An internal 12-bit counter (COUNT) is generated according to the clock settings. The switch turns off when COUNT is equal to the delay set by the corresponding PSFT register and stays off until the COUNT exceeds the sum of PSFT and PWM duty-control registers. In this way, the duty cycle and relative phase shift of the individual switches can be set independently.

Figure 1. PWM Phase and Duty Cycle Definitions

#### **Dimming With and Without Fade**

Each switch of the IC can be independently programmed to perform dimming without fade transition, or dimming with fade transition. For dimming without fade transition, the dimming changes from the initial value to the target value in one dimming cycle. For dimming with fade transition, the dimming changes transitionally step by step, starting from the initial value to the target value in multiple dimming cycles, following a predetermined exponential curve.

To enable dimming with fade transition, set the FADE bit to 1 and the DUTY bits to the target value for the specific switches. Each transitional step value is calculated using 12 bits according to the following formula:

DUTYnext = DUTYnow x CF

where DUTY is the duty cycle and CF is the constant factor

CF = 1.0625 and CF = 0.9375 for an up transition and down transition, respectively.

DUTYnext continues to be updated according to the formula until DUTYnext reaches the target value.

The transition period is defined by the TDIM\_ register for the switch. The number of transitional steps depends on the distance between the initial value and the target value. The maximum number of transitional steps from 1(/8191) to 8191(/8191) is 115 steps.

The number of transitional steps depends on the distance between the initial value and the target value. The maximum number of transitional steps from 8191(/8191) to 1(/8191) is 111 steps.

Duty-cycle steps smaller than CF update in one step.

Each step runs TDIM\_ PWM dimming cycles, and each dimming cycle consists of 8192 clock cycles by default; therefore Tstep = TDIM\_ x 8192. The 8192 clock cycles timer can also be changed to 16384, 32768, or 65536 clock cycles by

programming bits [3:2] in register address 0x02.

#### **LED Fault Detection and Protection**

The IC is able to detect a shorted LED, open LED, and open trace between the device and the LED. To detect and report a LED fault, several conditions must be met. First, the LED switch must be operating and LED-open and LED-short detection requires the switch to be open so the duty cycle must be greater than zero. Conversely, open-fault detection requires the switch to be closed so the PWM duty cycle must be less than 100%. In general, it takes up to one dimming cycle to make sure these conditions have been met after a fault condition is applied. This period depends on the PWM dimming frequency.

To ensure proper operation of the fault detection circuits, it is recommended to use a minimum PWM pulse width which is at least twice as long as the programmed slew rate.

#### **LED Short Threshold**

The LED short threshold is programmable to support single LED short detection for applications with 1, 2, or 3 LEDs per switch. The short threshold can be independently programmed for each group of three cascoded switches. The VSTH\_123 programs the short threshold for the three switches between DR3 and SRC1. The VSTH\_456 programs the short threshold for the three switches between DR6 and SRC4.

#### **UART Serial Interface**

#### Overview

The MAX25606 includes a full-duplex UART serial interface to enable fully programmable matrix manager functionality. The system ECU/MCU acts as the UART master, driving read/write packets on the RX line and receiving packets on the TX line. The RX and TX lines can connect up to 64 MAX25606 devices on a common bus using a star topology. The device address of each MAX25606 is pin-programmable using external resistors to ground on the A0 and A1 pins. Devices may be addressed individually using their Device ID[5:0]. They may also be simultaneously addressed using the General Call ID or by using the programmable Cluster Call ID value.

The baud rate of incoming UART packets on RX is automatically detected by the MAX25606, from a minimum of 10kbps up to a maximum of 500kbps. The MAX25606 then returns frames on the TX line at the same baud rate according to the packet format described below.

#### **Device Connections**

The UART interface ensures compatibility with standard microcontrollers from a variety of manufacturers. It also enables the use of CAN tranceivers for applications where the matrix manager is remote from the microcontroller. The RX line should be driven by the microcontroller master. It can be connected to an individual MAX25606 or to multiple devices in a star topology. The TX line is an open-drain output. Multiple devices can share the same TX connection as well. No external timing reference is required, the MAX25606 automatically detects the bit rate on each RX packet and adjusts the bit rate of the TX response accordingly.

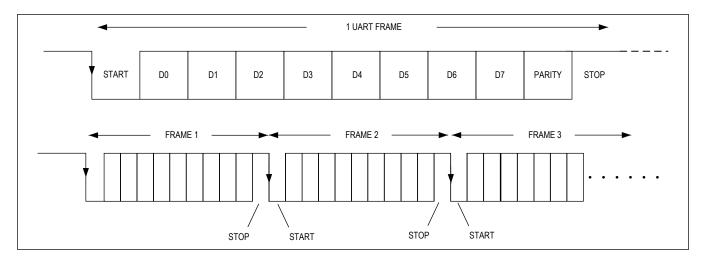

#### **UART Frame Format**

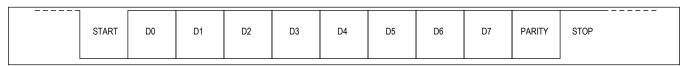

Read/write packets are composed from multiple UART frames. Each frame consists of 1 start bit, 8 data bits, 1 parity bit (even), and 1 stop bit. The parity bit should be high if the number of ones in the data bits is odd, otherwise it should be low. If the next frame is in the same packet, there can be no more than 12-bit periods of idle (high) state between frames.

#### **Synchronization and Acknowledge Frames**

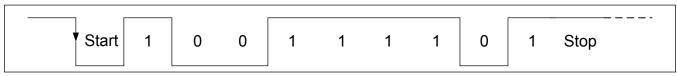

Each read/write packet must begin with a special Synchronization (SYNC) frame. This is a UART frame containing the data x79.

Figure 2. SYNC Frame

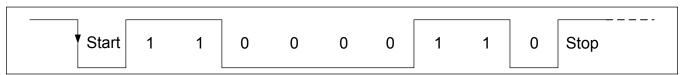

Each response packet always begins with a special Acknowledge (ACK) frame. This is a UART frame containing the data xC3.

Figure 3. ACK Frame

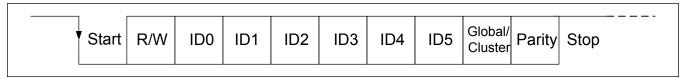

#### **Device ID and Address Frame Format**

Each MAX25606 device in the star configuration should be assigned a unique device ID number using resistors connected to the ADDR0 and ADDR1 pins. There are 64 possible device IDs that can be assigned in this way, from x00 to x3F. See MAX25606 Pin Resistor Decode Table.

In addition to addressing devices individually, the MAX25606 also supports Global Call and Cluster Call write commands. A Global write command addresses all devices on the bus. A Cluster call addresses all devices with a matching cluster call ID in the CNFG\_UART register. Read commands cannot use the Global/Cluster Call option and must be addressed to a specific device ID.

The address frame data bits are assigned as follows: the MSB is the Global/Cluster call bit. The next 6 bits are the device ID. The LSB is the Read/Write bit.

Figure 4. SYNC Frame

#### **Write Transactions**

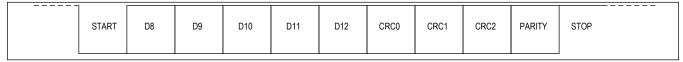

Each write packet consists of five UART frames on the RX pin. The first frame shall be the SYNC packet. The second frame consists of the Global/Cluster call flag, then the 6-bit device ID, and then the R/W bit. The R/W bit shall be low for a write command. The third frame shall be the register address being written to. The fourth frame shall be the lower byte of the data being written. The fifth and final frame shall include the 3-bit cyclic redundancy check (CRC) code followed by the upper 5 bits of the data being written. Upon receiving a valid write packet, the device responds with an ACK frame on the TX pin.

Fourth UART frame, lower 8 bits of data packet

Figure 5. SYNC Frame

Fifth UART frame, upper 5 bits of data packet + 3 bits of CRC

Figure 6. SYNC Frame

#### **CRC Error Checking**

Read/Write transactions are protected using a 3-bit CRC on the frame. The CRC is provided by the master on last three data bits of each UART\_RX packet. The MAX25606 calculates its own CRC using the same polynomial, and the transaction is only accepted if the CRC bits match. For response frames on read packets, the MAX25606 appends its own 3-bit CRC code to the 13-bit read data.

The input to the CRC calculation consists of the data bits from the device ID, address, and data frames.

The CRC calculation uses the polynomial  $x^3 + x^1 + 1$  with a starting value of 000.

#### **UART Watchdog Function**

The MAX25606 UART Watchdog feature sets the switches into a preconfigured state in the event of UART communication bus failures. If the EN\_WATCHDOG bit is set in the CNFG\_WATCHDOG register, the device asserts a UART\_WATCHDOG fault when the UART\_RX pin has been inactive for more than 4 seconds. When the UART\_WATCHDOG fault is set, the FLT output is asserted low and the state of the channel switches is set to the value of the WD\_LED\_STATE register. The default value of WD\_LED\_STATE is x00, which opens all six switches in the event of a watchdog fault. The fault can be masked by setting the MSK\_UART\_ERR bit in the CNFG\_MASK\_GEN register. The fault status is cleared by writing a 1 to the UART\_WATCHDOG bit. When the fault status is cleared, the switches resume operation according to the values of the PWM registers.

#### **UART Communication Error Handling**

In the event that the device receives a bad packet on UART\_RX, it asserts the relevant fault status bit in STAT\_UART and asserts the FLT output. The UART communications faults can be masked by setting the MSK\_UART\_ERR bit. Faults are cleared by writing 1 to the STAT\_UART bits. The following communications errors result in fault assertion:

- UART Watchdog timeout: UART RX stops transitioning for more than 4 seconds and EN WATCHDOG bit is set.

- UART\_RX timeout: UART\_RX stops transitioning for more than 16 bit lengths after a UART start bit has been received but before the end of a valid command sequence.

- RX CRC ERR: An invalid CRC code is detected on a UART transaction.

- RX\_SYNC\_PERR: parity error in the SYNC frame

- RX PL ERR: parity error in the payload frame

- RX\_STOP\_ERR: frame is missing the stop bit

#### **Thermal Protection**

The IC features an on-chip temperature-protection circuit to prevent the device from overheating.

When the die temperature rises above the thermal-warning threshold (+140°C), the TH\_WARN bit is set, causing the FLT pin to be asserted but no action is taken with the switches. To clear the TH\_WARN bit, a 1 must be written to the bit. If the die temperature is still above the threshold, the status bit is immediately set again.

When the die temperature rises above the thermal-shutdown threshold (+165°C), the TH\_SHDN bit is set, causing the FLT pin to be asserted and all switches to either be closed (LEDs turned off) or opened (LEDs turned on), depending on the value of the TH\_SHDN\_ACT register bit. Switches remain static and the FLT pin remains asserted until the fault status is cleared by writing 1 to the TH\_SHDN bit. If the die temperature is still above the threshold, the fault status is immediately set again.

When the device recovers from thermal shutdown, it resumes operation from where it was before the thermal shutdown. The TH WARN and TH SHDN bits are cleared by writing a 1.

#### **PWM Clock and Synchronous Operation with Multiple Devices**

The PWM clock for the IC can be selected from the internal oscillator or from an external clock source driving the CLK pin. The CLK pin is bidirectional, allowing a single device to be the master clock, providing a common clock source to multiple devices. The PWM clock source and CLK pin direction are configured through PWM\_CLK[1:0] in the CNFG\_GEN (0x03) register. The default value is internal oscillator with the CLK pin disabled. For synchronous operation with multiple devices, use the PWM\_CLK\_SEL bits in the CNFG\_GEN (0x03) register to set the master with internal oscillator and CLK pin output, and the slave devices with external oscillator and CLK pin input.

The PWM dimming frequency is programmable by setting the value of the DIV[1:0] bits in the CNFG\_GEN (0x03) register, which sets the divide ratio for both the internal (16.384MHz) and external clock sources.

The CLK output mode requires a pullup resistor from CLK to VDD because the CLK output is an open-drain output. The pullup strength depends on the desired UART frequency, a  $10k\Omega$  resistor pullup works for most frequencies. If 500k baud rate is needed, then  $1k\Omega$  or  $2k\Omega$  pullup may be better.

# **Register Map**

## MAX25606

| ADDRESS  | NAME                     | MSB             |                  |                        |                       |                       |                        |                                    | LSB                    |

|----------|--------------------------|-----------------|------------------|------------------------|-----------------------|-----------------------|------------------------|------------------------------------|------------------------|

| USER COM |                          |                 |                  |                        |                       |                       |                        |                                    |                        |

|          | NO OP[15:8]              |                 |                  |                        |                       |                       | REV_ID[4:0             | 1                                  |                        |

| 0x00     | NO OP[7:0]               | _               | _                | _                      |                       |                       | TANT_TES               |                                    |                        |

|          | SW_GO[15:8]              |                 | I                |                        | _                     | _                     | _                      | _                                  | _                      |

| 0x01     | SW_GO[7:0]               | _               | _                | _                      | _                     | _                     | _                      | _                                  | SW_GO<br>_EN           |

|          | CNFG_GEN[15:8]           |                 | I.               | L                      | V                     | STH_456[2:            | 0]                     | VSTH_                              | 123[2:1]               |

| 0x02     | CNFG_GEN[7:0]            | VSTH_1<br>23[0] | LE               | ED_SLEW[2              | ::0]                  | DIV                   | [1:0]                  | PWM_CLF                            | C_SEL[1:0]             |

| 0.00     | CNFG_UART[15:8]          |                 | I.               |                        | _                     | _                     | -                      | _                                  | _                      |

| 0x03     | CNFG_UART[7:0]           | _               | _                |                        |                       | CID                   | [5:0]                  |                                    |                        |

| 0.04     | CNFG_WATCHDOG[15:8]      |                 |                  | 1                      | EN_WAT<br>CHDOG       | _                     | -                      | _                                  | _                      |

| 0x04     | CNFG_WATCHDOG[7: 0]      | -               | _                |                        |                       | WD_LED_               | STATE[5:0]             |                                    |                        |

| 0.05     | CNFG_OPEN_OVRD[1<br>5:8] |                 |                  |                        | _                     | _                     | -                      | _                                  | _                      |

| 0x05     | CNFG_OPEN_OVRD[7:        | _               | _                |                        | OPEN_LED_OVR[5:0]     |                       |                        |                                    |                        |

| 0.00     | CNFG_GROUPA[15:8]        |                 |                  |                        | _                     | _                     | -                      | _                                  | _                      |

| 0x06     | 0x06                     |                 |                  |                        |                       | GROUPA                | _SEL[5:0]              |                                    |                        |

| 0.07     | CNFG_GROUPB[15:8]        |                 |                  |                        | _                     | _                     | _                      | _                                  | _                      |

| 0x07     | CNFG_GROUPB[7:0]         | _               | _                |                        |                       | GROUPB                | _SEL[5:0]              |                                    |                        |

|          | CNFG_MSK_GEN[15:8]       |                 |                  |                        | TH_SHD<br>N_ACT       | _                     | _                      | _                                  | _                      |

| 0x08     | CNFG_MSK_GEN[7:0]        | -               | MSK_UA<br>RT_ERR | MSK_OP<br>EN_TRA<br>CE | MSK_OP<br>EN_LED      | MSK_SH<br>ORT_LE<br>D | MSK_CP<br>_RDY_N       | MSK_RA<br>DC_ERR                   | MSK_TH<br>_WARN        |

| 0x09     | CNFG_MSK_LED[15:8]       |                 |                  |                        | _                     | _                     | _                      | _                                  | _                      |

| 0.03     | CNFG_MSK_LED[7:0]        | _               | _                |                        |                       | CNFG_MS               | K_LED[5:0]             |                                    |                        |

| 0x0A     | STAT_GEN[15:8]           |                 |                  |                        | _                     | _                     | -                      | CONFIG<br>_NOT_D<br>ONE            | RADC_E<br>RR           |

|          | STAT_GEN[7:0]            | EXT_CL<br>K_ERR | UART_E<br>RR     | OPEN_T<br>RACE         | OPEN_L<br>ED          | SHORT_<br>LED         | CP_RDY<br>_N           | TH_SHD<br>N                        | TH_WA<br>RN            |

|          | STAT_RADC[15:8]          |                 |                  |                        | _                     | _                     | _                      | _                                  | _                      |

| 0x0B     | STAT_RADC[7:0]           | _               | RADC_D<br>ONE    | R2_OVE<br>R_RANG<br>E  | R1_OVE<br>R_RANG<br>E | R0_OVE<br>R_RANG<br>E | R2_UND<br>ER_RAN<br>GE | RES1_U<br>NDR1_U<br>NDER_R<br>ANGE | R0_UND<br>ER_RAN<br>GE |

| 0x0C     | STAT_RES_CODE[15:8       |                 |                  | 1                      | _                     |                       | R2_C0                  | DE[3:0]                            | •                      |

|          | STAT_RES_CODE[7:0]       |                 | R1_C0            | DE[3:0]                | 1                     |                       | R0_CO                  | DE[3:0]                            |                        |

| ADDRESS | NAME                     | MSB                    |                |                  |                  |                          |                        |                         | LSB                   |

|---------|--------------------------|------------------------|----------------|------------------|------------------|--------------------------|------------------------|-------------------------|-----------------------|

| 0x0D    | STAT_UART[15:8]          | -                      |                |                  | _                | _                        | _                      | _                       | UART_<br>WATCH<br>DOG |

| OXOD    | STAT_UART[7:0]           | RX_TIM<br>EOUT_E<br>RR | RX_CRC<br>_ERR | RX_SYN<br>C_PERR | RX_PL_<br>PERR   | RX_SYN<br>C_STOP<br>_ERR | RX_PL_<br>STOP_E<br>RR | RX_PL_<br>START_<br>ERR | _                     |

| 0x0E    | STAT_SHORT_LED[15:<br>8] |                        |                |                  | _                | _                        | _                      | _                       | _                     |

| UXUE    | STAT_SHORT_LED[7:0       |                        |                |                  |                  | SHORT_LE                 | D_STAT[5:0             | )]                      |                       |

| 0x0F    | STAT_OPEN_LED[15:8]      |                        |                |                  | _                | _                        | _                      | _                       | _                     |

|         | STAT_OPEN_LED[7:0]       | -                      | _              |                  |                  | OPEN_LED                 | STAT[5:0]              |                         |                       |

| 0v10    | STAT_OPEN_TRACE[1 5:8]   |                        |                |                  | _                | _                        | _                      | _                       | _                     |

| 0x10    | STAT_OPEN_TRACE[7 :0]    | _                      | _              |                  | С                | PEN_TRAC                 | CE_STAT[5:             | 0]                      |                       |

| 0x11    | PSFT_GRP[15:8]           |                        |                |                  | _                | -                        | _                      | PSFT_GF                 | ROUP[1:0]             |

| UXII    | PSFT_GRP[7:0]            |                        |                |                  | PSF <sup>-</sup> | Γ[7:0]                   |                        |                         |                       |

| 0x12    | PSFT_0[15:8]             |                        |                |                  | _                | -                        | _                      | -                       | _                     |

| UX1Z    | PSFT_0[7:0]              | PSFT_0[7:0]            |                |                  |                  |                          |                        |                         |                       |

| 0x13    | PSFT_1[15:8]             |                        |                |                  | _                | -                        | _                      | -                       | _                     |

| UXIS    | PSFT_1[7:0]              |                        |                |                  | PSFT_            | _1[7:0]                  |                        |                         |                       |

| ()x14 ⊢ | PSFT_2[15:8]             |                        |                |                  | _                | -                        | -                      | -                       | _                     |

| UX 14   | PSFT_2[7:0]              |                        |                |                  | PSFT_            | _2[7:0]                  |                        |                         |                       |

| 0x15    | PSFT_3[15:8]             |                        |                |                  | _                | _                        | _                      | _                       | _                     |

| UXIS    | PSFT_3[7:0]              |                        |                |                  | PSFT_            | _3[7:0]                  |                        |                         |                       |

| 0x16    | PSFT_4[15:8]             |                        |                |                  | _                | _                        | _                      | _                       | _                     |

| 0.00    | PSFT_4[7:0]              |                        |                |                  | PSFT_            | _4[7:0]                  |                        |                         |                       |

| 0x17    | PSFT_5[15:8]             |                        |                |                  | _                | _                        | _                      | _                       | _                     |

| UX17    | PSFT_5[7:0]              |                        |                |                  | PSFT_            | _5[7:0]                  |                        |                         |                       |

| 0x18    | TDIM_GRP[15:8]           |                        |                |                  | _                | _                        | _                      | _                       | _                     |

| 0.00    | TDIM_GRP[7:0]            | -                      | _              | TDIM_GF          | ROUP[1:0]        | _                        |                        | TDIM[2:0]               |                       |

| 0x19    | TDIM_2_1_0[15:8]         |                        |                |                  | _                | _                        |                        | TDIM_2[2:0              | ]                     |

| 0.13    | TDIM_2_1_0[7:0]          | -                      |                | TDIM_1[2:0       | ]                | _                        |                        | TDIM_0[2:0              | ]                     |

| 0x1A    | TDIM_5_4_3[15:8]         |                        |                |                  | _                | _                        |                        | TDIM_5[2:0              | ]                     |

| UXIA    | TDIM_5_4_3[7:0]          | -                      |                | TDIM_4[2:0       | ]                | _                        |                        | TDIM_3[2:0              | ]                     |

| 0x1B    | PWM_GRPA_DUTY[15: 8]     | 5: FADE_A DUTY_A[1     |                |                  |                  |                          | A[11:8]                |                         |                       |

| OVID    | PWM_GRPA_DUTY[7:0]       |                        |                |                  | DUTY             | _A[7:0]                  |                        |                         |                       |

| 0.40    | PWM_GRPB_DUTY[15: 8]     |                        |                |                  | FADE_B           |                          | DUTY_                  | B[11:8]                 |                       |

| 0x1C    | PWM_GRPB_DUTY[7:0        |                        |                |                  | DUTY             | _B[7:0]                  |                        |                         |                       |

| 0x1D    | PWM0[15:8]               |                        |                |                  | FADE_0           |                          | DUTY                   | 0[11:8]                 |                       |

|         |                          |                        |                |                  |                  |                          |                        |                         |                       |

| ADDRESS | NAME       | MSB         |                     |        |         |       |          | LSB |  |

|---------|------------|-------------|---------------------|--------|---------|-------|----------|-----|--|

|         | PWM0[7:0]  |             | ·                   | DUTY   | _0[7:0] |       |          |     |  |

| 0x1E    | PWM1[15:8] |             | FADE_1 DUTY_1[11:8] |        |         |       |          |     |  |

| UXIE    | PWM1[7:0]  |             | ,                   | DUTY   | _1[7:0] |       |          |     |  |

| 0x1F    | PWM2[15:8] |             | FADE_2 DUTY_2[11:8] |        |         |       |          |     |  |

| UXIF    | PWM2[7:0]  |             | •                   | DUTY   | _2[7:0] |       |          |     |  |

| 0x20    | PWM3[15:8] |             | 1                   | FADE_3 |         | DUTY_ | 3[11:8]  |     |  |

| UX2U    | PWM3[7:0]  |             | DUTY_3[7:0]         |        |         |       |          |     |  |

| 0.21    | PWM4[15:8] |             | 1                   | FADE_4 |         | DUTY_ | _4[11:8] |     |  |

| 0x21    | PWM4[7:0]  | DUTY_4[7:0] |                     |        |         |       |          |     |  |

| 0,422   | PWM5[15:8] |             | FADE_5 DUTY_5[11:8] |        |         |       |          |     |  |

| 0x22    | PWM5[7:0]  |             | DUTY_5[7:0]         |        |         |       |          |     |  |

## **Register Details**

## NO\_OP (0x00)

NO OP is a read-only register that reads the content of RGRADE, revision ID, and test pattern.

| BIT            |             |   |   | 12        | 11 | 10          | 9     | 8 |  |  |

|----------------|-------------|---|---|-----------|----|-------------|-------|---|--|--|

| Field          | REV_ID[4:0] |   |   |           |    |             | •     |   |  |  |

| Reset          |             |   |   |           |    | 0b00000     |       |   |  |  |

| Access<br>Type |             |   |   | Read Only |    |             |       |   |  |  |

| BIT            | 7           | 6 | 5 | 4         | 3  | 2           | 1     | 0 |  |  |

| Field          | _           | - | _ |           | CC | NSTANT_TEST | [4:0] | • |  |  |

| Reset          | _           | - | _ | 0b10001   |    |             |       |   |  |  |

| Access<br>Type | _           | _ | _ | Read Only |    |             |       |   |  |  |

| BITFIELD      | BITS | DESCRIPTION                                                                    |  |  |  |  |

|---------------|------|--------------------------------------------------------------------------------|--|--|--|--|

| REV_ID 12:8 F |      | Revision Information: Reads back 5-bit hardware revision ID.                   |  |  |  |  |

| CONSTANT_TEST | 4:0  | Test Pattern: 0x11 is always returned in this location for interface checking. |  |  |  |  |

## SW\_GO (0x01)

SW\_GO us a read/write register that enables the PWN signals.

| BIT            |   |   |   | 12 | 11 | 10 | 9 | 8            |

|----------------|---|---|---|----|----|----|---|--------------|

| Field          |   |   |   | _  | _  | _  | _ | _            |

| Reset          |   |   |   | _  | _  | _  | _ | _            |

| Access<br>Type |   |   |   | _  | -  | _  | _ | _            |

| BIT            | 7 | 6 | 5 | 4  | 3  | 2  | 1 | 0            |

| Field          | _ | _ | _ | _  | _  | _  | _ | SW_GO_E<br>N |

| Reset          | _ | _ | _ | _  | _  | _  | _ | 0b0          |

| Access<br>Type | - | _ | - | _  | _  | _  | _ | Write, Read  |

| BITFIELD | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DECODE                                                                                                                                                                                 |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SW_GO_EN | 0    | Switching Enable signal. Enables LED dimming operation and starts dimming counters. If SW_GO_EN = 0, all LED switches are closed and all PWM counters in the LED Controller are reset to 0. If SW_GO_EN = 1, all LED switches operate according to their programmed values and all PWM counters start counting from 0.  The SW_GO_EN command should be issued after CP_RDY_N transitions low on STAT_GEN, ensuring CLK is present and CPP voltage is valid. | 0x0: All LED switches are closed, and all PWM counters are reset to 0. 0x1: All LED switches operate according to their programmed values, and all PWM counters start counting from 0. |

## CNFG\_GEN (0x02)

CNFG\_GEN is a read/write access register that controls the dimming clock divider ratio, the slew rate of the LED switches, the threshold used for the short-LED fault-detection function, and the functionality of the CLK pin.

| BIT            |                 |   |              | 12 | 11            | 10    | 9                | 8             |  |

|----------------|-----------------|---|--------------|----|---------------|-------|------------------|---------------|--|

| Field          |                 |   |              |    | VSTH_456[2:0] |       |                  | VSTH_123[2:1] |  |

| Reset          |                 |   |              |    |               |       |                  |               |  |

| Access<br>Type |                 |   |              |    | Write, Read   |       | Write,           | Write, Read   |  |

| BIT            | 7               | 6 | 5            | 4  | 3             | 2     | 1                | 0             |  |

| Field          | VSTH_123[<br>0] | I | _ED_SLEW[2:0 | ]  | DIV           | [1:0] | PWM_CLK_SEL[1:0] |               |  |

| Reset          |                 |   | 0b000        |    | Ob            | 000   | 0b00             |               |  |

| Access<br>Type | Write, Read     |   | Write, Read  |    | Write         | Read  | Write, Read      |               |  |

| BITFIELD | BITS  | DESCRIPTION                                                | DECODE                                                                                           |

|----------|-------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| VSTH_456 | 12:10 | Sets the Short LED Threshold value for Switches 4,5 and 6. | 0x0: 1.4V<br>0x1: 3.6V<br>0x2: 4V<br>0x3: 5.5V<br>0x4: 6V<br>0x5: 6.6V<br>0x6: 7.2V<br>0x7: 7.7V |

| VSTH_123 | 9:7   | Sets the Short LED Threshold value for Switches 1,2 and 3. | 0x0: 1.4V<br>0x1: 3.6V<br>0x2: 4V<br>0x3: 5.5V<br>0x4: 6V<br>0x5: 6.6V<br>0x6: 7.2V<br>0x7: 7.7V |

| BITFIELD        | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                            | DECODE                                                                                                                                                                           |

|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED_SLEW        | 6:4  | Slew Control for the Internal LED Gate Driver: Updating the LED gate-driver slews can take time, up to a full PWM dimming cycle; therefore, consecutive writes to LED_SLEW should be at least 1 dimming cycle apart in time. In most cases, this register is set only once, prior to setting SW_GO_EN. | 0x0: 10µs<br>0x1: 6.67µs<br>0x2: 5.0µs<br>0x3: 3.3µs<br>0x4: 2.5µs<br>0x5: 1.5µs<br>0x6: 1.0µs<br>0x7: 0.5µs                                                                     |

| DIV             | 3:2  | PWM Dimming-Frequency Select. The PWM dimming clock frequency, fpwm, is divided down from fosc by the chosen divider value. fosc can either be the internal oscillator clock or the external oscillator clock, depending on the PWM_CLK_SEL bit setting.                                               | 0x0: fpwm = fosc / 8192<br>0x1: fpwm = fosc / 16384<br>0x2: fpwm = fosc / 32768<br>0x3: fpwm = fosc / 65536                                                                      |

| PWM_CLK_<br>SEL | 1:0  | Determines internal/external PWM clock and direction of CLK pin.                                                                                                                                                                                                                                       | 0x0: Internal OSC, CLK pin disabled (default). 0x1: Internal OSC, CLK pin output. 0x2: External OSC, CLK pin input.[1 - 20Mhz clk] 0x3: External OSC, CLK pin input.[120Mhz clk] |

## CNFG\_UART (0x03)

CNFG\_UART is a read/write access register that controls the cluster ID assignment.

| BIT            |   |   |          | 12          | 11  | 10    | 9 | 8 |  |  |

|----------------|---|---|----------|-------------|-----|-------|---|---|--|--|

| Field          |   |   |          | _           | _   | _     | _ | _ |  |  |

| Reset          |   |   |          | _           | -   | _     | _ | _ |  |  |

| Access<br>Type |   |   |          | _           | _   | _     | _ | - |  |  |

| BIT            | 7 | 6 | 5        | 4           | 3   | 2     | 1 | 0 |  |  |

| Field          | _ | _ |          |             | CID | [5:0] |   |   |  |  |

| Reset          | _ | _ | 0b000001 |             |     |       |   |   |  |  |

| Access<br>Type | - | _ |          | Write, Read |     |       |   |   |  |  |

| BITFIELD | BITS | DESCRIPTION                                                                                                                                                       |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CID      | 5:0  | Cluster Identification: During a cluster call write transaction, the UART accepts the transaction if the received CID[5:0] matches the contents of this register. |

## CNFG\_WATCHDOG (0x04)

| BIT            | 12              | 11 | 10 | 9 | 8 |

|----------------|-----------------|----|----|---|---|

| Field          | EN_WATC<br>HDOG | -  | _  | - | - |

| Reset          |                 | _  | _  | _ | _ |

| Access<br>Type | Write, Read     | -  | -  | - | _ |

| BIT            | 7 | 6 | 5                 | 4 | 3      | 2    | 1 | 0 |  |

|----------------|---|---|-------------------|---|--------|------|---|---|--|

| Field          | _ | _ | WD_LED_STATE[5:0] |   |        |      |   |   |  |

| Reset          | _ | _ |                   |   |        |      |   |   |  |

| Access<br>Type | _ | _ |                   |   | Write, | Read |   |   |  |

| BITFIELD         | BITS | DESCRIPTION                                                                                                                                                                      | DECODE                                                         |