## **STA8090FG**

# Fully integrated GPS/Galileo/GLONASS/BeiDou/QZSS receiver with embedded RF and in-package Flash

Datasheet - production data

#### **Features**

- STMicroelectronics positioning receiver with 48 tracking channels and 2 fast acquisition channels supporting GPS, Galileo, GLONASS, BeiDou and QZSS systems

- Single die standalone receiver embedding RF Front-End and low noise amplifier

- -162 dBm indoor sensitivity (tracking mode)

- Fast TTFF < 1 s in Hot start and 30 s in Cold Start

- High performance ARM946 MCU (up to 196 MHz)

- 256 Kbyte embedded SRAM

- In-Package SQI Flash Memory (16 or 32 Mbits)

- · Real Time Clock (RTC) circuit

- · 32-bit Watch-dog timer

- 3 UARTs

- 1 I<sup>2</sup>C master interface

- 1 Synchronous Serial Port (SSP, Motorola-SPI supported)

- USB2.0 full speed (12 MHz) with integrated physical layer transceiver

- 2 Controller Area Network (CAN)

- 2 channels ADC (10 bits)

- 1 Secure-Digital Multimedia Memory Card Interfaces (SDMMC)

- 1 Multichannel Serial Port (MSP)

- Power Management Unit (PMU) embedding switching regulator

- Operating condition:

- Main voltage regulator (V<sub>INL</sub>): 1.6V to 4.3V

- Backup voltage (V<sub>INB</sub>): 1.6V to 4.3V

- Digital voltage (V<sub>DD</sub>): 1.0 V to 1.32 V

- RF core voltage ( $V_{CC}$ ): 1.2 V ± 10%

- IO Ring Voltage (V<sub>ddIO</sub>): 1.8 V ± 5% or 3.3 V ± 10%

- Package:

- TFBGA99 (5 x 6 x 1.2 mm) 0.5 mm pitch

- Operating temperature range: -40/+85°C

### **Description**

STA8090FG belongs to Teseo III family products. STA8090FG is a single die standalone positioning receiver IC working on multiple constellations (GPS/Galileo/GLONASS/BeiDou/QZSS).

STA8090FG, thanks to the ARM9 and wide IOs availability, can be used as microcontroller with GNSS capability, allowing a very compact design offering 256 kByte of internal RAM and 16 Mbits or 32 Mbits of internal Flash.

The minimal BOM makes STA8090FG the ideal solution for cost competitive and small footprint products such as OBD dongle, insurance boxes, trackers, telematics, portable, hands-held portable and sports accessories.

STA8090FGBD can also run TESEO-DRAW the STMicroelectronics dead reckoning firmware.

Table 1. Device summary

| Root Part Number | Package        | Packaging     |

|------------------|----------------|---------------|

| STA8090FG        | TFBGA99 5x 6mm | Tape and Reel |

STA8090FG Contents

# **Contents**

| 1 | Ove   | view                         |                               |

|---|-------|------------------------------|-------------------------------|

| 2 | Pin ( | escription                   |                               |

|   | 2.1   | Block diagram                |                               |

|   | 2.2   | TFBGA99 pin configuration    |                               |

|   | 2.3   | Power supply pins            |                               |

|   | 2.4   | Main function pins           |                               |

|   | 2.5   | Test/emulated dedicated pins |                               |

|   | 2.6   | Communication interface pins |                               |

|   | 2.7   |                              |                               |

|   | 2.8   | General purpose pins         |                               |

|   | 2.9   |                              |                               |

| 3 | Gen   | ral description              |                               |

|   | 3.1   | RF front end                 |                               |

|   | 3.2   | GPS/Galileo/GLONASS/BeiDou B | ase Band (G3BB+) processor 18 |

|   | 3.3   | MCU Subsystem                |                               |

|   |       | 3.3.1 AHB slaves             |                               |

|   | 3.4   | APB peripherals              |                               |

|   |       | 3.4.1 CAN                    | 20                            |

|   |       | 3.4.2 SSP                    | 20                            |

|   |       | 3.4.3 UART                   |                               |

|   |       |                              |                               |

|   |       |                              |                               |

|   |       |                              | 22                            |

|   |       |                              | 22                            |

|   |       |                              |                               |

|   |       |                              |                               |

|   |       |                              | 23                            |

| 4 | Elec  | rical characteristics        |                               |

|   | 4.1   | Parameter conditions         | 24                            |

|   |       | DS10719 Rev 6                | 3/41                          |

|   |       | 20.0.101101                  | 5/11                          |

|   | 4.2  | Minim    | um and maximum values                  |

|---|------|----------|----------------------------------------|

|   | 4.3  | Typica   | ıl values                              |

|   | 4.4  | Typica   | ll curves                              |

|   | 4.5  | Absolu   | ute maximum ratings                    |

|   | 4.6  | Recon    | nmended DC operating conditions        |

|   | 4.7  | DC ch    | aracteristics                          |

|   | 4.8  | AC ch    | aracteristics                          |

|   |      | 4.8.1    | RF electrical specifications           |

|   |      | 4.8.2    | Oscillator electrical specifications   |

|   |      | 4.8.3    | OSCI oscillator specifications         |

|   |      | 4.8.4    | ADC specifications                     |

|   |      | 4.8.5    | Flash specifications                   |

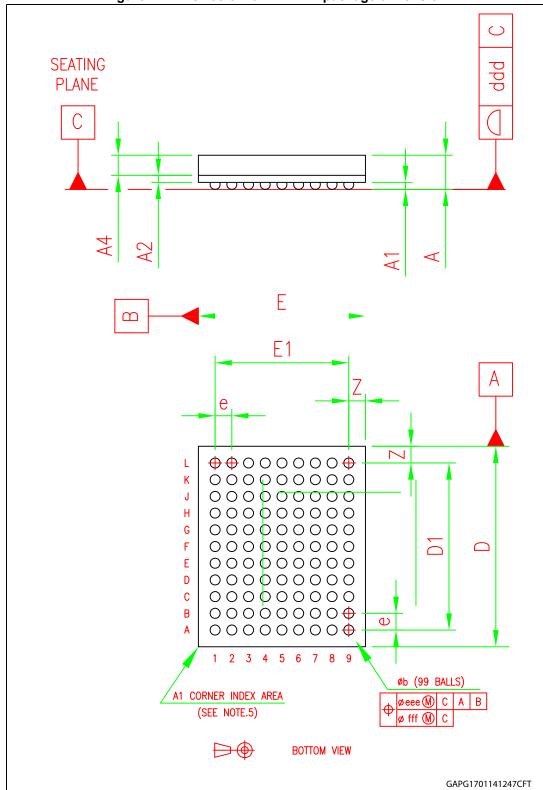

| 5 | Pack | age an   | d packing information                  |

|   | 5.1  | ECOP     | ACK packages                           |

|   | 5.2  | TFBG     | A99 5 x 6 x 1.2 mm package information |

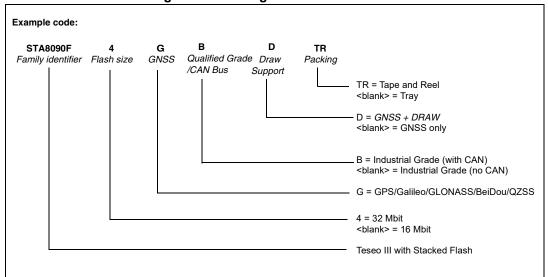

| 6 | Orde | ering in | formation                              |

| 7 | Revi | sion his | story                                  |

STA8090FG List of tables

# List of tables

| Table 1.  | Device summary                               | 2    |

|-----------|----------------------------------------------|------|

| Table 2.  | TFBGA99 connection diagram (with CAN)        |      |

| Table 3.  | TFBGA99 connection diagram (no CAN)          |      |

| Table 4.  | Power supply pins                            | . 10 |

| Table 5.  | Main function pins                           | . 11 |

| Table 6.  | Test/emulated dedicated pins                 | . 12 |

| Table 7.  | Communication interface pins                 |      |

| Table 8.  | Multimedia card pins                         | . 15 |

| Table 9.  | General purpose pins                         | . 16 |

| Table 10. | RF Front-end pins                            | . 17 |

| Table 11. | TCM Configuration                            | . 19 |

| Table 12. | Voltage characteristics                      | . 24 |

| Table 13. | Thermal characteristics                      | . 25 |

| Table 14. | Frequency limits                             | . 25 |

| Table 15. | Power consumption                            |      |

| Table 16. | Recommended DC operating conditions          | . 26 |

| Table 17. | SMPS DC characteristics                      |      |

| Table 18. | LDO1 DC characteristics                      | . 28 |

| Table 19. | LDO2 DC characteristics                      | . 28 |

| Table 20. | Low voltage detection thresholds             | . 28 |

| Table 21. | I/O buffers DC characteristics               | . 29 |

| Table 22. | 1.0 V I/O buffers DC characteristics         |      |

| Table 23. | RFACHAIN – GALGPS filter and VGA             |      |

| Table 24. | RFCHAIN – GLONASS/BeiDou filter and VGA      |      |

| Table 25. | Synthesizer                                  |      |

| Table 26. | Crystal recommended specifications           | . 32 |

| Table 27. | Oscillator amplifier specifications          |      |

| Table 28. | Characteristics of external slow clock input |      |

| Table 29. | SARADC specifications                        | . 34 |

| Table 30. | Flash specifications                         | . 35 |

| Table 31. | TFBGA99 package dimensions                   |      |

| Table 32. | Document revision history                    | . 39 |

DS10719 Rev 6 5/41

List of figures STA8090FG

# List of figures

| Figure 1. | STA8090FG system block diagram           | . 8 |

|-----------|------------------------------------------|-----|

| Figure 2. | 32.768 kHz crystal connection            | 33  |

| Figure 3. | SARADC connections                       | 34  |

| Figure 4. | TFBGA99 5 x 6 x 1.2 mm package dimension | 37  |

| Figure 5. | Ordering information scheme              | 38  |

47/

STA8090FG Overview

#### 1 Overview

STA8090FG is one of the part number of Teseo III STA8090x series.

STA8090FG is a highly integrated single-chip standalone GNSS receiver designed for positioning system applications.

STA8090FG embeds the new ST GNSS positioning engine capable of receiving signals from multiple satellite navigation systems, including the US GPS, European Galileo, Russia's GLONASS, Chinese BeiDou and Japan's QZSS.

The STA8090FG ability of tracking simultaneously the signals from multiple satellites regardless of their constellation, makes this chip capable of delivering exceptional accuracy in urban canyons and in the environments where buildings and other obstructions make satellite visibility challenging.

STA8090FG embeds innovative power management with switching regulator for power consumption optimization.

The extended voltage supply ranges from 1.6 V to 4.3 V, the 1.8 V and 3.3 V I/O compliance support makes the STA8090FG the suitable solution for different user applications.

The STA8090FG combines a high performance ARM946 microprocessor with I/O capabilities and enhanced peripherals. It supports USB2.0 standard at full speed (12 Mbps) with on-chip PHY.

The chip embeds backup logic with real time clock.

STA8090FG can host customer code on top of STMicroelectronics GNSS library.

Customers can develop on TeseoIII their application code by using a software development kit based on different real time operating systems.

STA8090FGBD can be offered also bundled with STMicroelectronics dead reckoning firmware called TESEO-DRAW; TESEO-DRAW firmware is a multi-sensors data fusion hub for Teseo family IC's.

The STA8090FG, using STMicroelectronics CMOSRF Technology, is housed in a TFBGA99 (5 x 6 x 1.2 mm) package with stacked 16 Mbit or 32 Mbit Flash memory.

DS10719 Rev 6 7/41

Downloaded from **Arrow.com**.

Pin description STA8090FG

# 2 Pin description

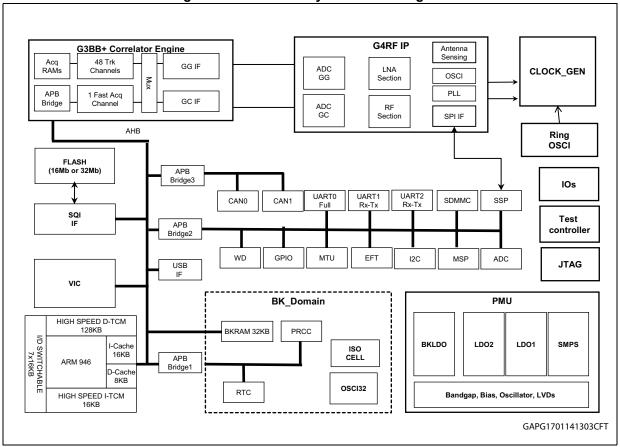

## 2.1 Block diagram

Figure 1. STA8090FG system block diagram

57/

STA8090FG Pin description

# 2.2 TFBGA99 pin configuration

Table 2. TFBGA99 connection diagram (with CAN)

|   | 1       | 2            | 3       | 4             | 5             | 6             | 7             | 8              | 9              |

|---|---------|--------------|---------|---------------|---------------|---------------|---------------|----------------|----------------|

| Α | VINM    | VINM         | SPI_CLK | SPI_CSN       | VINL1         | VOL1          | GND           | VINB           | VOB            |

| В | VLX     | VLX          | SPI_DI  | UART0_<br>TX  | UART0_<br>CTS | UART2_<br>RX  | GPIO1         | GPIO0          | GND            |

| С | GND     | GND          | SPI_DO  | VDDIO_<br>R1  | UART2_<br>TX  | UART0_<br>RTS | VDD_SQI       | VDD_<br>ADC    | Reserved       |

| D | VOM     | GND          | TMS     | UART0_<br>DSR | UART0_<br>DTR | GND           | ADC_IN2       | GND            | RTC_XTO        |

| E | VDD_ANA | TDO          | TRSTn   | UART0_<br>DCD | VDDD          | UART0_<br>RX  | ADC_IN1       | WAKEUP0        | RTC_XTI        |

| F | GND     | TDI          | VDDD    | VDDD          | GND           | GND           | WAKEUP1       | STDBYn         | RSTn           |

| G | USB_DP  | TCK          | VDDD    | GND           | GND           | GND           | STDBY_<br>OUT | PMU_<br>CFG    | XTAL_<br>OUT   |

| н | USB_DM  | GPIO10       | MMC_D3  | MMC_<br>CLK   | TP_IF_N       | GND           | GND           | VCC_PLL        | XTAL_IN        |

| J | CAN0_TX | GPIO11       | MMC_D2  | MMC_<br>CMD   | TP_IF_P       | GND           | GND           | ANT_<br>SENSE2 | VCC_<br>CHAIN  |

| K | CAN0_RX | VDDIO_<br>R2 | GPIO2   | MMC_D1        | GND_LNA       | GND_LNA       | GND_LNA       | GND            | ANT_<br>SENSE1 |

| L | GND     | I2C_SD       | I2C_CLK | MMC_D0        | VCC_RF        | LNA_IN        | VOL2          | VINL2          | GND            |

Pin description STA8090FG

Table 3. TFBGA99 connection diagram (no CAN)

|   | 1            | 2            | 3       | 4             | 5             | 6             | 7             | 8              | 9              |

|---|--------------|--------------|---------|---------------|---------------|---------------|---------------|----------------|----------------|

| Α | VINM         | VINM         | SPI_CLK | SPI_CSN       | VINL1         | VOL1          | GND           | VINB           | VOB            |

| В | VLX          | VLX          | SPI_DI  | UART0_<br>TX  | UART0_<br>CTS | UART2_<br>RX  | GPIO1         | GPIO0          | GND            |

| С | GND          | GND          | SPI_DO  | VDDIO_<br>R1  | UART2_<br>TX  | UART0_<br>RTS | VDD_SQI       | VDD_<br>ADC    | Reserved       |

| D | VOM          | GND          | TMS     | UART0_<br>DSR | UART0_<br>DTR | GND           | ADC_IN2       | GND            | RTC_XTO        |

| E | VDD_ANA      | TDO          | TRSTn   | UART0_<br>DCD | VDDD          | UART0_<br>RX  | ADC_IN1       | WAKEUP0        | RTC_XTI        |

| F | GND          | TDI          | VDDD    | VDDD          | GND           | GND           | WAKEUP1       | STDBYn         | RSTn           |

| G | USB_DP       | TCK          | VDDD    | GND           | GND           | GND           | STDBY_<br>OUT | PMU_<br>CFG    | XTAL_<br>OUT   |

| н | USB_DM       | GPIO10       | MMC_D3  | MMC_<br>CLK   | TP_IF_N       | GND           | GND           | VCC_PLL        | XTAL_IN        |

| J | UART0_<br>TX | GPIO11       | MMC_D2  | MMC_<br>CMD   | TP_IF_P       | GND           | GND           | ANT_<br>SENSE2 | VCC_<br>CHAIN  |

| K | UART0_<br>RX | VDDIO_<br>R2 | GPIO2   | MMC_D1        | GND           | GND           | GND           | GND_LNA        | ANT_<br>SENSE1 |

| L | GND          | I2C_SD       | I2C_CLK | MMC_D0        | VCC_RF        | LNA_IN        | VOL2          | VINL2          | GND            |

## 2.3 Power supply pins

Table 4. Power supply pins

| Symbol    | I/O voltage    | I/O | Description                                            | STA8090FG      |

|-----------|----------------|-----|--------------------------------------------------------|----------------|

| VCC_CHAIN | 1.2 V          | PWR | Analog supply voltage for RF chain (1.2V)              | J9             |

| VCC_PLL   | 1.2 V          | PWR | Analog supply voltage for PLL RF (1.2V)                | H8             |

| VCC_RF    | 1.2 V          | PWR | Analog supply voltage for RF (1.2V)                    | L5             |

| VDD_ADC   | 1.8 V          | PWR | Digital supply voltage for ADC (1.8V)                  | C8             |

| VDD_SQI   | 1.8 V          | PWR | Digital supply voltage for SQI                         | C7             |

| VDDD      | 1.1 V          | PWR | Digital supply voltage                                 | E5, F3, F4, G3 |

| VDDIO_R1  | 1.8 V or 3.3 V | PWR | Digital supply voltage for I/O ring 1 (1.8 V or 3.3 V) | C4             |

| VDDIO_R2  | 3.3V           | PWR | Digital supply voltage for I/O ring 2 (3.3 V)          | K2             |

| VINB      | 1.6 V - 4.3 V  | PWR | Backup LDO input supply voltage (1.6 V to 4.3 V)       | A8             |

| VINL1     | 1.6 V - 4.3 V  | PWR | LDO1 input supply voltage (1.6 V to 4.3 V)             | A5             |

| VINL2     | 1.6 V - 4.3 V  | PWR | LDO2 input supply voltage (1.6 V to 4.3 V)             | L8             |

STA8090FG Pin description

Table 4. Power supply pins (continued)

| Symbol  | I/O voltage    | I/O | Description                                                                                                | STA8090FG                                                                                     |

|---------|----------------|-----|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| VINM    | 1.6 V - 4.3 V  | PWR | SMPS coil input supply (1.6 V to 4.3 V)                                                                    | A1, A2                                                                                        |

| VDD_ANA | 1.6 V - 4.3 V  | PWR | SMPS input supply (1.6 V to 4.3 V)                                                                         | E1                                                                                            |

| VLX     | 0 V - 4.3 V    | PWR | SMPS coil output                                                                                           | B1, B2                                                                                        |

| VOB     | 1.0V           | PWR | LDO backup output voltage (1.0 V)                                                                          | A9                                                                                            |

| VOL1    | 1.1 V or 1.8 V | PWR | LDO1 output voltage:  PMU_CFG = high -> 1.1 V (it can be also configured to 1.2 V)  PMU_CFG = low -> 1.8 V | A6                                                                                            |

| VOL2    | 1.2 V          | PWR | LDO2 output voltage (1.2 V)                                                                                | L7                                                                                            |

| VOM     | 1.1 V or 1.8 V | PWR | SMPS output voltage PMU_CFG = high -> 1.8 V PMU_CFG = low -> 1.1 V (it can be also configured to 1.2 V)    | D1                                                                                            |

| GND     | GND            | GND | Ground                                                                                                     | A7, B9, C1,<br>C2, D2, D6,<br>D8, F1, F5, F6,<br>G4, G5, G6,<br>H6, H7, J6, J7,<br>K8, L1, L9 |

| GND_LNA | GND            | GND | Ground                                                                                                     | K5, K6, K7                                                                                    |

# 2.4 Main function pins

**Table 5. Main function pins**

| Symbol    | I/O voltage              | I/O | Description                                                                                                        | STA8090FG |

|-----------|--------------------------|-----|--------------------------------------------------------------------------------------------------------------------|-----------|

| ADC_IN1   | 1.4 V – 0 V typ<br>range | I   | ADC Analog input [1]                                                                                               | E7        |

| ADC_IN2   | 1.4 V – 0 V typ<br>range | I   | ADC Analog input [2]                                                                                               | D7        |

| PMU_CFG   | 1.0 V                    | ı   | Power management unit config pin High -> VOL1 = 1.1 V, VOM = 1.8 V Low -> VOL1 = 1.8 V, VOM = 1.1 V                | G8        |

| RSTn      | 1.0 V                    | I   | Reset Input with Schmitt-Trigger characteristics and noise filter.                                                 | F9        |

| RTC_XTI   | 1.0 V (max)              | I   | Input of the 32 KHz oscillator amplifier circuit and input of the internal real time clock circuit.                | E9        |

| RTC_XTO   | 1.0 V (max)              | 0   | Output of the oscillator amplifier circuit.                                                                        | D9        |

| STDBY_OUT | 1.0 V                    | 0   | When low, indicates the chip is in Standby mode                                                                    | G7        |

| STDBYn    | 1.0 V                    | I   | When low, the chip is forced in Standby Mode - All pins in high impedance except the ones powered by Backup supply | F8        |

DS10719 Rev 6 11/41

Pin description STA8090FG

Table 5. Main function pins (continued)

| Symbol  | I/O voltage | I/O | Description              | STA8090FG |

|---------|-------------|-----|--------------------------|-----------|

| WAKEUP0 | 1.0 V       | I   | WAKEUP from STANDBY mode | E8        |

| WAKEUP1 | 1.0 V       | I   | WAKEUP from STANDBY mode | F7        |

# 2.5 Test/emulated dedicated pins

Table 6. Test/emulated dedicated pins

| Symbol  | I/O voltage | I/O | Description                       | STA8090FG |

|---------|-------------|-----|-----------------------------------|-----------|

| TCK     | VDDIO_R2    | I   | JTAG Test Clock                   | G2        |

| TDI     | VDDIO_R2    | I   | JTAG Test Data In                 | F2        |

| TDO     | VDDIO_R2    | 0   | JTAG Test Data Out                | E2        |

| TMS     | VDDIO_R2    | I   | JTAG Test Mode Select             | D3        |

| TRSTn   | VDDIO_R2    | I   | JTAG Test Circuit Reset           | E3        |

| TP_IF_N | 1.2 V       | 0   | Diff.Test Point for IF – Negative | H5        |

| TP_IF_P | 1.2 V       | 0   | Diff.Test Point for IF – Positive | J5        |

# 2.6 Communication interface pins

**Table 7. Communication interface pins**

| Symbol                 | I/O<br>voltage | I/O | Alternative function | Function               | Description                       | STA8090FG |

|------------------------|----------------|-----|----------------------|------------------------|-----------------------------------|-----------|

|                        |                | I   | AF0<br>(default)     | CAN0_RX <sup>(1)</sup> | CAN0 receive data input           |           |

| CAN0_RX <sup>(1)</sup> | VDDIO_R2       | I   | AF1                  | UART0_RX               | UART0 Rx data                     | K1        |

| CANO_IOC               | VDDIO_I\Z      | I   | AF2                  | Tsense                 | External temperature capture port | KI        |

|                        |                | I/O | AF3                  | I2C_SD                 | I2C serial data                   |           |

|                        |                | 0   | AF0<br>(default)     | CAN0_TX <sup>(1)</sup> | CAN0 transmit data output         |           |

| CAN0_TX <sup>(1)</sup> | VDDIO_R2       | 0   | AF1                  | UART0_TX               | UART0 Tx data                     | J1        |

|                        |                | I/O | AF2                  | GPIO7                  | General purpose I/O #7            |           |

|                        |                | 0   | AF3                  | I2C_CLK                | I2C clock                         |           |

|                        |                | 0   | AF0<br>(default)     | I2C_CLK                | I2C clock                         |           |

| I2C_CLK                | VDDIO_R2       | I/O | AF1                  | GPIO8                  | General purpose I/O #8            | L3        |

|                        | _              | 0   | AF2                  | CAN1_TX <sup>(1)</sup> | CAN1 transmit data output         |           |

|                        |                | 0   | AF3                  | SPI_CLK                | SPI clock                         |           |

STA8090FG Pin description

Table 7. Communication interface pins (continued)

| Symbol    | I/O<br>voltage | I/O      | Alternative function | Function               | Description                                      | STA8090FG               |    |

|-----------|----------------|----------|----------------------|------------------------|--------------------------------------------------|-------------------------|----|

|           |                | I/O      | AF0<br>(default)     | I2C_SD                 | I2C serial data                                  |                         |    |

| I2C_SD    | VDDIO_R2       | I/O      | AF1                  | GPIO9                  | General purpose I/O #9                           | L2                      |    |

|           |                | I        | AF2                  | CAN1_RX <sup>(1)</sup> | CAN1 receive data input                          |                         |    |

|           |                | 0        | AF3                  | SPI_CSN                | SPI chip select active low                       |                         |    |

|           |                | 0        | AF0<br>(default)     | SPI_CLK                | SPI clock                                        |                         |    |

| SPI_CLK   | VDDIO_R1       | I/O      | AF1                  | GPIO25                 | General purpose I/O #25                          | A3                      |    |

|           |                | 0        | AF2                  | SQI_CLK                | SQI Flash clock                                  |                         |    |

|           |                | 0        | AF3                  | MMC_CLK                | Multimedia Clock line                            |                         |    |

|           |                | 0        | AF0<br>(default)     | SPI_CSN                | SPI chip select active low / IO_Power Sel Ring 1 |                         |    |

| SPI_CSN   | VDDIO_R1       | I/O      | AF1                  | GPIO24                 | General purpose I/O #24                          | A4                      |    |

|           | _              |          | 0                    | AF2                    | SQI_CEN                                          | SQI Flash chip enable   |    |

|           |                | I/O      | AF3                  | MMC_CMD                | Multimedia card command line                     |                         |    |

|           |                | Į        | AF0<br>(default)     | SPI_DI                 | SPI serial data input / BOOT2                    |                         |    |

| SPI_DI    | VDDIO_R1       | I/O      | AF1                  | Tsense                 | External temperature capture port                | В3                      |    |

|           |                | I/O      | AF2                  | SQI_SIO1/SO            | SQI Flash data IO 1 / ser. output                |                         |    |

|           |                | I/O      | AF3                  | MMC_D0                 | Multimedia card data 0                           |                         |    |

|           |                | 0        | AF0<br>(default)     | SPI_DO                 | SPI serial data output                           |                         |    |

| SPI_DO    | VDDIO_R1       | I/O      | AF1                  | GPIO27                 | General purpose I/O #27                          | C3                      |    |

|           |                | I/O      | AF2                  | SQI_SIO0/SI            | SQI Flash data IO 0 / ser. input                 |                         |    |

|           |                | I/O      | AF3                  | MMC_D1                 | Multimedia card data 1                           |                         |    |

|           |                | I        | AF0<br>(default)     | UART0_CTS              | UART0 clear to send                              |                         |    |

| UART0_CTS | VDDIO_R1       | I/O      | AF1                  | GPIO15                 | General purpose I/O #15                          | B5                      |    |

| _         | _              | 0        | AF2                  | i2s_out_sclk           | MSP serial clock output                          |                         |    |

|           |                | 0        | AF3                  | Clock GNSS             | GNSS clock out                                   |                         |    |

|           |                | I        | AF0<br>(default)     | UART0_DCD              | UART0 data carrier detect                        |                         |    |

| UART0_DCD | VDDIO_R1       | VDDIO_R1 | I/O                  | AF1                    | GPIO17                                           | General purpose I/O #17 | E4 |

|           |                | 0        | AF2                  | i2s_out_sdata          | MSP serial data output                           |                         |    |

|           |                | 0        | AF3                  | Clock GNSS             | GNSS clock out                                   |                         |    |

DS10719 Rev 6 13/41

Pin description STA8090FG

Table 7. Communication interface pins (continued)

|           |                |          |                      |               | e pins (continuea)                            |                         |    |

|-----------|----------------|----------|----------------------|---------------|-----------------------------------------------|-------------------------|----|

| Symbol    | I/O<br>voltage | I/O      | Alternative function | Function      | Description                                   | STA8090FG               |    |

|           |                | I        | AF0<br>(default)     | UART0_DSR     | UART0 data set ready                          |                         |    |

| UARTO DSR | VDDIO R1       | I/O      | AF1                  | GPIO16        | General purpose I/O #16                       | D4                      |    |

| UARTO_DSR | VDDIO_K1       | 0        | AF2                  | i2s_out_lrclk | MSP left/right clock output                   | ) D4                    |    |

|           |                | 0        | AF3                  | Sign GC       | GLONASS and BeiDou 3-bit coding output (Sign) |                         |    |

|           |                | 0        | AF0<br>(default)     | UART0_DTR     | UART0 data terminal read                      |                         |    |

|           |                | I/O      | AF1                  | GPIO18        | General purpose I/O #18                       |                         |    |

| UART0_DTR | VDDIO_R1       | I        | AF2                  | Timer_ICAPA   | Extended function timer - input capture A     | D5                      |    |

|           |                | 0        | AF3                  | Mag_1 GG      | GPS and Galileo 3-bit coding<br>Output (MAG1) |                         |    |

|           |                | 0        | AF0<br>(default)     | UART0_RTS     | UART0 request to send                         |                         |    |

| UARTO RTS | VDDIO_R1       | VDDIO_R1 | I/O                  | AF1           | GPIO14                                        | General purpose I/O #14 | C6 |

| UARIU_RIS |                |          | 0                    | AF2           | TCXO_OUT                                      | TCXO out clock          | Co |

|           |                | 0        | AF3                  | Sign GG       | GPS and Galileo 3-bit coding output (Sign)    |                         |    |

|           |                | I        | AF0<br>(default)     | UART0_RX      | UART0 Rx data                                 |                         |    |

| UARTO RX  | VDDIO R1       | 0        | AF1                  | SPI_DO        | SPI serial data output                        | E6                      |    |

| UARTO_RX  | VDDIO_K1       | I/O      | AF2                  | SQI_SIO2      | SQI Flash data IO 2                           |                         |    |

|           |                | I        | AF3                  | Timer_ICAPA   | Extended Function Timer - Input Capture A     |                         |    |

|           |                | 0        | AF0<br>(default)     | UART0_TX      | UART0 Tx data / BOOT1                         |                         |    |

| UARTO TX  | VDDIO_R1       | I        | AF1                  | SPI_DI        | Serial data input                             | B4                      |    |

| UARTO_TX  | VDDIO_K1       | I/O      | AF2                  | SQI_SIO3      | SQI Flash data IO 3                           | D4                      |    |

|           |                | 0        | AF3                  | Timer_OCMPA   | Extended Function Timer –<br>Output Compare A |                         |    |

|           |                | ı        | AF0<br>(default)     | UART2_RX      | UART 2 Rx data                                | B6                      |    |

| UART2_RX  | VDDIO_R1       | I/O      | AF1                  | GPIO28        | General purpose I/O #28                       |                         |    |

|           |                | I/O      | AF2                  | I2C_SD        | I2C serial data                               |                         |    |

|           |                | I/O      | AF3                  | MMC_D2        | Multimedia card data 2                        |                         |    |

STA8090FG Pin description

Table 7. Communication interface pins (continued)

| Symbol   | I/O<br>voltage | I/O | Alternative function | Function               | nction Description        |    |

|----------|----------------|-----|----------------------|------------------------|---------------------------|----|

|          |                | 0   | AF0<br>(default)     | UART2_TX               | UART 2 Tx data / BOOT0    |    |

| UART2_TX | VDDIO_R1       | I/O | AF1                  | GPIO29                 | General purpose I/O #29   | C5 |

|          |                | 0   | AF2                  | I2C_CLK                | I2C clock                 |    |

|          |                | I/O | AF3                  | MMC_D3                 | Multimedia card data 2    |    |

|          |                | USB | AF0                  | USB_DM                 | USB D- signal             |    |

| USB_DM   | VDDIO_R2       | I   | AF1<br>(default)     | UART1_RX               | UART1 Rx data             | H1 |

|          |                | I   | AF2                  | CAN1_RX <sup>(1)</sup> | CAN1 receive data input   |    |

|          |                | I/O | AF3                  | I2C_SD                 | I2C serial data           |    |

|          |                | USB | AF0                  | USB_DP                 | USB D+ signal             |    |

| USB_DP   | VDDIO R2       | 0   | AF1<br>(default)     | UART1_TX               | UART1 Tx data             | G1 |

|          |                | 0   | AF2                  | CAN1_TX <sup>(1)</sup> | CAN1 transmit data output |    |

|          |                | 0   | AF3                  | I2C_CLK                | I2C clock                 |    |

<sup>1.</sup> Only for STA8090FGB and STA8090FGBD.

# 2.7 Multimedia card pins

Table 8. Multimedia card pins

| Symbol    | I/O voltage | I/O       | Alternative function | Function               | Description                  | STA8090FG   |                                              |      |

|-----------|-------------|-----------|----------------------|------------------------|------------------------------|-------------|----------------------------------------------|------|

|           |             | 0         | AF0<br>(default)     | MMC_CLK                | Multimedia Clock line        |             |                                              |      |

| MMC CLK   | VDDIO R2    | 0         | AF1                  | i2s_out_lrclk          | MSP left/right clock output  | H4          |                                              |      |

| WIWIO_CLK | VDDIO_R2    | VDDIO_I\Z | VDDIO_IX2            | I                      | AF2                          | Timer_ICAPA | Extended Function Timer -<br>Input Capture A | 1 14 |

|           |             | I/O       | AF3                  | GPIO4                  | General purpose I/O #4       |             |                                              |      |

|           |             | I/O       | AF0<br>(default)     | MMC_CMD                | Multimedia card command line |             |                                              |      |

| MMC_CMD   | VDDIO_R2    | 0         | AF1                  | i2s_out_sdata          | MSP serial data output       | J4          |                                              |      |

|           |             | 0         | AF2                  | CAN0_TX <sup>(1)</sup> | CAN0 transmit data output    |             |                                              |      |

|           |             | I/O       | AF3                  | GPIO5                  | General purpose I/O #5       |             |                                              |      |

Pin description STA8090FG

Table 8. Multimedia card pins (continued)

| Symbol     | I/O voltage | I/O       | Alternative function | Function               | Description                       | STA8090FG |                                               |          |    |

|------------|-------------|-----------|----------------------|------------------------|-----------------------------------|-----------|-----------------------------------------------|----------|----|

|            |             | I/O       | AF0<br>(default)     | MMC_D0                 | Multimedia card data 0            |           |                                               |          |    |

| MMC_D0     | VDDIO_R2    | 0         | AF1                  | i2s_out_sclk           | MSP serial clock output           | L4        |                                               |          |    |

|            |             | I/O       | AF2                  | I2C_SD                 | I2C serial data                   |           |                                               |          |    |

|            |             | I/O       | AF3                  | GPIO20                 | General purpose I/O #20           |           |                                               |          |    |

|            |             | I/O       | AF0<br>(default)     | MMC_D1                 | Multimedia card data 1            |           |                                               |          |    |

| MMC D1     | VDDIO_R2    | ı         | AF1                  | i2s_in_sdata           | MSP serial data input             | K4        |                                               |          |    |

| IVIIVIC_D1 |             | VDDIO_I\Z | VDDIO_I\Z            | 0                      | AF2                               | Sign GC   | GLONASS and BeiDou 3-bit coding output (Sign) | 7 14     |    |

|            |             | I/O       | AF3                  | GPIO21                 | General purpose I/O #21           |           |                                               |          |    |

|            |             | I/O       | AF0<br>(default)     | MMC_D2                 | Multimedia card data 2            |           |                                               |          |    |

| MMC D2     | VDDIO B3    | VDDIO B3  | VDDIO R2             | VDDIO B3               | I/O                               | AF1       | Reserved                                      | Reserved | J3 |

| IVIIVIC_D2 | VDDIO_R2    | I         | AF2                  | CAN0_RX <sup>(1)</sup> | CAN0 receive data input           | - 33      |                                               |          |    |

|            |             | I/O       | AF3                  | Tsense                 | External temperature capture port |           |                                               |          |    |

|            |             | I/O       | AF0<br>(default)     | MMC_D3                 | Multimedia card data 2            |           |                                               |          |    |

| MMC_D3     | VDDIO_R2    | I/O       | AF1                  | Reserved               | Reserved                          | H3        |                                               |          |    |

|            |             | 0         | AF2                  | Sign GG                | GPS 3-bit coding output (Sign)    | ]         |                                               |          |    |

|            |             | I/O       | AF3                  | GPIO23                 | General purpose I/O #23           |           |                                               |          |    |

<sup>1.</sup> Only for STA8090FGB.

# 2.8 General purpose pins

Table 9. General purpose pins

| Symbol | I/O<br>voltage | I/O | Alternative function | Function Description |                                                  | STA8090FG |

|--------|----------------|-----|----------------------|----------------------|--------------------------------------------------|-----------|

|        |                | I/O | AF0 (default)        | GPIO0                | General purpose I/O #0                           |           |

|        |                | I   | AF1                  | PPS_IN               | Pulse per second input                           |           |

| GPIO0  | VDDIO_R1       | 0   | AF2                  | Timer_OCMPB          | Extended Function Timer – Output<br>Compare B    | В8        |

|        |                | 0   | AF3                  | Mag_0 GC             | GLONASS and BeiDou 3-bit coding<br>Output (MAG0) |           |

STA8090FG Pin description

Table 9. General purpose pins (continued)

| Symbol | I/O<br>voltage | I/O      | Alternative function     | Function     | Description                                      | STA8090FG |

|--------|----------------|----------|--------------------------|--------------|--------------------------------------------------|-----------|

|        |                | I/O      | AF0 (default)            | GPIO1        | General purpose I/O #1 / BOOT3                   |           |

| GPIO1  | VDDIO B1       | I        | AF1                      | i2s_in_sdata | MSP serial data input                            | B7        |

| GPIOT  | VDDIO_R1       | 0        | AF2                      | PPS_OUT      | Pulse per second output                          | D/        |

|        |                | I/O      | AF3                      | Tsense       | External temperature capture port                |           |

|        |                | I/O      | AF0 (default)            | GPIO2        | General purpose I/O #2                           |           |

|        |                | I/O      | AF1                      | Reserved     | Reserved                                         |           |

| GPIO2  | VDDIO_R2       | /DDIO_R2 |                          | Timer_ICAPB  | Extended Function Timer – Input<br>Capture B     | K3        |

|        |                | 0        | AF3                      | Mag_1 GC     | GLONASS and BeiDou 3-bit coding<br>Output (MAG1) |           |

|        |                | I/O      | AF0<br>(default),<br>AF1 | GPIO10       | General purpose I/O #10                          |           |

| GPIO10 | VDDIO_R2       | I        | AF2                      | Timer_ICAPA  | Extended Function Timer – Input<br>Capture A     | H2        |

|        |                | 0        | AF3                      | Timer_OCMPB  | Extended Function Timer – Output<br>Compare B    |           |

|        |                | I/O      | AF0<br>(default),<br>AF1 | GPIO11       | General purpose I/O #11                          |           |

| GPIO11 | VDDIO_R2       | 0        | AF2                      | Timer_OCMPA  | Extended Function Timer – Output<br>Compare A    | J2        |

|        |                | I        | AF3                      | Timer_ICAPB  | Extended Function Timer – Input<br>Capture B     |           |

# 2.9 RF Front-end pins

Table 10. RF Front-end pins

| Symbol     | I/O voltage | I/O | Description                                    | STA8090FG |

|------------|-------------|-----|------------------------------------------------|-----------|

| ANT_SENSE1 | 3.3 V       | I   | Antenna sensing input 1                        | К9        |

| ANT_SENSE2 | 3.3 V       | I   | Antenna sensing input 2                        | J8        |

| LNA_IN     | 1.2 V       | I   | Low Noise Amplifier Input                      | L6        |

| XTAL_IN    | 1.2 V       | I   | Input Side of Crystal Oscillator or TCXO Input | H9        |

| XTAL_OUT   | 1.2 V       | 0   | Output Side of Crystal Oscillator              | G9        |

General description STA8090FG

### 3 General description

#### 3.1 RF front end

The RF front-end is able to down-convert both the GPS-Galileo signal from 1575.42 MHz to 4.092 MHz (4 Fo, being F0 = 1.023 MHz), the GLONASS signal from 1601.718 MHz to 8.57 MHz and the BeiDou signal from 1561.098 MHz to 10.23 MHz.

It embeds high performance LNA minimizing external component count and two LDOs to supply the internal core facilitating requirements for external power supply. A three bits ADC converts the IF signals to sign (SIGN) and magnitude (MAG0 and MAG1). They can be sampled or not by SPI. The magnitude bits are internally integrated in order to control the variable gain amplifiers. The VGA gain can be also set by the SPI interface.

The RF tuner accepts a wide range of reference clocks (10 to 52 MHz) and can generate 64 Fo sampling clock for the baseband and 192 Fo clock for MCU subsystem.

# 3.2 GPS/Galileo/GLONASS/BeiDou Base Band (G3BB+) processor

STA8090FG integrates G3BB+ proprietary IP, which is the ST last generation high-sensitivity Baseband processor fully compliant with GPS, Galileo, GLONASS and BeiDou systems.

The baseband receives, from the embedded RF Front-End, two separate IF signals coded in sign-magnitude digital format on 3 bits and the related clocks. The Galileo/GPS (GALGPS) and GLONASS/BeiDou (GNSCOM) signals at the base band inputs are centered on 4.092 MHz, 8.57 MHz and 10.23 MHz.

The baseband processes the two IF signals performing data codification, sample rate conversion and final frequency conversion to zero IF before acquisition and tracking correlations.

The baseband processor has the capability of acquiring and tracking the Galileo, GPS, GLONASS and BeiDou signals in a simultaneous or single way, or a combination of three, being GLONASS and BeiDou mutually exclusive. The number of tracking channels to be used is programmable; the unused tracking channels can be powered down.

A complete multi-OS software library is provided by ST to handle GPS processing, managing satellite acquisition, tracking, pseudo-range calculation and positioning, generating the output in the standard NMEA message format or in a ST binary format. The library includes support of ST self-trained assisted GPS (ST-AGPS), a complete and scalable solution for assisting GPS start-up with autonomous and server-based ephemeris prediction and extension.

### 3.3 MCU Subsystem

The implemented sub-system includes an AHB Lite bus matrix.

An ARM946 core is embedded in the sub-system and masters the AHB bus. The totally available TCM SRAM is 256 KB. The amount of memory on ITCM and DTCM can be

STA8090FG General description

configured by the ARM946 (see *Table 11: TCM Configuration*). ITCM can be configured as Ni x 16 KB; DTCM can be configured as  $128 + Nd \times 16 KB$ , where Ni + Nd = 8, Ni  $\geq 1$ .

TCMcfg [2] TCMcfq [1] **DTCM** TCMcfg [0] **ITCM** 0 0 0 16 KB 240 KB 0 0 1 32 KB 224 KB 1 0 0 48 KB 208 KB 0 1 1 64 KB 192 KB 1 0 0 80 KB 176 KB 1 0 1 96 KB 160 KB 1 1 0 112 KB 144 KB 1 1 1 128 KB 128 KB

**Table 11. TCM Configuration**

#### 3.3.1 AHB slaves

- G3 APB port that allows to interface with the G3BB acquisition memory and control registers.

- 512 Kbytes ROM

- Vectored Interrupt Controller (VIC).

- SQI flash memory controller

- 3 x ARM946 APB peripheral bus (APB1, APB2, APB3).

#### **Vectored Interrupt Controller (VIC)**

This Vectored Interrupt Controller (VIC) allows the operative system interrupt handler to quickly dispatch interrupt service routines in response to peripheral interrupts. It provides a software interface to the interrupt system. There are up to 64 interrupt lines. The VIC uses a bit position for each different interrupt source.

The software can control each request line to generate software interrupts. Each interrupt line can be independently enabled and configured to trigger a non-vectored Normal Interrupt Request (IRQ) or Fast Interrupt Request (FIQ) to the ARM946 CPU. Sixteen interrupt lines can also be selected to trigger a vectored IRQ.

The VIC has two operation modes: the user mode and the privilege mode, in order to have the possibility to set (or not) one level of protection during execution.

#### FS USB device controller

#### Full speed USB device with transceiver.

It is an AHB slave. When active it requires a 48 MHz clock XTAL\_IN.

DS10719 Rev 6 19/41

General description STA8090FG

### 3.4 APB peripherals

#### 3.4.1 CAN

The 2 CAN<sup>(a)</sup> cores perform communication according to the CAN protocol version 2.0 part A and B. The bit rate can be programmed to values up to 1 MBit/s. For the connection to the physical layer, additional transceiver hardware is required.

CAN consists of the CAN core, message RAM, message handler, control registers and module. For communication on a CAN network, individual message objects are configured. The message objects and identifier masks for acceptance filtering of received messages are stored in the message RAM. All functions concerning the handling of messages are implemented in the message handler. These functions include acceptance filtering, the transfer of messages between the CAN core and the message RAM, and the handling of transmission requests as well as the generation of the module interrupt.

The register set of the CAN can be accessed directly by the CPU through the module interface. These registers are used to control/configure the CAN core and the message handler and to access the message RAM.

#### **CAN** features

- Supports CAN protocol version 2.0 part A and B

- 32 messages objects

- Each message object has its own identifier mask

- Maskable interrupt

- Disabled automatic re-transmission mode for time triggered CAN applications

- Programmable loop-back mode for self-test operation

- Two 16-bit module interfaces to the AMBA APB bus from ARM

#### 3.4.2 SSP

The SSP is a master interface for synchronous serial communication with peripheral devices that have Motorola SPI.

The SSP performs serial-to-parallel conversion on data received from a peripheral device on SPI\_DI pin, and parallel-to-serial conversion on data written by CPU for transmission on SPI\_DO pin. The transmit and receive paths are buffered with internal FIFO memories allowing up to 32 x 32-bit values to be stored independently in both transmit and receive modes. FIFOs may be burst-loaded or emptied by the system processor or DMA, from one to eight words per transfer. Each 32-bit word from the system fills one entry in FIFO.

The SSP includes a programmable bit rate clock divider and prescaler to generate the serial output clock SSPCLK from the on-chip clock. One combined interrupt is delivered, which is asserted from several internal maskable events.

a. STA8090FGB and STA8090FGBD only (see Figure 5: Ordering information scheme).

STA8090FG General description

#### SSP features

The SSP has the following features:

- Parallel-to-serial conversion on data written to an internal 32-bit wide, 32-location deep

- transmit FIFO

- Serial-to-parallel conversion on received data, buffering it in a 32-bit wide, 32-location

- deep receive FIFO

- Programmable data frame size from 4 to 32 bits

- Programmable clock bit rate and prescaler

- Programmable clock phase and polarity in SPI mode

#### 3.4.3 UART

The UARTx (x = 0|1|2) performs serial-to-parallel conversion on data asynchronously received from a peripheral device on UARTx\_RX pin, and parallel-to-serial conversion on data written by CPU for transmission on UARTx\_TX pin. The transmit and receive paths are buffered with internal FIFO memories allowing up to 64 data byte for transmission, and 64 data byte with 4-bit status (break, frame, parity, and overrun) for receive.

#### **UART** features

The UARTx (x = 0|1|2) are Universal Asynchronous Receiver/Transmitter that support much of the functionality of the industry-standard 16C650 UART. The main features are:

- Programmable baud rates up to UARTCLK / 16 (1.5 Mbps with UARTCLK at 24 MHz), or up to UARTCLK / 8 (3.0 Mbps with UARTCLK at 24 MHz), with fractional baud-rate generator

- 5, 6, 7 or 8 bits of data

- Even, odd, stick or no-parity bit generation and detection

- 1 or 2 stop bit generation

- Support of the modem control functions CTS, RTS, plus DCD, DSR, RTS, DTS and RI (UART0 only)

- Support of software flow control using programmable Xon/Xoff characters

- False start bit detection

- Line break generation and detection

- Separate 8-bit wide, 64-deep transmit FIFO and 12-bit wide, 64-deep receive FIFO

- Programmable FIFO disabling for 1-byte depth data path

These UARTs vary from industry-standard 16C650 on some minor points which are:

- Receive FIFO trigger levels

- The internal register map address space, and the bit function of each register differ

- The deltas of the modem status signals are not available

- 1.5 stop bits is not supported

- Independent receive clock feature is not supported

DS10719 Rev 6 21/41

General description STA8090FG

#### 3.4.4 Flash

The STA8090FG integrates 16 Mbits or 32 Mbits of Flash Memory. This eliminates the need of the external Flash simplifying the routing associated to integrate a GPS receiver into a customer board.

#### 3.4.5 SDMMC

STA8090FG features an SD/MMC host.

#### 3.4.6 MTU

The 2 Multi Timer Units provide access to eight interrupt generating programmable 32-bit Free-Running decrementing Counters (FRCs). The FRCs have their own clock input, allowing the counters to run from a much slower clock than the system clock.

The FRC is the part of the timer that performs the counting. There are four instantiations of the FRC block in each MTU, allowing eight counts to be performed in parallel. The 32-bit counter in the FRC is split up into two 16-bit counters.

#### 3.4.7 WDT

Watchdog Timer (WDT) provides a way of recovering from software crashes. The watchdog clock is used to generate a regular interrupt (WDOGINT), depending on a programmed value.

The watchdog monitors the interrupt and asserts a reset signal (WDOGRES) if the interrupt remains unserviced for the entire programmed period. You can enable or disable the watchdog unit as required.

Note: Watchdog is stalled when the ARM processor is in Debug mode.

#### 3.4.8 GPIO

The GPIO block provides twenty-one (21) programmable inputs or outputs. Each input or output can be controlled in two modes:

- software mode through an APB bus interface

- alternate mode, where GPIO becomes a peripheral input or output line

Any GPIO input can be independently enabled or disabled (masked) for interrupt generation. User can select for each GPIO which edge (rising, falling, both) will trigger an interrupt.

#### 3.4.9 ADC

10 bit SAR ADC operating at 1.8 V analog supply. It can convert up to 2 single ended channels with analog input multiplexer at 500KSPS

#### 3.4.10 RTC

This is an always-on power domain dedicated to RTC logic (backup system) with 32 Kbyte SRAM and supplied with a dedicated voltage regulator.

The RTC provides a high resolution clock which can be used for GPS. It keeps the time when the system is inactive and can be used to wake the system up when a programmed

STA8090FG General description

alarm time is reached. It has a clock trimming feature to compensate for the accuracy of the 32.768 kHz crystal and a secured time update.

#### **RTC** features

- 47-bit counter clocked by 32.768 kHz clock

- 32-bit for the integer part (seconds) and 15-bit for the fractional part

- The integer part and the fractional part are readable independently

- The counter, once enabled, can be stopped

- Integer part load register (32-bit)

- Fractional part load register (15-bit)

- Load bit to transfer the content of the entire load register (integer+fractional part) to the 47-bit counter. Once set by the MCU this bits is cleared by the hardware to signal to the MCU that the RTC has been updated.

#### 3.4.11 MSP

The STA8090FG provides one MSP transmitter block.

- Element (data) size from 8 to 32 bits, LSB or MSB first

- Programmable frequency shift clock for data transfer

- Direct interface to:

- Industry-standard codecs and serially connected A/D and D/A devices

- IIS compliant devices

- SPI compliant devices

- Transmit first-in, first-out memory buffers (FIFOs), 32 bits wide, 8 locations deep

DS10719 Rev 6 23/41

Electrical characteristics STA8090FG

### 4 Electrical characteristics

#### 4.1 Parameter conditions

Unless otherwise specified, all voltages are referred to GND.

#### 4.2 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$ °C.

### 4.3 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$ °C,  $V_{ddio} = 1.8$  V,  $V_{dd} = 1.20$  V. They are given only as design guidelines and are not tested.

### 4.4 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

### 4.5 Absolute maximum ratings

This product contains devices to protect the inputs against damage due to high static voltages, however it is advisable to take normal precautions to avoid application of any voltage higher than the specified maximum rated voltages.

Table 12 lists the absolute maximum rating for STA8090FG.

Table 12. Voltage characteristics

| Symbol                | Parameter                                              | Min. | Max. | Unit |

|-----------------------|--------------------------------------------------------|------|------|------|

| V <sub>CC_CHAIN</sub> | Analog supply voltage for RF chain (1.2 V)             | -0.3 | 1.32 | V    |

| V <sub>CC_PLL</sub>   | Analog supply voltage for PLL RF (1.2 V)               | -0.3 | 1.32 | V    |

| V <sub>CC_RF</sub>    | Analog supply voltage for RF (1.2 V)                   | -0.3 | 1.32 | V    |

| V <sub>DD_ADC</sub>   | Digital supply voltage for ADC (1.8 V)                 | -0.3 | 1.98 | V    |

| V <sub>DD_SQI</sub>   | Digital supply voltage for SQI                         | -0.3 | 1.95 | V    |

| $V_{DDD}$             | Power supply pins for the core logic.                  | -0.3 | 1.32 | V    |

| V <sub>DDIO_R1</sub>  | Digital supply voltage for I/O ring 1 (1.8 V or 3.3 V) | -0.3 | 3.63 | V    |

| V <sub>DDIO_R2</sub>  | Digital supply voltage for I/O ring 2 (3.3 V)          | -0.3 | 3.63 | V    |

| V <sub>INB</sub>      | Backup LDO input supply voltage (1.6 V to 4.3 V)       | -0.3 | 4.8  | V    |

| V <sub>INL1</sub>     | LDO1 input supply voltage (1.6 V to 4.3 V)             | -0.3 | 4.8  | V    |

| Symbol               | Parameter                                                     | Min. | Max. | Unit |

|----------------------|---------------------------------------------------------------|------|------|------|

| V <sub>INL2</sub>    | LDO2 input supply voltage (1.6 V to 4.3 V)                    | -0.3 | 4.8  | V    |

| V <sub>INM</sub>     | SMPS coil input supply (1.6 V to 4.3 V)                       | -0.3 | 4.8  | V    |

| V <sub>DD_ANA</sub>  | SMPS input supply (1.6 V to 4.3 V)                            | -0.3 | 4.8  | V    |

| V <sub>ESD-HBM</sub> | Electrostatic discharge, human body model <sup>(1)</sup> .    | -2   | 2    | kV   |

| V <sub>ESD-CDM</sub> | Electrostatic discharge, charge device model <sup>(2)</sup> . | -250 | 250  | V    |

**Table 12. Voltage characteristics (continued)**

Note:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 13. Thermal characteristics

| Symbol             | Parameter                                             | Min. | Max. | Unit |

|--------------------|-------------------------------------------------------|------|------|------|

| T <sub>oper</sub>  | Operative temperature range                           | -40  | 85   | °C   |

| T <sub>j</sub>     | Operative junction temperature                        | -40  | 125  | °C   |

| T <sub>st</sub>    | Storage temperature                                   | -55  | 150  | °C   |

| R <sub>j-amb</sub> | Thermal resistance junction to ambient <sup>(1)</sup> |      | 41   | °C/W |

<sup>1.</sup> According to JEDEC specification on a 2 layers board.

**Table 14. Frequency limits**

| Symbol           | Parameter                    | Test condition                        | Min. | Тур. | Max. | Unit |

|------------------|------------------------------|---------------------------------------|------|------|------|------|

| F <sub>CLK</sub> | Operating ARM9 CPU frequency | V <sub>DDD</sub> = 1.2 V;             | _    | _    | 196  | MHz  |

| F <sub>AHB</sub> | AHB frequency                | T <sub>C</sub> = 85 °C <sup>(1)</sup> |      |      | 49   | MHz  |

<sup>1.</sup> Not tested in production.

Balls sustaining only ±500 V are: A1, A2, A5, A6, A7, A8, A9, B1, B2, B9, C1, C2, D1, D2, D9, E1, E9, F1, L7 and L8.

<sup>2.</sup> Ball L6 (LNA\_IN) sustains only ±150 V.

Electrical characteristics STA8090FG

**Table 15. Power consumption**

| Symbol                           | Parameter                                                           | Test condition                                                                                                                                                                                  | Min. | Тур. | Max. | Unit |

|----------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                                  |                                                                     | G2 = GPS/Galileo;<br>T <sub>amb</sub> = 25 °C;<br>V <sub>INL2</sub> = 1.8 V                                                                                                                     | _    | 25   |      | mW   |

| P <sub>RF</sub>                  | RFIP power (total V <sub>INL2</sub> )                               | G2 + GLONASS;<br>T <sub>amb</sub> = 25 °C;<br>V <sub>INL2</sub> = 1.8 V                                                                                                                         | _    | 35   |      | mW   |

|                                  |                                                                     | G2 + COMPASS;<br>Beidou2<br>T <sub>amb</sub> = 25 °C;<br>V <sub>INL2</sub> = 1.8 V                                                                                                              | _    | 35   |      | mW   |

| P <sub>MVR</sub> <sup>(1)</sup>  | Switchable area power;<br>(total V <sub>INL1</sub> )                | $\begin{split} f_{ARM} &= 196 \text{ MHz;} \\ f_{AHB} &= 49 \text{ MHz;} \\ T_{amb} &= 25 \text{ °C;} \\ V_{INL1} &= 1.8 \text{ V; UART} \\ active; other peripherals} \\ inactive \end{split}$ | _    | 90   |      | mW   |

| P <sub>LPVR</sub> <sup>(1)</sup> | Always ON area power<br>(total V <sub>INB</sub> )                   | f <sub>ARM</sub> = 196 MHz;<br>f <sub>AHB</sub> = 49 MHz;<br>T <sub>amb</sub> = 25 °C; V <sub>INB</sub> = 3.3 V                                                                                 |      | 1    |      | mW   |

| P <sub>IO</sub> <sup>(1)</sup>   | IO rings power (total V <sub>DDIO_R1</sub> + V <sub>DDIO_R2</sub> ) | $\begin{split} f_{ARM} &= 196 \text{ MHz;} \\ f_{AHB} &= 49 \text{ MHz;} \\ T_{amb} &= 25 \text{ °C;} \\ V_{INL1} &= 1.8 \text{ V; UART} \\ active; other peripherals} \\ inactive \end{split}$ | _    | 4    |      | mW   |

| I <sub>DStandby</sub>            | Standby mode supply current                                         | RTC<br>running = 32.768 KHz;                                                                                                                                                                    |      | 29   |      | μA   |

| I <sub>DDeepStandby</sub>        | Deep standby mode supply current <sup>(2)</sup>                     | $T_{amb} = 25 \text{ °C; } V_{INB} = 1.8 \text{ V}$                                                                                                                                             | _    | 7    | _    | μΑ   |

<sup>1.</sup> Not tested in production.

### 4.6 Recommended DC operating conditions

Table 16 lists the functional recommended operating DC parameters for STA8090FG.

Table 16. Recommended DC operating conditions

| Symbol                | Parameter                                  | Min. | Тур. | Max. | Unit |

|-----------------------|--------------------------------------------|------|------|------|------|

| V <sub>CC_CHAIN</sub> | Analog supply voltage for RF chain (1.2 V) | 1.08 | 1.20 | 1.32 | V    |

| V <sub>CC_PLL</sub>   | Analog supply voltage for PLL RF (1.2 V)   | 1.08 | 1.20 | 1.32 | V    |

| V <sub>CC_RF</sub>    | Analog supply voltage for RF (1.2 V)       | 1.08 | 1.20 | 1.32 | V    |

| V <sub>DD_ADC</sub>   | Digital supply voltage for ADC (1.8 V)     | 1.71 | 1.80 | 1.89 | V    |

| V <sub>DD_SQI</sub>   | Flash power supply.                        | 1.71 | 1.80 | 1.89 | V    |

<sup>2.</sup> STDBY\_OUT pin not supported in deep standby.

Table 16. Recommended DC operating conditions (continued)

| Symbol               | Parameter                                                  | Min. | Тур. | Max. | Unit |

|----------------------|------------------------------------------------------------|------|------|------|------|

| $V_{DDD}$            | Power supply pins for the core logic.                      | 1.00 | 1.10 | 1.32 | V    |

| V                    | Digital supply voltage for I/O ring 1 (1.8 V)              | 1.71 | 1.80 | 1.89 | V    |

| V <sub>DDIO_R1</sub> | Digital supply voltage for I/O ring 1 (3.3 V)              | 3.00 | 3.30 | 3.60 | V    |

| V <sub>DDIO_R2</sub> | Digital supply voltage for I/O ring 2 (3.3 V)              | 3.00 | 3.30 | 3.60 | V    |

| V <sub>INB</sub>     | Backup LDO input supply voltage (1.6 V to 4.3 V)           | 1.60 |      | 4.30 | V    |

| \/                   | LDO1 input supply voltage to generate 1.1 V and 1.2 V      | 1.60 |      | 4.30 | V    |

| V <sub>INL1</sub>    | LDO1 input supply voltage to generate 1.8 V                | 2.10 |      | 4.30 | V    |

| V <sub>INL2</sub>    | LDO2 input supply voltage to generate 1.2 V                | 1.60 |      | 4.30 | V    |

| V <sub>INM</sub>     | SMPS coil input supply voltage to generate 1.1 V and 1.2 V | 1.60 |      | 4.30 | V    |

|                      | SMPS coil input supply voltage to generate 1.8 V           | 2.10 |      | 4.30 | ٧    |

| V <sub>DD_ANA</sub>  | SMPS input supply (1.6 V to 4.3 V)                         | 1.60 |      | 4.30 | V    |

| T <sub>C</sub>       | Operating temperature range                                | -40  |      | 85   | °C   |

### 4.7 DC characteristics

Table 17 specifies the SMPS voltage regulator characteristics.

Table 17. SMPS DC characteristics

| Symbol          | Parameter              | Test condition                                                                                            | Min. | Тур. | Max. | Unit |

|-----------------|------------------------|-----------------------------------------------------------------------------------------------------------|------|------|------|------|

|                 | Output voltage (1.2 V) | $1.6 \text{ V} \le \text{V}_{\text{INM}} \le 4.3 \text{ V};$<br>$\text{I}_{\text{OM}} \le 100 \text{ mA}$ | 1.08 | 1.20 | 1.32 | V    |

| V <sub>OM</sub> | Output voltage (1.1 V) | 1.6 V $\leq$ V <sub>INM</sub> $\leq$ 4.3 V;<br>I <sub>OM</sub> $\leq$ 100 mA                              | 1.0  | 1.10 | 1.21 | V    |

|                 | Output voltage (1.8 V) | 2.1 V ≤ V <sub>INM</sub> ≤ 4.3 V;<br>I <sub>OM</sub> ≤ 100 mA                                             | 1.71 | 1.80 | 1.89 | V    |

| I <sub>OM</sub> | Output current         |                                                                                                           | 0    | _    | 100  | mA   |

Table 18 specifies the LDO1 voltage regulator characteristics.

Electrical characteristics STA8090FG

Table 18. LDO1 DC characteristics

| Symbol           | Parameter             | Test condition                                                                                             | Min. | Тур. | Max. | Unit |

|------------------|-----------------------|------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>OL1</sub> | Output voltage (1.2V) | $1.6 \text{ V} \le \text{V}_{\text{INL1}} \le 4.3 \text{ V};$<br>$\text{I}_{\text{OL1}} \le 70 \text{ mA}$ | 1.08 | 1.20 | 1.32 | ٧    |

|                  | Output voltage (1.1V) | $1.6 \text{ V} \le \text{V}_{\text{INL1}} \le 4.3 \text{ V};$<br>$\text{I}_{\text{OL1}} \le 70 \text{ mA}$ | 1    | 1.10 | 1.21 | ٧    |

|                  | Output voltage (1.8V) | $2.1 \text{ V} \le \text{V}_{\text{INL1}} \le 4.3 \text{ V};$<br>$\text{I}_{\text{OL1}} \le 70 \text{ mA}$ | 1.71 | 1.80 | 1.89 | ٧    |

| I <sub>OL1</sub> | Output current        |                                                                                                            | 0    |      | 70   | mA   |

Table 19 specifies the LDO2 voltage regulator characteristics.

Table 19. LDO2 DC characteristics

| Symbol           | Parameter      | Test condition                                                                                             | Min. | Тур. | Max. | Unit |

|------------------|----------------|------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>OL2</sub> | Output voltage | $1.6 \text{ V} \le \text{V}_{\text{INL2}} \le 4.3 \text{ V};$<br>$\text{I}_{\text{OL2}} \le 30 \text{ mA}$ | 1.08 | 1.20 | 1.32 | ٧    |

| I <sub>OL2</sub> | Output current |                                                                                                            | 0    | _    | 30   | mA   |

Table 20 specifies the low voltage detection thresholds

Table 20. Low voltage detection thresholds

|                                | Parameter                                            | Min. | Тур.  | Max. | Unit |

|--------------------------------|------------------------------------------------------|------|-------|------|------|

| Input LVD always               | Upper voltage threshold                              | _    | 1.680 | _    | V    |

| on and main VRs <sup>(1)</sup> | Lower voltage threshold                              | _    | 1.650 | _    | V    |

| Output LVD always              | Upper voltage threshold                              | _    | 0.995 | _    | V    |

| on VR <sup>(1)</sup>           | Lower voltage threshold                              | _    | 0.935 | _    | V    |

|                                | Upper voltage threshold @ $V_{OL1/M}$ = 1.2 V        | _    | 1.142 | _    | V    |

| Output LVD main                | Lower voltage threshold @ $V_{OL1/M}$ = 1.2 V        | _    | 1.076 | _    | V    |

| VR <sup>(1)</sup>              | Upper voltage threshold @ V <sub>OL1/M</sub> = 1.1 V | _    | 1.048 | _    | V    |

|                                | Lower voltage threshold @ $V_{OL1/M}$ = 1.1 V        | _    | 0.986 | _    | V    |

| Output LVD main                | Upper voltage threshold @ $V_{OL1/M}$ = 1.8 V        | _    | 1.645 | _    | V    |

| VR <sup>(1)</sup>              | Lower voltage threshold @ $V_{OL1/M}$ = 1.8 V        | _    | 1.626 | _    | V    |

<sup>1.</sup> Not tested in production.

*Table 21* lists the DC characteristics for all the IO digital buffers expect for the following input buffers: STBYn (F8), STDBY\_OUT (G7), WAKEUP0 (E8), WAKEUP1 (F7), PMU\_CFG (G8) and RSTn (F9).

| Symbol                           | Parameter                        | Test conditions           | Min.                    | Тур. | Max.                    | Unit |

|----------------------------------|----------------------------------|---------------------------|-------------------------|------|-------------------------|------|

| V <sub>II</sub> <sup>(1)</sup>   | Logical input low level voltage  | V <sub>DDIO</sub> = 1.8 V | -0.3                    |      | 0.3 * V <sub>DDIO</sub> | V    |

| VIL.                             | Logical input low level voltage  | $V_{\rm DDIO} = 3.3V$     | -0.3                    |      | 0.8                     | V    |

| V <sub>IH</sub> <sup>(1)</sup>   | Logical input high level voltage | V <sub>DDIO</sub> = 1.8 V | 0.7 * V <sub>DDIO</sub> |      | V <sub>DDIO</sub> + 0.3 | V    |

| VIH.                             |                                  | V <sub>DDIO</sub> = 3.3V  | 2.0                     |      | V <sub>DDIO</sub> + 0.3 | V    |

| V <sub>HYST</sub> <sup>(2)</sup> | Schmitt-trigger hysteresis       | _                         | 50                      | _    |                         | mV   |

| V                                | Low lovel output voltage         | V <sub>DDIO</sub> = 1.8 V |                         | _    | 0.4                     | V    |

| V <sub>OL</sub>                  | Low level output voltage         | V <sub>DDIO</sub> = 3.3V  |                         | _    | 0.4                     | V    |

| V                                | I link lavel autout valtage      | V <sub>DDIO</sub> = 1.8 V | V <sub>DDIO</sub> - 0.4 |      |                         | V    |

| V <sub>OH</sub>                  | High level output voltage        | V <sub>DDIO</sub> = 3.3V  | V <sub>DDIO</sub> - 0.4 |      |                         | V    |

Table 21. I/O buffers DC characteristics

Table 22 lists the DC characteristics for the 1.0 V IO digital buffers input buffers: STBYn (F8), STDBY\_OUT (G7), WAKEUP0 (E8), WAKEUP1 (F7), PMU\_CFG (G8) and RSTn (F9).

**Symbol Test conditions** Min. Unit **Parameter** Тур. Max. 0.35 \* V<sub>OB</sub> -0.3  $V_{II}$ Logical input low level voltage  $V_{OB} = 1.0 V$ 0.65 \* V<sub>OB</sub>  $V_{OB} + 0.3$ Logical input high level voltage  $V_{OB} = 1.0 V$ ٧  $V_{IH}$  $V_{OB}$  = 1.0 V $V_{OL}$ Low level output voltage 0.2 ٧  $V_{\mathsf{OH}}$  $V_{OB} = 1.0 V$ ٧ High level output voltage V<sub>OB</sub> - 0.2

Table 22. 1.0 V I/O buffers DC characteristics

#### 4.8 AC characteristics

#### 4.8.1 RF electrical specifications

Table 23. RFACHAIN - GALGPS filter and VGA

| Symbol             | Parameter             | Test conditions                                  | Min | Тур              | Max | Unit |