# 12µV<sub>RMS</sub> Low Noise 500mA LDO Linear Regulator

### **General Description**

The MAX38902A/B/C/D are low-noise, linear regulators that deliver up to 500mA of output current with only  $12\mu V_{RMS}$  of output noise from 10Hz to 100kHz. These regulators maintain  $\pm 1\%$  output accuracy over a wide input voltage range, requiring only 100mV of input-to-output headroom at full load. The  $365\mu A$  no-load supply current is independent of drop-out voltage.

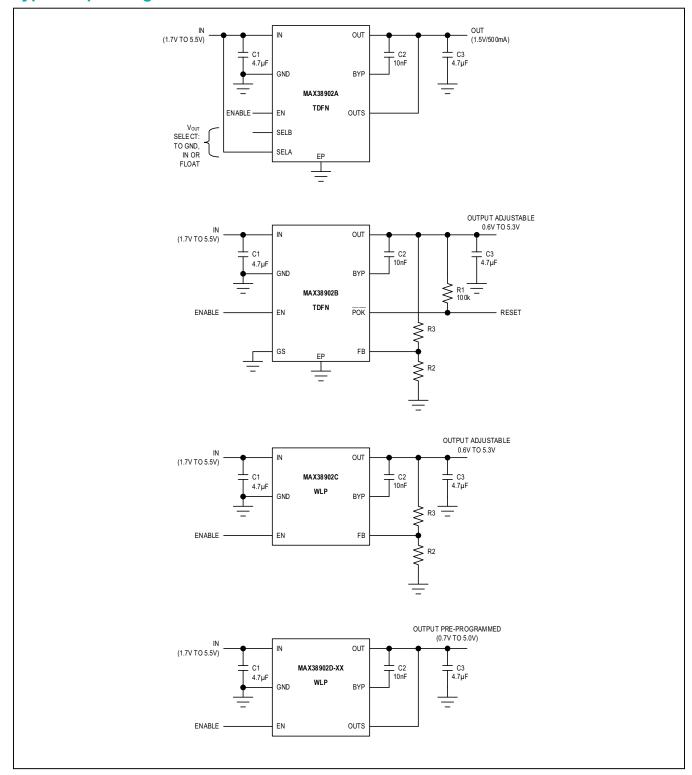

The MAX38902A have nine, pin-selectable output voltages 1.2V, 1.5V, 1.8V, 2.5V, 3.0V, 3.1V, 3.3V, 4.0V, and 5V. The MAX38902B/C have a resistor adjustable output voltage in the range of 0.6V to 5.3V. The MAX38902B also includes an active-low  $\overline{\text{POK}}$  output.

The MAX38902D have factory-preset output voltages ranging from 0.7V to 5V. All versions include a programmable output soft-start rate, output over-current and thermal overload protection.

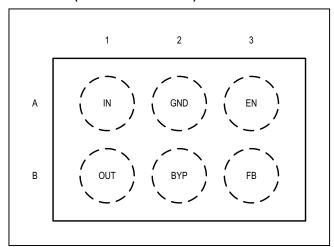

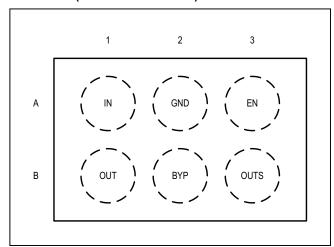

The MAX38902A/B are offered in an 8-pin TDFN package, while the MAX38902C/D are offered in a 2 x 3, 0.4mm wafer-level package (WLP).

### **Applications**

- Communication Circuitry

- Audio Systems

- High-Resolution Data Acquisition Systems

#### **Benefits and Features**

- 1.7V to 5.5V Input Voltage Range

- 0.6V to 5.3V Output Voltage Range

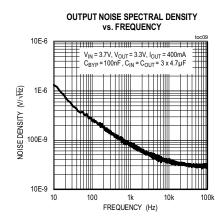

- 12μV<sub>RMS</sub> Output Noise, 10Hz to 100kHz

- 365µA Operating Supply Current

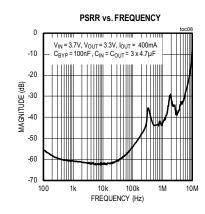

- 70dB PSRR at 10kHz

- 500mA Maximum Output Current

- ±1% DC Accuracy Over Load, Line, and Temperature

- 100mV (Max) Dropout at 500mA Load (3.6V<sub>IN</sub>)

- < 0.1μA Shutdown Supply Current

- Stable with 2µF(Min) Output Capacitance

- Programmable Soft-Start Rate

- Overcurrent and Overtemperature Protection

- Output-to-Input Reversed Current Protection

- POK Output

- 1.22mm x 0.82mm, 2 x 3 Bump, 0.4mm Pitch WLP, or 2mm x 2mm 8-pin TDFN Package

Ordering Information appears at end of data sheet.

## **Typical Operating Circuits**

# 12μV<sub>RMS</sub> Low Noise 500mA LDO Linear Regulator

### **Absolute Maximum Ratings**

| IN, EN, POK, SELA, SELB, GS, OUTS,        | TDFN (derate 9.8mW/°C above 70°C)784mW         |

|-------------------------------------------|------------------------------------------------|

| FB, BYP to GND0.3V to +6V                 | Operating Temperature Range40°C to +125°C      |

| OUT to GND0.3V to IN + 0.3V               | Maximum Junction Temperature+150°C             |

| Output Short-Circuit Duration             | Storage Temperature Range65°C to +150°C        |

| Continuous Power Dissipation (TA = +70°C) | Lead Temperature (Soldering, 10 seconds)+300°C |

| WLP (derate 10.5mW/°C above 70°C)840mW    | Soldering Temperature (reflow)+260°C           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### **TDFN**

| PACKAGE CODE                            | T822+3C |

|-----------------------------------------|---------|

| Outline Number                          | 21-0168 |

| Land Pattern Number                     | 90-0065 |

| Thermal Resistance, Single-Layer Board: |         |

| Junction to Ambient (θ <sub>JA</sub> )  | 130°C/W |

| Junction to Case (θ <sub>JC</sub> )     | 8°C/W   |

| Thermal Resistance, Four-Layer Board:   |         |

| Junction to Ambient (θ <sub>JA</sub> )  | 102°C/W |

| Junction to Case $(\theta_{JC})$        | 8°C/W   |

#### **WLP**

| <del></del>                            |                                |

|----------------------------------------|--------------------------------|

| PACKAGE CODE                           | N60G1+1                        |

| Outline Number                         | 21-100183                      |

| Land Pattern Number                    | Refer to Application Note 1891 |

| Thermal Resistance, Four-Layer Board:  |                                |

| Junction to Ambient (θ <sub>JA</sub> ) | 95.1°C/W                       |

| Junction to Case (θ <sub>JC</sub> )    | N/A                            |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

# 12μV<sub>RMS</sub> Low Noise 500mA LDO Linear Regulator

### **Electrical Characteristics**

$(V_{IN} = 3.6V, T_J = -40^{\circ}C \text{ to } +125^{\circ}C, C_{BYP} = 10 \text{nF}, C_{IN} = 4.7 \mu\text{F}, C_{OUT} = 4.7 \mu\text{F}, Typical Operating Circuits}$ . Typical values are at  $T_J = +25^{\circ}C$ , unless otherwise specified. (Note 1)

| PARAMETER                             | SYMBOL                    | CONDIT                                                                                                    | MIN                     | TYP   | MAX    | UNITS |                   |

|---------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------|-------|--------|-------|-------------------|

| Input Voltage Range                   | V <sub>IN</sub>           | Guaranteed by Output Accuracy                                                                             |                         | 1.7   |        | 5.5   | V                 |

| Input Undervoltage Lockout            | V <sub>IN_UVLO</sub>      | V <sub>IN</sub> rising, 100mV hysteresis                                                                  |                         | 1.5   | 1.6    | 1.7   | V                 |

| Output Voltage Range                  | V <sub>OUT</sub>          | V <sub>IN</sub> > V <sub>OUT</sub> + 0.1V                                                                 |                         | 0.6   |        | 5.3   | V                 |

| Output Capacitance                    | C <sub>OUT</sub>          | For stability and prop                                                                                    | per operation           | 2     | 4.7    |       | μF                |

|                                       | IQ                        | I <sub>OUT</sub> = 0mA                                                                                    |                         |       | 365    | 600   |                   |

| Supply Current                        |                           | V - 0V                                                                                                    | T <sub>J</sub> = +25°C  |       | 0.01   | 0.1   | μA                |

|                                       | ISHUTDOWN                 | V <sub>EN</sub> = 0V                                                                                      | T <sub>J</sub> = +125°C |       | 700    |       | nA                |

| Output Accuracy<br>(MAX38902A/D Only) | ACC <sub>38902A/D</sub>   | I <sub>OUT</sub> from 0.1mA to 5<br>V <sub>OUT</sub> + 0.3V to 5.5V                                       |                         | -1    |        | +1    | %                 |

| Output Accuracy<br>(MAX38902B/C Only) | ACC <sub>38902B/C</sub>   | I <sub>OUT</sub> from 0.1mA to 5<br>V <sub>OUT</sub> + 0.3V to 5.5V                                       |                         | 0.594 | 0.6    | 0.606 | V                 |

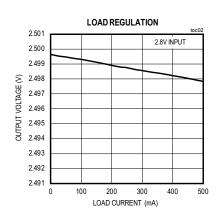

| Load Regulation                       |                           | I <sub>OUT</sub> from 0.1mA to V <sub>IN</sub> = V <sub>OUT</sub> + 300mV                                 |                         |       | 0.07   |       | %                 |

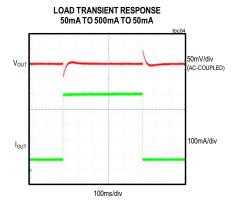

| Load Transient                        |                           | I <sub>OUT</sub> = 50mA to 500mA to 50mA,<br>t <sub>RISE</sub> = t <sub>FALL</sub> = 1µs                  |                         |       | 50     |       | mV                |

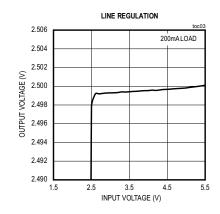

| Line Regulation                       |                           | V <sub>IN</sub> from V <sub>OUT</sub> + 0.3V to 5.5V,<br>V <sub>IN</sub> > 1.7V, I <sub>OUT</sub> = 200mA |                         |       | 0.06   |       | %                 |

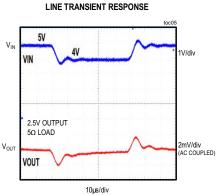

| Line Transient                        |                           | $V_{IN}$ = 4V to 5V to 4V, $I_{OUT}$ = 500mA,<br>$t_{RISE}$ = $t_{FALL}$ = 5 $\mu$ s                      |                         |       | 3      |       | mV                |

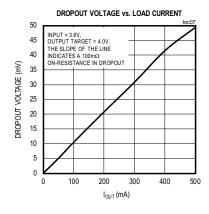

|                                       |                           |                                                                                                           | V <sub>IN</sub> = 3.6V  |       | 26     | 100   |                   |

| Dropout Voltage (Note 2)              |                           | I <sub>OUT</sub> = 500mA                                                                                  | V <sub>IN</sub> = 2.5V  |       | 36     | 200   | mV                |

|                                       |                           |                                                                                                           | V <sub>IN</sub> = 1.7V  |       | 63     | 300   |                   |

| Current Limit                         |                           | V <sub>OUTS/FB</sub> = 0V, V <sub>IN</sub>                                                                | V <sub>IN</sub> = 1.7V  | 600   | 700    | 800   | mA                |

| Current Limit                         |                           | - V <sub>OUT</sub> = 500mV                                                                                | V <sub>IN</sub> = 3.6V  | 600   | 700    | 800   | IIIA              |

| Output Noise                          |                           | I <sub>OUT</sub> = 100mA,<br>10Hz to 100kHz                                                               | C <sub>BYP</sub> = 47nF |       | 12     |       | μV <sub>RMS</sub> |

|                                       |                           |                                                                                                           | f = 1kHz                |       | 70     |       |                   |

| Power Supply Rejection                | PSRR                      | - 100mA                                                                                                   | f = 10kHz               |       | 70     |       | dB                |

| Ratio                                 | PSRR                      | I <sub>OUT</sub> = 100mA                                                                                  | f = 100kHz              |       | 60     |       | ] ub              |

|                                       |                           |                                                                                                           | f = 1MHz                |       | 40     |       |                   |

| BYP Capacitor Range                   | C <sub>BYP</sub>          | Regulator remains stable                                                                                  |                         | 0.001 |        | 0.1   | μF                |

| BYP Soft-Start Current                |                           | From BYP to GND during startup                                                                            |                         |       | 50     |       | μA                |

| EN Input Threshold                    | V <sub>IN</sub> from 1.7\ | V <sub>IN</sub> from 1.7V                                                                                 | EN rising               |       | 8.0    | 1.2   | V                 |

| Liv iliput iliiesilolu                |                           | to 5.5V                                                                                                   | EN falling              | 0.4   | 0.7    |       | <b>v</b>          |

| EN Input Leakage Current              |                           | V <sub>EN</sub> from 1.7V                                                                                 | T <sub>J</sub> = +25°C  | -1    | +0.001 | +1    | μA                |

| Lit input Loakage Ourient             |                           | to 5.5V                                                                                                   |                         |       | 0.01   |       | μ/                |

### **Electrical Characteristics (continued)**

$(V_{IN} = 3.6V, T_J = -40^{\circ}C \text{ to } +125^{\circ}C, C_{BYP} = 10 \text{nF}, C_{IN} = 4.7 \mu\text{F}, C_{OUT} = 4.7 \mu\text{F}, Typical Operating Circuits}$ . Typical values are at  $T_J = +25^{\circ}C$ , unless otherwise specified. (Note 1)

| PARAMETER                                    | SYMBOL | CONDIT                                                    | MIN                                  | TYP  | MAX    | UNITS |      |

|----------------------------------------------|--------|-----------------------------------------------------------|--------------------------------------|------|--------|-------|------|

| POK Threshold                                |        | V <sub>OUT</sub> when                                     | V <sub>OUT</sub> rising              | 88   | 91     | 94    | - %  |

| (MAX38902B Only)                             |        | POK switches                                              | V <sub>OUT</sub> falling             |      | 88     |       | 70   |

| POK Voltage, Low<br>(MAX38902B Only)         |        | I <sub>POK</sub> = 1mA                                    |                                      |      | 10     | 100   | mV   |

| POK Leakage Current                          |        | \/ - F F\/                                                | T <sub>J</sub> = +25°C               | -0.1 | +0.001 | +0.1  |      |

| (MAX38902B Only)                             |        | V <sub>POK</sub> = 5.5V                                   | T <sub>J</sub> = +125°C              |      | 0.01   |       | - μΑ |

| SELA/B Input Resistance                      |        | When shorted to GN                                        | When shorted to GND or IN. When Hi-Z |      |        | 500   | Ω    |

| (MAX38902A Only)                             |        | When Hi-Z                                                 |                                      |      |        |       | ΜΩ   |

| SELA/B Input Capacitance<br>(MAX38902A Only) |        | When Hi-Z                                                 |                                      |      |        | 10    | pF   |

| Input Reverse Current<br>Threshold           |        | V <sub>OUT</sub> = 3.6V, when V <sub>IN</sub> falls to 0V |                                      |      | 200    |       | mA   |

| Thermal Shutdown                             |        | T <sub>J</sub> when output                                | T <sub>J</sub> rising                |      | 165    |       | °C   |

| Threshold                                    |        | turns on/off                                              | T <sub>J</sub> falling               |      | 150    |       |      |

Note 1: Limits over the specified operating temperature and supply voltage range are guaranteed by design and characterization, and production tested at T<sub>,1</sub> = 25°C only.

**Note 2:** Dropout voltage is defined as  $(V_{IN} - V_{OUT})$ , when  $V_{OUT}$  is 5% lower than the value of  $V_{OUT}$  when  $V_{IN} = V_{OUT} + 0.5V$ .

Note 3: LED full-scale current maximum value is subjected to string number, LED number per string, and LX current limit. In SMBus modes, if the total load is heavier than eight strings with ten WLEDs per string at 25mA LED current, upon step-up regulator input VS removal, an OC fault may occur, resulting in SMBus status register OV\_CURR and FAULT bits being set to 1 and violating SMBus specifications.

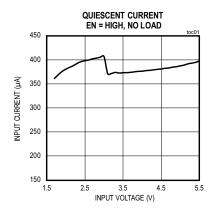

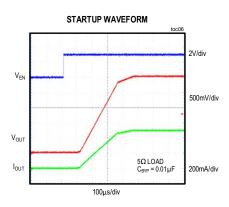

### **Typical Operating Characteristics**

(MAX38902A,  $V_{IN}$  = 3.6V,  $V_{OUT}$  = 2.5V,  $T_A$  = 25°C,  $C_{IN}$  = 4.7 $\mu$ F ,  $C_{OUT}$  = 4.7 $\mu$ F, unless otherwise noted.)

## **Pin Configurations**

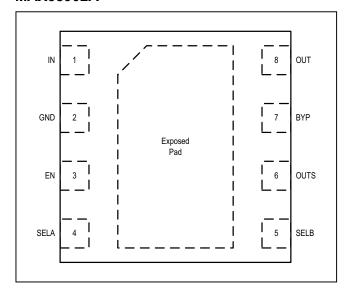

### MAX38902A

#### MAX38902B

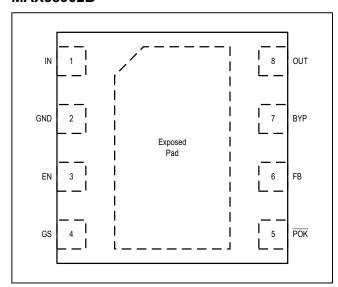

MAX38902C TOP VIEW (BUMP-SIDE DOWN)

MAX38902D TOP VIEW (BUMP-SIDE DOWN)

# 12μV<sub>RMS</sub> Low Noise 500mA LDO Linear Regulator

# **Pin Description**

|           | PIN       |           | NASSE     | FUNCTION |                                                                                                                                                                                                                               |  |

|-----------|-----------|-----------|-----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX38902A | MAX38902B | MAX38902C | MAX38902D | NAME     | FUNCTION                                                                                                                                                                                                                      |  |

| 1         | 1         | A1        | A1        | IN       | Regulator Supply Input. Connect to a voltage between 1.7V and 5.5V and bypass with a 4.7µF capacitor from IN to GND.                                                                                                          |  |

| 2         | 2         | A2        | A2        | GND      | Regulator Ground. Bring IN and OUT bypass capacitor GND connections to this pin for best performance.                                                                                                                         |  |

| 3         | 3         | A3        | A3        | EN       | Enable Input. Connect this pin to a logic signal to enable (V <sub>EN</sub> high) or disable (V <sub>EN</sub> low) the regulator output. Connect to IN to keep the output enabled whenever a valid supply voltage is present. |  |

| 4         | _         | _         | _         | SELA     | Output Select Input. Connect to GND, IN or leave unconnected to select one of three states. The state of the SELA and SELB pins are read when the device is enabled and used to select one of nine output voltages.           |  |

| _         | 4         | _         | _         | GS       | Ground Sense. Connect GS to GND.                                                                                                                                                                                              |  |

| 5         | _         | _         | _         | SELB     | Output Select Input. Connect to GND, IN or leave unconnected to select one of three states. The state of the SELA and SELB pins are read when the device is enabled and used to select one of nine output voltages.           |  |

| _         | 5         | _         | _         | POK      | Power-On Reset Output. Connect a pullup resistor from this pin to a supply to create a reset signal that goes low after the regulator output has reached its regulation voltage.                                              |  |

| 6         | _         | _         | В3        | OUTS     | Output Voltage Sense Input. Connect to the load at a point where accurate regulation is required to eliminate resistive metal drops.                                                                                          |  |

| _         | 6         | В3        | _         | FB       | Feedback Divider Input. Connect a resistor divider string from OUT to GND with the midpoint tied to this pin to set the output voltage. In the <u>Typical Operating Circuits</u> , V <sub>OUT</sub> = 0.6V x (1 + R3/R2).     |  |

| 7         | 7         | B2        | B2        | ВҮР      | Bypass Capacitor Input. Connect a 0.001µF to 0.1µF capacitor between OUT and BYP to reduce output noise and set the regulator soft-start rate.                                                                                |  |

| 8         | 8         | B1        | B1        | OUT      | Regulator Output. Sources up to 500mA at the output regulation voltage. Bypass with a 4.7 $\mu$ F (2 $\mu$ F minimum including voltage derating) low ESR (< 0.03 $\Omega$ ) capacitor to GND.                                 |  |

| EP        | EP        | _         | _         | EP       | Exposed Pad (TDFN Only). Connect the exposed pad to a ground plane with low thermal resistance to ambient to provide best heat sinking.                                                                                       |  |

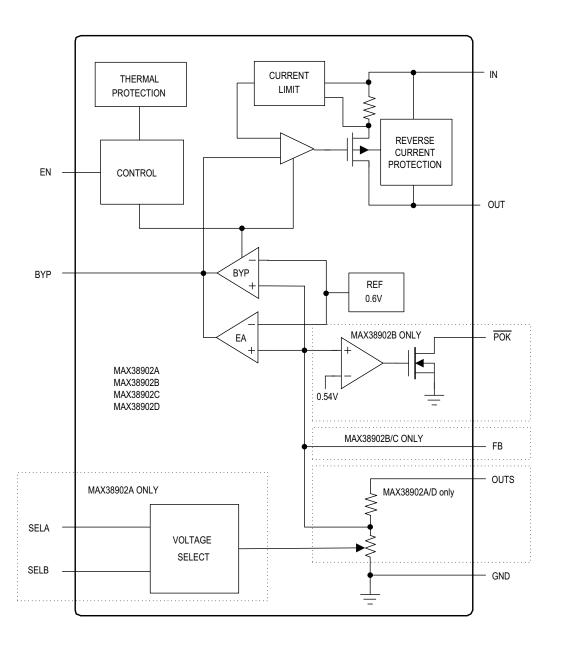

## **Functional Diagram**

## **Simplified Functional Diagram**

## 12μV<sub>RMS</sub> Low Noise 500mA LDO Linear Regulator

### **Detailed Description**

The MAX38902A/B/C/D low noise linear regulators deliver up to 500mA of output current with only  $12\mu V_{RMS}$  of output noise in a 10Hz to 100kHz bandwidth. These regulators maintain their output voltage over a wide input range, requiring only 100mV of input-to-output headroom at full load.

The MAX38902 maintains a low 365µA typical supply current, independent of the load current and drop-out voltage. The regulator control circuitry includes a programmable soft-start circuit, short-circuit, reverse input current, and thermal overload protection. Other features include an enable input and power-okay (POK) output (MAX38902B only). See Functional Diagram.

#### Enable (EN)

The MAX38902A/MAX38902B/MAX38902C/MAX38902D include an enable input (EN). Pull EN low to shut down the output, or drive EN high to enable the output. If a separate shutdown signal is not available, connect EN to IN.

#### Bypass (BYP)

The capacitor connected from BYP to OUT filters the noise of the reference, feedback resistors and regulator input stage, and provides a high-speed feedback path for improved transient response. A  $0.01\mu F$  capacitor rolls-off input noise at around 32Hz.

The slew rate of the output voltage during startup is also determined by the BYP capacitor. A  $0.01\mu F$  capacitor sets the slew rate to 5V/ms. This startup rate results in a 50mA slew current drawn from the input at start-up to charge the  $10\mu F$  output capacitance.

The BYP capacitor value can be adjusted from  $0.001\mu F$  to  $0.1\mu F$  to change the startup slew rate according to the following formula:

Startup Slew Rate =  $(5V/ms) \times (0.01 \mu F/CBYP)$

where  $C_{BYP}$  is in  $\mu F$ .

Note that this slew rate applies only at startup. That recovery from a short-circuit will occur at a slew rate approximately 500 times slower.

Also note that, being a low-frequency filter node, BYP is sensitive to leakage. BYP leakage currents above 10nA cause measurable inaccuracy at the output and should be avoided.

#### **Protection Features**

The MAX38902A/B/C/D are fully protected from an output short-circuit by a current-limiting and thermal overload circuit. If the output is shorted to GND, the output current is limited to 700mA (typ). Under these conditions, the part quickly heats up. When the junction temperature reaches 165°C, a thermal limit circuit shuts off the output device. When the junction cools to 150°C, the output turns back on in an attempt to reestablish regulation. While the fault persists, the output current cycles on and off, as the junction temperature slews between 150°C and 165°C.

The MAX38902A/B/C/D are also protected against reverse current when the output voltage is higher than the input. In the event that extra output capacitance is used at the output, a power-down transient at the input would normally cause a large reverse current through a conventional regulator. The MAX38902A/B/C/D include a reverse voltage detector that trips when IN drops 10mV below OUT, shutting off the regulator and opening the PMOS body diode connection, preventing any reverse current.

#### **Output Voltage Configuration (MAX38902A)**

The MAX38902A output can be set to one of nine voltages by shorting or opening the SELA and SELB inputs, as shown in <u>Table 1</u>. SELA and SELB should be connected to GND, IN, or left unconnected. Alternatively, they may be driven high, low, or open with external logic. However, the states of SELA and SELB are sampled only at startup. The regulation voltage can be set to a different level by cycling EN or IN momentarily to GND.

**Table 1. MAX38902A Output Configuration**

| V <sub>OUT</sub> (V) | SELA STATE  | SELB STATE  |

|----------------------|-------------|-------------|

| 1.2                  | Unconnected | IN          |

| 1.5                  | IN          | Unconnected |

| 1.8                  | Unconnected | GND         |

| 2.5                  | Unconnected | Unconnected |

| 3.0                  | GND         | GND         |

| 3.1                  | GND         | IN          |

| 3.3                  | GND         | Unconnected |

| 4.0                  | IN          | GND         |

| 5.0                  | IN          | IN          |

#### **Output Voltage Configuration (MAX38902B/C)**

The MAX38902B and MAX38902C use external feedback resistors to set the output regulation voltage as shown in <u>Typical Operating Circuits</u>. The output can be set from 0.6V to 5.3V. Set the lower feedback resistor R2 to  $300k\Omega$  or less to minimize FB input bias current error. Then calculate the value of the upper feedback resistor R3 as follows:

$$R3 = R2 \times \left(\frac{V_{OUT}}{V_{FB}} - 1\right)$$

where  $V_{FB}$  is the feedback regulation voltage of 0.6V. To set the output voltage to 2.5V, for example, R3 should be:

$$R3 = 300 k\Omega \times \left(\frac{2.5V}{0.6V} - 1\right) = 950 k\Omega$$

Table 2. MAX38902D Output Voltage

| PART NUMBER  | V <sub>OUT</sub> |

|--------------|------------------|

| MAX38902D-07 | 0.7V             |

| MAX38902D-08 | 0.8V             |

| MAX38902D-10 | 1.0V             |

| MAX38902D-12 | 1.2V             |

| MAX38902D-15 | 1.5V             |

| MAX38902D-18 | 1.8V             |

| MAX38902D-20 | 2.0V             |

| MAX38902D-25 | 2.5V             |

| MAX38902D-27 | 2.7V             |

| MAX38902D-30 | 3.0V             |

| MAX38902D-33 | 3.3V             |

| MAX38902D-46 | 4.6V             |

| MAX38902D-50 | 5.0V             |

#### **Output Voltage Configuration (MAX38902D)**

The MAX38902D output voltage comes pre-programmed to values listed below. Additionally, any voltage between 0.7V and 5.3V in 50mV steps can be factory trimmed, and special ordered.

#### Power-OK (MAX38902B)

The MAX38902B includes an additional open-drain output,  $\overline{POK}$ , that goes low to indicate the output voltage is in regulation. Connect a pullup resistor from this pin to an external supply. During startup,  $\overline{POK}$  stays high until the output voltage rises to 91%(typ) of its regulation level. If an overload occurs at the output, or the output is shutdown,  $\overline{POK}$  goes high.

#### **Input Capacitor**

A 4.7µF ceramic capacitor is recommended for the input. Select a capacitor that maintains its capacitance over temperature and DC bias. Capacitors with X5R or X7R temperature characteristics generally perform well.

#### **Output Capacitor**

A minimum of  $2\mu F$  capacitance is required at OUT to ensure stability. Select a ceramic capacitor that maintains its capacitance ( $2\mu F$  minimum) over temperature and DC bias. Capacitors with X5R or X7R temperature characteristics generally perform well. For example, the ceramic capacitor part number GRM155R60J475ME47 from Murata ( $4.7\mu F/6.3V/X5R$ ) derates to around  $2.9\mu F$  with 1.8V dc bias.

#### **Thermal Considerations**

The MAX38902A/B is packaged in an 8-pin 2mm x 2mm TDFN package with an exposed paddle. The exposed paddle is the main path for heat to leave the IC, and therefore must be connected to a ground plane with thermal vias to allow heat to dissipate from the device. Thermal properties of the IC package are given in the <u>Package Information</u> section.

# 12μV<sub>RMS</sub> Low Noise 500mA LDO Linear Regulator

## **Ordering Information**

| PART NUMBER    | TEMPERATURE RANGE | PIN-PACKAGE | OUTPUT VOLTAGE SETTING                     |

|----------------|-------------------|-------------|--------------------------------------------|

| MAX38902AATA+  | -40°C to +125°C   | 8 TDFN      | Pin-Selectable Output Voltage              |

| MAX38902BATA+* | -40°C to +125°C   | 8 TDFN      | External Resistor Feedback with POK output |

| MAX38902CANT+* | -40°C to +125°C   | 6 WLP       | External Resistor Feedback                 |

| MAX38902DANT+* | -40°C to +125°C   | 6 WLP       | Factory-trimmed option from 0.7V to 5.3V   |

<sup>\*</sup>Future product—Contact factory for availability.

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

# 12μV<sub>RMS</sub> Low Noise 500mA LDO Linear Regulator

## **Revision History**

| REVISION NUMBER | REVISION DATE | DESCRIPTION     | PAGES<br>CHANGED |

|-----------------|---------------|-----------------|------------------|

| 0               | 11/17         | Initial release | _                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.