# 2A STEP DOWN SWITCHING REGULATOR

#### 1 Features

- UP TO 2A STEP DOWN CONVERTER

- OPERATING INPUT VOLTAGE FROM 8V TO 55V

- PRECISE 3.3V (±1%) INTERNAL REFERENCE VOLTAGE

- OUTPUT VOLTAGE ADJUSTABLE FROM 3.3V TO 50V

- SWITCHING FREQUENCY ADJUSTABLE UP TO 300KHz

- VOLTAGE FEEDFORWARD

- ZERO LOAD CURRENT OPERATION

- INTERNAL CURRENT LIMITING (PULSE-BYPULSE AND HICCUP MODE)

- INHIBIT FOR ZERO CURRENT CONSUMPTION

- PROTECTION AGAINST FEEDBACK DISCONNECTION

- THERMAL SHUTDOWN

- SOFT START FUNCTION

#### 2 DESCRIPTION

The L4978 is a step down monolithic power switching regulator delivering 2A at a voltage between 3.3V and 50V (selected by a simple external divider). Realized in BCD mixed technology, the device uses an internal power D-MOS transistor (with a typical  $R_{dson}$  of  $0.25\Omega)$  to obtain very high

Figure 1. Packages

**Table 1. Order Codes**

| Part Number | Package             |

|-------------|---------------------|

| L4978       | DIP-8               |

| L4978D      | SO16                |

| L4978D013TR | SO16 in Tape & Reel |

efficency and high switching speed.

A switching frequency up to 300KHz is achievable (the maximum power dissipation of the packages must be observed). A wide input voltage range between 8V to 55V and output voltages regulated from 3.3V to 50V cover the majority of today's applications. Features of this new generations of DC-DC converter include pulse-by-pulse current limit, hiccup mode for short circuit protection, voltage feedforward regulation, soft-start, protection against feedback loop disconnection, inhibit for zero current consumption and thermal shutdown.

The device is available in plastic dual in line, DIP-8 for standard assembly, and SO16W for SMD assembly.

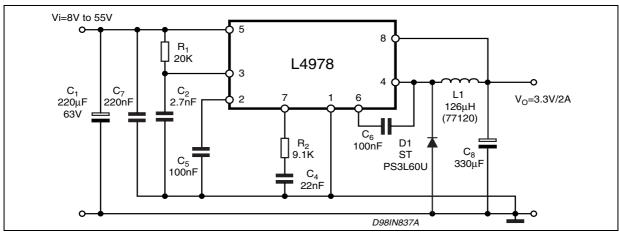

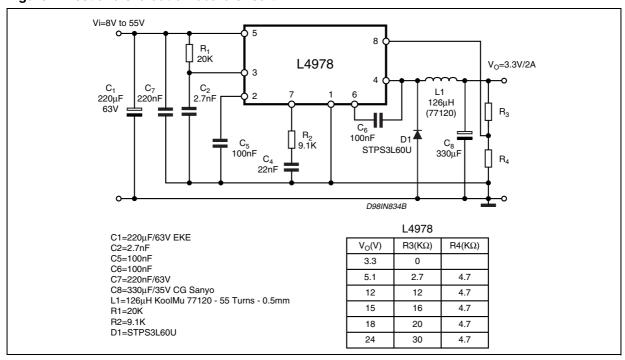

Figure 2. Typical Application Circuit

Rev. 9 1/13

May 2005

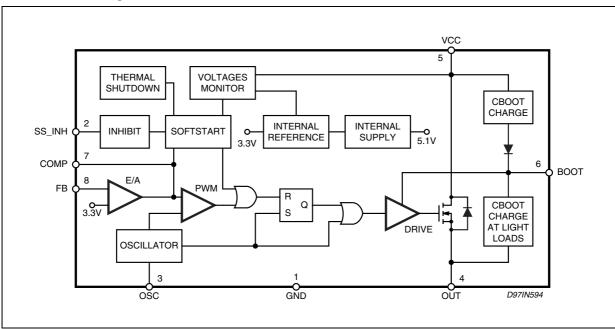

Table 2. Block Diagram

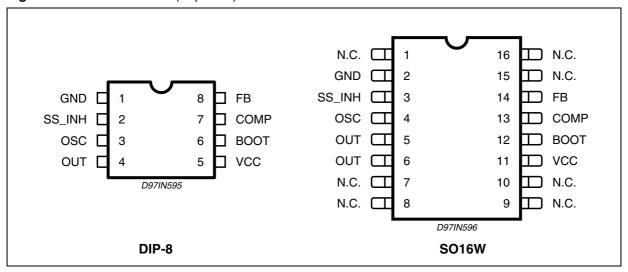

Figure 3. Pins Connection (Top view)

**Table 3. Pin Description**

| N° | Pin | Name   | Function                                                                                                                                                                                                                                    |

|----|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | 2   | GND    | Ground                                                                                                                                                                                                                                      |

| 2  | 3   | SS_INH | A logic signal (active low) disables the device (sleep mode operation).  A capacitor connected between this pin and ground determines the soft start time.  When this pin is grounded disables the device (driven by open collector/drain). |

| 3  | 4   | OSC    | An external resistor connected between the unregulated input voltage and this pin and a capacitor connected from this pin to ground fix the switching frequency. (Line feed forward is automatically obtained)                              |

Table 3. Pin Description (continued)

| N° | Pin  | Name            | Function                                                                                                                                                             |

|----|------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4  | 5, 6 | OUT             | Stepdown regulator output                                                                                                                                            |

| 5  | 11   | V <sub>CC</sub> | Unregulated DC input voltage                                                                                                                                         |

| 6  | 12   | BOOT            | A capacitor connected between this pin and OUT allows to drive the internal DMOS Transistors                                                                         |

| 7  | 13   | COMP            | E/A output to be used for frequency compensation                                                                                                                     |

| 8  | 14   | FB              | Stepdown feedback input. Connecting directly to this pin results in an output voltage of 3.3V. An external resistive divider is required for higher output voltages. |

<sup>(\*)</sup> Pins 1, 7, 8, 9, 10, 15 and 16 are not internally, electrically connected to the die.

#### **Table 4. Thermal Data**

| Symbol                 | Parameter                                   | Minidip | SO16    | Unit |

|------------------------|---------------------------------------------|---------|---------|------|

| R <sub>th(j-amb)</sub> | Thermal Resistance Junction to ambient Max. | 90 (*)  | 110 (*) | °C/W |

<sup>(\*)</sup> Package mounted on board.

#### **Table 5. Absolute Maximum Ratings**

| Syn                            | nbol                             | D                                                              | Malaa      | 1114        |  |  |

|--------------------------------|----------------------------------|----------------------------------------------------------------|------------|-------------|--|--|

| Minidip                        | S016                             | Parameter                                                      | Value      | Unit        |  |  |

| V <sub>5</sub>                 | V <sub>11</sub>                  | Input voltage                                                  | 58         | V           |  |  |

| $V_4$                          | V <sub>5</sub> ,V <sub>6</sub>   | Output DC voltage<br>Output peak voltage at t = 0.1ms f=200KHz | -1<br>-5   | V<br>V      |  |  |

| I <sub>4</sub>                 | I <sub>5</sub> ,I <sub>6</sub>   | Maximum output current                                         | int.       | int. limit. |  |  |

| V <sub>6</sub> -V <sub>5</sub> | V <sub>12</sub> -V <sub>11</sub> |                                                                | 14         | V           |  |  |

| V <sub>6</sub>                 | V <sub>12</sub>                  | Bootstrap voltage                                              | 70         | V           |  |  |

| V <sub>7</sub>                 | V <sub>13</sub>                  | Analogs input voltage (V <sub>CC</sub> = 24V)                  | 12         | V           |  |  |

| V <sub>2</sub>                 | V <sub>3</sub>                   | Analogs input voltage (V <sub>CC</sub> = 24V)                  | 13         | V           |  |  |

| V <sub>8</sub>                 | V <sub>14</sub>                  | (VCC= 20V)                                                     | 6<br>-0.3  | V<br>V      |  |  |

| F                              | Ptot                             | Power dissipation a Tamb ≤ 60°C DIP-8 SO16                     | 1<br>0.8   | W<br>W      |  |  |

| T <sub>j</sub> ,               | T <sub>stg</sub>                 | Junction and storage temperature                               | -40 to 150 | °C          |  |  |

**A7/**

**Table 6. Electrical Characteristcs**

$(T_j = 25^{\circ}C, C_{osc} = 2.7nF, R_{osc} = 20k\Omega, V_{CC} = 24V, unless otherwise specified)$ . " $\bullet$ " Specification Referred to  $T_j$  from 0 to 125°C

| Symbol                | Parameter                                         | Test Condition                                                                                                                                                              |   | Min.  | Тур. | Max.  | Unit  |

|-----------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|------|-------|-------|

| DYNAMIC (             | CHARACTERISTIC                                    | 1                                                                                                                                                                           |   |       |      |       | 1     |

| VI                    | Operating input voltage range                     | $V_0 = 3.3 \text{ to } 50V; I_0 = 2A$                                                                                                                                       | • | 8     |      | 55    | V     |

| Vo                    | Output voltage                                    | I <sub>0</sub> = 0.5A                                                                                                                                                       |   | 3.33  | 3.36 | 3.39  | V     |

|                       |                                                   | $I_0 = 0.2 \text{ to } 2A$                                                                                                                                                  |   | 3.292 | 3.36 | 3.427 | V     |

|                       |                                                   | $V_{cc} = 8 \text{ to } 55V$                                                                                                                                                | • | 3.22  | 3.36 | 3.5   | V     |

| V <sub>d</sub>        | Dropout voltage                                   | $V_{cc} = 10V; I_0 = 2A$                                                                                                                                                    |   |       | 0.58 | 0.733 | V     |

|                       |                                                   |                                                                                                                                                                             | • |       |      | 1.173 | V     |

| I <sub>I</sub>        | Maximum limiting current                          | V <sub>cc</sub> = 8 to 55V                                                                                                                                                  | • | 2.5   | 3    | 3.5   | Α     |

|                       | Efficiency                                        | $V_0 = 3.3V$ ; $I_0 = 2A$                                                                                                                                                   |   |       | 87   |       | %     |

| fs                    | Switching frequency                               |                                                                                                                                                                             | • | 90    | 100  | 110   | KHz   |

| SVRR                  | Supply voltage ripple rejection                   | $\begin{aligned} V_i &= V_{\text{CC}} + 2V_{\text{RMS}}; \ V_{\text{o}} = V_{\text{ref}}; \\ I_{\text{o}} &= 2.5\text{A}; \ f_{\text{ripple}} = 100\text{Hz} \end{aligned}$ |   | 60    |      |       | dB    |

|                       | Switching Frequency Stability vs. V <sub>cc</sub> | V <sub>cc</sub> = 8 to 55V                                                                                                                                                  |   |       | 3    | 6     | %     |

|                       | Temp. stability of switching frequency            | T <sub>j</sub> = 0 to 125°C                                                                                                                                                 |   |       | 4    |       | %     |

| SOFT STAF             | RT                                                |                                                                                                                                                                             |   |       |      |       |       |

|                       | Soft start charge current                         |                                                                                                                                                                             |   | 30    | 40   | 50    | μΑ    |

|                       | Soft start discharge current                      |                                                                                                                                                                             |   | 6     | 10   | 14    | μΑ    |

| INHIBIT               |                                                   |                                                                                                                                                                             |   |       |      |       |       |

| $V_{LL}$              | Low level voltage                                 |                                                                                                                                                                             | • |       |      | 0.9   | V     |

| $I_{SLL}$             | Isource Low level                                 |                                                                                                                                                                             | • |       | 5    | 15    | μΑ    |

| DC CHARA              | CTERISTICS                                        |                                                                                                                                                                             |   |       |      |       |       |

| I <sub>qop</sub>      | Total operating quiescent current                 |                                                                                                                                                                             |   |       | 4    | 6     | mA    |

| Ιq                    | Quiescent current                                 | Duty Cycle = 0; VFB= 3.8V                                                                                                                                                   |   |       | 2.5  | 3.5   | mA    |

| I <sub>qst-by</sub>   | Total stand-by quiescent                          | V <sub>inh</sub> < 0.9V                                                                                                                                                     |   |       | 100  | 200   | μΑ    |

|                       | current                                           | $V_{cc} = 55V; V_{inh} < 0.9V$                                                                                                                                              |   |       | 150  | 300   | μΑ    |

| ERROR AN              | IPLIFIER                                          |                                                                                                                                                                             |   |       |      |       |       |

| $V_{FB}$              | Voltage Feedback Input                            |                                                                                                                                                                             |   | 3.33  | 3.36 | 3.39  | V     |

| $R_{L}$               | Line regulation                                   | V <sub>cc</sub> = 8 to 55V                                                                                                                                                  |   |       | 5    | 10    | mV    |

|                       | Ref. voltage stability vs temperature             |                                                                                                                                                                             | • |       | 0.4  |       | mV/°C |

| V <sub>oH</sub>       | High level output voltage                         | V <sub>FB</sub> = 2.5V                                                                                                                                                      |   | 10.3  |      |       | V     |

| V <sub>oL</sub>       | Low level output voltage                          | V <sub>FB</sub> = 3.8V                                                                                                                                                      |   |       |      | 0.65  | V     |

| I <sub>o source</sub> | Source output current                             | V <sub>comp</sub> = 6V; V <sub>FB</sub> = 2.5V                                                                                                                              |   | 180   | 220  |       | μА    |

| I <sub>o sink</sub>   | Sink output current                               | $V_{comp} = 6V; V_{FB} = 3.8V$                                                                                                                                              |   | 200   | 300  |       | μА    |

| l <sub>b</sub>        | Source bias current                               |                                                                                                                                                                             |   |       | 2    | 3     | μА    |

| SVRR E/A              | Supply voltage ripple rejection                   | $V_{comp} = V_{FB}$ ; $V_{cc} = 8$ to 55V                                                                                                                                   |   | 60    | 80   |       | dB    |

|                       | DC open loop gain                                 | R <sub>L</sub> = ∞                                                                                                                                                          |   | 50    | 57   |       | dB    |

| 9m                    | Transconductance                                  | I <sub>comp</sub> = -0.1 to 0.1mA<br>V <sub>comp</sub> = 6V                                                                                                                 |   |       | 2.5  |       | mS    |

#### **Table 6. Electrical Characteristcs**

$(T_j = 25^{\circ}C, C_{osc} = 2.7 nF, R_{osc} = 20 k\Omega, V_{CC} = 24 V, unless otherwise specified)$ . "•" Specification Referred to  $T_i$  from 0 to 125°C

| Symbol    | Parameter          | Test Condition                                                                    |  | Min. | Тур. | Max. | Unit |  |  |

|-----------|--------------------|-----------------------------------------------------------------------------------|--|------|------|------|------|--|--|

| OSCILLATO | OSCILLATOR SECTION |                                                                                   |  |      |      |      |      |  |  |

|           | Ramp Valley        |                                                                                   |  | 0.78 | 0.85 | 0.92 | V    |  |  |

|           | Ramp peak          | $V_{cc} = 8V$                                                                     |  | 2    | 2.15 | 2.3  | V    |  |  |

|           |                    | $V_{cc} = 55V$                                                                    |  | 9    | 9.6  | 10.2 | V    |  |  |

|           | Maximum duty cycle |                                                                                   |  | 95   | 97   |      | %    |  |  |

|           | Maximum Frequency  | Duty Cycle = $0\%$<br>R <sub>osc</sub> = $13k\Omega$ , C <sub>osc</sub> = $820pF$ |  |      |      | 300  | kHz  |  |  |

Figure 4. Test and evaluation board circuit.

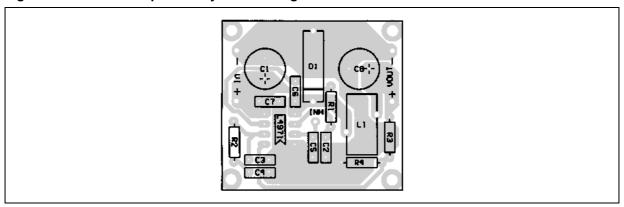

Figure 5. PCB and component layout of the figure 4.

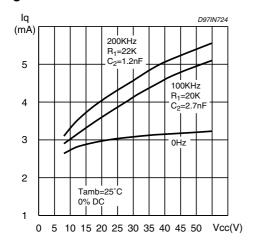

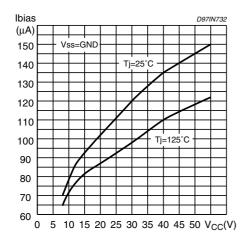

Figure 6. Quiescent drain current vs. input voltage.

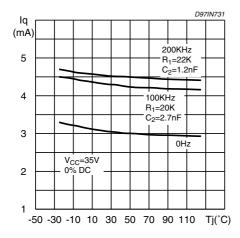

Figure 7. Quiescent current vs. junction temperature

Figure 8. Stand by drain current vs. input voltage.

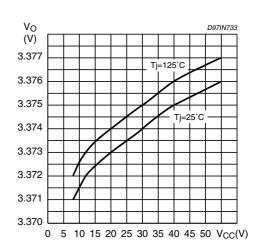

Figure 9. Line Regulation

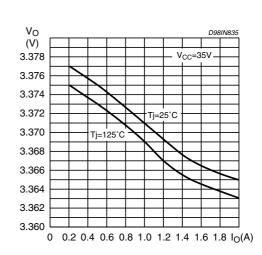

Figure 10. Load regulation

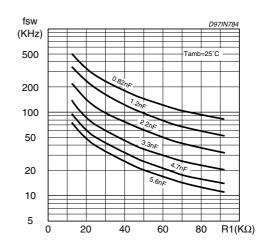

Figure 11. Switching frquency vs. R1 and C2

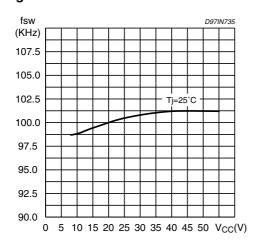

Figure 12. Switching Frequency vs. input voltage..

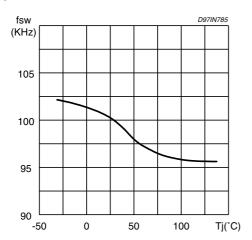

Figure 13. Switching frequency vs. junction temperature.

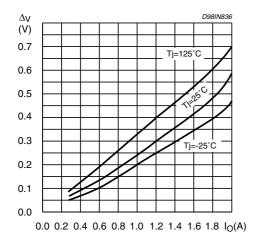

Figure 14. Dropout voltage between pin 5 and 4.

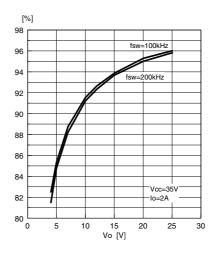

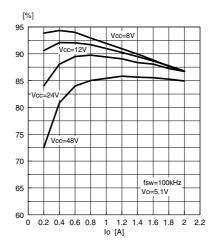

Figure 15. Efficiency vs output voltage.

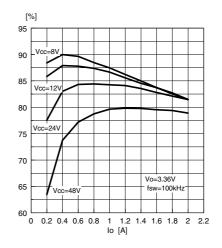

Figure 16. Efficiency vs. output current.

Figure 17. Efficiency vs. output current.

70

65

#### Figure 18. Efficiency vs. output current.

90 V<sub>CC</sub>=12V 85 V<sub>CC</sub>=24V 75

fsw=200KHz V<sub>O</sub>=5.1V

Figure 19. Efficiency vs. output current.

0.2 0.4 0.6 0.8 1.0 1.2 1.4 I<sub>O</sub>(A)

75 70 65 60 55 0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 I<sub>O</sub>(A)

Figure 20. Efficiency vs. Vcc.

Figure 21. Power dissipation vs. Vcc.

Pdiss [mW]

1000

Vo=5.1V

fsw=100kHz

10=1.5A

10=0.5A

10=0.5A

Figure 22. Device Power dissipation vs. Vo

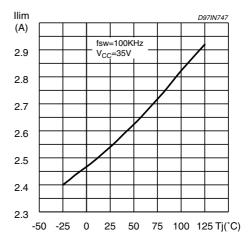

Figure 23. Pulse by pulse limiting current vs. junction temperature..

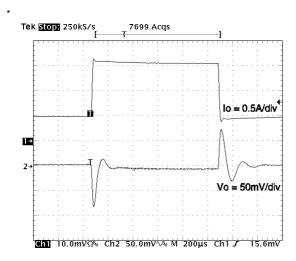

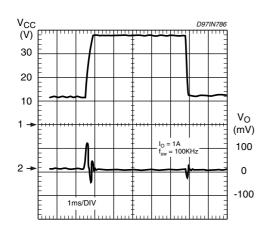

Figure 24. Load transient.

Figure 25. Line transient.

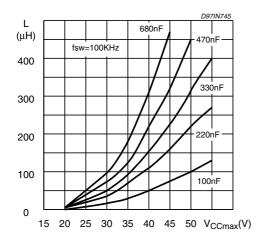

Figure 26. Soft start capacitor selection Vs inductor and  $V_{\text{ccmax}}$ .

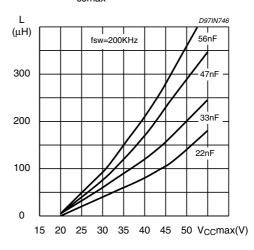

Figure 27. Soft start capacitor selection Vs inductor and  $V_{\text{\tiny CCmax}}.$

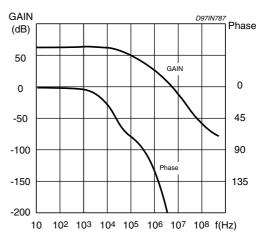

Figure 28. Open loop frequency and phase of error amplifier .

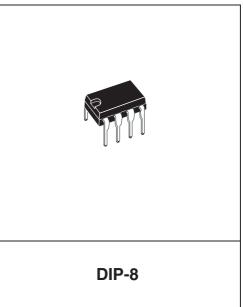

# 3 Package Informations

| TYP. MAX. MIN. TYP. MAX.                                                               |                         | inch  |       |       | mm   |       | DIM. |  |

|----------------------------------------------------------------------------------------|-------------------------|-------|-------|-------|------|-------|------|--|

|                                                                                        | P. MAX.                 | TYP.  | MIN.  | MAX.  | TYP. | MIN.  |      |  |

| 3.32 0.131                                                                             | 31 L                    | 0.131 |       |       | 3.32 |       | Α    |  |

| 0.020                                                                                  |                         |       | 0.020 |       |      | 0.51  | a1   |  |

| 1.65 0.045 0.065                                                                       | 0.065                   |       | 0.045 | 1.65  |      | 1.15  | В    |  |

| 0.55 0.014 0.022                                                                       | 0.022                   |       | 0.014 | 0.55  |      | 0.356 | b    |  |

| 0.304 0.008 0.012                                                                      | 0.012                   |       | 0.008 | 0.304 |      | 0.204 | b1   |  |

| 10.92 0.430                                                                            | 0.430                   |       |       | 10.92 |      |       | D    |  |

| 9.75 0.313 0.384                                                                       | 0.384                   |       | 0.313 | 9.75  |      | 7.95  | Е    |  |

| 2.54 0.100                                                                             | 00                      | 0.100 |       |       | 2.54 |       | е    |  |

| 7.62 0.300                                                                             | 00                      | 0.300 |       |       | 7.62 |       | еЗ   |  |

| 7.62 0.300                                                                             | 00                      | 0.300 |       |       | 7.62 |       | e4   |  |

| 6.6 0.260                                                                              | 0.260                   |       |       | 6.6   |      |       | F    |  |

| 5.08 0.200                                                                             | 0.200                   |       |       | 5.08  |      |       | I    |  |

| 3.81 0.125 0.150                                                                       | 0.150                   |       | 0.125 | 3.81  |      | 3.18  | L    |  |

| 1.52 0.060                                                                             | 0.060                   |       |       | 1.52  |      |       | Z    |  |

| 7.62     0.300       6.6     0.260       5.08     0.200       3.81     0.125     0.150 | 0.260<br>0.200<br>0.150 |       | 0.125 | 5.08  |      | 3.18  |      |  |

**/**/ 10/13

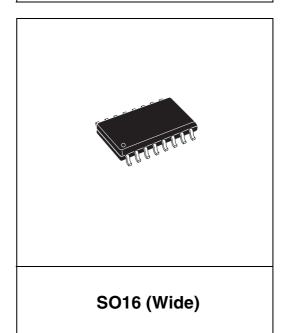

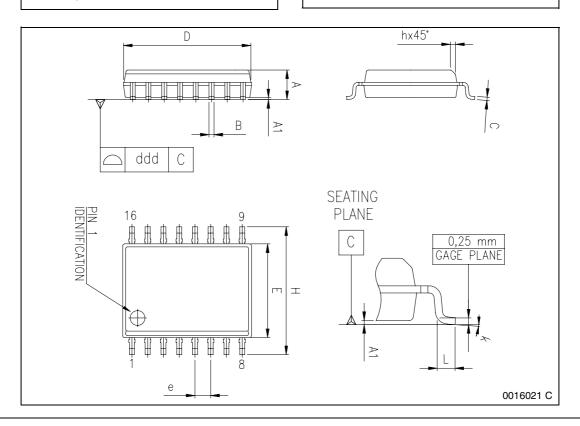

Figure 30. SO16 Wide Mechanical Data & Package Dimensions

| DIM.   |       | mm   |           |         | inch  |       |  |

|--------|-------|------|-----------|---------|-------|-------|--|

| Dilvi. | MIN.  | TYP. | MAX.      | MIN.    | TYP.  | MAX.  |  |

| Α      | 2.35  |      | 2.65      | 0.093   |       | 0.104 |  |

| A1     | 0.10  |      | 0.30      | 0.004   |       | 0.012 |  |

| В      | 0.33  |      | 0.51      | 0.013   |       | 0.200 |  |

| С      | 0.23  |      | 0.32      | 0.009   |       | 0.013 |  |

| D (1)  | 10.10 |      | 10.50     | 0.398   |       | 0.413 |  |

| Е      | 7.40  |      | 7.60      | 0.291   |       | 0.299 |  |

| е      |       | 1.27 |           |         | 0.050 |       |  |

| Н      | 10.0  |      | 10.65     | 0.394   |       | 0.419 |  |

| h      | 0.25  |      | 0.75      | 0.010   |       | 0.030 |  |

| L      | 0.40  |      | 1.27      | 0.016   |       | 0.050 |  |

| k      |       | 0    | ° (min.), | 8° (max | .)    |       |  |

| ddd    |       |      | 0.10      |         |       | 0.004 |  |

<sup>(1) &</sup>quot;D" dimension does not include mold flash, protusions or gate burrs. Mold flash, protusions or gate burrs shall not exceed 0.15mm per side.

# OUTLINE AND MECHANICAL DATA

## L4978

## **Table 7. Revision History**

| Date         | Revision | Description of Changes     |

|--------------|----------|----------------------------|

| October 2001 | 8        | First Issue                |

| May 2005 9   |          | Modified D1 on the Fig. 4. |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2005 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America www.st.com

47/