Click here to ask an associate for production status of specific part numbers.

### Best-in-Class Optical Pulse Oximeter and Heart-Rate Sensor AFE for Wearable Health

### **General Description**

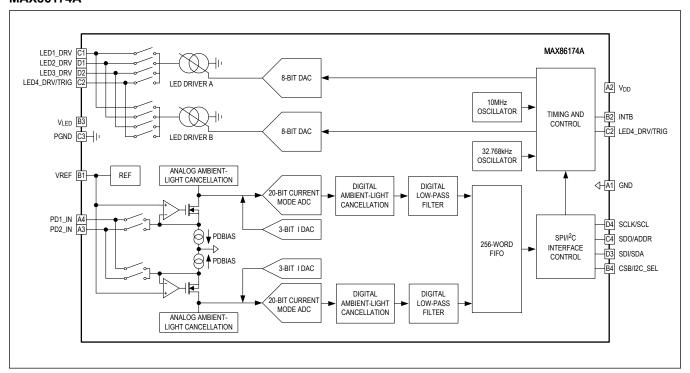

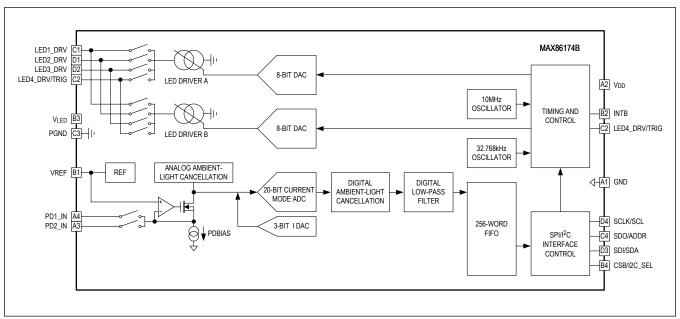

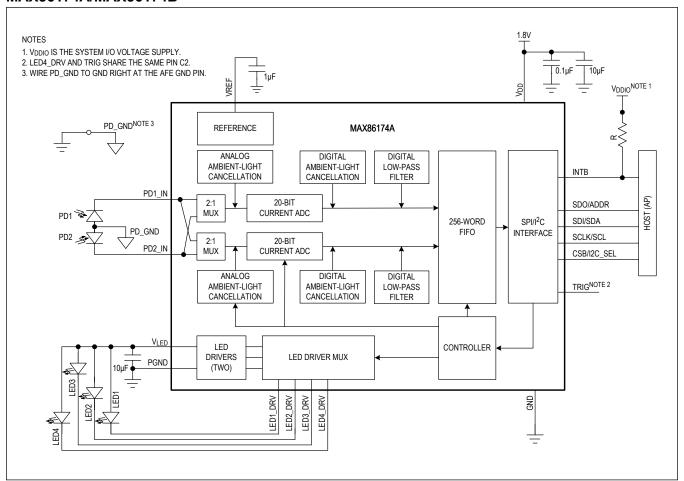

The MAX86174A/MAX86174B are ultra-low-power optical data acquisition systems with both transmit and receive channels. On the transmitter side, the MAX86174A/MAX86174B have four LED driver output pins. Each pin is programmable from two, high-current, 8-bit LED drivers. On the receiver side, the MAX86174A consists of two optical readout channels that can operate simultaneously while the MAX86174B has a single optical readout channel. The devices have low-noise, charge-integrating analog front-end, 20-bit ADC, and best-in-class ambient-light cancellation (ALC) circuits.

Due to the low power consumption, compact size, ease and flexibility of use, the MAX86174A/MAX86174B are ideal for a wide variety of optical sensing applications such as pulse oximetry and heart-rate detection.

The MAX86174A/MAX86174B operate on a 1.8V main supply voltage and a 2.7V to 5.5V LED driver supply voltage. The devices support both I<sup>2</sup>C- and SPI-compatible interfaces in a fully autonomous way. The devices have a large 256-word built-in FIFO. The MAX86174A/MAX86174B are available in a compact 16-WLP package.

#### **Applications**

- Wearable Devices for Fitness, Wellness and Medical Applications

- Clinical Accuracy

- · Suitable for Wrist, Finger, Ear, and Other Locations

- Optimized Performance to Detect

- Optical Heart Rate

- Heart-Rate Variability

- Oxygen Saturation (SpO<sub>2</sub>)

- Body Hydration

- Muscle and Tissue Oxygen Saturation (SmO<sub>2</sub> and StO<sub>2</sub>)

- Maximum Oxygen Consumption (VO2 Max)

### **Benefits and Features**

- Complete Optical Data Acquisition System

- Ultra-Low-Power Operation for Body Wearable Devices

- Low-Power-Operation, Optical Readout Channel < 11μA (typ) at 25fps

- Exposure Integration Period Ranging from 14.6µs to 117.1µs

- Low Shutdown Current < 1µA (typ)</li>

- Excellent Top-End Dynamic Range > 93dB in White Card Loop-Back Test (Nyquist Sample-to-Sample Variance)

- Extended Dynamic Range up to 111dB (Averaging and Off-Chip Filtering) to Enable SpO<sub>2</sub> on Wrist/Chest for Low Perfusion Cases

- Support Frame Rates from 1fps to 2048fps

- High-Resolution 20-Bit Charge-Integrating ADCs

- Support Both Burst Averaging and Decimation Averaging Modes

- On-Chip 12Hz Low-Pass Filter for Improved SNR and Reduced Power for Continuous Heart-Rate Measurement

- Supports Two PD Inputs for Multi-Parameter Measurements

- Supports Four LED Driver Output Pins Generated from Two 8-Bit LED Current Drivers

- Low Dark-Current Noise of < 50pA<sub>RMS</sub> (Sample-to-Sample Variance in 117.1µs Integration Time)

- Excellent Ambient Range and Rejection Capability

- 200µA Ambient Photodiode Current

- > 70dB Ambient Rejection at 120Hz (Burst Average > 2)

- Miniature 1.67mm x 1.78mm, 0.4mm Ball Pitch, 4 x 4 WLP Package

- -40°C to +85°C Operating Temperature Range

### **Simplified Block Diagram**

#### MAX86174A

#### **MAX86174B**

### **TABLE OF CONTENTS**

| General Description                                  |    |

|------------------------------------------------------|----|

| Applications                                         |    |

| Benefits and Features                                |    |

| Simplified Block Diagram                             |    |

| Absolute Maximum Ratings                             |    |

| Package Information                                  |    |

| 16 WLP                                               | 7  |

| Electrical Characteristics                           |    |

| Typical Operating Characteristics                    |    |

| Pin Configuration                                    |    |

| MAX86174A/MAX86174B                                  |    |

| Pin Description                                      |    |

| Detailed Description                                 |    |

| Optical Transmitter Overview                         |    |

| Optical Receiver Overview                            |    |

| Photodiode Biasing                                   |    |

| Measurement Configuration and Timing                 | 20 |

| Ambient-Light Cancellation                           | 21 |

| Frame and Frame Rate                                 | 22 |

| On-Chip Averaging                                    | 23 |

| Burst Average                                        | 24 |

| Decimation Average                                   | 24 |

| On-Chip Filtering                                    |    |

| ADC Decimation Filter                                |    |

| Digital Low-Pass Filter                              |    |

| AFE Exposure Control and SNR                         | 26 |

| Threshold Detect Function                            |    |

| Automatic Proximity Detect Mode                      | 28 |

| Synchronization Modes                                | 29 |

| Internal Frame Oscillator and Divider Mode           | 29 |

| External Frame Trigger Input Mode                    |    |

| External Frame Clock Input Mode                      | 29 |

| FIFO Description                                     | 29 |

| Digital Interface                                    |    |

| SPI/I <sup>2</sup> C Selection for Serial Interface  |    |

| SPI Interface                                        |    |

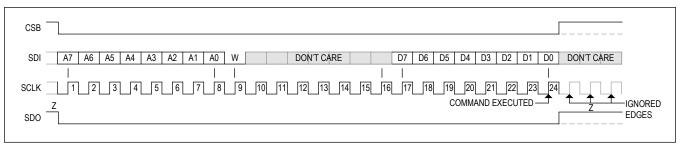

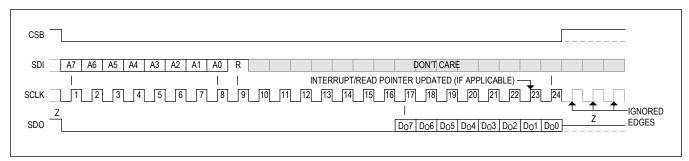

| Single Word SPI Register Read and Write Transactions |    |

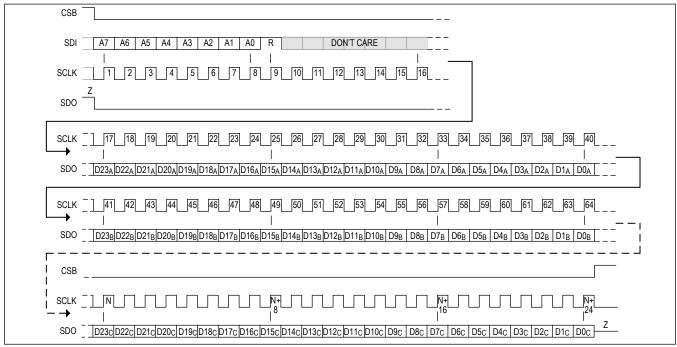

| SPI Burst Mode Read Transaction                      |    |

| I <sup>2</sup> C-/SMBus-Compatible Serial Interface  |    |

# Best-in-Class Optical Pulse Oximeter and Heart-Rate Sensor AFE for Wearable Health

## TABLE OF CONTENTS (CONTINUED)

| Bit Transfer                       | 36 |

|------------------------------------|----|

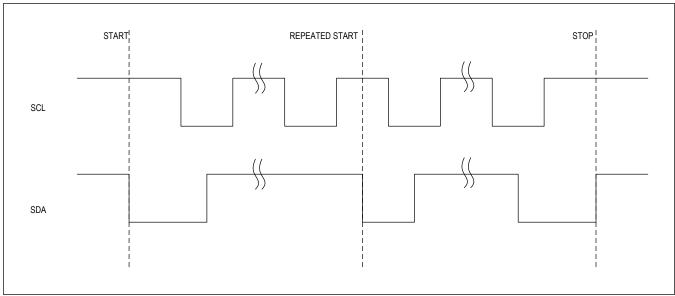

| START and STOP Conditions          | 36 |

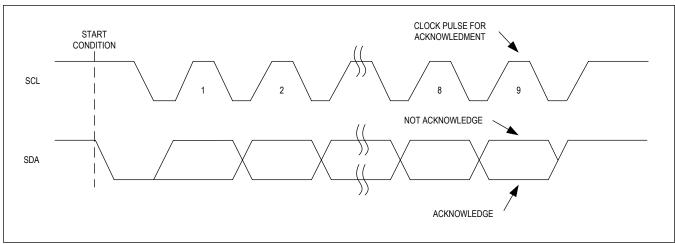

| Acknowledge Bit                    | 37 |

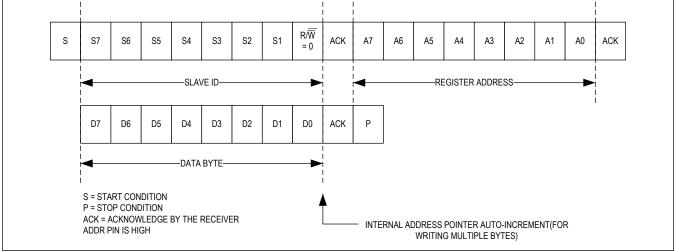

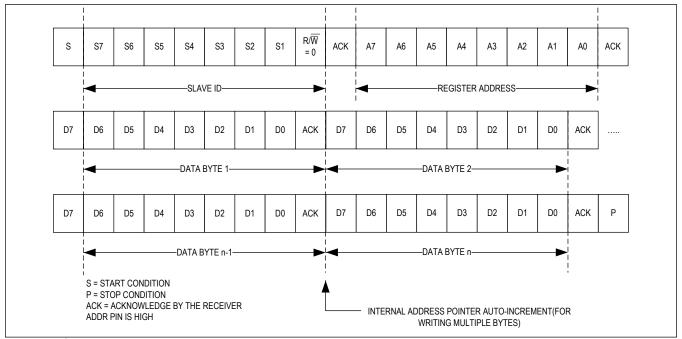

| I <sup>2</sup> C Write Data Format | 38 |

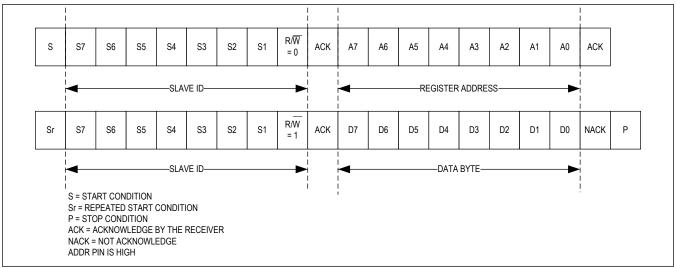

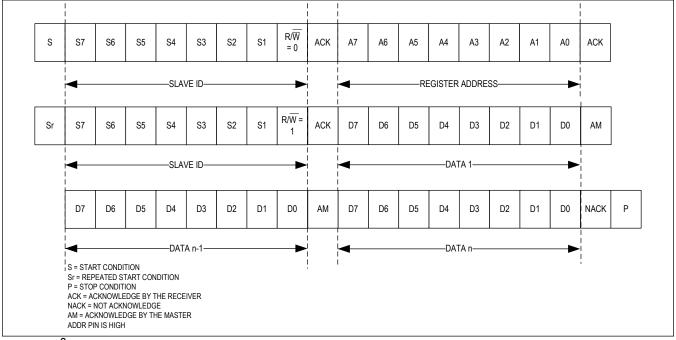

| I <sup>2</sup> C Read Data Format  | 39 |

| I <sup>2</sup> C Broadcast         | 40 |

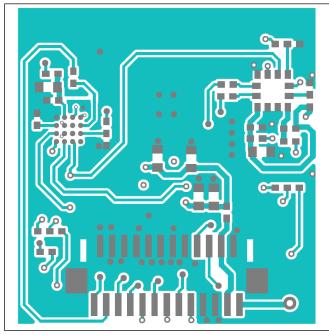

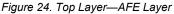

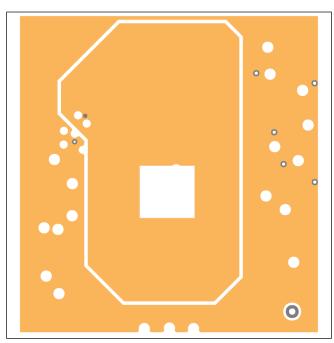

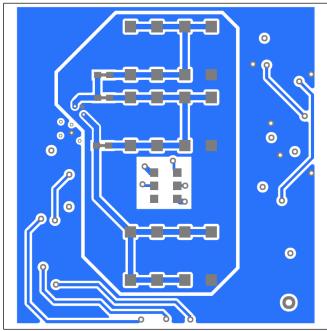

| Layout Guidelines                  | 41 |

| Register Map                       | 43 |

| User Register Map                  | 43 |

| Register Details                   | 46 |

| Typical Application Circuits       | 85 |

| MAX86174A/MAX86174B                | 85 |

| Ordering Information               | 85 |

| Revision History                   | 86 |

|                                    |    |

# Best-in-Class Optical Pulse Oximeter and Heart-Rate Sensor AFE for Wearable Health

### LIST OF FIGURES

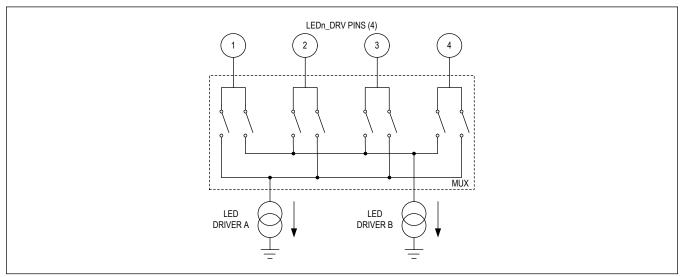

| Figure 1. LED Drivers                                                  |    |

|------------------------------------------------------------------------|----|

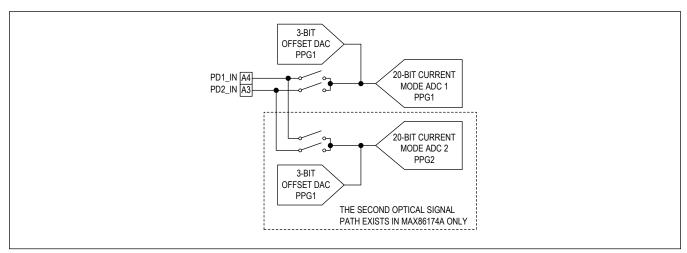

| Figure 2. On-Chip Mux for the PD1_IN and PD2_IN pins                   |    |

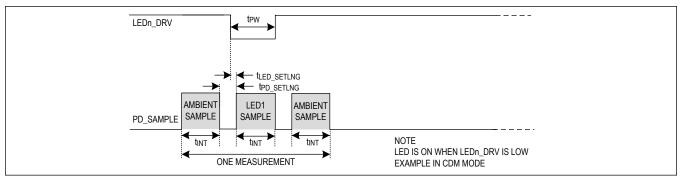

| Figure 3. Measurement with One LED On                                  |    |

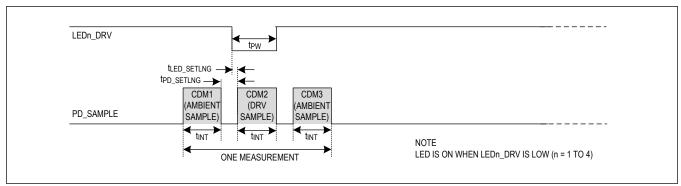

| Figure 4. Central Difference Method (CDM)                              |    |

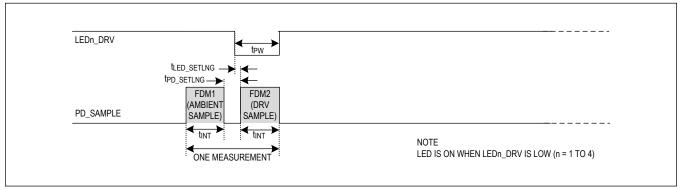

| Figure 5. Forward Difference Method (FDM)                              | 22 |

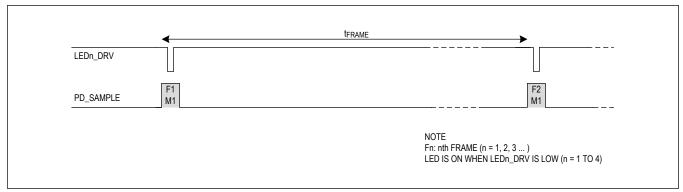

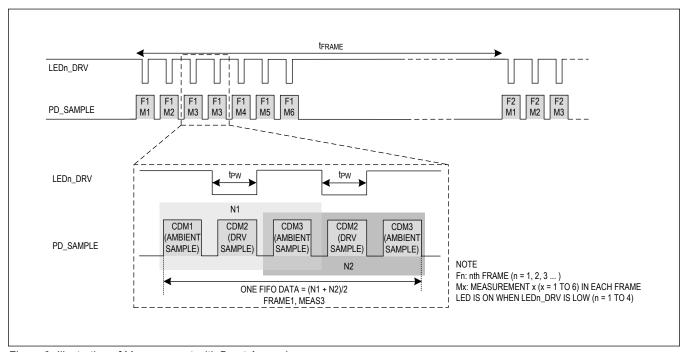

| Figure 6. Frame with One Measurement                                   | 23 |

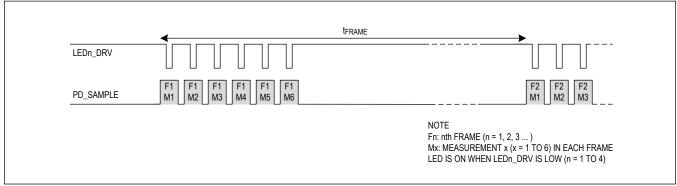

| Figure 7. Frame with Six Measurements                                  | 23 |

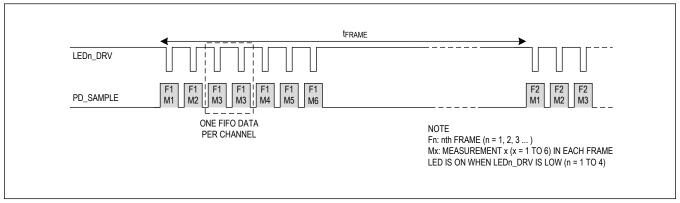

| Figure 8. Frame with Measurement Burst Averaging                       |    |

| Figure 9. Illustration of Measurement with Burst Averaging             |    |

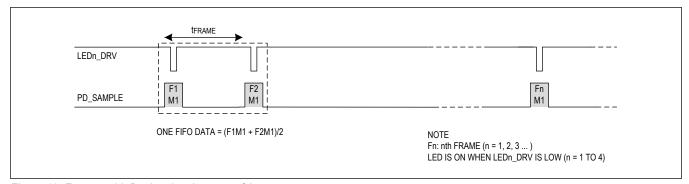

| Figure 10. Frames with Decimation Average of 2                         |    |

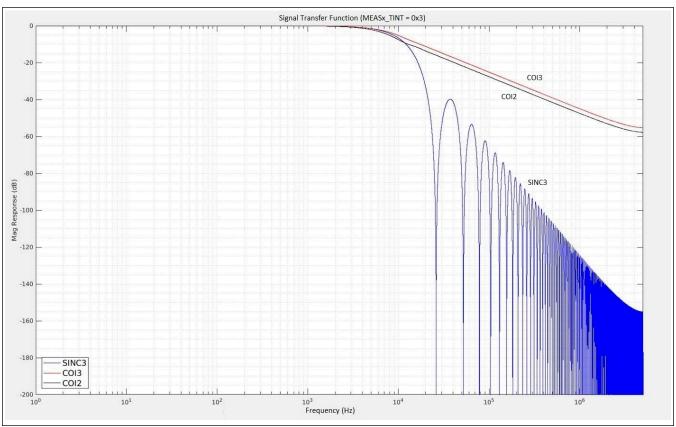

| Figure 11. Signal Transfer Function of Decimation Filters              |    |

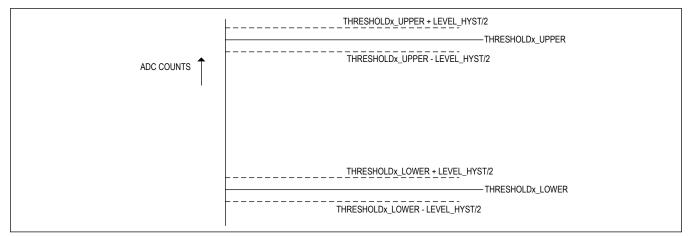

| Figure 12. Threshold limits with LEVEL_HYST                            | 28 |

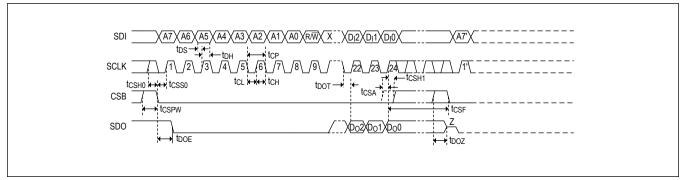

| Figure 13. Detailed SPI Timing Diagram                                 |    |

| Figure 14. SPI Write Transaction                                       |    |

| Figure 15. SPI Read Transaction                                        |    |

| Figure 16. SPI FIFO Burst Mode Read Transaction                        |    |

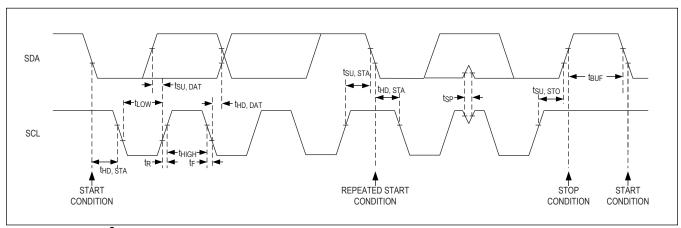

| Figure 17. Detailed I <sup>2</sup> C Timing Diagram                    |    |

| Figure 18. I <sup>2</sup> C START, STOP, and REPEATED START Conditions |    |

| Figure 19. I <sup>2</sup> C Acknowledge Bit                            |    |

| Figure 20. I <sup>2</sup> C Single Byte Write Transaction              |    |

| Figure 21. I <sup>2</sup> C Multi-Byte Write Transaction               |    |

| Figure 22. I <sup>2</sup> C Single Byte Read Transaction               | 40 |

| Figure 23. I <sup>2</sup> C Multi-Byte Read Transaction                |    |

| Figure 24. Top Layer—AFE Layer                                         |    |

| Figure 25. Layer 5—Pseudo PD_GND Shields PD_IN                         |    |

| Figure 26. Bottom Laver—Optics Laver                                   | 42 |

# Best-in-Class Optical Pulse Oximeter and Heart-Rate Sensor AFE for Wearable Health

# LIST OF TABLES

| Table 1. LED Driver and LED Mux Configuration       |    |

|-----------------------------------------------------|----|

| Table 2. LED Driver Full-Scale Range Trade-Off      | 18 |

| Table 3. Configuration for ADC Decimation Filter    | 25 |

| Table 4. Typical SNR Benefit Of Various Parameters  | 26 |

| Table 5. Clock Sources in Each Synchronization Mode | 29 |

| Table 6. FIFO Tags                                  | 30 |

| Table 7. Slave Addresses for I <sup>2</sup> C Mode  | 33 |

|                                                     |    |

Analog Devices | 6 www.analog.com

# Best-in-Class Optical Pulse Oximeter and Heart-Rate Sensor AFF for Wearable Health

### **Absolute Maximum Ratings**

| V <sub>DD</sub> to GND              | 0.3V to +2.2V                     |

|-------------------------------------|-----------------------------------|

| V <sub>I FD</sub> to PGND           | 0.3V to +6.0V                     |

| PGND to GND                         | 0.3V to +0.3V                     |

| VREF to GND                         | 0.3V to +2.2V                     |

| LEDn_DRV (n = 1 to 4), TRIG to PGND | 0.3V to (V <sub>LED</sub> + 0.3V) |

| PDm_IN to GND (m = 1, 2)            | 0.3V to +2.2V                     |

| SDO/ADDR to GND                     | 0.3V to (V <sub>DD</sub> + 0.3V)  |

| SDI/SDA, SCLK/SCL, CSB/I2C_SEL, INTB to GND0.3V            | ' to |

|------------------------------------------------------------|------|

| +(                                                         | 6V   |

| Output Short-Circuit DurationContinuo                      | us   |

| Continuous Input Current into Any Pin (except LEDn_DRV Pir | ns,  |

| n = 1 to 4)±50n                                            | nΑ   |

| Operating Temperature Range40°C to +85                     | °C   |

| Storage Temperature Range40°C to +150                      | °C   |

| Soldering Temperature (reflow)+260                         | °C   |

|                                                            |      |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### **16 WLP**

| Package Code                           | N161B1+1                       |

|----------------------------------------|--------------------------------|

| Outline Number                         | <u>21-100454</u>               |

| Land Pattern Number                    | Refer to Application Note 1891 |

| THERMAL RESISTANCE, FOUR-LAYER BOARD   |                                |

| Junction to Ambient (θ <sub>JA</sub> ) | 57.93°C/W                      |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{DD}$  = 1.8V,  $V_{LED}$  = 5.0V, MEASx\_PPGy\_ADC\_RGE = 16 $\mu$ A, FR\_CLK\_DIV = 32 (f<sub>FRAME</sub> = 1024fps), MEASx\_TINT = 14.6 $\mu$ s, MEASx\_LED\_SETLNG = 6 $\mu$ s, MEASx\_LED\_RGE = 128 $\mu$ A, C<sub>PD</sub> = 65 $\mu$ F, T<sub>A</sub> = +25°C, min/max are from T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 1, 2, 3)

| PARAMETER            | SYMBOL           | CONDITIONS                | MIN | TYP | MAX | UNITS |

|----------------------|------------------|---------------------------|-----|-----|-----|-------|

| POWER SUPPLY         |                  |                           |     |     |     |       |

| Power-Supply Voltage | V <sub>DD</sub>  | Verified during PSRR Test | 1.7 | 1.8 | 2.0 | V     |

| LED-Supply Voltage   | V <sub>LED</sub> | Verified during PSRR Test | 2.7 |     | 5.5 | V     |

## **Electrical Characteristics (continued)**

( $V_{DD}$  = 1.8V,  $V_{LED}$  = 5.0V, MEASx\_PPGy\_ADC\_RGE = 16µA, FR\_CLK\_DIV = 32 (f<sub>FRAME</sub> = 1024fps), MEASx\_TINT = 14.6µs, MEASx\_LED\_SETLNG = 6µs, MEASx\_LED\_RGE = 128mA,  $C_{PD}$  = 65pF,  $T_A$  = +25°C, min/max are from  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 1, 2, 3)

| PARAMETER                                  | SYMBOL                                           | COND                                                     | ITIONS                 | MIN                    | TYP  | MAX | UNITS      |    |

|--------------------------------------------|--------------------------------------------------|----------------------------------------------------------|------------------------|------------------------|------|-----|------------|----|

|                                            |                                                  | Single channel,                                          | FR = 512fps            |                        | 95   | 150 |            |    |

|                                            |                                                  | one Measure/                                             | FR = 64fps             |                        | 17   |     | μΑ         |    |

|                                            |                                                  | Frame (Note 5a)                                          | FR = 8fps              |                        | 3.5  |     |            |    |

|                                            |                                                  | Single channel,                                          | FR = 512fps            |                        | 300  | 420 |            |    |

|                                            |                                                  | four Measures/                                           | FR = 64fps             |                        | 40   |     |            |    |

| Average V <sub>DD</sub> Supply             |                                                  | Frame (Note 5a)                                          | FR = 8fps              |                        | 6.5  |     | μA         |    |

| Current                                    | I <sub>DD</sub>                                  | Dual channel, one                                        | FR = 512fps            |                        | 150  | 210 |            |    |

|                                            |                                                  | Measure/Frame                                            | FR = 64fps             |                        | 24   |     |            |    |

|                                            |                                                  | (Note 5b)                                                | FR = 8fps              |                        | 4.5  |     | ] <b>,</b> |    |

|                                            |                                                  | Dual channel, four                                       | FR = 512fps            |                        | 480  | 650 | μA         |    |

| 1                                          |                                                  | Measures/Frame                                           | FR = 64fps             |                        | 60   |     | -          |    |

|                                            |                                                  | (Note 5b)                                                | FR = 8fps              |                        | 9.5  |     |            |    |

|                                            |                                                  | Single Channel,                                          | FR = 512fps            |                        | 870  |     |            |    |

| Average V <sub>LED</sub> Supply<br>Current | I <sub>LED</sub>                                 | one LED/Frame,<br>MEASx_LED_SET                          | FR = 64fps             |                        | 98   |     | μA         |    |

| Current                                    |                                                  | LNG = 1 (Note 5a)                                        | FR = 8fps              |                        | 12.5 |     |            |    |

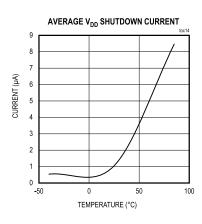

| V <sub>DD</sub> Current in<br>Shutdown     | I <sub>DD_SHDN</sub>                             | T <sub>A</sub> = +25°C                                   | , , ,                  |                        | 1.0  | 3   | μА         |    |

| V <sub>LED</sub> Current in<br>Shutdown    | I <sub>LED_SHDN</sub>                            | T <sub>A</sub> = +25°C                                   |                        |                        |      | 0.5 | μА         |    |

| LED DRIVER                                 |                                                  |                                                          |                        |                        |      |     |            |    |

| LED Current Resolution                     |                                                  |                                                          |                        |                        | 8    |     | bits       |    |

| Driver DNL                                 | DNL <sub>TX</sub>                                | MEASx_LED_RGE :                                          | = 0x3                  | -1                     |      | +1  | LSB        |    |

| Driver INL                                 | INL <sub>TX</sub>                                | MEASx_LED_RGE :                                          | = 0x3                  |                        | 1    |     | LSB        |    |

|                                            |                                                  |                                                          | MEASx_LED_RGE<br>= 0x0 |                        | 32   |     |            |    |

| Full Cools I FD Current                    | LED Current I <sub>LED</sub> MEASx_DRVy_P = 0xFF | MFASx DRVv PA                                            | MEASx_LED_RGE<br>= 0x1 |                        | 64   |     | 1          |    |

| ruii-Scale LED Current                     |                                                  |                                                          | = 0xFF                 | MEASx_LED_RGE<br>= 0x2 |      | 96  |            | mA |

|                                            |                                                  |                                                          | MEASx_LED_RGE<br>= 0x3 | 120                    | 128  | 136 |            |    |

| LED Driver Rise Time                       |                                                  | MEASx_DRVy_PA = 0xFF, 10% to 90%, all LED range settings |                        |                        |      | 3   | μs         |    |

| LED Driver Fall Time                       |                                                  | MEASx_DRVy_PA = all LED range setting                    |                        |                        |      | 3   | μs         |    |

## **Electrical Characteristics (continued)**

( $V_{DD}$  = 1.8V,  $V_{LED}$  = 5.0V, MEASx\_PPGy\_ADC\_RGE = 16µA, FR\_CLK\_DIV = 32 (f<sub>FRAME</sub> = 1024fps), MEASx\_TINT = 14.6µs, MEASx\_LED\_SETLNG = 6µs, MEASx\_LED\_RGE = 128mA,  $C_{PD}$  = 65pF,  $T_A$  = +25°C, min/max are from  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 1, 2, 3)

| PARAMETER                          | SYMBOL                                                                     | COND                                                                        | ITIONS                 | MIN           | TYP   | MAX           | UNITS |  |

|------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------|---------------|-------|---------------|-------|--|

|                                    |                                                                            |                                                                             | MEASx_LED_RGE<br>= 0x0 |               | 135   |               |       |  |

| Minimum Output                     |                                                                            | MEASx_DRVy_PA<br>= 0xFF, < 1%                                               | MEASx_LED_RGE<br>= 0x1 |               | 260   |               | mV    |  |

| Voltage                            | V <sub>OL</sub>                                                            | change in LED current                                                       | MEASx_LED_RGE<br>= 0x2 |               | 380   |               |       |  |

|                                    |                                                                            |                                                                             | MEASx_LED_RGE<br>= 0x3 |               | 500   | 800           |       |  |

|                                    |                                                                            |                                                                             | MEASx_LED_RGE<br>= 0x0 |               | ±5    |               | μA/V  |  |

| LED Driver DC V <sub>LED</sub>     |                                                                            | MEASx_DRVy_PA<br>= 0xFF, V <sub>DD</sub> =                                  | MEASx_LED_RGE<br>= 0x1 |               | ±5    |               |       |  |

| PSR                                |                                                                            | 1.8V, V <sub>LEDn_DRV</sub> = -<br>1.2V, V <sub>LED</sub> = 3.1V<br>to 5.5V | MEASx_LED_RGE<br>= 0x2 |               | ±5    |               | μA/V  |  |

|                                    |                                                                            |                                                                             | MEASx_LED_RGE<br>= 0x3 | -150          |       | +150          |       |  |

|                                    |                                                                            | MEASx_LED_RGE :                                                             | = 0x0                  | 120           | 148   | 180           | mV    |  |

| LED Driver Compliance              |                                                                            | MEASx_LED_RGE :                                                             | = 0x1                  | 260           | 287   | 320           |       |  |

| Interrupt Threshold                |                                                                            | MEASx_LED_RGE :                                                             | = 0x2                  | 395           | 425   | 460           |       |  |

|                                    |                                                                            | MEASx_LED_RGE :                                                             | = 0x3                  | 530           | 560   | 600           | 1     |  |

| READOUT CHANNEL                    |                                                                            |                                                                             |                        |               |       |               |       |  |

| ADC Resolution                     |                                                                            |                                                                             |                        |               | 20    |               | bits  |  |

| INL                                | INL <sub>RX</sub>                                                          | MEASx_TINT = 117                                                            | .1µs                   |               | ±10   |               | LSB   |  |

| IINL                               | INCRX                                                                      | MEASx_TINT = 14.6                                                           | βμs                    |               | ±40   |               | LOD   |  |

| DNL                                | DNL <sub>RX</sub>                                                          | MEASx_TINT = 117                                                            | .1µs                   |               | ±3    |               | LSB   |  |

| DIVL                               | DNLRX                                                                      | MEASx_TINT = 14.6                                                           | βμs                    |               | ±10   |               | LOD   |  |

|                                    |                                                                            | MEASx_PPGy_ADC                                                              | _RGE = 0x0             |               | 4.0   |               |       |  |

| ADC Full-Scale Input               | I <sub>FS</sub>                                                            | MEASx_PPGy_ADC                                                              | _RGE = 0x1             |               | 8.0   |               | μA    |  |

| Current                            | 'F5<br>                                                                    | MEASx_PPGy_ADC                                                              |                        |               | 16.0  |               | μΛ    |  |

|                                    |                                                                            | MEASx_PPGy_ADC                                                              | _RGE = 0x3             |               | 32.0  |               |       |  |

|                                    |                                                                            | MEASx_TINT = 0x0                                                            |                        |               | 14.6  |               |       |  |

| ADC Integration Time               | Time $t_{INT} = \frac{\text{MEASx\_TINT} = 0x1}{\text{MEASx\_TINT} = 0x2}$ |                                                                             |                        | 29.2          |       | μs            |       |  |

| 7.50 megration rime                |                                                                            | MEASx_TINT = 0x2                                                            |                        |               | 58.6  |               | μο    |  |

|                                    |                                                                            | MEASx_TINT = 0x3                                                            |                        |               | 117.1 |               |       |  |

| Minimum Free-Running<br>Frame Rate |                                                                            |                                                                             |                        |               | 1     |               | fps   |  |

| Maximum Free-Running Frame Rate    |                                                                            |                                                                             |                        |               | 2048  |               | fps   |  |

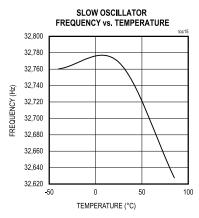

| Internal Frame-Rate<br>Clock       | fFRAME_CLK                                                                 |                                                                             |                        | -2% of<br>typ | 32768 | +2% of<br>typ | Hz    |  |

## **Electrical Characteristics (continued)**

( $V_{DD}$  = 1.8V,  $V_{LED}$  = 5.0V, MEASx\_PPGy\_ADC\_RGE = 16µA, FR\_CLK\_DIV = 32 (f<sub>FRAME</sub> = 1024fps), MEASx\_TINT = 14.6µs, MEASx\_LED\_SETLNG = 6µs, MEASx\_LED\_RGE = 128mA,  $C_{PD}$  = 65pF,  $T_A$  = +25°C, min/max are from  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 1, 2, 3)

| PARAMETER                               | SYMBOL             | COND                                                              | ITIONS                           | MIN                   | TYP  | MAX   | UNITS             |

|-----------------------------------------|--------------------|-------------------------------------------------------------------|----------------------------------|-----------------------|------|-------|-------------------|

| TRIG External Frame-<br>Clock Frequency | fTRIG_EXT_CL<br>K  |                                                                   |                                  |                       |      | 34000 | Hz                |

| TRIG Pulse Width                        | t <sub>TRIG</sub>  |                                                                   |                                  | 1                     |      |       | μs                |

| Internal Power-Up Time                  |                    |                                                                   |                                  |                       | 200  |       | μs                |

| ADC Clock Frequency                     | CLK                |                                                                   |                                  | 9.75                  | 10.0 | 10.25 | MHz               |

| Maximum DC-Ambient-<br>Light Rejection  | ALR                | ALC_OVF = 1                                                       |                                  |                       | 200  |       | μА                |

| Dynamic Ambient-Light Rejection         |                    | I <sub>EXPOSURE</sub> = 1μA, I<br>with ±0.4μA <sub>P-P</sub> 120F | AMBIENT = 1µA DC<br>Iz sine wave |                       | 80   |       | dB                |

| DC Ambient-Light<br>Rejection           |                    | I <sub>EXPOSURE</sub> = 1μA, I<br>30μA                            | AMBIENT = 1µA and                |                       | 0.5  |       | nA                |

| Dark-Current Offset                     | DC_O               | PDm_BIAS = 0x1, t <sub>II</sub>                                   | NT = 117.1µs                     |                       | ±1   |       | Counts            |

|                                         |                    | MEASx_TINT = 14.6                                                 | iµs                              |                       | 212  |       |                   |

| Dark-Current Input-                     |                    | MEASx_TINT = 29.2                                                 | 2µs                              |                       | 150  |       | pA <sub>RMS</sub> |

| Referred Noise                          |                    | MEASx_TINT = 58.6                                                 | βμs                              |                       | 106  |       |                   |

|                                         |                    | MEASx_TINT = 117                                                  | .1µs                             |                       | 75   |       | pA <sub>RMS</sub> |

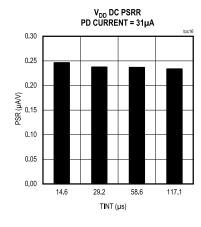

|                                         |                    |                                                                   | t <sub>INT</sub> = 14.6μs        |                       | 1100 |       | - LSB/V           |

| V                                       |                    | I <sub>EXPOSURE</sub> = 1μA,                                      | t <sub>INT</sub> = 29.2µs        |                       | 750  |       |                   |

| V <sub>DD</sub> DC PSR                  |                    | $V_{DD} = 1.7V \text{ to } 2.0V$                                  | t <sub>INT</sub> = 58.6µs        |                       | 530  |       |                   |

|                                         |                    |                                                                   | t <sub>INT</sub> = 117.1μs       |                       | 410  | 800   |                   |

| DIGITAL I/O CHARACTE                    | RISTICS            |                                                                   | •                                | •                     |      |       | •                 |

| Input-Voltage Low                       | V <sub>IL</sub>    | SDI/SDA, SCLK/SCI<br>I2C_SEL                                      | L, TRIG, CSB/                    |                       |      | 0.4   | V                 |

| Input-Voltage High                      | V <sub>IH</sub>    | SDI/SDA, SCLK/SCI<br>I2C_SEL                                      | L, TRIG, CSB/                    | 1.4                   |      |       | V                 |

| Input Hysteresis                        | V <sub>HYS</sub>   | SDI/SDA, SCLK/SCI<br>I2C_SEL                                      | L, TRIG, CSB/                    |                       | 430  |       | mV                |

| Input Capacitance                       | C <sub>IN</sub>    | SDI/SDA, SCLK/SCI<br>I2C_SEL                                      | L, TRIG, CSB/                    |                       | 10   |       | pF                |

| Input-Leakage Current                   | I <sub>IN</sub>    | SDI/SDA, SCLK/SCI<br>I2C_SEL. T <sub>A</sub> = +25°               |                                  | -1                    | 0.01 | +1    | μA                |

| Output-Low Voltage                      | V <sub>OL</sub>    | SDO, INTB, SDI/SD/<br>I <sub>SINK</sub> = 4mA                     | A (in I <sup>2</sup> C mode ),   |                       |      | 0.4   | V                 |

| Output-High Voltage                     | V <sub>OH</sub>    | SDO, INTB, I <sub>SOURCE</sub> = 4mA                              |                                  | V <sub>DD</sub> - 0.4 |      |       | V                 |

| Open-Drain Output-Low<br>Voltage        | V <sub>OL_OD</sub> | INTB_OCFG = 0x0, I <sub>SINK</sub> = 4mA                          |                                  |                       |      | 0.4   | V                 |

| SPI TIMING CHARACTE                     | RISTICS (Note 4    | )                                                                 |                                  | •                     |      |       | •                 |

| SCLK Frequency                          | f <sub>SCLK</sub>  |                                                                   |                                  |                       |      | 24    | MHz               |

| SCLK Period                             | t <sub>CP</sub>    |                                                                   |                                  | 41.7                  |      |       | ns                |

| SCLK Pulse-Width High                   | t <sub>CH</sub>    |                                                                   |                                  | 18                    |      |       | ns                |

## **Electrical Characteristics (continued)**

( $V_{DD}$  = 1.8V,  $V_{LED}$  = 5.0V, MEASx\_PPGy\_ADC\_RGE = 16µA, FR\_CLK\_DIV = 32 (f<sub>FRAME</sub> = 1024fps), MEASx\_TINT = 14.6µs, MEASx\_LED\_SETLNG = 6µs, MEASx\_LED\_RGE = 128mA,  $C_{PD}$  = 65pF,  $T_A$  = +25°C, min/max are from  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 1, 2, 3)

| PARAMETER                                             | SYMBOL              | CONDITIONS                                                                  | MIN | TYP | MAX | UNITS |

|-------------------------------------------------------|---------------------|-----------------------------------------------------------------------------|-----|-----|-----|-------|

| SCLK Pulse-Width Low                                  | t <sub>CL</sub>     |                                                                             | 18  |     | ns  |       |

| CSB Fall to SCLK Rise<br>Setup Time                   | t <sub>CSS0</sub>   | Applies to 1st SCLK rising edge after CSB goes low                          | 20  |     |     | ns    |

| CSB Fall to SCLK Rise<br>Hold Time                    | t <sub>CSH0</sub>   | Applies to inactive rising edge preceding 1st rising edge                   | 5   |     |     | ns    |

| Last SCLK Rise to CSB<br>Rise                         | t <sub>CSH1</sub>   | Applies to last SCLK rising edge in a transaction                           | 20  |     |     | ns    |

| Last SCLK Rise to next<br>CSB Fall                    | t <sub>CSF</sub>    | Applies to last SCLK rising edge to next CSB falling edge (new transaction) | 60  |     |     | ns    |

| CSB Pulse-Width High                                  | t <sub>CSPW</sub>   |                                                                             | 40  |     |     | ns    |

| SDI to SCLK Rise Setup<br>Time                        | $t_{DS}$            |                                                                             | 5   |     |     | ns    |

| SDI to SCLK Rise Hold<br>Time                         | t <sub>DH</sub>     |                                                                             | 5   |     |     | ns    |

| SCLK Fall to SDO<br>Transition                        | t <sub>DOT</sub>    | C <sub>LOAD</sub> = 30pF                                                    |     |     | 15  | ns    |

| CSB Fall to SDO<br>Enabled                            | t <sub>DOE</sub>    | C <sub>LOAD</sub> = 0pF                                                     | 20  |     |     | ns    |

| CSB Rise to SDO Hi-Z                                  | t <sub>DOZ</sub>    | Disable Time                                                                |     |     | 5   | ns    |

| I <sup>2</sup> C TIMING CHARACTER                     | RISTICS (Note 4     | l)                                                                          |     |     |     |       |

| I <sup>2</sup> C Write Address                        |                     | ADDR = 0                                                                    |     | D4  |     | Hex   |

| 1 6 Wille Address                                     |                     | ADDR = 1                                                                    |     | D6  |     | TICX  |

| I <sup>2</sup> C Read Address                         |                     | ADDR = 0                                                                    |     | D5  |     | Hex   |

| 1 O Nead Address                                      |                     | ADDR = 1                                                                    |     | D7  |     | TICX  |

| Serial Clock Frequency                                | f <sub>SCL</sub>    |                                                                             | 0   |     | 400 | kHz   |

| Bus-Free Time Between<br>STOP and START<br>Conditions | t <sub>BUF</sub>    |                                                                             | 1.3 |     |     | μs    |

| Hold Time START and<br>Repeat START<br>Condition      | <sup>t</sup> HD,STA |                                                                             | 0.6 |     |     | μs    |

| SCL Pulse-Width Low                                   | t <sub>LOW</sub>    |                                                                             | 1.3 |     |     | μs    |

| SCL Pulse-Width High                                  | <sup>t</sup> HIGH   |                                                                             | 0.6 |     |     | μs    |

| Setup Time for a<br>Repeated START<br>Condition       | tsu,sta             |                                                                             | 0.6 |     |     | μs    |

| Data Hold Time                                        | t <sub>HD,DAT</sub> |                                                                             | 0   |     | 900 | ns    |

| Data Setup Time                                       | t <sub>SU,DAT</sub> |                                                                             | 100 |     |     | ns    |

| Setup Time for STOP<br>Condition                      | tsu,sto             |                                                                             | 0.6 |     |     | μs    |

| Pulse-Width of<br>Suppressed Spike                    | t <sub>SP</sub>     |                                                                             | 0   |     | 50  | ns    |

#### **Electrical Characteristics (continued)**

(V<sub>DD</sub> = 1.8V, V<sub>LED</sub> = 5.0V, MEASx\_PPGy\_ADC\_RGE = 16μA, FR\_CLK\_DIV = 32 (f<sub>FRAME</sub> = 1024fps), MEASx\_TINT = 14.6μs, MEASx\_LED\_SETLNG =  $6\mu$ s, MEASx\_LED\_RGE = 128mA,  $C_{PD}$  = 65pF,  $T_A$  =  $+25^{\circ}$ C, min/max are from  $T_A$  =  $-40^{\circ}$ C to  $+85^{\circ}$ C, unless otherwise noted.) (Note 1, 2, 3)

| PARAMETER                          | SYMBOL          | CONDITIONS | MIN                       | TYP | MAX | UNITS |

|------------------------------------|-----------------|------------|---------------------------|-----|-----|-------|

| Bus Capacitance                    | C <sub>B</sub>  |            |                           |     | 400 | pF    |

| SDA and SCL Receiving<br>Rise Time | t <sub>R</sub>  |            | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| SDA and SCL Receiving Fall Time    | t <sub>F</sub>  |            | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| SDA Transmitting Fall Time         | t <sub>TF</sub> |            | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

Note 1: All devices are 100% production tested at T<sub>A</sub> = +25°C. Specifications over temperature limits are guaranteed by Maxim Integrated's bench or proprietary automated test equipment (ATE) characterization.

Note 2: All other register settings are assumed to be POR defaults, unless otherwise noted.

Note 3: Definitions of terms:

- Frame = All measurements made during a particular wake-up interval.

- Sample = Ambient-light-corrected exposure measurement where both LED exposure and ambient-light ADC conversions

#### Register nomenclature:

- ADC\_RGE = Measurement of full-scale range as defined in the MEASx\_PPGy\_ADC\_RGE registers (x = 1 to 6, y = 1, 2). TINT = ADC integration time as defined in the MEASx\_TINT registers (x = 1 to 6).

- PDm BIAS = Photodiode bias setting register (m = 1 to 2).

- LED\_RGE = Measurement of full-scale range of the LED driver in the MEASx\_LED\_RGE register (x = 1 to 6). DRVy\_PA = Measurement of the LED driver DAC code in the MEASx\_DRVy\_PA register (x = 1 to 6, y = A, B, C). LED\_SETLNG = Measurement of the LED settling time in the MEASx\_LED\_SETLNG registers (x = 1 to 6).

- Note 4: For design guidance only. Not production tested.

#### Note 5: FR = PPG Frame Rate

- MEASx\_TINT = 14.6µs, MEASx\_LED\_RGE = 128mA, MEASx\_DRVy\_PA = 0x7F, PPG1\_PWRDN = 0, PPG2\_PWRDN =

- MEASx\_TINT = 14.6µs, MEASx\_LED\_RGE = 128mA, MEASx\_DRVy\_PA = 0x7F, PPG1\_PWRDN = 0, PPG2\_PWRDN =

Analog Devices | 12 www.analog.com

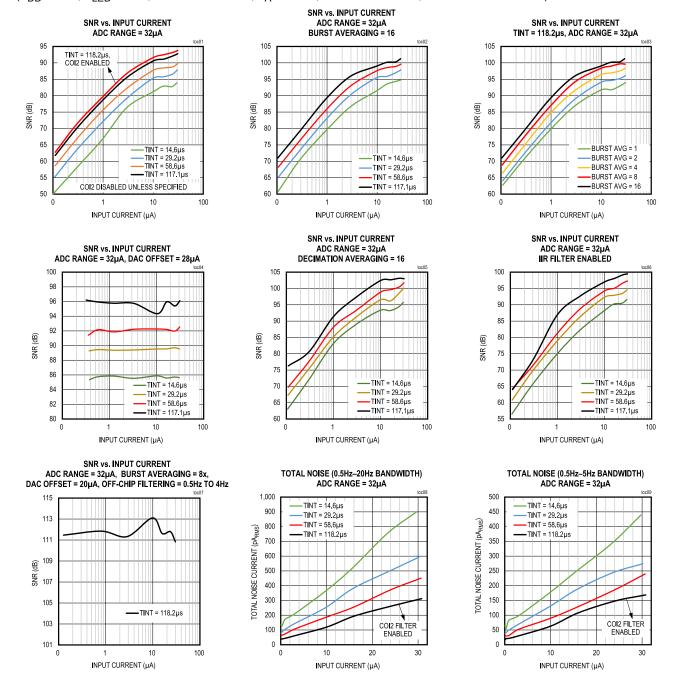

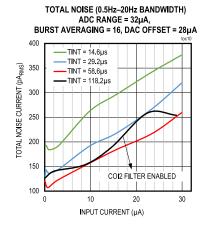

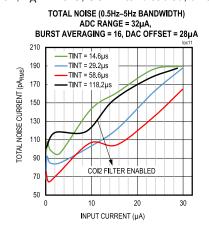

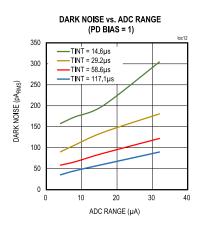

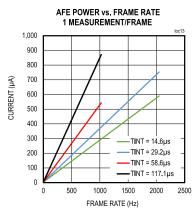

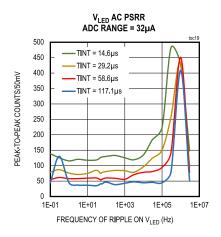

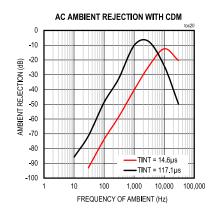

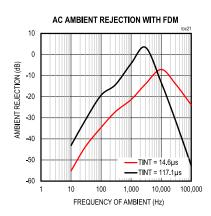

### **Typical Operating Characteristics**

(V<sub>DD</sub> = 1.8V, V<sub>LED</sub> = 5.0V, GND = PGND = 0V, T<sub>A</sub> = +25°C, COI2 filter disabled, unless otherwise noted.)

### **Typical Operating Characteristics (continued)**

(V<sub>DD</sub> = 1.8V, V<sub>LED</sub> = 5.0V, GND = PGND = 0V, T<sub>A</sub> = +25°C, COI2 filter disabled, unless otherwise noted.)

### **Typical Operating Characteristics (continued)**

(V<sub>DD</sub> = 1.8V, V<sub>LED</sub> = 5.0V, GND = PGND = 0V, T<sub>A</sub> = +25°C, COI2 filter disabled, unless otherwise noted.)

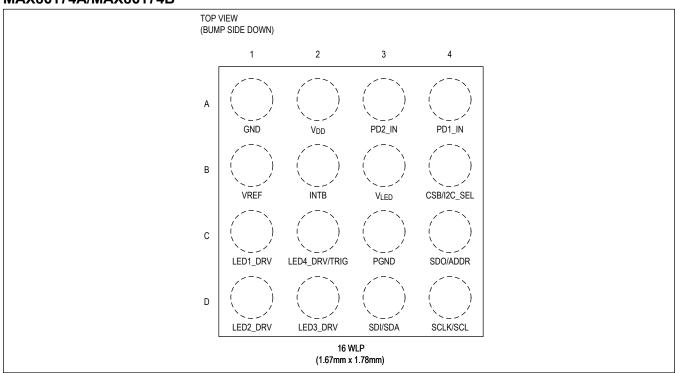

### **Pin Configuration**

#### MAX86174A/MAX86174B

# **Pin Description**

| PIN          | NAME             | FUNCTION                                                                                                                                                                                                                                |

|--------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER        |                  |                                                                                                                                                                                                                                         |

| A2           | V <sub>DD</sub>  | Power Supply. Connect to an externally regulated supply. Bypass with a 0.1µF capacitor as close as possible to the bump and a 10µF capacitor to GND.                                                                                    |

| A1           | GND              | Main Power Supply Return. Connect to PCB Ground. Refer to the <u>Layout Guidelines</u> section for more information.                                                                                                                    |

| В3           | V <sub>LED</sub> | LED Power Supply Input. In a configuration with more than one LED supply, connect V <sub>LED</sub> to the highest LED supply voltage. Bypass with a 10µF capacitor to PGND.                                                             |

| C3           | PGND             | LED Power Return. Connect to PCB Ground. Refer to the <u>Layout Guidelines</u> section for more information.                                                                                                                            |

| CONTROL INT  | ERFACE           |                                                                                                                                                                                                                                         |

| D4           | SCLK/SCL         | SPI Clock/I <sup>2</sup> C Clock                                                                                                                                                                                                        |

| C4           | SDO/ADDR         | SPI Data Output. In I <sup>2</sup> C mode, this pin selects the I <sup>2</sup> C device address.                                                                                                                                        |

| D3           | SDI/SDA          | SPI Data Input/I <sup>2</sup> C Data                                                                                                                                                                                                    |

| B4           | CSB/<br>I2C_SEL  | SPI Chip Select Input. The state of this pin sets the serial interface to typical levels. Low = SPI and High = $I^2C$ .                                                                                                                 |

| C2           | TRIG             | External Clock or Start of Conversion Trigger Input. Do not leave unconnected. Tie to GND or V <sub>DD</sub> when it is not used.                                                                                                       |

| B2           | INTB             | Interrupt Output. When INTB is not used, it can be left unconnected.                                                                                                                                                                    |

| OPTICAL PINS | 5                |                                                                                                                                                                                                                                         |

| A4           | PD1_IN           | Photodiode Cathode Input 1. Tie to GND when this pin is not used.                                                                                                                                                                       |

| A3           | PD2_IN           | Photodiode Cathode Input 2. Tie to GND when this pin is not used.                                                                                                                                                                       |

| C1           | LED1_DRV         | LED Output 1. Driven when MEASx_DRVy = 0 ( $x = 1$ to 6, $y = A$ , B). Connect the LED cathode to LED1_DRV and its anode to the V <sub>LED</sub> supply. This pin can be left unconnected when not used.                                |

| D1           | LED2_DRV         | LED Output 2. Driven when MEASx_DRVy = 1 ( $x = 1$ to 6, $y = A$ , B). Connect the LED cathode to LED2_DRV and its anode to the V <sub>LED</sub> supply. This pin can be left unconnected when not used.                                |

| D2           | LED3_DRV         | LED Output 3. Driven when MEASx_DRVy = 2 ( $x = 1$ to 6, $y = A$ , B). Connect the LED cathode to LED3_DRV and its anode to the V <sub>LED</sub> supply. This pin can be left unconnected when not used.                                |

| C2           | LED4_DRV         | LED Output 4. Driven when MEASx_DRVy = 3 (x = 1 to 6, y = A, B). Connect the LED cathode to LED4_DRV and its anode to the $V_{LED}$ supply. Do not leave unconnected when this pin is not used. When not used, tie to GND or $V_{DD}$ . |

| REFERENCE    |                  |                                                                                                                                                                                                                                         |

| B1           | VREF             | ADC Reference Buffer Output. Bypass to GND with a 1µF X5R ceramic capacitor.                                                                                                                                                            |

#### **Detailed Description**

The MAX86174A/MAX86174B are complete integrated optical data acquisition systems, ideal for various applications including optical pulse-oximetry and heart-rate detection applications. The devices are designed for the demanding requirements of wearable devices and require minimal external hardware components for integration into a wearable device.

The MAX86174A includes dual optical-readout channels operating simultaneously and the MAX86174B has a single optical-readout channel. Both devices incorporate robust ambient light cancellation and two high-current LED drivers to form a complete optical-readout signal chain. The two LED drivers support up to 4 LED drive output pins through two on-chip 4x1 multiplexers and control logic. Both devices support 2 PD input pins.

The MAX86174A/MAX86174B are fully adjustable through software registers and the digital output data is stored in a 256-word FIFO. The FIFO allows the MAX86174A/MAX86174B to be connected to a microcontroller or processor on a shared bus, I<sup>2</sup>C or SPI depending on the hardware selection on I2C\_SEL pin, on which the data is not being read continuously from the MAX86174A/MAX86174B registers. Both operate in fully autonomous mode for low-power battery applications.

The MAX86174A/MAX86174B operate on a 1.8V main supply voltage, with a separate 2.7V to 5.5V LED driver-supply voltage (supplied at  $V_{LED}$ ). Both devices have flexible exposure, timing and shutdown configurations as well as control of individual blocks to optimize measurements with minimum power consumption and a high level of accuracy. The MAX86174A/MAX86174B operate in a dynamic power-down mode, always powering down between frames; thus, minimizing power consumption. For more details on the power consumption at various frame rates, refer to the <u>Electrical Characteristics</u> table.

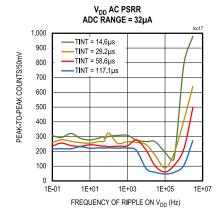

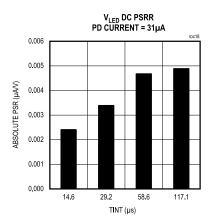

Keeping the ripple on the  $V_{LED}$  line as low as possible ensures the highest SNR is achieved. If a regulated supply is not available, the switching frequency on  $V_{LED}$  should be kept between 100kHz and 3MHz. By ensuring the switching frequency stays within the recommended range, along with a good load transient response, high SNR can be maintained at the heaviest loads (high LED drive-current applications).

The  $\underline{MAX20345}$  or the smaller  $\underline{MAX20343}$  are recommended solutions for a buck-boost supplying V<sub>LED</sub>. Both offer highly efficient buck-boost regulators with a very small load ripple, fast load transient responses, and have load pulse consistencies that provide more than 93dB SNR in a white card DC SNR test.

The various blocks and features in the PPG system are discussed in detail in the following sections.

#### **Optical Transmitter Overview**

The MAX86174A/MAX86174B have two independent precision LED current drivers that are connected to four LED-driver pins through two 4x1 muxes. Two LED current DACs modulate LED pulses for a variety of optical measurements. The two LED current DACs have 8-bit dynamic range with four programmable full-scale range settings of 32mA, 64mA, 96mA, and 128mA (typ). The configuration of the LED drivers can be uniquely set for each measurement. The PPG MEASx Setup (x = 1 to 6) register blocks (0x20 to 0x4E) define how each LED driver is connected for that particular measurement. Each measurement can drive one or both LED drivers.

Table 1. LED Driver and LED Mux Configuration

| MEASx_DRVy<br>(x = 1 to 6, y = A, B) | LEDn_DRV PIN CONNECTED TO LED DRIVER (n = 1 to 4) |

|--------------------------------------|---------------------------------------------------|

| 0x0                                  | LED1_DRV                                          |

| 0x1                                  | LED2_DRV                                          |

| 0x2                                  | LED3_DRV                                          |

| 0x3                                  | LED4_DRV                                          |

This configuration of LED drivers and LED muxes is highly flexible, not only allowing any of the four LED driver pins to be used at any one time, but also allowing for any pin to sink up to 256mA by combining both drivers to generate a higher output current. In this compact design, LED4\_DRV shares the same pin package with the TRIG input. If LED4\_DRV is in use, TRIGLED4\_SEL[0](0x17) is configured to be 1. Figure 1 shows how the two LED drivers are connected to the four LED-driver pins.

Both LED drivers are low dropout-current sources allowing for low-noise, power-supply independent LED currents to be sourced with minimal voltage overhead; thereby, minimizing LED power consumption. Four full-scale range settings are provided to allow for the optimization of LED driver noise, and dropout voltage on the LEDn\_DRV (n = 1 to 4) pins. <u>Table</u> 2 illustrates this trade-off.

| Table 2. L | <b>.ED</b> Driver | <b>Full-Scale</b> | Range | <b>Trade-Off</b> |

|------------|-------------------|-------------------|-------|------------------|

|------------|-------------------|-------------------|-------|------------------|

| FULL-SCALE RANGE (mA) | RECOMMENDED MINIMUM VLEDn_DRV (mV) | PEAK REFLECTOR CARD SNR (dB)<br>WITH COI2 FILTER ENABLED |

|-----------------------|------------------------------------|----------------------------------------------------------|

| 32                    | 300                                | 87                                                       |

| 64                    | 500                                | 91                                                       |

| 96                    | 700                                | 92                                                       |

| 128                   | 900                                | 93                                                       |

The LED on-time is the sum of the receiver integration time selected in MEASx\_TINT, and the LED settling time selected in MEASx\_LED\_SETLNG. The duty cycle is set by the ratio of the LED on-time and the frame period. The average LED supply current is calculated as the product of the programmed LED current and the duty cycle.

Note:  $MEASx\_TINT[4:3]$  (x = 1-6) is in registers 0x21, 0x29, 0x31, 0x39, 0x41, 0x49 and  $MEASx\_LED\_SETLNG[4:3]$  (x = 1-6) is in registers 0x23, 0x2B, 0x33, 0x3B, 0x43, 0x4B.

The voltage on  $V_{LED}$  depends on the forward voltage ( $V_F$ ) of the LEDs driven by the MAX86174A/MAX86174B. The AFE requires a minimum of 2.7V applied to the  $V_{LED}$  pin (see the <u>Electrical Characteristics</u> table). Additionally, the minimum required  $V_{LED}$  voltage in a system is determined by the sum of forward voltage ( $V_F$ ) of each LED at maximum LED current and the minimum  $V_{LEDn\_DRV}$  voltage in <u>Table 2</u>. Also note that <u>Table 2</u> is based on the Maxim internal test board and it is recommended to test and verify the SNR with the best  $V_{LEDn\_DRV}$  on the different PCBs.

The  $V_{LED}$  voltage must be above this minimum to avoid compression, and allow for enough headroom to supply the LED drive current as needed; otherwise, the  $I_{LED}$  can be reduced and more sensitive to  $V_{LED}$  supply changes. The voltage on the LEDn\_DRV pins can be measured during an exposure to ensure the minimum headroom voltage is maintained during each LED exposure (LED on time). The minimum  $V_{LED}$  can be simply calculated by using the formulas below:

V<sub>LED</sub> ≥ 2.7V and V<sub>LED</sub> ≥ V<sub>F</sub> + V<sub>LEDn DRV</sub>

where, V<sub>F</sub> is a function of maximum LED current for the system.

Figure 1. LED Drivers

#### **Optical Receiver Overview**

The optical path in MAX86174A/MAX86174B is composed of a front-end photodiode biasing circuit with an analog ambient-light cancellation (ALC) sample and hold circuit that nulls the ambient-light photodiode current at the input of the ADC. This front-end photodiode biasing circuit is followed by a current integrating, continuous-time sigma-delta ADC with a proprietary discrete time filter. This discrete time filter uses multiple dark and exposure samples to generate an accurate 20-bit effective exposure output signal with excellent low- and high-frequency ambient-light rejection.

The MAX86174A incorporates dual optical-signal paths and the MAX86174B incorporates a single optical-signal path. Both have four photodiode input pins which are configured by MEASx\_PDSEL (x = 1 to 6) in each measurement. The on-chip Mux connects the two photodiode inputs to the optical signal path, as shown in Figure 2.

Note:  $MEASx_PDSEL[7:6]$  (x = 1-6) is in registers 0x21, 0x29, 0x31, 0x39, 0x41, 0x49.

For scenarios with MAX86174A requiring only one optical-signal path to be active (for example, lower power consumption), either one of the two channels can be powered down by setting PPG1\_PWRDN[2](0x11) or PPG2\_PWRDN[3](0x11) to 1. In this way, the MAX86174A is used in a single-channel configuration. By default, the MAX86174A PPG has dual channels enabled.

Each optical signal path supports four full-scale range settings of  $4\mu$ A,  $8\mu$ A,  $16\mu$ A, and  $32\mu$ A set in the MEASx\_PPGy\_ADC\_RGE (x = 1 to 6, y = 1, 2 for MAX86174A, y = 1 for MAX86174B) field in each of the measurement configurations block. Also supported are four options for integration time, which effectively modulate the optical channel bandwidth, allowing for a trade-off between LED power consumption and PPG signal quality.

Note: MEASx\_PPG1\_ADC\_RGE[1:0] (x = 1–6) and MEASx\_PPG2\_ADC\_RGE[3:2] (x = 1–6) are in registers 0x22, 0x2A, 0x32, 0x3A, 0x42, 0x4A.

Each optical signal path also incorporates a 3-bit offset DAC for extending the optical dynamic range by sourcing some of the exposure current to the offset DAC. The current offset is selected in the MEASx\_PPGy\_DACOFF register bit field. This feature is especially useful under certain conditions that occur when attempting to limit the exposure ADC counts, for example, when avoiding saturation while increasing the exposure signal perfusion index.

Note:  $MEASx_PPG1_DACOFF[2:0]$  (x = 1-6) and  $MEASx_PPG2_DACOFF[6:4]$  (x = 1-6) are in registers 0x24, 0x2C, 0x34, 0x3C, 0x44, 0x4C.

Also, higher SNR is achieved by enabling the DAC offset in addition to utilizing the burst averaging and off-chip low-pass or band-pass filtering, allowing for 111dB SNR to be achieved. The optical channels also support multiple photodiode and LED settling time settings in order to support flexible multiparameter measurements for different types of photodiode/LED wavelength combinations.

Figure 2. On-Chip Mux for the PD1\_IN and PD2\_IN pins

Most significantly, each signal path supports up to six unique combinations of the above configurations as needed. This

# Best-in-Class Optical Pulse Oximeter and Heart-Rate Sensor AFE for Wearable Health

allows a single optical AFE to support multiple optical measurements in a compact, energy-efficient design.

#### **Photodiode Biasing**

The MAX86174A/MAX86174B provide three photodiode biasing options to support a large range of photodiode capacitance. Each photodiode input can have a separate bias setting; thereby, allowing for different photodiodes to be used. The PDm\_BIAS (m = 1, 2, register 0x15) settings adjust the PDm\_IN bias point impedance to ensure that each photodiode settles rapidly enough to support the sample timing.

The PDm\_BIAS impacts the dark current noise of the MAX86174A/MAX86174B. Because of the increased noise with a higher PDm\_BIAS setting, the lowest recommended PDm\_BIAS value should be used for any given photodiode capacitance.

#### **Measurement Configuration and Timing**

A measurement is essentially one combination of LED (or LEDs) and PD (or PDs) that results in an optical measurement. The MAX86174A/MAX86174B support six individual measurements, each of which can be configured independently. Each measurement can be configured by the group of registers named PPG MEASx Setup (x = 1 to 6). These registers set up a number of parameters as listed below.

- Connection of each of the two LED drivers to one of the four LED driver pins

- Connection of ADC channel(s) to one of two possible photodiodes

- Ambient measurement

- LED driver range and drive currents

- LED settling time

- PD settling time

- Number of burst averages of each measurement

- Ambient rejection scheme (CDM or FDM)

- On-chip decimation filter selection (COI or SINC3)

- ADC integration time

- ADC range for each channel

- · DAC offset for each channel

A measurement can be configured to pulse one or two LED drivers sequentially at multiple wavelengths as is done in pulse oximetry measurements or simultaneously to drive multiple LEDs such as is done with heart-rate measurements on the wrist. A measurement is also configurable to measure direct ambient level. If direct ambient is enabled in a measurement through MEASx AMB, it must be the last measurement in the sequence of enabled measurements.

Note: MEASx AMB[6] (x = 1-6) is in registers 0x20, 0x28, 0x30, 0x38, 0x40, 0x48.

Figure 3 represents one measurement with only one of the LEDs active. No averaging is used. As seen in Figure 3 only LED1\_DRV is pulsing during the exposure time. In this mode, each driver pulse results in a single optical sampled value for each PD input to be stored in the FIFO. For example, in a single-channel configuration, only one sample is stored in the FIFO for each driver pulse but for a dual-channel configuration, two samples are stored in the FIFO for each driver pulse.

This timing mode in Figure 3 is used when heart rate is being measured with a single LED.

Figure 3. Measurement with One LED On

#### **Ambient-Light Cancellation**

The MAX86174A/MAX86174B implement ambient-light cancellation (ALC) in two steps, a coarse cancellation and a fine cancellation. Each PPG channel has its own dedicated ambient-light cancellation circuits. Also, each MEASx has its own ambient-light cancellation configuration. The coarse cancellation is in the analog domain. It is enabled by default and can be disabled by setting the ALC\_DISABLE[4](0x13) to 1. The fine cancellation is a digital cancellation scheme and is configured with either a central difference method (CDM) or forward difference method (FDM) through the MEASx\_FILT\_SEL (x = 1 to 6) bit.

Note: MEASx FILT SEL[6] (x = 1-6) is in registers 0x22, 0x2A, 0x32, 0x3A, 0x42, 0x4A.

ALC coarse cancellation can cancel up to 200µA of DC photodiode current. Any drift or residual from coarse cancellation is canceled by CDM/FDM cancellation.

One CDM sample is comprised of 3 ADC conversions, with 2 ambient and 1 exposure conversion where ambient-light estimation is made from dark measurements before and after the exposure measurement. One FDM sample is comprised of 2 ADC conversions with 1 ambient only and 1 exposure conversion where the ambient light is estimated by a dark measurement before the exposure measurement. The ambient and exposure samples are used for digital cancellation of any residual error (from ALC) or drift (in ambient signal). The final computed value is the effective exposure signal that is stored in the FIFO.

See Figure 4 for the timing diagram of CDM and Figure 5 for the timing diagram of FDM.

Ambient-light cancellation in low frequency ambient light improves when using burst average by setting MEASx\_AVER ≥ 0x2. In addition, the MAX86174A/MAX86174B have a SINC3 decimation filter for the delta-sigma PPG ADC, which is enabled for each measurement individually by setting MEASx\_SINC3\_SEL. This filter provides improved high-frequency roll-off that improves the high-frequency ambient-light rejection. MAX86174A/MAX86174B by default uses a third order COI3 decimation filter that provides excellent quantization, but the roll-off at high frequencies is only 20dB/dec. The SINC3 filter provides a 60dB/dec roll-off for out-of-band frequencies; thus, improving ambient-light rejection at high frequencies. This filter is only available for MEASx\_TINT = 0x3 (117.1µs). See Figure 11 for different decimation filters.

Note:  $MEASx\_AVER[2:0]$  (x = 1-6) and  $MEASx\_TINT[4:3]$  (x = 1-6) are in registers 0x21, 0x29, 0x31, 0x39, 0x41, 0x49.  $MEASx\_SINC3\_SEL[7]$  (x = 1-6) is in registers 0x22, 0x2A, 0x3A, 0x4A.

Figure 4. Central Difference Method (CDM)

Figure 5. Forward Difference Method (FDM)

#### Frame and Frame Rate

A frame is a combination of one (min) to six (max) measurements configured in MEASx\_EN (x = 1 to 6) (register 0x12). The frame rate defines how frequently a frame is repeated and is expressed in units of frames per second (fps). Frame rate is defined by two methods:

- Frame Rate = 32768/FR\_CLK\_DIV, where FR\_CLK\_DIV = 16 to 32766 are directly programmable (see <u>Register</u> 0x1B and 0x1C) or

- Frame Rate = Active edge of the TRIG input with SYNC MODE[5:4](0x11) = 1.

Any combination of measurements can be enabled, but measurements are done in a numerical order inside a frame. For example, it is valid to enable MEAS1, MEAS2, and MEAS5 while MEAS3 and MEAS4 are skipped. But if a measurement of direct ambient is configured, then this measurement must be configured as the last measurement in the frame.

Figure 6 represents the timing diagram for one measurement with CDM enabled in each frame.

<u>Figure 7</u> illustrates timing for six measurements in each frame. Each measurement can be configured independently using the PPG MEASx Setup register blocks (0x20 to 0x4E). Alternatively, all measurements share the same configuration of MEAS1 by setting MEAS1\_CONFIG\_SEL[0](0x13) to 1.

<u>Figure 8</u> illustrates timing for six measurements in each frame with MEAS3 configured to have a burst average of 2. The result of MEAS3 in each frame only has one FIFO data pushed into FIFO per ADC channel. This FIFO data is the average of the two PD samples labeled as F1M3.

Figure 6. Frame with One Measurement

Figure 7. Frame with Six Measurements

Figure 8. Frame with Measurement Burst Averaging

#### **On-Chip Averaging**

The MAX86174A/MAX86174B incorprote both burst average and decimation average on chip. Burst average applies to one measurement where a given number of LED bursts are fired. Decimation average is frame-based where a given number of measurements from successive frames are averaged, resulting in a lower FIFO data rate.

#### **Burst Average**

Burst average defines the number of LED exposures in one measurement and it is configured by the MEASx\_AVER (x = 1 to 6) bit. Burst average works only with CDM, MEASx\_FILT\_SEL = 0. In each measurement, (2(MEASx\_AVER +1) + 1) ADC conversions of interleaved dark and exposure samples are made and the weighted computed average is fed to the digital low-pass filter. The example in Figure 9 has burst average of 2, MEASx\_AVER = 0x1; hence, there are 5 conversions. When ambient-light cancellation is configured as FDM in a given measurement (MEASx\_FILT\_SEL = 1), only one dark ADC conversion and one exposure ADC conversion are done, regardless of the value of MEASx\_AVER.

Note:  $MEASx\_AVER[2:0]$  (x = 1-6) is in register 0x21, 0x29, 0x31, 0x39, 0x41, 0x49 and  $MEASx\_FILT\_SEL[6]$  (x = 1-6) is in registers 0x22, 0x2A, 0x32, 0x3A, 0x42, 0x4A.

Burst averaging improves the exposure SNR. SNR benefits of the higher burst average ratio are shown in the <u>Typical Operating Characteristics</u> section. Besides, burst averaging can be used to improve ambient-light cancellation at the same LED power consumption level. For example, one application requires signal quality at MEASx\_TINT = 117.1µs and burst average = 1x. Without increasing the LED illumination time, applying MEASx\_TINT = 29.2µs but burst average = 4x can keep the exposure SNR the same and have better ambient cancellation at MEASx\_TINT = 29.2µs.

Note:  $MEASx_TINT[4:3]$  (x = 1-6) is in registers 0x21, 0x29, 0x31, 0x39, 0x41, 0x49.

Figure 9. Illustration of Measurement with Burst Averaging

#### **Decimation Average**

Decimation averaging operates on multi-frames, which does not impact the LED exposure sequence nor front-end signal acquisition. It reduces the FIFO data rate. <u>Figure 10</u> shows an example of a decimation average of 2.

Decimation averaging is integrated to reduce the data rate to FIFO in the digital low pass filter. See the <u>On-Chip Filtering</u> section for details.

Figure 10. Frames with Decimation Average of 2

#### **On-Chip Filtering**

The MAX86174A/MAX86174B have two stages of on-chip filtering, decimation filtering at the ADC stage and digital low-pass filtering after the ADC stage.

#### **ADC Decimation Filter**

Users can select a second-order decimation filter (COI2), a third-order decimation filter (COI3), or SINC3 decimation filter. MAX86174A/MAX86174B by default use a third-order cascade of integrators (COI3) decimation filter. This filter provides excellent quantization, but only a 20dB/dec roll-off at higher frequencies. COI2 has a narrower bandwidth as compared to the COI3, which improves the PPG SNR by about 1dB to 2dB. The SINC3 filter has a better rollover (60dB/dec), and therefore, provides higher AC ambient-light cancellation at high frequencies and  $V_{LED}$  power-supply rejection. The SINC3 filter generates poor quantization performance and is, thus, only available on the longest integration time, MEASx\_TINT = 0x3 (117.1 $\mu$ s). SINC3 is selected for each measurement individually by setting MEASx\_SINC3\_SEL to 1. To set the decimation filter to COI2 for all measurements, PPG\_FILT2\_SEL[7](0x14) is set to 1. Both SINC3 and COI2 can only be used with the longest integration time (MEASx\_TINT = 0x3).

Note: MEASx\_TINT[4:3] (x = 1-6) is in registers 0x21, 0x29, 0x31, 0x39, 0x41, 0x49 and MEASx\_SINC3\_SEL[7] (x = 1-6) is in registers 0x22, 0x2A, 0x32, 0x3A, 0x42, 0x4A.

<u>Table 3</u> shows the configuration for different ADC decimation filters. Combinations of the 3 parameters out of this table are not suggested.

Table 3. Configuration for ADC Decimation Filter

| MEASx_SINC3_SEL | PPG_FILT2_SEL | MEASx_TINT | DECIMATION FILTER |

|-----------------|---------------|------------|-------------------|

| 0               | 0             | All TINTs  | COI3 (Default)    |

| 0               | 1             | TINT = 0x3 | COI2              |

| 1               | 0 or 1        | TINT = 0x3 | SINC3             |

See Figure 11 for the transfer function of different decimation filters.

Figure 11. Signal Transfer Function of Decimation Filters

#### **Digital Low-Pass Filter**

The digital low-pass filter processes data before it gets saved in the FIFO. Users can either select an on-chip IIR filter or decimation averaging for low-pass filtering. The digital low-pass filter improves the SNR significantly. To enable digital low-pass filter, for all enabled measurements, DLPF\_EN[5:4](0x14) is configured as needed. IIR filter configuration is programmed in IIR\_CFG[3](0x14) and decimation averaging is set in DEC\_AVE[2:0](0x14). The IIR cutoff frequency depends on the IIR\_CFG bit. The decimation averaging option reduces the FIFO data rate by a factor of  $2^{\text{DEC}}_{\text{AVE}}$ .

FIFO data rate = Frame rate x Number of enabled measurements x Number of enabled channels / 2DEC\_AVE.

#### **AFE Exposure Control and SNR**

MAX86174A/MAX86174B provide the options above to support extensive application scenarios that require different signal bandwidth and signal-to-noise (SNR) ratio. The  $\underline{\text{Table 4}}$  shows the SNR benefits when applying different parameters.

**Table 4. Typical SNR Benefit Of Various Parameters**

| TINT (μs)  | BURST<br>AVERAGE | DAC<br>OFFSET | COI2<br>FILTER | DIGITAL<br>LPF | PEAK SNR<br>(dB) | DIFFERENCE<br>(dB) | BW<br>(Hz) |

|------------|------------------|---------------|----------------|----------------|------------------|--------------------|------------|

| 14.6/117.1 | 1                | 0             | OFF            | OFF            | 83.9/91.6        | +7.7               | 50         |

| 117.1      | 1/16             | 0             | OFF            | OFF            | 91.6/98.9        | +7.3               | 50         |

| 117.1      | 1                | 0/28          | OFF            | OFF            | 91.6/94.1        | +2.5               | 50         |

| 117.1      | 1                | 0             | OFF/ON         | OFF            | 91.6/92.7        | +1.1               | 50         |

| Table 4. 1 | ypical | <b>SNR</b> | <b>Benefit</b> | Of | <b>Various</b> | <b>Parameters</b> | (continued) | ) |

|------------|--------|------------|----------------|----|----------------|-------------------|-------------|---|

|------------|--------|------------|----------------|----|----------------|-------------------|-------------|---|

| TINT (µs) | BURST<br>AVERAGE | DAC<br>OFFSET | COI2<br>FILTER | DIGITAL<br>LPF | PEAK SNR<br>(dB) | DIFFERENCE<br>(dB) | BW<br>(Hz) |

|-----------|------------------|---------------|----------------|----------------|------------------|--------------------|------------|

| 117.1     | 1                | 0             | OFF            | OFF/ON         | 91.6/95.6        | +4                 | 11.5       |

| 117.1     | 1/16             | 0             | ON             | ON             | 96.5/101.6       | +5.1               | 11.5       |

| 117.1     | 16               | 0/24          | ON             | ON             | 101.6/106.6      | +5                 | 11.5       |