# Preliminary Datasheet

# R2A25110KSP

# Intelligent Power Device for IGBT Drive with Micro Isolator

### 1. Description

The R2A25110KSP device is an intelligent power device for IGBT gate-drive in the high voltage inverter application. The Micro Isolator with the coreless transformer structure is adopted for data transfer with high voltage isolation between the primary circuit (MCU side) and the secondary circuit (IGBT side). This device contains IGBT gate drive circuit, Miller clamp circuit, soft turn-off circuit as well as several types of protection circuits such as IGBT temperature detection. This device also supports driving parallel IGBTs.

# 1.1. Features

On-chip Micro Isolator (isolated circuit)

High voltage isolation: 2500V<sub>RMS</sub>

- ➤ High Common Mode Rejection (CMR): over 35kV/us

- High output gate drive circuit

- ➤ Gate drive output resistance: 1.0 ohm max (IGBT parallel connection supported)

- On-chip active Miller clamp function

- On-chip soft turn-off function

- Various on-chip protection circuits

- ➤ IGBT emitter current detection circuit: 2 channels

Over current detection (threshold voltage: 0.25 V typ.), short circuit detection (threshold voltage: 0.5 V typ.)

Over current detection function can be enabled/disabled (SEL pin)

- IGBT temperature detection circuit: 2 channels

- On-chip under voltage lockout circuit

VCC1 (5 V system): 4.1 V typ.

VCC2 (15 V system): 10 V typ.

- On-chip over temperature protection circuit (200 degC)

- > FAULT feedback

Adjustable FAULT hold time with the external capacitor

- Operating temperature: 40 to 125 degC (junction temperature: 150 degC max)

- On-chip 5 V regulator

### 1.2. Applications

- Main inverters for EV/HEV in automotive applications

- Converters for EV/HEV in automotive applications

- Inverters and converters for industrial instruments, etc.

Note: The information contained in this document is the one that was obtained when the document was issued, and may be subject to change.

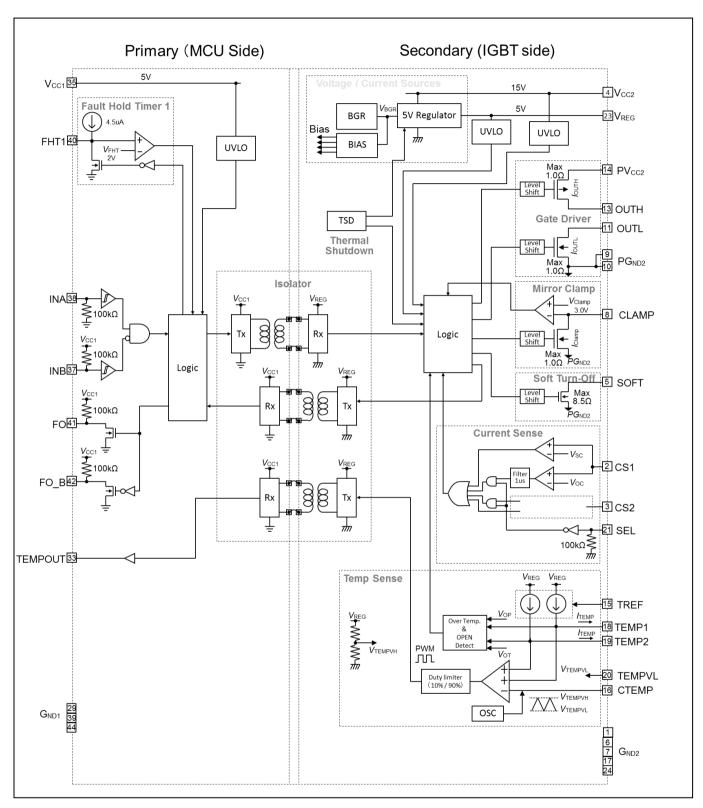

# 2. Block Diagram

Figure 1: Block Diagram

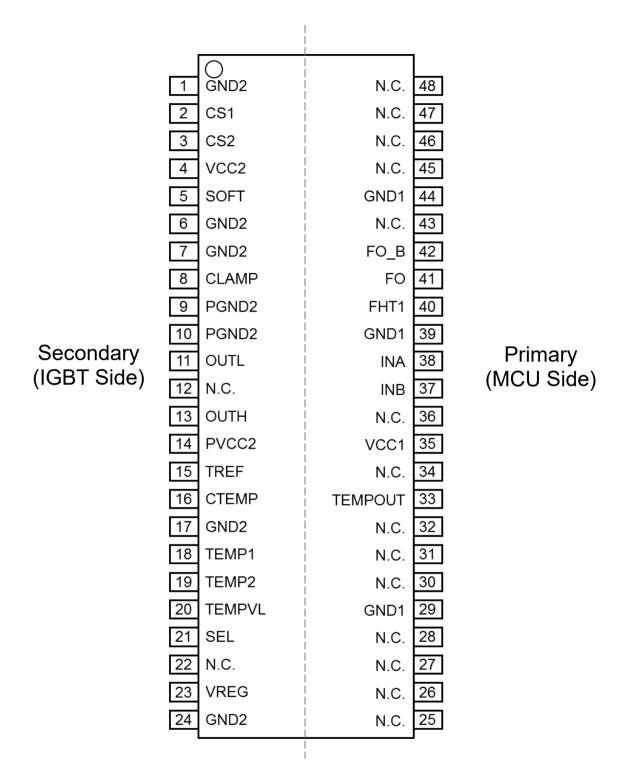

# 3. Pin Arrangement

Figure 2: SSOP48 (Top View)

Table 1: Pin List (1/2)

|         |          | Reference | ,     |                                                                              |

|---------|----------|-----------|-------|------------------------------------------------------------------------------|

| PIN No. | PIN NAME | pin       | PU/PD | Functions                                                                    |

| 1       | GND2     | _         | _     | Secondary GND                                                                |

| 2       | CS1      | GND2      | _     | Emitter current detection input (ch1)                                        |

| 3       | CS2      | GND2      | _     | Emitter current detection input (ch2)                                        |

| 4       | VCC2     | GND2      | _     | Secondary power supply input (15 V typ.)                                     |

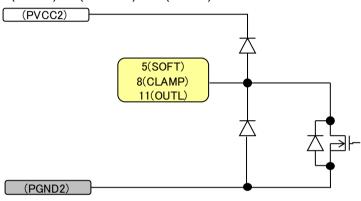

| 5       | SOFT     | PGND2     | _     | Soft turn-off output                                                         |

| 6       | GND2     | _         | _     | Secondary GND                                                                |

| 7       | GND2     | _         | _     | Secondary GND                                                                |

| 8       | CLAMP    | PGND2     | _     | Active Miller clamp output                                                   |

| 9       | PGND2    | _         | _     | Secondary power GND                                                          |

| 10      | PGND2    | _         | _     | Secondary power GND                                                          |

| 11      | OUTL     | PGND2     | _     | Low side gate drive output                                                   |

| 12      | N.C.     | _         | _     | Non Connection                                                               |

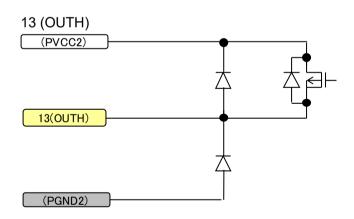

| 13      | OUTH     | PGND2     | _     | High side gate drive output                                                  |

| 14      | PVCC2    | PGND2     | _     | Secondary power supply input (15 V typ.)                                     |

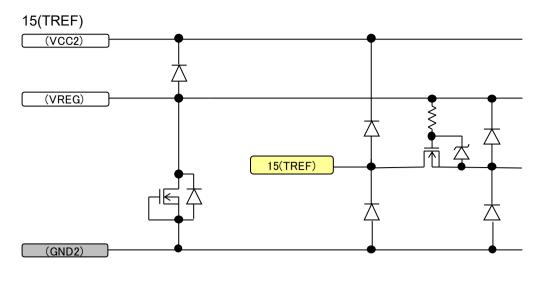

| 15      | TREF     | GND2      | _     | Constant current setting pin connected to resistor for IGBT temp detection   |

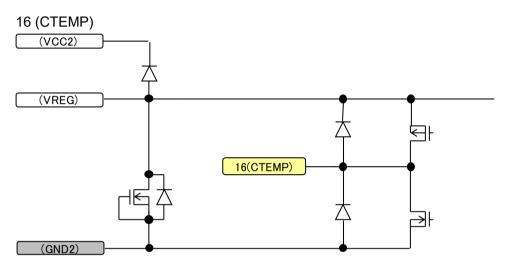

| 16      | СТЕМР    | GND2      | _     | IGBT temp detection period setting pin connected to capacitor                |

| 17      | GND2     | _         | _     | Secondary GND                                                                |

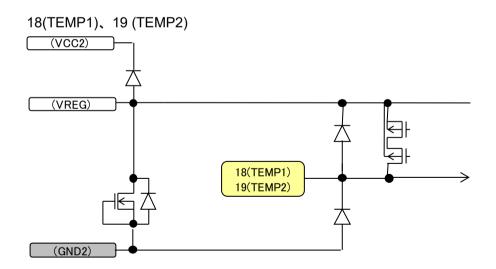

| 18      | TEMP1    | GND2      | _     | IGBT temp detection input (ch1)                                              |

| 19      | TEMP2    | GND2      | _     | IGBT temp detection input (ch2)                                              |

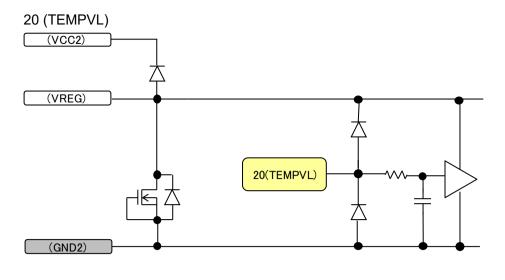

| 20      | TEMPVL   | GND2      | _     | IGBT temp voltage detection threshold value input (lower limit)              |

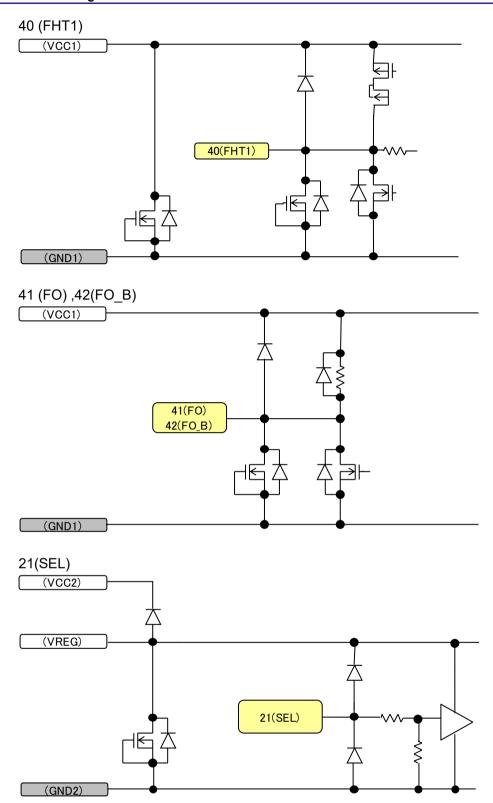

| 21      | SEL      | GND2      | PD    | Selection of over current detection function (GND2: Enabled, VREG: Disabled) |

| 22      | N.C.     | _         | _     | Non Connection                                                               |

| 23      | VREG     | GND2      | _     | 5 V regulator output                                                         |

| 24      | GND2     | _         | _     | Secondary GND                                                                |

| 25      | N.C.     | _         | _     | Non Connection                                                               |

| 26      | N.C.     | _         | _     | Non Connection                                                               |

| 27      | N.C.     | _         | _     | Non Connection                                                               |

| 28      | N.C.     | _         | _     | Non Connection                                                               |

| 29      | GND1     | _         | _     | Primary GND                                                                  |

| 30      | N.C.     | _         | _     | Non Connection                                                               |

| 31      | N.C.     | _         | _     | Non Connection                                                               |

| 32      | N.C.     | _         | _     | Non Connection                                                               |

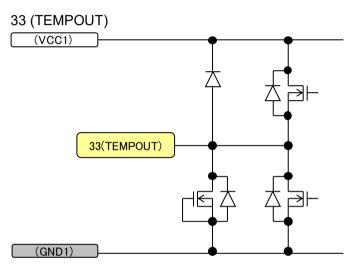

| 33      | TEMPOUT  | GND1      | _     | IGBT temp detection output                                                   |

| 34      | N.C.     | _         | _     | Non Connection                                                               |

| 35      | VCC1     | GND1      | _     | Primary power supply input (5 V typ.)                                        |

| 36      | N.C.     | _         | _     | Non Connection                                                               |

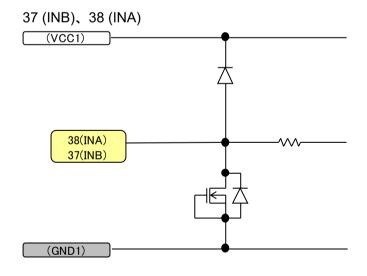

| 37      | INB      | GND1      | PU    | Inverted gate drive input                                                    |

| 38      | INA      | GND1      | PD    | Non-inverted gate drive input                                                |

| 39      | GND1     | _         | _     | Primary GND                                                                  |

| 40      | FHT1     | GND1      | _     | Fault hold time setting pin connected to capacitor                           |

| 41      | FO       | GND1      | PU    | Non-inverted fault output (H level output at error)                          |

| 42      | FO_B     | GND1      | PU    | Inverted fault output (L level output at error)                              |

Remark: PD - Pull down resistor / PU- Pull up resistor

N.C. pins in open state is recommended.

Table 1: Pin List (2/2)

| PIN No. | PIN NAME | Reference<br>pin | PU/PD | Functions      |

|---------|----------|------------------|-------|----------------|

| 43      | N.C.     | 1                | _     | Non Connection |

| 44      | GND1     | 1                | _     | Primary GND    |

| 45      | N.C.     | 1                | _     | Non Connection |

| 46      | N.C.     | -                | _     | Non Connection |

| 47      | N.C.     | _                | _     | Non Connection |

| 48      | N.C.     | _                | _     | Non Connection |

Remark: PD - Pull down resistor / PU- Pull up resistor

N.C. pins in open state is recommended.

# 4. Functional Description

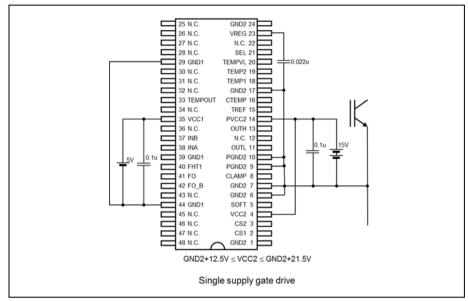

### 4.1 Power Supply

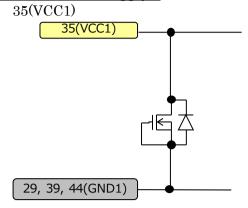

The primary circuit has the power supply pin (VCC1) which supplies 5 V power reference to GND1.

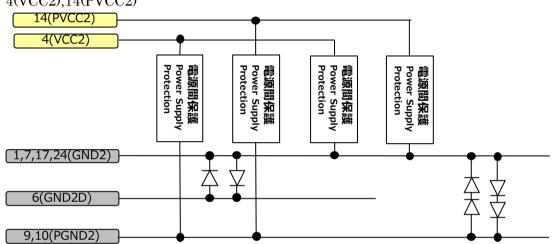

The secondary circuit has two types of power supply pins VCC2 and PVCC2, and two types of GND pins GND2 and PGND2. VCC2 supplies 15 V power reference to GND2 to the control circuit of the secondary side, and PVCC2 supplies 15 V power reference to PGND2 to the gate drive circuit. The IGBT gate voltage is applied from PVCC2 at the ON state and from PGND2 at the OFF state, VCC2 and PVCC2 should be externally short-circuited and GND2 and PGND2 should also be externally shortcircuited.

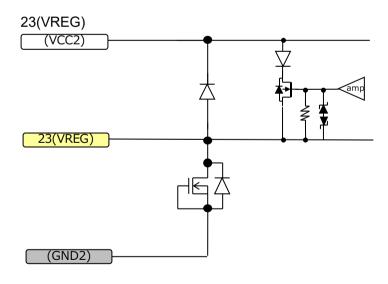

The IC incorporates a 5-V output regulator, and outputs 5 V from the VREG pin. This regulator is capable of supplying a maximum of 5-mA current to the external circuits, thus being useful for setting the IGBT temperature detection circuit and other circuits. Even when the 5-V power is not necessary for external circuits, the 0.022-uF capacitor should be connected to the VREG pin to stabilize the internal voltage.

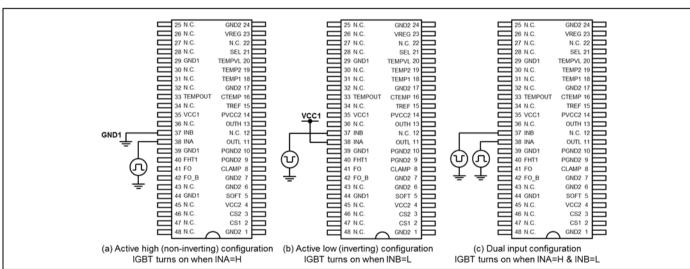

# 4.2 Inverted input/Non-inverted input

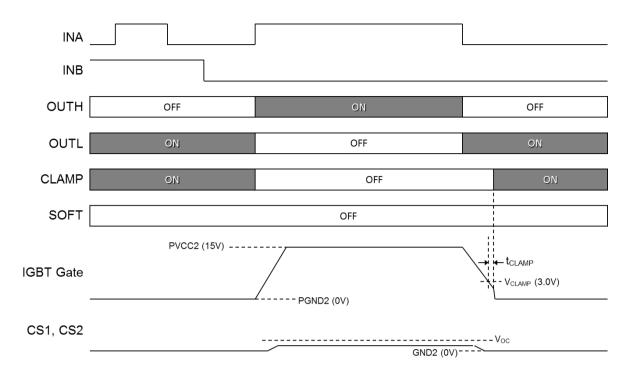

The IGBT gate can be turned on or off by either non-inverted logic (active high) input or inverted logic (active low) input. The IGBT gate is turned on only when the INA= high (H) and INB= low (L) (refer to

When the non-inverted logic is used, the input signal should be applied to the INA pin with the INB pin fixed to the low level.

When the inverted logic is used, the input signal should be applied to the INB pin with the INA pin fixed to the high level.

The INA and INB pins are internally pulled down and pulled up, respectively. Therefore, the IGBT is turned off when one of the INA and INB pins are open.

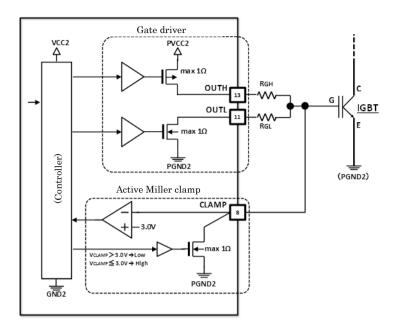

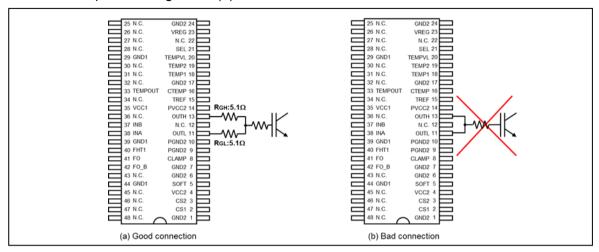

#### 4.3 Gate Driver

The gate driver charges or discharges the IGBT gate pins. Figure 3 shows a block diagram of the

To turn on the IGBT, the OUTH pin is short-circuited to the PVCC2 pin via a 1.0 Ohm or smaller transistor; and the OUTL pin is driven to the high-impedance state.

To turn off the IGBT, the OUTL pin is short-circuited to the PGND2 pin via a 1.0 Ohm or smaller transistor; and the OUTH pin is driven to the high-impedance state.

Since the high-side gate drive output pin OUTH and the low-side gate drive output pin OUTL are independent of each other, the slew rates of the rise and fall of the gate voltage can be separately adjusted using the external resistors (RGH and RGL). The OUTH and OUTL pins should be provided with individual gate resistors and connected to the IGBT. The external resistor values (RGH and RGL) should be determined so that the peak current does not exceed the absolute maximum ratings (IOUTH and IOUTL) while the IGBT is being charged or discharged.

OUTH INA INB **OUTL IGBT State** Χ Hi-Z **OFF** L L Χ Н Hi-Z **OFF** L Н L Н Hi-Z ON

Table 2: I/O Truth Table

# 4.4 Active Miller Clamp

The active Miller clamp is the feature to prevent the self-turn-on of the IGBT due to the coupling capacitance between the IGBT gate and collector. Figure 3 shows a block diagram of the circuit.

The CLAMP pin also serves as the input pin to detect the IGBT gate voltage. If the CLAMP pin voltage falls below V<sub>CLAMP</sub> (3.0 V typ.) while the input signal to turn off the IGBT is applied to the INA or INB pin, the IGBT gate is short-circuited to the PGND2 pin with 1.0 Ohm or lower.

With the CLAMP pin, the gate can be connected to the PGND2 pin with the lower impedance than the OUTL pin to which the gate resistor (RGL) is connected. Therefore, self-turn-on of the IGBT can be prevented more effectively, compared to the case in which only the OUTL pin is used to ground the gate.

The active Miller clamp not only works at normal turn-off operation of the IGBT as shown in the timing chart in figure 12 but also works at soft turn-off operation as shown in figures 13 to 17.

Figure 3: Gate Driver and Active Miller Clamp Circuit

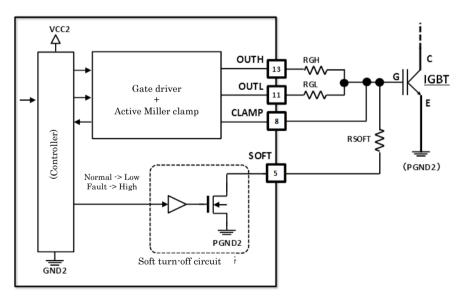

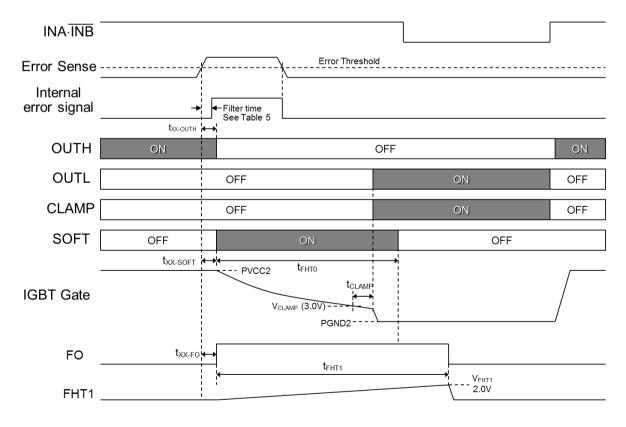

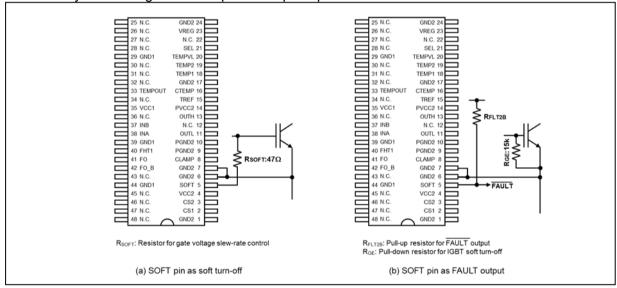

### 4.5 Soft Turn-off

The soft turn-off is the feature to lower the gate voltage of the IGBT gradually and turn it off when any of the following abnormal states is detected on the secondary circuit: low voltage, over current, short circuit, over temperature (IGBT and IC), TEMP1 or TEMP2 open, and timeout (communication error). Figure 4 shows a block diagram of the soft turn-off circuit.

If a fault such as over current occurs and the IGBT is turned off immediately, the IGBT may be destroyed due to the excessive voltage applied between the collector and emitter of the IGBT. To prevent this, the IGBT gate is discharged slowly using the soft turn-off pin instead of using a high current gate driver or active Miller clamp. The turn-off time can be adjusted by the resistor (RSOFT) connected between the SOFT pin and the IGBT gate pin.

Figure 4: Soft Turn-off Circuit

#### 4.6 Abnormal State Detection

This product can detect various abnormal states (faults) and externally output the associated fault signals. The following types of abnormal states can be detected:

- 1. IGBT over current and short circuit

- 2. IGBT over temperature and temperature sense diode open

- 3. Low voltage (UVLO)

- 4. Timeout

- 5. Over temperature of the product (TSD)

Sections 4.6.1 to 4.6.6 describe the above functions.

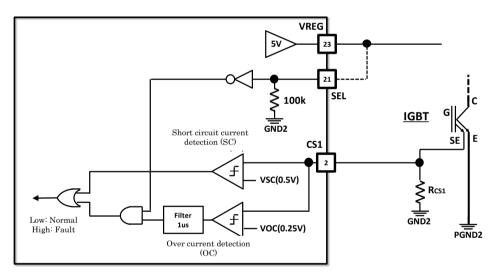

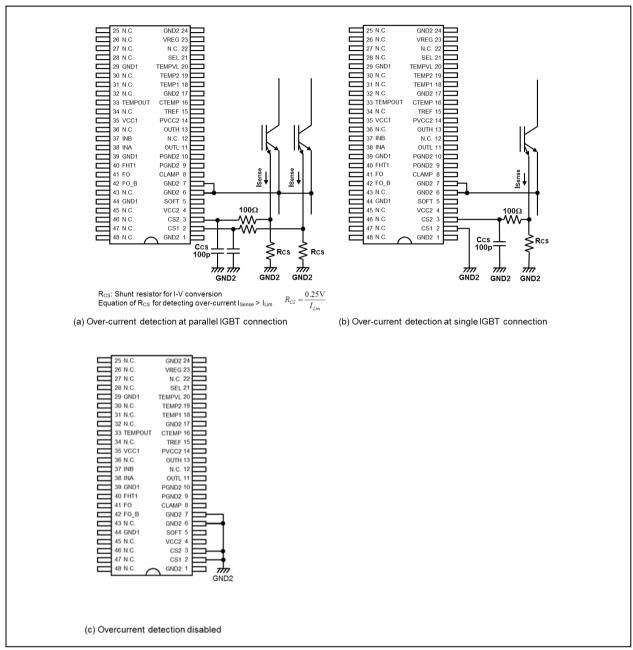

#### 4.6.1 IGBT Over Current and Load Short Circuit Detection

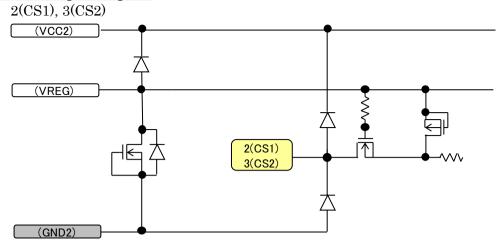

This feature turns off the output from the gate driver if the over current or short-circuit current in the IGBT is detected. Figure 5 shows a block diagram of the circuit. Since two CS pins (CS1 and CS2) are provided, it is possible to separately detect the emitter current of the two IGBTs connected in parallel.

By applying the pin voltage of the shunt resistor connected to the IGBT emitter pin to the CS1 or CS2 pin, it is possible to detect whether the IGBT emitter is in the over current state or load short circuit state. The over current detection threshold can be set through the shunt resistor value.

The IGBT is soft turned-off if the voltage applied to the CS1 or CS2 pin rises beyond the threshold voltage\* when the IGBT is in the on-state. At this time, the high level is output to the FO pin and the low level is output to the FO B pin of the primary circuit.

- \*Over current detection voltage (Voc): 0.25 V typ.; filtering time 1 us typ.

- \* Short circuit current detection voltage (Vsc): 0.5 V typ.

The over current detection function is enabled when the SEL pin is open or connected to the GND2 pin; to disable the function, connect the SEL pin to the VREG pin (5 V typ.).

Figure 5: Over Current and Short Circuit Current Detection Circuit

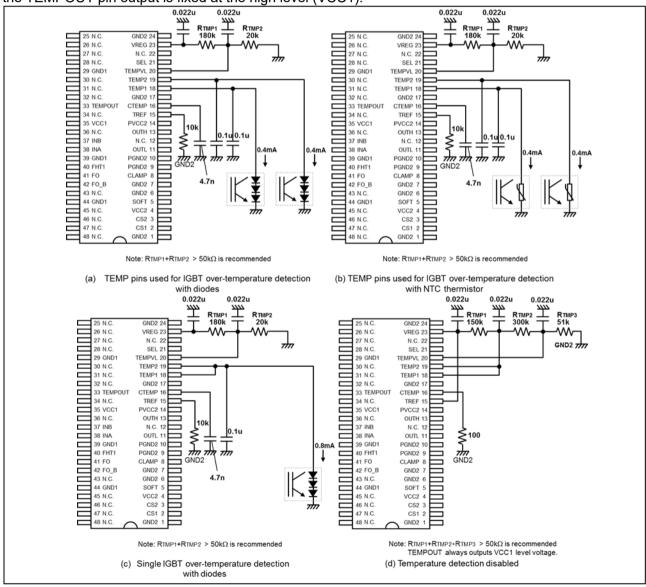

#### 4.6.2 IGBT Temperature Detection

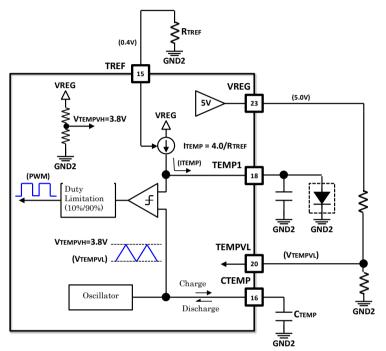

Figure 6 shows the IGBT temperature detection circuit. This circuit outputs the constant current ( $I_{TEMP} = 4/R_{TREF}$ ) from the TEMP pin to the temperature sense diode incorporated in the IGBT. The forward voltage of the temperature sense diode (IGBT chip temperature voltage) is input to the IGBT temperature detection circuit via the TEMP pin, converted to the PWM signal having the duty cycle proportional to the voltage, and finally output from the TEMPOUT pin via the Micro Isolator.

Since two TEMP pins (TEMP1 and TEMP2) are provided, it is possible to separately monitor the temperature of the two IGBTs connected in parallel. In this case, the lower TEMP pin voltage (the higher IGBT chip temperature) of the two is selected and output.

When the temperature of only one IGBT is to be monitored, connect the TEMP1 and TEMP2 pins in parallel. In this case, the sum of the TEMP1 and TEMP2 pin current flows in the IGBT temperature sense diode connected to the TEMP pins. Therefore, appropriately adjust the current value using the external RTREE

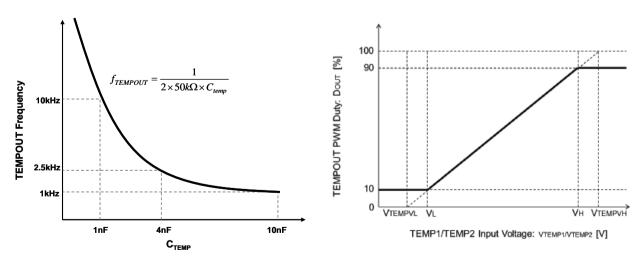

The CTEMP pin is used to set the frequency of the PWM signal output from the TEMPOUT pin. Connect the capacitor Ctemp to the CTEMP pin. The frequency of the PWM signal  $f_{\text{TEMPOUT}}$  can be

determined by the equation shown in figure 7.

Figure 8 shows the relationship between the temperature sense voltage input to the TEMP pin and the duty cycle of the PWM signal output from the TEMPOUT pin. Based on the VL and VH determined by the equation below, the duty cycle linearly changes from 10% to 90% when the TEMP pin voltage is in a range from VL to VH. When the TEMP pin voltage is lower than VL, the duty cycle is limited to 10% and when the TEMP pin voltage is higher than VH, the duty cycle is limited to 90%.

$V_L = 0.1 \times V_{TEMPVH} + 0.9 \times V_{TEMPVL}$

$V_H = 0.9 \times V_{TEMPVH} + 0.1 \times V_{TEMPVL}$

(VTEMPVH = 3.8 V; VTEMPVL is set using the TEMPVL pin.)

The TEMPOUT pin output is fixed to the low level (GND1) if the voltage for under-voltage lock out (VCC1, VCC2) is detected.

Figure 6: IGBT Temperature Detection Circuit

Figure 7: CTEMP-TEMPOUT Frequency Figure 8: Relation between TEMP1 and TEMP2 Voltages and PWM Output Duty Cycle

### 4.6.3 IGBT Over Temperature Detection and Detection of Temperature Sense Diode Open

This feature turns off the IGBT if over temperature of the IGBT is detected. This feature is included in Rev. 5.2 E R33DS0010EJ0520 Page 9 of 38 2020.04.23

the IGBT temperature detection circuit shown in figure 6.

If the TEMP1 or TEMP2 pin voltage falls below the over temperature detection threshold ( $V_{OT} = V_{TEMPVL} - 0.1 \text{ V}$  typ.), the IGBT is soft turned off. At this time, the high level is output to the FO pin and the low level is output to the FO B pin of the primary circuit.

In addition, if the TEMP1 or TEMP2 pin voltage rises beyond the open detection threshold ( $V_{OP} = 4.25$  V typ.), the temperature sense diode is determined to be open. At this time, the IGBT is soft turned off and the high level is output to the FO pin and the low level is output to the FO\_B pin of the primary circuit.

### 4.6.4 Under Voltage Lock Out (UVLO) Circuit

This feature turns off the IGBT to prevent the damage on the IGBT due to malfunctioning of the IC when the supply voltage goes low.

The primary circuit is equipped with a UVLO that detects a voltage drop of VCC1, and the UVLO turns off the IGBT (this is a normal turn-off operation different from a soft turn-off) when the VCC1 voltage drops below 4.1 V. At this time, the high level is output to the FO pin and the low level is output to the FO B pin of the primary circuit.

The secondary circuit is equipped with a UVLO that detects the voltage drop of VCC2 and a UVLO that detects the voltage drop of VREG (output from 5 V regulator). The IGBT is soft turned off if the VCC2 voltage drops below 10 V or the VREG voltage drops below 4.1 V. At this time, the high level is output to the FO pin and the low level is output to the FO B pin of the primary circuit.

#### 4.6.5 Timeout Detection

The timeout detection is a feature that outputs a fault status when the data transfer via Micro Isolator is not correctly performed.

For example, a timeout is detected at the secondary circuit when a signal transferred from the primary circuit to the secondary circuit via Micro Isolator is not detected in a certain period of time. The IGBT is soft turned off if a timeout is detected at the secondary circuit. At this time, the high level is output to the FO pin and the low level is output to the FO B pin of the primary circuit.

Also, a timeout is detected at the primary circuit when a signal transferred from the secondary circuit to the primary circuit via Micro Isolator is not detected in a certain period of time. When a timeout is detected at the primary circuit, the high level is output to the FO pin and the low level is output to the FO B pin of the primary circuit. The IGBT is not forcibly turned off in this condition.

### 4.6.6 Internal Over Temperature Detection (TSD)

This feature turns off the IGBT to prevent the damage on the IGBT due to malfunctioning of the IC when an extraordinary over heat (200 degC) is detected in the IC (thermal shut down: TSD). The operation is resumed when the IC temperature is decreased by the TSD hysteresis temperature (30 degC).

Temperature sense diodes are placed at the three positions that tend to be heated in the IC (near the OUTH, OUTL and CLAMP pins). The IGBT is soft turned off if the temperature of the driver transistor in the IC exceeds a threshold value due to the over load or the increased ambient temperature. At this time, the high level is output to the FO pin and the low level is output to the FO B pin of the primary circuit.

In addition, another temperature sense diode is placed near the VREG pin. Output from the 5 V regulator is stopped when the temperature of the 5 V regulator exceeds a threshold value due to the over load on the VREG pin (5 V output) or the increased ambient temperature. A temperature sense signal from the 5 V regulator does not directly soft turn off the IGBT or output a fault signal to the primary circuit. However, when the regulator stops and the VREG voltage drops to 4.1 V or less, the under voltage lock out circuit starts operation and soft turns off the IGBT. At this time, the high level is output to the FO pin and the low level is output to the FO\_B pin of the primary circuit.

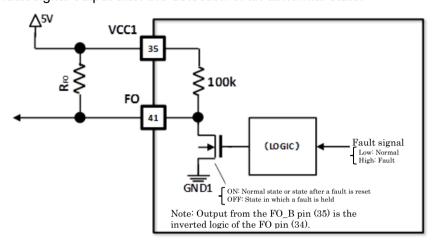

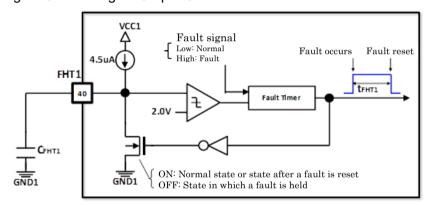

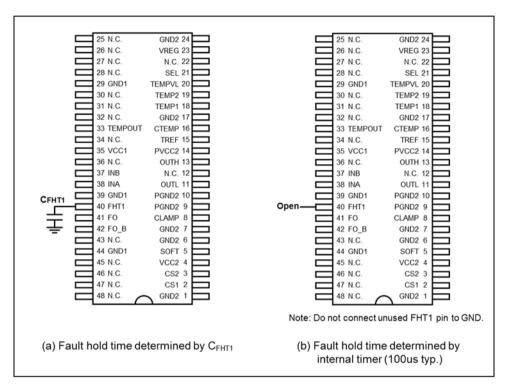

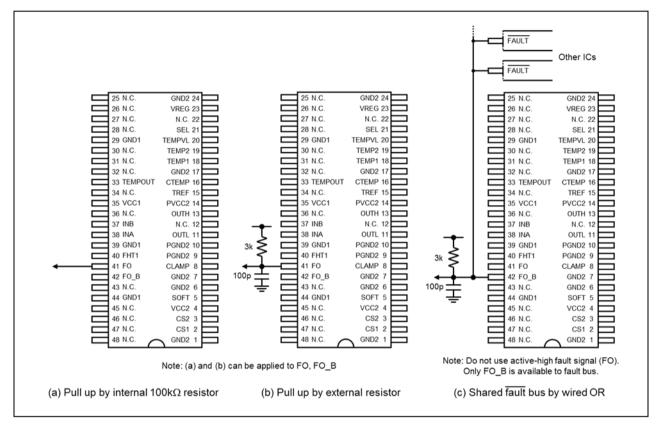

#### 4.7 Fault Signal Output Hold

This feature holds a fault signal output in a certain period of time when any of the following abnormal states is detected on the secondary circuit: under voltage, over current/short circuit, over temperature (IGBT over temperature, IC internal over temperature), TEMP1 and TEMP2 pin open, or timeout. Figure 9 is a fault signal output circuit. Figure 10 is a fault signal output hold time setting circuit.

While a fault signal output is held, the high level and the low level are output from the non-inverted fault output pin (FO) and the inverted fault output pin (FO\_B) on the primary circuit, respectively, and the IGBT is forcibly turned off. The IGBT cannot be turned on again until the end of the fault signal output hold time.

The time for which a fault signal output is held can be set by the capacitor C<sub>FHT1</sub> connected to the FHT1 Rev. 5.2 E R33DS0010EJ0520 Page 10 of 38

pin. Table 3 shows the relationship between the hold time of a fault signal output on the primary circuit (MCU side) and the hold time of a soft turn-off output on the secondary circuit (IGBT side).

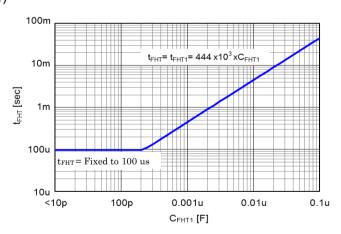

Table 11 shows the relationship between the capacitance of C<sub>FHT1</sub> and the fault signal hold time t<sub>FHT</sub>. In addition, since the secondary circuit includes a 100 us timer, the fault signal output hold time t<sub>FHT</sub> is 100 us when the value of C<sub>FHT1</sub> is smaller than 100 us. Refer to table 4 for the conditions needed to reset a fault signal output after the detection of an abnormal state.

Figure 9: Fault Signal Output Circuit

Figure 10: Fault Signal Output Hold Time Setting Circuit

Table 3: Fault Signal Output Hold Time (tFHT)

|                                                                | Hold time for fault signal off | output and IGBT soft turn-          |  |  |  |  |  |

|----------------------------------------------------------------|--------------------------------|-------------------------------------|--|--|--|--|--|

|                                                                | Without CFHT1                  | With CFHT1                          |  |  |  |  |  |

| MCU-side<br>fault signal<br>output hold<br>time (FO &<br>FO_B) | 100us                          | Greater value of<br>tFHT1 or 100 us |  |  |  |  |  |

| IGBT-side<br>soft turn-off<br>hold time                        | 100us                          | 100us                               |  |  |  |  |  |

| Values are typical                                             |                                |                                     |  |  |  |  |  |

Note:  $t_{FHT1}$  is fixed to 100 us when  $t_{FHT1} \le 100$ us.

Figure 11: Relationship between Capacitor Value Connected to FHT1 Pin and Fault Signal Output Hold Time

Table 4: Abnormal State Detecting Conditions and Fault Signal Output Hold Resetting Conditions

| Out Pins   | Fault "SET" conditions                                                                                                                                                                                                                                                                                                                             | Fault "RESET" conditions                                                                                                                                                                                                                |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FO<br>FO_B | At least one of the following conditions occurs  • Over Current: CS1/2 > 0.25V (When IGBT=ON)  • Short Circuit: CS1/2 > 0.5V (When IGBT=ON)  • TEMP1/2 < VTEMPVL-0.1V  • TEMP1/2 > 4.25V  • VCC2 < 10V  • VREG < 4.1V  • Driver temperature > 200°C  • No signal from MCU-side to IGBT-side  • No signal from IGBT-side to MCU-side  • VCC1 < 4.1V | All the following conditions are satisfied  • All the fault "SET" conditions cleared  • 100us (typ.) elapsed since fault occurred  • t <sub>FHT1</sub> elapsed since fault occurred  • INA=L or INB=H  • Signal from IGBT-side detected |

Note: All of the values in the table are typical.

Table 5 shows a list of abnormal states and the operations when those abnormal states are detected. If an abnormal state detection signal is instantaneously kept shorter than the filtering time, it is ignored as a noise.

Table 5: List of Abnormal States (When SEL Pin Input Level is Low (= GND2))

|                  |                            |                     |                       |                          |                       | IGBT-Si               | de Fault              |                       |                       |                       | MCU-Si           | de Fault  |

|------------------|----------------------------|---------------------|-----------------------|--------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|------------------|-----------|

|                  |                            | Normal<br>Condition | Short<br>Circuit      | Over<br>Current<br>Note) | IGBT<br>Over Temp.    | TEMP1/2<br>Open       | VCC2<br>UVLO          | VREG<br>UVLO          | Timeout               | TSD                   | VCC1<br>UVLO     | Timeout   |

| ditions          | Monitor<br>Pin             | -                   | cs                    | 1/2                      | TEM                   | P1/2                  | VCC2                  | VREG                  | Internal              | Internal              | VCC1             | Internal  |

| Input conditions | Fault<br>Criteria          | -                   | > 0.5V                | > 0.25V                  | < VTEMPVL-<br>0.1     | > 4.25                | < 10V                 | < 4.1V                | No Signal             | >200°C                | < 4.1V           | No Signal |

| qu               | Filter Time                | -                   | None                  | 1us                      | 10us                  | 10us                  | 25us                  | 2us                   | 20us                  | 2us                   | 2us              | 20us      |

|                  | FO<br>MCU-Side<br>Output   | L                   | Н                     | н                        | Н                     | Н                     | Н                     | Н                     | Н                     | Н                     | Н                | Н         |

| Outputs          | FO_B<br>MCU-Side<br>Output | н                   | ٦                     | L                        | L                     | L                     | ٦                     | L                     | ٦                     | ٦                     | L                | L         |

|                  | IGBT-Side<br>Operation     | IGBT<br>On / Off    | IGBT Soft<br>Turn Off | IGBT Soft<br>Turn Off    | IGBT Soft<br>Turn Off | IGBT Soft<br>Turn Off | IGBT Soft<br>Turn Off | IGBT Soft<br>Turn Off | IGBT Soft<br>Turn Off | IGBT Soft<br>Turn Off | IGBT Turn<br>Off | -         |

-: Not related

Values are typical

Note: When the SEL pin input level is high (= VREG), the IGBT over current detection function is disabled (4.6.1).

Table 6: I/O Truth Table

|                   |         |                                             |               |                   |                       |                       |                 |                           |                         |              |                   |               |                   |                                           |                                            |                    |                    |                    |                   |                                                                                                    |               |          | _                 |

|-------------------|---------|---------------------------------------------|---------------|-------------------|-----------------------|-----------------------|-----------------|---------------------------|-------------------------|--------------|-------------------|---------------|-------------------|-------------------------------------------|--------------------------------------------|--------------------|--------------------|--------------------|-------------------|----------------------------------------------------------------------------------------------------|---------------|----------|-------------------|

| 1                 | Note    | VCC1 under voltage<br>MCU-side fault output | IGBT turn-off |                   | #o can't lowrold TGOI | ופם ואסווושו ומווי-סו |                 | ao amin'i Journal I Taoli | ופם ו אסווושו ומווי-סוו | Over current | IGBT soft tum-off | Short circuit | IGBT soft tum-off | VCC1 under voltage MCLI-side fault output | Communication timeout<br>IGBT soft tum-off | VREG under voltage | IGBT soft tum-off  | VCC2 under voltage | IGBT soft tum-off | IGBT over-temp MCU-side fault output IGBT soft turn-off Open IGBT temp diode MCU-side fault output |               |          | IGBT soft tum-off |

|                   | FHT1    | Charge                                      |               |                   |                       | -                     | _               | ,                         |                         |              |                   |               |                   |                                           |                                            | Charge             | )                  |                    |                   |                                                                                                    |               |          |                   |

| outputs           | FO_B    | _                                           |               |                   |                       |                       | Е               |                           |                         |              |                   |               |                   |                                           |                                            | ب                  |                    |                    |                   |                                                                                                    |               |          |                   |

| MCU-side outputs  | FO      | I                                           |               |                   |                       | _                     |                 |                           |                         |              |                   |               |                   |                                           |                                            | I                  |                    |                    |                   |                                                                                                    |               |          |                   |

| 2                 | TEMPOUT | Γ                                           |               |                   |                       |                       |                 | PWM                       | Output                  |              |                   |               |                   |                                           |                                            | ٦                  |                    |                    |                   |                                                                                                    | PWM           | Output   |                   |

|                   | SOFT    |                                             |               |                   | High-Z                |                       |                 |                           |                         |              |                   |               |                   |                                           |                                            | ب                  |                    |                    |                   |                                                                                                    |               |          |                   |

| IGBT-side outputs | ОПТН    |                                             |               | High-Z            |                       |                       |                 | _                         | <b>E</b>                |              |                   |               |                   |                                           |                                            | High-Z             | )                  |                    |                   |                                                                                                    |               |          |                   |

| IGBT-sid          | OUTL    |                                             |               | _                 |                       |                       |                 | ۱. طه: ا                  | 7-ligil                 |              | Z-t               |               | Z-ı               |                                           | Z-ı                                        |                    | Z-ı                |                    | Z-ı               |                                                                                                    | Z-ı           |          | Z-ı               |

|                   | CLAMP   | T                                           | High-Z        | L                 | High-Z                | Г                     | High-Z          | 7 451                     | 7-IIBIL                 |              | High-Z            |               | High-Z            | Т                                         | High-Z                                     |                    | High-Z             | ٦                  | High-Z            | T                                                                                                  | High-Z        | Γ        | High-Z            |

|                   | CLAMP   | <3.0V                                       | >3.0V         | <3.0V             | >3.0V                 | <3.0V                 | >3.0V           | >                         | <                       | <3.0V        | >3.00             | <3.0V         | >3.0V             | <3.0V                                     | >3.0V                                      | <3.0V              | >3.0V              | <3.0V              | >3.0V             | <3.0V                                                                                              | >3.0V         | <3.0V    | >3.0V             |

|                   | TEMP1/2 |                                             | •             | >VTEMPVL<br>-0.1V | , <u>c</u>            | 2 (                   | <4. <u>2</u> 5V |                           |                         |              | •                 |               |                   |                                           | ×                                          | •                  |                    |                    |                   | <vtempvl< td=""><td>-0.1<i>v</i></td><td>&gt;4.25V</td><td>&gt;10us</td></vtempvl<>                | -0.1 <i>v</i> | >4.25V   | >10us             |

| e inputs          | SEL     |                                             |               |                   | ×                     |                       |                 |                           | I                       | -            | _                 |               |                   |                                           |                                            |                    | ×                  |                    |                   |                                                                                                    |               |          |                   |

| IGBT-side inputs  | CS1/2   |                                             |               | ×                 |                       |                       |                 | <0.25V                    | >0.25V                  | and<br><0.5V | >1.0us            | 740           | 5.0               |                                           |                                            |                    |                    | ×                  |                   |                                                                                                    |               |          |                   |

|                   | VCC2    |                                             |               |                   |                       |                       | >11<            | •                         |                         |              |                   | •             |                   |                                           | ×                                          |                    |                    | <10V               | >25us             |                                                                                                    | 74            | <u>-</u> |                   |

|                   | VREG    |                                             |               |                   |                       |                       | >4.20           |                           |                         |              |                   |               |                   |                                           | ×                                          | / 1/               | <u>-</u><br>+<br>/ |                    |                   | č                                                                                                  | ۷<br>۲.<br>۲. |          |                   |

| uts               | INB     | ×                                           |               | >                 | <                     | _                     | Г               | _                         |                         |              |                   |               |                   | ×                                         |                                            |                    |                    |                    |                   |                                                                                                    |               |          |                   |

| MCU-side inputs   | ANI     | ×                                           |               | _                 | J                     | >                     | <               | ± ±                       |                         |              | ×                 |               |                   |                                           |                                            |                    |                    |                    |                   |                                                                                                    |               |          |                   |

| MCU.              | VCC1    | ×4.1V                                       | snozs         |                   | _                     |                       |                 | 6 7                       | 74.2v                   |              |                   |               |                   | V1 4>                                     | >20us                                      |                    |                    |                    |                   |                                                                                                    |               |          |                   |

# 5. Electrical Characteristics

# 5.1 Absolute Maximum Ratings

Ta = -40 to 125 degC, PGND2 = GND2=0V, PVCC2 = VCC2, unless otherwise specified.

| NI. | 0                                     | D                                          | Dia Conditions                         |      | Values |                       | 1.1              |

|-----|---------------------------------------|--------------------------------------------|----------------------------------------|------|--------|-----------------------|------------------|

| No. | Symbol                                | Parameter                                  | Pin, Conditions                        | Min. | Тур.   | Max.                  | Units            |

| A1  | V <sub>ISO1</sub>                     | Maximum Isolation (t=60sec)                |                                        | 2500 | -      | -                     | $V_{RMS}$        |

| A2  | V <sub>ISO2</sub>                     | Maximum Isolation (t=1sec)                 |                                        | 3000 | -      | -                     | V <sub>RMS</sub> |

| A3  | V <sub>ISO3</sub>                     | Maximum Isolation DC                       |                                        | 650  |        |                       | V                |

| A4  | $V_{CMR}$                             | Common Mode Rejection                      |                                        | 35   | -      | -                     | KV/us            |

| A5  | V <sub>CC1</sub>                      | Positive Power Supply MCU-side             | VCC1                                   | -0.3 | -      | 6.5                   | V                |

| A6  | V <sub>CC2</sub>                      | Positive Power Supply IGBT-side            | VCC2, PVCC2                            | -0.3 | -      | 40                    | V                |

| A7  | V <sub>OUT2</sub>                     | Gate Driver Output Voltage                 | OUTH, OUTL, CLAMP, SOFT                | -0.3 | -      | V <sub>CC2</sub> +0.3 | V                |

| A8  | I <sub>OUTH</sub>                     | Gate Driver High-Side Peak<br>Current      | OUTH<br>fiso=10kHz, t=1us              | -10  | -      | 0                     | А                |

| A9  | I <sub>OUTL</sub>                     | Gate Driver Low-Side Peak Current          | OUTL, CLAMP<br>fiso=10kHz, t=1us       | 0    | -      | 10                    | А                |

| A10 | I <sub>SOFT</sub>                     | Soft Turn Off Peak Current                 | SOFT                                   | 0    | -      | 1.0                   | Α                |

| A11 | $V_{REG}$                             | Regulator Output Voltage                   | VREG                                   | -0.3 | -      | 6.5                   | V                |

| A12 | I <sub>REG</sub>                      | Regulator Output Current                   | VREG                                   | -10  | -      | 0                     | mA               |

| A13 | V <sub>OCD</sub>                      | Overcurrent Sense Input Voltage            | CS1, CS2                               | -0.3 | -      | V <sub>CC2</sub> +0.3 | V                |

| A14 | V <sub>IN2</sub>                      | IGBT-Side Input Voltage                    | TEMP1, TEMP2, SEL, TEMPVL, TREF, CTEMP | -0.3 | -      | V <sub>REG</sub> +0.3 | V                |

| A15 | V <sub>IN1</sub>                      | MCU-Side Input Pin Voltage                 | INA, INB                               | -0.3 | -      | V <sub>CC1</sub> +0.3 | V                |

| A16 | V <sub>OUT1</sub>                     | Fault Output Voltage                       | FO, FO_B                               | -0.3 | -      | V <sub>CC1</sub> +0.3 | V                |

| A17 | $V_{TOUT}$                            | Temp Monitor Output Voltage                | TEMPOUT                                | -0.3 | -      | V <sub>CC1</sub> +0.3 | V                |

| A18 | V <sub>FHT1</sub>                     | MCU-Side Fault Hold Timer Input<br>Voltage | FHT1                                   | -0.3 | -      | V <sub>CC1</sub> +0.3 | V                |

| A19 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | ESD Canability (LIDM)                      | FO, FO_B                               | -1   | -      | 1                     | kV               |

| AI9 | V <sub>ESD1</sub>                     | ESD Capability (HBM)                       | Other Pins                             | -2   | -      | 2                     | kV               |

| A20 | V <sub>ESD2</sub>                     | ESD Capability (MM)                        | All Pins                               | -200 | -      | 200                   | V                |

| A21 | V <sub>ESD3</sub>                     | ESD Capability (CDM)                       | All Pins                               | -500 | -      | 500                   | V                |

| AZI | V ESD3                                | ESD Capability (CDIVI)                     | Corner Pins                            | -750 | -      | 750                   | V                |

| A22 | $P_d$                                 | Power Dissipation                          | Rj-a=83.3°C/W Note1                    | -    | -      | 0.30                  | W                |

| A23 | T <sub>A</sub>                        | Ambient Temperature                        | -                                      | -40  | -      | 125                   | °C               |

| A24 | TJ                                    | Junction Temperature                       | -                                      | -40  | -      | 150                   | °C               |

| A25 | T <sub>STG</sub>                      | Storage Temperature                        | -                                      | -55  | -      | 150                   | °C               |

Current flowing directions are:

Plus (+) or none: from outside to IC, Minus (–): from IC to outside  $\,$

Note1: Mounted on FR4 board. IC stand alone. JEDEC compliant

### 5.2 Recommended Operating Conditions

PGND2 = GND2 = 0 V, PVCC2 = VCC2, unless otherwise specified.

|     |                      |                                 |                  | ,    | ,      |      | о ороошош. |

|-----|----------------------|---------------------------------|------------------|------|--------|------|------------|

| No. | Symbol               | Parameter                       | Pin, Conditions  |      | Values |      | Units      |

| NO. | Syllibol             | Farameter                       | Fill, Collations | Min. | Тур.   | Max. | Ullits     |

| B1  | V <sub>CC1</sub>     | Positive Power Supply MCU-side  | Pin: VCC1        | 4.5  | 5.0    | 5.5  | V          |

| B2  | V <sub>CC2</sub>     | Positive Power Supply IGBT-side | Pin: VCC2, PVCC2 | 12.5 | 15     | 21.5 | V          |

| В3  | $V_{TEMPVL_R}$       | TEMPVL Input Voltage Range      | Pin: TEMPVL      | 0.5  | -      | 2.4  | V          |

| B4  | f <sub>ISO</sub>     | Signal Frequency                | Pin: INA, INB    | -    | 15     | 100  | kHz        |

| B5  | t <sub>IN</sub>      | Minimum Input Pulse Width       | Pin: INA, INB    | -    | 20     | -    | ns         |

| В6  | f <sub>TEMPOUT</sub> | TEMPOUT Output Frequency        | Pin: TEMPOUT     | 1    | -      | 10   | kHz        |

| В7  | T <sub>A</sub>       | Ambient Temperature             | -                | -40  | -      | 125  | °C         |

# 5.3. Power Supply

Ta = -40 to 125 degC, GND1 = GND2 = PGND2 = 0 V, VCC1 = 4.5 to 5.5 V, VCC2 = PVCC2 = 12.5 to 21.5 V, unless otherwise specified.

| No.  | Symbol               | Parameter                        | Din Co                            | onditions   |      | Values |      | Unit | Note |

|------|----------------------|----------------------------------|-----------------------------------|-------------|------|--------|------|------|------|

| INO. | Symbol               | Parameter                        | i iii, Ooriditions                |             | Min. | Тур.   | Max. | s    | Note |

| V1   | I <sub>CC1Q</sub>    | VCC1 Quiescent Supply<br>Current | Pin: VCC1<br>INA, INB=GN          | ND1 or VCC1 | 1    | 3.1    | 5.5  | mA   |      |

| V2   | I <sub>CC1_15k</sub> | VCC1 Operation Supply<br>Current | Pin: VCC1<br>INA=15kHz,           | INB=GND1    | ı    | 3.5    | 6.0  | mA   |      |

| V3   | I <sub>CC2Q</sub>    | VCC2 Quiescent Supply<br>Current | Pin: VCC2<br>INA, INB=GN          | ND1 or VCC1 | ı    | 6.3    | 9.0  | mA   |      |

| V4   | I <sub>CC2_15k</sub> | VCC2 Operation Supply<br>Current | Pin: VCC2, I<br>INB=GND1,         | ,           | ı    | 6.8    | 12.0 | mA   |      |

| V5   | V                    | VPEC Output Voltage              | Pin:<br>VREG,                     | -40°C∼125°C | 4.7  | 5.0    | 5.3  | V    |      |

| VS   | $V_{REG1}$           | VREG Output Voltage              | I <sub>REG</sub> =0mA             | 25°C        | 4.8  | 5.0    | 5.2  | ٧    |      |

| V6   | $V_{REG2}$           | VREG Output Voltage              | Pin: VREG, I <sub>REG</sub> =-5mA |             | 4.7  | 5.0    | 5.3  | >    |      |

Current flowing directions are:

Plus (+) or none: from outside to IC, Minus (-): from IC to outside

### 5.4. Logic Input/Output

Ta = -40 to 125 degC, GND1 = GND2 = PGND2 = 0 V, VCC1 = 4.5 to 5.5 V, VCC2 = PVCC2 = 12.5 to 21.5 V, unless otherwise specified.

| No.  | Symbol              | Parameter                              | Pin, Conditions                     |                        |                         | Unite                  | Note           |      |

|------|---------------------|----------------------------------------|-------------------------------------|------------------------|-------------------------|------------------------|----------------|------|

| INO. | Symbol              | Faiailletei                            | Fill, Collations                    | Min.                   | Тур.                    | Max.                   | V V V KΩ KΩ RΩ | NOLE |

| L1   | $V_{INL}$           | Low Level Input Voltage                | Pin: INA, INB                       | -                      |                         | 0.3 x V <sub>CC1</sub> | V              |      |

| L2   | $V_{INH}$           | High Level Input Voltage               | Pin: INA, INB                       | 0.7 x V <sub>CC1</sub> | -                       | -                      | <b>V</b>       |      |

| L3   | V <sub>INHYS</sub>  | Input Hysteresis                       | Pin: INA, INB                       | -                      | 0.12 x V <sub>CC1</sub> | -                      | ٧              |      |

| L4   | R <sub>INA</sub>    | INA Pull-down Resistance               | Pin: INA,                           | 50                     | 100                     | 200                    | kΩ             |      |

| L5   | R <sub>INB</sub>    | INB Pull-up Resistance                 | Pin: INB,                           | 50                     | 100                     | 200                    | kΩ             |      |

| L6   | R <sub>OL_FO</sub>  | FO/FOB Low Level Output<br>Resistance  | Pin: FO, FO_B, I <sub>0</sub> =2mA  | -                      | 20                      | 100                    | Ω              |      |

| L7   | R <sub>OH_FO</sub>  | FO/FOB High Level Output<br>Resistance | Pin:FO,FO_B, I <sub>O</sub> = -10uA | 50                     | 100                     | 250                    | kΩ             |      |

| L8   | I <sub>OFF_FO</sub> | IOπ Leak Current                       | Pin: FO, FO_B<br>FO=FO B=VCC1       | -1                     | -                       | 1                      | uA             |      |

Current flowing directions are:

Plus (+) or none: from outside to IC, Minus (-): from IC to outside

### 5.5. Gate Driver

Ta = -40 to 125 degC, GND1 = GND2 = PGND2 = 0 V, VCC1 = 4.5 to 5.5 V, VCC2 = PVCC2 = 12.5 to 21.5 V, unless otherwise

specified.

| No.  | Symbol               | Parameter                                 | Pin, Conditions                                                 |      | Values |      | Linito             | Note |

|------|----------------------|-------------------------------------------|-----------------------------------------------------------------|------|--------|------|--------------------|------|

| INO. | Symbol               | Parameter                                 | Pili, Coliditions                                               | Min. | Тур.   | Max. | Units Ω uA Ω uA ns | Note |

| D1   | R <sub>O_OUTH</sub>  | OUTH High Level Output<br>Resistance      | Pin: OUTH,<br>I <sub>o</sub> =-100mA                            | ı    | 0.5    | 1.0  | Ω                  |      |

| D2   | I <sub>OL_OUTH</sub> | OUTH Low Level Leak<br>Current            | Pin: OUTH,<br>OUTH=PGND2                                        | -10  | 1      | 1    | uA                 |      |

| D3   | R <sub>O_OUTL</sub>  | OUTL Low Level Output<br>Resistance       | Pin: OUTL,<br>I <sub>0</sub> =100mA                             | ,    | 0.5    | 1.0  | Ω                  |      |

| D4   | I <sub>OH_OUTL</sub> | OUTL High Level Leak<br>Current           | Pin: OUTL,<br>OUTL=PVCC2                                        | ,    | ,      | 10   | uA                 |      |

| D5   | t <sub>PLH</sub>     | INA High to OUTH 10%<br>Propagation Delay | Pin: INA, OUTH, $R_{GH}$ =5.1 $\Omega$ , $R_{GL}$ =5.1 $\Omega$ | 30   | 70     | 140  | ns                 |      |

| D6   | t <sub>PHL</sub>     | INA Low to OUTL 90%<br>Propagation Delay  | Pin: INA, OUTL, $R_{GH}$ =5.1 $\Omega$ , $R_{GL}$ =5.1 $\Omega$ | 30   | 70     | 140  | ns                 |      |

Current flowing directions are:

Plus (+) or none: from outside to IC, Minus (-): from IC to outside

### 5.6. Active Miller Clamp

Ta = -40 to 125 degC, GND1 = GND2 = PGND2 = 0 V, VCC1 = 4.5 to 5.5 V, VCC2 = PVCC2 = 12.5 to 21.5 V, unless otherwise 1.5 V, VCC2 = 1.5 VCC2 = 1.5 V, VCC2 = 1.5 VCC2 = 1.5 VCC2

specified.

| No.  | Cumhal                | Parameter                         | Pin, Conditions                      |      | Values |      |       |      |

|------|-----------------------|-----------------------------------|--------------------------------------|------|--------|------|-------|------|

| INO. | Symbol                | Parameter                         | Pin, Conditions                      | Min. | Тур.   | Max. | Units | Note |

| M1   | R <sub>O_CLAMP</sub>  | CLAMP Low Level Output Resistance | Pin: CLAMP,<br>I <sub>0</sub> =100mA | -    | 0.5    | 1.0  | Ω     |      |

| M2   | I <sub>OH_CLAMP</sub> | CLAMP High Level Leak<br>Current  | Pin: CLAMP,<br>CLAMP=PVCC2           | -    | 1      | 10   | uA    |      |

| M3   | V <sub>CLAMP</sub>    | CLAMP Trip Voltage                | Pin: CLAMP                           | 2.7  | 3.0    | 3.3  | V     |      |

| M4   | t <sub>CLAMP</sub>    | Active Mirror Clamp<br>Delay Time | Pin: CLAMP                           | 20   | 70     | 140  | ns    |      |

Current flowing directions are:

Plus (+) or none: from outside to IC, Minus (-): from IC to outside

# 5.7. Soft Turn-off

Ta = -40 to 125 degC, GND1 = GND2 = PGND2 = 0 V, VCC1 = 4.5 to 5.5 V, VCC2 = PVCC2 = 12.5 to 21.5 V, unless otherwise

specified.

| эрссии | , u.                 |                                     |                             |      |        |       |        |      |

|--------|----------------------|-------------------------------------|-----------------------------|------|--------|-------|--------|------|

| No.    | Symbol               | Parameter                           | Pin, Conditions             |      | Values | Units | Note   |      |

|        |                      |                                     | Pill, Collditions           | Min. | Тур.   | Max.  | Uillis | Note |

| S1     | R <sub>o_SOFT</sub>  | SOFT Low Level Output<br>Resistance | ttput Pin: SOFT,<br>Io=0.1A |      | 3.5    | 8.5   | Ω      |      |

| S2     | I <sub>OH_SOFT</sub> | SOFT High Level Leak<br>Current     | Pin: SOFT,<br>SOFT=PVCC2    | -    | -      | 3     | uA     |      |

Current flowing directions are:

Plus (+) or none: from outside to IC, Minus (-): from IC to outside

# 5.8. UVLO

$Ta = -40 \text{ to } 125 \text{ degC}, \\ GND1 = GND2 = PGND2 = 0 \\ V, \\ VCC1 = 4.5 \\ \text{ to } 5.5 \\ V, \\ VCC2 = PVCC2 = 12.5 \\ \text{ to } 21.5 \\ V, \\ \text{unless otherwise} \\ V, \\ VCC1 = 4.5 \\ \text{ to } 5.5 \\ V, \\ VCC2 = PVCC2 = 12.5 \\ \text{ to } 21.5 \\ V, \\ \text{unless otherwise} \\ V, \\ VCC1 = 4.5 \\ \text{ to } 5.5 \\ V, \\ VCC2 = PVCC2 = 12.5 \\ \text{ to } 21.5 \\ V, \\ \text{unless otherwise} \\ V, \\ \text{u$

specified.

| No.  | Symbol                  | Parameter                     | Pin, Conditions   |      | Values |      |          | Note |

|------|-------------------------|-------------------------------|-------------------|------|--------|------|----------|------|

| INO. |                         |                               | Pili, Coliditions | Min. | Тур.   | Max. | Units    | Note |

| U1   | V <sub>UVLO_VCC1T</sub> | VCC1 UVLO Trip<br>Voltage     | Pin: VCC1         | 3.8  | 4.1    | 4.4  | V        |      |

| U2   | V <sub>UVLO_VCC1R</sub> | VCC1 UVLO Recovery<br>Voltage | Pin: VCC1         | 3.9  | 4.2    | 4.5  | V        |      |

| U3   | V <sub>UVLO_VCC1H</sub> | VCC1 UVLO<br>Hysteresis       | Pin: VCC1         | -    | 0.1    | -    | V        |      |

| U7   | V <sub>UVLO_VCC2T</sub> | VCC2 UVLO Trip<br>Voltage     | Pin: VCC2         | 9    | 10     | 11   | V        |      |

| U8   | V <sub>UVLO_VCC2R</sub> | VCC2 UVLO Recovery<br>Voltage | Pin: VCC2         | 10   | 11     | 12   | >        |      |

| U9   | V <sub>UVLO_VCC2H</sub> | VCC2 UVLO<br>Hysteresis       | Pin: VCC2         | -    | 1.0    | -    | ٧        |      |

| U13  | V <sub>UVLO_VREGT</sub> | VREG UVLO Trip<br>Voltage     | Pin: VREG         | 3.8  | 4.1    | 4.4  | V        |      |

| U14  | V <sub>UVLO_VREGR</sub> | VREG UVLO<br>Recovery Voltage | Pin: VREG         | 3.9  | 4.2    | 4.5  | ٧        |      |

| U15  | V <sub>UVLO_VREGH</sub> | VREG UVLO<br>Hysteresis       | Pin: VREG         | -    | 0.1    | -    | <b>V</b> |      |

Current flowing directions are:

Plus (+) or none: from outside to IC, Minus (-): from IC to outside

#### Note

Guaranteed by design and not subject to production testing.

# 5.9. Over Current (OC) Detection/Short Circuit (SC) Detection

$Ta = -40 \text{ to } 125 \text{ degC}, \text{ GND1} = \text{GND2} = \text{PGND2} = 0 \text{ V}, \text{ VCC1} = 4.5 \text{ to } 5.5 \text{ V}, \text{ VCC2} = \text{PVCC2} = 12.5 \text{ to } 21.5 \text{ V}, \text{ unless otherwise } 1.5 \text{ V}, \text{ VCC2} = 1.5 \text{ VCC2} = 1.5 \text{ V}, \text{ VCC2} = 1.5 \text{ VCC2} = 1.5 \text{ VCC2} = 1.5 \text{ VCC2} = 1.5 \text$

specified.

| No.  | Symbol               | Parameter                          | Din Conditions                                           | Values                 |      |                        | Units | Note |

|------|----------------------|------------------------------------|----------------------------------------------------------|------------------------|------|------------------------|-------|------|

| INO. |                      |                                    | Pin, Conditions                                          | Min.                   | Тур. | Max.                   | Ullis | Note |

| C1   | I <sub>CSL</sub>     | CS Low Level Input<br>Current      | Pin: CS1, CS2<br>CS1, CS2=GND2                           | -1                     | -    | -                      | uA    |      |

| C2   | I <sub>CSH</sub>     | CS High Level Input<br>Current     | Pin: CS1, CS2<br>CS1, CS2=VREG                           | -                      | 1    | 1                      | uA    |      |

| СЗ   | V <sub>oc</sub>      | OC Threshold Voltage               | Pin: CS1, CS2<br>SEL=GND2                                | 0.22                   | 0.25 | 0.28                   | V     |      |

| C4   | t <sub>oc-outh</sub> | OC Sense to 90%<br>OUTH Delay      | Pin: CS1, CS2, OUTH, SEL=GND2, $R_L$ =1k $\Omega$        |                        |      | 2.4                    | us    |      |

| C5   | t <sub>oc-soft</sub> | OC Sense to 90%<br>SOFT Delay      | Pin: CS1, CS2, SOFT,<br>SEL=GND2, R <sub>SOFT</sub> =1kΩ | - 1/                   |      | 2.4                    | us    |      |

| C6   | t <sub>OC-FO_B</sub> | OC Sense to 10%<br>FO_B Delay      | Pin: CS1, CS2, FO_B, SEL=GND2, $R_{FO}$ =3k $\Omega$     | -                      | 1.2  | 2.4                    | us    |      |

| C7   | V <sub>sc</sub>      | SC Threshold Voltage               | Pin: CS1, CS2<br>SEL=VREG                                | 0.44                   | 0.5  | 0.56                   | ٧     |      |

| C8   | t <sub>sc-оитн</sub> | SC Sense to 90%<br>OUTH Delay      | Pin: CS1, CS2, OUTH, SEL=VREG, $R_L$ =1 $k\Omega$        | -                      | 100  | 400                    | ns    | 1    |

| С9   | t <sub>SC-SOFT</sub> | SC Sense to 90%<br>SOFT Delay      | Pin: CS1, CS2, SOFT, SEL=VREG, $R_{SOFT}$ =1k $\Omega$   | -                      | 100  | 400                    | ns    | 1    |

| C10  | t <sub>sc-FO_B</sub> | SC Sense to 10%<br>FO_B Delay      | Pin: CS1, CS2, FO_B,<br>SEL=VREG, R <sub>FO</sub> =3kΩ   | -                      | 100  | 400                    | ns    | 1    |

| C11  | R <sub>SEL</sub>     | SEL Pull-down<br>Resistance        | Pin: SEL                                                 | 50                     | 100  | 200                    | kΩ    |      |

| C12  | V <sub>INL_SEL</sub> | Low Level Input<br>Voltage at SEL  | Pin: SEL                                                 | -                      |      | 0.3 x V <sub>REG</sub> | V     |      |

| C13  | V <sub>INH_SEL</sub> | High Level Input<br>Voltage at SEL | Pin: SEL                                                 | 0.7 x V <sub>REG</sub> |      | -                      | V     |      |

Current flowing directions are:

Plus (+) or none: from outside to IC, Minus (-): from IC to outside

#### Note

1. Guaranteed by design and not subject to production testing.

# 5.10. Temperature Monitor

Ta = -40 to 125 degC, GND1 = GND2 = PGND2 = 0 V, VCC1 = 4.5 to 5.5 V, VCC2 = PVCC2 = 12.5 to 21.5 V, unless otherwise

| specifie | ed.                  |                                                         | T                                                     |                                              |             |                            |       |                            | ,      |      |

|----------|----------------------|---------------------------------------------------------|-------------------------------------------------------|----------------------------------------------|-------------|----------------------------|-------|----------------------------|--------|------|

| No.      | Symbol               | Parameter                                               | Parameter Pin, Conditions                             |                                              |             |                            | Units | Note                       |        |      |

| 140.     | Cymbol               | rarameter                                               |                                                       | Fill, Collations                             |             |                            | Тур.  | Max.                       | Ullits | Note |

| T1       | $V_{TREF}$           | TREF Output<br>Voltage                                  | Pin: TREF<br>I <sub>TREF</sub> = -100uA               |                                              |             | 0.36                       | 0.40  | 0.44                       | V      |      |

| T2       | V <sub>TEMPVH</sub>  | IGBT Temperature<br>Monitor High Limit<br>Input Voltage | (IC internal)                                         |                                              |             | 3.50                       | 3.80  | 4.10                       | ٧      | 1    |

| Т3       | T3 I <sub>TEMP</sub> | TEMP Bias Current                                       | Pin:<br>TEMP1,<br>TEMP2                               | I <sub>TREF</sub> = -10uA                    |             | -107                       | -100  | -93                        | uA     |      |

| 10       | TEMP                 | TEIVII BIAS CUITCH                                      | V <sub>TEMP1</sub> =3.0V<br>V <sub>TEMP2</sub> =3.0V  | I <sub>TREF</sub> = -100uA                   |             | -1070                      | -1000 | -930                       | uA     |      |

|          |                      |                                                         |                                                       | TEMP=1.16V                                   |             | 13                         | 20    | 27                         | %      |      |

| T4       | _                    | PWM On Duty                                             |                                                       | TEMP-0.45\/                                  | -40°C~125°C | 43                         | 50    | 57                         | %      |      |

| T4       | D <sub>OUT</sub>     | PWW On Duty                                             | Pin:<br>TEMPOUT                                       | TEMP=2.15V                                   | 25°C        | 45                         | 50    | 55                         | %      |      |

|          |                      |                                                         |                                                       | TEMP=3.14V                                   |             | 73                         | 80    | 87                         | %      |      |

| T5       | D <sub>OUT_UL</sub>  | PWM On Duty<br>Upper Limit                              | TEMPVL<br>=0.5V                                       | TEMP>3.6V                                    |             | 83                         | 90    | 97                         | %      |      |

| Т6       | D <sub>OUT_LL</sub>  | PWM On Duty<br>Lower Limit                              |                                                       | TEMP<0.7V                                    |             |                            | 10    | 17                         | %      |      |

| Т7       | I <sub>TEMPVL</sub>  | TEMPVL Input<br>Current                                 | Pin: TEMPVL                                           |                                              |             | -1.0                       | -     | 1.0                        | uA     |      |

| Т8       | F <sub>TEMPOUT</sub> | TEMPOUT Output<br>Frequency                             | Pin: TEMPOUT<br>TEMPVL=0.5V<br>CTEMP=4.7nF            |                                              |             | 1                          | 2     | 4                          | kHz    |      |

| Т9       | V <sub>OL_TO</sub>   | Low Level Output<br>Voltage                             | Pin: TEMPOUT, I <sub>O</sub> =1mA                     |                                              |             | -                          | -     | 0.20 x<br>V <sub>CC1</sub> | ٧      |      |

| T10      | V <sub>OH_TO</sub>   | High Level Output<br>Voltage                            | Pin: TEMPOUT, I <sub>O</sub> =-1mA                    |                                              |             | 0.80 x<br>V <sub>CC1</sub> | -     | -                          | V      |      |

| T11      | V <sub>OT</sub>      | OT Detect Threshold<br>Voltage                          | Pin: TEMP1, TE<br>TEMPVL=0.5V                         | MP2,                                         |             | 0.36                       | 0.4   | 0.44                       | V      |      |

| T12      | V <sub>OP</sub>      | OPEN Detect<br>Threshold Voltage                        | Pin: TEMP1, T                                         | TEMP2                                        |             | 3.85                       | 4.25  | 4.65                       | ٧      |      |

| T13      | t <sub>от-оитн</sub> | OT Sense to 90%<br>OUTH Delay                           | Pin: TEMP1, TE<br>R <sub>L</sub> =1kΩ                 | Pin: TEMP1, TEMP2, OUTH, R <sub>L</sub> =1kΩ |             |                            | 10    | 20                         | us     |      |

| T14      | t <sub>OT-SOFT</sub> | OT Sense to 90%<br>SOFT Delay                           | Pin: TEMP1, TEMP2, SOFT, $R_{SOFT}$ =1 $k\Omega$      |                                              |             | 5                          | 10    | 20                         | us     |      |

| T15      | t <sub>OT-FO</sub>   | OT Sense to 10%<br>FO Delay                             | Pin: TEMP1, TEMP2, FO, $R_{FO}$ =3k $\Omega$          |                                              |             | 5                          | 10    | 20                         | us     |      |

| T16      | t <sub>OP-OUTH</sub> | OPEN Sense to 90%<br>OUTH Delay                         | Pin: TEMP1, TEMP2, OUTH, R <sub>L</sub> =1kΩ          |                                              |             | 5                          | 10    | 20                         | us     |      |

| T17      | t <sub>OP-SOFT</sub> | OPEN Sense to 90%<br>SOFT Delay                         | Pin: TEMP1, TEMP2, SOFT, $R_{\text{SOFT}}{=}1k\Omega$ |                                              |             | 5                          | 10    | 20                         | us     |      |

| T18      | t <sub>OP-FO</sub>   | OPEN Sense to 10%<br>FO Delay                           | Pin: TEMP1, TEMP2, FO, $R_{FO}$ =3k $\Omega$          |                                              |             | 5                          | 10    | 20                         | us     |      |

Current flowing directions are:

Plus (+) or none: from outside to IC, Minus (-): from IC to outside

### Note

Guaranteed by design and not subject to production testing.

# 5.11. Fault Signal Output Hold Timer

$Ta = -40 \text{ to } 125 \text{ degC}, \text{ GND1} = \text{GND2} = \text{PGND2} = 0 \text{ V}, \text{ VCC1} = 4.5 \text{ to } 5.5 \text{ V}, \text{ VCC2} = \text{PVCC2} = 12.5 \text{ to } 21.5 \text{ V}, \text{ unless otherwise } 1.5 \text{ V}, \text{ VCC2} = 1.5 \text{ VCC2} = 1.5 \text{ V}, \text{ VCC2} = 1.5 \text{ VCC2} = 1.5 \text{ VCC2} = 1.5 \text{ VCC2} = 1.5 \text$

specified.

| No. | Symbol                  | Parameter                             | Din Conditions                                                    | Values |      |      | l lucita | Note |

|-----|-------------------------|---------------------------------------|-------------------------------------------------------------------|--------|------|------|----------|------|

|     |                         |                                       | Pin, Conditions                                                   | Min.   | Тур. | Max. | Units    | Note |

| F1  | V <sub>FHT1</sub>       | Fault Hold Timer<br>Threshold Voltage | Pin: FHT1                                                         | 1.75   | 2    | 2.35 | ٧        |      |

| F2  | I <sub>CHG_FHT1</sub>   | Fault Hold Timer<br>Charge Current    | Pin: FHT1,<br>FHT1=1V                                             | -6     | -4.5 | -2.5 | uA       |      |

| F3  | I <sub>DSCHG_FHT1</sub> | Fault Hold Timer<br>Discharge Current | Pin: FHT1,<br>FHT1=1V                                             | 1.0    | 3.6  | 1    | mA       |      |

| F4  | t <sub>FHT0</sub>       | Fault Hold Time 0                     | Pin: FO, FO_B,SOFT<br>R <sub>FO</sub> =3kΩ, C <sub>FHT1</sub> =0  | 50     | 100  | 200  | us       |      |

| F5  | t <sub>FHT1</sub>       | Fault Hold Time 1                     | Pin: FO, FO_B<br>R <sub>FO</sub> =3kΩ, C <sub>FHT1</sub> =0.047uF | 15     | 21   | 45   | ms       |      |

Current flowing directions are:

Plus (+) or none: from outside to IC, Minus (-): from IC to outside

### 6. Timing Chart

### 6.1 Normal Gate Drive Output

Figure 12: Normal IGBT ON and OFF Operation

# 6.2 Gate Drive Output at Detection of Abnormal State

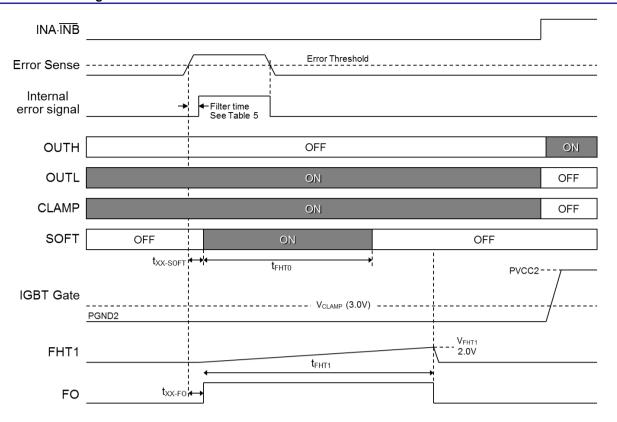

Figure 13: Operation When an Abnormal State is detected with IGBT being ON (Fault Signal Output Cleared by FHT1 Hold Time)

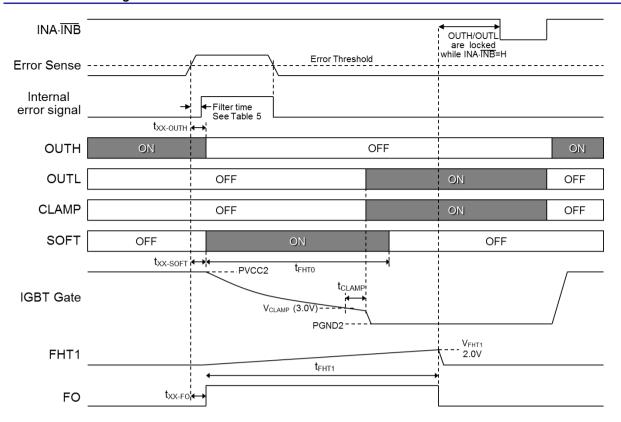

Figure 14: Operation When an Abnormal State is detected with IGBT being OFF (Fault Signal Output Cleared by FHT1 Hold Time)

Figure 15: Fault Signal Output Cleared by Edge of INA INB

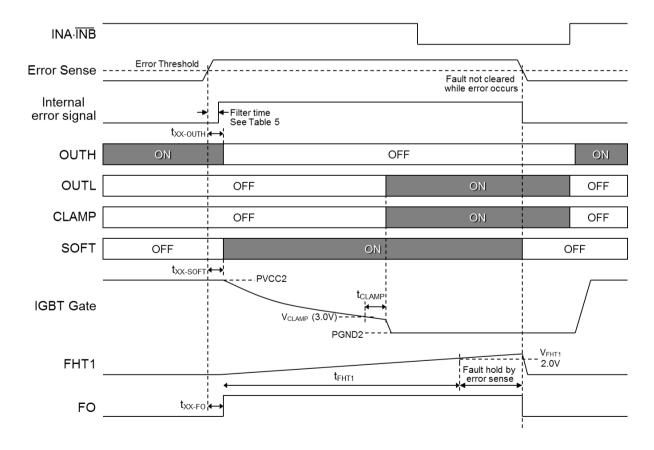

Figure 16: Fault Signal Output Cleared by Falling of Error Input Signal

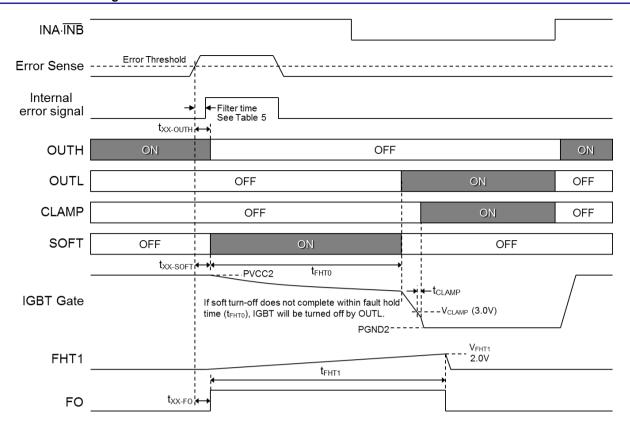

Figure 17: In Case of Uncompleted Soft Turn-off

### 6.3 Timing Charts for Detections of Various Abnormal States

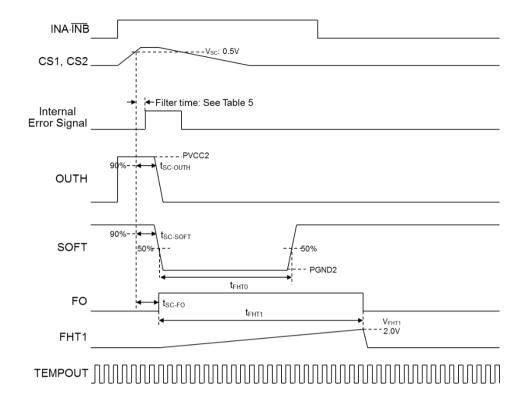

Figure 18: Short Circuit (SC) Detection

Figure 19: Over Current (OC) Detection

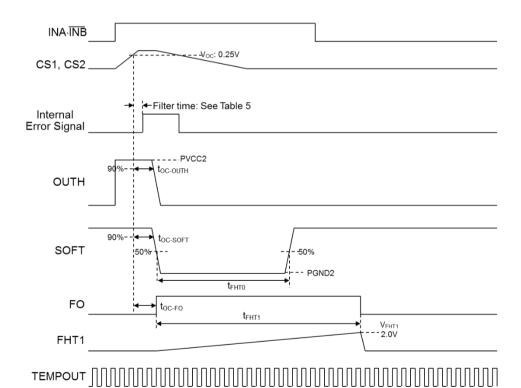

Figure 20: IGBT Temperature Monitor

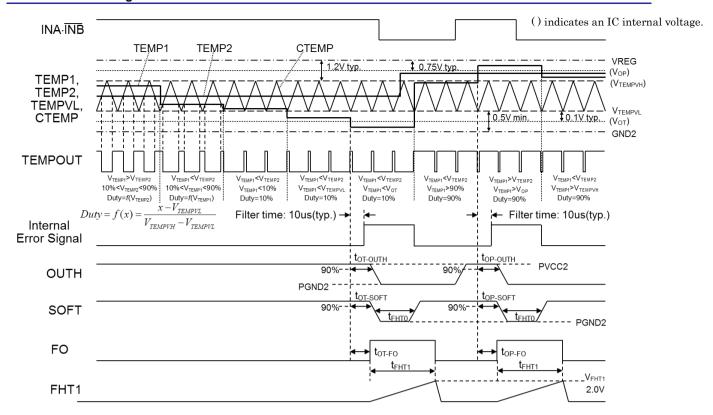

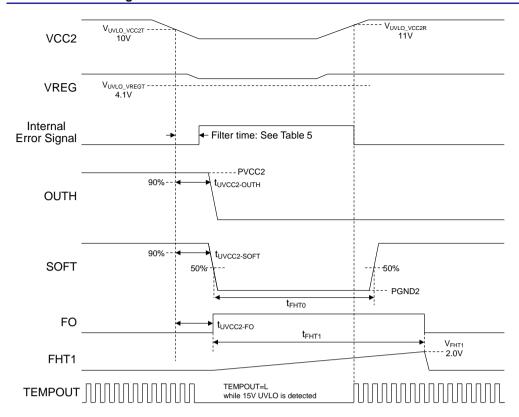

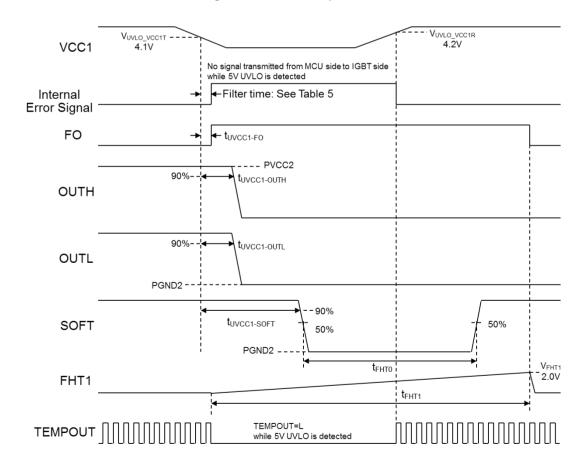

Figure 21: Secondary 5 V UVLO

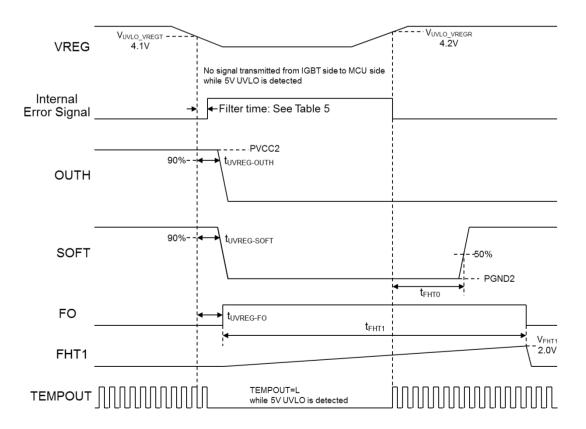

Figure 22: Secondary 15 V UVLO

Figure 23: Primary UVLO

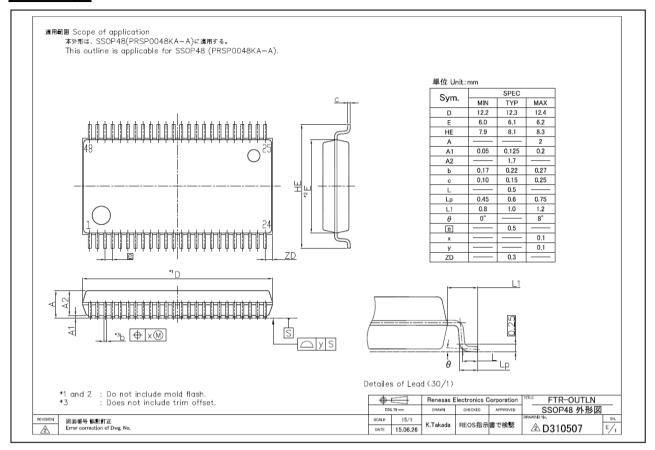

# 7. Package

Figure 24: SSOP48 Package

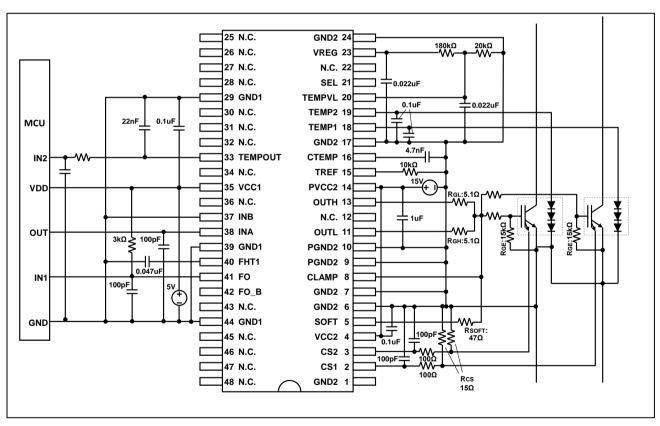

### 8. Application Examples

Figure 25 shows a circuit example including two IGBTs connected in parallel. In this example, the secondary power supply (VCC2) is 15 V. The primary power supply (VCC1) voltage is the same as the power supply voltage of the MCU (VDD).

For the gate pins of the IGBT, 5.1 ohms are inserted between that and OUTH of the IC (Rgh) and between that and OUTL (Rgh), respectively. To the gate pins of the IGBT, the SOFT and CLAMP pins of the IC are directly connected via 47 ohms (Rsoft), respectively.

For over current and load short-circuit current detection, the emitter current is detected by a combination of the multi-emitter output IGBT and shunt resistors. In this example, the shunt resistors (Rcs) to be connected to the CS1 and CS2 pins are 15 ohms. By this setting, when current flowing into the shunt resistor exceeds 16.7 mA for 1 us or more, it is detected as the over current state; when exceeding 33.3 mA, it is detected as the load short-circuit state immediately (detected as an abnormal state).

For IGBT temperature detection, the TEMP1 and TEMP2 pins are connected to the temperature sense diodes implemented in the IGBTs. Normally, a PWM signal with the on-duty ratio corresponding to a lower voltage of either the TEMP1 or TEMP2 pin is sent out from the TEMPOUT pin to the MCU. Since 4.7 nF is connected with the CTEMP pin, a frequency of the PWM signal to be sent out becomes 2.1 kHz. Since 0.5 V obtained by dividing the VREG pin output is applied to the TEMPVL pin, when either the TEMP1 or TEMP2 pin falls short of 0.4 V (Vot = Vtempvl - 0.1) or exceeds 4.25 V (Vop), it is detected as an abnormal state.

If an abnormal state is detected, the gate of the IGBT is soft turned off, and a fault signal is sent out from the FO pin to the MCU at the same time. Since 0.047 uF is connected with the FHT1 pin, the fault signal is held for about 21 ms.

Figure 25: Circuit Example around the IC

### 8.1 Circuit Example of Power Supply and GND Pins

Figure 26 shows the circuit example of the power supply and GND pins. Two GND1 pins (pin 25 and pin 37) must be short-circuited outside the IC. The GND2 pins (pin 5 and pin 14) and PGND2 pins (pin 8 and pin 7) must be short-circuited outside the IC. The bypass capacitor should be placed near each power supply pin as close as possible.

Figure 26: Circuit Example of Power Supply Pins

### 8.2 Circuit Examples of Inverted/Non-inverted Input Pins