#

## Low-Power µP Supervisory Circuits with Battery-Backup Circuit and Chip-Enable Gating

## **General Description**

The MAX16016/MAX16020/MAX16021 supervisory circuits monitor power supplies, provide battery-backup control, and chip-enable (CE) gating to write protect memory in microprocessor ( $\mu$ P)-based systems. These low-power devices improve system reliability by providing several supervisory functions in a small, single integrated solution.

The MAX16016/MAX16020/MAX16021 perform four basic system functions:

- 1) Provide a µP reset output during V<sub>CC</sub> supply powerup, power-down, and brownout conditions.

- Control V<sub>CC</sub> to battery-backup switching internally to maintain data or low-power operation for memories, real-time clocks (RTCs), and other digital logic when the main power is removed.

- 3) Provide memory write protection through internal chip-enable gating during brownout.

- 4) Provide a combination of additional supervisory functions listed in the *Features* section.

The MAX16016/MAX16020/MAX16021 operate from a 1.53V to 5.5V supply voltage and offer fixed reset thresholds for monitoring 5V, 3.3V, 3V, 2.5V, and 1.8V systems. Each device is available with either a push-pull or open-drain reset output.

The MAX16016/MAX16020/MAX16021 are available in small TDFN/TQFN packages and are fully specified for an operating temperature range of -40°C to +85°C.

### **Applications**

Main/Backup Power for RTCs, CMOS Memories Industrial Control

GPS Systems

Set-Top Boxes

Point-of-Sale Equipment

Portable/Battery Equipment

### Features

- System Monitoring for 5V, 3.3V, 3V, 2.5V, or 1.8V Power-Supply Voltages

- 1.53V to 5.5V Operating Voltage Range

- Low 1.2µA Supply Current (0.25µA in Battery-Backup Mode)

- 145ms (min) Reset Timeout Period

- Battery Freshness Seal

- On-Board Gating of CE Signals, 1.5ns Propagation Delay (MAX16020/MAX16021)

- Debounced Manual Reset Input

- ♦ Watchdog Timer, 1.2s (typ) Timeout

- Power-Fail Comparator and Low-Line Indicator for Monitoring Voltages Down to 0.6V

- Battery-On, Battery-OK, and Battery Test Indicators

- Small 10-Pin TDFN or 16-Pin TQFN Packages

- ♦ UL<sup>®</sup>-Certified to Conform to IEC 60950-1

## \_Ordering Information

| PART           | TEMP RANGE     | PIN-PACKAGE |

|----------------|----------------|-------------|

| MAX16016_TB_+T | -40°C to +85°C | 10 TDFN-EP* |

The first placeholder "\_" designates all output options. Letter "L" indicates push-pull outputs and letter "P" indicates opendrain outputs. The last placeholder "\_" designates the reset threshold (see Table 1).

T = Tape and reel.

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

#### Ordering Information continued at end of data sheet.

Selector Guide located at end of data sheet.

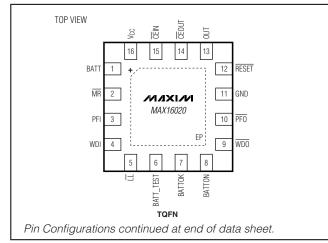

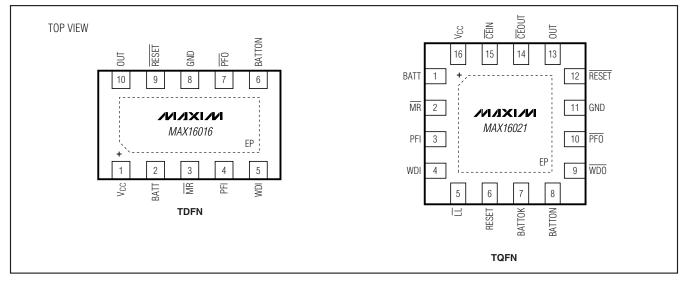

### \_Pin Configurations

UL is a registered trademark of Underwriters Laboratories, Inc.

### Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> , BATT, OUT, BATT_TEST to GND0.3V to +6V         RESET, RESET, PFO, BATTOK, WDO, BATTON,         BATT_TEST, IL, (all open-drain) to GND0.3V to +6V         RESET, RESET, BATTOK, WDO, BATTON,         IL (all push-pull) to GND0.3V to (V <sub>OUT</sub> + 0.3V)         WDI, PFI to GND0.3V to (V <sub>OUT</sub> + 0.3V)         CEIN, CEOUT to GND0.3V to (V <sub>OUT</sub> + 0.3V)         Input Current         V <sub>CC</sub> Peak Current | Output Current       10s         OUT Short Circuit to GND Duration       10s         RESET, RESET, BATTON       20mA         Continuous Power Dissipation (T <sub>A</sub> = +70°C)       10-Pin TDFN (derate 24.4mW/°C above +70°C)         10-Pin TQFN (derate 25mW/°C above +70°C)       1951mW         16-Pin TQFN (derate 25mW/°C above +70°C)       2000mW         Operating Temperature Range       -40°C to +85°C         Junction Temperature Range       -65°C to +150°C         Storage Temperature (soldering, 10s)       +300°C         Soldering Temperature (reflow)       TDFN       +260°C |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BATT Peak Current                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BATT Continuous Current70mA                                                                                                                                                                                                                                                                                                                                                                                                                                      | TQFN+240°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### PACKAGE THERMAL CHARACTERISTICS (Note 1)

TDFN

TQFN

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maxim-ic.com/thermal-tutorial</u>.

## **ELECTRICAL CHARACTERISTICS**

(V<sub>CC</sub> = 1.53V to 5.5V, V<sub>BATT</sub> = 3V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                                    | SYMBOL                              | CONDITI                                                                                          | ONS              | MIN                   | ТҮР                      | MAX | UNITS |

|----------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------|------------------|-----------------------|--------------------------|-----|-------|

| Operating Voltage Range (Note 3)             | V <sub>CC</sub> , V <sub>BATT</sub> | $V_{CC}$ or $V_{BATT} > V_{TH}$                                                                  |                  | 0                     |                          | 5.5 | V     |

|                                              |                                     |                                                                                                  | $V_{CC} = 1.62V$ |                       | 1.2                      | 2   |       |

| Supply Current                               | Icc                                 | V <sub>CC</sub> > V <sub>TH</sub>                                                                | $V_{CC} = 2.8V$  |                       | 1.9                      | 3   | μA    |

|                                              | 100                                 | VCC > VIH                                                                                        | $V_{CC} = 3.6V$  |                       | 2.3                      | 3.5 | μΑ    |

|                                              |                                     |                                                                                                  | $V_{CC} = 5.5V$  |                       | 3.4                      | 5   |       |

| Supply Current in<br>Battery-Backup Mode     | IBATT                               | $V_{CC} = 0V$                                                                                    |                  |                       | 0.25                     | 0.5 | μA    |

| V <sub>CC</sub> Switchover Threshold Voltage |                                     | V <sub>CC</sub> rising, V <sub>CC</sub> - V <sub>BATT</sub>                                      |                  |                       | 0.1<br>x V <sub>CC</sub> |     | V     |

| BATT Switchover Threshold<br>Voltage         |                                     | V <sub>CC</sub> falling, V <sub>CC</sub> < V <sub>TH</sub> , V <sub>CC</sub> - V <sub>BATT</sub> |                  |                       | 0                        |     | mV    |

| BATT Standby Current                         |                                     | $V_{CC} > V_{BATT} + 0.2V$                                                                       |                  | -10                   |                          | +10 | nA    |

| BATT Freshness Leakage Current               |                                     | $V_{BATT} = 5.5V$                                                                                |                  |                       |                          | 20  | nA    |

|                                              |                                     | $V_{CC} = 4.75V, I_{OUT} = 15$                                                                   | 0mA              |                       | 1.4                      | 4.5 |       |

| V <sub>CC</sub> to OUT On-Resistance         | Pou                                 | V <sub>CC</sub> = 3.15V, I <sub>OUT</sub> = 65mA                                                 |                  |                       | 1.7                      | 4.5 | Ω     |

| VCC to OUT ON-Nesistance                     | R <sub>ON</sub>                     | $V_{CC} = 2.35V, I_{OUT} = 25mA$                                                                 |                  |                       | 2.1                      | 5.0 |       |

|                                              |                                     | $V_{CC} = 1.91V, I_{OUT} = 10mA$                                                                 |                  |                       | 2.6                      | 5.5 |       |

| Output Voltage in                            | Vour                                | $V_{BATT} = 4.5V, I_{OUT} = 20mA$                                                                |                  | VBATT -               | 0.1                      |     | v     |

| Battery-Backup Mode                          | Vout                                | $V_{BATT} = 2.5V, I_{OUT} = 20$                                                                  | )mA              | V <sub>BATT</sub> - 0 | ).15                     |     | v     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 1.53V \text{ to } 5.5V, V_{BATT} = 3V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                                           | SYMBOL          | CONDITIONS                                                                               | MIN                   | ТҮР      | MAX                 | UNITS |

|-----------------------------------------------------|-----------------|------------------------------------------------------------------------------------------|-----------------------|----------|---------------------|-------|

| RESET OUTPUT (RESET, RESE                           | T)              |                                                                                          |                       |          |                     |       |

| Reset Threshold                                     | V <sub>TH</sub> |                                                                                          | (Se                   | ee Table | e 1)                | V     |

| V <sub>CC</sub> Falling to Reset Delay              | t <sub>RD</sub> | V <sub>CC</sub> falling at 10V/ms                                                        |                       | 20       |                     | μs    |

| Reset Timeout Period                                | t <sub>RP</sub> |                                                                                          | 145                   | 215      | 285                 | ms    |

|                                                     |                 | V <sub>CC</sub> ≥ 3.3V, I <sub>SINK</sub> = 3.2mA, RESET asserted                        |                       |          | 0.3                 |       |

| RESET Output Low Voltage                            | VOL             | $V_{CC} \ge 1.6V$ , $I_{SINK} = 1mA$ , RESET asserted                                    |                       |          | 0.3                 | V     |

|                                                     |                 | $V_{CC} \ge 1.2V$ , $I_{SINK} = 100\mu A$ , RESET asserted                               |                       |          | 0.3                 |       |

| RESET Output High Voltage<br>(Push-Pull Output)     | V <sub>OH</sub> | $V_{CC} = 1.1 \times V_{TH}$ , Isource = 100µA,<br>RESET deasserted                      | Vout<br>- 0.3         |          |                     | V     |

| RESET Output Leakage Current<br>(Open-Drain Output) |                 | $V_{\overline{RESET}} = 5.5V, \overline{RESET}$ deasserted                               |                       |          | 1                   | μA    |

| RESET Output Low Voltage                            | Vol             | V <sub>CC</sub> ≥ 3.3V, I <sub>SINK</sub> = 3.2mA, RESET<br>deasserted                   |                       |          | 0.3                 | V     |

| HESET Output Low Voltage                            | VOL             | V <sub>CC</sub> ≥ 1.8V, I <sub>SINK</sub> = 1.0mA, RESET<br>deasserted                   |                       |          | 0.3                 | v     |

| RESET Output High Voltage<br>(Push-Pull Output)     | V <sub>OH</sub> | V <sub>CC</sub> = 0.9 x V <sub>TH</sub> , I <sub>SOURCE</sub> = 100µA,<br>RESET asserted | Vout<br>- 0.3         |          |                     | V     |

| RESET Output Leakage Current<br>(Open-Drain Output) |                 | VRESET = 5.5V, RESET asserted                                                            |                       |          | 1                   | μA    |

| POWER-FAIL COMPARATOR                               |                 |                                                                                          |                       |          |                     |       |

| PFI, Input Threshold                                | VPFT            | $V_{IN}$ falling, 1.6V $\leq V_{CC} \leq 5.5V$                                           | 0.572                 | 0.590    | 0.611               | V     |

| PFI, Hysteresis                                     | VPFT-HYS        |                                                                                          |                       | 30       |                     | mV    |

| PFI Input Current                                   |                 | $V_{CC} = 5.5V$                                                                          | -1                    |          | +1                  | μA    |

|                                                     |                 | $V_{CC} \ge 1.6V$ , $I_{SINK} = 1mA$ , output asserted                                   |                       |          | 0.3                 |       |

| PFO Output Low Voltage                              | Vol             | $V_{CC} \ge 1.2V$ , $I_{SINK} = 100\mu A$ , output asserted                              |                       |          | 0.3                 | V     |

| PFO Output Voltage<br>High (Push-Pull Output)       | V <sub>OH</sub> | $V_{CC} = 1.1 \times V_{TH}$ , Isource = 100µA, output asserted                          | Vout<br>- 0.3         |          |                     | V     |

| PFO, Leakage Current<br>(Open-Drain Output)         |                 | $V_{PFO} = 5.5V$ , output deasserted                                                     |                       |          | 1                   | μA    |

| PFO, Delay Time                                     |                 | VPFT + 100mV to VPFT - 100mV                                                             |                       | 20       |                     | μs    |

| MANUAL RESET (MR)                                   | _               | -                                                                                        | _                     |          |                     |       |

| Input Low Voltage                                   | VIL             |                                                                                          |                       |          | $0.3 \times V_{CC}$ | V     |

| Input High Voltage                                  | VIH             |                                                                                          | 0.7 × V <sub>CC</sub> |          |                     | V     |

| Pullup Resistance                                   |                 |                                                                                          | 20                    | 30       |                     | kΩ    |

| Glitch Immunity                                     |                 | V <sub>CC</sub> = 3.3V                                                                   |                       | 100      |                     | ns    |

| MR to Reset Delay                                   |                 |                                                                                          |                       | 120      |                     | ns    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 1.53V \text{ to } 5.5V, V_{BATT} = 3V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                                     | SYMBOL           | CONDITIONS                                                                            | MIN                        | ТҮР   | MAX                      | UNITS |

|-----------------------------------------------|------------------|---------------------------------------------------------------------------------------|----------------------------|-------|--------------------------|-------|

| WATCHDOG TIMER (WDI, WDO                      | )                |                                                                                       |                            |       |                          |       |

| Watchdog Timeout Period                       | twD              |                                                                                       | 0.83                       | 1.235 | 1.64                     | S     |

| Minimum WDI Input Pulse Width                 | t <sub>WDI</sub> |                                                                                       | 320                        |       |                          | ns    |

| WDI Input Low Voltage                         | V <sub>IL</sub>  | (Note 6)                                                                              |                            |       | 0.3 x<br>V <sub>CC</sub> | V     |

| WDI Input High Voltage                        | V <sub>IH</sub>  | (Note 6)                                                                              | 0.7 x<br>V <sub>CC</sub>   |       |                          | V     |

| WDI Input Current (Note 7)                    |                  | V <sub>WDI</sub> = 0V or 5.5V, time average                                           | -1                         |       | +1                       | μA    |

| WDO Output Low Voltage                        | Vol              | $V_{CC} = 5.0V$ , $I_{SINK} = 1$ mA, $\overline{WDO}$ asserted                        |                            |       | 0.3                      | V     |

| WDO Output High Voltage<br>(Push-Pull Output) | Vон              | $V_{CC} = 1.1 \times V_{TH}$ , $I_{SOURCE} = 100 \mu A$ , $\overline{WDO}$ deasserted | Vout<br>- 0.3              |       |                          | V     |

| WDO Leakage Current<br>(Open-Drain Output)    |                  | $V_{\overline{WDO}} = 5.5V, \overline{WDO}$ deasserted                                |                            |       | 1                        | μA    |

| <b>BATTERY-ON INDICATOR (BAT</b>              | TON)             |                                                                                       |                            |       |                          |       |

| Output Low Voltage                            | VOL              | I <sub>SINK</sub> = 3.2mA, V <sub>BATT</sub> = 2.1V                                   |                            |       | 0.3                      | V     |

| BATTON Leakage Current                        |                  | $V_{BATTON} = 5.5V$                                                                   |                            |       | 1                        | μA    |

| BATTON Output High Voltage                    | V <sub>OH</sub>  | $V_{CC} = 0.9 \times V_{TH}$ , $I_{SOURCE} = 100 \mu A$ , BATTON asserted             | V <sub>OUT</sub><br>- 0.3  |       |                          | V     |

| Output Short-Circuit Current<br>(Note 4)      |                  | Sink current, V <sub>CC</sub> = 5V                                                    |                            | 60    |                          | mA    |

| CE GATING (CEIN, CEOUT)                       |                  |                                                                                       |                            |       |                          |       |

| CEIN Leakage Current                          |                  | Reset asserted, $V_{CC} = 0.9 \times V_{TH}$ or 0V                                    | -1                         |       | +1                       | μA    |

| CEIN to CEOUT Resistance                      |                  | Reset not asserted (Note 5)                                                           |                            | 8     | 50                       | Ω     |

| CEOUT Short-Circuit Current                   |                  | Reset asserted, $\overline{CE}OUT = 0$ ,<br>V <sub>CC</sub> = 0.9 × V <sub>TH</sub>   |                            | 0.75  | 2                        | mA    |

| CEIN to CEOUT Propagation<br>Delay            |                  | $50\Omega$ source, C <sub>LOAD</sub> = 50pF, V <sub>CC</sub> = 4.75V                  |                            | 1.5   | 7                        | ns    |

| Output Lligh Voltage                          |                  | $V_{CC} = 5V, V_{CC} \ge V_{BATT}, I_{SOURCE} = 100\mu A$                             | 0.8 x<br>V <sub>CC</sub>   |       |                          |       |

| Output High Voltage                           |                  | $V_{CC} = 0V, V_{BATT} \ge 2.2V, I_{SOURCE} = 1\mu A$                                 | V <sub>BATT</sub> -<br>0.1 |       |                          |       |

| Reset to CEOUT Delay                          |                  |                                                                                       |                            | 12    |                          | μs    |

## ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = 1.53V \text{ to } 5.5V, V_{BATT} = 3V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$  (Note 2)

| PARAMETER                                     | SYMBOL          | CONDITIONS                                                                                | MIN                       | TYP      | MAX   | UNITS |

|-----------------------------------------------|-----------------|-------------------------------------------------------------------------------------------|---------------------------|----------|-------|-------|

| LOW LINE (LL)                                 |                 |                                                                                           |                           |          |       |       |

| Low Line to Reset Threshold<br>Voltage        |                 | V <sub>CC</sub> falling                                                                   | (s                        | ee Table | 2)    | mV    |

| V <sub>CC</sub> Falling to LL Delay           |                 | V <sub>CC</sub> falling at 10V/ms                                                         |                           | 20       |       | μs    |

| LL Output Low Voltage                         | V <sub>OL</sub> | $V_{CC} \ge 1.6V$ , $I_{SINK} = 1$ mA, $\overline{LL}$ asserted                           |                           |          | 0.3   | v     |

|                                               | VOL             | $V_{CC} \ge 1.2V$ , $I_{SINK} = 100\mu A$ , $\overline{LL}$ asserted                      |                           |          | 0.3   | v     |

| LL Output High Voltage (Push-<br>Pull Output) | V <sub>OH</sub> | $V_{CC} = 0.9 \times V_{TH}_{LL}$ , ISOURCE = 100µA,<br>LL deasserted                     | V <sub>OUT</sub> -<br>0.3 |          |       | V     |

| Output Leakage Current                        |                 | $V_{\overline{LL}} = 5.5V, \overline{LL}$ deasserted                                      |                           |          | 1     | μA    |

| BATTERY-OK INDICATOR (BAT                     | TOK, BATT_T     | EST)                                                                                      |                           |          |       |       |

| BATTOK Threshold                              |                 | Inferred internally from BATT                                                             | 2.508                     | 2.6      | 2.673 | V     |

| BATTOK Output Voltage Low                     | V <sub>OL</sub> | $V_{CC}$ = 1.1 x V <sub>TH</sub> , I <sub>SINK</sub> = 1mA, reset asserted                |                           |          | 0.3   | V     |

| BATTOK Output High Voltage                    | V <sub>OH</sub> | V <sub>CC</sub> = 1.1 x V <sub>TH</sub> , I <sub>SOURCE</sub> = 100µA,<br>BATTOK asserted | V <sub>OUT</sub> -<br>0.3 |          |       | V     |

| BATTOK Output Leakage<br>Current              |                 | $V_{BATTOK} = 5.5V$ , deasserted                                                          |                           |          | 1     | μA    |

| BATT_TEST Output Low Voltage                  |                 | $V_{CC} = 1.1 \times V_{TH}$ , $I_{SINK} = 1$ mA                                          |                           |          | 0.3   | V     |

**Note 2:** All devices are 100% production tested at  $T_A = +25^{\circ}C$  and  $T_A = +85^{\circ}C$ . Limits to -40°C are guaranteed by design. **Note 3:** V<sub>BATT</sub> can be 0V anytime, or V<sub>CC</sub> can go down to 0V if V<sub>BATT</sub> is active (except at startup).

**Note 4:** Use external current-limit resistor to limit current to 20mA (max).

**Note 5:**  $\overline{CEIN}/\overline{CEOUT}$  resistance is tested with V<sub>CC</sub> = 5V and V<sub>CEIN</sub> = 0V or 5V.

**Note 6:** WDI is internally serviced within the watchdog period if WDI is left unconnected.

**Note 7:** The WDI input current is specified as the average input current when the WDI input is driven high or low. The WDI input is designed for a three-stated output device with a 10μA maximum leakage current and capable of driving a maximum capacitive load of 200pF. The three-state device must be able to source and sink at least 200μA when active.

# Table 1a. Reset Threshold Ranges(MAX16016)

| SUFFIX | RESET THRESHOLD RANGES (V) |       |       |  |  |  |

|--------|----------------------------|-------|-------|--|--|--|

| SUFFIX | MIN                        | ТҮР   | МАХ   |  |  |  |

| L      | 4.508                      | 4.63  | 4.906 |  |  |  |

| M      | 4.264                      | 4.38  | 4.635 |  |  |  |

| Т      | 2.991                      | 3.08  | 3.239 |  |  |  |

| S      | 2.845                      | 2.93  | 3.080 |  |  |  |

| R      | 2.549                      | 2.63  | 2.755 |  |  |  |

| Z      | 2.243                      | 2.32  | 2.425 |  |  |  |

| Y      | 2.117                      | 2.19  | 2.288 |  |  |  |

| W      | 1.603                      | 1.67  | 1.733 |  |  |  |

| V      | 1.514                      | 1.575 | 1.639 |  |  |  |

# Table 1b. Reset Threshold Ranges(MAX16020/MAX16021)

| SUFFIX | RESET THRESHOLD RANGES (V) |       |       |  |  |  |

|--------|----------------------------|-------|-------|--|--|--|

| JUFFIA | MIN                        | ТҮР   | MAX   |  |  |  |

| L      | 4.520                      | 4.684 | 4.852 |  |  |  |

| М      | 4.275                      | 4.428 | 4.585 |  |  |  |

| Т      | 3.010                      | 3.100 | 3.190 |  |  |  |

| S      | 2.862                      | 2.946 | 3.034 |  |  |  |

| R      | 2.568                      | 2.640 | 2.716 |  |  |  |

| Z      | 2.260                      | 2.323 | 2.390 |  |  |  |

| Y      | 2.133                      | 2.192 | 2.255 |  |  |  |

| W      | 1.616                      | 1.661 | 1.710 |  |  |  |

| V      | 1.528                      | 1.571 | 1.618 |  |  |  |

### **Table 2. Low-Line Threshold Ranges**

| SUFFIX | LOW-LINE THRESHOLD RANGES (V) |       |       |  |  |

|--------|-------------------------------|-------|-------|--|--|

|        | MIN                           | ТҮР   | МАХ   |  |  |

| L      | 4.627                         | 4.806 | 4.955 |  |  |

| М      | 4.378                         | 4.543 | 4.683 |  |  |

| Т      | 3.075                         | 3.181 | 3.274 |  |  |

| S      | 2.922                         | 3.023 | 3.111 |  |  |

| R      | 2.620                         | 2.409 | 2.787 |  |  |

| Z      | 2.309                         | 2.383 | 2.450 |  |  |

| Y      | 2.180                         | 2.246 | 2.311 |  |  |

| W      | 1.653                         | 1.704 | 1.752 |  |  |

| V      | 1.563                         | 1.612 | 1.657 |  |  |

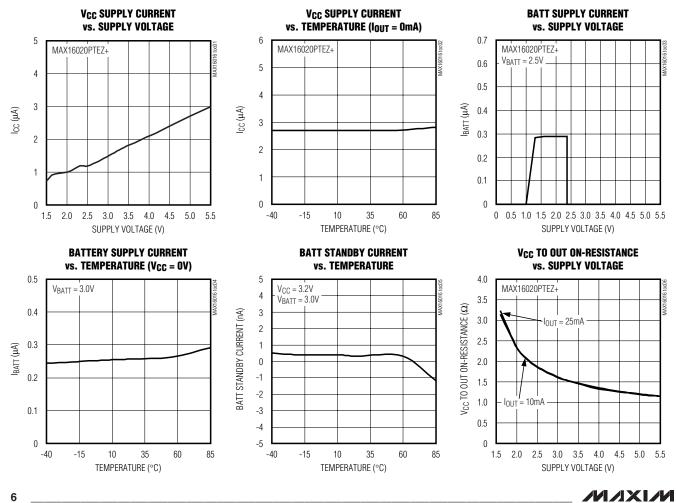

(V<sub>CC</sub> = 5V, V<sub>BATT</sub> = 0V,  $T_A$  = +25°C, unless otherwise noted.)

### **Typical Operating Characteristics**

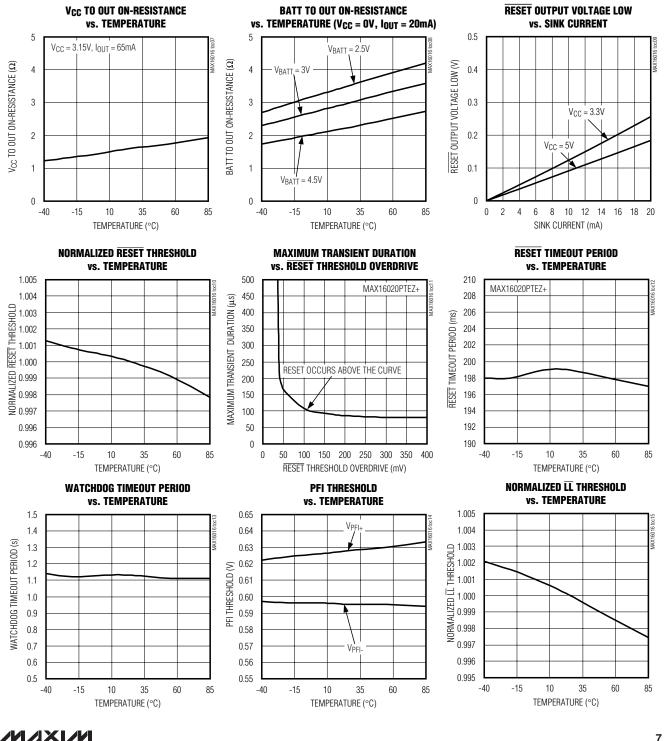

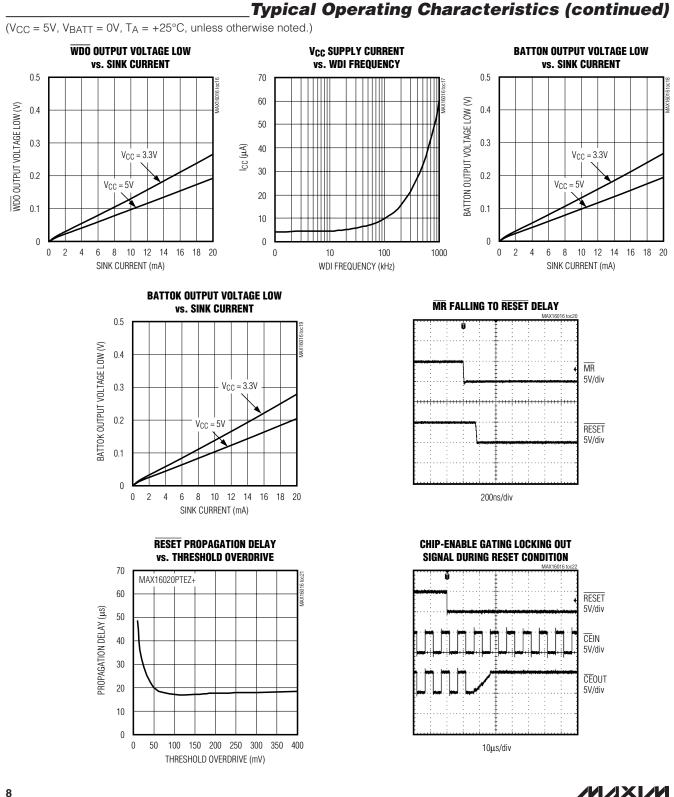

### **Typical Operating Characteristics (continued)**

$(V_{CC} = 5V, V_{BATT} = 0V, T_A = +25^{\circ}C, unless otherwise noted.)$

MAX16016/MAX16020/MAX16021

## Pin Description—MAX16016

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>CC</sub> | Supply Voltage Input. Bypass V <sub>CC</sub> to GND with a 0.1 $\mu$ F capacitor.                                                                                                                                                                                                                                                                                                                                                                                 |

| 2   | BATT            | Backup Battery Input. If V <sub>CC</sub> falls below its reset threshold, and if V <sub>BATT</sub> > V <sub>CC</sub> , OUT connects to BATT. If V <sub>CC</sub> rises above 1.01 x V <sub>BATT</sub> , OUT connects to V <sub>CC</sub> . Bypass BATT to GND with a 0.1 $\mu$ F capacitor.                                                                                                                                                                         |

| 3   | MR              | Active-Low Manual Reset Input. $\overline{\text{RESET}}$ asserts when $\overline{\text{MR}}$ is pulled low. $\overline{\text{RESET}}$ remains low for the duration of reset timeout period after $\overline{\text{MR}}$ transitions from low to high. Connect $\overline{\text{MR}}$ to V <sub>CC</sub> or leave unconnected if not used. $\overline{\text{MR}}$ is internally connected to V <sub>CC</sub> through a 30k $\Omega$ pullup resistor.               |

| 4   | PFI             | Power-Fail Comparator Input. Connect PFI to a resistive divider to set the desired PFI threshold. The PFI input is referenced to an internal V <sub>PFT</sub> threshold. A V <sub>PFT-HYS</sub> internal hysteresis provides noise immunity. The power-fail comparator is powered from OUT.                                                                                                                                                                       |

| 5   | WDI             | Watchdog Timer Input. If WDI remains high or low for longer than the watchdog timeout period ( $t_{WD}$ ), the internal watchdog timer runs out and a reset pulse is triggered for the reset timeout period. The internal watchdog clears when reset asserts or whenever WDI sees a rising or falling edge. To disable the watchdog feature, leave WDI unconnected or three-state the driver connected to WDI.                                                    |

| 6   | BATTON          | Active-High Battery-On Output. BATTON goes high when in battery-backup mode.                                                                                                                                                                                                                                                                                                                                                                                      |

| 7   | PFO             | Active-Low Power-Fail Comparator Output. $\overline{PFO}$ goes low when V <sub>PFI</sub> falls below the internal V <sub>PFT</sub> threshold and goes high when V <sub>PFI</sub> rises above V <sub>PFT</sub> + V <sub>PFT-HYS</sub> hysteresis.                                                                                                                                                                                                                  |

| 8   | GND             | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9   | RESET           | Active-Low Reset Output. $\overrightarrow{\text{RESET}}$ asserts when V <sub>CC</sub> falls below the reset threshold or $\overrightarrow{\text{MR}}$ is pulled low.<br>$\overrightarrow{\text{RESET}}$ remains low for the duration of the reset timeout period after V <sub>CC</sub> rises above the reset threshold<br>and $\overrightarrow{\text{MR}}$ goes high. $\overrightarrow{\text{RESET}}$ also asserts low when the internal watchdog timer runs out. |

| 10  | OUT             | Switched Output. OUT is connected to V <sub>CC</sub> when the reset output is not asserted or when V <sub>CC</sub> is greater than V <sub>BATT</sub> . OUT connects to BATT when RESET is asserted and V <sub>BATT</sub> is greater than V <sub>CC</sub> . Bypass OUT to GND with a $0.1\mu$ F (min) capacitor.                                                                                                                                                   |

| _Pin Description—MAX16 | 6020/MAX16021 |

|------------------------|---------------|

|------------------------|---------------|

| PI       | IN       |           | FUNCTION                                                                                                                                                                                                                                                                                                                                                                         |

|----------|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX16020 | MAX16021 | NAME      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                         |

| 1        | 1        | BATT      | Backup Battery Input. If V <sub>CC</sub> falls below its reset threshold, and if V <sub>BATT</sub> > V <sub>CC</sub> , OUT connects to BATT. If V <sub>CC</sub> rises above 1.01 x V <sub>BATT</sub> , OUT connects to V <sub>CC</sub> . Bypass BATT to GND with a 0.1 $\mu$ F capacitor.                                                                                        |

| 2        | 2        | MR        | Active-Low Manual Reset Input. RESET asserts when MR is pulled low. RESET remains low for the duration of reset timeout period after MR transitions from low to high. Connect MR to V <sub>CC</sub> or leave unconnected if not used. MR is internally connected to V <sub>CC</sub> through a $30k\Omega$ pullup resistor.                                                       |

| 3        | 3        | PFI       | Power-Fail Comparator Input. Connect PFI to a resistive divider to set the desired PFI threshold. The PFI input is referenced to an internal threshold VPFT, VPFT-HYS internal hysteresis provides noise immunity. The power-fail comparator is powered from OUT.                                                                                                                |

| 4        | 4        | WDI       | Watchdog Timer Input. If WDI remains high or low for longer than the watchdog timeout period ( $t_{WD}$ ), the internal watchdog timer runs out and asserts $\overline{WDO}$ . The internal watchdog clears when reset asserts or whenever WDI sees a rising or falling edge. To disable the watchdog feature, leave WDI unconnected or three-state the driver connected to WDI. |

| 5        | 5        | ĪĹ        | Active-Low Low-Line Output. $\overline{LL}$ goes low when V <sub>CC</sub> falls to 2.5% above the reset threshold (Table 2). $\overline{LL}$ provides an early warning of V <sub>CC</sub> failure before reset asserts. Use this output to generate a nonmaskable interrupt (NMI) to initiate an orderly shutdown routine when V <sub>CC</sub> is falling.                       |

| 6        |          | BATT_TEST | Open-Drain Battery-Test Output. Pulses low for 1.3s every 24 hours during the battery voltage test. If $V_{BATT} < 2.6V$ , BATTOK deasserts low. See Figure 6 for providing additional load during the battery test.                                                                                                                                                             |

|          | 6        | RESET     | Active-High Reset Output. RESET asserts when V <sub>CC</sub> falls below the reset threshold or when $\overline{\text{MR}}$ asserts and stays asserted for the reset timeout period after V <sub>CC</sub> rises above the reset threshold and $\overline{\text{MR}}$ deasserts.                                                                                                  |

| 7        | 7        | BATTOK    | Battery-OK Output. BATTOK goes low when the battery voltage falls below the BATTOK threshold (BATTOK is low when in battery-backup mode).                                                                                                                                                                                                                                        |

| 8        | 8        | BATTON    | Active-High Battery-On Output. BATTON goes high when in battery-backup mode.                                                                                                                                                                                                                                                                                                     |

### Pin Description—MAX16020/MAX16021 (continued)

| PIN      |          |                 | FUNCTION                                                                                                                                                                                                                                                                                                                                |  |  |  |

|----------|----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MAX16020 | MAX16021 | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 9        | 9        | WDO             | Active-Low Watchdog Output. $\overline{\text{WDO}}$ asserts when WDI remains high or low longer than the watchdog timeout period. $\overline{\text{WDO}}$ returns high on the next WDI transition or when a reset is asserted.                                                                                                          |  |  |  |

| 10       | 10       | PFO             | Active-Low Power-Fail Comparator Output. PFO goes low when V <sub>PFI</sub> falls below the internal 0.6V V <sub>PFT</sub> threshold and goes high when V <sub>PFI</sub> rises above V <sub>PFT</sub> + V <sub>PFT-HYS</sub> hysteresis.                                                                                                |  |  |  |

| 11       | 11       | GND             | Ground                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 12       | 12       | RESET           | Active-Low Reset Output. $\overline{\text{RESET}}$ asserts when V <sub>CC</sub> falls below the reset threshold or $\overline{\text{MR}}$ is pulled low. $\overline{\text{RESET}}$ remains low for the duration of the reset timeout period after V <sub>CC</sub> rises above the reset threshold and $\overline{\text{MR}}$ goes high. |  |  |  |

| 13       | 13       | OUT             | Switched Output. OUT is connected to V <sub>CC</sub> when the reset output is not asserted or when V <sub>CC</sub> is greater than V <sub>BATT</sub> . OUT connects to BATT when RESET is asserted and V <sub>BATT</sub> is greater than V <sub>CC</sub> . Bypass OUT to GND with a 0.1 $\mu$ F (min) capacitor.                        |  |  |  |

| 14       | 14       | CEOUT           | Active-Low Chip-Enable Output. $\overline{CE}OUT$ goes low only when $\overline{CE}IN$ is low and reset is not asserted. If $\overline{CE}IN$ is low when reset is asserted, $\overline{CE}OUT$ stays low for 12µs (typ) or until $\overline{CE}IN$ goes high, whichever occurs first.                                                  |  |  |  |

| 15       | 15       | CEIN            | Chip-Enable Input. The input to CE gating circuitry. Connect to GND or OUT if not used.                                                                                                                                                                                                                                                 |  |  |  |

| 16       | 16       | V <sub>CC</sub> | Supply Voltage Input. Bypass $V_{CC}$ to GND with a 0.1µF capacitor.                                                                                                                                                                                                                                                                    |  |  |  |

|          | _        | EP              | Exposed Pad. Internally connected to GND. Connect EP to a large ground plane to aid heat dissipation. Do not use EP as the only ground connection for the device.                                                                                                                                                                       |  |  |  |

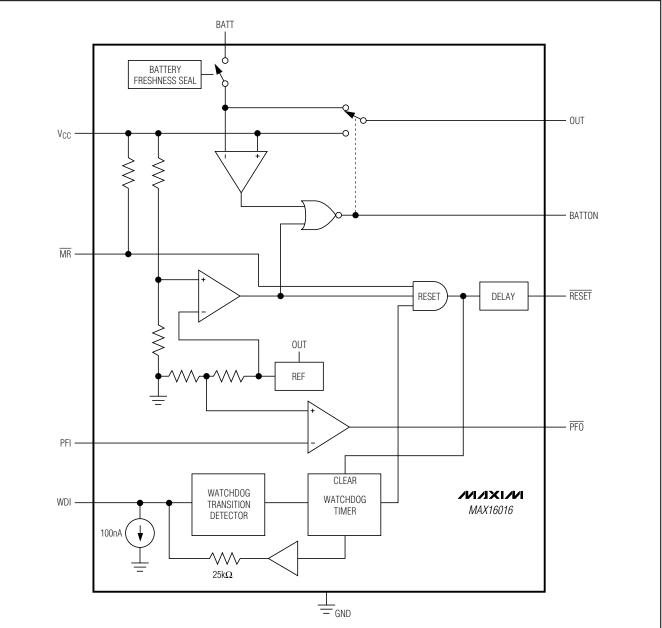

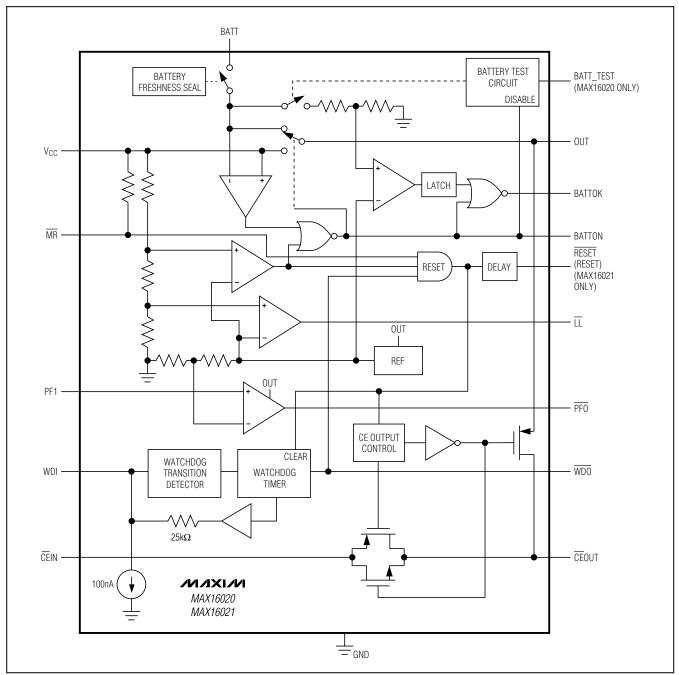

**Functional Diagrams**

### **Detailed Description**

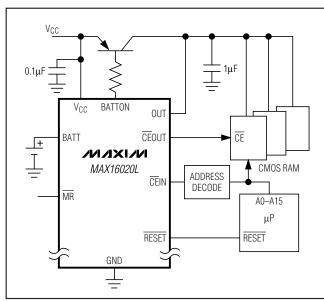

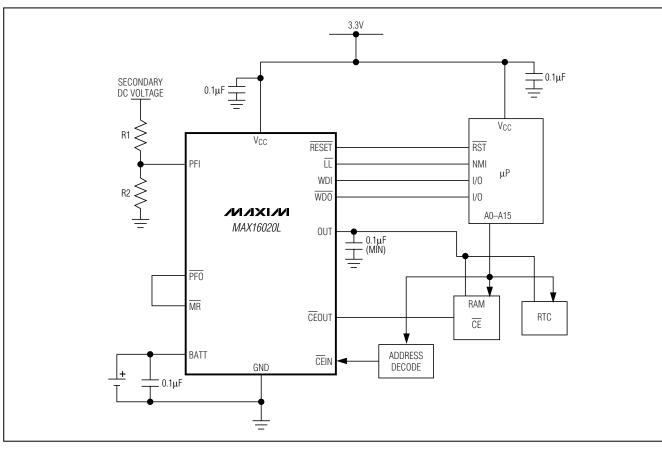

The *Typical Application Circuit* shows a typical connection using the MAX16020. OUT powers the static random-access memory (SRAM). If V<sub>CC</sub> is greater than the reset threshold (V<sub>TH</sub>), or if V<sub>CC</sub> is lower than V<sub>TH</sub>, but higher than V<sub>BATT</sub>, V<sub>CC</sub> connects to OUT. If V<sub>CC</sub> is lower than V<sub>TH</sub> and V<sub>CC</sub> is less than V<sub>BATT</sub>, BATT connects to OUT (see the *Functional Diagrams*). In battery-backup mode, an internal MOSFET connects the backup battery to OUT. The on-resistance of the MOSFET is a function of backup-battery voltage and temperature.

#### **Backup-Battery Switchover**

In a brownout or power failure, it may be necessary to preserve the contents of the RAM. With a backup battery installed at BATT, the MAX16016/MAX16020/MAX16021 automatically switch the RAM to the backup power when  $V_{CC}$  falls. The MAX16016/MAX16020/MAX16021 have a BATTON output that goes high when in battery-backup mode. These devices require two conditions before switching to battery-backup mode:

- 1)  $V_{CC}$  must be below the reset threshold.

- 2) VCC must be below VBATT.

Table 3 lists the status of the inputs and outputs in battery-backup mode. The device does not power up if the only voltage source is on BATT. OUT only powers up from  $V_{CC}$  at startup.

#### **CE Signal Gating**

The MAX16020/MAX16021 provide internal gating of CE signals to prevent erroneous data from being written to CMOS RAM in the event of a power failure or

# Table 3. Input and Output Status inBattery-Backup Mode

| PIN             | STATUS                                                                                                                                                         |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V <sub>CC</sub> | Disconnected from OUT                                                                                                                                          |  |  |  |

| OUT             | Connected to BATT                                                                                                                                              |  |  |  |

| BATT            | Connected to OUT. Current drawn from the battery is less than 0.55 $\mu$ A (at V <sub>BATT</sub> = 3V, excluding I <sub>OUT</sub> ) when V <sub>CC</sub> = 0V. |  |  |  |

| RESET/RESET     | Asserted                                                                                                                                                       |  |  |  |

| BATTON, WDO     | High state (push-pull), high impedance<br>(open-drain)                                                                                                         |  |  |  |

| BATTOK, LL      | Low state                                                                                                                                                      |  |  |  |

| CEIN            | Disconnected from CEOUT                                                                                                                                        |  |  |  |

| CEOUT           | Pulled up to V <sub>OUT</sub>                                                                                                                                  |  |  |  |

| PFO             | Not affected                                                                                                                                                   |  |  |  |

brownout. During normal operation, the CE gate is enabled and passes all CE transitions. When the reset output asserts, this path becomes disabled, preventing erroneous data from corrupting the CMOS RAM. CEOUT is pulled up to OUT through an internal current source. The 1.5ns propagation delay from CEIN to CEOUT allows the devices to be used with most  $\mu$ Ps and high-speed DSPs.

During normal operation (reset not asserted),  $\overline{CEIN}$  is connected to  $\overline{CEOUT}$  through a low on-resistance transmission gate. If  $\overline{CEIN}$  is high when a reset asserts,  $\overline{CEOUT}$  remains high regardless of any subsequent transition on  $\overline{CEIN}$  during the reset event.

If  $\overline{CEIN}$  is low when reset asserts,  $\overline{CEOUT}$  is held low for 12µs to allow completion of the read/write operation. After the 12µs delay expires,  $\overline{CEOUT}$  goes high and stays high regardless of any subsequent transitions on  $\overline{CEIN}$  during the reset event. When  $\overline{CEOUT}$  is disconnected from  $\overline{CEIN}$ ,  $\overline{CEOUT}$  is actively pulled up to OUT.

The propagation delay through the CE circuitry depends on both the source impedance of the drive to CEIN and the capacitive loading at CEOUT. Minimize the capacitive load at CEOUT to minimize the propagation delay, and use a low output-impedance driver.

#### Low-Line Output (LL)

The low-line comparator monitors V<sub>CC</sub> with a threshold voltage typically 2.5% higher than the reset threshold (see Table 2).  $\overline{LL}$  asserts prior to a reset condition during a brownout condition. On power-up,  $\overline{LL}$  deasserts after the reset output.  $\overline{LL}$  can be used to provide a nonmaskable interrupt (NMI) to the  $\mu$ P when the voltage begins to fall to initiate an orderly software shutdown routine.

#### **Manual Reset Input**

Many  $\mu$ P-based products require manual reset capability, allowing the operator, a test technician, or external logic circuitry to initiate a reset. For the MAX16016/MAX16020/ MAX16021, a logic-low on MR asserts RESET/RESET. RESET/RESET remains asserted while MR is low. When MR goes high RESET/RESET deasserts after a minimum of 145ms (tRP). MR has an internal 30k $\Omega$  pullup resistor to VCC. MR can be driven with TTL/CMOS logic levels or with open-drain/collector outputs. Connect a normally open momentary switch from MR to GND to create a manual reset function; external debounce circuitry is not required. If MR is driven from a long cable or the device is used in a noisy environment, connect a 0.1 $\mu$ F capacitor from MR to GND to provide additional noise immunity.

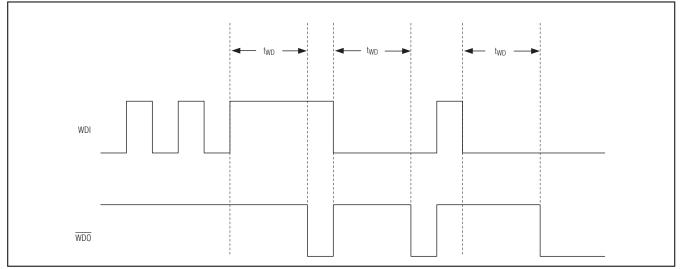

#### Watchdog Timer Watchdog Input

The watchdog monitors µP activity through the input WDI. If the µP becomes inactive, either the reset output is asserted in pulses (MAX16016) or the watchdog output goes low (MAX16020/MAX16021). To use the watchdog function, connect WDI to a bus line or µP I/O line. If WDI remains high or low for longer than the watchdog timeout period, the internal watchdog timer runs out and RESET asserts for the reset timeout period (MAX16016) or WDO goes low (MAX16020/MAX16021). The internal watchdog timer clears whenever the reset output asserts or the WDI sees a rising or falling edge within the watchdog timeout period. The WDI input is designed for a threestated output device with a 10µA maximum leakage current and the capability of driving a maximum capacitive load of 200pF. The three-state device must be able to source and sink at least 200µA when active. Disable the watchdog timer by leaving WDI unconnected or by three-stating the driver connected to WDI. The watchdog timer periodically attempts to pulse WDI to the opposite logic-level through a  $25k\Omega$  resistor for 40µs to determine whether WDI is either unconnected or latched to a logic state. The watchdog function is also disabled when in battery-backup mode.

#### Watchdog Output

WDO remains high if there is a transition or pulse at WDI during the watchdog-timeout period. WDO goes low if no transition occurs at WDI during the watchdog timeout period and remains low until the next transition at WDI or when a reset is asserted. Connect WDO to MR to generate a system reset on every watchdog fault. When a

watchdog fault occurs in this mode,  $\overline{\text{WDO}}$  goes low, which pulls  $\overline{\text{MR}}$  low, causing a reset pulse to be issued. As soon as the reset output is asserted, the watchdog timer clears and  $\overline{\text{WDO}}$  returns high. With  $\overline{\text{WDO}}$  connected to  $\overline{\text{MR}}$ , a continuous high or low on WDI causes 145ms (min) reset pulses to be issued every 1.235s.

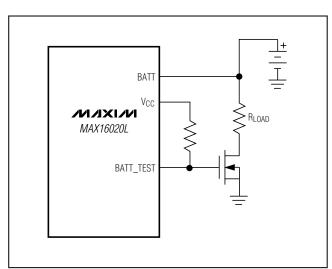

#### Battery Testing Function/BATTOK Indicator (MAX16020/MAX16021)

The MAX16020/MAX16021 feature a battery testing function that works in conjunction with the BATTOK output. The battery voltage is tested for 1.235s after V<sub>CC</sub> is applied and once every 24 hours thereafter. During this test, an internal 100k $\Omega$  resistor is connected from BATT to ground and the battery is monitored to ensure that the battery voltage is above 2.6V. If the battery voltage is below 2.6V, the BATTOK output deasserts low to indicate a weak battery condition. The MAX16020 has a BATT\_TEST output that pulses high during the battery voltage test. Connect a resistor and FET as shown in Figure 6 to provide an additional load during the battery test. In battery-backup mode, the battery testing function is disabled and BATTOK goes low.

#### **Battery Freshness Seal Mode**

The MAX16016/MAX16020/MAX16021 battery freshness seal disconnects the backup battery from internal circuitry and OUT until V<sub>CC</sub> is applied. This ensures the backup battery connected to BATT is fresh when the final product is used for the first time.

The internal freshness seal latch prevents BATT from powering OUT until  $V_{CC}$  has come up for the first time, setting the latch. When  $V_{CC}$  subsequently turns off, BATT begins to power OUT.

Figure 1. Watchdog Timing (MAX16016/MAX16020)

To reenable the freshness seal:

1) Connect a battery to BATT.

2) Bring V<sub>CC</sub> to 0V.

3) Drive MR higher than V<sub>BATT</sub> + 1.2V for at least 3µs.

4) Pull OUT to 0V.

#### **Reset Output**

A  $\mu$ P's reset input starts the  $\mu$ P in a known state. The  $\mu$ P supervisory circuits assert a reset to prevent codeexecution errors during power-up, power-down, and brownout conditions. Reset output is guaranteed to be a logic-low or logic-high depending on the device chosen. RESET or RESET asserts when V<sub>CC</sub> is below the reset threshold and remains asserted for at least 145ms (t<sub>RP</sub>) after V<sub>CC</sub> rises above the reset threshold. RESET or RESET also asserts when MR is low. The MAX16016 watchdog function causes RESET to assert in pulses following a watchdog timeout. The reset output is available in both push-pull and open-drain configurations.

#### **Power-Fail Comparator**

The MAX16016/MAX16020/MAX16021 offer an undervoltage comparator that the output  $\overline{PFO}$  goes low when the voltage at PFI falls below its V<sub>PFT</sub> threshold.

Common uses for the power-fail comparator include monitoring the power supply (such as a battery) before any voltage regulation to provide an early power-fail warning, so software can conduct an orderly system shutdown. The power-fail comparator has a typical input hysteresis of VPFT-HYS and is powered from OUT, making it independent of the reset circuit. Connect the PFI input to GND if not used.

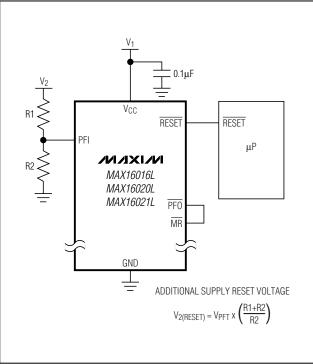

### **Applications Information**

#### Monitoring an Additional Supply

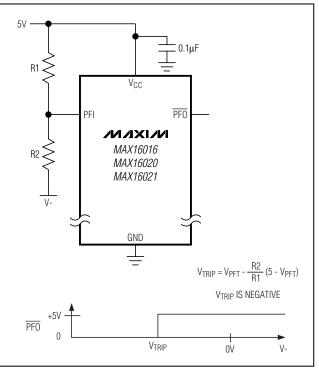

The MAX16016/MAX16020/MAX16021  $\mu$ P supervisors can monitor either positive or negative supplies using a resistive voltage-divider to PFI. PFO can be used to generate an interrupt to the  $\mu$ P or to trigger a reset (Figures 2 and 3). To monitor a negative supply, connect the top of the resistive divider to V<sub>CC</sub>. Connect the bottom of the resistive divider to the negative voltage to be monitored.

Figure 2. Monitoring an Additional Supply by Connecting  $\overrightarrow{\text{PFO}}$  to  $\overrightarrow{\text{MR}}$

Figure 3. Monitoring a Negative Supply

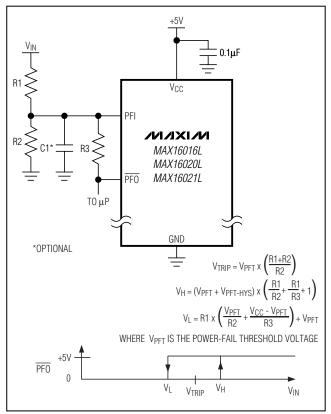

#### **Adding Hysteresis to PFI**

The power-fail comparators have a typical input hysteresis of VPFT-HYS. This is sufficient for most applications where a power-supply line is being monitored through an external voltage-divider (see the *Monitoring an Additional Supply* section). Figure 4 shows how to add hysteresis to the power-fail comparator. Select the ratio of R1 and R2 so that PFI sees VPFT when VIN falls to the desired trip point (VTRIP). Resistor R3 adds hysteresis. R3 is typically an order of magnitude greater than R1 or R2. R3 should be larger than 50k $\Omega$  to prevent it from loading down PFO. Capacitor C1 adds additional noise rejection.

### **Battery-On Indicator (Push-Pull Version)**

BATTON goes high when in battery-backup mode. Use BATTON to indicate battery-switchover status or to supply base drive to an external pass transistor for higher current applications (Figure 5).

#### **Operation Without a Backup Power Source**

The MAX16016/MAX16020/MAX16021 provide a battery-backup function. If a backup power source is not used, connect BATT to GND and OUT to  $V_{CC}.$

Figure 4. Adding Hysteresis to the Power-Fail Comparator

Figure 5. BATTON Driving an External Pass Transistor

Figure 6. Adjustable BATT\_TEST Load

#### **Replacing the Backup Battery**

When  $V_{CC}$  is above  $V_{TH}$ , the backup power source can be removed without danger of triggering a reset pulse. The device does not enter battery-backup mode when  $V_{CC}$  stays above the reset threshold voltage.

#### **Negative-Going Vcc Transients**

The MAX16016/MAX16020/MAX16021 are relatively immune to short duration, negative going V<sub>CC</sub> transients. Resetting the  $\mu$ P when V<sub>CC</sub> experiences only small glitches is usually not desirable. A 0.1 $\mu$ F bypass capacitor mounted close to V<sub>CC</sub> provides additional transient immunity.

## Pin Configurations (continued)

## **Typical Application Circuit**

MAX16016/MAX16020/MAX16021

### **Selector Guide**

| PART         | ALL LOGIC<br>OUTPUTS (EXCEPT<br>BATT_TEST) | MR           | POWER-FAIL<br>COMPARATOR | WATCHDOG<br>TIMER | BATTON       | LOW-<br>LINE<br>OUTPUT | BATTOK/<br>BATT_TEST/<br>RESET | CHIP-<br>ENABLE |

|--------------|--------------------------------------------|--------------|--------------------------|-------------------|--------------|------------------------|--------------------------------|-----------------|

| MAX16016LTB_ | Push-pull                                  | $\checkmark$ | $\checkmark$             | WDI               | $\checkmark$ | _                      | —                              |                 |

| MAX16016PTB_ | Open-drain                                 | $\checkmark$ | $\checkmark$             | WDI               | $\checkmark$ |                        |                                |                 |

| MAX16020LTE_ | Push-pull                                  | $\checkmark$ | $\checkmark$             | WDI/WDO           | $\checkmark$ | $\checkmark$           | BATTOK/<br>BATT_TEST           | $\checkmark$    |

| MAX16020PTE_ | Open-drain                                 | $\checkmark$ | $\checkmark$             | WDI/WDO           | $\checkmark$ | $\checkmark$           | BATTOK/<br>BATT_TEST           | $\checkmark$    |

| MAX16021LTE_ | Push-pull                                  | $\checkmark$ | $\checkmark$             | WDI/WDO           | $\checkmark$ | $\checkmark$           | BATTOK/<br>RESET               | $\checkmark$    |

| MAX16021PTE_ | Open-drain                                 | $\checkmark$ | $\checkmark$             | WDI/WDO           | $\checkmark$ |                        | BATTOK/<br>RESET               |                 |

### \_Ordering Information (continued)

| PART           | TEMP RANGE     | PIN-PACKAGE |  |  |

|----------------|----------------|-------------|--|--|

| MAX16020_TE_+T | -40°C to +85°C | 16 TQFN-EP* |  |  |

| MAX16021_TE_+T | -40°C to +85°C | 16 TQFN-EP* |  |  |

The first placeholder "\_" designates all output options. Letter "L" indicates push-pull outputs and letter "P" indicates opendrain outputs. The last placeholder "\_" designates the reset threshold (see Table 1).

T = Tape and reel.

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad. **Chip Information**

PROCESS: BiCMOS

### **Package Information**

For the latest package outline information and land patterns (footprints), go to **www.maxim-ic.com/packages**. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO. | LAND<br>PATTERN NO. |  |

|-----------------|-----------------|----------------|---------------------|--|

| 10 TDFN-EP      | T1033+1         | <u>21-0137</u> | <u>90-0093</u>      |  |

| 16 TQFN-EP      | T1644+4         | <u>21-0139</u> | <u>90-0070</u>      |  |

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                 | PAGES<br>CHANGED                             |

|--------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 0                  | 5/08             | Initial release                                                                                                                             | —                                            |

| 1                  | 7/08             | Released the MAX16016. Updated Ordering Information, Electrical Characteristics, Tables 1 and 2, Pin Description, and Detailed Description. | 1, 3, 4, 5, 9, 10, 12,<br>13, 15, 16, 19, 20 |

| 2                  | 10/08            | Released the MAX16021.                                                                                                                      | 20                                           |

| 3                  | 12/08            | Updated <i>Electrical Characteristics</i> , <i>Pin Description</i> , Table 3, and the <i>Power-Fail Comparator</i> section.                 | 3, 9, 10, 11, 14, 16                         |

| 4                  | 1/10             | Updated Electrical Characteristics.                                                                                                         | 4                                            |

| 5                  | 4/11             | Updated Pin Description.                                                                                                                    | 9, 10                                        |

| 6                  | 11/11            | Updated Pin Description.                                                                                                                    | 9, 10                                        |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_\_\_

Maxim is a registered trademark of Maxim Integrated Products, Inc.

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated: MAX16016LTBL+T MAX16016LTBM+T MAX16016LTBR+T MAX16016LTBS+T MAX16016LTBT+T MAX16016LTBV+T MAX16016LTBW+T MAX16016LTBY+T MAX16016LTBZ+T MAX16016PTBL+T MAX16016PTBM+T MAX16016PTBR+T MAX16016PTBS+T MAX16016PTBT+T MAX16016PTBV+T MAX16016PTBW+T MAX16016PTBY+T MAX16016PTBZ+T MAX16020LTEL+T MAX16020LTEM+T MAX16020LTES+T MAX16020LTET+T MAX16020LTEV+T MAX16020LTEW+T MAX16020LTEY+T MAX16020LTEZ+T MAX16020PTEL+T MAX16020PTEM+T MAX16020PTER+T MAX16020PTES+T MAX16020PTET+T MAX16020PTEV+T MAX16020PTEW+T MAX16020PTEY+T MAX16020PTEZ+T MAX16021LTEL+ MAX16021LTEL+T MAX16021LTEM+ MAX16021LTEM+T MAX16021LTER+ MAX16021LTER+T MAX16021LTES+ MAX16021LTET+ MAX16021LTET+T MAX16021LTEV+ MAX16021LTEV+T MAX16021LTEW+ MAX16021LTEW+T MAX16021LTEY+ MAX16021LTEY+T MAX16021LTEZ+ MAX16021LTEZ+T MAX16021PTEL+ MAX16021PTEL+T MAX16021PTEM+ MAX16021PTEM+T MAX16021PTER+ MAX16021PTER+T MAX16021PTES+ MAX16021PTES+T MAX16021PTET+ MAX16021PTET+T MAX16021PTEV+ MAX16021PTEV+T MAX16021PTEW+T MAX16021PTEY+ MAX16021PTEY+T MAX16021PTEZ+ MAX16021PTEZ+T MAX16021PTEW+ MAX16020LTET+ MAX16020LTES+ MAX16020LTES MAX16020PTET+ MAX16020LTER+T