# Zero Drift, High Voltage, Low Power, Programmable Gain Instrumentation Amplifier

### **Data Sheet**

# ADA4254

### FEATURES

**Optimized for ADC synchronization** Low power: 22 mW (±12 V supplies) 12 binary gain steps from 1/16 V/V to 128 V/V 3 scaling gains: 1 V/V, 1.25 V/V, and 1.375 V/V ±60 V protected input multiplexer **Excellent dc precision** Low input offset voltage: ±14 µV maximum Low input offset voltage drift: ±0.08 µV/°C maximum **Gain calibration via ROM** Low gain drift: ±1 ppm/°C maximum High CMRR: 116 dB minimum, G = 1 V/V Low input bias current: ±1.5 nA maximum **High input impedance** Integrated input EMI filtering Wide input supply range: ±5 V to ±28 V **Dedicated output amplifier supplies** 7 GPIO ports with special functions Sequential chip select mode **External multiplexer control Excitation current sources** SPI port with checksum (CRC) support **Internal fault detection** Wire break test currents **On-chip test multiplexer** 28-lead, 5 mm × 5 mm LFCSP, 24-lead TSSOP Specified temperature range: -40°C to +105°C APPLICATIONS Universal process control front ends **Data acquisition systems**

Test and measurement systems

#### **GENERAL DESCRIPTION**

The ADA4254 is a zero drift, high voltage, low power programmable gain instrumentation amplifier (PGIA) designed for process control and industrial applications. The ADA4254 features 12 binary weighted gains ranging from 1/16 V/V to 128 V/V and three scaling gain options of 1 V/V, 1.25 V/V, and 1.375 V/V, resulting in 36 possible gain settings. The power consumption of the ADA4254 is a mere 22 mW, making the device an excellent choice for industrial systems that demand precision, robustness, and low power.

The zero drift amplifier topology of the ADA4254 self calibrates dc errors and low frequency 1/f noise, achieving excellent dc precision over the entire specified temperature range. This high level of precision maximizes dynamic range and greatly reduces calibration requirements in many applications.

#### Rev. B

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

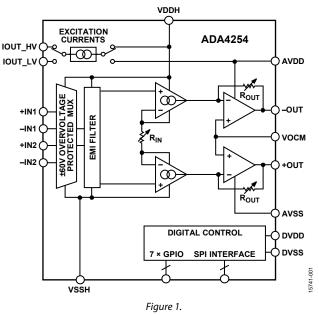

#### SIMPLIFIED FUNCTIONAL BLOCK DIAGRAM

The input multiplexer provides  $\pm 60$  V protection to the high impedance inputs of the amplifier, while providing the capability to switch between two input sources. In addition, integrated electromagnetic interference (EMI) filters block harsh RF noise from the sensitive inputs of the amplifier.

Various safety features on the ADA4254 detect both internal and external faults. The serial port interface (SPI) supports cyclical redundancy check (CRC) error detection to ensure robust communication. These safety features ease system safety integrity level (SIL) certification.

Seven general-purpose input/output (GPIO) pins, which can be configured to provide various special functions, are included in the ADA4254. An excitation current source output is available to bias sensors such as resistance temperature detectors (RTDs).

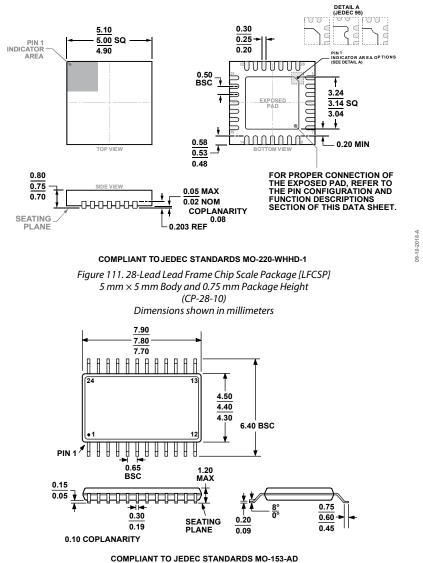

The ADA4254 is specified over the  $-40^{\circ}$ C to  $+105^{\circ}$ C temperature range and is offered in a compact 5 mm × 5 mm, 28-lead LFCSP and a 24-lead TSSOP.

### **COMPANION PRODUCTS**

ADCs: AD4007, AD7768, AD7175-2 ADC Drivers: ADA4945-1, LTC6363 Voltage References: ADR4550, ADR3450, LT6656

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2019–2020 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# TABLE OF CONTENTS

| Features                                       |

|------------------------------------------------|

| Applications 1                                 |

| General Description                            |

| Simplified Functional Block Diagram 1          |

| Companion Products1                            |

| Revision History                               |

| Specifications                                 |

| Timing Specifications                          |

| Absolute Maximum Ratings 9                     |

| Thermal Resistance9                            |

| ESD Caution                                    |

| Pin Configurations and Function Descriptions10 |

| Typical Performance Characteristics11          |

| Theory of Operation                            |

| Programmable Gain Instrumentation Amplifier    |

| Input Multiplexer                              |

| EMI Reduction and Internal EMI Filter          |

| Input Amplifier25                              |

| Output Amplifier25                             |

| Power Supplies                                 |

| ESD Map26                                      |

| Output Ripple Calibration Configuration        |

| General-Purpose Inputs/Outputs (GPIOs)         |

| Excitation Currents                            |

| External Clock Synchronization                 |

| Sequential Chip Select (SCS)                   |

| Gain Error Calibration                         |

| Wire Break Detection                           |

| Test Multiplexer                               |

| External Mux Control                           |

| Digital Interface                              |

| SPI Interface                                  |

| Accessing the ADA4254 Register Map             |

| Checksum Protection                            |

| CRC Calculation                                |

| Memory Map Checksum Protection                 |

| Read-Only Memory (ROM) Checksum Protection     |

| SPI Read/Write Error Detection                                     | . 35 |

|--------------------------------------------------------------------|------|

| SPI Command Length Error Detection                                 | . 35 |

| Applications Information                                           | . 36 |

| Input and Output Offset Voltage and Noise                          | . 36 |

| ADC Clock Synchronization                                          | . 36 |

| Programmable Logic Controller (PLC) Voltage/Current                |      |

| Input                                                              |      |

| 3-Wire RTD With Current Excitation                                 |      |

| High Rail Current Sensing                                          | . 39 |

| Register Summary                                                   |      |

| Register Details                                                   |      |

| GAIN_MUX Register Details                                          | . 42 |

| Software Reset Register (Reset) Details                            | . 43 |

| Clock Synchronization Configuration Register (SYNC_Cl Details      |      |

| Digital Error Register (DIGITAL_ERR) Details                       | . 45 |

| Analog Error Register (ANALOG_ERR) Details                         | . 46 |

| GPIO Data Register (GPIO_DATA) Details                             | . 47 |

| Internal Mux Control Register (INPUT_MUX) Details                  | . 48 |

| Wire Break Detect Register (WB_DETECT) Details                     | . 49 |

| GPIO Direction Register (GPIO_DIR) Details                         | . 50 |

| Sequential Chip Select Register (SCS) Details                      | . 50 |

| Analog Error Mask Register (ANALOG_ERR_DIS) Details                | . 51 |

| Digital Error Mask Register (DIGITAL_ERR_DIS) Details              | . 52 |

| Special Function Configuration Register (SF_CFG) Details           | . 53 |

| Error Configuration Register                                       | . 54 |

| Test Multiplexer Register (TEST_MUX) Details                       | . 55 |

| Excitation Current Configuration Register (EX_CURRENT_CFG) Details | . 56 |

| Gain Calibration Registers (GAIN_CALx) Details                     |      |

| Trigger Calibration Register (TRIG_CAL) Details                    | . 58 |

| Master Clock Count Register (M_CLK_CNT) Details                    | . 58 |

| DIE Revision Identification Register (DIE_REV_ID) Deta             |      |

| Device Identification Registers (PART_ID) Details                  |      |

| Outline Dimensions                                                 |      |

| Ordering Guide                                                     | . 59 |

|                                                                    |      |

### **REVISION HISTORY**

| 6/2020—Rev. A to Rev. B                              |    |

|------------------------------------------------------|----|

| Changes to Figure 10                                 | 11 |

| Changes to Figure 23                                 | 13 |

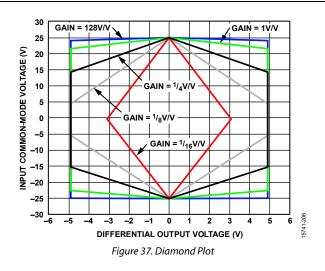

| Changes to Figure 37                                 | 16 |

| Change to Input Multiplexer Section                  | 24 |

| Changes to External Clock Synchronization Section    |    |

| Change to Wire Break Detection Section               | 31 |

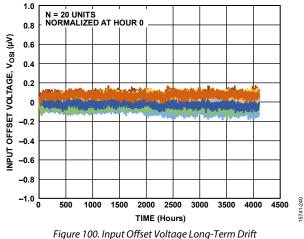

| Changes to Figure 100                                |    |

| Change to 3-Wire RTD with Current Excitation Section |    |

| Change to Table 21                                   | 49 |

| Change to Bits[7:0], DIE_REV_ID[7:0]—Die Revision    |    |

| Identification Number Section                        | 58 |

|                                                      |    |

#### 11/2019-Rev. 0 to Rev. A

Changes to Features Section and General Description Section ......1 Changes to Static Power Dissipation Parameter, Table 1 ..........7 Changes to 3-Wire RTD With Current Excitation Section .......38

11/2019—Revision 0: Initial Version

# **SPECIFICATIONS**

$T_A = 25^{\circ}C$ , VDDH = 28 V, VSSH = -28 V, AVDD = 5 V, AVSS = 0 V, DVDD = 3.3 V, DVSS = 0 V, VOCM = AVDD/2, and no load, unless otherwise noted.

### Table 1.

| Parameter                                                                                         | Test Conditions/Comments                                        | Min | Тур    | Max   | Unit   |

|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----|--------|-------|--------|

| OFFSET VOLTAGE                                                                                    | Total offset, referred to input (RTI) =                         |     |        |       |        |

|                                                                                                   | $V_{OSI} + \frac{V_{OSO}}{Gain}$                                |     |        |       |        |

| Differential Offset Voltage                                                                       |                                                                 |     |        |       |        |

| Input Offset Voltage (Vosi)                                                                       |                                                                 |     | ±3     | ±14   | μV     |

| Output Offset Voltage (Voso)                                                                      |                                                                 |     | ±40    | ±125  | μV     |

| Differential Offset Voltage                                                                       | $T_A = -40^{\circ}C$ to $+105^{\circ}C^1$ , total offset drift, |     |        |       |        |

| Drift                                                                                             | $RTI = V_{OSI}/T + \frac{V_{OSO}/T}{Gain}$                      |     |        |       |        |

| V <sub>osl</sub> /T                                                                               |                                                                 |     | ±0.03  | ±0.08 | µV/°C  |

| Voso/T                                                                                            |                                                                 |     | ±0.98  | ±2.5  | μV/°C  |

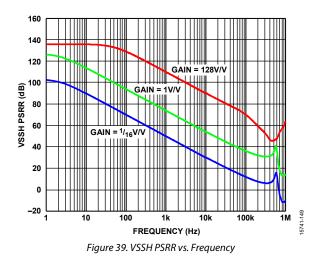

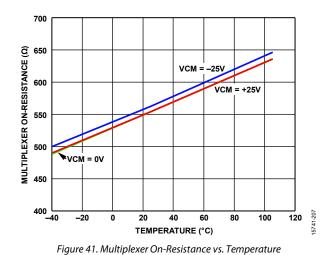

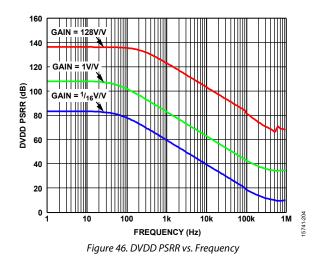

| Differential Offset Voltage vs.<br>VDDH and VSSH (Power<br>Supply Rejection Ratio<br>(PSRR)), RTI | VDDH – VSSH = 10 V to 56 V                                      |     |        |       |        |

| Gain (G) = 1/16 V/V                                                                               |                                                                 | 80  | 90     |       | dB     |

| G = 1 V/V                                                                                         |                                                                 | 110 | 120    |       | dB     |

| G = 128 V/V                                                                                       |                                                                 | 140 | 154    |       | dB     |

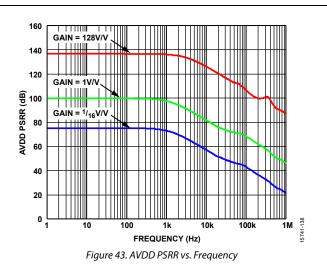

| Differential Offset Voltage vs.<br>AVDD (PSRR), RTI                                               | AVDD – AVSS = 2.7 V to 5.5 V                                    |     |        |       |        |

| G = 1/16 V/V                                                                                      |                                                                 | 66  | 76     |       | dB     |

| G = 1 V/V                                                                                         |                                                                 | 90  | 100    |       | dB     |

| G = 128 V/V                                                                                       |                                                                 | 118 | 136    |       | dB     |

| Differential Offset vs. External<br>Clock Frequency, RTI                                          | Clock frequency = 0.8 MHz to 1.2 MHz                            |     |        |       |        |

| G = 1/16 V/V                                                                                      |                                                                 |     | ±0.2   |       | μV/kHz |

| G = 1 V/V                                                                                         |                                                                 |     | ±0.1   |       | μV/kHz |

| G = 128 V/V                                                                                       |                                                                 |     | ±0.002 |       | μV/kHz |

| COMMON–MODE REJECTION<br>RATIO (CMRR), RTI                                                        | +IN = -IN = -25 V to $+25 V$ , scaling gain $= 1 V/V$           |     |        |       |        |

| CMRR to 60 Hz                                                                                     |                                                                 |     |        |       |        |

| G = 1/16 V/V                                                                                      |                                                                 | 92  | 102    |       | dB     |

| G = 1 V/V                                                                                         |                                                                 | 116 | 126    |       | dB     |

| G = 128 V/V                                                                                       |                                                                 | 140 | 150    |       | dB     |

| G = 1/16                                                                                          | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C^1$                | 88  |        |       | dB     |

| G = 1                                                                                             | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C^1$                | 112 |        |       | dB     |

| G = 128                                                                                           | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C^1$                | 136 |        |       | dB     |

| Parameter                                     | Test Conditions/Comments                                                  | Min      | Тур            | Max        | Unit       |

|-----------------------------------------------|---------------------------------------------------------------------------|----------|----------------|------------|------------|

| GAIN                                          | Output voltage ( $V_{OUT}$ ) = 8.5 V p-p <sup>2</sup>                     |          |                |            |            |

| Input Gain Range                              |                                                                           |          | 1/16 to 128    |            | V/V        |

| Output Gain Range                             |                                                                           |          | 1, 1.25, 1.375 |            | V/V        |

| Gain Error                                    |                                                                           |          | ,,             |            |            |

| Before Calibration                            | All Gains                                                                 |          | <±0.06         | ±0.12      | %          |

| Using Calibration                             | All Gains                                                                 |          | <±0.00         | ±0.025     | %          |

| Coefficient                                   |                                                                           |          | 120.01         | ±0.025     | /0         |

| All Gain Values Except as<br>Follows:         | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C^1$                          |          | <±0.3          | ±1         | ppm/°C     |

| G = 1/16 V/V, All Scaling<br>Gains            | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C^1$                          |          | ±0.8           | ±1.5       | ppm/°C     |

| G = 32 V/V, 64 V/V, All<br>Scaling Gains      | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C^1$                          |          | ±0.4           | ±1.5       | ppm/°C     |

| G = 128 V/V, Scaling Gains<br>1 V/V, 1.25 V/V | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C^1$                          |          | ±0.6           | ±2         | ppm/°C     |

| G = 128 V/V, Scaling Gain<br>1.375 V/V        | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C^1$                          |          | ±0.7           | ±2.5       | ppm/°C     |

| Nonlinearity                                  | All gains except 32 V/V, 64 V/V and 128 V/V <sup>2, 3</sup>               |          | 5              | 15         | ppm        |

|                                               | G = 32 V/V                                                                |          | 7.5            |            | ppm        |

|                                               | G = 64 V/V                                                                |          | 12             |            | ppm        |

|                                               | G = 128 V/V                                                               |          | 15             |            | ppm        |

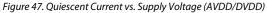

| NOISE                                         | Total noise, RTI = $\sqrt{e_{ni}^2 + \left(\frac{e_{no}}{Gain}\right)^2}$ |          |                |            |            |

| Voltage Noise, 1 kHz, RTI                     |                                                                           |          |                |            |            |

| Input Noise (e <sub>ni</sub> )                |                                                                           |          | 17             |            | nV/√Hz     |

| Output Noise (eno)                            |                                                                           |          | 253            |            | nV/√Hz     |

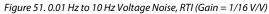

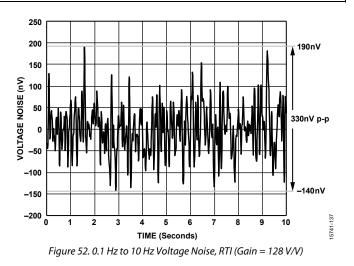

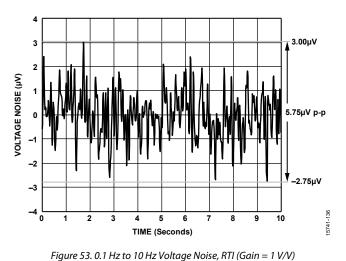

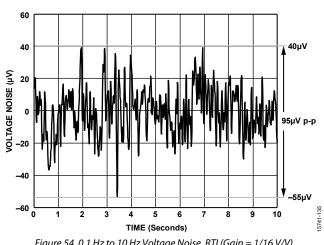

| 0.1 Hz to 10 Hz, RTI                          |                                                                           |          |                |            |            |

| G = 1/16 V/V                                  |                                                                           |          | 95             |            | μV p-p     |

| G = 1 V/V                                     |                                                                           |          | 5.75           |            | μV p-p     |

| G = 128 V/V                                   |                                                                           |          | 330            |            | nV p-p     |

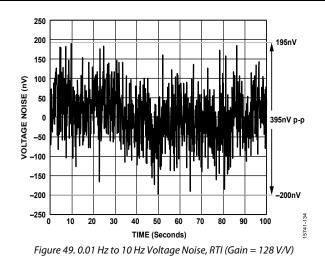

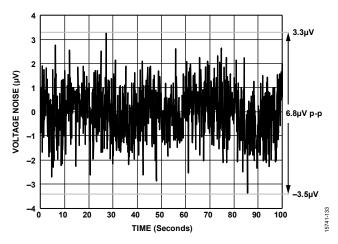

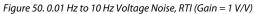

| 0.01 Hz to 10 Hz, RTI                         |                                                                           |          |                |            |            |

| G = 1/16 V/V                                  |                                                                           |          | 100            |            | μV p-p     |

| G = 1 V/V                                     |                                                                           |          | 6.8            |            | μV p-p     |

| G = 128 V/V                                   |                                                                           |          | 395            |            | nV p-p     |

| Current Noise                                 |                                                                           |          | 575            |            | III P P    |

| 10 Hz                                         |                                                                           |          | 100            |            | fA/√Hz     |

| 0.1 Hz to 10 Hz                               |                                                                           |          | 3.1            |            | pA p-p     |

| 0.01 Hz to 10 Hz                              |                                                                           |          | 4              |            | рАр-р      |

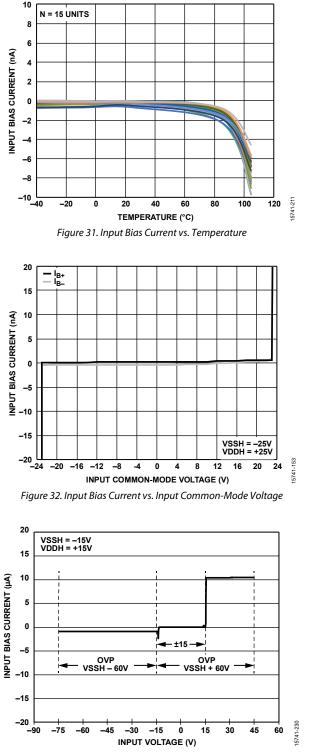

| INPUT CHARACTERISTICS                         |                                                                           |          | 7              |            | prop       |

| Input Bias Current                            |                                                                           |          | ±0.45          | ±1.5       | nA         |

| input bias current                            | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C^1$                           |          | ±0.45          | ±1.5<br>±4 | nA         |

|                                               |                                                                           |          |                |            |            |

| have to ffeet Comment                         | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C^1$                          |          |                | ±14        | nA         |

| Input Offset Current                          |                                                                           |          | ±0.2           | ±1.3       | nA         |

|                                               | $T_A = -40^{\circ}$ C to $+85^{\circ}$ C <sup>1</sup>                     |          |                | ±2.5       | nA<br>nA   |

|                                               | $T_{A} = -40^{\circ}C \text{ to } +105^{\circ}C^{1}$                      |          |                | ±3.5       | nA         |

| Input Impedance                               | Common mode                                                               |          | >1  11         |            | GΩ  pF     |

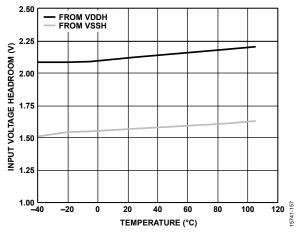

| Input Operating Voltage Range                 | Differential<br>Guaranteed by CMRR                                        | VSSH + 3 | >1  4.7        | VDDH – 3   | GΩ∥pF<br>V |

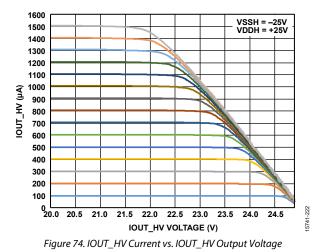

| MUX_OVER_VOLT_ERR                             |                                                                           |          |                |            |            |

| Positive Threshold                            |                                                                           |          | VDDH – 0.9     |            | V          |

| Negative Threshold                            |                                                                           |          | VSSH + 0.9     |            | V          |

| INPUT_ERR/GAIN_RST                            |                                                                           |          |                |            |            |

| Positive Threshold                            |                                                                           |          | VDDH – 1.5     |            | V          |

| Negative Threshold                            |                                                                           |          | VSSH + 1.5     |            | V          |

| Parameter                              | Test Conditions/Comments                                            | Min         | Тур         | Max            | Unit   |

|----------------------------------------|---------------------------------------------------------------------|-------------|-------------|----------------|--------|

| ANALOG OUTPUTS                         |                                                                     |             |             |                |        |

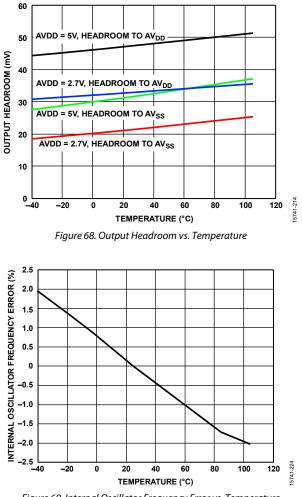

| Output Voltage Swing from<br>Each Rail | AVDD = 5 V, load resistor (R <sub>L</sub> ) = 2.49 k\Omega to 2.5 V | AVSS + 0.06 |             | AVDD –<br>0.08 | V      |

| EdCITRAII                              |                                                                     |             |             | 0.08<br>AVDD – | V      |

|                                        | AVDD = 2.7 V, $R_L$ = 1.8 k $\Omega$ to 1.35 V                      | AVSS + 0.05 |             | avdd -<br>0.06 | V      |

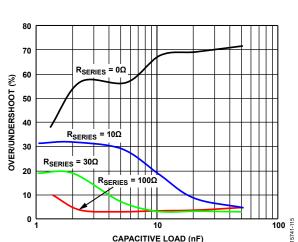

| Capacitive Load Drive                  |                                                                     |             | 500         | 0.00           | рF     |

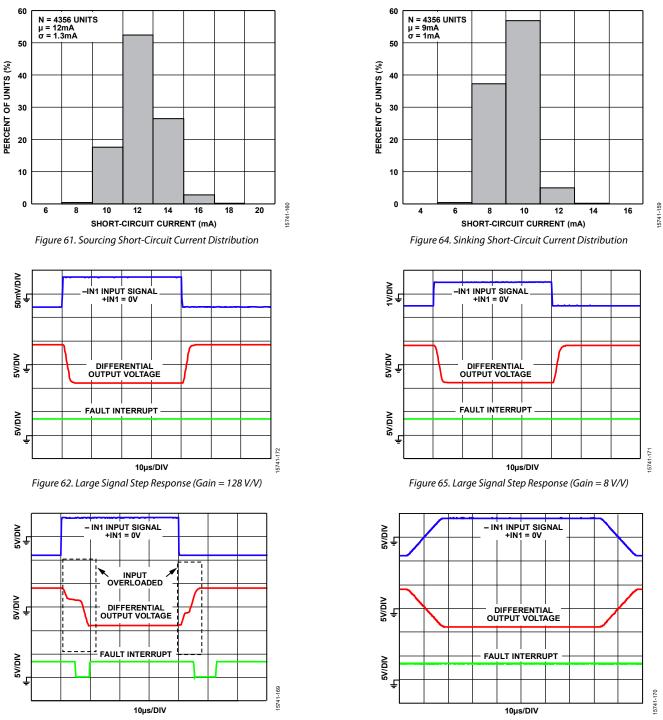

| Short-Circuit Current                  | To 2.5 V, G = 1.375, AVDD = 2.7 V to 5 V                            | 3.5         | 11          | 25             | mA     |

| OUTPUT_ERR                             |                                                                     |             |             |                |        |

| Positive Threshold                     |                                                                     |             | AVDD - 0.03 |                | v      |

| Negative Threshold                     |                                                                     |             | AVSS + 0.03 |                | v      |

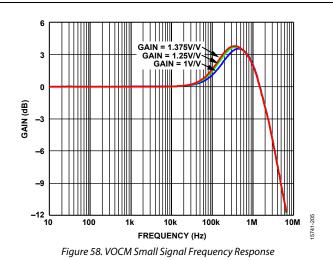

| VOCM DYNAMIC PERFORMANCE               |                                                                     |             |             |                |        |

| –3 dB Bandwidth                        |                                                                     |             | 2.3         |                | MHz    |

| Slew Rate                              |                                                                     |             | 1.9         |                | V/µs   |

| Voltage Noise                          | Frequency = 1 kHz                                                   |             | 160         |                | nV/√Hz |

| Gain                                   |                                                                     |             | 1           |                | V/V    |

| VOCM INPUT CHARACTERISTICS             |                                                                     |             |             |                |        |

| Input Voltage Range                    |                                                                     | AVSS        |             | AVDD – 1       | v      |

| Input Resistance                       |                                                                     |             | 10          |                | GΩ     |

| Common Mode Offset Voltage             |                                                                     |             | 20          |                | μV     |

| Common Mode Offset                     |                                                                     |             | 2.5         |                | μV/°C  |

| Voltage Drift                          |                                                                     |             | 2.0         |                | p., c  |

| Input Bias Current                     |                                                                     |             | 500         |                | рА     |

| DYNAMIC RESPONSE                       |                                                                     |             |             |                |        |

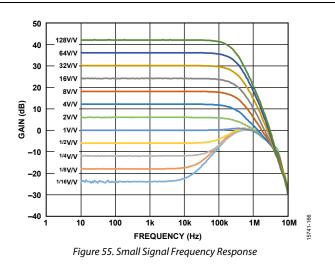

| Small Signal ±3 dB Bandwidth           |                                                                     |             |             |                |        |

| G = 1/16 V/V                           |                                                                     |             | 15          |                | kHz    |

| G = 1/8 V/V                            |                                                                     |             | 28          |                | kHz    |

| G = 1/4 V/V                            |                                                                     |             | 67          |                | kHz    |

| G = 1/2 V/V                            |                                                                     |             | 138         |                | kHz    |

| G = 1 V/V                              |                                                                     |             | 1800        |                | kHz    |

| G = 2 V/V                              |                                                                     |             | 513         |                | kHz    |

| G = 4 V/V                              |                                                                     |             | 341         |                | kHz    |

| G = 8 V/V                              |                                                                     |             | 319         |                | kHz    |

| G = 16 V/V                             |                                                                     |             | 297         |                | kHz    |

| G = 32 V/V                             |                                                                     |             | 275         |                | kHz    |

| G = 64 V/V                             |                                                                     |             | 257         |                | kHz    |

| G = 128 V/V                            |                                                                     |             | 209         |                | kHz    |

| Settling Time 0.01%                    | V <sub>OUT</sub> = 8 V p-p                                          |             |             |                |        |

| G = 1 V/V                              |                                                                     |             | 10          |                | μs     |

| G = 8 V/V                              |                                                                     |             | 8           |                | μs     |

| G = 128 V/V                            |                                                                     |             | 5           |                | μs     |

| Settling Time 0.0015% (16-Bit)         | V <sub>оит</sub> = 8 V р-р                                          |             |             |                |        |

| G = 1 V/V                              |                                                                     |             | 18          |                | μs     |

| G = 8 V/V                              |                                                                     |             | 15          |                | μs     |

| G = 128 V/V                            |                                                                     |             | 15          |                | μs     |

| Slew Rate                              | $V_{OUT} = 8 V p - p^2$                                             |             |             |                |        |

| G = 1/16 V/V                           |                                                                     |             | 0.06        |                | V/µs   |

| G = 1 V/V                              |                                                                     |             | 0.8         |                | V/µs   |

| G = 128 V/V                            |                                                                     |             | 3.1         |                | V/µs   |

| Parameter                                       | Test Conditions/Comments                         | Min        | Тур                   | Max  | Unit       |

|-------------------------------------------------|--------------------------------------------------|------------|-----------------------|------|------------|

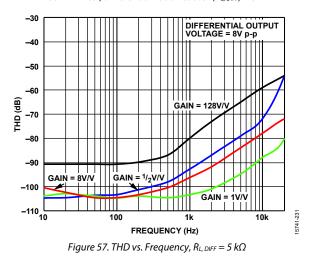

| THD                                             | Vout = 8 V p-p at frequency = 1 kHz              |            |                       |      | 1          |

| G = 1 V/V                                       |                                                  |            | -104                  |      | dB         |

| G = 8 V/V                                       |                                                  |            | -96                   |      | dB         |

| G = 128 V/V                                     |                                                  |            | -80                   |      | dB         |

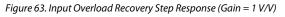

| Input Overload Recovery Time                    | Input voltage (V <sub>IN</sub> ) = 56 V p-p      |            | 40                    |      | μs         |

| Output Overload Recovery                        | $G = 1 V/V, V_{IN} = 10 V p-p$                   |            | 6                     |      | μs         |

| Time                                            |                                                  |            |                       |      | •          |

| EXCITATION CURRENT SOURCES<br>(IOUT_LV/IOUT_HV) |                                                  |            |                       |      |            |

| Output Current Range                            |                                                  | 100        |                       | 1500 | μΑ         |

| Initial Tolerance                               |                                                  |            | ±3                    | ±10  | %          |

| Drift                                           | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C$   |            | ±200                  |      | ppm/°      |

| Current Matching                                |                                                  |            | ±3                    | ±8   | %          |

| Drift Matching                                  | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C$   |            | ±50                   |      | ppm/°      |

| WIRE BREAK CURRENTS                             |                                                  |            |                       |      |            |

| Output Current Range                            |                                                  | 0.25       |                       | 16   | μA         |

| Impedance Threshold                             |                                                  |            | $(VDDH - 4)/I_{WB}^4$ |      | Ω          |

| Initial Tolerance                               |                                                  |            | ±12                   |      | %          |

| Drift                                           | $T_{A} = -40^{\circ}C \text{ to } +105^{\circ}C$ |            | ±250                  |      | ppm/°      |

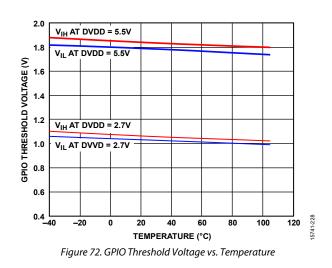

| DIGITAL INPUTS                                  |                                                  |            |                       |      | 1          |

| Low (V <sub>INL</sub> )                         |                                                  | 0          |                       | 0.8  | v          |

| High (V <sub>INH</sub> )                        |                                                  | 0.6 × DVDD |                       | DVDD | v          |

| Digital Input Pin Capacitance                   |                                                  |            | 5                     |      | pF         |

| DIGITAL OUTPUT                                  |                                                  |            | -                     |      | 1          |

| Low (V <sub>OL</sub> )                          | Sinking 4 mA                                     |            |                       | 0.7  | v          |

| High (V <sub>он</sub> )                         | Sourcing 2 mA                                    | DVDD - 0.8 |                       |      | v          |

| INTERNAL/EXTERNAL CLOCK                         |                                                  |            |                       |      |            |

| Internal Clock                                  |                                                  |            |                       |      |            |

| Frequency                                       |                                                  | 0.8        | 1                     | 1.2  | MHz        |

| Duty Cycle                                      |                                                  | 0.0        | 50                    | 1.2  | %          |

| Internal Clock Divider Range                    |                                                  | 1          | 50                    | 32   | /0<br>MHz/ |

| internal clock Divider hange                    |                                                  |            |                       | JZ   | MHz        |

| POWER SUPPLY                                    |                                                  |            |                       |      |            |

| VDDH – VSSH                                     |                                                  | 10         |                       | 56   | v          |

| AVDD – AVSS                                     |                                                  | 2.7        |                       | 5    | v          |

| DVDD – DVSS                                     |                                                  | 2.7        |                       | 5    | V          |

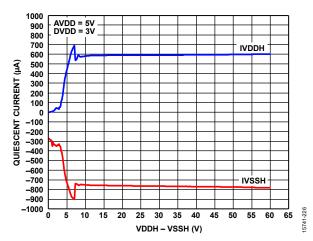

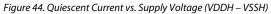

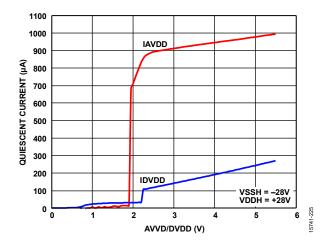

| IVDDH                                           |                                                  |            | 600                   | 765  | μA         |

| IVSSH                                           |                                                  |            | 780                   | 985  | μA         |

| IDVDD                                           | DVDD = 3 V                                       |            | 150                   | 205  | μΑ         |

| IAVDD                                           |                                                  |            | 980                   | 1305 | μΑ         |

| Static Power Dissipation                        | DVDD = 3 V, VSSH = -28 V, VDHH = 28 V            |            | 44                    | 56   | mW         |

|                                                 | DVDD = 3 V, VSSH = -15 V, VDDH = 15 V            |            | 26                    | 34   | mW         |

|                                                 | DVDD = 3 V, VSSH = -12 V, VDDH = 12 V            |            | 20                    | 28   | mW         |

<sup>1</sup> Guaranteed by design. These specifications are not production tested but are supported by characterization data at the initial product release.

<sup>2</sup> For gains less than 1/2, a smaller output swing is used.

<sup>3</sup> Only G = 1 V/V is production tested.

<sup>4</sup> I<sub>WB</sub> means wire break current.

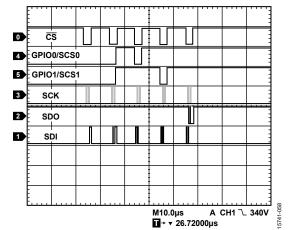

### TIMING SPECIFICATIONS

VDDH = 28 V, VSSH = -28 V, AVDD = 5 V, AVSS = 0 V, DVDD = 3.3 V, DVSS = 0 V, VOCM = AVDD/2 V.

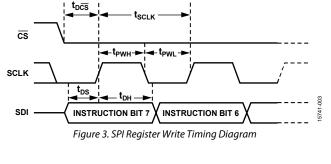

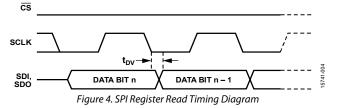

#### Table 2. Digital Values and SPI Timing Specifications

| Parameter                  | Test Conditions/Comments | Min | Тур | Мах | Unit |

|----------------------------|--------------------------|-----|-----|-----|------|

| Maximum Clock Rate (SCLK)  |                          |     |     | 5   | MHz  |

| Minimum Pulse Width (SCLK) |                          |     |     |     |      |

| High                       | t <sub>РWH</sub>         | 75  |     |     | ns   |

| Low                        | tpwl                     | 75  |     |     | ns   |

| SDI/SDO to SCLK Setup Time | t <sub>DS</sub>          | 10  |     |     | ns   |

| SDI/SDO to SCLK Hold Time  | t <sub>DH</sub>          | 10  |     |     | ns   |

| Data Valid, SDO to SCLK    | t <sub>DV</sub>          | 50  |     |     | ns   |

| Setup Time, CS to SCLK     | t <sub>DCS</sub>         | 30  |     |     | ns   |

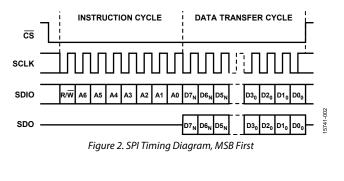

#### **Timing Diagrams**

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| 1 ubic 5.                                                                                        |                              |  |  |  |  |

|--------------------------------------------------------------------------------------------------|------------------------------|--|--|--|--|

| Parameter                                                                                        | Rating                       |  |  |  |  |

| VDDH                                                                                             | VSSH – 0.3 V to VSSH + 60 V  |  |  |  |  |

| AVDD                                                                                             | AVSS – 0.3 V to AVSS + 5.5 V |  |  |  |  |

| DVDD                                                                                             | DVSS – 0.3 V to DVSS + 5.5 V |  |  |  |  |

| AVSS or DVSS                                                                                     | VSSH – 0.3 V to VSSH + 30 V  |  |  |  |  |

| Voltage                                                                                          | VDDH – 30 V to VDDH + 0.3 V  |  |  |  |  |

| Current                                                                                          | ±10 mA                       |  |  |  |  |

| Input Voltage (+IN1, –IN1, +IN2,<br>or –IN2)                                                     | VSSH – 60 V to VSSH + 60 V   |  |  |  |  |

| Differential Input Voltage<br>Between Any Two Amplifier<br>Inputs (+IN1, –IN1, +IN2, or<br>–IN2) | 60 V                         |  |  |  |  |

| <ul> <li>–OUT, +OUT Short-Circuit</li> <li>Current</li> </ul>                                    | Indefinite                   |  |  |  |  |

| VOCM                                                                                             |                              |  |  |  |  |

| Voltage                                                                                          | AVSS – 0.3 V to AVDD + 0.3 V |  |  |  |  |

| Current                                                                                          | ±10 mA                       |  |  |  |  |

| Digital Inputs/Outputs (SPI and GPIO), Voltage                                                   | DVSS – 0.3 V to DVDD + 0.3 V |  |  |  |  |

| Digital Inputs (SPI and GPIO),<br>Current                                                        | ±10 mA                       |  |  |  |  |

| IOUT_LV                                                                                          |                              |  |  |  |  |

| Voltage                                                                                          | AVSS – 0.3 V to AVDD + 0.3 V |  |  |  |  |

| Current                                                                                          | ±10 mA                       |  |  |  |  |

| IOUT_HV                                                                                          |                              |  |  |  |  |

| Voltage                                                                                          | VSSH – 0.3 V to VDDH + 0.3 V |  |  |  |  |

| Current                                                                                          | ±10 mA                       |  |  |  |  |

| Operating Temperature Range                                                                      | -40°C to +125°C              |  |  |  |  |

| Specified Temperature Range                                                                      | –40°C to +105°C              |  |  |  |  |

| Maximum Junction Temperature                                                                     | +150°C                       |  |  |  |  |

| Storage Temperature Range                                                                        | –65°C to +150°C              |  |  |  |  |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection, junction to ambient, thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

#### Table 4. Thermal Resistance

| Package Type <sup>1</sup> | Αιθ  | οις   | Unit |

|---------------------------|------|-------|------|

| CP-28-10                  | 36.9 | 1.9   | °C/W |

| RU-24                     | 64.8 | 14.11 | °C/W |

<sup>1</sup> The thermal resistance values specified in Table 4 are simulated based on JEDEC specifications (unless specified otherwise) and must be used in compliance with JESD51-12.

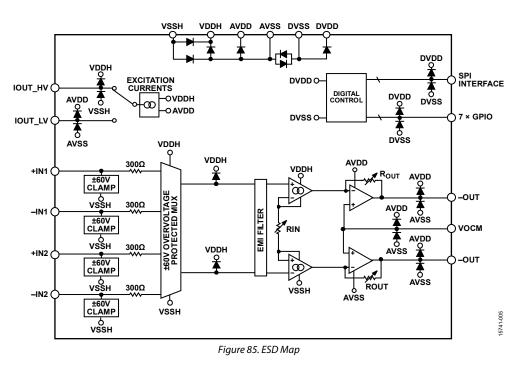

Refer to the ESD Map section for a schematic of ESD diodes and paths.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

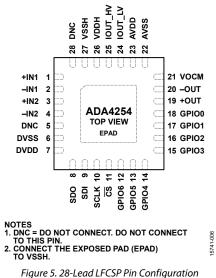

### PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

-OUT 1 24 +OUT 2 23 GPIO0 VOCM 22 GPIO1 AVSS 3 AVDD 4 21 GPIO2 20 GPIO3 IOUT\_LV 5 ADA4254 19 GPIO4 IOUT\_HV 6 TOP VIEW VDDH 7 18 CS 17 SCLK VSSH 8 16 SDI +IN1 9 15 SDO -IN1 10 14 DVDD +IN2 11 1574 1-007 13 DVSS -IN2 12

Figure 6. 24-Lead TSSOP Pin Configuration

| Mnemonic | LFCSP Pin No. | TSSOP Pin No.  | Description                                                                                          |  |

|----------|---------------|----------------|------------------------------------------------------------------------------------------------------|--|

| +IN1     | 1             | 9              | Channel 1 Positive Input.                                                                            |  |

| –IN1     | 2             | 10             | Channel 1 Negative Input.                                                                            |  |

| +IN2     | 3             | 11             | Channel 2 Positive Input.                                                                            |  |

| –IN2     | 4             | 12             | Channel 2 Negative Input.                                                                            |  |

| DNC      | 5, 28         | Not applicable | Do Not Connect. Do not connect to this pin.                                                          |  |

| DVSS     | 6             | 13             | Negative Digital Supply Voltage.                                                                     |  |

| DVDD     | 7             | 14             | Positive Digital Supply Voltage.                                                                     |  |

| SDO      | 8             | 15             | SPI Serial Data Output.                                                                              |  |

| SDI      | 9             | 16             | SPI Serial Data Input.                                                                               |  |

| SCLK     | 10            | 17             | SPI Serial Clock Input.                                                                              |  |

| CS       | 11            | 18             | SPI Chip Select Input.                                                                               |  |

| GPIO6    | 12            | Not applicable | GPIO6/SCS6.                                                                                          |  |

| GPIO5    | 13            | Not applicable | GPIO5/SCS5.                                                                                          |  |

| GPIO4    | 14            | 19             | GPIO4/SCS4/Clock Input or Output.                                                                    |  |

| GPIO3    | 15            | 20             | GPIO3/SCS3/Fault Interrupt Output.                                                                   |  |

| GPIO2    | 16            | 21             | GPIO2/SCS2/Calibration Busy Out.                                                                     |  |

| GPIO1    | 17            | 22             | GPIO1/SCS1/External Multiplexer Control 1.                                                           |  |

| GPIO0    | 18            | 23             | GPIO0/SCS0/External Multiplexer Control 0.                                                           |  |

| +OUT     | 19            | 24             | Positive Output.                                                                                     |  |

| -OUT     | 20            | 1              | Negative Output.                                                                                     |  |

| VOCM     | 21            | 2              | Output Amplifier Common-Mode Voltage Input. This pin is high impedance and is not internally biased. |  |

| AVSS     | 22            | 3              | Output Amplifier Negative Supply Voltage.                                                            |  |

| AVDD     | 23            | 4              | Output Amplifier Positive Supply Voltage.                                                            |  |

| IOUT_LV  | 24            | 5              | Low Voltage Excitation Current Source Output.                                                        |  |

| IOUT_HV  | 25            | 6              | High Voltage Excitation Current Source Output.                                                       |  |

| VDDH     | 26            | 7              | Positive High Voltage Supply.                                                                        |  |

| VSSH     | 27            | 8              | Negative High Voltage Supply.                                                                        |  |

| EPAD     |               | Not applicable | Exposed Pad. Connect the exposed pad (EPAD) to VSSH.                                                 |  |

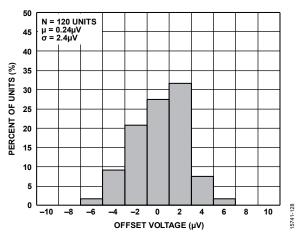

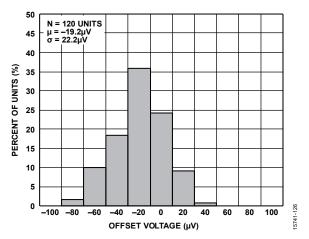

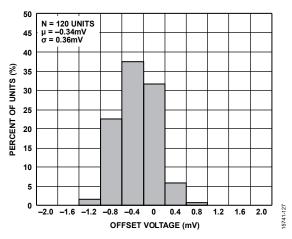

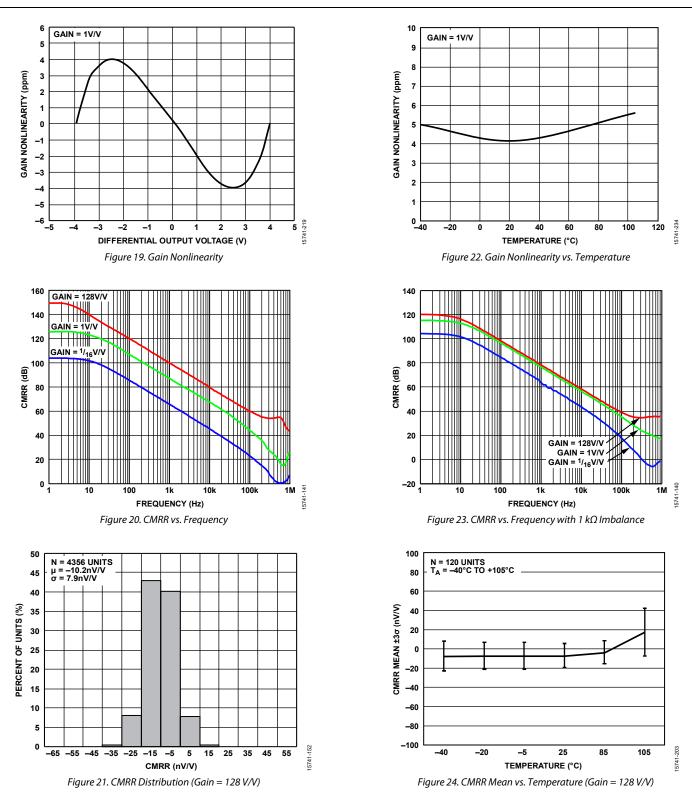

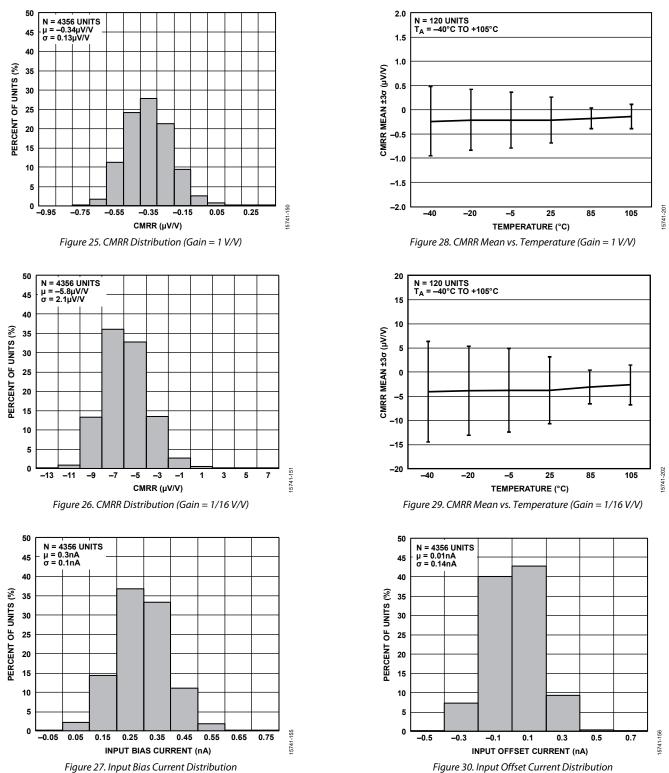

### **TYPICAL PERFORMANCE CHARACTERISTICS**

$T_A = 25^{\circ}$ C, VDDH = 28 V, VSSH = -28 V, AVDD = 5 V, AVSS = 0 V, DVDD = 3.3 V, DVSS = 0 V, VOCM = AVDD/2, and no load, unless otherwise noted.

Figure 7. Offset Voltage Distribution, RTI (Gain = 128 V/V)

Figure 8. Offset Voltage Distribution, RTI (Gain = 1 V/V)

Figure 9. Offset Voltage Distribution, RTI (Gain = 1/16 V/V)

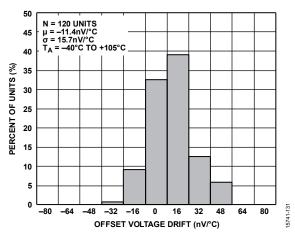

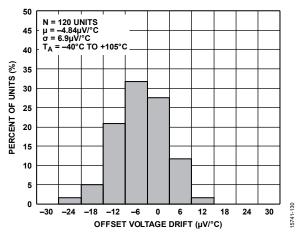

Figure 10. Offset Voltage Drift Distribution, RTI (Gain = 128 V/V)

*Figure 11. Offset Voltage Drift Distribution, RTI (Gain = 1 V/V)*

Figure 12. Offset Voltage Drift Distribution, RTI (Gain = 1/16 V/V)

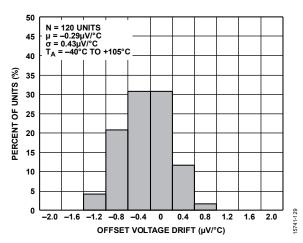

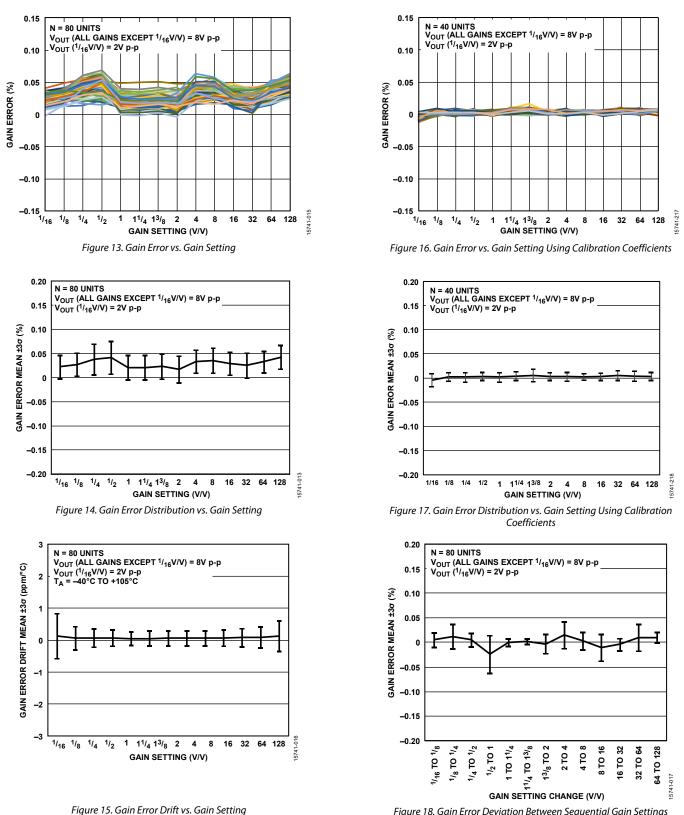

Figure 18. Gain Error Deviation Between Sequential Gain Settings

Rev. B | Page 12 of 59

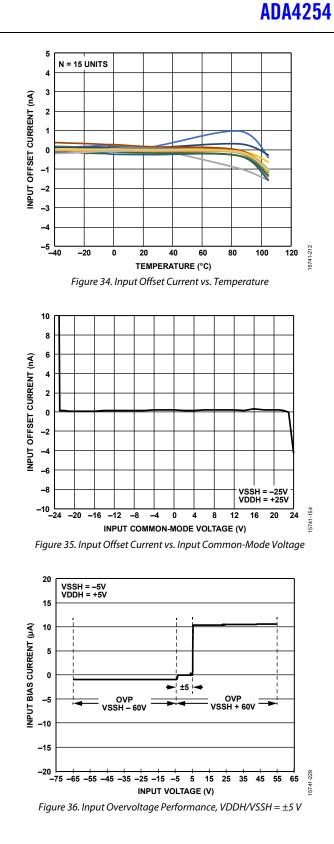

Figure 30. Input Offset Current Distribution

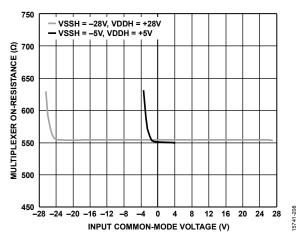

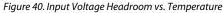

Figure 38. Multiplexer On-Resistance vs. Input Common-Mode Voltage

**Data Sheet**

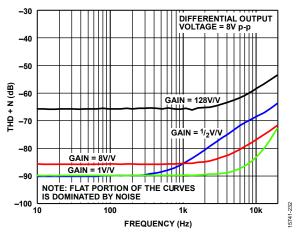

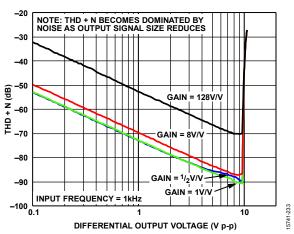

Figure 56. Total Harmonic Distortion Plus Noise (THD + N) vs. Frequency with 100 kHz Filter, Differential Load Resistor ( $R_{L, DIFF}$ ) = 5 k $\Omega$

Figure 59. THD + N vs. Differential Output Voltage with 100 kHz Filter,  $R_{L, DIFF} = 5 k\Omega$

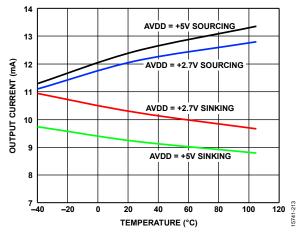

Figure 60. Sinking/Sourcing Short-Circuit Output Current vs. Temperature

Figure 66. Large Signal Step Response (Gain = 1 V/V)

### 10V/DIV - IN1 INPUT SIGNA. +IN1 = 0V INPUT OVERLOADED DIFFERENTIAL OUTPUT VOLTAGE 1V/DIV Т ---- I FAULT INTERRUPT 5V/DIV ٦ 5741-167 20µs/DIV

Figure 67. Input Overload Recovery Step Response (Gain = 1/16 V/V)

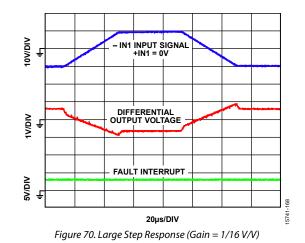

Figure 69. Internal Oscillator Frequency Error vs. Temperature

CAPACITIVE LOAD (nF)

Figure 71. Overshoot/Undershoot vs. Capacitive Load

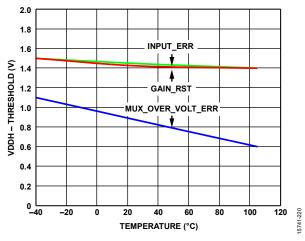

Figure 75. Error Flag Negative Trip Voltage (Threshold – VSSH) vs. Temperature

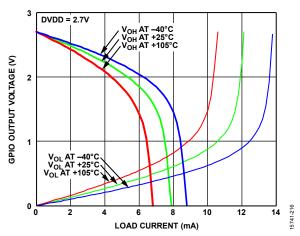

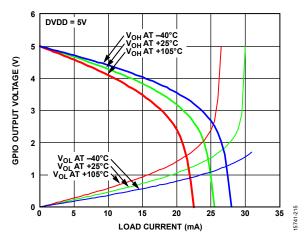

Figure 76. GPIO Output Voltage ( $V_{OH}/V_{OL}$ ) vs. Load Current for Various Temperatures; DVDD = 5 V

Figure 78. Error Flag Positive Trip Voltage (VDDH – Threshold) vs. Temperature

5741-050

### THEORY OF OPERATION PROGRAMMABLE GAIN INSTRUMENTATION AMPLIFIER

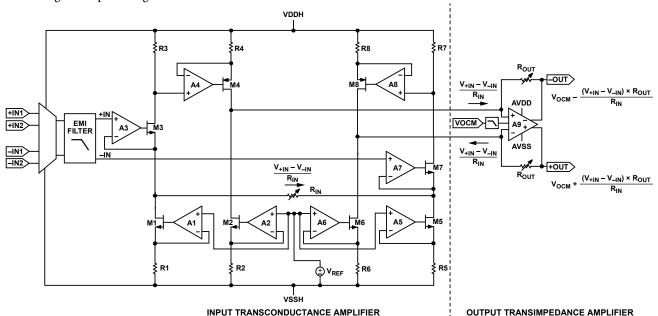

The ADA4254 is a direct current mode instrumentation amplifier implemented with zero drift amplifiers. The ADA4254 topology ensures precision operation over temperature. Refer to the simplified architecture shown in Figure 79 to understand the following circuit description.

The input multiplexer connects the inputs to Amplifier A3 and Amplifier A7, which are configured to replicate these input voltages on the  $R_{IN}$  input resistor. The A1, A2, A5, and A6 amplifiers are configured to replicate the internal reference voltage,  $V_{REF}$ , on R1, R2, R5, and R6, creating four nominally equal dc bias currents in the drains of M1, M2, M5, and M6. Amplifier A4 and Amplifier A8 are configured to replicate the currents in R3 and R7 in the drains of M4 and M8, respectively, forming current mirrors.

When positive voltage is applied to the ADA4254 inputs, a proportional current is conducted by  $R_{IN}$ . The drain currents of M3 and M4 increase by this amount, and the drain currents of M7 and M8 reduce by this amount. This portion of the amplifier operates as a transconductance with differential output, each having a gain of  $1/R_{IN}$ . Output amplifier A9 is configured as a transimpedance amplifier with gain of  $R_{OUT}$ . A9 provides a common-mode level shift to the output and produces the differential output voltage ( $V_{OUT, DIFF}$ ) as follows:

$$V_{OUT, DIFF} = \frac{(V_{+IN} - V_{-IN}) \times R_{OUT} \times 2}{R_{IN}}$$

where:

$V_{+IN}$  is the positive input voltage.  $V_{-IN}$  is the negative input voltage. The overall gain of the ADA4254 amplifier is  $2 \times R_{OUT}/R_{IN}$ . The different gain settings are achieved by internally switching in different values for  $R_{OUT}$  and  $R_{IN}$ .

The value of  $R_{IN}$  can be set to 12 different values via the G3 to G0 bits, resulting in 12 binary weighted input gains. The value of  $R_{OUT}$  can also be set to three different values via G4 and G5, resulting in three output scaling gains. Table 6 shows the 36 possible gain configurations, making the ADA4254 versatile when interfacing with a wide selection of sensors and ADCs.

| Table 0. Possible Gam Settings |        |                           |          |  |  |  |  |  |

|--------------------------------|--------|---------------------------|----------|--|--|--|--|--|

|                                | 0      | Output Scaling Gain (V/V) |          |  |  |  |  |  |

| Input Gain                     | 1      | 1.25                      | 1.375    |  |  |  |  |  |

| 0.0625                         | 0.0625 | 0.078125                  | 0.085938 |  |  |  |  |  |

| 0.125                          | 0.125  | 0.15625                   | 0.171875 |  |  |  |  |  |

| 0.25                           | 0.25   | 0.3125                    | 0.34375  |  |  |  |  |  |

| 0.5                            | 0.5    | 0.625                     | 0.6875   |  |  |  |  |  |

| 1                              | 1      | 1.25                      | 1.375    |  |  |  |  |  |

| 2                              | 2      | 2.5                       | 2.75     |  |  |  |  |  |

| 4                              | 4      | 5                         | 5.5      |  |  |  |  |  |

| 8                              | 8      | 10                        | 11       |  |  |  |  |  |

| 16                             | 16     | 20                        | 22       |  |  |  |  |  |

| 32                             | 32     | 40                        | 44       |  |  |  |  |  |

| 64                             | 64     | 80                        | 88       |  |  |  |  |  |

| 128                            | 128    | 160                       | 176      |  |  |  |  |  |

Table 6. Possible Gain Settings

Each amplifier used in the ADA4254 uses a proprietary, zero drift architecture to ensure very low offset voltage, offset voltage drift, and 1/f noise.

INPUT TRANSCONDUCTANCE AMPLIFIER ! OUTPUT TRANSIMPEDANCE AMPLIFIER Figure 79. Simplified ADA4254 Programmable Gain Instrumentation Amplifier Topology

#### **INPUT MULTIPLEXER**

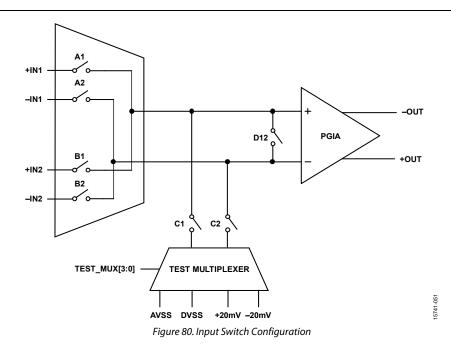

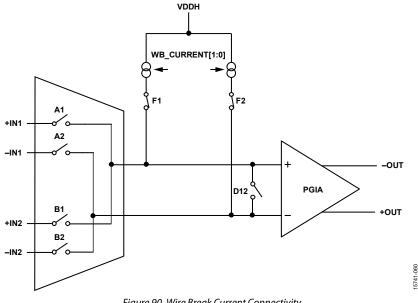

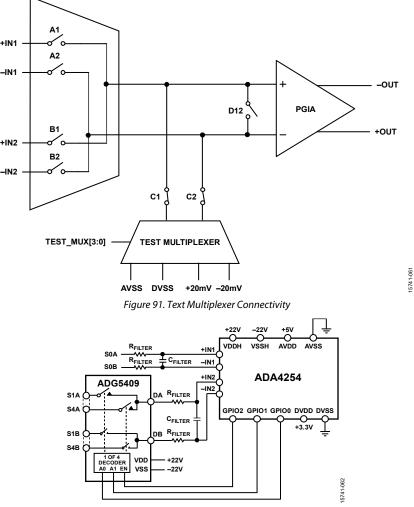

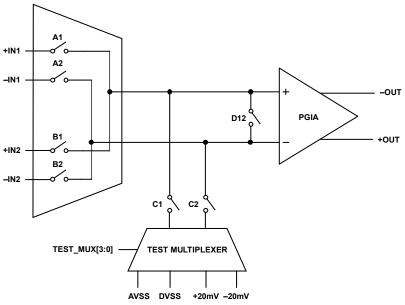

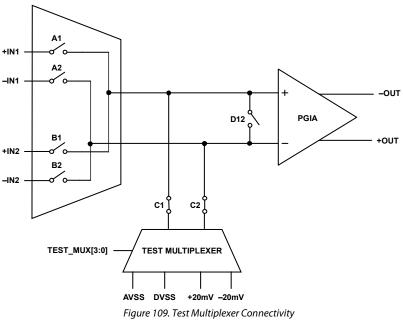

The ADA4254 input multiplexer withstands input voltages up to  $\pm 60$  V with respect to VSSH, and 60 V differentially. As shown in Figure 80, the multiplexer switches between two sets of inputs and features additional switch functionality on the output of the multiplexer. Input switching is controlled via the INPUT\_MUX register. The A1, A2, B1, and B2 switches connect the different inputs to the amplifier. The C1 and C2 switches connect the multiplexer outputs to the test multiplexer. Switch D12 connects both inputs together. The input multiplexer features <140 dB of crosstalk.

If excessive input voltage is detected by the input multiplexer, MUX\_OVER\_VOLT\_ERR in the analog error register trips. When this error flag is set, the multiplexer automatically opens A1, A2, B1, and B2 to protect the input amplifier and input resistor network. This error flag can be disabled by setting MUX\_OVER\_VOLT\_ERR\_DIS. By default, both sets of inputs cannot be selected simultaneously. This protection can be overridden via MUX\_PROT\_DIS.

### EMI REDUCTION AND INTERNAL EMI FILTER

In many industrial and data acquisition applications, the ADA4254 amplifies small signals accurately in the presence of large commonmode voltages or high levels of noise. Typically, the sources of these very small signals (in the order of microvolts or millivolts) are sensors that may be a significant distance from the signal conditioning circuit. Although these sensors may be connected to signal conditioning circuitry using shielded or unshielded twisted pair cabling, the cabling may act as an antenna, conveying very high frequency interference directly to the inputs of the ADA4254.

The amplitude and frequency of this high frequency interference can have an adverse effect on the input stage of the instrumentation amplifier due to unwanted dc shift in the input offset voltage of the amplifier. This well known effect is called EMI rectification and is produced when out of band interference is coupled (inductively, capacitively, or via radiation) and rectified by the input transistors of the instrumentation amplifier. These transistors act as high frequency signal detectors, in the same way diodes were used as RF envelope detectors in early radio designs. Regardless of the type of interference or the method by which it is coupled to the circuit, an out of band error signal appears in series with the inputs of the instrumentation amplifier.

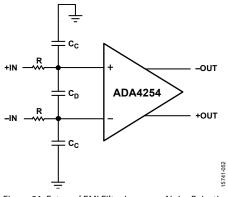

To minimize this effect, the ADA4254 has 35 MHz on-chip EMI filters to attenuate high frequencies before interacting with the input transistors. These on-chip filters are well matched due to their monolithic construction, which minimizes degradation in ac CMRR. To reduce any further effect of these out of band signals on the input offset voltage of the ADA4254, an additional external low-pass filter can be used at the inputs. Locate the filter very close to the input pins of the circuit. An effective filter configuration is shown in Figure 81 where three capacitors are added to the ADA4254 inputs. The filter limits the input signal according to the following relationship:

Filter Frequency<sub>DIFF</sub> =

$$\frac{1}{2\pi R(2C_D + C_C)}$$

Filter Frequency<sub>CM</sub> =  $\frac{1}{2\pi RC_C}$

where:

$C_D$  is the differential capacitor and is  $\geq 10 C_C$ .  $C_C$  is the common-mode capacitor.

$C_{\rm D}$  affects the difference signal.  $C_{\rm C}$  affects the common-mode signal. Any mismatch in R  $\times$   $C_{\rm C}$  degrades the ADA4254 CMRR. To avoid inadvertently reducing CMRR bandwidth performance,

ensure that  $C_C$  is at least one magnitude smaller than  $C_D$ . The effect of mismatched C<sub>C</sub> values is reduced with a larger C<sub>D</sub>:C<sub>C</sub> ratio.

Figure 81. External EMI Filter Improves Noise Rejection

### **INPUT AMPLIFIER**

The ADA4254 input amplifier operates on high voltage power supplies, VDDH and VSSH. The input amplifiers are monitored for clipping due to excessive signal swing. If excessive output swing is detected by an input amplifier (A3 and A7 in Figure 79), the INPUT\_ERR flag trips. If INPUT\_ERR is tripped for more than 200 µs, the gain settings in the GAIN\_MUX register are reset to their default values and the G\_RST flag trips. This setup protects the input amplifiers and the input resistor network. The gain reset function can be disabled via the G\_RST\_DIS bit.

### **OUTPUT AMPLIFIER**

The ADA4254 features a fully differential output amplifier running from dedicated low voltage supplies, AVDD and AVSS. Use AVDD and AVSS in a single-supply configuration. By running the output amplifier on low voltage supplies, circuitry connected to the output of the ADA4254 is inherently protected. The common-mode output voltage is set by the VOCM input voltage. VOCM has a high input impedance and is not biased internally. VOCM also features a 29 MHz EMI filter to minimize EMI interference. Typically, VOCM is biased to midsupply through a voltage divider between AVDD and AVSS to allow the widest swing on the output. The output amplifier can be set to three different scaling gains via G4 or G5: 1 V/V, 1.25 V/V, or 1.375 V/V. On power-up or soft reset, the output amplifier scaling gain defaults to 1 V/V. The output amplifier is monitored for clipping due to excessive signal swing. When the output saturates to either supply, the OUTPUT\_ERR error flag trips.

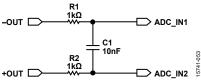

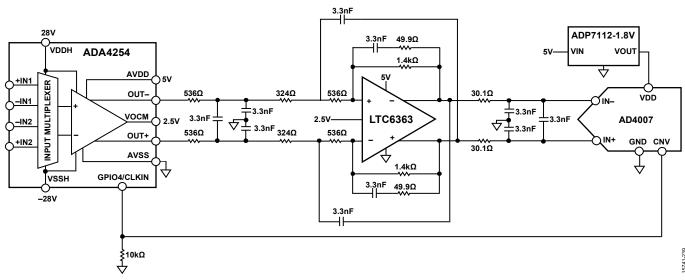

The differential output stage of the ADA4254 allows the device to be directly connected to high precision ADCs, such as the AD7768 and the AD4007. When making such a connection, it is recommended to use a low-pass filter to minimize noise and aliasing, as shown in Figure 82. The LTC6363 is configured as a three-pole, low-pass filter with a cutoff frequency of 40 kHz.

Figure 82. Simple Output Filter Preventing Aliasing and Filters Switching Noise

Figure 83. LTC6363 Used as a Low-Pass Filter/Driver

5741-235

### **POWER SUPPLIES**

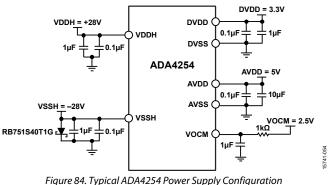

The ADA4254 has three supply voltage domains: the high voltage analog input amplifier supply, the low voltage analog output amplifier supply, and the low voltage digital supply.

The high voltage analog supplies, VDDH and VSSH, power the input section of the ADA4254. VSSH is connected to the substrate of the ADA4254. Therefore, VSSH must be connected to the most negative supply voltage in the circuit and VSSH must not exceed AVSS. It is recommended to use a Schottky diode to clamp VSSH to AVSS. The Schottky diode must have a forward bias voltage of 0.3 V or lower at 1 mA and withstand –28 V of reverse voltage. The ADA4254 monitors the VDDH and VSSH supplies to detect if the VDDH or VSSH drops below 8 V and sets the POR\_HV flag. VDDH and VSSH must be decoupled with 0.1  $\mu$ F and 1  $\mu$ F to ground, as close to the pins as possible.

The low voltage analog output amplifier supply, AVDD and AVSS, powers the output amplifier of the ADA4254. AVSS must be within VSSH – 0.3 V to VSSH + 30 V and VDDH – 30 V to VDDH + 0.3 V. AVDD – AVSS is typically a 5 V single supply, compatible with most high precision ADCs. Use 0.1  $\mu F$  and 10  $\mu F$  decoupling capacitors between AVDD and AVSS as close as possible to the AVDD and AVSS supply pins.

The digital supplies, DVDD and DVSS, power the digital circuitry inside the ADA4254. DVSS must be the same potential as AVSS.

Use 0.1  $\mu$ F and 1  $\mu$ F decoupling capacitors from DVDD to DVSS as close as possible to the DVDD and DVSS supply pins. Figure 84 shows a typical ADA4254 supply configuration. The recommended decoupling values described in this section are minimum recommendations. Depending on amplifier loading and system noise, higher capacitance values and/or additional lower capacitor values may improve performance.

#### ESD MAP

Figure 85 shows the various ESD diode paths inside the ADA4254. Figure 85, in conjunction with the Absolute Maximum Ratings section, helps in understanding current paths during power-on and fault conditions.

### **OUTPUT RIPPLE CALIBRATION CONFIGURATION**

The amplifiers inside the ADA4254 achieve zero drift by using a technique commonly referred to as chopping. When chopping is used to null the offset of an amplifier, the unchopped offsets are modulated to the frequency at which the chopping is performed. All chopping amplifiers feature this phenomenon, which is commonly referred to as ripple.

The ADA4254 instrumentation amplifier features a proprietary calibration routine that reduces the residual voltage ripple at the output of the ADA4254 by nulling the internal offsets of all amplifiers. This calibration occurs automatically when the ADA4254 is initially powered on, after a POR\_HV event, or after a soft reset occurs. Further calibrations can be performed either on a scheduled or triggered basis.

While the ADA4254 is calibrating, SW\_A1, SW\_A2, SW\_B1, and SW\_B2 are temporarily opened and the amplifier inputs are internally connected to AVSS through SW\_C1 and SW\_C2. After a calibration completes, the switches return to their previous states. Two calibration types can be selected via CAL\_SEL: full calibration or quick calibration.

A full calibration sequentially calibrates each individual amplifier and fully computes a new calibration code. This calibration takes approximately 85 ms. Full calibration always occurs after power-up, after a POR\_HV event, or after a soft reset.

A quick calibration calculates a new calibration code for all amplifiers at the same time. The calibration code of each amplifier is then adjusted by an incremental amount. This type of calibration takes approximately 8 ms.

By default, calibrations only occur after power-up, after a POR\_HV event, or after a reset. Additional scheduled calibrations are configured via CAL\_EN, or are triggered via the TRIG\_CAL bit.

When scheduled calibrations are configured via CAL\_EN, the selected calibration type occurs at the rate configured via CAL\_EN.

Calibrations can also be manually triggered via TRIG\_CAL.

The internal offsets, which are nulled by the ADA4254 calibration routine, can change when the circuit or the environmental conditions change. Changes in temperature, supply voltage, common-mode input voltage, time, and so on, can all cause an increase in output ripple. Recalibrations, either triggered or scheduled, renull internal offsets and reduce residual output ripple.

During a calibration, noise can limit the ability of the ADA4254 to fully null internal offsets and fully reduce the residual output ripple. Proper decoupling and shielding techniques help ensure accurate calibrations. Avoid large input transients during calibrations. Calibrations typically reduce the output ripple to <200  $\mu$ V rms, but results as high as 5 mV rms can be observed in the presence of noise or input transients. If excessive residual ripple is detected, subsequent calibrations can be performed to reduce the output ripple.

ADC synchronization and simple filtering, either passive or active, are also effective methods in reducing residual output ripple. These techniques are discussed in detail in the External Clock Synchronization section and the Output Amplifier section.

### **GENERAL-PURPOSE INPUTS/OUTPUTS (GPIOs)**

The ADA4254 features several multifunction GPIOs. There are five GPIOs on the TSSOP and seven on the LFCSP package. These GPIOs can be configured to either read a logic input or output a logic signal. A GPIO pin is configured as an input or an output using the GPIO\_DIR register. The bit position in the GPIO\_DIR register corresponds to the GPIO pin number. For example, the bit at Position 0 controls the GPIO0 direction.

The GPIO\_DATA register sets the GPIO output when a GPIO is configured as an output. The GPIO\_DATA register also reads the data at the GPIO pin when a GPIO is configured as an input. The bit field position in the GPIO\_DATA register corresponds to the GPIO pin number. For example, the bit at Position 0 corresponds to GPIO0.

The ADA4254 GPIOs can be configured to perform additional special functions.

Each GPIO can be configured as an output to extend the chip select signal from the SPI master to other slave devices. This special functionality is referred to as sequential chip select. This special functionality is controlled by the SCS register.

GPIO0 and GPIO1 can also be configured as external multiplexer control signals. This function is enabled in the special function register, SF\_CFG. After GPIO0 and GPIO1 are configured as outputs, the EXT\_MUX bit field in the GAIN\_MUX register controls the state of GPIO0 and GPIO1, allowing the gain and the external mux setting to be modified with one write operation.

GPIO2 can be configured to output a calibration busy signal. This function is enabled via CAL\_BUSY\_OUT. The calibration busy signal indicates that the ADA4254 is performing a calibration routine. GPIO2 must be configured as an output to use this special function.

GPIO3 can be configured to output a fault interrupt signal. This signal is an OR function of all the analog and digital error indicators found in the ANALOG\_ERR and DIGITAL\_ERR registers. This function is enabled via FAULT\_INT\_OUT. GPIO3 must be configured as an output to use this special function.

When configured as an output, GPIO4 can be configured to output the 1 MHz master clock or the 125 kHz chopping clock. This is configured via INT\_CLK\_OUT and CLK\_OUT\_SEL. When configured as an input, GPIO4 can also accept an external clock. This function is configured via EXT\_CLK\_IN.

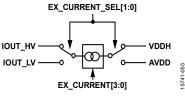

### **EXCITATION CURRENTS**

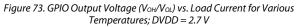

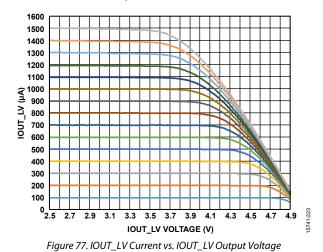

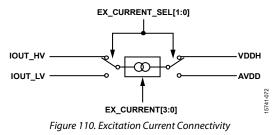

The ADA4254 contains two software configurable excitation current sources, IOUT\_LV and IOUT\_HV. These current sources can be used to excite external circuitry, such as resistive bridges or RTD sensors. IOUT\_LV is sourced from AVDD and IOUT\_HV is

sourced from VDDH (see Figure 86). Only one of the sources can be on at one time. The source can be selected via EX\_CURRENT\_SEL.

Figure 86. Excitation Current Configuration

The excitation currents can be programmed to a value from 100  $\mu$ A to 1.5 mA in increments of 100  $\mu$ A. The current output is controlled via EX\_CURRENT.

### **EXTERNAL CLOCK SYNCHRONIZATION**

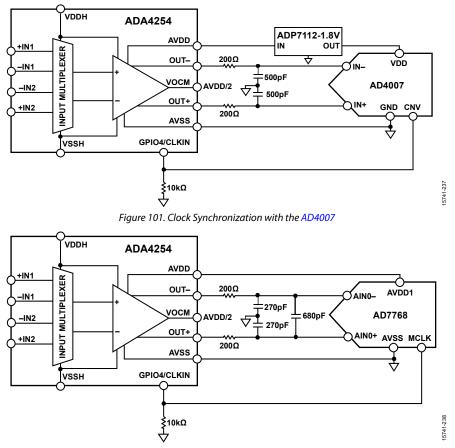

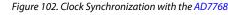

The ADA4254 uses an internal 1 MHz master clock. The master clock is used to derive the 125 kHz chopping clock used by the internal amplifiers. Either clock can be brought out on the GPIO4 pin to allow synchronization of external systems. Use the following procedure to enable the external clock synchronization feature:

- 1. Configure GPIO4 as an output by setting Bit 4 in the GPIO\_DIR register to 1.

- 2. Enable the internal oscillator output special function by setting the INT\_CLK\_OUT bit to 1 and the EXT\_CLK\_IN bit to 0 in the SF\_CFG register.

- 3. To output the 125 kHz clock, set the CLK\_OUT\_SEL bit in the SYNC\_CFG register to 1. To output the 1 MHz clock, set the CLK\_OUT\_SEL bit to 0.

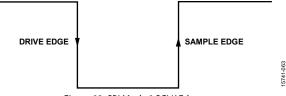

The ADA4254 can alternatively be configured to accept an external clock on GPIO4. The ADA4254 allows external clocks ranging from 1 MHz up to 32 MHz. In the case of an external clock that is higher than 1 MHz, the input clock must be divided down to 1 MHz using the internal clock divider. The edge on which the ADA4254 synchronizes can also be configured.

Use the following procedure to configure the ADA4254 to accept an external clock on GPIO4:

- 1. Configure GPIO4 as an input by setting Bit 4 in the GPIO\_DIR register to 0.

- 2. Set the EXT\_CLK\_IN bit to 1 and ensure that the INT\_CLK\_OUT bit is set to 0 in the SF\_CFG register.

- 3. Depending on the frequency of the input clock, configure the internal clock divider value such that the resulting clock is 1 MHz. The internal clock divider value is controlled by the SYNC bits in the SYNC\_CFG register.

- 4. For synchronizing on the rising edge, set the SYNC\_POL bit in the SYNC\_CFG register to 1. For synchronizing on the falling edge, set SYNC\_POL to 0.

To maintain the performance of the ADA4254, the external clock must in the specified range. The quality of the clock used may affect the device performance. Prevent any overshoot or undershoot on the clock used, and provide an equal rise and fall to minimize the impact on the offset voltage.

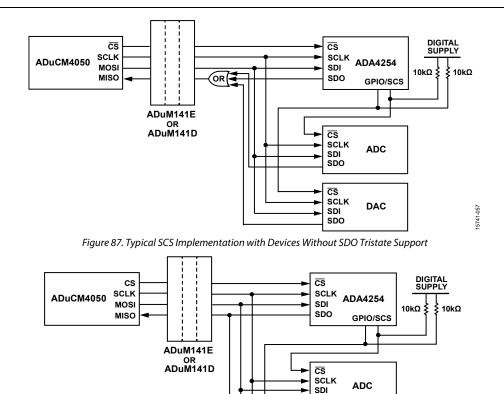

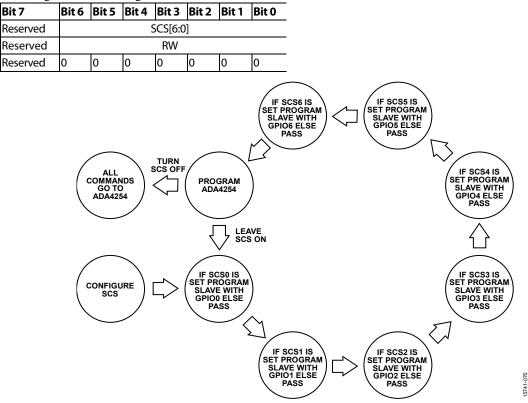

### **SEQUENTIAL CHIP SELECT (SCS)**

SCS is one of the special functions on the ADA4254 that can be configured on the GPIO pins. This mode simplifies isolation requirements by allowing multiple slave devices to communicate over the SPI using a single host chip select  $(\overline{\text{CS}})$  line. This communication also supports CRC checksums transparently.

A GPIO is configured for SCS by first setting the GPIO as an output using a GPIO\_DIR bit, and then setting the respective bit in the SCS register. Configuring a GPIO for SCS mode is blocked if the GPIO is already configured for another function from the special functions register, SF\_CFG.

When using SCS, the  $\overline{\text{CS}}$  signal from the SPI host controller is provided to the ADA4254  $\overline{\text{CS}}$  pin. The serial data input (SDI), serial data output (SDO), and serial clock (SCLK) are shared connections with other SPI devices. The ADA4254 SDO pin supports tristate operation. Slave SDO pins can be directly connected to SDO if the slave pins support tristate operation. For slave devices with SDO pins that do not support tristate operation, an OR gate can be used to combine the SDO signals. If external logic is used to combine SDO lines, pull-down or pull-up resistors are recommended to avoid floating logic gate inputs. Figure 87 and Figure 88 show typical implementations. It is recommended to place pull-up resistors on the GPIOs configured in SCS mode to prevent any unintended communication with slave devices when configuring the ADA4254 in SCS mode.

SDI DAC

SDO

CS SCLK

$Figure \ 88. \ Typical \ SCS \ Implementation \ with \ All \ Devices \ Supporting \ SDO \ Tristate$

When configured for SCS, communication with the ADA4254 and all slave devices follows a predefined pattern. The first  $\overline{CS}$ pulse is passed to the first GPIO that is set up for SCS, effectively communicating with the first slave device. Subsequent  $\overline{CS}$  pulses progress through any GPIOs configured for SCS in ascending order. The last  $\overline{CS}$  pulse addresses the ADA4254 itself. This pattern repeats until SCS is disabled.

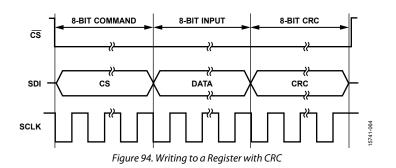

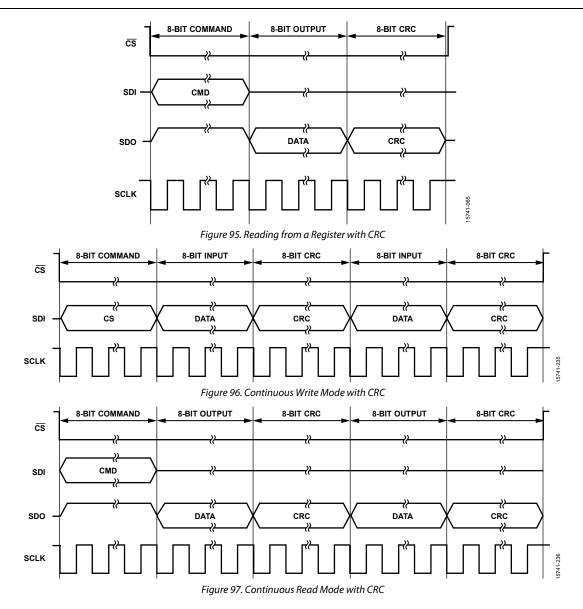

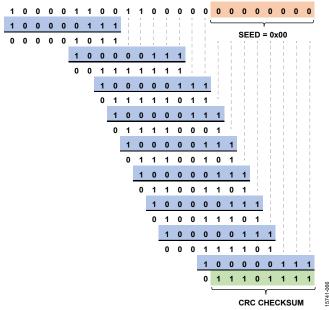

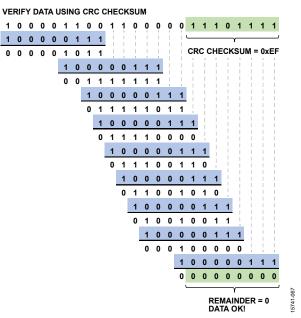

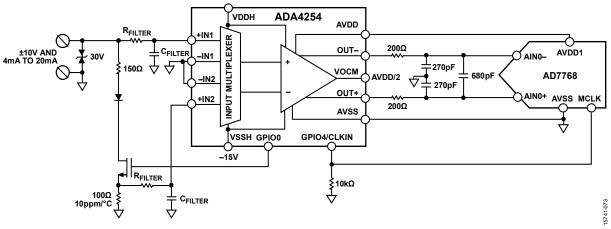

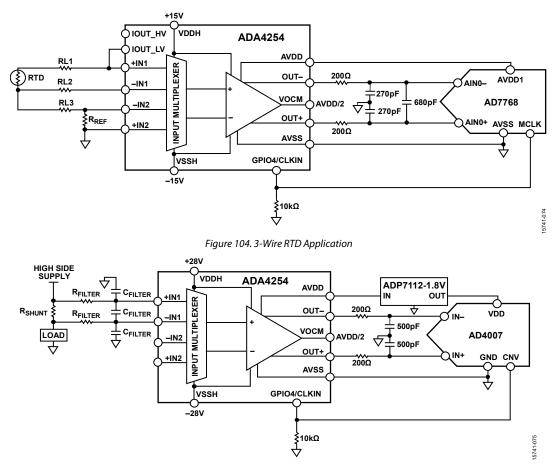

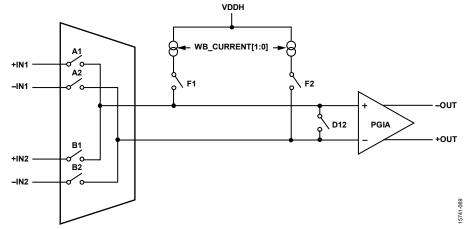

Figure 87 and Figure 88 show the ADA4254 operating in SCS mode with GPIO0 and GPIO1 communicating with two slave devices. GPIO0 is connected to the  $\overline{\text{CS}}$  line of an ADC. GPIO1 is connected to the  $\overline{\text{CS}}$  line of a DAC.