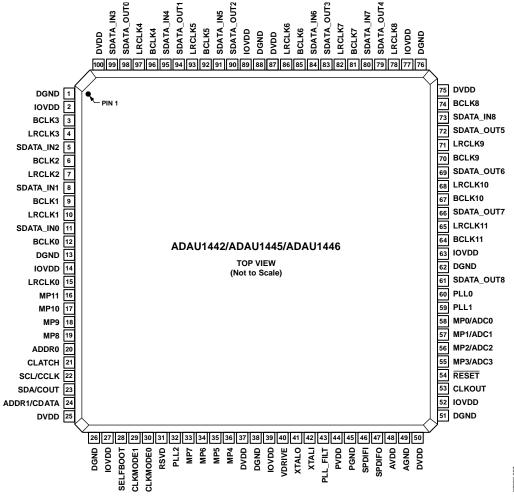

# SigmaDSP Digital Audio Processor with Flexible Audio Routing Matrix

### **Data Sheet**

# ADAU1442/ADAU1445/ADAU1446

#### **FEATURES**

Fully programmable audio digital signal processor (DSP) for enhanced sound processing

Features SigmaStudio, a proprietary graphical programming tool for the development of custom signal flows

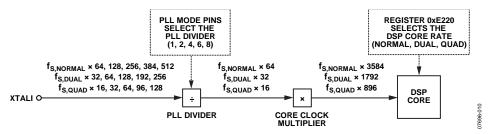

172 MHz SigmaDSP core; 3584 instructions per sample at 48 kHz 4k parameter RAM, 8k data RAM

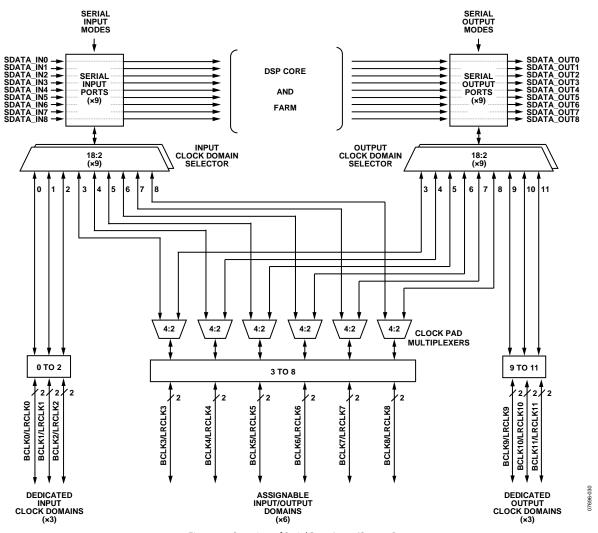

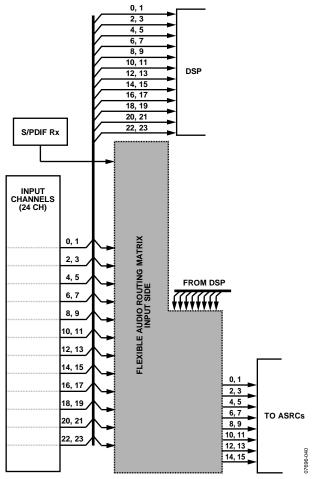

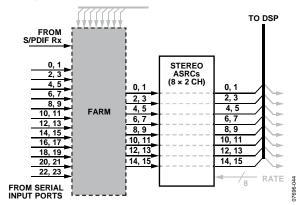

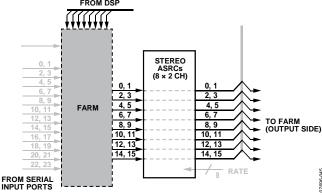

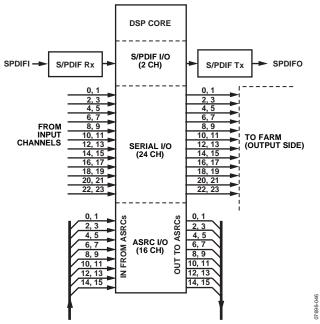

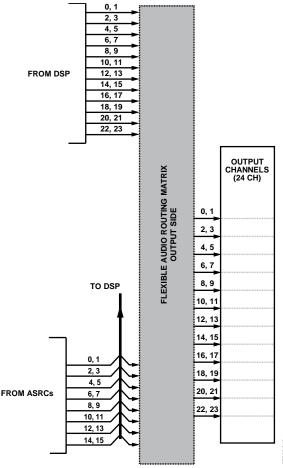

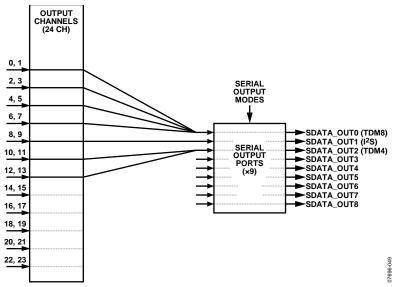

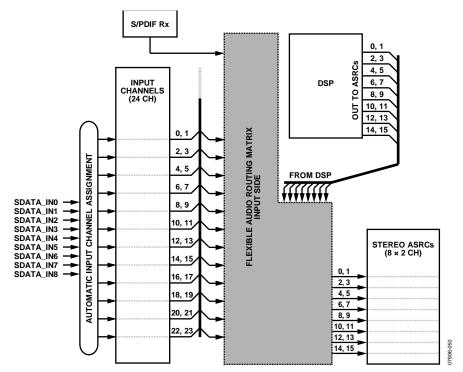

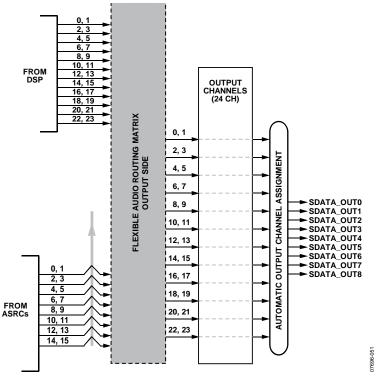

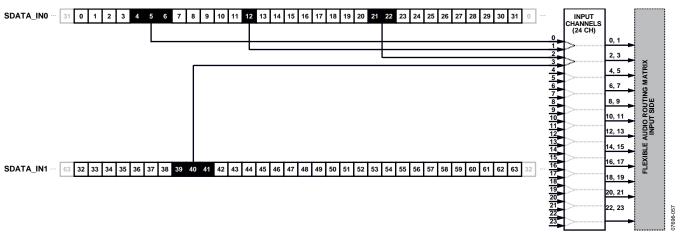

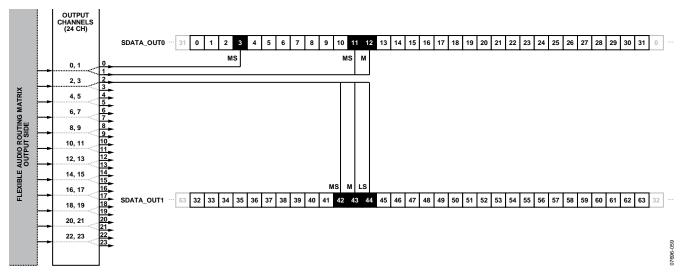

Flexible audio routing matrix (FARM)

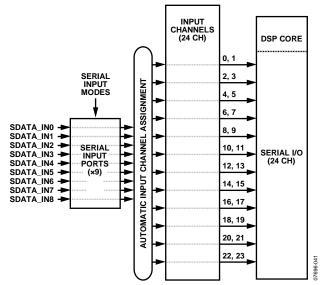

24-channel digital input and output

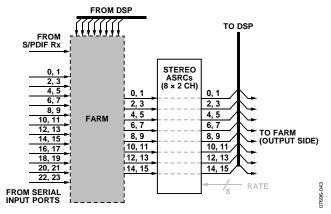

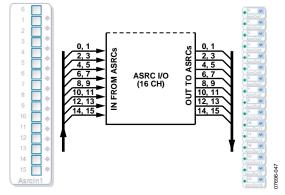

Up to 8 stereo asynchronous sample rate converters

(from 1:8 up to 7.75:1 ratio and 139 dB DNR)

Stereo S/PDIF input and output

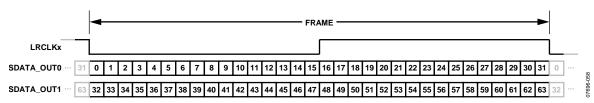

Supports serial and TDM I/O, up to  $f_s = 192 \text{ kHz}$

Multichannel byte-addressable TDM serial port

Pool of 170 ms digital audio delay (at 48 kHz)

Clock oscillator for generating master clock from crystal PLL for generating core clock from common audio clocks

I<sup>2</sup>C and SPI control interfaces

Standalone operation

**Self-boot from serial EEPROM**

4-channel, 10-bit auxiliary control ADC

Multipurpose pins for digital controls and outputs

Easy implementation of available third-party algorithms On-chip regulator for generating 1.8 V from 3.3 V supply 100-lead TQFP and LQFP packages

Temperature range: -40°C to +105°C

#### **APPLICATIONS**

**Automotive audio processing**

**Head units**

**Navigation systems**

**Rear-seat entertainment systems**

DSP amplifiers (sound system amplifiers)

**Commercial audio processing**

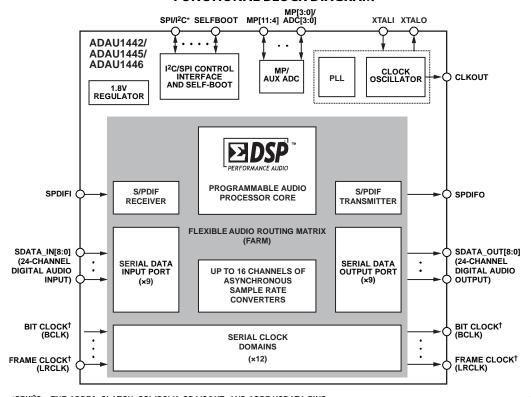

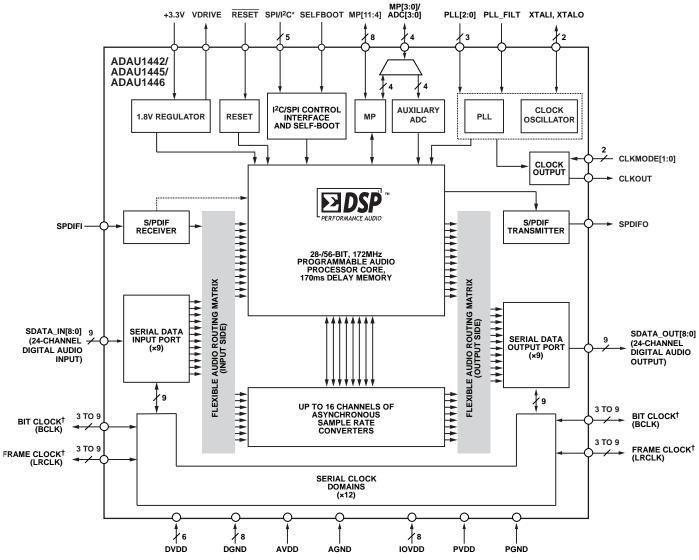

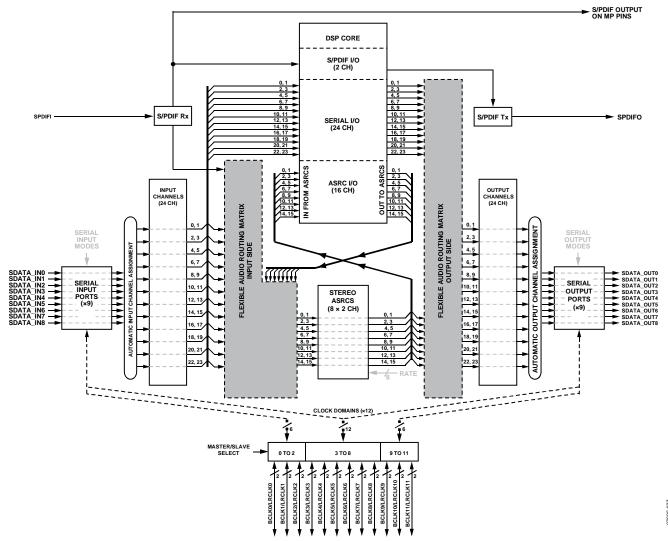

#### **FUNCTIONAL BLOCK DIAGRAM**

\*SPI/I<sup>2</sup>C = THE ADDRO, CLATCH, SCL/CCLK, SDA/COUT, AND ADDR1/CDATA PINS. †THERE ARE 12 BIT CLOCKS (BCLK[11:0]) AND 12 FRAME CLOCKS (LRCLK[11:0]) IN TOTAL. OF THE 12 CLOCKS, SIX ARE ASSIGNABLE, THREE MUST BE OUTPUTS, AND THREE MUST BE INPUTS.

Figure 1.

# **Data Sheet**

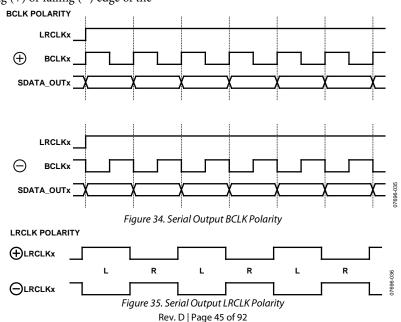

# ADAU1442/ADAU1445/ADAU1446

# **TABLE OF CONTENTS**

| Features                                            | ASRC Modes and Settings                               | 58       |

|-----------------------------------------------------|-------------------------------------------------------|----------|

| Applications1                                       | DSP Core                                              | 60       |

| Functional Block Diagram1                           | DSP Core Modes and Settings                           | 61       |

| Revision History 3                                  | Reliability Features                                  | 62       |

| General Description4                                | RAMs                                                  | 64       |

| Specifications5                                     | S/PDIF Receiver and Transmitter                       | 65       |

| Digital Timing Specifications8                      | S/PDIF Modes and Settings                             | 66       |

| Absolute Maximum Ratings11                          | Multipurpose Pins                                     | 69       |

| Thermal Resistance                                  | Multipurpose Pins Modes and Settings                  | 69       |

| ESD Caution11                                       | Auxiliary ADC                                         | 70       |

| Pin Configuration and Function Descriptions         | Auxiliary ADC Modes and Settings                      | 70       |

| Theory of Operation17                               | Interfacing with Other Devices                        | 71       |

| System Block Diagram17                              | Drive Strength Modes and Settings                     | 71       |

| Overview                                            | Flexible TDM Modes                                    | 76       |

| Initialization                                      | Serial Input Flexible TDM Interface Modes and Setting | gs 76    |

| Master Clock and PLL21                              | Serial Output Flexible TDM Interface Modes and Setti  | ngs . 78 |

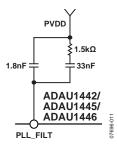

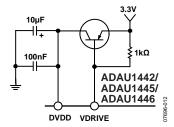

| Voltage Regulator                                   | Software Features                                     | 81       |

| SRC Group Delay25                                   | Software Safeload                                     | 81       |

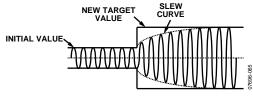

| Control Port                                        | Software Slew                                         | 81       |

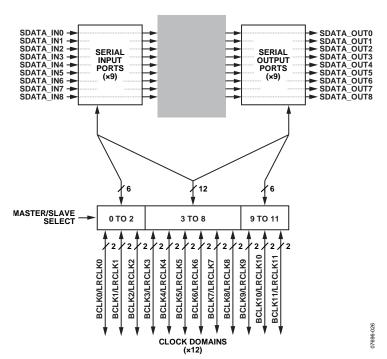

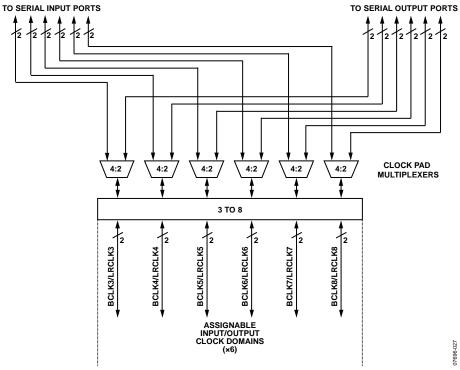

| Serial Data Input/Output31                          | Global RAM and Register Map                           | 82       |

| Serial Input Ports                                  | Overview of Register Address Map                      | 82       |

| Serial Input Port Modes and Settings                | Details of Register Address Map                       | 82       |

| Serial Output Ports41                               | Applications Information                              | 87       |

| Serial Output Port Modes and Settings42             | Layout Recommendations                                | 87       |

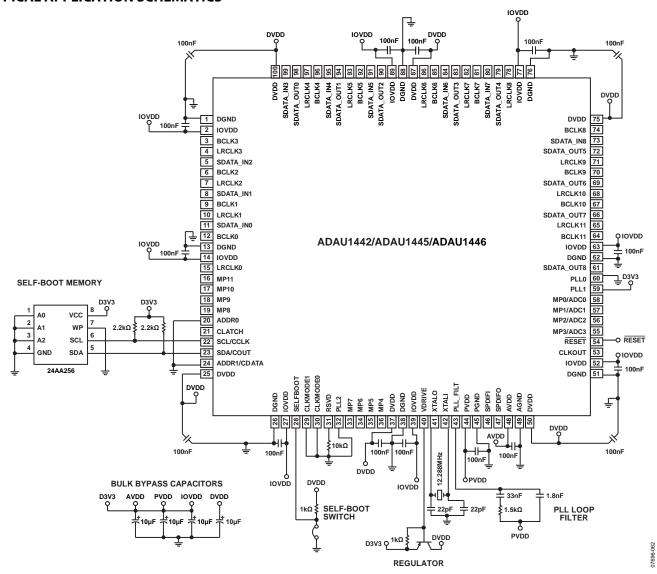

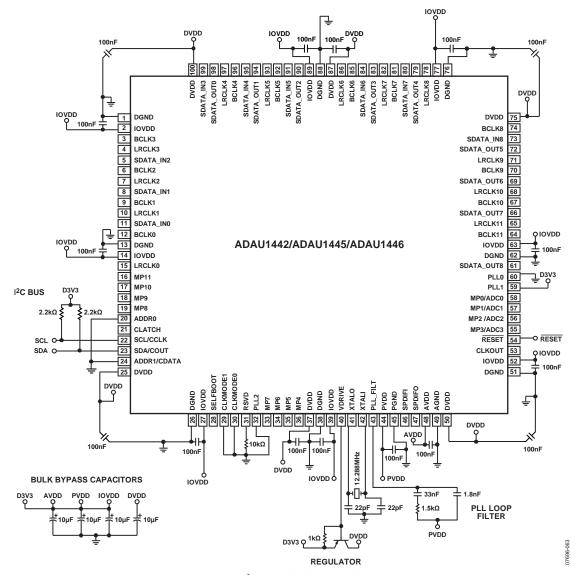

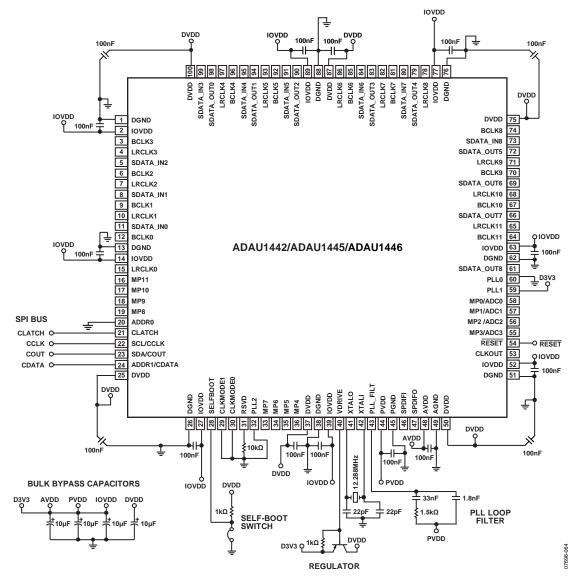

| Flexible Audio Routing Matrix (FARM)46              | Typical Application Schematics                        | 89       |

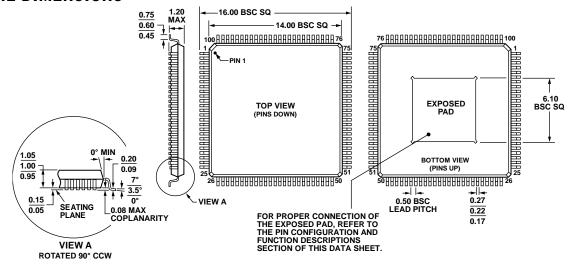

| Flexible Audio Routing Matrix Modes and Settings 52 | Outline Dimensions                                    | 92       |

| Asynchronous Sample Rate Converters58               | Ordering Guide                                        | 92       |

|                                                     |                                                       |          |

# **Data Sheet**

# ADAU1442/ADAU1445/ADAU1446

### **REVISION HISTORY**

| 11/13—Rev. C to Rev. D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Changes to Table 714                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Changes to Serial Input Flexible TDM Interface Modes and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Settings Section76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Change to Figure 6388                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Change to Figure 6691                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9/10—Rev. B to Rev. C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Added Table 1, Renumbered Sequentially4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Changes to System Initialization Sequence Section20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Changes to Table 1224                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Changes to Figure 2029                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Changes to EEPROM Format Section30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Changes to Table 2639                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Changes to Table 3044                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Changes to Stereo ASRC[3:0] Lock Status and Mute Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| (Address 0xE101), Stereo ASRC[3:0] Mute Ramp Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Register (Address 0xE103), and Stereo ASRC[7:4] Lock Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| and Mute Register (Address 0xE141) Sections58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Changes to Architecture Section and Figure 5160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Changes to Core Run Register (Address 0xE228) Section61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Changes to Table 5566                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Changes to Table 5967                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Changes to Multipurpose Pins Section and Table 6869                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4/10—Rev. A to Rev. B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Added ADAU1442Universal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Added ADAU1442Universal Changes to General Description Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Changes to General Description Section4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Changes to General Description Section4 Changes to Table 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Changes to General Description Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Changes to General Description Section       4         Changes to Table 1       5         Added Table 2; Renumbered Sequentially       6         Changes to Table 4       11         Changes to Overview Section       16         Changes to Power-Up Sequence Section, System Initialization       19         Sequence Section, and Table 6       19         Changes to Data Bytes Section       28                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Changes to General Description Section       4         Changes to Table 1       5         Added Table 2; Renumbered Sequentially       6         Changes to Table 4       11         Changes to Overview Section       16         Changes to Power-Up Sequence Section, System Initialization       19         Changes to Data Bytes Section       28         Changes to Serial Clock Domains Section       33                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Changes to General Description Section       4         Changes to Table 1       5         Added Table 2; Renumbered Sequentially       6         Changes to Table 4       11         Changes to Overview Section       16         Changes to Power-Up Sequence Section, System Initialization       Sequence Section, and Table 6       19         Changes to Data Bytes Section       28         Changes to Serial Clock Domains Section       33         Changes to Flexible Audio Routing Matrix—Input Side Section       47                                                                                                                                                                                                                                                                                                                                                |

| Changes to General Description Section       4         Changes to Table 1       5         Added Table 2; Renumbered Sequentially       6         Changes to Table 4       11         Changes to Overview Section       16         Changes to Power-Up Sequence Section, System Initialization       5         Sequence Section, and Table 6       19         Changes to Data Bytes Section       28         Changes to Serial Clock Domains Section       33         Changes to Flexible Audio Routing Matrix—Input Side Section       47         Changes to ASRC Input Select Pairs [7:0] Registers                                                                                                                                                                                                                                                                           |

| Changes to General Description Section       4         Changes to Table 1       5         Added Table 2; Renumbered Sequentially       6         Changes to Table 4       11         Changes to Overview Section       16         Changes to Power-Up Sequence Section, System Initialization       5         Sequence Section, and Table 6       19         Changes to Data Bytes Section       28         Changes to Serial Clock Domains Section       33         Changes to Flexible Audio Routing Matrix—Input Side Section       47         Changes to ASRC Input Select Pairs [7:0] Registers       (Address 0xE080 to Address 0xE087) Section       52                                                                                                                                                                                                                 |

| Changes to General Description Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Changes to General Description Section       4         Changes to Table 1       5         Added Table 2; Renumbered Sequentially       6         Changes to Table 4       11         Changes to Overview Section       16         Changes to Power-Up Sequence Section, System Initialization       19         Changes to Data Bytes Section       28         Changes to Serial Clock Domains Section       33         Changes to Flexible Audio Routing Matrix—Input Side Section       47         Changes to ASRC Input Select Pairs[7:0] Registers       (Address 0xE080 to Address 0xE087) Section       52         Changes to ASRC Output Rate Bits (Bits[5:0]) Section       54         Changes to Stereo ASRC[3:0] Lock Status and Mute Register                                                                                                                        |

| Changes to General Description Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Changes to General Description Section       4         Changes to Table 1       5         Added Table 2; Renumbered Sequentially       6         Changes to Table 4       11         Changes to Overview Section       16         Changes to Power-Up Sequence Section, System Initialization       19         Changes to Data Bytes Section       28         Changes to Serial Clock Domains Section       33         Changes to Flexible Audio Routing Matrix—Input Side Section       47         Changes to ASRC Input Select Pairs [7:0] Registers       (Address 0xE080 to Address 0xE087) Section       52         Changes to ASRC Output Rate Bits (Bits [5:0]) Section       54         Changes to Stereo ASRC [3:0] Lock Status and Mute Register       (Address 0xE101) Section       57         Changes to Stereo ASRC [7:4] Lock Status and Mute Register       57 |

| Changes to General Description Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Changes to Table 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Changes to General Description Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Changes to General Description Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Changes to General Description Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

### 4/09—Rev. 0 to Rev. A

| Added ADAU1446                                          | Universal   |

|---------------------------------------------------------|-------------|

| Added LQFP                                              | Universal   |

| Added Minimum Digital Current (DVDD) of ADAU            | 1446,       |

| Maximum Digital Current (DVDD) of ADAU1446              | , and       |

| AVDD, DVDD, PVDD During Operation of ADAU               | 1446        |

| Parameters, Table 1                                     | 5           |

| Changes to Table 4                                      | 9           |

| Changes to Overview Section                             |             |

| Change to Table 9                                       |             |

| Changes to Voltage Regulator Section                    | 23          |

| Changes to EEPROM Format Section                        |             |

| Changes to Serial Clock Domains Section                 |             |

| Changes to Flexible Audio Routing Matrix—Input Sie      | de Section; |

| Added Figure 40; Renumbered Sequentially                | 46          |

| Changes to Stereo ASRC Routing Overview Section         | 47          |

| Changes to ASRC Input Select Pairs[7:0] Registers (Addr | ess 0xE080  |

| to Address 0xE087) Section                              | 51          |

| Changes to ASRC Output Rate Bits (Bits[5:0]) Section    | n53         |

| Changes to Serial Output Data Selector Bits             |             |

| (Bits[5:0]) Section                                     | 55          |

| Changes to ASRC Modes and Settings Section              | 56          |

| Added Table 43; Renumbered Sequentially                 | 61          |

| Updated Outline Dimensions                              |             |

| Changes to Ordering Guide                               |             |

|                                                         |             |

### 1/09—Revision 0: Initial Version

### **GENERAL DESCRIPTION**

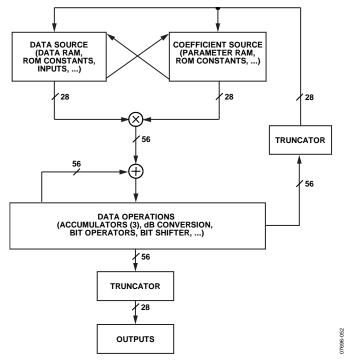

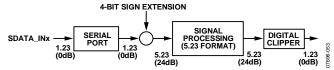

The ADAU1442/ADAU1445/ADAU1446 are enhanced audio processors that allow full flexibility in routing all input and output signals. The SigmaDSP® core features full 28-bit processing (56-bit in double-precision mode), synchronous parameter loading for ensuring filter stability, and 100% code efficiency with the SigmaStudio™ tools. This DSP allows system designers to compensate for the real-world limitations of speakers, amplifiers, and listening environments, resulting in a dramatic improvement of the perceived audio quality through speaker equalization, multiband compression, limiting, and third-party branded algorithms.

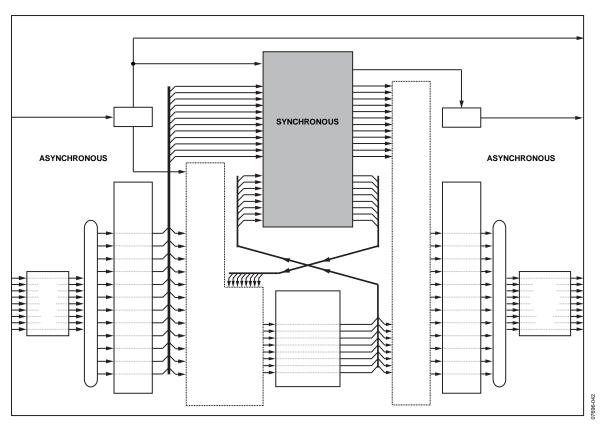

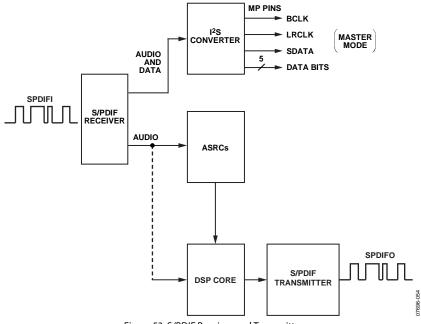

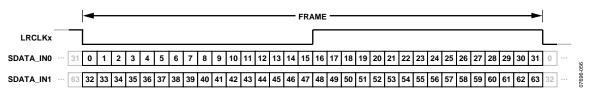

The flexible audio routing matrix (FARM) allows the user to multiplex inputs from multiple sources running at various sample rates to or from the SigmaDSP core. This drastically reduces the complexity of signal routing and clocking issues in the audio system. FARM includes up to eight stereo asynchronous sample rate converters (depending on the device model), Sony/Philips Digital Interconnect Format (S/PDIF) input and output, and serial (I²S) and time division multiplexing (TDM) I/Os. Any of these inputs can be routed to the SigmaDSP core or to any of the asynchronous sample rate converters (ASRCs). Similarly, any one of the output signals can be taken from the SigmaDSP core or from any of the ASRC outputs. This routing scheme, which can

be modified at any time via control registers, allows for maximum system flexibility.

The ADAU1442, ADAU1445, and ADAU1446 differ only in ASRC functionality and packaging. The ADAU1442/ADAU1445 contain 16 channels of ASRCs and are packaged in TQFP packages, whereas the ADAU1446 contains no ASRCs and is packaged in an LQFP. The ADAU1442 can handle nine clock domains, the ADAU1445 can handle three clock domains, and the ADAU1446 can handle one clock domain.

The ADAU1442/ADAU1445/ADAU1446 can be controlled in one of two operational modes: the settings of the chip can be loaded and dynamically updated through the SPI/I<sup>2</sup>C\* port, or the DSP can self-boot from an external EEPROM in a system with no microcontroller. There is also a bank of multipurpose (MP) pins that can be used as general-purpose digital I/Os or as inputs to the 4-channel auxiliary control ADC.

The ADAU1442/ADAU1445/ADAU1446 are supported by the SigmaStudio graphical development environment. This software includes audio processing blocks such as FIR and IIR filters, dynamics processors, mixers, low level DSP functions, and third-party algorithms for fast development of custom signal flows.

Table 1.

| Device   | ASRC Channels | ASRC Clock Domains | Package |

|----------|---------------|--------------------|---------|

| ADAU1442 | 16            | 8                  | TQFP    |

| ADAU1445 | 16            | 2                  | TQFP    |

| ADAU1446 | 0             | N/A                | LQFP    |

# **SPECIFICATIONS**

$AVDD = 3.3 \text{ V}, DVDD = 1.8 \text{ V}, PVDD = 3.3 \text{ V}, IOVDD = 3.3 \text{ V}, T_A = 25^{\circ}\text{C}, \text{ master clock input} = 12.288 \text{ MHz}, \text{ core clock } f_{CORE} = 172.032 \text{ MHz}, I/O \text{ pins set to } 2 \text{ mA drive setting, unless otherwise noted.}$

Table 2.

| Parameter                                        | Min  | Тур                    | Max  | Unit | Test Conditions/Comments                                                                                    |

|--------------------------------------------------|------|------------------------|------|------|-------------------------------------------------------------------------------------------------------------|

| ANALOG PERFORMANCE                               |      |                        |      |      | $AVDD = 3.3 V \pm 10\%.$                                                                                    |

| Auxiliary Analog Inputs                          |      |                        |      |      |                                                                                                             |

| Resolution                                       |      | 10                     |      | Bits |                                                                                                             |

| Full-Scale Analog Input                          |      | AVDD                   |      | V    |                                                                                                             |

| Integral Nonlinearity (INL)                      | -2.3 |                        | +2.3 | LSB  |                                                                                                             |

| Differential Nonlinearity (DNL)                  | -2.0 |                        | +2.0 | LSB  |                                                                                                             |

| Gain Error                                       | -2.0 |                        | +2.0 | LSB  |                                                                                                             |

| Input Impedance                                  |      | 200                    |      | kΩ   |                                                                                                             |

| Sample Rate                                      |      | f <sub>CORE</sub> /896 | 5    | kHz  | 4:1 multiplexed input, each                                                                                 |

|                                                  |      | ICONE OF               |      |      | channel at f <sub>CORE</sub> /3584. For f <sub>CORE</sub> = 172.032 MHz, each channel is sampled at 48 kHz. |

| POWER                                            |      |                        |      |      |                                                                                                             |

| Supply Voltage                                   |      |                        |      |      |                                                                                                             |

| Analog Voltage (AVDD)                            | 2.97 | 3.3                    | 3.63 | V    |                                                                                                             |

| Digital Voltage (DVDD)                           | 1.62 | 1.8                    | 1.98 | V    |                                                                                                             |

| PLL Voltage (PVDD)                               | 2.97 | 3.3                    | 3.63 | V    |                                                                                                             |

| IOVDD Voltage (IOVDD)                            | 2.97 | 3.3                    | 3.63 | V    |                                                                                                             |

| Supply Current                                   |      |                        |      |      |                                                                                                             |

| Analog Current (AVDD)                            |      | 2                      |      | mA   |                                                                                                             |

| PLL Current (PVDD)                               |      | 10                     |      | mA   |                                                                                                             |

| I/O Current (IOVDD)                              |      | 10                     |      | mA   | Depends greatly on the num-                                                                                 |

| vo current (10vbb)                               |      | 10                     |      |      | ber of active serial ports, clock<br>pins, and characteristics of<br>external loads.                        |

| Digital Current (DVDD)                           |      |                        |      |      |                                                                                                             |

| ADAU1442                                         |      |                        |      |      |                                                                                                             |

| Typical Program                                  |      | 335                    |      | mA   | Test program includes<br>16 channels I/O, 10-band EQ<br>per channel, all ASRCs active.                      |

| Minimal Program                                  |      | 115                    |      | mA   | Test program includes<br>2 channels I/O, 10-band EQ<br>per channel.                                         |

| ADAU1445                                         |      |                        |      | _    |                                                                                                             |

| Typical Program                                  |      | 270                    |      | mA   | Test program includes<br>16 channels I/O, 10-band EQ<br>per channel, all ASRCs active.                      |

| Minimal Program                                  |      | 115                    |      | mA   | Test program includes<br>2 channels I/O, 10-band EQ<br>per channel.                                         |

| ADAU1446                                         |      |                        |      |      |                                                                                                             |

| Typical Program                                  |      | 135                    |      | mA   | Test program includes<br>16 channels I/O, 10-band EQ<br>per channel, all ASRCs active.                      |

| Minimal Program                                  |      | 110                    |      |      | Test program includes<br>2 channels I/O, 10-band EQ<br>per channel.                                         |

| ASYNCHRONOUS SAMPLE RATE CONVERTERS <sup>1</sup> |      |                        |      |      |                                                                                                             |

| Dynamic Range                                    |      | 139                    |      | dB   | A-weighted, 20 Hz to 20 kHz.                                                                                |

| I/O Sample Rate                                  | 6    |                        | 192  | kHz  |                                                                                                             |

Rev. D | Page 5 of 92

| Parameter              | Min  | Тур  | Max    | Unit | Test Conditions/Comments |

|------------------------|------|------|--------|------|--------------------------|

| I/O Sample Rate Ratio  | 1:8  |      | 7.75:1 |      |                          |

| THD + N                |      | -133 | -120   | dB   |                          |

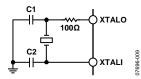

| CRYSTAL OSCILLATOR     |      |      |        |      |                          |

| Transconductance       |      | 40   |        | mS   |                          |

| REGULATOR <sup>2</sup> |      |      |        |      |                          |

| DVDD Voltage           | 1.65 | 1.75 | 1.85   | V    | Maximum 500 mA load.     |

<sup>&</sup>lt;sup>1</sup> To calculate the group delay, refer to the SRC Group Delay section.

$AVDD = 3.3 \ V \pm 10\%, DVDD = 1.8 \ V \pm 10\%, PVDD = 3.3 \ V, IOVDD = 3.3 \ V \pm 10\%, T_A = -40 ^{\circ}C \ to +105 ^{\circ}C, master clock input = 12.288 \ MHz, core clock f_{CORE} = 172.032 \ MHz, I/O pins set to 2 mA drive setting, unless otherwise noted.$

Table 3.

| Parameter                                         | Min          | Тур                    | Max                | Unit | Test Conditions/Comments                                                                                                                |

|---------------------------------------------------|--------------|------------------------|--------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------|

| ANALOG PERFORMANCE                                |              |                        |                    |      | $AVDD = 3.3 V \pm 10\%$ .                                                                                                               |

| Auxiliary Analog Inputs                           |              |                        |                    |      |                                                                                                                                         |

| Resolution                                        |              | 10                     |                    | Bits |                                                                                                                                         |

| Full-Scale Analog Input                           |              | AVDD                   |                    | V    |                                                                                                                                         |

| Integral Nonlinearity (INL)                       | -2.3         |                        | +2.3               | LSB  |                                                                                                                                         |

| Differential Nonlinearity (DNL)                   | -2.0         |                        | +2.0               | LSB  |                                                                                                                                         |

| Gain Error                                        | -2.0         |                        | +2.0               | LSB  |                                                                                                                                         |

| Input Impedance                                   |              | 200                    |                    | kΩ   |                                                                                                                                         |

| Sample Rate                                       |              | f <sub>CORE</sub> /896 |                    | kHz  | 4:1 multiplexed input, each channel at f <sub>CORE</sub> /3584. For f <sub>CORE</sub> = 172.032 MHz, each channel is sampled at 48 kHz. |

| DIGITAL I/O                                       |              |                        |                    |      |                                                                                                                                         |

| Input Voltage, High (V <sub>H</sub> )             | 0.7 × IOVDD  |                        |                    | V    | Digital input pins except<br>SPDIFI.1                                                                                                   |

| Input Voltage, Low (V <sub>IL</sub> )             |              |                        | $0.3 \times IOVDD$ | V    | Digital input pins except<br>SPDIFI.1                                                                                                   |

| Input Leakage, High ( $I_{\mathbb{H}}$ ) at 3.3 V | -2           |                        | +2                 | μΑ   | Digital input pins except<br>MCLK and SPDIFI.                                                                                           |

|                                                   | -2           |                        | +8                 | μΑ   | MCLK.                                                                                                                                   |

|                                                   | 60           |                        | 140                | μΑ   | SPDIFI.                                                                                                                                 |

| Input Leakage, Low (I <sub>IL</sub> ) at 0 V      | -85          |                        | -10                | μA   | All other pins.                                                                                                                         |

|                                                   | -2           |                        | +2                 | μΑ   | CLKMODEx, RSVD, PLLx, RESET.                                                                                                            |

|                                                   | -8           |                        | +2                 | μΑ   | MCLK.                                                                                                                                   |

|                                                   | -140         |                        | -60                | μΑ   | SPDIFI.                                                                                                                                 |

| High Level Output Voltage (Voн)                   | 0.85 × IOVDD |                        |                    | V    | I <sub>OH</sub> = 1 mA.                                                                                                                 |

| Low Level Output Voltage (V <sub>OL</sub> )       |              |                        | $0.1 \times IOVDD$ | V    | $I_{OL} = 1 \text{ mA}.$                                                                                                                |

| Input Capacitance (C <sub>I</sub> )               |              | 5                      |                    | pF   | Guaranteed by design.                                                                                                                   |

| Multipurpose Pins Output Drive                    |              | 2                      |                    | mA   | These pins are not designed for static current draw and should not drive LEDs directly.                                                 |

| POWER                                             |              |                        |                    |      | ·                                                                                                                                       |

| Supply Voltage                                    |              |                        |                    |      |                                                                                                                                         |

| Analog Voltage (AVDD)                             | 2.97         | 3.3                    | 3.63               | V    |                                                                                                                                         |

| Digital Voltage (DVDD)                            | 1.62         | 1.8                    | 1.98               | V    |                                                                                                                                         |

| PLL Voltage (PVDD)                                | 2.97         | 3.3                    | 3.63               | V    |                                                                                                                                         |

| IOVDD Voltage (IOVDD)                             | 2.97         | 3.3                    | 3.63               | V    |                                                                                                                                         |

| Supply Current                                    |              |                        |                    |      |                                                                                                                                         |

| Analog Current (AVDD)                             |              | 2                      |                    | mA   |                                                                                                                                         |

<sup>&</sup>lt;sup>2</sup> Regulator specifications are calculated using an NJT4030P transistor from On Semiconductor in the circuit.

# **Data Sheet**

# ADAU1442/ADAU1445/ADAU1446

| Parameter                                        | Min  | Тур  | Max    | Unit | Test Conditions/Comments                                                                                 |

|--------------------------------------------------|------|------|--------|------|----------------------------------------------------------------------------------------------------------|

| PLL Current (PVDD)                               |      | 10   |        | mA   |                                                                                                          |

| I/O Current (IOVDD)                              |      | 10   |        | mA   | Depends greatly on the number of active serial ports, clock pins, and characteristics of external loads. |

| Maximum Digital Current (DVDD)                   |      |      |        |      |                                                                                                          |

| ADAU1442                                         |      |      | 460    | mA   | Test program includes<br>24 channels I/O, fully utilized<br>program RAM.                                 |

| ADAU1445                                         |      |      | 365    | mA   | Test program includes<br>24 channels I/O, fully utilized<br>program RAM.                                 |

| ADAU1446                                         |      |      | 315    | mA   | Test program includes<br>24 channels I/O, fully utilized<br>program RAM.                                 |

| Power Dissipation                                |      |      |        |      |                                                                                                          |

| AVDD, DVDD, PVDD During Operation of ADAU1442    |      |      | 960    | mW   | All supplies at nominal +10%, IOVDD is not included in measurement.                                      |

| AVDD, DVDD, PVDD During Operation of ADAU1445    |      |      | 780    | mW   | All supplies at nominal +10%, IOVDD is not included in measurement.                                      |

| AVDD, DVDD, PVDD During Operation of ADAU1446    |      |      | 675    | mW   | All supplies at nominal +10%, IOVDD is not included in measurement.                                      |

| Reset, All Supplies                              |      | 94   |        | mW   |                                                                                                          |

| ASYNCHRONOUS SAMPLE RATE CONVERTERS <sup>2</sup> |      |      |        |      |                                                                                                          |

| Dynamic Range                                    |      | 139  |        | dB   | A-weighted, 20 Hz to 20 kHz.                                                                             |

| I/O Sample Rate                                  | 6    |      | 192    | kHz  |                                                                                                          |

| I/O Sample Rate Ratio                            | 1:8  |      | 7.75:1 |      |                                                                                                          |

| THD + N                                          |      | -133 | -120   | dB   |                                                                                                          |

| CRYSTAL OSCILLATOR                               |      |      |        |      |                                                                                                          |

| Transconductance                                 |      | 40   |        | mS   |                                                                                                          |

| REGULATOR <sup>3</sup>                           |      |      |        |      |                                                                                                          |

| DVDD Voltage                                     | 1.65 | 1.75 | 1.85   | V    | Maximum 500 mA load.                                                                                     |

<sup>&</sup>lt;sup>1</sup> SPDIFI input voltage range exceeds the requirements of the S/PDIF specification. <sup>2</sup> To calculate the group delay, refer to the SRC Group Delay section. <sup>3</sup> Regulator specifications are calculated using an NJT4030P transistor from On Semiconductor in the circuit.

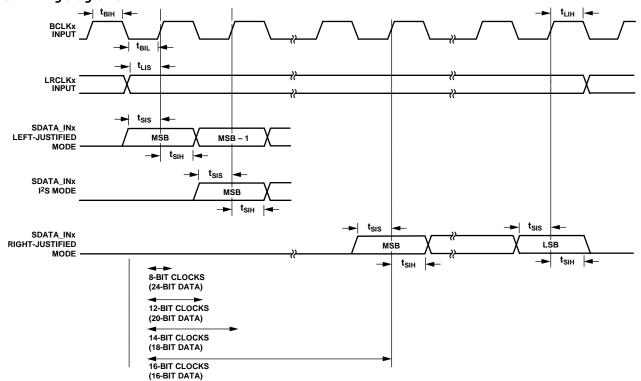

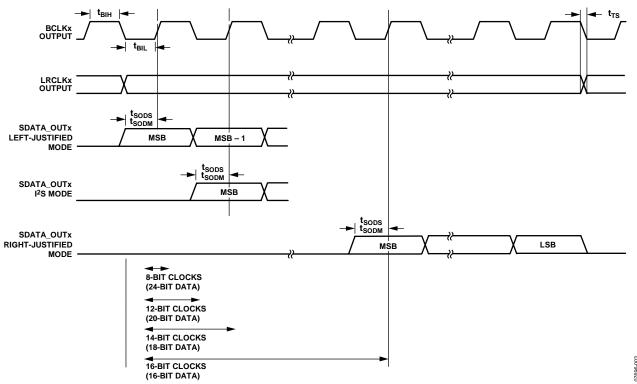

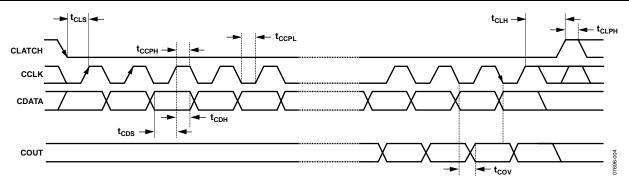

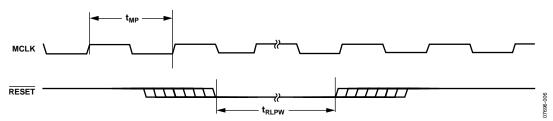

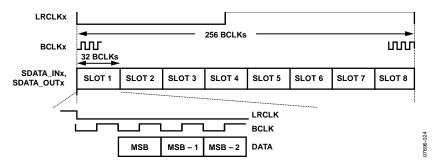

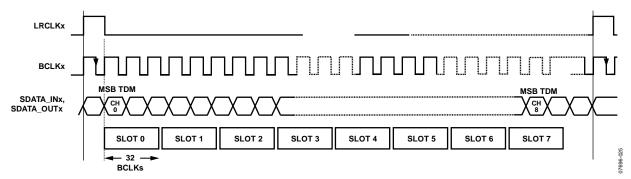

### **DIGITAL TIMING SPECIFICATIONS**

$T_A = -40$ °C to +105°C, DVDD = 1.8 V, IOVDD = 3.3 V.

Table 4

| Table 4.  Parameter <sup>1</sup> | Min    | Max                         | Unit       | Description                                                            |

|----------------------------------|--------|-----------------------------|------------|------------------------------------------------------------------------|

| MASTER CLOCK                     | 141111 | IVIQA                       | Oilit      | Description                                                            |

|                                  | 2 022  | 24 576                      | NAL 1-     | Master alask (MCLK) fragrenser Coatha Master Clask and DLL coation     |

| f <sub>MP</sub>                  | 2.822  | 24.576                      | MHz        | Master clock (MCLK) frequency. See the Master Clock and PLL section.   |

| <b>t</b> <sub>MP</sub>           | 40.69  | 354.36                      | ns         | Master clock (MCLK) period. See the Master Clock and PLL section.      |

| <b>t</b> <sub>MD</sub>           | 25     | 75                          | %          | Master clock (MCLK) duty cycle.                                        |

| CLKOUT Jitter                    |        | 250                         | ps         | Cycle-to-cycle rms average.                                            |

| CORE CLOCK                       |        |                             |            |                                                                        |

| f <sub>CORE</sub>                |        | 172.032                     | MHz        | DSP core clock frequency.                                              |

| SERIAL PORT                      |        |                             |            |                                                                        |

| $f_{BCLK}$                       |        | 24.576                      | MHz        | BCLK frequency.                                                        |

| t <sub>BCLK</sub>                | 40.69  |                             | ns         | BCLK period.                                                           |

| t <sub>BIL</sub>                 | 30     |                             | ns         | BCLKx low pulse width, slave mode.                                     |

| t <sub>BIH</sub>                 | 30     |                             | ns         | BCLKx high pulse width, slave mode.                                    |

| t <sub>LIS</sub>                 | 20     |                             | ns         | LRCLKx setup to BCLKx input rising edge, slave mode.                   |

| t <sub>LIH</sub>                 | 20     |                             | ns         | LRCLKx hold from BCLKx input rising edge, slave mode.                  |

| t <sub>sis</sub>                 | 10     |                             | ns         | SDATA_INx setup to BCLKx input rising edge.                            |

| t <sub>SIH</sub>                 | 10     |                             | ns         | SDATA_INx hold from BCLKx input rising edge.                           |

| t <sub>rs</sub>                  |        | 5                           | ns         | BCLKx output falling edge to LRCLKx output timing skew.                |

| t <sub>sops</sub>                |        | 30                          | ns         | SDATA_OUTx delay in slave mode from BCLKx output falling edge.         |

| t <sub>sodm</sub>                |        | 30                          | ns         | SDATA_OUTx delay in master mode from BCLKx output falling edge.        |

| SPI PORT                         |        | 30                          | 113        | 3DATA_001x delay in master mode from BCEIxx output failing edge.       |

|                                  |        | 22                          | NAL 1-     | CCLK frequency. <sup>2</sup>                                           |

| fcclk write                      |        | 32                          | MHz<br>MHz |                                                                        |

| f <sub>CCLK read</sub>           | 20     | 16                          |            | CCLK frequency. <sup>2</sup>                                           |

| <b>t</b> ccpl                    | 20     |                             | ns         | CCLK pulse width low.                                                  |

| <b>t</b> ccph                    | 20     |                             | ns         | CCLK pulse width high.                                                 |

| t <sub>CLS</sub>                 | 0      |                             | ns         | CLATCH setup to CCLK rising edge.                                      |

| <b>t</b> <sub>CLH</sub>          | 35     |                             | ns         | CLATCH hold from CCLK rising edge.                                     |

| <b>t</b> <sub>CLPH</sub>         | 20     |                             | ns         | CLATCH pulse width high.                                               |

| t <sub>CLDLY</sub>               | 20     |                             | ns         | Minimum delay between CLATCH low pulses.                               |

| t <sub>CDS</sub>                 | 0      |                             | ns         | CDATA setup to CCLK rising edge.                                       |

| <b>t</b> <sub>CDH</sub>          | 35     |                             | ns         | CDATA hold from CCLK rising edge.                                      |

| t <sub>cov</sub>                 |        | 40                          | ns         | COUT valid output delay from CCLK falling edge.                        |

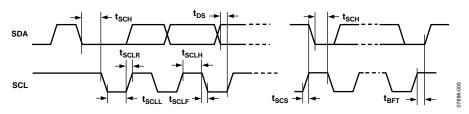

| I <sup>2</sup> C PORT            |        |                             |            |                                                                        |

| f <sub>SCL</sub>                 |        | 400                         | kHz        | SCL clock frequency.                                                   |

| <b>t</b> sclh                    | 0.6    |                             | μs         | SCL pulse width high.                                                  |

| t <sub>scll</sub>                | 1.3    |                             | μs         | SCL pulse width low.                                                   |

| tscs                             | 0.6    |                             | μs         | Start and repeated start condition setup time.                         |

| t <sub>sch</sub>                 | 0.6    |                             | μs         | Start condition hold time.                                             |

| tos                              | 100    |                             | ns         | Data setup time.                                                       |

|                                  | 0.9    |                             |            | Data hold time.                                                        |

| t <sub>DH</sub>                  | 0.9    | 300                         | μs         | SCL rise time.                                                         |

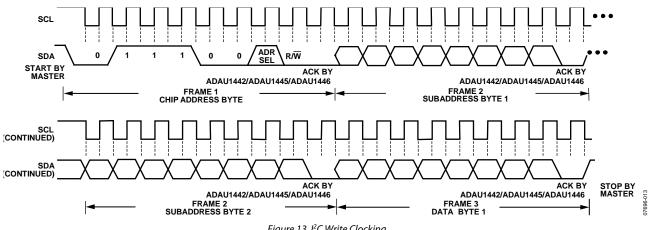

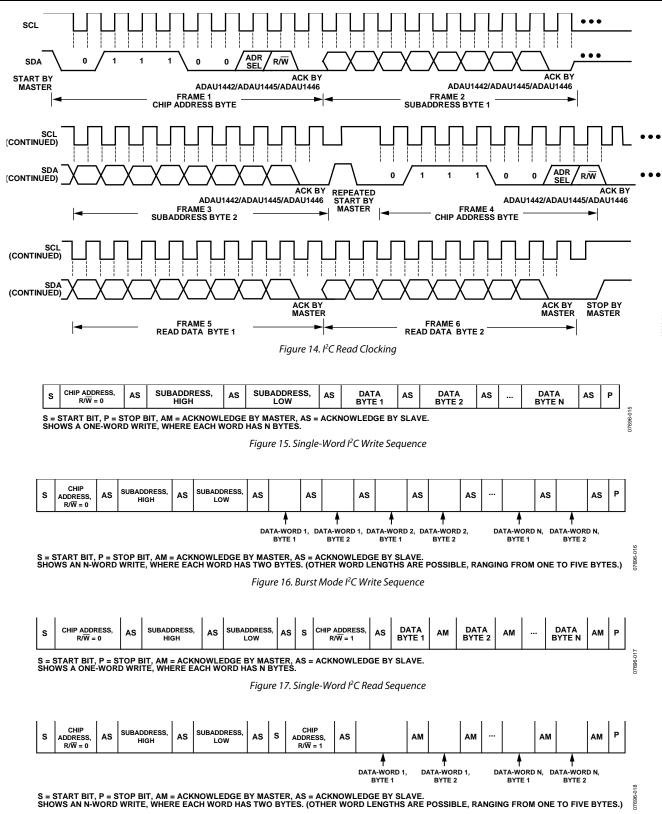

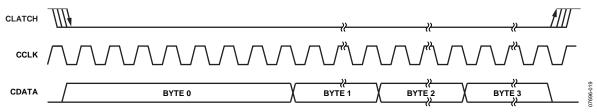

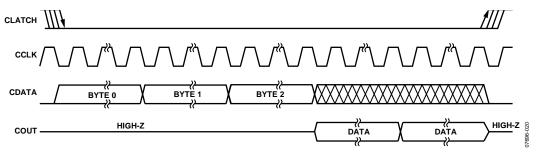

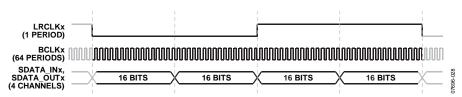

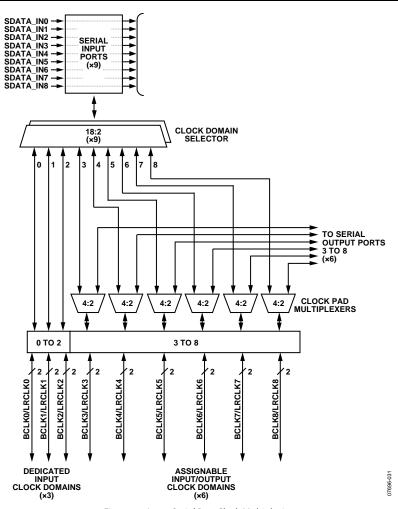

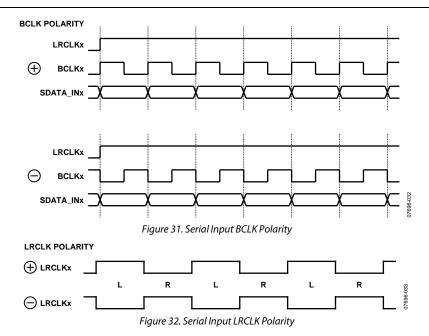

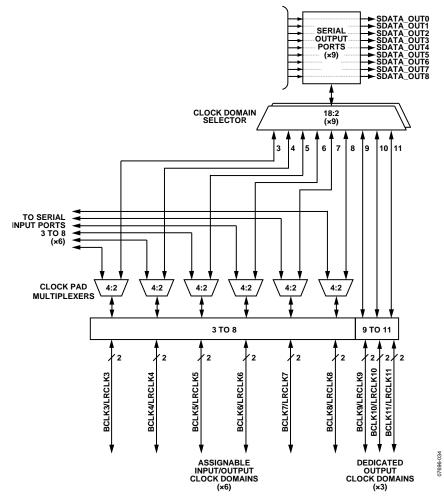

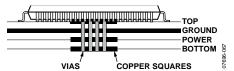

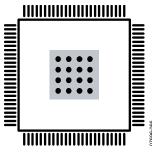

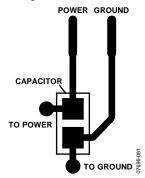

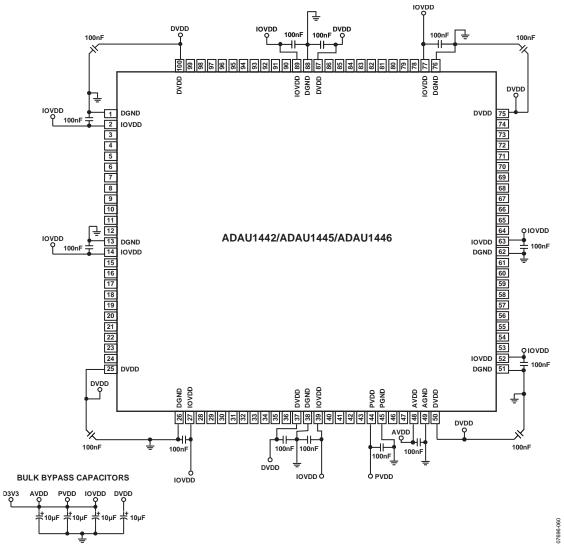

| t <sub>sclr</sub>                |        | 300                         | ns         | SCL rise time.                                                         |