# 5W+5W DUAL BRIDGE AMPLIFIER

PRELIMINARY DATA

- WIDE SUPPLY VOLTAGE RANGE (3.5 12V)

- OUTPUT POWER 5+5W @THD = 10%,  $R_L = 8\Omega$ ,  $V_{CC} = 9.5V$

- SINGLE SUPPLY

- MINIMUM EXTERNAL COMPONENTS

- NO SVR CAPACITOR

- NO BOOTSTRAP

- NO BOUCHEROT CELLS

- INTERNALLY FIXED GAIN

- STAND-BY & MUTE FUNCTIONS

- SHORT CIRCUIT PROTECTION

- THERMAL OVERLOAD PROTECTION

# PowerSO20 Slug Down ORDERING NUMBER: TDA7266D

designed for LCD TV/Monitor, PC Motherboard, TV and Portable Audio applications.

# **DESCRIPTION**

The TDA7266D is a dual bridge amplifier specially

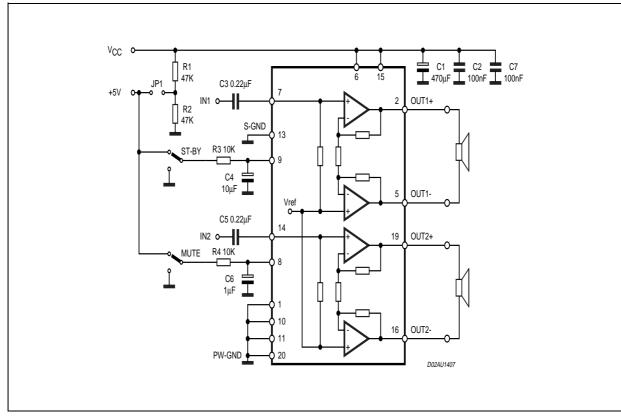

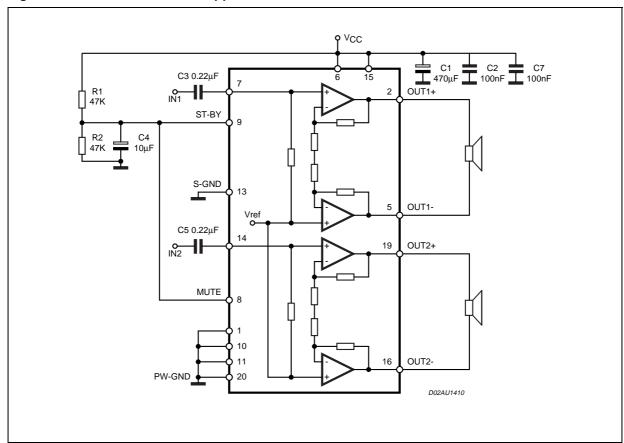

# **TEST AND APPLICATION CIRCUIT**

May 2003 1/13

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol                            | Parameter                                        | Value      | Unit |

|-----------------------------------|--------------------------------------------------|------------|------|

| Vs                                | Supply Voltage                                   | 20         | V    |

| Io                                | Output Peak Current (internally limited)         | 1.5        | А    |

| P <sub>tot</sub>                  | Total Power Dissipation (T <sub>amb</sub> = 70°C | 25         | W    |

| T <sub>op</sub>                   | Operating Temperature                            | 0 to 70    | °C   |

| T <sub>stg</sub> , T <sub>j</sub> | Storage and Junction Temperature                 | -40 to 150 | °C   |

# THERMAL DATA

| Symbol                 | Parameter                                                     | Value | Unit |

|------------------------|---------------------------------------------------------------|-------|------|

| R <sub>th j-case</sub> | Thermal Resistance Junction-case                              | 2.1   | °C/W |

| R <sub>th j-amb</sub>  | Thermal Resistance Junction-ambient (on recomended PCB) note1 | 15    | °C/W |

Notes: 1. See Application note AN668, available on WEB FR4 with 15 via holes and ground layer.

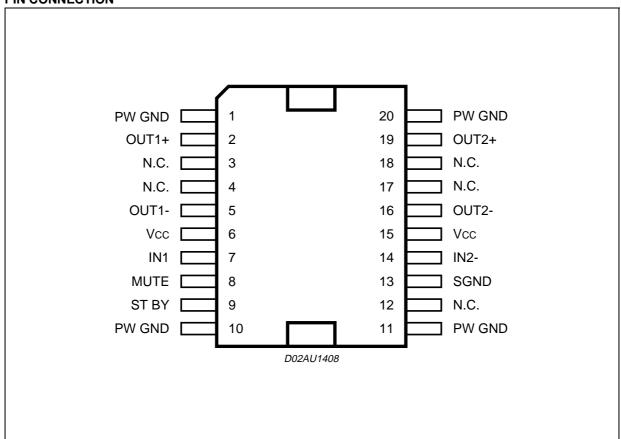

# **PIN CONNECTION**

# **ELECTRICAL CHARACTERISTCS** (Refer to test circuit) $V_{CC} = 9.5V$ , $R_L = 8\Omega$ , f = 1KHz, $T_{amb} = 25^{\circ}C$ unless otherwise specified)

| Symbol              | Parameter                 | Test Condition                                    | Min.                     | Тур.                        | Max.                       | Unit |

|---------------------|---------------------------|---------------------------------------------------|--------------------------|-----------------------------|----------------------------|------|

| V <sub>CC</sub>     | Supply Range              |                                                   | 3.5                      | 9.5                         | 12                         | V    |

| Iq                  | Total Quiescent Current   |                                                   |                          | 50                          | 60                         | mA   |

| Vos                 | Output Offset Voltage     |                                                   |                          |                             | 120                        | mV   |

| Po                  | Output Power              | THD 10%                                           | 4.3                      | 5                           |                            | W    |

| THD                 | Total Harmonic Distortion | P <sub>O</sub> = 1W                               |                          | 0.05                        | 0.2                        | %    |

|                     |                           | P <sub>O</sub> = 0.1W to 2W<br>f = 100Hz to 15KHz |                          |                             | 1                          | %    |

| SVR                 | Supply Voltage Rejection  | f = 100Hz, VR =0.5V                               | 40                       | 56                          |                            | dB   |

| СТ                  | Crosstalk                 |                                                   | 46                       | 60                          |                            | dB   |

| A <sub>MUTE</sub>   | Mute Attenuation          |                                                   | 60                       | 80                          |                            | dB   |

| T <sub>w</sub>      | Thermal Threshold         |                                                   |                          | 150                         |                            | °C   |

| G <sub>V</sub>      | Closed Loop Voltage Gain  |                                                   | 25                       | 26                          | 27                         | dB   |

| ΔG <sub>V</sub>     | Voltage Gain Matching     |                                                   |                          |                             | 0.5                        | dB   |

| Ri                  | Input Resistance          |                                                   | 25                       | 30                          |                            | ΚΩ   |

| VT <sub>MUTE</sub>  | Mute Threshold            | for $V_{CC} > 6.4V$ ; $V_{O} = -30dB$             | 2.3                      | 2.9                         | 4.1                        | V    |

|                     |                           | for V <sub>CC</sub> < 6.4V; Vo = -30dB            | V <sub>CC</sub> /2<br>-1 | V <sub>CC</sub> /2<br>-0.75 | V <sub>CC</sub> /2<br>-0.5 | V    |

| VT <sub>ST-BY</sub> | St-by Threshold           |                                                   | 0.8                      | 1.3                         | 1.8                        | V    |

| I <sub>ST-BY</sub>  | St-by Current V6 = GND    |                                                   |                          |                             | 100                        | μΑ   |

| e <sub>N</sub>      | Total Output Voltage      | A Curve                                           |                          | 150                         |                            | μV   |

#### **APPLICATIVE SUGGESTIONS**

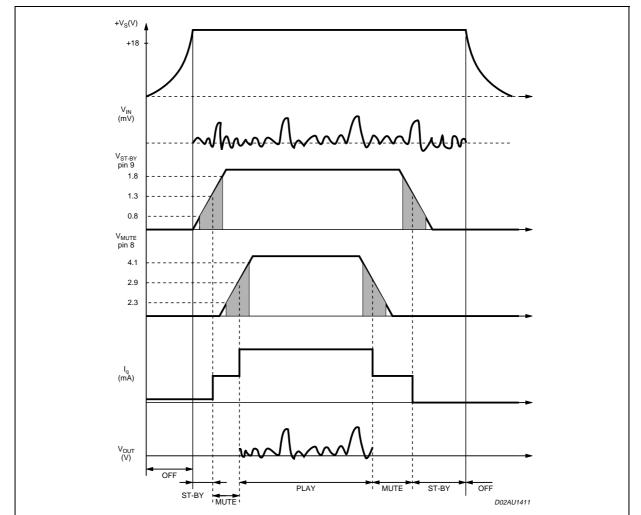

STAND-BY AND MUTE FUNCTIONS

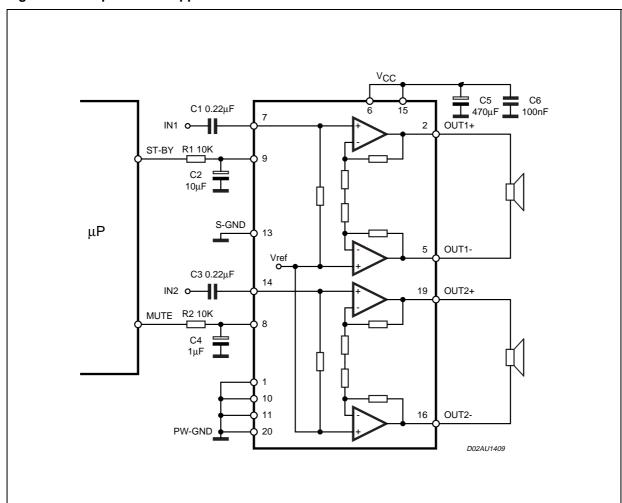

# (A) Microprocessor Application

In order to avoid annoying "Pop-Noise" during Turn-On/Off transients, it is necessary to guarantee the right Stby and mute signals sequence. It is quite simple to obtain this function using a microprocessor (Fig. 1 and 2).

At first St-by signal (from  $\mu P$ ) goes high and the voltage across the St-by terminal (Pin 9) starts to increase exponentially. The external RC network is intended to turn-on slowly the biasing circuits of the amplifier, this to avoid "POP" and "CLICK" on the outputs.

When this voltage reaches the St-by threshold level, the amplifier is switched-on and the external capacitors in series to the input terminals (C1, C3) start to charge.

It's necessary to mantain the mute signal low until the capacitors are fully charged, this to avoid that the device goes in play mode causing a loud "Pop Noise" on the speakers.

A delay of 100-200ms between St-by and mute signals is suitable for a proper operation.

Figure 1. Microprocessor Application

Figure 2. Microprocessor Driving Signals

# **B) Low Cost Application**

In low cost applications where the mP is not present, the suggested circuit is shown in fig.3.

The St-by and mute terminals are tied together and they are connected to the supply line via an external voltage divider.

The device is switched-on/off from the supply line and the external capacitor C4 is intended to delay the St-by and mute threshold exceeding, avoiding "Popping" problems.

So to avoid any popping or clicking sond, it is important to clock:

- a **Correct Sequence:** At turn-ON, the Stand-by must be removed at first, then the Mute must be released after a delay of about 100-200ms. On the contrary at turn-OFF the Mute must be activated as first and then the Stand-by.

- With the values suggested in the Application circuit the right operation is guaranteed.

- b **Correct Threshold Voltages:** In order to avoid that due to the spread in the internal thresholds (see the above limits) a wrong external voltage causes uncertain commutations for the two functions we suggest to use the following values:

Mute for Vcc>6.4V : VT = 2.3VMute for Vcc<6.4V : VT = Vcc/2 - 1Stand-by : VT = 0.8V

Figure 3. Stand-alone low-cost Application

# **PCB Layout and External Components:**

Regarding the PCB layout care must be taken for three main subjects:

- c) Signal and Power Gnd separation

- d) Dissipating Copper Area

- e) Filter Capacitors positioning

#### )Signal and Power Gnd separation:

c To the Signal GND must be referred the Audio Input Signals, the Mute and Stand-by Voltages and the device PIN.13. This Gnd path must be as clean as possible in order to improve the device THD+Noise and to avoid spurious oscillations across the speakers.

The Power GND is directly connected to the Output power Stage transistors (Emitters) and is crossed by large amount of current, this path is also used in this device to dissipate the heating generated (no needs of external heatsinker).

Referring to the typical application circuit, the separation between the two GND paths must be obtained connecting them separately (star routing) to the bulk

Electrolithic capacitor C1 (470μF).

Regarding the Power Gnd dimensioning we have to consider the Dissipated Power the Thermal Protection Threshold and the Package thermal Characteristics.

# d Dissipating Copper Area:

## **Dissipated Power:**

The max dissipated power happens for a THD near 1% and is given by the formula:

$$P_{dmax(W)} = 2 \cdot \frac{V_{CC}^{2}}{\pi^{2} \frac{RI}{2}} + I_{q}V_{CC}$$

This gives for: Vcc = 9.5V,  $RI = 8\Omega$ , Iq = 50mA a dissipated power of Pd = 5W.

#### Thermal Protection:

The thermal protection threshold is placed at a junction temperature of 150°C.

#### Package Thermal Characteristics:

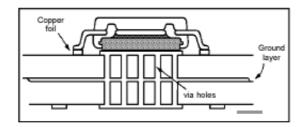

The thermal resistance Junction to Ambient obtainable with a GND copper Area of 3x3 cm and with 16 via holes (see picture) is about 15°C/W. This means that with the above mentioned max dissipated Power (Pd=5W) we can expect a 75°C, this gives a safety margin before the thermal protection intervention in the consumer environments where a 50°C ambient is specified as maximum

The Thermal constraints determine the max supply voltage that can be used for the different Load Impedances, this in order to avoid the thermal Protection Intervention.

The max. dissipated power must be not in excess of 5W, this at turns gives the following operating supply voltages:

| Load (Ohm) | Supply Voltage (V) |

|------------|--------------------|

| 4          | 6.5                |

| 6          | 8.5                |

| 8          | 9.5                |

| 16         | 14                 |

#### e Filter Capacitors Positioning:

The two Ceramic capacitors C2/C7 (100nF) must be placed as close as possible respectively to the two Vcc pins (6 - 15) in order to avoid the possibility of oscillations arising on the output Audio signals.

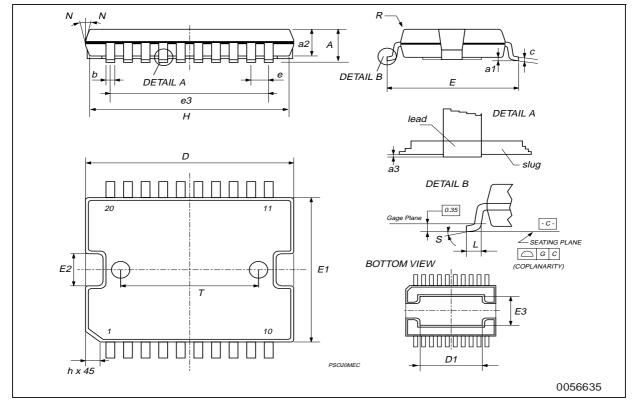

# **Package Informations:**

You can find a complete description for the PowerSO package into the APPLICATION NOTE AN668 available on web.

Here we want to focalize the attention only on the the Dissipating elements and ground layer.

47/

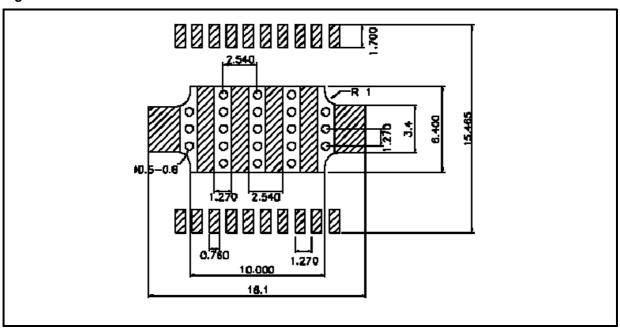

Considering the dissipated power involved in the TDA7266D application that is in the range of 5W, as explained in a previous section, we suggest via holes (see fig. 4).

Using via holes a more direct thermal path is obtained from the slug to the ground layer. The number of vias is chosen accordingly to the desired performance (in our demonstration board we use 15 vias).

In fig.4 is shown as an example the footprint to be used to create the vias.

Figure 4.

The above metioned mounting solution is enough to dissipate the power involved In the most part of the application using the TDA7266D.

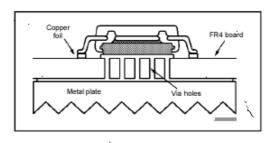

If necessary a further improvement in the Rth J-Ambient can be obtained as shown in fig.5 where the PowerSO20 is soldered onto a via hole structure with a metal plate glued on the opposite side of the board.

Figure 5. Mounting on epoxy FR4 using via Holes for heat transfer and external metal plate

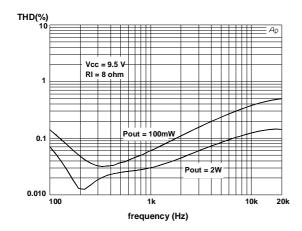

Figure 6. Distortion vs Frequency

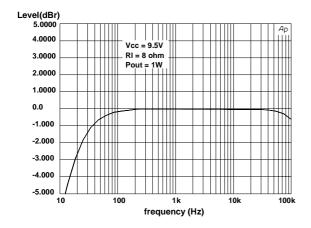

Figure 7. Gain vs Frequency

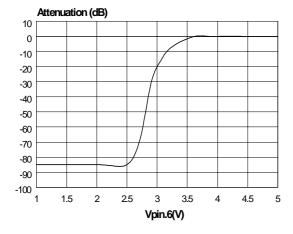

Figure 8. Mute Attenuation vs Vpin.8

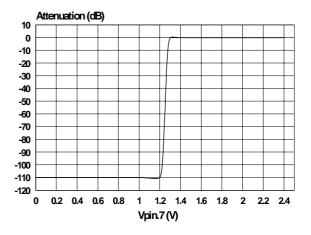

Figure 9. Stand-By attenuation vs Vpin 9

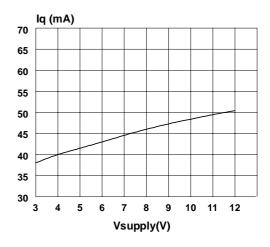

Figure 10. Quiescent Current vs Supply Voltage

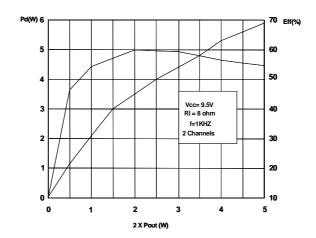

Figure 11. Total Power Dissipation & Efficiency vs Pout

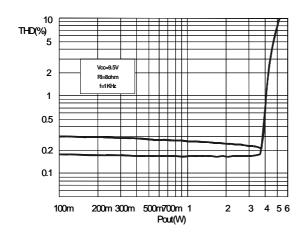

Figure 12. THD+N vs Output Power

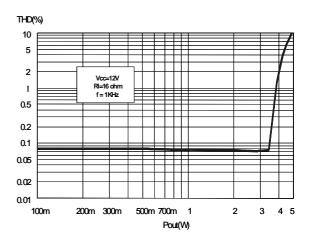

Figure 13. THD+N vs Output Power

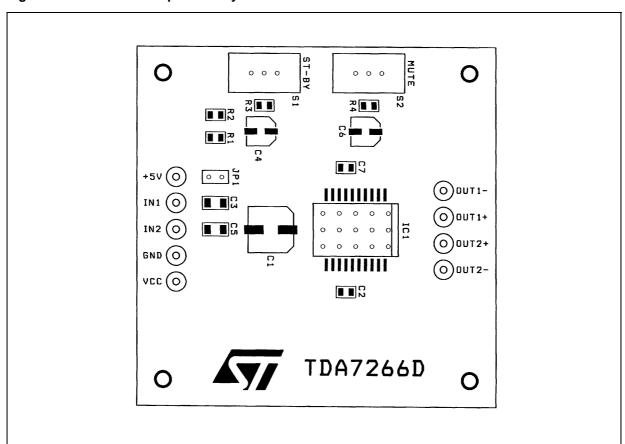

Figure 14. PC Board Component Layout

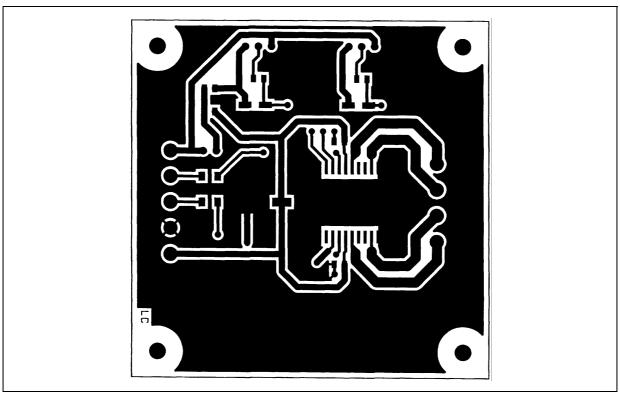

Figure 15. Evaluation Board Top Layer Layout

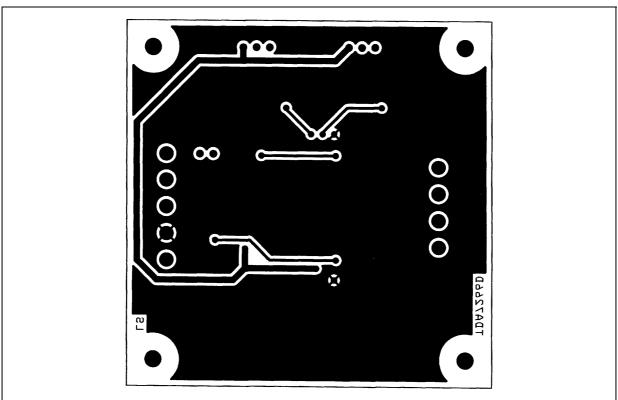

Figure 16. Evaluation Board Bottom Layer Layout

| DIM.   | mm        |       |      | inch  |       |       |

|--------|-----------|-------|------|-------|-------|-------|

| DIN.   | MIN.      | TYP.  | MAX. | MIN.  | TYP.  | MAX.  |

| Α      |           |       | 3.6  |       |       | 0.142 |

| a1     | 0.1       |       | 0.3  | 0.004 |       | 0.012 |

| a2     |           |       | 3.3  |       |       | 0.130 |

| а3     | 0         |       | 0.1  | 0.000 |       | 0.004 |

| b      | 0.4       |       | 0.53 | 0.016 |       | 0.021 |

| С      | 0.23      |       | 0.32 | 0.009 |       | 0.013 |

| D (1)  | 15.8      |       | 16   | 0.622 |       | 0.630 |

| D1     | 9.4       |       | 9.8  | 0.370 |       | 0.386 |

| Е      | 13.9      |       | 14.5 | 0.547 |       | 0.570 |

| е      |           | 1.27  |      |       | 0.050 |       |

| e3     |           | 11.43 |      |       | 0.450 |       |

| E1 (1) | 10.9      |       | 11.1 | 0.429 |       | 0.437 |

| E2     |           |       | 2.9  |       |       | 0.114 |

| E3     | 5.8       |       | 6.2  | 0.228 |       | 0.244 |

| G      | 0         |       | 0.1  | 0.000 |       | 0.004 |

| Н      | 15.5      |       | 15.9 | 0.610 |       | 0.626 |

| h      |           |       | 1.1  |       |       | 0.043 |

| L      | 0.8       |       | 1.1  | 0.031 |       | 0.043 |

| N      | 8° (typ.) |       |      |       |       |       |

| S      | 8° (max.) |       |      |       |       |       |

| Т      |           | 10    |      |       | 0.394 |       |

- (1) "D and E1" do not include mold flash or protusions.

Mold flash or protusions shall not exceed 0.15mm (0.006")

Critical dimensions: "E", "G" and "a3".

# **OUTLINE AND MECHANICAL DATA**

47/ 12/13

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics © 2003 STMicroelectronics - All Rights Reserved

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.

http://www.st.com

47/