# **Intel® Cyclone® 10 LP Device Overview**

C10LP51001 | 2019.12.30 Latest document on the web: PDF | HTML

## **Contents**

| Intel® Cyclone® 10 LP Device Overview                             | 3  |

|-------------------------------------------------------------------|----|

| Summary of Intel Cyclone 10 LP Features                           |    |

| Intel Cyclone 10 LP Available Options                             |    |

| Intel Cyclone 10 LP Maximum Resources                             |    |

| Intel Cyclone 10 LP Package Plan                                  | 6  |

| Intel Cyclone 10 LP I/O Vertical Migration                        |    |

| Logic Elements and Logic Array Blocks                             |    |

| Embedded Multipliers                                              | 8  |

| Embedded Memory Blocks                                            | 8  |

| Clocking and PLL                                                  | 8  |

| FPGA General Purpose I/O                                          |    |

| Configuration                                                     |    |

| Power Management                                                  | 10 |

| Document Revision History for Intel Cyclone 10 LP Device Overview | 10 |

## Intel® Cyclone® 10 LP Device Overview

The Intel® Intel Cyclone® 10 LP FPGAs are optimized for low cost and low static power, making them ideal for high-volume and cost-sensitive applications.

Intel Cyclone 10 LP devices provide a high density sea of programmable gates, on-board resources, and general purpose I/Os. These resources satisfies the requirements of I/O expansion and chip-to-chip interfacing. The Intel Cyclone 10 LP architecture suits smart and connected end applications across many market segments:

- · Industrial and automotive

- Broadcast, wireline, and wireless

- Compute and storage

- Government, military, and aerospace

- Medical, consumer, and smart energy

The free but powerful Intel Quartus<sup>®</sup> Prime Lite Edition software suite of design tools meets the requirements of several classes of users:

- Existing FPGA designers

- Embedded designers using the FPGA with Nios® II processor

- Students and hobbyists who are new to FPGA

Advanced users who require access to the full IP Base Suite can subscribe to the Intel Quartus Prime Standard Edition or purchase the license separately.

#### **Related Information**

- Software Development Tools, Nios II Processor

Provides more information about the Nios II 32-bit soft IP processor and Embedded Design Suite (EDS).

- Intel Quartus Prime IP Base Suite

- Intel Quartus Prime Editions

## **Summary of Intel Cyclone 10 LP Features**

### Table 1. Summary of Features for Intel Cyclone 10 LP Devices

| Feature                         | Description                                                                                                                                                                                                                                                                             |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Technology                      | <ul> <li>Low-cost, low-power FPGA fabric</li> <li>1.0 V and 1.2 V core voltage options</li> <li>Available in commercial, industrial, and automotive temperature grades</li> </ul>                                                                                                       |

| Packaging                       | Several package types and footprints:         — FineLine BGA (FBGA)         — Enhanced Thin Quad Flat Pack (EQFP)         — Ultra FineLine BGA (UBGA)         — Micro FineLine BGA (MBGA)          • Multiple device densities with pin migration capability         • RoHS6 compliance |

| Core architecture               | <ul> <li>Logic elements (LEs)—four-input look-up table (LUT) and register</li> <li>Abundant routing/metal interconnect between all LEs</li> </ul>                                                                                                                                       |

| Internal memory blocks          | <ul> <li>M9K—9-kilobits (Kb) of embedded SRAM memory blocks, cascadable</li> <li>Configurable as RAM (single-port, simple dual port, or true dual port), FIFO buffers, or ROM</li> </ul>                                                                                                |

| Embedded multiplier blocks      | One 18 × 18 or two 9 × 9 multiplier modes, cascadable     Complete suite of DSP IPs for algorithmic acceleration                                                                                                                                                                        |

| Clock networks                  | <ul> <li>Global clocks that drive throughout entire device, feeding all device quadrants</li> <li>Up to 15 dedicated clock pins that can drive up to 20 global clocks</li> </ul>                                                                                                        |

| Phase-locked loops<br>(PLLs)    | Up to four general purpose PLLs     Provides robust clock management and synthesis                                                                                                                                                                                                      |

| General-purpose I/Os<br>(GPIOs) | Multiple I/O standards support     Programmable I/O features     True LVDS and emulated LVDS transmitters and receivers     On-chip termination (OCT)                                                                                                                                   |

| SEU mitigation                  | SEU detection during configuration and operation                                                                                                                                                                                                                                        |

| Configuration                   | <ul> <li>Active serial (AS), passive serial (PS), fast passive parallel (FPP)</li> <li>JTAG configuration scheme</li> <li>Configuration data decompression</li> <li>Remote system upgrade</li> </ul>                                                                                    |

#### **Intel Cyclone 10 LP Available Options**

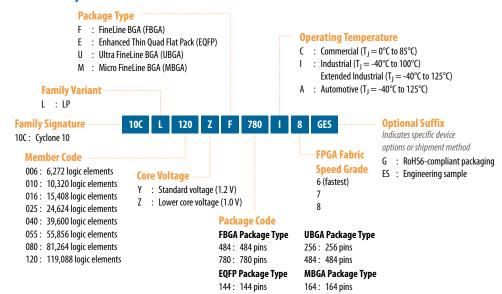

# Figure 1. Sample Ordering Code and Available Options for Intel Cyclone 10 LP Devices —Preliminary

#### **Related Information**

#### Extended Temperature Device Support

Lists the ordering part number of devices that support the extended industrial operating temperature, the devices' operational speed grade, and Intel Quartus Prime option to set for performing timing analysis at the extended junction temperature range.

## **Intel Cyclone 10 LP Maximum Resources**

Table 2.

Maximum Resource Counts for Intel Cyclone 10 LP Devices

| Danassina    |                  |         |         |         | Des     |         |         |         |         |  |  |  |

|--------------|------------------|---------|---------|---------|---------|---------|---------|---------|---------|--|--|--|

| Resource     |                  |         | Device  |         |         |         |         |         |         |  |  |  |

|              |                  | 10CL006 | 10CL010 | 10CL016 | 10CL025 | 10CL040 | 10CL055 | 10CL080 | 10CL120 |  |  |  |

| Logic Elem   | ents (LE)        | 6,272   | 10,320  | 15,408  | 24,624  | 39,600  | 55,856  | 81,264  | 119,088 |  |  |  |

| M9K          | Block            | 30      | 46      | 56      | 66      | 126     | 260     | 305     | 432     |  |  |  |

| Memory       | Capacity<br>(Kb) | 270     | 414     | 504     | 594     | 1,134   | 2,340   | 2,745   | 3,888   |  |  |  |

| 18 × 18 M    | ultiplier        | 15      | 23      | 56      | 66      | 126     | 156     | 244     | 288     |  |  |  |

| PLL          |                  | 2       | 2       | 4       | 4       | 4       | 4       | 4       | 4       |  |  |  |

| Clock        |                  | 20      | 20      | 20      | 20      | 20      | 20      | 20      | 20      |  |  |  |

| Maximum      | I/O              | 176     | 176     | 340     | 150     | 325     | 321     | 423     | 525     |  |  |  |

| Maximum LVDS |                  | 65      | 65      | 137     | 52      | 124     | 132     | 178     | 230     |  |  |  |

# **Intel Cyclone 10 LP Package Plan**

Table 3. Package Plan for Intel Cyclone 10 LP Devices

| Device |                           | Package |        |            |               |              |               |            |              |            |               |            |               |  |

|--------|---------------------------|---------|--------|------------|---------------|--------------|---------------|------------|--------------|------------|---------------|------------|---------------|--|

|        | Type M164<br>164-pin MBGA |         | Туре   |            | U2<br>256-pir | 56<br>1 UBGA | U4<br>484-pir |            | E1<br>144-pi |            | F4<br>484-pii |            | F7<br>780-pii |  |

|        | Size                      | 8 mm >  | < 8 mm | 14 mn<br>m |               | 19 mn<br>m   |               | 22 mn<br>m |              | 23 mn<br>m |               | 29 mn<br>m |               |  |

|        | Ball<br>Pitch             | 0.5     | mm     | 0.8        | mm            | 0.8          | mm            | 0.5        | mm           | 1.0        | mm            | 1.0        | mm            |  |

|        | I/O<br>Type               | GPIO    | LVDS   | GPIO       | LVDS          | GPIO         | LVDS          | GPIO       | LVDS         | GPIO       | LVDS          | GPIO       | LVDS          |  |

| 10CL   | .006                      | _       | _      | 176        | 65            | _            | _             | 88         | 22           | _          | _             | _          | _             |  |

| 10CL   | .010                      | 101     | 26     | 176        | 65            | _            | _             | 88         | 22           | _          | _             | _          | _             |  |

| 10CL   | .016                      | 87      | 22     | 162        | 53            | 340          | 137           | 78         | 19           | 340        | 137           | _          | _             |  |

| 10CL   | .025                      | _       | _      | 150        | 52            | _            | _             | 76         | 18           | _          | _             | _          | _             |  |

| 10CL   | .040                      | _       | _      | _          | _             | 325          | 124           | _          | _            | 325        | 124           | _          | _             |  |

| 10CL   | .055                      | _       | _      | _          | _             | 321          | 132           | _          | _            | 321        | 132           | _          | _             |  |

| 10CL   | .080                      |         |        |            | _             | 289          | 110           |            | _            | 289        | 110           | 423        | 178           |  |

| 10CL   | .120                      | _       | _      | _          | _             | _            | _             | _          | _            | 277        | 103           | 525        | 230           |  |

### **Intel Cyclone 10 LP I/O Vertical Migration**

#### Figure 2. Migration Capability Across Intel Cyclone 10 LP Devices

- The arrows indicate the migration paths. The devices included in each vertical migration path are shaded. Devices with lesser I/O resources in the same path have lighter shades.

- To achieve full I/O migration across devices in the same migration path, restrict I/O usage to match the device with the lowest I/O count.

| D. t.   | Package  |         |      |          |      |         |  |  |  |

|---------|----------|---------|------|----------|------|---------|--|--|--|

| Device  | M164     | U256    | U484 | E144     | F484 | F780    |  |  |  |

| 10CL006 |          | <b></b> |      | <b></b>  |      |         |  |  |  |

| 10CL010 | <b>A</b> |         |      |          |      |         |  |  |  |

| 10CL016 | •        |         |      |          |      |         |  |  |  |

| 10CL025 |          | •       |      | <b>*</b> |      |         |  |  |  |

| 10CL040 |          | ,       |      |          |      |         |  |  |  |

| 10CL055 |          |         |      |          |      |         |  |  |  |

| 10CL080 |          |         | •    |          |      | <b></b> |  |  |  |

| 10CL120 |          |         |      |          | •    |         |  |  |  |

Note: To verify the pin migration compatibility, use the Pin Migration View window in the Intel Quartus Prime software Pin Planner.

## **Logic Elements and Logic Array Blocks**

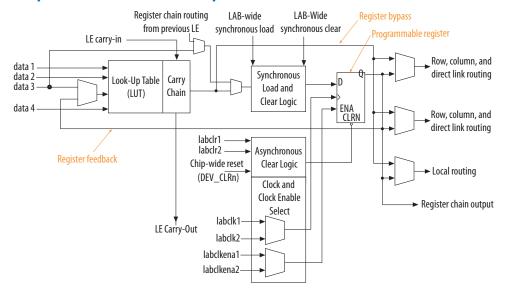

The LAB consists of 16 logic elements (LE) and a LAB-wide control block. An LE is the smallest unit of logic in the Intel Cyclone 10 LP device architecture. Each LE has four inputs, a four-input look-up table (LUT), a register, and output logic. The four-input LUT is a function generator that can implement any function with four variables.

Figure 3. Intel Cyclone 10 LP Device Family LEs

#### **Embedded Multipliers**

Each embedded multiplier block in Intel Cyclone 10 LP devices supports one individual  $18 \times 18$ -bit multiplier or two individual  $9 \times 9$ -bit multipliers. You can cascade the multiplier blocks to form wider or deeper logic structures.

You can control the operation of the embedded multiplier blocks using the following options:

- Parameterize the relevant IP cores with the Intel Quartus Prime parameter editor

- Infer the multipliers directly with VHDL or Verilog HDL

Intel and partners offer popular DSP IPs for Intel Cyclone 10 LP devices, including:

- Finite impulse response (FIR)

- Fast Fourier transform (FFT)

- Numerically controlled oscillator (NCO) functions

For a streamlined DSP design flow, the DSP Builder tool integrates the Intel Quartus Prime software with MathWorks Simulink and MATLAB design environments.

### **Embedded Memory Blocks**

The embedded memory structure consists of M9K memory blocks columns. Each M9K memory block of a Intel Cyclone 10 LP device provides 9 Kb of on-chip memory. You can cascade the memory blocks to form wider or deeper logic structures.

You can configure the M9K memory blocks as RAM, FIFO buffers, or ROM.

Table 4. M9K Operation Modes and Port Widths

| Operation Modes  | Port Widths                                |

|------------------|--------------------------------------------|

| Single port      | ×1, ×2, ×4, ×8, ×9, ×16, ×18, ×32, and ×36 |

| Simple dual port | ×1, ×2, ×4, ×8, ×9, ×16, ×18, ×32, and ×36 |

| True dual port   | ×1, ×2, ×4, ×8, ×9, ×16, and ×18           |

#### **Clocking and PLL**

Intel Cyclone 10 LP devices feature global clock (GCLK) networks, dedicated clock pins, and general purpose PLLs.

- Up to 20 GCLK networks that drive throughout the device

- Up to 15 dedicated clock pins

- Up to four general purpose PLLs with five outputs per PLL

The PLLs provide robust clock management and synthesis for the Intel Cyclone 10 LP device. You can dynamically reconfigure the PLLs in user mode to change the clock phase or frequency.

#### FPGA General Purpose I/O

Intel Cyclone 10 LP devices offer highly configurable GPIOs with these features:

- Support for over 20 popular single-ended and differential I/O standards.

- Programmable bus hold, pull-up resistors, delay, and drive strength.

- Programmable slew rate control to optimize signal integrity.

- Calibrated on-chip series termination (R<sub>S</sub> OCT) or driver impedance matching (R<sub>S</sub>) for single-endd I/O standards.

- True and emulated LVDS buffers with LVDS SERDES implemented using logic elements in the device core.

- Hot socketing support.

## **Configuration**

Intel Cyclone 10 LP devices use SRAM cells to store configuration data. Configuration data is downloaded to the Intel Cyclone 10 LP device each time the device powers up.

You can use EPCS or EPCQ (AS x1) flash configuration devices to store configuration data and configure the Intel Cyclone 10 LP FPGAs.

- Intel Cyclone 10 LP devices support 1.5 V, 1.8 V, 2.5 V, 3.0 V, and 3.3 V programming voltages and several configuration schemes.

- The single-event upset (SEU) mitigation feature detects cyclic redundancy check (CRC) errors automatically during configuration and optionally during user mode<sup>(1)</sup>.

Table 5. Configuration Schemes and Features Supported by Intel Cyclone 10 LP

Devices

| Configuration Scheme        | Configuration Method            | Decompression | Remote System<br>Upgrade |  |

|-----------------------------|---------------------------------|---------------|--------------------------|--|

| Active serial (AS)          | Serial configuration device     | Yes           | Yes                      |  |

| Passive serial (PS)         | External host with flash memory | Yes           | Yes                      |  |

|                             | Download cable                  | Yes           | _                        |  |

| Fast passive parallel (FPP) | External host with flash memory | _             | Yes                      |  |

| JTAG                        | External host with flash memory | _             | _                        |  |

|                             | Download cable                  | _             | _                        |  |

#### **Related Information**

Configuration Devices

Provides more information about the EPCS and EPCQ configuration devices.

<sup>(1)</sup> User mode error detection is not supported on 1.0 V core voltage Intel Cyclone 10 LP device variants.

#### **Power Management**

Intel Cyclone 10 LP devices are built on optimized low-power process:

- Available in two core voltage options: 1.2 V and 1.0 V

- Hot socketing compliant without needing external components or special design requirements

To accelerate your design schedule, combine Intel Intel Cyclone 10 LP FPGAs with Intel Enpirion® Power Solutions. Intel's ultra-compact and efficient Intel Enpirion PowerSoCs are ideal for meeting Intel Cyclone 10 LP power requirements. Intel Enpirion PowerSoCs integrate most of the required components to provide you fully-validated and straightforward solutions with up to 96% efficiency. These advantages reduce your power supply design time and allow you to focus on your IP and FPGA designs.

#### **Related Information**

**Enpirion Power Solutions**

Provides more information about Enpirion PowerSoC devices.

#### **Document Revision History for Intel Cyclone 10 LP Device Overview**

| Document<br>Version | Changes                                                                                                                                                                                                                                                         |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2019.12.30          | Added related information link to the <i>Extended Temperature Device Support</i> page that provides a list of devices that support the extended temperature range, their operational speed grade, and related Intel Quartus Prime settings for timing analysis. |

| Date     | Version    | Changes          |

|----------|------------|------------------|

| May 2017 | 2017.05.08 | Initial release. |

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

#### Intel:

```

10CL016YF484C8G

10CL016YU256C8G

10CL016YE144I7G

10CL016YU256C6G

10CL016YM164C8G

10CL016YE144C6G

10CL016YM164C8G

10CL016YU256I7G

10CL016YF484I7G

10CL016YE144C8G

10CL016YM164I7G

10CL016YF484C6G

10CL016YU484C6G

10CL016YU484C8G

10CL016YU484C8G

10CL010YU256C8G

10CL025YE144C6G

10CL055YF484C8G

10CL006YE144C6G

10CL025YU256C6G

10CL025YU256C8G

10CL035YF484I7G

10CL010YM164C8G

10CL010YE144C8G

10CL010YU256C6G

10CL055YF484C6G

10CL055YF484C6G

10CL040YU484I7G

10CL040YF484C6G

10CL010YF780C8G

10CL010YF780I7G

10CL010YM164C6G

10CL080YF780I7G

10CL040YU484C6G

10CL006YE144I7G

10CL040YF484C8G

10CL010YM164I7G

10CL040YU484C8G

10CL010YW1256I7G

10CL010YW164C8G

10CL010YW164C8G

10CL010YW164C8G

10CL006YU256I7G

10CL010YF780C8G

10CL025YU256I7G

10CL055YU484C8G

10CL006YU256A7G

10CL010YW164A7G

10CL010YW164A7G

10CL010YU256A7G

10CL016YE144A7G

10CL006YU256A7G

10CL016YM164A7G

10CL016YU256A7G

10CL016YU484A7G

10CL025YE144A7G</

```