### Dual-Channel Synchronous Buck, High-Brightness LED Controller with and without SPI Interface

#### **General Description**

The MAX20096/MAX20097 are dual-channel, high-voltage, synchronous n-channel high-current buck LED drivers. The ICs use a proprietary average current-mode-control scheme to regulate the inductor current. This control method does not require any control-loop compensation, maintaining nearly constant switching frequency. Inductor current sense is achieved by sensing the current in the bottom switching device. The ICs integrate two fully synchronous buck-converter controllers, and operate over a wide 4.5V to 65V input range. The ICs are designed for high-frequency operation and can operate at switching frequencies as high as 1MHz.

In the MAX20096, the output voltages and currents on both channels and the junction temperature can be read back through the SPI interface. Protection features include inductor current-limit protection, overvoltage protection, and thermal shutdown. The MAX20096 is available in a space-saving thermally enhanced (5mm x 5mm), 32-pin side-wettable TQFN package and is specified to operate over the -40°C to +125°C automotive temperature range.

The MAX20097 is available in a 28-pin thermally enhanced TSSOP package, but does not have the SPI interface. It includes an open-drain fault flag (FLTB) that goes low in case of an open string, shorted string, or overvoltage activation in any one of the channels, or also in thermal shutdown.

#### **Applications**

- · Automotive Exterior Lighting

- · High-Beam/Low-Beam/Signal/Position Lights

- Daytime Running Lights (DRLs)

- · Fog Light and Adaptive Front Light Assemblies

- · Commercial, Industrial, and Architectural Lighting

#### **Benefits and Features**

- Integration Minimizes BOM for High-Brightness LED Driver, Saving Space and Cost

- Wide 4.5V to 65V Input Voltage Range

- · No Compensation Components

- Programmable Switching Frequency

- External MOSFETs that are Sizable for the Appropriate Current

- Wide Dimming Ratio Allows High-Contrast Ratio

- · Analog Dimming

- PWM Dimming

- Suitable for Matrix Lighting

- Maintains Current Regulation While Shorting/ Opening Individual LEDs in the String

- Ultra-Fast Response Control Loop Prevents Overshoots and Undershoots

- Protection Features and Wide Temperature Range Increase System Reliability

- Short Circuit, Overvoltage, and Thermal Protection

- -40°C to +125°C Operating Temperature Range

- Thermal Monitor and LED Current Monitor

- Fault Diagnosis Through SPI Interface and Through FLTB Pin for Applications without SPI Interface

Ordering Information appears at end of data sheet.

### **Absolute Maximum Ratings**

| V <sub>IN</sub> to V <sub>AGND</sub> 0.3V to +70V                                                                                              | Short-Circuit Current on V <sub>CC</sub> Continuous      |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| V <sub>LX</sub> to V <sub>AGND</sub> 0.3V to (V <sub>IN</sub> + 0.3)V                                                                          | Continuous Power Dissipation (Multilayer Board)          |

| V <sub>CSN</sub> , V <sub>CSP</sub> to V <sub>AGND</sub> 2.5V to +6V                                                                           | 32-Pin SW TQFN (T <sub>A</sub> = +70°C, derate 34.5mW/°C |

| $V_{CC}$ , $\overline{V}_{IO}$ to $\overline{V}_{AGND}$ 0.3V to +6.0V                                                                          | above +70°C)2758.6mW                                     |

| V <sub>BST</sub> to V <sub>AGND</sub> 0.3V to +72.0V                                                                                           | Continuous Power Dissipation (Multilayer Board)          |

| V <sub>BST</sub> to V <sub>LX</sub> 0.3V to +6.0V                                                                                              | 28-Pin TSSOP (T <sub>A</sub> = +70°C, derate 29.7mW/°C   |

| V <sub>TON</sub> to V <sub>AGND</sub> 0.3V to +65V                                                                                             | above +70°C) mW to 2380mW                                |

| V <sub>PGND</sub> to V <sub>AGND</sub> 0.3V to +0.3V                                                                                           | Operating Temperature Range40°C to +125°C                |

| V <sub>REFI</sub> to V <sub>AGND</sub> 0.3V to +2.5V                                                                                           | Junction Temperature+150°C                               |

| V <sub>DIM</sub> to V <sub>AGND</sub> 0.3V to +6.0V                                                                                            | Storage Temperature Range40°C to +150°C                  |

| $V_{OUT}$ , $V_{CSB}$ , $V_{SCLK}$ , $V_{SDI}$ , $V_{RESETB}$ to $V_{AGND}$ -0.3V to +6.0V, $V_{SDO}$ to $V_{AGND}$ 0.3V to ( $V_{IO}$ + 0.3)V | Soldering Temperature (reflow)+260°C                     |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Thermal Characteristics (Note 1)**

| 32-Pin SW TQFN                                                  |

|-----------------------------------------------------------------|

| Thermal Resistance, Single-Layer Board:                         |

| Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> )47°C/W |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> )3°C/W     |

| Thermal Resistance, Four-Layer Board:                           |

| Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> )36°C/W |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )3°C/W      |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

#### **Electrical Characteristics**

$(V_{IN} = 12V, Limits are 100\% tested at T_A = +25^{\circ}C and T_A = +125^{\circ}C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)$

| PARAMETER                                        | SYMBOL               | CONDITIONS                                           | MIN   | TYP  | MAX   | UNITS |

|--------------------------------------------------|----------------------|------------------------------------------------------|-------|------|-------|-------|

| INPUT SUPPLY VOLTAGE                             |                      |                                                      |       |      |       |       |

| Operational Supply Voltage                       | V <sub>IN</sub>      |                                                      | 4.5   |      | 65    | V     |

| IN Supply Current                                | I <sub>INQ</sub>     | DIM1 = DIM2 = 5V                                     |       |      | 10    | mA    |

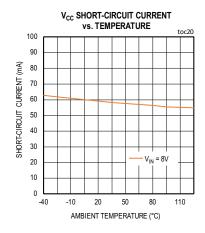

| V <sub>CC</sub> REGULATOR                        |                      |                                                      |       |      |       |       |

| Otm., t \ /= t====                               | \/                   | I <sub>VCC</sub> = 1mA, 5.5V < V <sub>IN</sub> < 65V | 4.875 | 5.0  | 5.125 | V     |

| Output Voltage                                   | V <sub>CC</sub>      | I <sub>VCC</sub> = 10mA, 6V < V <sub>IN</sub> < 25V  | 4.875 | 5.0  | 5.125 |       |

| V <sub>CC</sub> Dropout Voltage                  |                      | I <sub>VCC</sub> = 10mA, V <sub>IN1</sub> = 4.5V     |       | 200  | 500   | mV    |

| V <sub>CC</sub> Short-Circuit Current            | VCC <sub>IMAX</sub>  | V <sub>CC</sub> = 0V                                 |       | 60   |       | mA    |

| V <sub>CC</sub> Undervoltage Lockout,<br>Rising  | VCC <sub>UVLOR</sub> | I <sub>NS</sub> rising                               | 3.8   | 4.1  | 4.4   | V     |

| V <sub>CC</sub> Undervoltage Lockout,<br>Falling | VCC <sub>UVLOF</sub> | I <sub>NS</sub> falling                              | 3.55  | 3.85 | 4.15  | V     |

### **Electrical Characteristics (continued)**

$(V_{IN} = 12V, Limits are 100\% tested at T_A = +25^{\circ}C and T_A = +125^{\circ}C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)$

| PARAMETER                                                | SYMBOL                | CONDITIONS                                                                 | MIN   | TYP   | MAX   | UNITS |

|----------------------------------------------------------|-----------------------|----------------------------------------------------------------------------|-------|-------|-------|-------|

| ANALOG DIMMING INPUT                                     |                       |                                                                            |       |       |       |       |

| REFI Input Voltage Range<br>(Fail-Safe Mode)             | REFIRNG               | RESETB = 0 or RESETB = 1 with CNFG_<br>SEL = 0                             | 0.2   |       | 1.2   | V     |

| REFI Zero-Current Threshold,<br>Falling (Fail-Safe Mode) | REFI <sub>ZC_TH</sub> | RESETB = 0 or RESETB = 1 with CNFG_<br>SEL = 0, CS < 5mV                   | 0.165 | 0.18  | 0.195 | V     |

| Zero-Current Threshold, Falling (SPI Enabled)            |                       |                                                                            |       | 0.176 |       | А     |

| REFI Clamp Voltage                                       | REFI <sub>CLMP</sub>  | RESETB = 0 or RESETB = 1 with CNFG_<br>SEL = 0, IREFI sink = 1µA           | 1.274 | 1.3   | 1.326 | V     |

| REFI Input Bias Current                                  | REFI <sub>IN</sub>    | RESETB = 0 or RESETB = 1 with CNFG_<br>SEL = 0                             | 0     | 20    | 200   | nA    |

| ON-TIME CONTROL/OVERVO                                   | LTAGE PRO             | TECTION/SHORT FAULT INDICATOR                                              |       |       |       |       |

| Minimum On-Time                                          | t <sub>ON-MIN</sub>   |                                                                            |       | 60    | 100   | ns    |

| Programmed On-Time                                       | ton                   | $V_{OUT}$ = 1V, C1 = C4 = 1nF, R1 = R4 = 24.9k $\Omega$ , $V_{IN}$ = 12V   |       | 2.27  |       | μs    |

| TON_ Pulldown Resistance                                 |                       |                                                                            |       | 15    | 40    | Ω     |

| OUT_ Overvoltage Threshold                               | V <sub>TH_OVP</sub> _ | OUT rising, RESETB = 0 or RESETB = 1 and SPI_EN = 0                        | 2.45  | 2.5   | 2.55  | V     |

| OUT_ Overvoltage Hysteresis                              |                       | OUT_ falling                                                               |       | 22    |       | mV    |

|                                                          |                       | Output failing, V <sub>OUT</sub> _ is lower than threshold, no SPI         |       | 50    |       |       |

| Short Fault Threshold                                    |                       | SPI enabled, V_SHORT_[1:0] = b'00, V_OUT_ is lower than threshold          |       | 100   |       | mV    |

|                                                          |                       | SPI enabled, V_SHORT_[1:0] = 11, V <sub>OUT</sub> _is lower than threshold |       | 400   |       |       |

| OFF-TIME CONTROL                                         |                       |                                                                            |       |       |       |       |

| Minimum Off-Time                                         |                       | V <sub>CS</sub> _ = 0V                                                     |       | 160   | 280   | ns    |

| Linear Range of Pulse Doubler                            |                       |                                                                            | 0.25  |       | 2.5   | μs    |

| Maximum Off-Time                                         |                       |                                                                            |       | 42    |       | μs    |

| PWM DIMMING (FAIL-SAFE M                                 | IODE)                 |                                                                            |       |       |       |       |

| Internal Ramp Frequency                                  | f <sub>RAMP</sub>     |                                                                            | 180   | 200   | 220   | Hz    |

| Phase Shift Between DIM1 and DIM2                        | P <sub>SFT</sub>      | Fail-safe mode using internal 200Hz dimming                                |       | 180   |       | deg   |

| External Sync Frequency<br>Range                         |                       |                                                                            | 80    |       | 2000  | Hz    |

| External Sync Low-Level<br>Voltage                       | V <sub>LTH</sub>      |                                                                            | 0.4   |       |       | V     |

| External Sync High-Level<br>Voltage                      | V <sub>HTH</sub>      |                                                                            |       |       | 3.2   | V     |

### **Electrical Characteristics (continued)**

$(V_{IN} = 12V, Limits are 100\% tested at T_A = +25^{\circ}C$  and  $T_A = +125^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                          | SYMBOL               | CONDITIONS                                                          | MIN   | TYP  | MAX   | UNITS |

|------------------------------------|----------------------|---------------------------------------------------------------------|-------|------|-------|-------|

| DIM Comparator Offset Voltage      |                      |                                                                     | 170   | 200  | 230   | mV    |

| DIM Voltage for 100% Duty<br>Cycle |                      |                                                                     | 3.2   |      |       | V     |

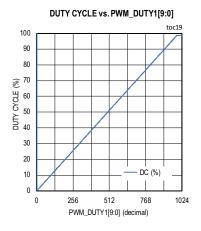

| PWM DIMMING (SPI CONTRO            | LLED)                |                                                                     |       |      |       |       |

|                                    |                      | SPI enabled with PWM1_SEL = PWM2_<br>SEL = 1, PWM_FREQ[2:0] = 0     |       | 200  |       |       |

| Programmed Dimming Frequency       |                      | SPI enabled with PWM1_SEL = PWM2_<br>SEL = 1, PWM_FREQ[2:0] = 110   |       | 2000 |       | Hz    |

|                                    |                      | SPI enabled with PWM1_SEL = PWM2_<br>SEL = 1, PWM_FREQ[2:0] = 001   |       | 333  |       |       |

|                                    |                      | SPI is enabled, PWM1_SEL = PWM2_SEL = 1, PWM_DUTY[9:0] = 1LSB       |       | 0.1  |       |       |

| Programmed DIM Duty Cycle          |                      | SPI is enabled, PWM1_SEL = PWM2_SEL = 1, PWM_DUTY[9:0] = 500        |       | 50   |       | %     |

|                                    |                      | SPI is enabled, PWM1_SEL = PWM2_SEL = 1, PWM_DUTY[9:0] = 1000       |       | 100  |       |       |

| CURRENT-SENSE AMPLIFIER            | ₹                    |                                                                     |       |      |       |       |

| Current-Sense Amplifier Offset     |                      |                                                                     | 0.192 | 0.2  | 0.208 | V     |

| Current-Sense Gain                 |                      |                                                                     | 4.84  | 5.0  | 5.12  | V/V   |

| CURRENT MONITOR                    |                      |                                                                     |       |      |       |       |

| Offset Voltage                     |                      |                                                                     |       | 0.2  |       | V     |

| Current Monitor Amplifier Gain     |                      |                                                                     |       | 5    |       | V/V   |

| DH_AND DL_ DRIVERS                 |                      |                                                                     |       |      |       |       |

| DH_ Sourcing Resistance            | R <sub>ON_HS</sub>   | $D_{H_{-}}$ = high, $T_{A}$ = -40°C to +125°C                       |       | 2.5  | 5.0   | Ω     |

| DH_ Sinking Resistance             | R <sub>DH_SINK</sub> | D <sub>H</sub> _= low, T <sub>A</sub> = -40°C to 125°C              |       | 1.0  | 2.0   | Ω     |

| DL_ Sourcing Resistance            | R <sub>DL</sub> SRC  | D <sub>L</sub> = high, T <sub>A</sub> = -40°C to +125°C             |       | 2.5  | 5.0   | Ω     |

| DL_ Sinking Resistance             | R <sub>DL_SINK</sub> | D <sub>L</sub> = low, T <sub>A</sub> = -40°C to +125°C              |       | 1.8  | 3.5   | Ω     |

| DHto-DL_ Dead Time                 |                      | DH_ fall to DL_ rise, CL = 1nF (measured at V <sub>TH</sub> = 1.5V) |       | 20   |       | ns    |

| DLto-DH_ Dead Time                 |                      | DL_ fall to DH_ rise, CL = 1nF (measured at V <sub>TH</sub> = 1.5V) |       | 20   |       | ns    |

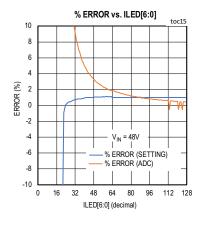

| ADC (MAX20096 ONLY)                |                      |                                                                     |       |      |       |       |

| Resolution                         |                      |                                                                     |       | 8    |       | bits  |

| Offset Error                       |                      |                                                                     | -2    |      | +2    | %FS   |

| Gain Error                         |                      |                                                                     | -2    | ·    | +2    | %FS   |

| SPI ELECTRICAL CHARACTE            | ERISTICS (M          | AX20096 ONLY)                                                       |       |      |       |       |

| I/O Supply Voltage                 | V <sub>IO</sub>      |                                                                     | 1.8   |      | 5.5   | V     |

| Static I/O Supply Current (Note 2) | I <sub>DDIO</sub>    | Static inputs, all outputs unloaded                                 |       |      | 1     | μA    |

### **Electrical Characteristics (continued)**

$(V_{IN} = 12V, Limits are 100\% tested at T_A = +25^{\circ}C and T_A = +125^{\circ}C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)$

| PARAMETER                                          | SYMBOL            | CONDITIONS                                                | MIN                      | TYP  | MAX                      | UNITS |

|----------------------------------------------------|-------------------|-----------------------------------------------------------|--------------------------|------|--------------------------|-------|

| DIGITAL INPUT CHARACTER                            | ISTICS (SCL       | K, SDI, CSB, RESETB)                                      |                          |      |                          |       |

| Input High-Voltage V <sub>MAX</sub>                | VIH               | 2.2V < V <sub>IO</sub> < 5.5V                             | 0.7 x                    |      |                          | V     |

| mpat riigii voltage viviAX                         | Y III             | 2.24 1 10 10.04                                           | V <sub>IO</sub>          |      |                          | •     |

| Input High-Voltage V <sub>MIN</sub>                | V <sub>IH</sub>   | 1.8V < V <sub>IO</sub> < 2.2V                             | 0.8 x<br>V <sub>IO</sub> |      |                          | V     |

| Input Low-Voltage V <sub>MAX</sub>                 | V <sub>IL</sub>   | 2.2V < V <sub>IO</sub> < 5.5V                             |                          |      | 0.3 x<br>V <sub>IO</sub> | V     |

| Input Low-Voltage V <sub>MIN</sub>                 | V <sub>IL</sub>   | 1.8V < V <sub>IO</sub> < 2.2V                             |                          |      | 0.2 x<br>V <sub>IO</sub> | V     |

| Input Leakage Current (Note 3)                     | I <sub>IN</sub>   | V <sub>IN</sub> = 0V or V <sub>IO</sub>                   |                          | ±0.1 | ±1                       | μA    |

| Internal Safety-Impedance<br>Pulldown (Notes 4, 5) | R <sub>PD</sub>   | SDI, SCLK pulldown to AGND                                | 40                       | 100  | 160                      | kΩ    |

| Internal Safety-Impedance<br>Pullup (Notes 4, 5)   | R <sub>PU</sub>   | CSB, RESETB pullup to V <sub>IO</sub>                     | 40                       | 100  | 160                      | kΩ    |

| Input Capacitance                                  | C <sub>IN</sub>   |                                                           |                          | 10   |                          | pF    |

| Hysteresis Voltage                                 | V <sub>H</sub>    |                                                           |                          | 0.35 |                          | V     |

| DIGITAL OUTPUT CHARACTE                            | ERISTICS (SI      | DO)                                                       |                          |      |                          |       |

| Output High-Voltage V <sub>MAX</sub>               | V <sub>OH</sub>   | V <sub>IO</sub> > 2.5V, I <sub>SOURCE</sub> = 5mA         | V <sub>IO</sub><br>-0.4  |      |                          | V     |

| Output High-Voltage V <sub>MIN</sub>               | V <sub>OH</sub>   | V <sub>IO</sub> > 1.8V, I <sub>SOURCE</sub> = 2mA         | V <sub>IO</sub><br>-0.4  |      |                          | V     |

| Output Low-Voltage V <sub>MAX</sub>                | V <sub>OL</sub>   | V <sub>IO</sub> > 2.5V, I <sub>SINK</sub> = 5mA           |                          |      | 0.4                      | V     |

| Output Low-Voltage V <sub>MIN</sub>                | V <sub>OL</sub>   | V <sub>IO</sub> > 1.8V, I <sub>SINK</sub> = 2mA           |                          |      | 0.4                      | V     |

| Output Short-Circuit Current                       | I <sub>OSS</sub>  | I <sub>SINK</sub> , I <sub>SOURCE</sub>                   |                          | 250  |                          | mA    |

| Output Three-State Leakage                         | loz               |                                                           |                          | ±0.1 | ±1                       | μA    |

| Output Three-State Capacitance                     | C <sub>OZ</sub>   |                                                           |                          | 10   |                          | pF    |

| SPI TIMING CHARACTERISTI                           | CS (MAX200        | 96 ONLY)                                                  |                          |      |                          |       |

| SCLK Frequency                                     | fsclk             |                                                           | 0                        |      | 4                        | MHz   |

| SCLK Period                                        | t <sub>CP</sub>   |                                                           | 250                      |      |                          | ns    |

| SCLK Pulse Width High                              | t <sub>CH</sub>   |                                                           |                          | 62.5 |                          | ns    |

| SCLK Pulse Width Low                               | t <sub>CL</sub>   | (Note 6)                                                  |                          | 62.5 |                          | ns    |

| CSB Fall to SCLK Rise<br>Setup Time                | t <sub>CSS0</sub> | To 1st SCLK rising edge (RE) (Note 6)                     | 25                       |      |                          | ns    |

| CSB Fall to SCLK Rise Hold<br>Time                 | t <sub>CSH0</sub> | Applies to inactive rising edge preceding 1st rising edge | 25                       |      |                          | ns    |

| CSB Rise to SCLK Rise Hold<br>Time                 | t <sub>CSH1</sub> | Applies to N x 16th rising edge                           | 25                       |      |                          | ns    |

#### **Electrical Characteristics (continued)**

$(V_{IN} = 12V, Limits are 100\% tested at T_A = +25^{\circ}C and T_A = +125^{\circ}C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)$

| PARAMETER                          | SYMBOL            | CONDITIONS                                                                 | MIN | TYP | MAX | UNITS |

|------------------------------------|-------------------|----------------------------------------------------------------------------|-----|-----|-----|-------|

| CSB Rise to SCLK Rise              | t <sub>CSA</sub>  | Applies to N x 16th rising edge, guarantees aborted (unqualified) sequence | 25  |     |     | ns    |

| CSB Rise to SCLK Rise              | tcsq              | Applies to (N x 16) + 1 rising edge, guarantees qualified sequence         | 25  |     |     | ns    |

| CSB Pulse Width High               | t <sub>CSPW</sub> |                                                                            | 100 |     |     | ns    |

| SDI-to-SCLK Rise Setup Time        | t <sub>DS</sub>   |                                                                            | 20  |     |     | ns    |

| SDI-to-SCLK Rise Hold Time         | t <sub>DH</sub>   |                                                                            | 20  |     |     | ns    |

| RESETB Pulse Width Low             | t <sub>RBPW</sub> | For request to be recognized                                               | 25  |     |     | ns    |

| RESETB Rise to CSB Fall<br>Removal | t <sub>RBCS</sub> | For write transaction to be executed                                       | 20  |     |     | ns    |

| SCLK Fall to SDO Transition        | t <sub>DOT</sub>  | C <sub>LOAD</sub> = 20pF                                                   |     |     | 100 | ns    |

| SCLK Fall to SDO Hold              | t <sub>DOH</sub>  | C <sub>LOAD</sub> = 0pF                                                    | 2   |     |     | ns    |

| CSB Fall to SDO Transition         | t <sub>DOE</sub>  | C <sub>LOAD</sub> = 20pF                                                   |     |     | 100 | ns    |

| CSB Rise to SDO Hi-Z               | t <sub>DOZ</sub>  | Output disable time                                                        |     |     | 80  | ns    |

| THERMAL SHUTDOWN                   |                   |                                                                            |     |     |     |       |

| Thermal Warning (MAX20096 only)    |                   |                                                                            |     | 150 |     | °C    |

| Thermal Shutdown                   |                   |                                                                            |     | 165 |     | °C    |

| Hysteresis                         |                   |                                                                            |     | 15  |     | °C    |

- Note 2: Static logic inputs with  $V_{IL}$  = AGND and  $V_{IH}$  =  $V_{IO}$ . CSB, RESETB =  $V_{IH}$  (if safety pullup active).

- Note 3: No internal safety pullup/pulldown impedances active, input buffers only.

- Note 4: Internal safety pullup/pulldown impedances available, with enable function.

- Note 5: If pullup is supported, note CSB and RESETB connection and diode to V<sub>IO</sub>; this diode is present regardless of enable mode.

- Note 6: Applications must afford time for the device to drive data on the SDO bus and meet the μC setup time prior to the μC latching in the result on the following SCLK rising edge. In practice, this is determined by loading and μC characteristics, and the relevant t<sub>DOT</sub>/t<sub>DOE</sub> specification must be satisfied.

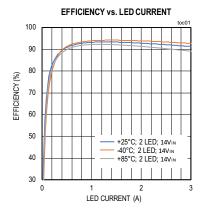

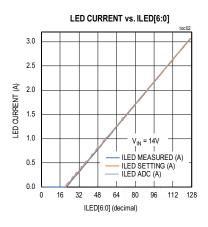

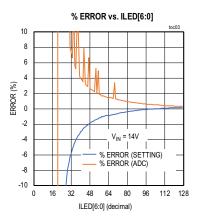

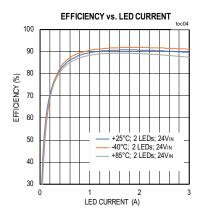

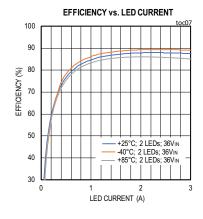

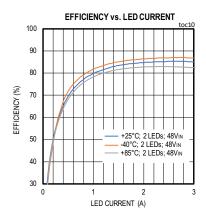

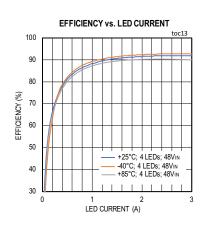

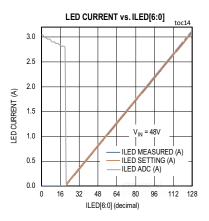

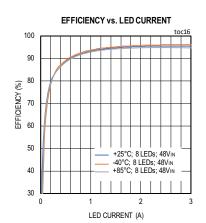

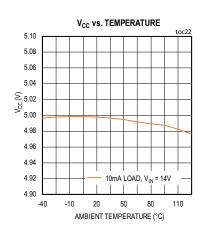

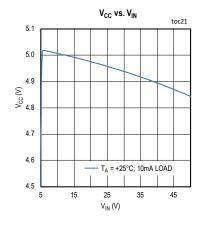

### **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

### **Typical Operating Characteristics (continued)**

(T<sub>A</sub> = +25°C, unless otherwise noted.)

### **Typical Operating Characteristics (continued)**

(T<sub>A</sub> = +25°C, unless otherwise noted.)

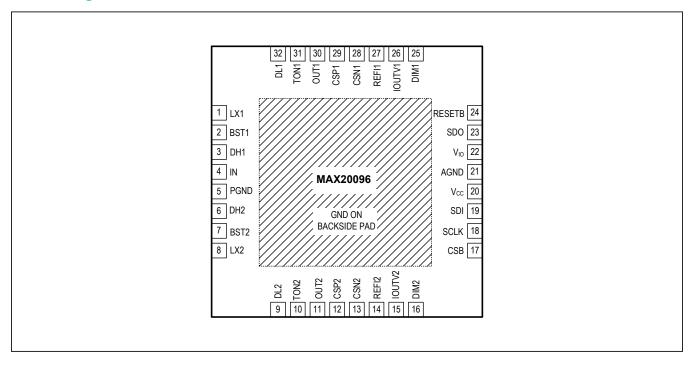

### **Pin Configurations**

# Dual-Channel Synchronous Buck, High-Brightness LED Controller with and without SPI Interface

## **Pin Description**

| Р                   | IN                |                 |                                                                                                                                                                                                                                 |

|---------------------|-------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SW TQFN<br>MAX20096 | TSSOP<br>MAX20097 | NAME            | FUNCTION                                                                                                                                                                                                                        |

| 1                   | 4                 | LX1             | Switching Node of Buck LED Driver on Channel 1. Connect to one end of output inductor on channel 1.                                                                                                                             |

| 2                   | 5                 | BST1            | High-Side Power Supply for High-Side Gate Drive for Channel 1. Connect a 0.1µF ceramic capacitor from BST1 to LX1.                                                                                                              |

| 3                   | 6                 | DH1             | High-Side Driver of Channel 1. Connect to gate of high-side n-channel MOSFET of buck LED driver for channel 1. Use a series resistor to limit current slew rate and mitigate EMI noise, if required.                            |

| 4                   | 7                 | IN              | Supply Input Pin for $V_{CC}$ Regulator. Connect a 1 $\mu$ F ceramic capacitor from IN to PGND. If an external $V_{CC}$ regulator is used, then connect IN to $V_{CC}$ .                                                        |

| 5                   | 8                 | PGND            | Power-Ground Connection                                                                                                                                                                                                         |

| 6                   | 9                 | DH2             | High-Side Driver of Channel 2. Connect to gate of high-side n-channel MOSFET of buck LED driver for channel 2. Use a series resistor to limit current slew rate and mitigate EMI noise, if required.                            |

| 7                   | 10                | BST2            | High-Side Power Supply for High-Side Gate Drive for Channel 2. Connect a 0.1µF ceramic capacitor from BST2 to LX2.                                                                                                              |

| 8                   | 11                | LX2             | Switching Node of Buck LED Driver on Channel 2. Connect to one end of output inductor on channel 2.                                                                                                                             |

| 9                   | 12                | DL2             | Low-Side Driver of Channel 2. Connect to gate of low-side n-channel MOSFET of LED driver for channel 2. Use a series resistor to limit current slew rate and mitigate EMI noise, if necessary.                                  |

| 10                  | 13                | TON2            | Frequency-Setting Pin for Channel 2. Connect a resistor to the input supply and capacitor to AGND to set switching frequency for channel 2.                                                                                     |

| 11                  | 14                | OUT2            | Connect a resistor-divider from OUT2 to the output voltage on channel 2. OUT2 has the scaled-down feedback of the output voltage on channel 2.                                                                                  |

| 12                  | 15                | CSP2            | Current-Sense Input on Channel 2. Connect to source of external MOSFET driven by DL2. Connect a resistor from this pin to CSN2 to sense the current in the MOSFET.                                                              |

| 13                  | 16                | CSN2            | Negative Current-Sense Connection on Channel 2. Connect this pin to power ground.                                                                                                                                               |

| 14                  | 17                | REFI2           | Analog Dimming Input for Channel 2 in Default Mode. Connect to a resistor-divider from $V_{CC}$ to set the default LED current in channel 2.                                                                                    |

| 15                  | 18                | IOUTV2          | Current Monitor Output on Channel 2                                                                                                                                                                                             |

| 16                  | 19                | DIM2            | PWM Dimming Input in Default Mode for Channel 2. Connect to an external PWM signal or connect to an analog voltage between 0.2V and 3V to set the PWM duty cycle in channel 2.                                                  |

| 17                  | _                 | CSB             | Chip-Select Pin for SPI Interface. This pin is pulled low to enable the SPI Interface.                                                                                                                                          |

| 18                  | _                 | SCLK            | Clock Input Pin for SPI Interface                                                                                                                                                                                               |

| 19                  | _                 | SDI             | Data Input Pin for SPI Interface                                                                                                                                                                                                |

| 20                  | 20                | V <sub>CC</sub> | +5V Regulator Output. Connect a 1 $\mu$ F ceramic capacitor from this pin to GND. If an internal V <sub>CC</sub> regulator is not used, then connect V <sub>CC</sub> to IN and connect an external V <sub>CC</sub> to this pin. |

# Dual-Channel Synchronous Buck, High-Brightness LED Controller with and without SPI Interface

## **Pin Description (continued)**

| Р                   | IN                |                 |                                                                                                                                                                                             |

|---------------------|-------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SW-TQFN<br>MAX20096 | TSSOP<br>MAX20097 | NAME            | FUNCTION                                                                                                                                                                                    |

| 21                  | 21                | AGND            | Analog Ground Connection                                                                                                                                                                    |

| 22                  | 22                | V <sub>IO</sub> | Microcontroller Power Supply Pin for MAX20096. For the MAX20097, connect $V_{\text{IO}}$ to $V_{\text{CC}}$ externally                                                                      |

| 23                  | _                 | SDO             | Data Output Pin for SPI Interface externally                                                                                                                                                |

| 24                  | _                 | RESETB          | Active-Low Reset Pin for SPI. Toggling the reset pin switches control switches programming of REFI_, DIM_, and oscillator frequency on both channels to the analog control pins.            |

| 25                  | 24                | DIM1            | PWM Dimming Input in Default Mode for Channel 1. Connect to an external PWM signal or connect it to an analog voltage between 0.2V to 3V to set the PWM duty cycle in Channel 1.            |

| 26                  | 25                | IOUTV1          | Current Monitor Output on Channel 1                                                                                                                                                         |

| 27                  | 26                | REFI1           | Analog Dimming Input for Channel 1 in Default Mode. Connect to a resistor divider from V <sub>CC</sub> to set the default LED Current in Channel 1.                                         |

| 28                  | 27                | CSN1            | Negative Current-Sense Connection on Channel 1. Connect CSN1 to power ground.                                                                                                               |

| 29                  | 28                | CSP1            | Current-Sense Input on Channel 1. Connect to source of external MOSFET that is driven by DL1. Connect a resistor from this pin to CSN1 to sense the current in the MOSFET.                  |

| 30                  | 1                 | OUT1            | Connect a resistor divider from this pin to the output voltage on channel 1. This pin has the scaled down feedback of the output voltage on channel 1.                                      |

| 31                  | 2                 | TON1            | Frequency-Setting Pin for Channel 1. Connect a resistor to the input supply and capacitor to AGND to set switching frequency for channel 1.                                                 |

| 32                  | 3                 | DL1             | Low-Side Driver of Channel 1. Connect to gate of low-side N-channel MOSFET of LED Driver for channel 1. Use series resistor to limit current slew-rate and mitigate EMI noise if necessary. |

| _                   | 23                | FLTB            | Fault Flag Output in MAX20097                                                                                                                                                               |

| _                   | _                 | EP              | Exposed Pad. Connect EP to a large-area contiguous copper ground plane for effective power dissipation. Do not use as the main IC ground connection. EP must be connected to GND.           |

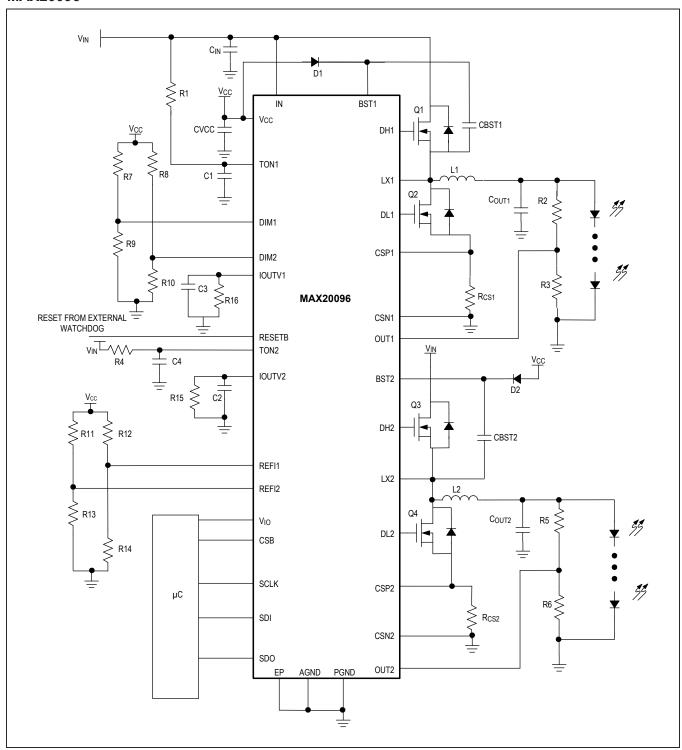

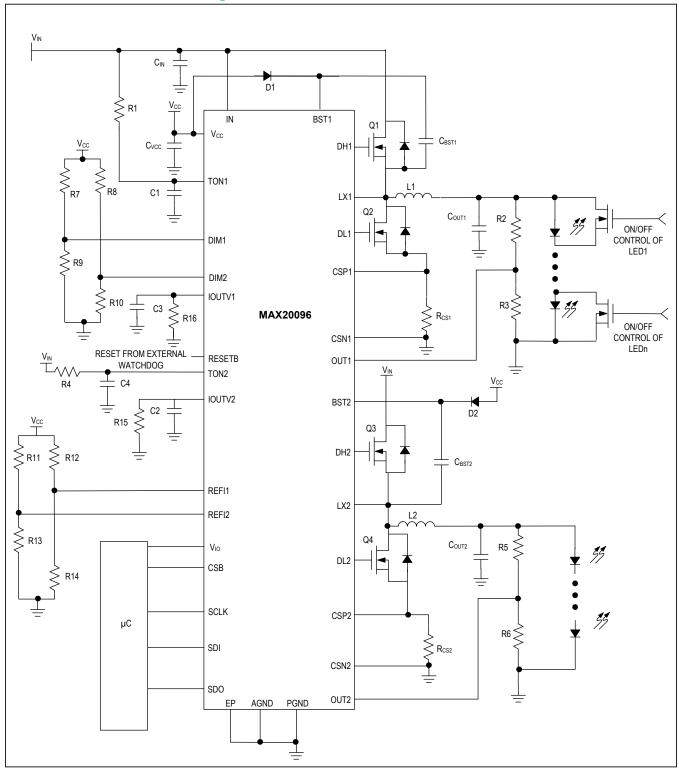

### **Buck Diagrams**

### **MAX20096**

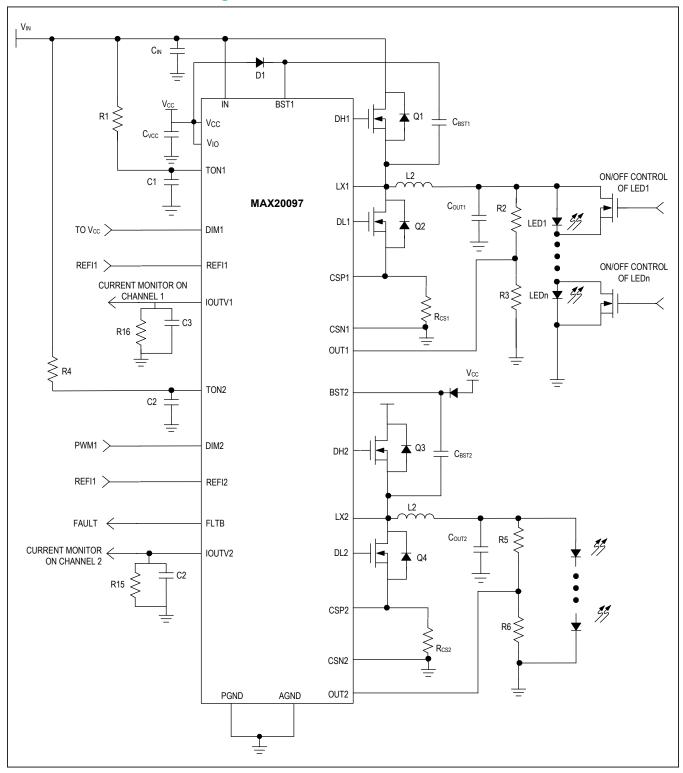

### **Buck Diagrams (continued)**

#### **MAX20097**

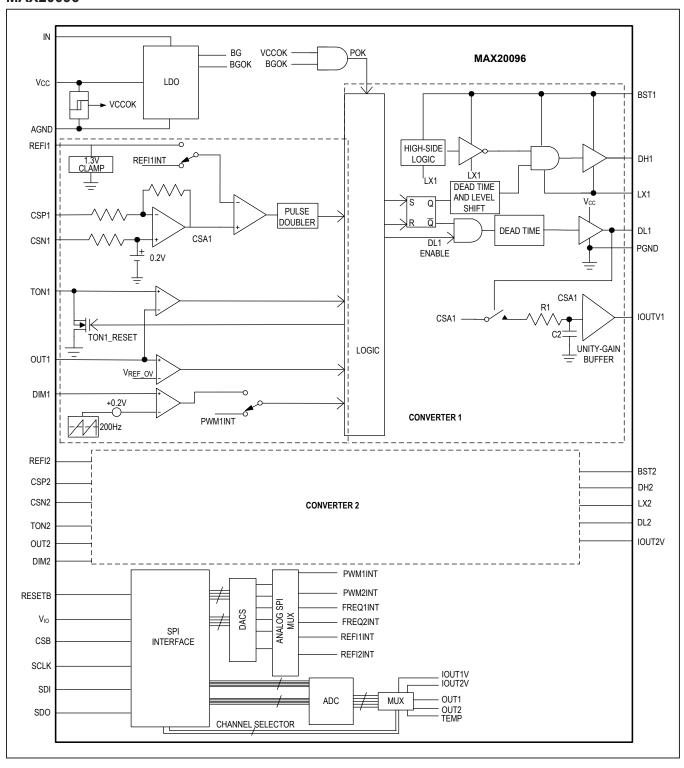

### **Block Diagrams**

#### MAX20096

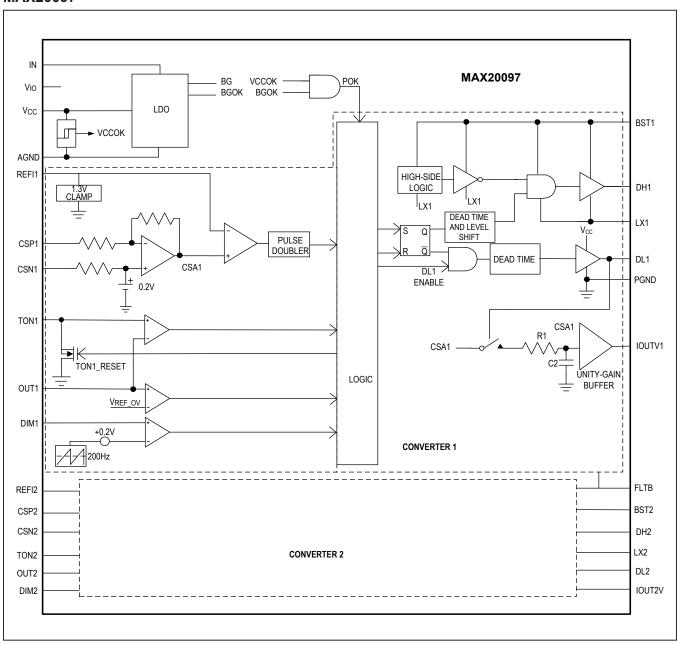

### **Block Diagrams (continued)**

#### **MAX20097**

#### **Detailed Description**

The MAX20096/MAX20097 ICs are dual-channel, high-voltage, synchronous n-channel high-current buck LED drivers. The ICs use a proprietary average current-mode-control scheme to regulate the inductor current. This control method does not require any control-loop compensation, maintaining nearly constant switching frequency. Inductor current sense is achieved by sensing the current in the bottom switching device. The ICs integrate two fully synchronous buck controllers. The ICs operate over a wide 4.5V to 65V input range, are designed for high-frequency operation, and can operate at switching frequencies as high as 1MHz.

In the MAX20096, the output voltages and currents are on both channels and the junction temperature can be read back through the SPI interface. Protection features include inductor current-limit protection, overvoltage protection and thermal shutdown. The MAX20096 is available in a space-saving, thermally enhanced (5mm x 5mm), 32-pin side-wettable TQFN package and is specified to operate over the -40°C to +125°C automotive temperature range.

The MAX20097 is available in a 28-pin thermally enhanced TSSOP package, but does not have the SPI interface. It includes an open-drain fault flag (FLTB) that goes low in case of an open string, shorted string, or overvoltage activation in any one of the channels, or in the event of thermal shutdown.

#### **Vcc Supply**

The V<sub>CC</sub> supply is the low-voltage digital and analog supply for the chip and derives power from the input voltage from IN to GND. An internal power-on reset (POR) monitors the V<sub>CC</sub> voltage and the IN voltage. A POR low is generated when V<sub>CC</sub> goes below its UVLO threshold, causing the IC to be reset. The chip comes out of the reset state once the input voltage goes back up and the V<sub>CC</sub> regulator output is back in regulation. Bypass V<sub>CC</sub> to GND with a minimum of 1µF ceramic capacitor as close as possible to the device. In certain applications when an external regulated 5V supply is available, IN and V<sub>CC</sub> can be connected together and the regulated 5V can be applied directly to V<sub>CC</sub>, saving the power dissipation in the internal regulator of the device. The internal V<sub>CC</sub> regulator is capable of delivering 10mA to external circuitry on V<sub>CC</sub>

#### **Buck LED Driver**

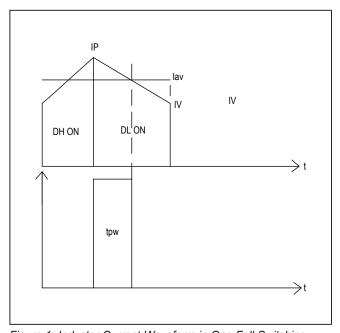

The ICs use a new average current-mode-control scheme to regulate the current in the output inductor of the buck LED drivers. The inductor current is not directly sensed. In case of a synchronous buck LED driver, the ICs sense the current in the bottom synchronous switch for both channels. In a buck converter, when operating in continuousconduction mode when the top switch is turned off, the current in the inductor also flows in the bottom switch or diode. This peak current is Ip. When the bottom switch or diode is turned off and the top switch is then turned on, the current in the switch is the same as the current in the inductor, which is IV. The average current in the inductor is given by  $I_{AV} = 0.5(I_P + I_V)$ .  $I_{AV}$  is the same as the output current IO. If the bottom switch or diode current is sensed at exactly half of the bottom switch/diode period, the current in the switch/diode would be IAV. This fact is used by the new average current-mode-control scheme to regulate the inductor current when the buck converter is operating in continuous conduction mode.

Figure 1. Inductor Current Waveform in One Full Switching Cycle

#### **Switching Frequency**

The on-time for Channel 1 is determined based on the external resistor (R1) connected between  $T_{ON1}$  and the input voltage, in combination with a capacitor (C1) between R1 and AGND/PGND pins. The input voltage and the R1 resistor set the current sourced into the capacitor (C1), which governs the ramp speed. The ramp threshold is proportional to scaled-down feedback of the output voltage at the OUT pin. The proportionality of  $V_{OUT}$  is set by an external resistor-divider (R2, R3) from  $V_{OUT}$ .

$$t_{ON} \times V_{IN}/R1 = C1 (V_{OUT} \times R3/(R3 + R2))$$

$t_{ON} = K \times V_{OUT}/V_{IN}$

where  $K = C1 \times R3 \times R1/(R3 + R2)$

In the case of a buck converter, t<sub>ON x</sub> V<sub>IN</sub> is also given by:

$$tON = V_{OUT}/V_{IN x} f_{SW}$$

where f<sub>SW</sub> is the switching frequency.

Based on that, the switching frequency in case of the new average current-mode-controlled architecture is given by:

$$f_{SW} = 1/K \text{ or } f_{SW} = (R3 + R2)/(C1 \times R3 \times R1)$$

The switching frequency is independent of input and output voltage and is held fixed. In the actual application, there will be slight variations in switching frequency due to the drops in the switches and the inductor. These drops were ignored in the calculations for switching frequency. For Channel 2, the switching frequency is given by

$$f_{SW} = (R6 + R5)/(C2 \times R6 \times R4)$$

#### **Analog Dimming**

Analog dimming is performed by controlling the LED current amplitude during operation in both output channels.

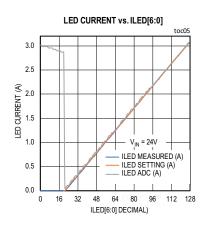

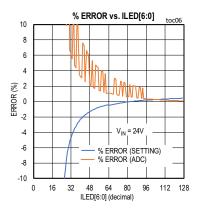

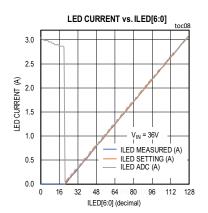

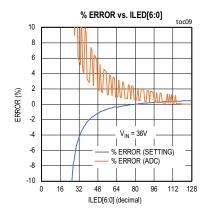

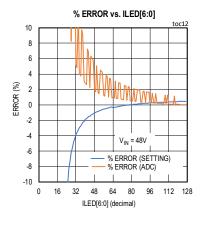

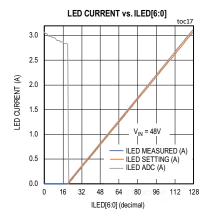

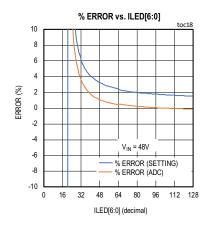

# Analog Dimming Through the SPI Interface (MAX20096 Only)

For analog dimming through the SPI registers, the CNFG\_SEL bit in the CNFG\_GEN (0X02) register needs to be set at 1. Once this bit is set at 1, the LED current in channel 1 is programmed by the contents of the CNFG\_CRNT1 (0X03) register, and by CNFG\_CRNT2 (0X04) for LED current in channel 2. The programmed LED current in channel 1 is given by:

The LED current for channel 2 is given by:

I<sub>LED2</sub> SET = ((CNFG\_CRNT2[6:0](dec) x 1.25/127) - 0.2)/5 x R<sub>CS2</sub> in Amps

#### Analog Dimming Through REFI\_ Pins

For this configuration, the CNFG\_SEL bit in the CNFG\_GEN register is set at 0 in the MAX20096. Once this is set at 0, the analog dimming is controlled by the analog dimming pins (REFI1 and REFI2). The voltage at REFI\_sets the LED current level when  $V_{REFI}$  < 1.2V. The LED current can be linearly adjusted from zero with the voltage on REFI\_. For  $V_{REFI}$  > 1.3V, an internal reference sets the LED current. The maximum withstand voltage of this input is 5.5V. The LED current is at zero when  $V_{REFI}$  is below 0.2V. In the MAX20097, analog dimming is similar to the analog dimming through the MAX20096 REFI\_pins.

The equation for setting the LED current is given by

$$I_{LED} = (V_{REFI} - 0.2)/(5 \times RCS_)$$

#### **PWM Dimming**

The ICs support PWM dimming. PWM dimming is the preferred method of dimming because it maintains the LED color, regardless of the brightness. In PWM dimming, the LED current-waveform frequency is constant and the duty cycle is set according to the required light intensity. To avoid flicker issues the PWM dimming frequency should be set above 200Hz.

The MAX20096 handles two distinct PWM dimming modes (external and internal), depending on the SPI parameters (PWM1\_SEL and PWM2\_SEL) in the CNFG\_GEN register.

In the MAX20097, there is no SPI interface and therefore no PWM dimming through the SPI interface.

#### PWM Dimming Through DIM\_ Pins

The two independent inputs (DIM1 and DIM2) handle the PWM dimming signals for the two independent channels. This mode is selected independently for channel 1 by PWM1\_SEL = 0, and PWM2\_SEL = 0 for channel 2. These bits are found in the CNFG\_GEN register in the MAX20096. For the MAX20097, PWM dimming is controlled directly by the DIM\_ pins.

In this mode, the PWM dimming functions with either analog or PWM control signals. For PWM dimming with a pulsating PWM signal, once the internal pulse detector detects three successive edges of a PWM signal with a frequency between 10Hz and 2kHz, the ICs synchronize to the external signal and pulse-width modulates the LED current for that channel at the external DIM\_ input frequency with the same duty cycle as the DIM\_ input. If an analog control signal is applied to DIM\_, the ICs compare the DC input to an internally generated 200Hz ramp to pulse-width-modulate the LED current (fDIM = 200Hz). The output current duty cycle is linearly adjustable from 0% to 100% (0.2V < VDIM\_ < 2.8V). Use the following formula to calculate the voltage (VDIM\_) necessary for a given output-current duty cycle D:

$$V_{DIM} = (D \times 2.6) + 0.2V$$

where  $V_{\mbox{DIM}}$  is the voltage applied to DIM\_ in volts.

The 200Hz internal ramp for channels 1 and 2 are 180° degrees out of phase, which allows for phase shifting of 180° when the dimming in the two channels are set by an analog voltage on DIM1 and DIM2.

# PWM Dimming Through SPI Interface (MAX20096 Only)

This mode is selected independently for buck channel 1 by PWM1\_SEL = 1 and for channel 2 by PWM2\_SEL = 1. The PWM frequency is common between both channels and is programmable through the PWM\_FREQ[2:0] SPI parameter. The PWM dimming frequency is given by:

$$f_{DIM} = PWM_FREQ[2:0](dec) \times 225 + 200Hz$$

The PWM dimming in each channel is determined by the PWM\_DUTY\_[9:0] bits. The PWM control signals are out of phase between the two channels. This helps in alleviating EMI problems. Each least significant bit (LSB) change corresponds to 0.1% duty cycle. 100% duty cycle is achieved when the decimal value in the PWM\_DUTY\_[9:0] bits exceeds 1000. Register values between 1000 and 1023 all provide 100% duty cycle.

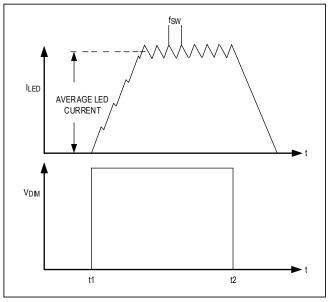

#### **Behavior of LED Driver During PWM Dimming**

When the internal PWM dimming signal is high the switching of the high-side MOSFET in the buck LED driver is enabled; however, when DIM goes low, both the high-and low-side MOSFETs are turned off. When the internal PWM dimming signal makes a low-to-high transition, the bottom internal MOSFET inside the device is turned on for 180ns and then the bottom switch is turned off and the

top switch turned on. The LED current waveform is shown in <u>Figure 2</u>. The bottom MOSFET is turned on for 180ns to guarantee that the capacitors on the BST\_ pin are sufficiently charged to provide adequate gate drive when the top switch is turned on.

#### **Current Monitor**

The device includes a current monitor on the  $I_{OUTV}$  pins. The  $I_{OUTV}$  voltage is an analog voltage indication of the inductor current when DIM is high. The current-sense signal on the bottom MOSFET across RCS\_ is inverted and amplified by a factor of 5 by an inverting amplifier inside the device. An added offset voltage of 0.2V is also added to this voltage. This amplified signal goes through a sample and hold switch, which is controlled by the DL\_ signal. The sample and hold switch is turned on only when DL\_ is high (and is off when DL\_ is low). This provides a signal on the output of the sample and hold that is a true representation of the inductor current when DIM\_ is high. The sample and hold signal passes through an RC filter and then the buffered output is available on the  $I_{OUTV}$  pin. The voltage on the  $I_{OUTV}$  pin is given by:

$$V_{IOUTV}$$

= ILED\_ x RCS\_ x 5 + 0.2V

where I<sub>LED</sub> is the LED current, which is the same as the average inductor current when DIM is high.

#### ADC (MAX20096 Only)

Figure 2. LED Current Waveform with PWM Dimming

### Dual-Channel Synchronous Buck, High-Brightness LED Controller with and without SPI Interface

#### General

The MAX20096 has an internal ADC that measures output voltage on both channels, LED currents on both channels, and IC temperature. The output voltage is monitored by measuring the voltage on the OUT\_ pin. Fault monitoring and switching-stage output-voltage optimization is possible by using an external microcontroller to read out these digitized voltages through the SPI interface. The ADC is an 8-bit SAR (successive-approximation register) topology. It sequentially samples each of these voltages using a 5-channel multiplexer. Conversions are driven by an internally generated 2MHz clock. For the output voltage, the voltages are sensed on the OUT pins; the ADC conversion is also gated by the PWM dimming signal. The ADC samples the output voltage on each channel only when its PWM goes high and after a delay that is set by the DLY bits. After a conversion, each measurement is stored into its respective register and can be accessed through the SPI interface.

Note that none of the external microcontroller SPI commands interfere with the internal ADC state-machine sample and conversion operations. The microcontroller always gets the last available data at the moment of the register read. All MAX20096 ADC registers' data integrity is protected by odd parity on bit 8 (i.e., the 9th bit, if counting from the LSB named 0). See the <u>Register Map</u> section for further details.

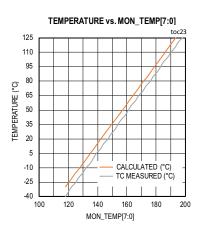

#### **Device Temperature ADC (MON\_TEMP)**

By means of the MON\_TEMP measurement, the MCU can monitor the device junction temperature ( $T_J$ ) over time. The conversion formula is:  $T_J = ((TEMP[7:0] \times 523)/255) - 272^{\circ}C$ , where MON\_TEMP[6:0] is the value read out directly from the related 8-bit SPI register (see the *Register Map*

section). The value is also used internally by the device for the thermal-warning and thermal-shutdown functions.

# Output Voltages (MON\_VBUCK1 and MON\_VBUCK2)

The voltages on OUT1 and OUT2 are measured by the ADC. The output voltages on each of the LED channels are determined by the formula:

The output voltage is sampled only when the PWM dimming is high after a delay set by the DLY\_ bits. This information is used to determine the status of the LED strings. This is used to determine if an individual LED is shorted, or if the string is shorted to GND or if it is shorted to battery. This feature can be exploited by MCU-embedded algorithm diagnostics to read the LED channel's voltage even when in the OFF state, before enabling the LED strings at power-up.

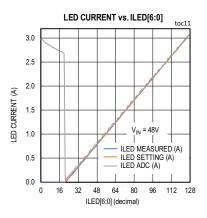

#### Output Current (MON\_I<sub>LED</sub> )

The MON\_ $I_{LED1}$  and MON\_ $I_{LED2}$  registers indicate the current flowing out of Channel 1 and Channel 2, respectively. The actual currents in channels 1 and 2 are given by the following equation:

```

I_{LED1} = ((2.5V \times IMON1[7:0]/255) - 0.2V)/(5 \times R_{CS1})

I_{LED2} = ((2.5V \times IMON2[7:0]/255) - 0.2V)/(5 \times R_{CS2})

```

The ADC samples the voltage on  $I_{\mbox{\scriptsize OUTV1}}$  and  $I_{\mbox{\scriptsize OUTV2}}.$

#### **SPI Interface**

#### Overview

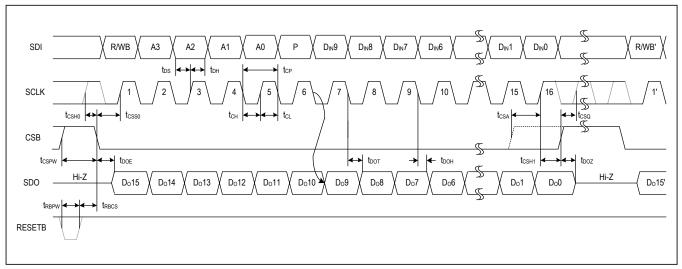

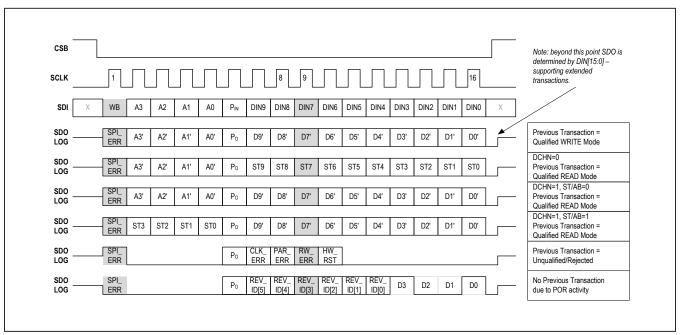

The MAX20096 interface is SPI/QSPI/Microwire/DSP compatible. The operation and timing criteria of the SPI interface is shown in Figure 3. The MAX20096 is programmed by an (N x 16)-cycle SPI instruction framed by a CSB low interval. The start of the transaction is defined by the SCLK rising edge, following the CSB falling edge (subject to  $t_{CSH0}$  and  $t_{CSS0}$  timing criteria). Transactions, including a number of SCLK rising edges not evenly divisible by 16, do not qualify for execution (also based on  $t_{CSA}$ ,  $t_{CSH1}$ , and  $t_{CSQ}$  timing criteria). Qualified transactions are executed on the rising edge of CSB. To abort a command sequence, the rise of CSB must precede a qualified (N x 16th) rising edge of SCLK (meeting the  $t_{CSA}$  timing requirement).

The SDI content of the SPI transaction consists of a leading read/write (R/WB) bit followed by address, parity, and input data information. Data is latched into the MAX20096 on SCLK rising edges, subject to setup and hold criteria (t<sub>DS</sub>, t<sub>DH</sub>).

SDO is actively driven by the MAX20096 when CSB falls ( $t_{DOE}$  timing applies), initially presenting the MSB of the output data (the SPI\_ERR bit for all transactions). Following the initial SCLK rising edge, SDO is updated in response to SCLK falling edges, conforming to hold and transition time criteria ( $t_{DOH}$ ,  $t_{DOT}$ ), allowing the  $\mu$ C to

latch the data on SCLK rising edges. When CSB is high, the SDO line is high impedance, allowing other devices to access the SDO bus.

#### **RESETB Behavior**

The RESETB pin provides the means of asynchronously resetting the part to fail-safe default modes of operation in the event of an SPI interface failure. The RESETB pin is active low, meaning the reset condition is asserted when the input is low.

In response to RESETB falling, all configuration content is reset to its default state. All write mode transactions to the part, during which RESETB is asserted, are rejected and reported as an interface error (notifying the user the transaction was ignored). The one exception is the CNFG\_SPI register, which is not cleared by RESETB and can be written during RESETB, allowing the interface to be configured and continue to operate during RESETB assertions. Read-mode transactions are not impacted. The part remains in reset mode until the RESETB condition is removed by pulling the pin high. After the RESETB assertion is removed, the SPI interface resumes normal operation (subject to t<sub>RBCS</sub> timing criteria). Control of the part can then be returned to the SPI configuration registers, once the CNFG SEL bit is programmed.

Figure 3. SPI Timing Diagram

### Dual-Channel Synchronous Buck, High-Brightness LED Controller with and without SPI Interface

#### **Device Connections**

The SPI interface ensures compatible operation with standard microcontrollers ( $\mu$ Cs) from a variety of manufacturers. The  $\mu$ C always operates as the master and is able to initiate read and write transactions to individual slave devices (using standard connections), or groups of slave devices (using daisy-chain connections) selected by a specific CSB connection. The device(s) always operate in the slave role when connected to a  $\mu$ C and cannot initiate a SPI transaction.

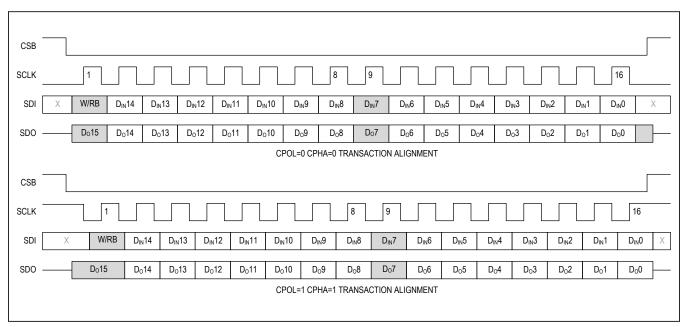

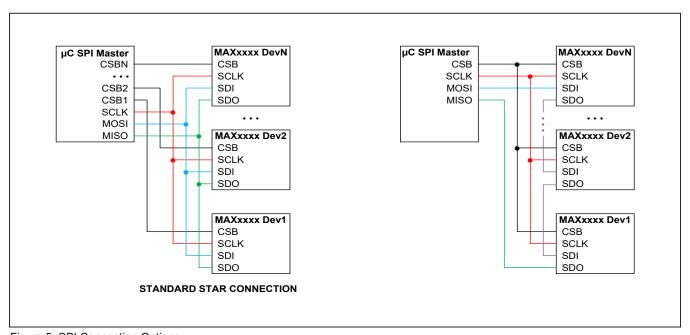

The SCLK line should be driven by the master and hooked up to all slave devices. Only the slave devices (or group of devices) with its CSB line low will accept SCLK. SPI transactions to the slave devices are defined by SCLK rising edges. The MAX20096 can support SPI formats with (CPOL = 0, CPHA = 0) or (CPOL = 1, CPHA = 1). See Figure 4 for alignment examples.

The SDI line should be hooked up to a master-out-slave-in (MOSI) port. A single SDI line can be routed to all SPI slave devices sharing the interface, but only the slave device (or group of devices) with its CSB line low will accept the SDI data. The  $\mu$ C should update SDIN in response to SCLK falling edges so the slave can latch data in on SCLK rising edges.

The SDO line should be hooked up to a master-in-slave-out (MISO) port. A single SDO line can be routed to all SPI slave devices sharing the interface, but only the slave device (or group of devices) with its CSB line low can access and drive the shared SDO bus. The slave updates SDO in response to SCLK falling edges so the  $\mu C$  can latch data in on SCLK rising edges.

#### Standard (Star) Device Connections (DCHN = 0)

The SPI interface allows multiple devices to share the SPI interface, with the active device for the transaction being selected by pulling its unique CSB port low. Note that each slave device on the interface requires a dedicated CSB line from the master. The SCLK, SDI, and SDO lines are common to all devices. A total of (3 + N) lines is required for an interface supporting N slave devices. Transaction-qualification criteria remain in effect, and in write mode the device executes the instructions present in the last 16 bits of a qualified transaction. In read mode, a device operating in standard mode (DCHN = 0) will return the requested data through SDO during the read-mode transaction. A standard connection example is shown in Figure 5.

Figure 4. SPI Transaction Format

#### **Daisy-Chain Device Connections (DCHN = 1)**

The SPI interface also allows a group of similar devices to share a single CSB line and effectively function as a single extended device employing a daisy-chain connection. In a daisy-chain, the  $\mu C$  MOSI line is attached to the SDI pin of the first device in the chain. The SDO of each device is then connected to the SDI of the next device in the chain, and the SDO of the final device is connected to the  $\mu C$  MISO line. The CSB and SCLK lines are common to all devices within the group. A total of four lines are required for an interface supporting a group consisting of any number of devices; however, the SPI transaction length becomes N x 16 bits, where N is the number of devices in the group or chain.

Transaction-qualification criteria remain in effect, and in write mode each device executes the instructions present in the last 16 bits of a qualified transaction. In read mode, once properly configured (DCHN = 1), a daisy-chained array of devices register the request for data to be read back based on the last 16 bits of a qualified transaction. The requested data is then read back through the SDO pin by each device in the chain during the initial 16-bit data frame of the following transaction, allowing the data from all

devices to be read back in a single extended transaction, regardless of whether the following transaction is a read or write mode (minimizing communication overhead).

A daisy-chain connection example is shown in <u>Figure 5</u>. All daisy-chain examples use the conventions shown in <u>Figure 5</u>. The top device in the chain (SDI connected to MOSI) is referred to as device N, while the bottom device in the chain (SDO connected to MISO) is device 1.

#### Status/Address-Selection Bit (ST/AB)

This configuration bit is only used in daisy-chain mode and tells the MAX20096 if the internal transaction log (LOG[15:0]) assembled in response to a read mode transaction will include up to four bits of device status information ST[3:0] (ST/AB = 1) or the address requested A[3:0] (ST/AB = 0).

#### **Daisy-Chain Initial Configuration Example**

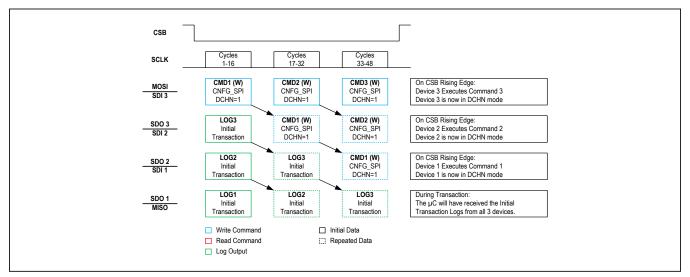

Upon power-up, the  $\mu C$  must first configure the grouped devices in daisy-chain mode (DCHN = 1). This is required to ensure predictable read mode behavior for all future transactions; write mode behavior is identical for standard and daisy-chain configured devices.

Figure 5. SPI Connection Options

### Dual-Channel Synchronous Buck, High-Brightness LED Controller with and without SPI Interface

In order to configure N devices in daisy-chain mode, issue a SPI write mode transaction N x 16 SCLK cycles in length writing the CNFG\_SPI register N times with DCHN = 1. Other aspects of the interface could also be configured at this time, depending on part options. During this transaction, the devices will present the Initial Transaction Log on their SDO ports, allowing the  $\mu$ C a chance to confirm integrity of the connection. An illustration of the transaction is shown in Figure 6.

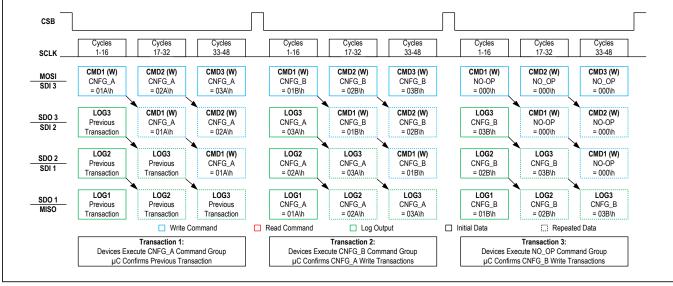

#### **Daisy-Chain Write-Mode Example**

Once properly configured, daisy-chained devices are always addressed as a group. Only full N x 16-bit frames

should be used with a chain of N devices. NO-OP commands should be used when it is necessary to write to some devices in the chain, leaving the others untouched.

<u>Figure 7</u> shows an example of a multiple-transaction write-mode operation to arbitrary configuration registers. Although here each transaction wrote to the same register address for all devices (albeit with different data to each device), this is not required. Also note the  $\mu C$  can confirm the previous write-mode transaction during the next transaction (regardless of read/write mode). Finally, a NO-OP transaction shows how the 2nd transaction can be verified without disturbing register contents.

Figure 6. Configuring a Group of Daisy-Chained Devices

Figure 7. Writing to a Group of Daisy-Chained Devices

### Dual-Channel Synchronous Buck, High-Brightness LED Controller with and without SPI Interface

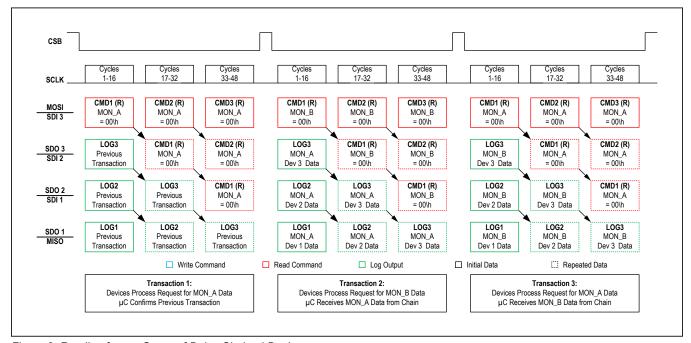

#### **Daisy-Chain Read-Mode Example**

Once properly configured, daisy-chained devices are always addressed as a group. Only full N x 16-bit frames should be used with a chain of N devices. Note that in a daisy-chain, a read transaction is always interpreted as a request for data, with the requested data being provided during the following transaction within the internal transaction log (LOG).

<u>Figure 8</u> shows an example of a multiple-transaction read-mode operation from arbitrary supervisory monitor registers. Here each transaction reads from the same address for all devices; this is not required, but may be recommended to simplify record keeping. Also note the  $\mu C$  receives the previously requested data during the following transaction (regardless of read/write mode).

Note the data provided in the LOG readback frames is fetched during the transaction where it is to be read back (rather than at the end of the transaction where it was requested). This ensures the latest information is provided to the  $\mu C$ .

Finally, one could imagine continuously repeating transactions 2 and 3 to realize a continuous-monitoring sequence of critical-device performances. Once the sequence is set

up, communication overhead is minimized, since data is continuously provided to the  $\mu$ C, with negligible latency due to timing of the fetch operation. This sequence can be extended to a series of monitor readback commands of arbitrary length.

#### Safety PullUp/Pullown Resistors

To guard against broken SPI interface connections, the MAX20096 includes internal safety terminations on all interface input ports. SCLK and SDI have internal pull-downs to AGND. CSB and RESETB (if present) have internal pullups to  $V_{\text{IO}}$ . All safety resistors are  $100 k\Omega$  nominal.

The internal safety resistors can be individually enabled or disabled using SPI configuration bits (SFT\_CLK, SFT\_SDI, SFT\_CSB, SFT\_RB) with a high state (default), indicating that safety termination is enabled/engaged and a low state, indicating it is disengaged. This allows the user to eliminate loading currents when the safety resistors are not needed. Note pullup resistors to  $V_{IO}$  will still have a resistor and diode connection to  $V_{IO}$  even if disengaged (limiting CSB and RESETB voltages to  $V_{IO}$  + 0.3V to avoid conduction).

Figure 8. Reading from a Group of Daisy-Chained Devices

#### **SPI Transactions**

#### **Write-Mode Transactions**

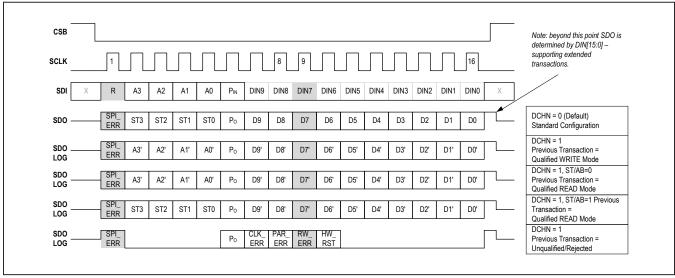

A properly constructed write mode transaction will be made up of N 16-bit data frames. Each SDI data frame from the master (or the previous device in the chain) will contain a R/WB bit, a four bit Address or Command, a parity bit, and ten bits of Input Data or Instructions. During a write mode transaction, the MAX20096 will output data on the SDO line; both transaction log and repeated transaction data will be transferred through SDO. The MAX20096 will only accept and execute qualified SPI transactions, based on the last 16 bits of data received. Details of write mode transactions are explained below and summarized in Figure 9.

Note there is no difference in MAX20096 behavior in standard and daisy-chain configurations during write mode transactions. This is required so that devices hooked up in daisy-chain configurations can be written into daisy-chain mode (DCHN = 1).

Write Bit — R/WB = 0 (DIN15): Write-mode transactions are identified by R/WB = 0 in the MSB position of a 16-bit data frame.

Address — A[3:0] (DIN[14:11]): Write-mode transactions allow new information to be written to internal configuration registers within the device. The configuration register address to be written is indicated by A[3:0] within the data

frame. In this format, up to 16 register addresses are supported (0\h thru F\h) for write-mode access.

**SDI Parity Bit** — **Pin (DIN10):** Write-mode transactions are protected by a parity bit (P) facilitating an odd parity check on the SDI data frame. The parity bit for each 16-bit data frame is calculated by the sending device (master) as the inverse of the bit-wise XOR of the 15 bits of information in the data frame. The sending device (master) must embed the correct parity bit (P) within each data frame for the transaction to qualify for execution:

P = NOT( XOR(R/WB, A3, A2, A1, A0, D9, D8, D7, D6, D5, D4, D3, D2, D1, D0) )

The receiving device (slave) only accepts/executes the command if the bit-wise XOR of the entire frame content, including the parity bit, is 1 (indicating an odd number of 1s are present in the 16-bit data frame, as received):

OK = XOR(R/WB, A3, A2, A1, A0, P, D9, D8, D7, D6, D5, D4, D3, D2, D1, D0))

**Input Data** — **DIN[9:0]** (**DIN[9:0]**): The 10 LSBs of data in the 16-bit data frame represent data to be written to the requested register, or describe internal operations to be executed.

Output Data — LOG[15:0] and Delayed DIN[15:0]: During write-mode transactions, the MAX20096 outputs data through the SDO line.

Figure 9. SPI Write-Mode Transactions

### Dual-Channel Synchronous Buck, High-Brightness LED Controller with and without SPI Interface

In write mode, the MAX20096 relays the contents of the internal transaction log register (LOG[15:0]) through SDO during the 16-bit data frame immediately following the falling edge of CSB. See the *Internal Transaction Log* section for a detailed explanation of content.

If further SCLK cycles are provided in the transaction (as required for daisy-chain applications), the MAX20096 relays the previously received SDI data frame with a 16-cycle delay out through the SDO port, providing the previous data frame content without modification. This is required to allow the write-mode instructions to be propagated to the next device in a daisy-chain configuration.

**Note:** This method also provides the  $\mu$ C an opportunity to check the SPI interface integrity, since the transaction log content of the previously qualified/executed transaction (N x 16 bits) is relayed back to the  $\mu$ C through SDO during each complete single or extended transaction.

Write Mode Qualification Check (SPI\_ERR): To qualify for write-mode execution, the following conditions must be met:

- SPI transaction must be exactly N x 16 bits in length (no CLK ERR recorded)

- SDI data frame parity check must pass (no PAR\_ ERR recorded)

- A[3:0] must select a valid write-accessible register or command (no RW\_ERR recorded)

- RESETB must not have been asserted during the transaction (no RW ERR recorded)

If the SPI transaction is qualified, the instruction is executed, any requested internal register contents are updated, and the internal transaction log updated to indicate the successful transaction.

If the SPI write transaction is not qualified, the instruction is not executed, the device's internal SPI\_ERR indicator and appropriate SPI diagnostic bit are set, and the internal transaction log updated to indicate the failed transaction. The SPI\_ERR bit is returned in response to later read- and

write-mode transactions, notifying the  $\mu C$  that the SPI interface may be compromised.

#### **Read-Mode Transactions**

A properly constructed read-mode transaction is made up of N 16-bit data frames. Each SDI data frame from the master (or the previous device in the chain) contains a R/WB bit, 4-bit address request, parity bit, and 10 bits of data set to all zeros (000\h). During a read-mode transaction, the MAX20096/MAX20097 output data on the SDO line; the content of the SDO data frame is determined by the device configuration (standard or daisy-chain), as described in detail below. The MAX20096 only accepts qualified SPI transactions, based on the last 16 bits of data received. Details of read-mode transactions are explained below and summarized in Figure 8.

**Note:** There is no difference in MAX20096 behavior in standard and daisy-chain configurations during readmode transactions after the initial 16-bit data frame following a CSB falling edge; however, the data presented on SDO during the initial 16-bit data fame depends on the device configuration mode (DCHN and ST/AB). To provide predictable readback results, devices connected in daisy-chain configurations should be written into daisy-chain mode (DCHN = 1) prior to performing any readmode transactions.

**Read Bit** — **R/WB = 1 (DIN15):** Read-mode transactions are identified by R/WB = 1 in the MSB position of a 16-bit data frame.

Address — A[3:0] (DIN[14:11]): Read-mode transactions allow new information to be read from internal registers within the device. The register address to be read back is indicated by A[3:0] within the data frame. In this format, up to 16 register addresses are supported (0\h thru F\h) for read-mode access.

### Dual-Channel Synchronous Buck, High-Brightness LED Controller with and without SPI Interface

**SDI Parity Bit** — **Pin (DIN10):** Read-mode transactions are protected by a parity bit (P), facilitating an odd parity check on the SDI data frame. The parity bit for each 16-bit data frame is calculated by the sending device (master) as the inverse of the bit-wise XOR of the 15 bits of information in the data frame. The sending device (master) must embed the correct parity bit (P) within each data frame for the transaction to qualify for execution, since DIN[8:0] needs to be all zeros for read-mode qualification checks, the parity calculation can be simplified:

P = NOT( XOR(R/WB, A3, A2, A1, A0, D9, D8, D7, D6, D5, D4, D3, D2, D1, D0) )

The receiving device (slave) only accepts/executes the transaction if the bit-wise XOR of the entire frame content, including the parity bit, is 1 (indicating an odd number of 1s are present in the 16-bit data frame as received):

OK = XOR(R/WB, A3, A2, A1, A0, P, D9, D8, D7, D6, D5, D4, D3, D2, D1, D0))

**Input Data** — **DIN[9:0]** (**DIN[9:0]**): The 10 LSBs of data in a read-mode 16-bit data frame must be set to zero (000\h).

# Standard Output Data — Current Status[3:0] + Data Requested[9:0] and Delayed DIN[15:0]

The MAX20096 operating in standard mode (DCHN = 0) relays the SPI\_ERR status, up to 4 bits of general status data (ST[3:0]), a calculated SDO parity bit covering the entire 16-bit SDO frame, and the 10 bits of data requested

by A[3:0] in direct response to an incoming read-mode transaction.

Although not recommended or required in standard read mode, if further SCLK cycles are provided in the transaction (as would be required for daisy-chain applications), the MAX20096 relays the previously received SDI data frame with a 16-cycle delay out through the SDO port, providing the previous data frame content without modification.

Note that standard mode readback data is fetched when A[3:0] is known, and may not be accurate or current if cleared by RESETB activity later during the SPI read transaction.

# Daisy-Chain Output Data — LOG[15:0] and Delayed DIN[15:0]

The MAX20096 relays the contents of the internal transaction log (LOG[15:0]) through SDO during the 16-bit data frame immediately following the falling edge of CSB. See the *Initial Transaction Log* section for a detailed explanation of content. Conceptually, in daisy-chain mode, the register data requested from each device with a read-mode transaction will be provided during the following SPI transaction, which is required since daisy-chained devices must execute the command present in the last 16 bits of the transaction. Also, once a device is programmed into daisy-chain mode, there is no difference in SDO content for read- and write-mode transactions. The latest LOG is always returned during the initial 16-bit data fame.

Figure 10. SPI Read Mode Transactions

### Dual-Channel Synchronous Buck, High-Brightness LED Controller with and without SPI Interface

If further SCLK cycles are provided in the transaction (as required for daisy-chain applications), the MAX20096 will relay the previously received SDI data frame with a 16 cycle delay out through the SDO port, providing the previous data frame content without modification. This is required to allow the read mode instructions to be propagated to the next device in a daisy-chain configuration.