**THAT 2162**

## **FEATURES**

- Two Independent Channels

- Wide Dynamic Range: >118 dB

- Wide Gain Range: >130 dB

- Exponential (dB) Gain Control

- Low Distortion: 0.05% typ.

- Wide Supply Voltage Range:

- $\pm 2.25 \text{V} \sim \pm 16 \text{V}$

- Low Supply Current: 5.2 mA typ. (±15V)

- 3 mA typ. (±5V)

- Dual Control Ports (pos/neg)

- Low Cost

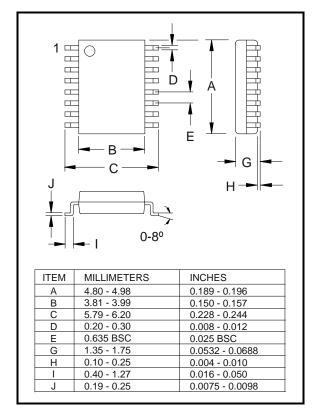

- Small Package (16-pin QSOP)

## **APPLICATIONS**

- Faders

- Panners

- Compressors & Limiters

- Gates & Expanders

- Mixers

- Equalizers

- Filters

- Oscillators

## **Description**

THAT 2162 contains two high-performance Blackmer® voltage-controlled amplifiers (VCAs). With two opposing-polarity, voltage-sensitive control ports, they offer wide-range exponential control of gain and attenuation with low signal distortion. Both VCAs are trimmed at wafer stage to deliver low distortion and control-voltage feedthrough without further adjustment. However, external symmetry adjustment is possible to further optimize distortion and control feedthrough for critical applications.

The 2162 operates from a split power supply up to  $\pm 16$  Vdc, drawing only 5.2mA at  $\pm 15$ V and 3 mA at  $\pm 5$ V. The part can also operate at supply voltages as low as  $\pm 2.25$ V, making it suitable for battery-operated applications.

The two VCAs are independent of each other, sharing only their power supply connections. The 2162 is extremely flexible and capable of being configured for a wide range of stereo or multichannel applications. It is available in a RoHS-compliant 16-pin QSOP package.

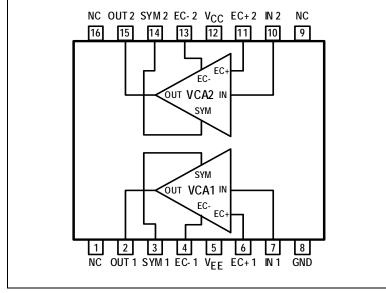

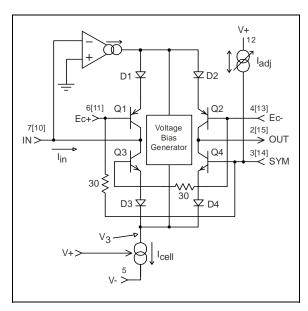

Figure 1. THAT 2162 Block Diagram

| Pin Name        | Pin Number |

|-----------------|------------|

| NC              | 1          |

| OUT 1           | 2          |

| SYM 1           | 3          |

| Ec- 1           | 4          |

| $V_{EE}$        | 5          |

| Ec+ 1           | 6          |

| IN 1            | 7          |

| GND             | 8          |

| NC              | 9          |

| IN 2            | 10         |

| Ec+ 2           | 11         |

| V <sub>cc</sub> | 12         |

| Ec- 2           | 13         |

| SYM 2           | 14         |

| OUT 2           | 15         |

| NC              | 16         |

Table 1. Pin Assignments

| Order Number |

|--------------|

| 2162Q16-U    |

|              |

Table 2. Ordering Information

## SPECIFICATIONS<sup>1</sup>

# Absolute Maximum Ratings<sup>2</sup>

Operating Temperature Range (TOP) -40 to +85 °C Supply Voltages (V<sub>CC</sub>, V<sub>EE</sub>)  $\pm 18$ V Junction Temperature (T<sub>J</sub>) +125 °C VCA Control Voltage  $\pm 0.6$  V Storage Temperature Range (T<sub>ST</sub>) -40 to +125 °C Input or Output Voltage  $\pm 0.5$  V

| Electrical Characteristics <sup>3</sup> |                                                                          |                                                                                                                                       |                  |                        |              |                                          |

|-----------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------|--------------|------------------------------------------|

| Parameter                               | Symbol                                                                   | Conditions                                                                                                                            | Min              | Тур                    | Max          | Units                                    |

| Positive Supply Voltage                 | V <sub>cc</sub>                                                          | Referenced to GND                                                                                                                     | +2.25            | _                      | +16          | V                                        |

| Negative Supply Voltage                 | $V_{EE}$                                                                 | Referenced to GND                                                                                                                     | -2.25            | _                      | -16          | V                                        |

| Supply Current                          | I <sub>CC</sub><br>I <sub>EE</sub><br>I <sub>CC</sub><br>I <sub>EE</sub> | No Signal $V_{CC}$ =+15V, $V_{EE}$ = -15V $V_{CC}$ =+15V, $V_{EE}$ = -15V $V_{CC}$ =+5V, $V_{EE}$ = -5V $V_{CC}$ =+5V, $V_{EE}$ = -5V | _<br>_<br>_<br>_ | 5.2<br>-5.2<br>3<br>-3 | 7<br>-7<br>— | mA<br>mA<br>mA<br>mA                     |

| Equivalent Input Bias Curre             | ent I <sub>B</sub>                                                       | 0 dB Gain                                                                                                                             | _                | 3                      | _            | nA                                       |

| Input Offset Voltage                    | $V_{OFF(IN)}$                                                            | 0 dB Gain                                                                                                                             | _                | -7                     | _            | mV                                       |

| Output Offset Voltage Char              | nge <sup>4</sup> Δ V <sub>OFF(OUT)</sub>                                 | $R_{OUT}$ = 20 k $\Omega$<br>0 dB gain<br>+15 dB gain                                                                                 | _                | ±1<br>±3               | ± 5<br>± 20  | mV<br>mV                                 |

| Gain Cell Idling Current                | I <sub>IDLE</sub>                                                        | 0 dB Gain                                                                                                                             |                  | 20                     |              | μΑ                                       |

| Power Supply Rejection Ra               | atio PSRR                                                                | 0 dB Gain, Rin = Rout = 20 kΩ, 100 Hz<br>Positive supply, 100 Hz<br>Negative supply, 100 Hz                                           |                  | 80<br>75               | =            | dB<br>dB                                 |

| Max. I/O Signal Current                 | i <sub>IN(VCA)</sub> + i <sub>OUT(VCA)</sub>                             | $V_{CC}$ =+15V, $V_{EE}$ = -15V $V_{CC}$ =+5V, $V_{EE}$ = -5V                                                                         |                  | ± 1.5<br>± 815         |              | mA <sub>peak</sub><br>μΑ <sub>peak</sub> |

| VCA Gain Range                          |                                                                          |                                                                                                                                       | -70              | _                      | +60          | dB                                       |

| Gain-Control Constant                   | E <sub>c+</sub> /Gain (dB)                                               | -60 dB < gain < +60 dB<br>$V_{CC}$ = +15V, $V_{EE}$ = -15V<br>$V_{CC}$ = +5V, $V_{EE}$ = -5V                                          | _                | 6.4<br>6.1             | _            | mV/dB<br>mV/dB                           |

| Gain-Control Tempco                     | $\Delta E_{c}/\Delta T_{CHIP}$                                           | Ref T <sub>CHIP</sub> =27°C                                                                                                           | _                | +0.33                  | _            | %/°C                                     |

| Gain Control Linearity                  |                                                                          | -60 dB to +40 dB Gain                                                                                                                 | _                | 1                      | _            | %                                        |

| Off Isolation                           |                                                                          | 1 kHz, Ec+ = -0.45 V, Ec- = +0.45 V                                                                                                   | _                | 130                    | _            | dB                                       |

| Output Noise                            | e <sub>N(OUT)</sub>                                                      | 22Hz~22kHz, $R_{IN}$ = $R_{OUT}$ = 20 kΩ<br>0 dB gain<br>+15 dB gain                                                                  |                  | -97.5<br>-86           | -95<br>-84   | dBV<br>dBV                               |

| Crosstalk                               |                                                                          | 1 kHz, 0 dB Gain, Rin = Rout = 20 k $\Omega$                                                                                          | _                | 110                    | _            |                                          |

<sup>&</sup>lt;sup>1</sup> All specifications are subject to change without notice.

If the devices are subjected to stress above the Absolute Maximum Ratings, permanent damage may result. Sustained operation at or near the Absolute Maximum Ratings conditions is not recommended. In particular, like all semiconductor devices, device reliability declines as operating temperature increases.

<sup>&</sup>lt;sup>3</sup> Unless otherwise noted, TA=25°C, VCC=+15V, VEE= -15V.

<sup>&</sup>lt;sup>4</sup> Reference is to output offset with -40 dB VCA gain.

| Electrical Characteristics (con't) <sup>3</sup> |        |                                                         |      |      |      |       |

|-------------------------------------------------|--------|---------------------------------------------------------|------|------|------|-------|

| Parameter                                       | Symbol | Conditions                                              | Min  | Тур  | Max  | Units |

| Total Harmonic Distortion                       | THD    | $V_{IN}$ = 0dBV, 1kHz, $E_{C+}$ = $E_{C-}$ = 0V         | _    | 0.05 | 0.12 | %     |

|                                                 |        | $V_{IN}$ = -5dBV, 1kHz, $E_{C+}$ = 0V, $E_{C-}$ = -90mV | _    | 0.09 | 0.15 | %     |

|                                                 |        | $V_{IN}$ = +10dBV, 1kHz, $E_{C+}$ = 0V, $E_{C-}$ = 90mV | _    | 0.09 | 0.15 | %     |

| Slew Rate                                       |        | 0 dB Gain, Rin = Rout = 20 k $\Omega$                   | _    | 6.5  | _    | V/μs  |

| Gain at 0V Control                              | $G_0$  | $E_C+ = E_C- = 0V$                                      | -1.0 | 0    | +1.0 | dB    |

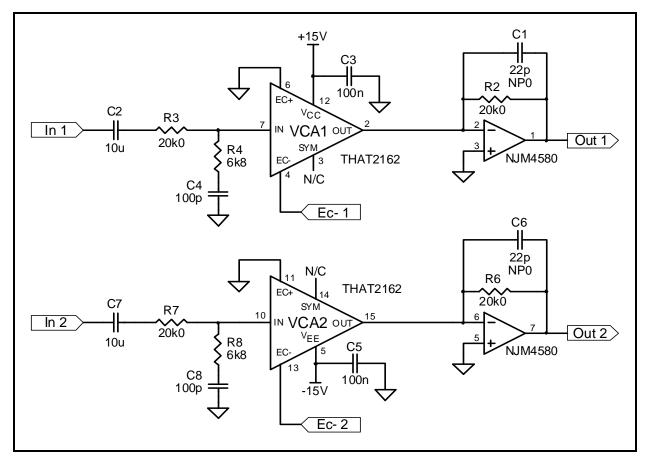

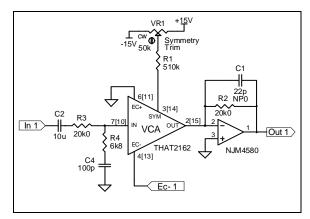

Figure 2. Typical Application Circuit

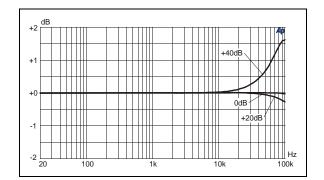

Figure 3. 2162 Frequency Response Vs. Gain

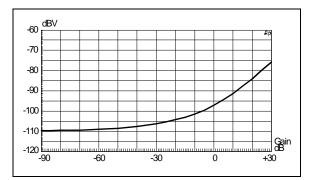

Figure 4. 2162 Noise (22 kHz NBW) Vs. Gain

## **Theory of Operation**

The THAT 2162 VCA is designed for high performance in audio-frequency applications requiring exponential gain control, wide dynamic range, low control-voltage feedthrough, and low cost. This part controls gain by converting an input current signal to a bipolar logged voltage, adding a dc control voltage, and re-converting the summed voltage back to a current through a bipolar antilog circuit.

Figure 5 presents a considerably simplified internal circuit diagram of the IC. The ac input signal current flows in pin 7 [10]¹, the input pin. An internal operational transconductance amplifier (OTA) works to maintain pin 7 [10] at a virtual ground potential by driving the emitters of Q1 and (through the Voltage Bias Generator) Q3. Q3/D3 and Q1/D1 act to log the input current, producing a voltage, V3, which represents the bipolar logarithm of the input current. The voltage at the junction of D1 and D2 is the same as V3, but shifted by four forward Vbe drops.

## Gain Control

Since pin 2 [15], the output, is usually connected to a virtual ground, Q2/D2 and Q4/D4 take the bipolar antilog of V3, creating an output current which is a precise replica of the input current. If pin 6 [11] ( $E_{\rm C+}$ ) and pin 4 [13] ( $E_{\rm C-}$ ) are held at ground, the output current will equal the input current. For pin 6 [11] positive or pin 4 [13] negative, the output current will be scaled larger than the input current. For pin 6 [11] negative or pin 4 [13] positive, the output current is scaled smaller than the input.

The scale factor between the output and input currents is the gain of the VCA. Either pin 6 [11]  $(E_{\rm C+})$  or pin 4 [13]  $(E_{\rm C})$ , or both, may be used to control gain. Gain is exponentially proportional to the voltage at pin 6 [11], and exponentially

Figure 5. Simplified internal circuit

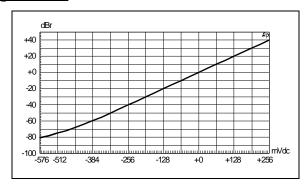

Figure 6. Gain Vs. Control Voltage (Ec+) @ 1 kHz

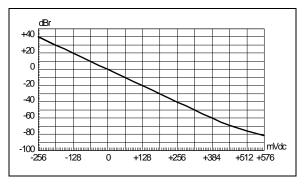

Figure 7. Gain Vs. Control Voltage (Ec-) @ 1 kHz

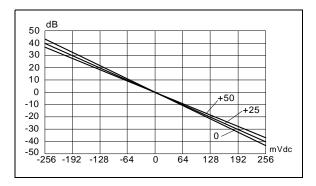

Figure 8. Gain Vs. Control Voltage (Ec-) with Temp (°C)

proportional to the negative of the voltage at pin 4 [13]. Therefore, pin 6 [11] ( $E_{\text{C+}}$ ) is the positive control port, while pin 4 [13] ( $E_{\text{C-}}$ ) is the negative control port. Because of the exponential characteristic, the control voltage sets gain linearly in decibels. Figure 6 shows the decibel current gain of a 2162 versus the voltage at  $E_{\text{C+}}$ , while Figure 7 shows gain versus  $E_{\text{C-}}$ .

### **Temperature Effects**

The logging and antilogging in the VCA depends on the logarithmic relationship between voltage and current in a semiconductor junction (in particular, between a transistor's Vbe and Ic). As is well known, this relationship is temperature dependent. Therefore, the gain of any log-antilog VCA depends on its temperature.

<sup>&</sup>lt;sup>1</sup> Pin number references are for VCA1, with VCA2 shown in brackets.

Figure 8 shows the effect of temperature on the negative control port. (The positive control port behaves in the same manner.) Note that the gain at  $E_{\rm c}=0~V$  is 0 dB, regardless of temperature. Changing temperature changes the scale factor of the gain by 0.33%/C, which pivots the curve about the 0 dB point.

Mathematically, the 2162's gain characteristic is

$$Gain = \frac{E_{C+} - E_{C-}}{(0.0064)(1+0.0033\Delta T)},$$

Eq. 1

where  $\Delta T$  is the difference between room temperature (25°C) and the actual temperature, and Gain is the gain in decibels. At room temperature, this reduces to

$$Gain = \frac{E_{C+} - E_{C-}}{0.0064}$$

, Eq. 2

If only the positive control port is used, this becomes

$$Gain = \frac{E_{C+}}{0.0064}$$

, Eq. 3

If only the negative control port is used, this becomes

$$Gain = \frac{-E_{C^-}}{0.0064}$$

. Eq. 4

#### DC Bias Currents

The 2162 current consumption is determined by an internal bias generator ( $I_{\rm CELL}$ ), which varies its current based on the power supply voltage. At  $V_{\rm CC}{=}{-}V_{\rm EE}{=}15V,\ I_{\rm CELL}$  is approximately 2.25 mA; at  $V_{\rm CC}{=}{-}V_{\rm EE}{=}5V,\ I_{\rm CELL}$  is approximately 1.15 mA.

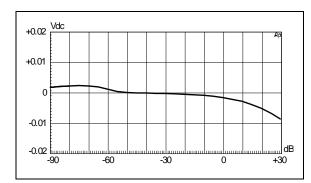

Figure 9. Offset Vs. Gain (Ec+)

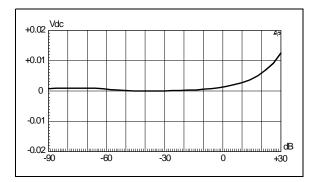

Figure 10. Offset Vs. Gain (Ec-)

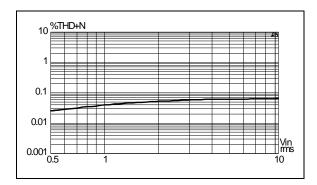

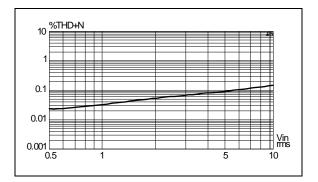

Figure 11. THD+Noise Vs. Input Level, 0 dB Gain

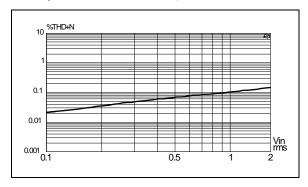

Figure 12. THD+Noise Vs. Input Level, +15 dB Gain

Figure 13. THD+Noise Vs. Input Level, -15 dB Gain

Another  $\sim 350~\mu\text{A}$  is used to bias each OTA.  $I_{\text{CELL}}$  is split in two parts: about 250  $\mu\text{A}$  is necessary for the bias generator, the rest is available for the sum of input and output signal current.

#### Trimming

The VCA symmetry (actually, the combined  $V_{\rm BE}$  offsets of the gain cell transistors) is trimmed for low distortion and control-voltage feedthrough during wafer probe. However, limited trim resolution and shifts during IC packaging limit the ultimate pre-trimmed performance of the finished part. In general, the second harmonic distortion and offset change with gain can be reduced via external trimming, as shown in the circuit of Figure 14. Pin 3 [14] (SYM) allows this adjustment. The 2162 includes on-chip  $30\Omega$  resistors between the SYM pins and their respective  $E_{\rm C+}$  pins. The external trim circuitry shown provides for up to  $\pm$  880  $\mu V$  offset across these pins. Symmetry should be trimmed for

Page 6 of 11

minimum THD with a modest level (e.g.,  $\sim 1$  Vrms), middle-frequency (e.g.,  $\sim 1$  kHz) sine wave input.

The parameter that is being trimmed here (the combined  $V_{\text{BE}}$  offset of the gain cell transistors) is a constant that varies depending on the specific IC involved. It is substantially independent of power supply voltage, though the setting will vary slightly with power supply voltage. Note that the on-board trim is set with  $\pm 15$  V power supply rails. Typically, the 1 kHz THD+N at 0 dB gain and 1 Vrms input will

Figure 14. External trimming circuit

vary by approximately 0.003% - 0.005% per 5 V change in the supply voltage from  $\pm 15$  V.

Most parts will require less than  $600~\mu V$  of trim adjustment. But, in the circuit of Figure 14, the available range of adjustment is directly proportional to the power supply voltage. For best results, R1 should be scaled proportional to the supply voltage.

If the external symmetry circuitry is omitted, pins 3 and 14 should be left open, as shown in Figure 2.

## DC Feedthrough

Normally, a small dc error term flows in pin 2 [15] (the output). When the gain is changed, the dc term changes. This control-voltage feedthrough increases with gain. See Figures 9 and 10 for typical curves for dc offset vs. gain. As noted above, dc feedthrough is affected by the symmetry trim.

#### Audio Performance

The 2162 VCA design, fabrication and testing ensure good audio performance when used as recommended. In particular, the 2162 maintains low distortion over a wide range of gain, cut and signal levels. Figures 11 through 13 show typical distortion performance for representative samples of the part.

## **Applications**

### Input

Input signals are currents in pin 7 [10] -- the 2162's VCA IN pins. These pins are virtual grounds with negative feedback provided internally. The input resistor  $R_{\rm 3}~(R_7)$  in Figure 2 should be scaled to convert the available ac input voltage to a current within the linear range of the device. Generally, peak input currents should be kept under 750  $\mu A$  for best distortion performance.

Refer to Figures 11 through 13 to see how distortion typically varies with signal level for 0 dB, +15 dB and -15 dB gain. The circuit of Figure 2, Page 3 was used to generate these curves.

For a specific application, the acceptable distortion will usually determine the maximum signal current level which may be used. Note that, with  $20~k\Omega$  current-to-voltage converting resistors, distortion remains low even at 10~V rms input at 0~dB or -15~dB gain, and at 1.7~V rms input at +15~dB gain ( $\sim 10~V$  rms output).

#### AC Coupling

Pin 7 [10], the VCA IN pin will also have a small dc offset away from ground. It is important to prevent this dc offset from becoming a dc current in the input, since any dc input currents will be modulated by gain changes, thereby becoming audible as thumps. To prevent the dc input offset voltage and the previous stage's dc output offset from causing dc input currents, the input pins are normally ac-coupled ( $C_2$ ,  $C_7$  in Figure 2). This blocks such offset currents and reduces dc offset variation with gain. Choose a capacitor which will give acceptable low frequency performance for the application. The mean offset voltage is slightly negative, so if a polarized capacitor is used, it should be oriented with the negative side toward the VCA input.

#### Summing Multiple Input Signals

Multiple signals may be summed via multiple resistors, just as with an inverting opamp configuration. In such a case, a single coupling capacitor may be located next to pin 1 rather than multiple capacitors at the driven ends of the summing resistors. However, take care that the capacitor does not pick up stray signals.

#### Stability

In order to guarantee stability at low gains, the source impedance seen at the VCA IN terminal must be less than 5  $k\Omega$  above approximately 250 kHz. The  $R_4\text{-}C_4$  and  $R_8\text{-}C_8$  networks in Figure 2 ensure this.

### Output

The VCA output signal, at pin 2 (15), is also a current, inverted with respect to the input current. In normal operation, the output current is connected to

a virtual ground node, and converted to a voltage via an external op-amp. The current-to-voltage conversion ratio is determined by the feedback resistor,  $R_2 \ [R_6]$  in Figure 2 connected between the op-amp's output and its inverting input. The resulting signal path through the VCA plus op-amp is non-inverting.

R3 [R7] -- the input resistor -- determines the voltage-to-current conversion at the input, and  $R_2 \ (R_6)$  -- the output resistor -- determines the current-to-voltage conversion rate at the output. As a result, the familiar ratio of Rf /Ri for an inverting opamp will determine the overall voltage gain when the 2162 is set for 0 dB current gain. Since the VCA performs best at settings near unity gain, use the input and feedback resistors to provide design-center gain or loss, if necessary.

A small feedback capacitor around the output opamp is needed to cancel the output capacitance of the VCA. Without it, this capacitance will destabilize most opamps. The capacitance at pin 2 [15] is typically 3 pF The 22 pF capacitor shown at  $C_1$  ( $C_6$ ) ensures stability.

### Voltage Control

The VCA gain is controlled by the voltage applied between pin 6 [11] --  $E_{\rm C^+}$  and pin 4 [13] --  $E_{\rm C^-}$ . Note that any unused control ports should be connected to ground (as  $E_{\rm C^+}$  is in Figure 2). The gain (in decibels) is proportional to ( $E_{\rm C^+}$  -  $E_{\rm C^-}$ ). The constant of proportionality is 6.4 mV/dB for the voltage at  $E_{\rm C^+}$  (relative to  $E_{\rm C^-}$ ). See Figure 6 through 8. Note that neither  $E_{\rm C^+}$  or  $E_{\rm C^-}$  should be driven more than  $\pm 0.6$  V away from ground.

## Positive and Negative

Note for Figures 9 and 10 that the  $E_{\text{C}}$  port yields lower offset change at very low gains than the  $E_{\text{C+}}$  port. For best performance with large attenuations both control ports can be utilized simultaneously with differential drives.

## Symmetry

As described more fully in the Theory section under "Trimming", Pin 3 [14] -- the SYM pin -- can be used to improve the preprogrammed distortion setting, allowing for finer resolution than available on-chip, and for shifts that may occur during IC packaging. The recommended additional trim circuitry is shown in Figure 14. The wiper resistor R1, shown as 510 k $\Omega$ , is recommended for the ±15V supplies shown. For other power supply voltages, scale R1 directly proportional to the supply voltage.

Adjust the Symmetry control for minimum THD with a modest level (e.g.,  $\sim 1$  Vrms), low-frequency (e.g.,  $\sim 1$  kHz) sine wave input. Since the SYM pins are connected to internal bias generators, if an external symmetry adjustment is omitted, leave the SYM pins open.

#### Control Port Drive Impedance

The control ports are connected directly to the bases of the logging and/or antilogging transistors. The accuracy of the logging and antilogging is dependent on the  $E_{\text{C+}}$  and  $E_{\text{C-}}$  voltages being exactly as desired to control gain. The base current in the core transistors will follow the collector currents, of course. Since the collector currents are signal-related, the base currents are therefore also signal-related. Should the source impedance of the control voltage(s) be large, the signal-related base currents will cause signal-related voltages to appear at the control ports, which will interfere with precise logging and antilogging, in turn causing distortion.

The 2162 VCAs are designed to be operated with zero source impedance at pins 4 [13] and 6 [11], and a high (> 100 k $\Omega$ ) source impedance at pin 3 [14]. To realize all the performance designed into a 2162, keep the source impedance of the control voltage driver well under 50  $\Omega$ .

#### Noise Considerations

The VCA's noise performance varies with gain in a predictable way (shown in Figure 4), but due to the way internal bias currents vary with gain, noise at the output is not strictly the product of a static input noise times the voltage gain commanded. At large attenuation, the noise floor is usually limited by the input noise of the output op-amp and its feedback resistor. At 0 dB gain, the noise floor of  $\sim$  -97.5 dBV is the result of the VCA's output noise current, converted to a voltage by the typical 20  $k\Omega$  I-V converter resistor (R<sub>2</sub> [R<sub>6</sub>] in Figure 2). In the vicinity of 0 dB gain, the noise increases more slowly than the gain: approximately 7.5 dB noise increase for every 10 dB gain increase. Finally, as gain approaches 30 dB, output noise begins to increase directly with gain.

Another factor that influences noise is that the 2162 VCAs act like multipliers: when no signal is present at the signal input, noise at the control input is rejected. So, when measuring noise (in the absence of signal – as most everyone does), even very noisy control circuitry often goes unnoticed. However, noise at the control port of these parts will cause noise modulation of the signal. This can become significant if care is not taken to drive the control ports with quiet signals.

The 2162 VCA has a small amount of inherent noise modulation because of its class AB biasing scheme, where the shot noise in the core transistors reaches a minimum with no signal, and increases with the square root of the instantaneous signal current. However, in an optimum circuit, the noise floor rises only to -93.5 dBV with a 50  $\mu A$  rms signal at unity gain — 4 dB of noise modulation. By contrast, if a unity-gain connected, non-inverting 5534 opamp is used to directly drive the control port, the noise floor will rise to 91.5 dBV — 6 dB of noise modulation.

To avoid excessive noise, one must take care to use quiet electronics throughout the control-voltage circuitry. One useful technique is to process control voltages at a multiple of the eventual control constant (e.g., 64~mV/dB — ten times higher than the VCA requires), and then attenuate the control signal just before the final drive amplifier. With careful attention to impedance levels, relatively noisy opamps may be used for all but the final stage.

## Stray Signal Pickup

It is also common practice among audio designers to design circuit boards to minimize the pickup of stray signals within the signal path. As with noise in the control path, signal pickup in the control path can adversely effect the performance of an otherwise good VCA. Because it is a multiplier, the 2162 produces second harmonic distortion if the audio signal itself is present at the control port. Only a small voltage at the control port is required: as little as 10  $\mu \rm V$  of signal can increase distortion by over 0.01%. This can frequently be seen at high frequencies, where capacitive coupling between the signal and control paths can cause stray signal pickup.

Because the signal levels involved are very small, this problem can be difficult to diagnose. One clue to the presence of this problem is that the symmetry null for minimum THD varies with frequency. It is often possible to counteract a small amount of pure fundamental picked up in the control path by "misadjusting" the symmetry setting. Since the amount of pickup usually varies with frequency, the optimum trim setting will vary with frequency and level. A useful technique to confirm this problem is to temporarily bypass the control port to ground via a modest-sized capacitor (e.g.,  $10~\mu F$ ). If the distortion diminishes, signal pickup in the control path is the likely cause.

#### Temperature Sensitivity

As shown by Equation 1 (Page 5), the gain of a 2162 VCA is sensitive to temperature in proportion to the amount of gain or loss commanded. The constant of proportionality is 0.33% of the decibel gain commanded, per degree Celsius, referenced to 27°C (300°K). This means that at 0 dB gain, there is no change in gain with temperature. However, at -122 mV, the gain will be +20 dB at room temperature, but will be 20.66 dB at a temperature 10 °C lower.

For most audio applications, this change with temperature is of little consequence. However, if necessary, it may be compensated by a resistor embedded in the control voltage path whose value varies with temperature at the same rate of 0.33%/°C. Such parts are available from RCD Components, Inc, Manchester, NH, USA [+1(603)669-0054], [www.rcd-comp.com] and KOA/Speer Electronics, Bradford, PA, 16701 USA [+1(814)362-5536], [www.koaspeer.com].

Differences Between 2162 and 2180-series VCAs

While the 2162's VCA circuitry is very similar to that of the THAT 2180 Series VCAs, there are several important differences, as follows.

- 1. As noted in the Theory section under "DC Bias Currents," supply current for the 2162 VCA depends on the supply voltage. At  $\pm 5$  V, approximately 850  $\mu$ A is available for the sum of input and output signal currents. This increases to about 1.8 mA at  $\pm 15$  V. (Compare this to  $\sim 1.8$  mA for a 2180 Series VCA when biased as recommended.)

- 2. The control-voltage constant is approximately 6.4 mV/dB when operating from  $\pm 15$ V supplies (it is  $\sim 6.1$ mV/dB in the 2180-series). This difference is due primarily to the higher internal operating

temperature of the 2162 compared to that of the 2180 Series.

3. As noted in the Applications section under "Stability," the source impedance seen at the VCA input must be less than 5 k $\Omega$  at frequencies above 250 kHz. In typical applications using a 20 k $\Omega$  input resistor, this is accomplished via a series network consisting of a 6.8 k $\Omega$  resistor and a 100 pF capacitor to ground.

### Closing Thoughts

THAT Corporation welcomes comments, questions and suggestions regarding these devices, their design and application. Our engineering staff includes designers who have decades of experience in applying our parts. Please feel free to contact us to discuss your applications in detail.

# Package and Soldering Information

The THAT 2162 is available in a 16-pin QSOP package. The package dimensions are shown in Figure 15 below, while the pinout is given in Table 1 on page 1.

The 2162 is available only in a lead-free, "green" package. The lead frame is copper, plated with successive layers of nickel palladium, and gold. This approach makes it possible to solder these devices using lead-free and lead-bearing solders. The plastic mold compound, and the material in which the parts are packaged, contains no hazardous substances as

specified in the RoHS directive. For more information, including MDDS forms which disclose the substances contained in our ICs and their packaging, please visit: www.thatcorp.com/RoHShome.html.

The package has been qualified using reflow temperatures as high as 250°C for 10 seconds. This makes it suitable for use in a 100% tin solder process. Furthermore, the 2162 has been qualified to a JEDEC moisture sensitivity level of MSL1. No special humidity precautions are required prior to flow soldering the parts.

| Package Characteristics  |                                                                   |                              |     |           |     |       |

|--------------------------|-------------------------------------------------------------------|------------------------------|-----|-----------|-----|-------|

| Parameter                | Symbol                                                            | Conditions                   | Min | Тур       | Max | Units |

| Package Style            |                                                                   | See Fig. 15 for dimensions   | 1   | 6 Pin QSC | )P  |       |

| Thermal Resistance       | $\theta_{JA}$                                                     | SO package soldered to board |     | 150       |     | °C/W  |

| Environmental Regulation | vironmental Regulation Compliance Complies with RoHS requirements |                              |     | ments     |     |       |

| Soldering Reflow Profile |                                                                   | JEDEC JESD22-A113-D (250 °C) |     |           |     |       |

Figure 15. QSOP-16 surface mount package

# **Revision History**

| Revision | Date       | Changes                                                                                                                                                                                                                                                                    | Page    |

|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 00       | Sept. 2008 | Release                                                                                                                                                                                                                                                                    |         |

| 01       | Jun. 2010  | -Changed THD spec as follows:  Under Vin = 0 dBV, Changed Typ. from 0.04 to 0.05 and Max. from 0.09 to 0.12  Under Vin = -5 dBV, Changed Typ. from 0.075 to 0.09 and Max. from 0.1 to 0.15  Under Vin = +10 dBV, Changed Typ. from 0.075 to 0.09 and Max. from 0.1 to 0.15 | 2       |

| 02       | Oct. 2010  | -Added footnote 1 "All specifications are subject to change without notice" and renumbered existing footnotes sequentiallyAdded Revision History table.                                                                                                                    | 2<br>11 |