# Synchronous Buck Regulator with PMBUS™, 35 A

# **FAN251030**

### Description

The FAN251030 is a highly efficient synchronous buck regulator with digital interface, capable of operating with an input range from 4.5 V to 18 V and supporting up to 35 A load currents.

The FAN2510xx utilizes a fixed-frequency voltage-mode control architecture to provide a synchronized constant switching frequency while ensuring fast transient response.

Switching frequency and over-current protection can be programmed to provide a flexible solution for various applications. Output over-voltage, under-voltage, over-current, and thermal shutdown protections help prevent damage to the device during fault conditions.

#### **Features**

- VIN Range: 4.5 V to 18 V

- PMBUS 1.3.1 Compatible

- Accurate Voltage, Current and Thermal Telemetry Reporting

- High Efficiency: Over 96% PeakContinuous Output Current: 35 A

- Internal Linear Bias Regulator

- Output Voltage Range: 0.5 V to 5.5 V

- Adjustable Frequency: 200 kHz to 1.8 MHz

- Programmable Soft-Start

- Low Shutdown Current

- Internal Boot Diode

- Thermal Shutdown

- This Device is Pb–Free, Halogen Free/BFR Free, and is RoHS Compliant

### **Typical Applications**

- Server and Desktop Computers, Notebooks, Gaming

- Telecommunications

- High Density Power Solutions

### ON Semiconductor®

www.onsemi.com

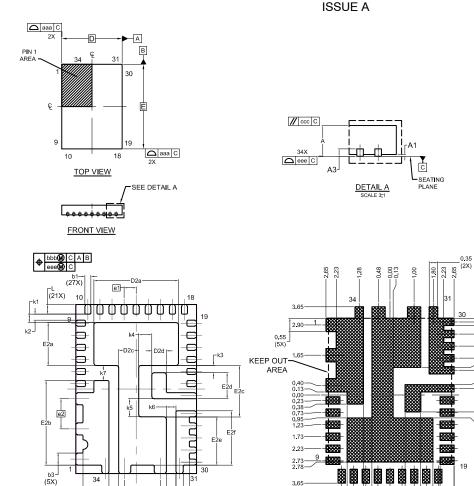

WQFN34 5x7, 0.5P CASE 510CL

#### **MARKING DIAGRAM**

\$Y FAN25 1030 AWLYYWW

FAN251030 = Specific Device Code \$Y = ON Semiconductor Logo A = Assembly Location

WL = Wafer Lot YY = Year WW = Work Week

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 49 of this data sheet.

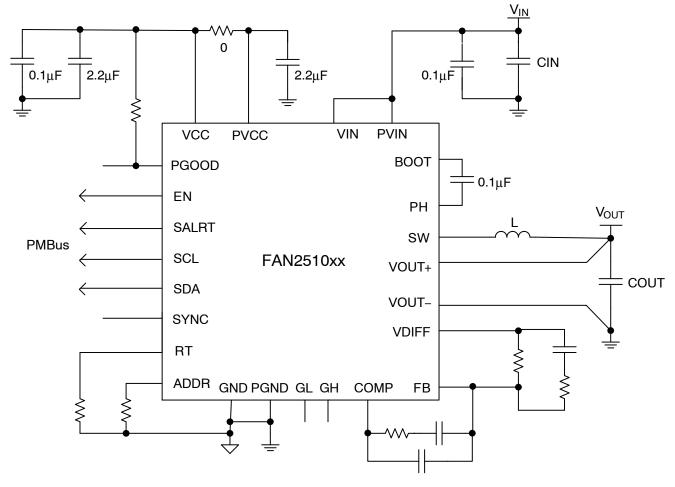

Figure 1. Application Circuit

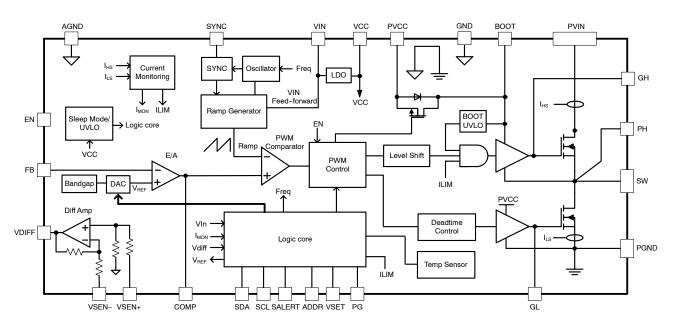

Figure 2. Block Diagram

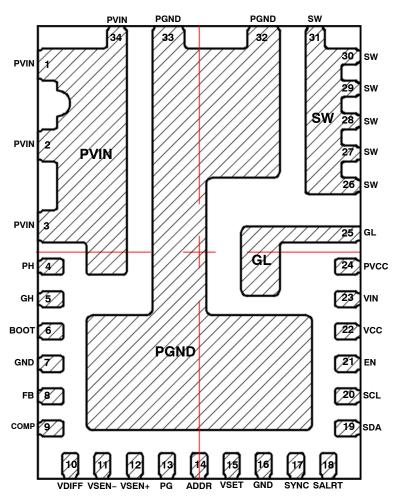

### **PIN CONNECTIONS**

Figure 3. Pin Assignment, Top Transparent View (5x7 mm, 0.5 mm Pin Pitch)

### PIN FUNCTION DESCRIPTION

| Pad/Pin     | Name  | Type   | Description                                                                                                                                                                                                                                                            |

|-------------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3, 34 | PVIN  | Power  | Power Input for the Power stage (High-side MOSFET Drain Connection). Apply Vin voltage always with Vcc capacitor                                                                                                                                                       |

| 4           | PH    | Power  | Return connection for the boot capacitor, internally connected to SW                                                                                                                                                                                                   |

| 5           | GH    | I/O    | High-side MOSFET gate monitor (do not connect anything to this pin)                                                                                                                                                                                                    |

| 6           | воот  | Power  | Supply for high-side MOSFET gate driver. A capacitor from BOOT to PH supplies the charge to turn on the N-channel high-side MOSFET. During the freewheeling interval (low-side MOSFET on), the high-side capacitor is recharged by an internal diode connected to PVCC |

| 7, 16       | GND   | Ground | Analog Ground                                                                                                                                                                                                                                                          |

| 8           | FB    | I/O    | Inverting input to the voltage error amplifier                                                                                                                                                                                                                         |

| 9           | COMP  | I/O    | Output of the voltage error amplifier                                                                                                                                                                                                                                  |

| 10          | VDIFF | I/O    | Output of the VOUT sensing differential amplifier                                                                                                                                                                                                                      |

| 11          | VSEN- | I/O    | Negative Input of the VOUT sensing differential amplifier                                                                                                                                                                                                              |

| 12          | VSEN+ | I/O    | Positive Input of the VOUT sensing differential amplifier                                                                                                                                                                                                              |

| 13          | PG    | I/O    | Power GOOD; open-drain output indicating VOUT is within set limits                                                                                                                                                                                                     |

| 14          | ADDR  | I/O    | PMBUS address programming pin. Use a resistor (with up to 1% tolerance) to set the address                                                                                                                                                                             |

| 15          | VSET  | I/O    | VOUT pre-setting pin. Use a resistor (with up to 1% tolerance) to pre-set the output voltage (PMBUS command can override)                                                                                                                                              |

| 17          | SYNC  | I/O    | Synchronization input or output                                                                                                                                                                                                                                        |

| 18          | SALRT | I/O    | PMBUS Alert pin                                                                                                                                                                                                                                                        |

| 19          | SDA   | I/O    | PMBUS Data pin                                                                                                                                                                                                                                                         |

| 20          | SCL   | I/O    | PMBUS Clock pin                                                                                                                                                                                                                                                        |

| 21          | EN    | I/O    | Enable input (and PMBUS Control pin)                                                                                                                                                                                                                                   |

| 22          | VCC   | Power  | Output of the linear regulator; Supply pin for the controller. Can NOT be separated from PVCC. The capacitor should be always connected to this pin                                                                                                                    |

| 23          | VIN   | Power  | Power input to the linear regulator; also used in the modulator for input voltage feed-forward. Must always be connected even if the LDO is not used                                                                                                                   |

| 24          | PVCC  | Power  | Directly supplies power for the low-side gate driver and boot diode. This pin and VCC can NOT be separated, or connected to the external power supply                                                                                                                  |

| 25          | GL    | I/O    | Low-side MOSFET gate monitor (do not connect anything to this pin)                                                                                                                                                                                                     |

| 26–31       | SW    | Power  | Switching Node; Internally Connected to the High-side MOSFET Source and Low-side MOSFET Drain                                                                                                                                                                          |

| 32, 33      | PGND  | Ground | Power Ground (Low-side MOSFET Source Connection), internally connected to GND                                                                                                                                                                                          |

### **MAXIMUM RATINGS**

All voltages with respect to GND, unless otherwise specified.

| Rating                                      | (Note 1)                                                                                        | Symbol                                | Value                                               | Unit |

|---------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------|------|

| Input Voltage Range                         | referenced to GND (Note 2)                                                                      | $V_{PVIN}, V_{IN}$                    | -0.3 to 25                                          | V    |

| BOOT voltage range:                         | referenced to PVCC<br>referenced to PVCC, < 20 ns<br>referenced to SW, PH<br>referenced to PGND | V <sub>ВООТ</sub>                     | -0.3 to 26<br>-0.3 to 30<br>-0.3 to 6<br>-0.3 to 30 | V    |

| SW voltage range:                           | referenced to PGND<br>referenced to PGND, <20 ns                                                | V <sub>SW</sub> , V <sub>PH</sub>     | -1 to 25<br>-5 to 25                                | V    |

| High-Side MOSFET Gate voltage range:        | referenced to SW, PH referenced to PGND                                                         | V <sub>GH</sub>                       | -0.3 to 6<br>-0.3 to 30                             | V    |

| Low-Side MOSFET Gate voltage range:         | referenced to PGND                                                                              | $V_{GL}$                              | -0.3 to 6                                           | V    |

| Driver Supply Input voltage range           | referenced to PGND                                                                              | V <sub>PVCC</sub>                     | -0.3 to 6                                           | V    |

| Controller Supply Input voltage range       |                                                                                                 | V <sub>VCC</sub>                      | -0.3 to 6                                           | V    |

| Output Voltage Sense voltage range          |                                                                                                 | V <sub>SEN+</sub> , V <sub>SEN-</sub> | -0.3 to 6                                           | V    |

| Differential Amplifier Output voltage range |                                                                                                 | $V_{DIFF}$                            | -0.3 to 6                                           | V    |

| Error Amplifier Input voltage range         |                                                                                                 | $V_{FB}$                              | -0.3 to 6                                           | V    |

| Error Amplifier Output voltage range        |                                                                                                 | $V_{COMP}$                            | -0.3 to 6                                           | V    |

| SYNC voltage range                          |                                                                                                 | V <sub>SYNC</sub>                     | -0.3 to 6                                           | V    |

| Power Good Output voltage range             |                                                                                                 | V <sub>PG</sub>                       | -0.3 to 6                                           | V    |

| Enable Input voltage range                  |                                                                                                 | V <sub>EN</sub>                       | -0.3 to 6                                           | V    |

| Vout Setting Input voltage range            |                                                                                                 | V <sub>VSET</sub>                     | -0.3 to 6                                           | V    |

| PMBUS Data pin voltage range                |                                                                                                 | $V_{SDA}$                             | -0.3 to 6                                           | V    |

| PMBUS Clock input voltage range             |                                                                                                 | V <sub>SCL</sub>                      | -0.3 to 6                                           | V    |

| PMBUS Alert Output voltage range            |                                                                                                 | V <sub>SALERT</sub>                   | -0.3 to 6                                           | V    |

| PMBUS Address Input voltage range           |                                                                                                 | V <sub>ADDR</sub>                     | -0.3 to 6                                           | V    |

| Maximum Junction Temperature                |                                                                                                 | T <sub>J(max)</sub>                   | 150                                                 | °C   |

| Storage Temperature Range                   |                                                                                                 | T <sub>STG</sub>                      | -55 to 150                                          | °C   |

| Lead Temperature Soldering Reflow (Note     | : 3)                                                                                            | T <sub>SLD</sub>                      | 260                                                 | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

### THERMAL CHARACTERISTICS

| Rating                                        | Symbol        | Value | Unit |

|-----------------------------------------------|---------------|-------|------|

| Thermal Resistance, Junction-to-Air (Note 4)  | $R_{	hetaJA}$ | 14.6  | °C/W |

| Thermal Reference, Junction-to- Case (Note 4) | $R_{\Psi JC}$ | 1.5   | °C/W |

<sup>4.</sup> Values are based on On Semiconductor Evaluation Board of 2 oz copper thickness, No airflow and FR4 PCB substrate.

<sup>1.</sup> Refer to ELECTRICAL CHĂRACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

2. PGND is internally connected to GND.

<sup>3.</sup> For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### **RECOMMENDED OPERATING RANGE**

| Rating                    | Symbol           | Min | Max | Unit |

|---------------------------|------------------|-----|-----|------|

| Input Voltage             | V <sub>in</sub>  | 4.5 | 18  | V    |

| Output Voltage            | V <sub>out</sub> | 0.5 | 5.5 | V    |

| Continuous Output Current | l <sub>out</sub> | 0   | 35  | Α    |

| Adjustable Output Voltage | V <sub>out</sub> | 0.5 | 5.5 | V    |

| EN Pin Voltage            | V <sub>EN</sub>  | 0   | 5   | V    |

| Junction Temperature      | T <sub>J</sub>   | -40 | 125 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$V_{IN} = 12 \text{ V}, V_{OLIT} = 3.3 \text{ V}, \text{ for typical values } T_A = 25^{\circ}\text{C}, \text{ for min/max values } T_A = T_{.I} = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}; \text{ unless otherwise specified.}$

| Parameter                                         | Test Conditions                                                                      | Symbol                    | Min         | Typical        | Max         | Unit |

|---------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------|-------------|----------------|-------------|------|

| SUPPLY CURRENT                                    | •                                                                                    | •                         | •           | •              |             |      |

| Quiescent Current                                 | EN Low, not switching                                                                | $I_{VIN,Q}$               | -           | 2.8            | -           | mA   |

| LINEAR REGULATOR                                  |                                                                                      | •                         |             | •              |             | •    |

| Regulator Output Voltage                          |                                                                                      | $V_{REG}$                 | 4.75        | 5              | 5.25        | V    |

| Regulator Current Limit                           | Not for external use                                                                 | I <sub>REG</sub>          | 60          | -              | -           | mA   |

| Regulator Drop Out Voltage                        | I <sub>LDO</sub> = 40 mA, V <sub>IN</sub> = 5 V                                      | V <sub>DROPOUT</sub>      | -           | -              | 0.3         | V    |

| INTERNAL MOSFET RDS-ON (Note 5)                   |                                                                                      |                           |             |                |             |      |

| High Side MOSFET                                  | V <sub>GS</sub> = 5 V                                                                | HS-RDSon                  | -           | 2.8            | _           | mΩ   |

| Low Side MOSFET                                   | 1                                                                                    | LS-RDS <sub>ON</sub>      | -           | 1.3            | -           | mΩ   |

| DIFFERENTIAL AMPLIFIER                            | •                                                                                    | •                         | •           | 1              |             |      |

| V <sub>SEN+</sub> Pin Input Impedance             |                                                                                      | R <sub>SEN+</sub>         | -           | 100            | -           | kΩ   |

| V <sub>SEN</sub> – Pin Input Impedance            | G = 1<br>G = 0.5<br>G = 0.25                                                         | R <sub>SEN</sub> _        | -<br>-<br>- | 50<br>66<br>78 | -<br>-<br>- | kΩ   |

| Output Sinking current capability                 |                                                                                      | I <sub>DIFF(sink)</sub>   | 3           | -              | -           | mA   |

| Output Sourcing current capability                |                                                                                      | I <sub>DIFF(source)</sub> | 3           | -              | -           | mA   |

| Closed-Loop Bandwidth (Note 5)                    |                                                                                      | BW <sub>DIFF</sub>        | 2           | -              | -           | MHz  |

| Closed-Loop Gain                                  | G = 1, for V <sub>OUT</sub> ≤ 1.99                                                   |                           | -           | 1              | -           | V/V  |

|                                                   | G = 0.5 for $1.99 \le V_{OUT} \le 3.99$                                              |                           | -           | 0.5            | -           | 1    |

|                                                   | G = 0.25, for V <sub>OUT</sub> ≥ 3.99                                                |                           | -           | 0.25           | -           |      |

| Closed-Loop Accuracy                              | G = 1, V <sub>OUT</sub> = 600 mV, no load                                            | V <sub>err</sub>          | -1          | -              | 1           | %    |

|                                                   | G = 0.5, V <sub>OUT</sub> = 3.3 V, no load                                           |                           | -1          | -              | 1           |      |

|                                                   | G = 0.25, V <sub>OUT</sub> = 5 V, no load                                            |                           | -1          | -              | 1           |      |

| REFERENCE, V <sub>OUT</sub> SETTING AND MARG      | INING                                                                                |                           |             |                |             |      |

| FB Pin Voltage Accuracy                           | $0^{\circ}C \le T_{J} \le 125^{\circ}C,$<br>$V_{FB} = 0.6 \text{ V}, 1.65 \text{ V}$ | V <sub>REF</sub>          | -1          | -              | 1           | %    |

| V <sub>OUT</sub> Setting Range (Note 5)           |                                                                                      | V <sub>OUT,RNG</sub>      | 0.5         | -              | 5.5         | V    |

| V <sub>OUT</sub> Setting and Margin Step (Note 5) |                                                                                      | $V_{TM,S}$                | -           | 1.953          | -           | mV   |

| Margin Low Default Value                          |                                                                                      | $V_{ m MGL}$              | -           | 3.1            | -           | V    |

| Margin Low Default Value Range (Note 5)           |                                                                                      | $V_{MGL}$                 | 0.5         | -              | 5.5         | V    |

| Parameter                                                      | Test Conditions                                              | Symbol                  | Min   | Typical                                        | Max   | Unit   |

|----------------------------------------------------------------|--------------------------------------------------------------|-------------------------|-------|------------------------------------------------|-------|--------|

| REFERENCE, V <sub>OUT</sub> SETTING AND MARG                   | INING                                                        |                         |       |                                                |       |        |

| Margin High Default Value                                      |                                                              | $V_{MGH}$               | _     | 3.4                                            | _     | V      |

| Margin High Default Value Range (Note 5)                       |                                                              | $V_{MGH}$               | 0.5   | -                                              | 5.5   | ٧      |

| Default Transition Rate                                        |                                                              | k <sub>TRAN</sub>       | _     | 0.203                                          | -     | mV/μs  |

| Transition Rate Range (Note 5)                                 |                                                              | k <sub>TRAN,RNG</sub>   | 0.203 | -                                              | 9.375 | mV/μs  |

| Transition Rate Accuracy                                       |                                                              |                         | _     | ±10                                            | -     | %      |

| OSCILLATOR                                                     |                                                              | •                       |       | •                                              |       | •      |

| Default Switching Frequency                                    |                                                              | F <sub>SW</sub>         | 540   | 600                                            | 660   | kHz    |

| Switching Frequency Setting Range (Note 5)                     |                                                              | F <sub>SW,RNG</sub>     | 200   | -                                              | 1800  | kHz    |

| Switching Frequency Step Size (Note 5)                         | 200 ≤ F <sub>SW</sub> ≤ 1200 kHz                             | F <sub>SW,ST</sub>      | _     | 50                                             | -     | kHz    |

|                                                                | 1200 < F <sub>SW</sub> ≤ 1800 kHz                            |                         | _     | 100                                            | _     | 1      |

| Switching Frequency Accuracy                                   |                                                              | F <sub>SW,ACC</sub>     | -10   | -                                              | 10    | %      |

| FREQUENCY SYNCHRONIZATION                                      |                                                              | <u>.</u>                |       | <u> </u>                                       |       |        |

| SYNC Input Logic HIGH                                          |                                                              | V <sub>SYNC_IN_H</sub>  | 2     | -                                              | _     | ٧      |

| SYNC Input Logic LOW                                           |                                                              | V <sub>SYNC_IN_L</sub>  | _     | -                                              | 0.8   | ٧      |

| Input HIGH Level Pulse Width                                   |                                                              | thigh_in_min            | 135   | -                                              | _     | ns     |

| Input LOW Level Pulse Width                                    |                                                              | t <sub>LOW_IN_MIN</sub> | 150   | -                                              | _     | ns     |

| Synchronize Frequency (Note 5)                                 | Percentage of the oscillator frequency                       | F <sub>SYNC</sub>       | 80    | -                                              | 120   | %      |

| Transition Delay before Synchronizing to SYNC frequency        | In Number of oscillator Clock<br>Cycles per 2 ms time period | tsync_dl                | -     | 64                                             | -     | Cycles |

| SYNC Pin Pull down Resistance                                  |                                                              | R <sub>SYNC_PD</sub>    | -     | 100                                            | -     | kΩ     |

| SYNC Output Driver Pull-up Resistance                          |                                                              | R <sub>SYNCDRPU</sub>   | _     | 10                                             | -     | Ω      |

| SYNC Output Driver Pull-down Resistance                        |                                                              | R <sub>SYNCDRPD</sub>   | -     | 12                                             | -     | Ω      |

| SYNC Output Duty Cycle                                         |                                                              | D <sub>SYNC_OUT</sub>   | _     | 45                                             | _     | %      |

| SYNC Pin Lead Capacitance                                      | V <sub>OUT</sub> = 0 V (Note 5)                              | C <sub>L_SYNC</sub>     | -     | -                                              | 200   | pF     |

| RAMP AND PWM MODULATOR                                         |                                                              |                         |       |                                                |       |        |

| PWM Modulator Feed-forward(Vin) Gain, $V_{IN}/\Delta V_{RAMP}$ |                                                              | k <sub>PWM</sub>        | _     | 10                                             | ı     |        |

| PWM Minimum ON Time                                            |                                                              | t <sub>ON_MIN</sub>     | 30    | 50                                             | 70    | ns     |

| PWM Minimum OFF Time                                           |                                                              | t <sub>OFF_MIN</sub>    | 100   | 150                                            | 200   | ns     |

| ERROR AMPLIFIER                                                |                                                              | -                       |       |                                                |       |        |

| Unity Gain Bandwidth (Note 5)                                  |                                                              | G <sub>BW</sub>         | 5     | 10                                             | _     | MHz    |

| DC Gain (Note 5)                                               | V <sub>FB</sub> = 0.6 V                                      | G                       | 78    | 100                                            | -     | dB     |

| COMP Source Current                                            |                                                              | I <sub>COMP_SRC</sub>   | 2     | 10                                             | -     | mA     |

| COMP Sink Current                                              |                                                              | I <sub>COMP_SNK</sub>   | 2     | 9                                              | -     | mA     |

| SOFT-START (Low side FET turns ON after                        | r V <sub>OUT</sub> > 300 mV)                                 | <u> </u>                |       | <u>-                                      </u> |       |        |

| Default TON-Rise                                               |                                                              | t <sub>SST</sub>        | _     | 5                                              | -     | ms     |

| TON-Rise Range (Note 5)                                        |                                                              | t <sub>SST,RNG</sub>    | 1     | -                                              | 20    | ms     |

| Default TON Delay                                              |                                                              | t <sub>ONDLY</sub>      | _     | 1                                              | _     | ms     |

| Parameter                                      | Test Conditions              | Symbol                  | Min  | Typical | Max   | Unit |

|------------------------------------------------|------------------------------|-------------------------|------|---------|-------|------|

| SOFT-START (Low side FET turns ON afte         | r V <sub>OUT</sub> > 300 mV) | •                       |      |         |       |      |

| TON Delay Range (Note 5)                       |                              | t <sub>ONDLY,RNG</sub>  | 1    | -       | 10    | ms   |

| Default TOFF-Fall                              |                              | t <sub>SSP</sub>        | -    | 5       | _     | ms   |

| TOFF-Fall Range (Note 5)                       |                              | t <sub>SSP,RNG</sub>    | 1    | -       | 20    | ms   |

| Default TOFF Delay                             |                              | tOFFDLY                 | -    | 1       | _     | ms   |

| TOFF Delay Range (Note 5)                      |                              | toffdly,rng             | 0    | -       | 10    | ms   |

| Default TON MAX FAULT LIMIT                    |                              | t <sub>maxFLT</sub>     | -    | 12      | -     | ms   |

| TON MAX FAULT LIMIT Range (Note 5)             |                              | t <sub>maxFLT,RNG</sub> | 0    | -       | 50    | ms   |

| CYCLE-BY-CYCLE CURRENT LIMIT                   |                              |                         |      |         |       |      |

| High-Side Current Limit Blanking Time (Note 5) |                              | <sup>t</sup> LIMPKBLNK  | -    | 50      | -     | ns   |

| Peak (High-Side) Current Limit Default         |                              | I <sub>LIMPK</sub>      | -    | 54      | -     | Α    |

| Peak (High-Side) Current Limit Range           |                              | I <sub>LIMPK,RNG</sub>  | 2    | -       | 62    | Α    |

| Peak (High-Side) Current Limit Accuracy        | I <sub>LIMPK</sub> = 40 A    | I <sub>LIMPK,ACC</sub>  | -15  | -       | 15    | %    |

| Low- Side Current Limit Blanking Time (Note 5) |                              | tLIMNEGBLNK             | -    | 60      | -     | ns   |

| Negative (Low-Side) Current Limit Default      |                              | I <sub>LIMNEG</sub>     | -    | 14      | -     | Α    |

| Negative (Low-Side) Current Limit Range        |                              | I <sub>LIMNEG,RNG</sub> | 10   | -       | 24    | Α    |

| AVERAGE OUTPUT CURRENT                         |                              |                         |      |         |       |      |

| Output Current Warning                         |                              |                         | -    | 32      | -     | Α    |

| Output Current Warning Range (Note 5)          |                              |                         | 1    | -       | 64    | Α    |

| Output Current Fault                           |                              |                         | -    | 45      | -     | Α    |

| Output Current Fault Range (Note 5)            |                              |                         | 1    | -       | 64    | Α    |

| Average Fault Response Time Range (Note 5)     |                              |                         | 0    | -       | 10    | ms   |

| ENABLE                                         |                              |                         |      |         |       |      |

| Enable Threshold                               | EN voltage rising            | V <sub>EN</sub>         | 1.12 | 1.22    | 1.32  | V    |

| Disable Threshold                              | EN voltage falling           | V <sub>DIS</sub>        | 1.00 | 1.105   | 1.195 | V    |

| Hysteresis                                     |                              | V <sub>EN,HYS</sub>     | -    | 115     | -     | mV   |

| EN Pin Internal Pull-down Resistor             |                              | R <sub>EN</sub>         | -    | 900     | -     | kΩ   |

| EN Pin Internal Clamp Resistance               | V <sub>EN</sub> = 5 V        | R <sub>ENCLMP</sub>     | -    | 250     | -     | kΩ   |

| VCC UVLO                                       |                              |                         |      |         |       |      |

| VCC UVLO Enable Threshold                      | VCC voltage rising           | $V_{CC,EN}$             | -    | 4       | 4.35  | V    |

| VCC UVLO Disable Threshold                     | VCC voltage falling          | V <sub>CC,DIS</sub>     | 3.58 | 3.8     | -     | V    |

| VCC UVLO Hysteresis                            |                              | V <sub>CCHYS</sub>      | -    | 175     | -     | mV   |

| INPUT VOLTAGE PROTECTIONS                      |                              |                         |      |         |       |      |

| Default VIN Turn-on Threshold                  | V <sub>IN</sub> rising       | V <sub>ON</sub>         | -    | 6       | -     | V    |

| VIN Turn-on Threshold Range                    |                              | V <sub>ON,RNG</sub>     | 3    | -       | 10.5  | V    |

| VIN Turn-on Threshold Accuracy                 |                              | V <sub>ON,ACC</sub>     | -8   | -       | 8     | %    |

| Default VIN Turn-off Threshold                 | V <sub>IN</sub> falling      | V <sub>OFF</sub>        | -    | 5.5     | _     | V    |

| Parameter                                    | Test Conditions                                                         | Symbol                | Min | Typical | Max | Unit |

|----------------------------------------------|-------------------------------------------------------------------------|-----------------------|-----|---------|-----|------|

| INPUT VOLTAGE PROTECTIONS                    |                                                                         |                       |     |         |     |      |

| VIN Turn-off Threshold Range                 |                                                                         | $V_{OFF,RNG}$         | 2.5 | -       | 10  | ٧    |

| VIN Turn-off Threshold Accuracy              |                                                                         | V <sub>OFF,ACC</sub>  | -10 | -       | 8   | %    |

| Default VIN Overvoltage Threshold            | V <sub>IN</sub> rising                                                  | V <sub>INOV</sub>     | _   | 20      | -   | ٧    |

| VIN Overvoltage Threshold Range              |                                                                         | V <sub>INOV,RNG</sub> | 18  | -       | 24  | V    |

| VIN Overvoltage Threshold Accuracy           |                                                                         | V <sub>INOV,ACC</sub> | -8  | -       | 5   | %    |

| OUTPUT VOLTAGE PROTECTIONS (as a             | percentage of V <sub>OUT</sub> )                                        |                       |     |         |     |      |

| Default VOUT Overvoltage Threshold           | V <sub>OUT</sub> rising                                                 | V <sub>OOV</sub>      | -   | 116     | -   | %    |

| VOUT Overvoltage Threshold Setting Range     |                                                                         | V <sub>OOV,RNG</sub>  | 110 | -       | 124 | %    |

| VOUT Overvoltage Threshold Setting Step      |                                                                         |                       | -   | 2       | _   | %    |

| Default VOUT Warning Threshold               | V <sub>OUT</sub> rising                                                 | V <sub>OWRN</sub>     | -   | 108     | _   | %    |

| VOUT Warning Threshold Setting Range         |                                                                         | V <sub>OWRN,RNG</sub> | 106 | -       | 116 | %    |

| VOUT Overvoltage Threshold Setting Step      |                                                                         |                       | _   | 2       | -   | %    |

| Default VOUT Under-voltage Threshold         | V <sub>OUT</sub> falling                                                | V <sub>OUV</sub>      | _   | 75      | -   | %    |

| VOUT Under-voltage Threshold Setting Range   |                                                                         | V <sub>OUV,RNG</sub>  | 55  | -       | 90  | %    |

| VOUT Under-voltage Threshold Setting<br>Step |                                                                         |                       | _   | 5       | -   | %    |

| OUTPUT POWER GOOD (AS A PERCENT              | AGE OF V <sub>OUT</sub> )                                               | •                     |     | •       |     |      |

| Default PG Asserting Threshold               | V <sub>OUT</sub> rising                                                 | $V_{PGON}$            | -   | 90      | -   | %    |

| PG Asserting Threshold Range (Note 5)        |                                                                         | V <sub>PGON,RNG</sub> | 84  | -       | 98  | %    |

| PG Asserting Threshold Accuracy              |                                                                         | V <sub>PGON,ACC</sub> | -2  | -       | 2   | %    |

| Default PG de-asserting Threshold            | V <sub>OUT</sub> falling                                                | V <sub>PGOF</sub>     | _   | 84      | -   | %    |

| PG De-asserting Threshold Range              |                                                                         | $V_{PGOF,RNG}$        | 82  | -       | 96  | %    |

| PG De-asserting Threshold Accuracy           |                                                                         | V <sub>PGOF,ACC</sub> | -2  | -       | 2   | %    |

| PG Leakage Current                           |                                                                         | I <sub>PG,LEAK</sub>  | _   | -       | 1   | μΑ   |

| PG De-glitch Filter Duration                 |                                                                         | t <sub>PG_FLT</sub>   | -   | 5       | _   | μs   |

| PG Rising Delay                              |                                                                         |                       | -   | 560     | -   | μs   |

| PG Falling Delay                             |                                                                         |                       | -   | 10      | -   | μs   |

| PG Output Low Voltage                        | V <sub>OUT</sub> = 70% V <sub>OUTREF</sub> ,<br>I <sub>PG</sub> = -1 mA | V <sub>PG_L</sub>     | -   | 6       | 12  | mV   |

| INTERNAL BOOTSTRAP DIODE                     |                                                                         |                       |     |         |     |      |

| Forward Voltage                              | I <sub>F</sub> = 10 mA                                                  | $V_{FBOOT}$           | -   | -       | 0.3 | ٧    |

| Bootstrap Voltage UVLO                       | V <sub>BOOT</sub> falling                                               | V <sub>BTUV</sub>     | 2.9 | 3.2     | -   | ٧    |

| Bootstrap Voltage UVLO Hysteresis            | V <sub>BOOT</sub> rising                                                | V <sub>BTUVHYS</sub>  | -   | 0.35    | -   | V    |

| THERMAL PROTECTION                           |                                                                         |                       |     | •       |     |      |

| Default Thermal Fault Threshold              | T <sub>J</sub> rising                                                   | T <sub>OFF</sub>      | -   | 140     | -   | °C   |

| Thermal Fault Threshold Setting Range        |                                                                         | T <sub>OFF,RNG</sub>  | 80  | _       | 160 | °C   |

| Default Thermal Warning Threshold            | T <sub>J</sub> rising                                                   | T <sub>OFF</sub>      | -   | 115     | -   | °C   |

| Thermal Warning Threshold Range              |                                                                         | T <sub>OFF,RNG</sub>  | 70  | -       | 150 | °C   |

### **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN}$  = 12 V,  $V_{OUT}$  = 3.3 V, for typical values  $T_A$  = 25°C, for min/max values  $T_A$  =  $T_J$  = -40°C to 125°C; unless otherwise specified.

| Parameter                                 | Test Conditions                                                  | Symbol                 | Min  | Typical | Max | Unit |

|-------------------------------------------|------------------------------------------------------------------|------------------------|------|---------|-----|------|

| THERMAL PROTECTION                        | •                                                                | •                      | •    |         |     |      |

| Thermal Shutdown Threshold Umbrella       | T <sub>J</sub> rising                                            | T <sub>SHDN</sub>      | _    | 160     | _   | °C   |

| Thermal Shutdown Hysteresis               |                                                                  | T <sub>SHDN,HYS</sub>  | _    | 15      | -   | °C   |

| TELEMETRY REPORTING                       |                                                                  |                        |      |         |     |      |

| Telemetry Refresh Time Interval (Note 5)  |                                                                  | <sup>t</sup> telemetry | _    | 900     | _   | μs   |

| VIN Voltage Accuracy                      | EN = 0                                                           | V <sub>IN,ACC</sub>    | -5   | -       | 5   | %    |

| VOUT Voltage Accuracy                     | G = 1, VSET = AGND                                               | V <sub>OUT,ACC</sub>   | -2   | -       | 2   | %    |

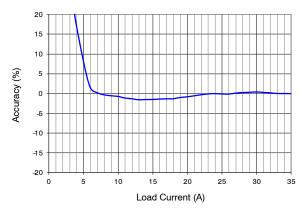

| Output Current Accuracy                   | I <sub>OUT</sub> = 6 A to 35 A                                   | I <sub>OUT,ACC</sub>   | _    | ±10     | _   | %    |

| Input Current Accuracy                    | F <sub>SW</sub> = 600 kHz,<br>For I <sub>OUT</sub> = 6 A to 35 A | I <sub>OUT,ACC</sub>   | -    | ±10     | -   | %    |

| Temperature Accuracy (Note 5)             | 0°C – 125°C                                                      | T <sub>ACC</sub>       | -5   | -       | 5   | °C   |

| PMBUS INTERFACE (Note 5)                  |                                                                  |                        |      | -       |     |      |

| Pin Capacitance (SCL, SDA)                |                                                                  |                        | -    | -       | 10  | pF   |

| PMBUS Operating Frequency Range           |                                                                  |                        | 10   | -       | 400 | kHz  |

| Bus Free Time between START and Stop      |                                                                  |                        | 1.3  | -       | -   | μs   |

| Hold Time after Repeated START            |                                                                  |                        | 0.6  | -       | -   | μs   |

| Repeated START Setup Time                 |                                                                  |                        | 0.6  | -       | _   | μs   |

| Data Hold Time (receive & transmit modes) |                                                                  |                        | 0    | -       | _   | ns   |

| Data Setup Time                           |                                                                  |                        | 100  | -       | _   | ns   |

| Detect Clock Low Timeout                  |                                                                  |                        | 25   | -       | 35  | ms   |

| Cumulative Clock Low Master Extend Time   |                                                                  |                        | -    | -       | 10  | ms   |

| Cumulative Clock Low Slave Extend Time    |                                                                  |                        | _    | -       | 25  | ms   |

| Clock Low Time                            |                                                                  |                        | 1.3  | -       | _   | μs   |

| Clock High Time                           |                                                                  |                        | 0.6  | -       | 50  | μS   |

| SCL/SDA Fall Time                         |                                                                  |                        | _    | -       | 120 | ns   |

| SCL/SDA Rise Time                         |                                                                  |                        | _    | -       | 120 | ns   |

| SCL/SDA High/Rising Threshold             |                                                                  |                        | 1.95 | -       | -   | V    |

| SCL/SDA Low/Falling Threshold             |                                                                  |                        | _    | -       | 0.8 | V    |

| SCL/SDA Threshold Hysteresis              |                                                                  |                        | _    | 0.6     | -   | V    |

| Noise Spike Suppression Time              |                                                                  |                        | 0    | -       | 50  | ns   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

5. Performance guaranteed over the indicated operating temperature range by design and/or characterization tested at  $T_J = T_A = 25^{\circ}C$ . Low

duty cycle pulse techniques are used during testing to maintain the junction temperature as close to ambient as possible.

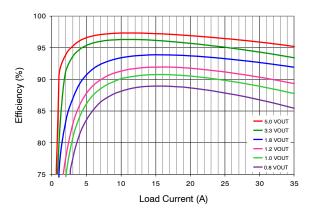

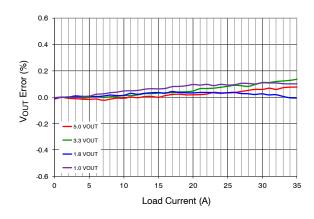

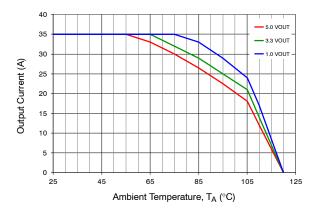

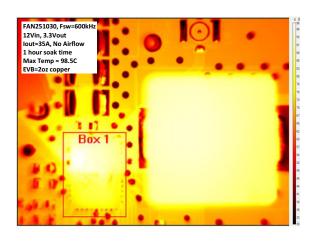

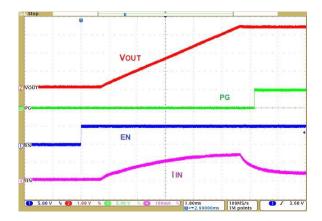

### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{IN}$  = 12 V,  $V_{OUT}$  = 3.3 V,  $F_{sw}$  = 600 kHz, L = 1  $\mu$ H (Note 6),  $C_{OUT}$  = 1000  $\mu$ F,  $T_{A}$  = 25 °C, unless otherwise indicated.

Figure 4. Efficiency

Figure 5. Load Regulation

Figure 6. Thermal Safe Operating Area, No Airflow, PCB: 2 oz. Cu

Figure 7. Thermal Image, No Airflow, I<sub>OUT</sub> = 35 A

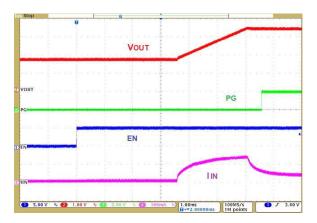

Figure 8. 5 msec Start-Up, No Load

Figure 9. 5 msec Start-Up with 50% Pre-Bias

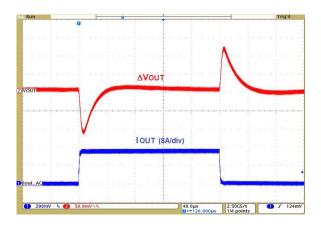

Figure 10. Load Transient 0–15 A, 10 A/ $\mu$ s

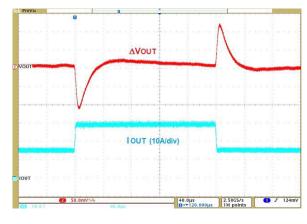

Figure 11. Load Transient 15–30 A, 10 A/ $\mu$ s

6. Tests conducted using L = 1.0  $\mu$ H (Pulse PA4343.102NLT)

#### **APPLICATION INFORMATION**

The FAN2510xx is a high-efficiency synchronous buck converter with integrated controller, driver and two power MOSFETs. It can operate over a 4.5 V to 18 V input voltage range, and delivers up to 35 A continuous load current.

FAN2510xx uses a voltage mode PWM control scheme with input voltage feed–forward feature for wide input voltage range. A differential amplifier monitors the output voltage and feeds the high bandwidth error amplifier that generates the control signal for the pulse width modulation block. By adjusting the external compensation network, the system performance can be optimized based on the application parameters. The Low–Side FET turns ON after  $V_{\rm OUT}$  > 300 mV.

The switching frequency is set by PMBUS programming and can be synchronized to an external clock signal.

The high-side MOSFET current is sensed for the peak current limiting function and the output voltage is reduced in current limiting condition. Other protection functions include over temperature warning and shut-down, output voltage under- and over-voltage protections and warning, output over-current warning, and input over-voltage (all adjustable by PMBUS).

At the beginning of each switching cycle, the clock signal initiates a PWM signal to turn on the high-side MOSFET, and at the same time, the ramp signal starts to rise up. A reset pulse is generated by the comparator when the ramp signal intercepts the COMP signal. This reset pulse turns off the high-side MOSFET and turns on the low-side MOSFET until the next clock cycle comes. If the current limit is hit, the high-side MOSFET is turned off until the next PWM signal (cycle by cycle current limit protection). When certain fault conditions are met, the device can enter a protection mode (hiccup or latch-off) to further protect itself.

### **PMBUS Address**

A resistor between the ADDR pin and GND (with up to 1% tolerance) sets the PMBUS offset address, enabling 14 different possible addresses (see Table 1 for details). The offset address is added to an adjustable base address with PMBUS. The base section is programmable through MTP.

Table 1. PMBUSTM ADDRESS SETTING

| ADDR Resistor<br>Value (kΩ) | Offset Address (h) | PMBUS Address (h) |

|-----------------------------|--------------------|-------------------|

| 0 (short)                   | -                  | 0F                |

| 0.845                       | 00                 | Base+00           |

| 1.3                         | 01                 | Base+01           |

| 1.78                        | 02                 | Base+02           |

| 2.32                        | 03                 | Base+03           |

| 2.87                        | 04                 | Base+04           |

| 3.48                        | 05                 | Base+05           |

| 4.12                        | 06                 | Base+06           |

| 4.75                        | 07                 | Base+07           |

| 5.49                        | 08                 | Base+08           |

| 6.19                        | 09                 | Base+09           |

| 6.98                        | 0A                 | Base+0A           |

| 7.87                        | 0B                 | Base+0B           |

| 8.87                        | 0C                 | Base+0C           |

| 10                          | 0D                 | Base+0D           |

| ≥12.4                       | _                  | 0F                |

### **V<sub>OUT</sub> Voltage Pre-set**

A resistor between the VSET pin and GND (with up to 1% tolerance) sets the output voltage without having to program it through PMBUS. It offers 15 different values (see table 2 for details). The  $V_{OUT}$  setting can be overridden through PMBUS programming. The  $V_{OUT}$  Voltage Pre–set feature can be enabled/disabled using MFR MODE (C8h) bit 0, which is enabled (0) by default.

Table 2. Vout PRESET SETTING

| VSET Resistor Value (k $\Omega$ ) | V <sub>OUT</sub> preset value (V) |

|-----------------------------------|-----------------------------------|

| Short                             | 0.6                               |

| 0.845                             | 0.6                               |

| 1.3                               | 0.9                               |

| 1.78                              | 0.95                              |

| 2.32                              | 1                                 |

| 2.87                              | 1.05                              |

| 3.48                              | 1.2                               |

| 4.12                              | 1.25                              |

| 4.75                              | 1.5                               |

| 5.49                              | 1.8                               |

| 6.19                              | 2.1                               |

| 6.98                              | 2.5                               |

| 7.87                              | 3.3                               |

| 8.87                              | 5                                 |

| 10 & greater value                | 0.8                               |

#### Output Over-current Protection

The FAN2510xx monitors the current in both the high-side and low-side MOSFETs, and offers several different sets of protections and warning:

High-side FET Positive Cycle-by-cycle Peak Current Limit with Programmable Delay and Response

- Limits the peak current in the high-side FET at each cycle to a level adjustable between 2 A and 62 A (using the IOUT\_OC\_FAULT\_LIMIT command)

- The duration during which it is allowed to run in cycle-by- cycle current limitation before going into fault protection mode is adjustable from 0 to 10ms (using the IOUT OC FAULT RESPONSE command)

- The fault protection mode is programmable, and can be chosen between "ignore without VOUT UVLO", "ignore with VOUT UVLO", "1-second hiccup" or "latch-off" (using the IOUT\_OC\_FAULT\_RESPONSE command)

- An additional limit equal to 130% of the level set by IOUT\_OC\_FAULT\_LIMIT immediately terminates switching if reached. This fault can be ignored: the FAN2510xx is latched off if IOUT\_OC\_FAULT\_RESPONSE is "latch-off", otherwise a 1-second hiccup is applied.

Average Output Current Fault with Programmable Delay and Response

- Based on the output current measured by the telemetry

- Does not limit the cycle-by-cycle current

- The threshold is adjustable between 1 A and 50 A (using the IOUT\_AVG\_FAULT\_LIMIT command)

- The duration during which the FAN2510xx is allowed to run above the threshold before going into fault protection mode is adjustable from 0 to 10ms (using the IOUT\_AVG\_FAULT\_RESPONSE command)

- The fault protection mode is programmable, and can be chosen between "ignore", "1-second hiccup" or "latch-off"

(using the IOUT\_AVG\_FAULT\_RESPONSE command)

### Average Output Current Warning

- Based on the output current measured by the telemetry

- The threshold is adjustable between 1 A and 64 A (using the IOUT OC WARN LIMIT command)

Low-side FET Negative Cycle-by-cycle Current Limit

Limits the negative low-side FET peak current at each cycle to a level adjustable between 10 A and 24 A (using the IOUT UC FAULT LIMIT command)

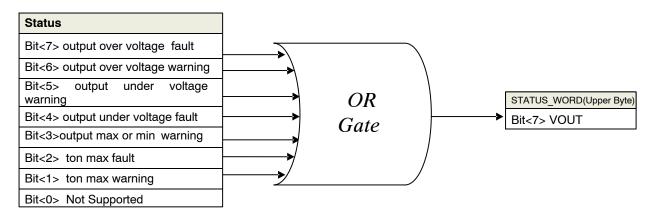

#### Output Voltage Monitoring and Protection

The FAN2510xx monitors the output voltage and offers several different sets of protections and warnings:

### Under-voltage Protection

- The threshold is adjustable as a percentage of the regulated output voltage, between 55% and 90% (using the PCT VOUT LIMIT command)

- The amount of filtering is adjustable (between 5µs and 10µs) and the fault response is programmable (between "ignore", "1-second hiccup" or "latch-off") using the VOUT UV FAULT RESPONSE command

### Under-voltage Warning

- Based on the output voltage measured by the telemetry

- The threshold is adjustable between 0.1 V and 5.5 V (using the VOUT\_UV\_WARN\_LIMIT command)

#### Over-voltage Protection

- The threshold is adjustable as a percentage of the regulated output voltage, between 110% and 124% (using the PCT\_VOUT\_LIMIT command)

- The amount of filtering is adjustable (between 5μs and 10 μs) and the fault response is programmable (between "ignore", "1-second hiccup" or "latch-off") using the VOUT OV FAULT RESPONSE command

#### Over-voltage Warning

- Switching stops when V<sub>OUT</sub> goes above this warning threshold, and resumes when back in regulation

- The threshold is adjustable as a percentage of the regulated output voltage, between 106% and 116% (using the PCT\_VOUT\_LIMIT command), and should be always set to the less than over-voltage protection threshold

- The behavior can be changed to turn on the low-side FET to actively pull V<sub>OUT</sub> down (by using MFR\_MODE\_SETTINGS).

### Power GOOD Signal and Pin

- The PGOOD signal is held low during soft-start and soft-shutdown.

- The power good signal is high whenever V<sub>OUT</sub> is in regulation, after the end of soft-start

- The rising threshold is adjustable as a percentage of the regulated output voltage, between 84% and 98% (using the PCT VOUT PGOOD command)

- The falling threshold is adjustable as a percentage of the regulated output voltage, between 82% and 96% (using the PCT\_VOUT\_PGOOD command)

- The power Good signal also goes low when V<sub>OUT</sub> is above the over-voltage protection threshold

### Output Voltage Margining

FAN2510xx can be set for output voltage margin by applying positive (margin\_high) or negative (margin\_low) offset commands during operation.

Scale loop changes and back to back margining for the output changes are not supported in FAN2510xx. New offset can be applied long enough until the previous margining is completed. In the same scale loop, the big output voltage changes with the highest slew rate is not recommended if OVP option is enabled during the margining.

#### Input SYNC Function

Two parts can be synchronized from an input source as master/slave with 0° (in phase) or 180° (out phase) phase shift. When device acts as master, it sends out a 45% duty cycle clock through SYNC pin with rising edge sync'd with its own switching cycle. Slave device switching node's rising edge lags behind either SYNC CLK's rising edge (in phase) or falling edge (out of phase) by 200 ns.

The slave is synchronized to SYNC CLK after it's validated over 64 clock cycles. Then, SYNC\_CLK is compared to the internal clock. If outside the  $\pm 20\%$  frequency window when compared to the internal clock, the device exits slave mode and relies on its internal clock rate. Refer to INTERLEAVE (Reg37h) section for additional setting details.

### **Input Voltage Monitoring and Protection**

The FAN2510xx monitors the input voltage and offers several different sets of protections and warnings:

Over-voltage protection

- The threshold is adjustable between 18 V and 24 V (using the VIN\_OV\_FAULT\_LIMIT command)

- The amount of filtering is adjustable (between 5 μs and 10 μs) and the fault response is programmable (between "ignore", "recovery", "1-second hiccup" or "latch-off") using the VIN\_OV\_FAULT\_RESPONSE command

### Turn-on Threshold

The FAN2510xx only starts switching if VIN is above this threshold, adjustable between 4.5 V and 10.5 V (using the

VIN\_ON command). For less than 4.5 V, down to 3 V, external  $V_{CC}$  should be used.

### Turn-off Threshold

The FAN2510xx shuts down if VIN is below this threshold, adjustable between 4 V and 10 V (using the VIN\_OFF command). For less than 4 V, down to 3 V, external  $V_{CC}$  should be used.

### Temperature Monitoring and Protection

The FAN2510xx monitors its die temperature and offers several different sets of protections and warnings:

### Over-temperature Protection

- Based on the temperature measured by the telemetry

- The threshold is adjustable between 80°C and 160°C (using the OT\_FAULT\_LIMIT command)

- The fault protection mode is programmable, and can be chosen between "ignore", "recovery", "1-second hiccup" or "latch-off" (using the OT\_FAULT\_RESPONSE command)

- In case the die temperature reaches T<sub>SHDN</sub> (based on the analog sensor reading), the FAN2510xx immediately shuts of (including the LDO regulator), even if the fault response is set to "ignore"

#### Over-temperature Warning

- Based on the temperature measured by the telemetry

- The threshold is adjustable between 70°C and 150°C (using the OT WARN LIMIT command)

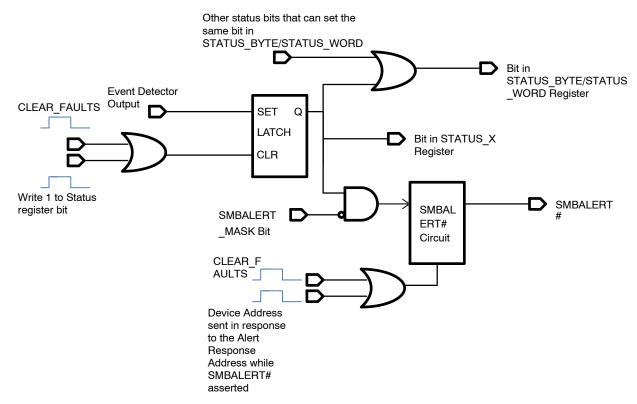

### **Protection Summary**

The FAN2510xx includes various protection features, with different behaviors and options. See Table 3 for a summary, and dedicated sections for more details about each one.

**Table 3. SUMMARY OF PROTECTION FUNCTIONS**

| Protection name                                      | Adjustability | Default Behavior                                                                                  | Options                                                       |

|------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Output overvoltage warning                           | PMBUS         | HS FET and LS FET both turn off until back in regulation                                          | HS FET turns off but LS FET turns on until back in regulation |

| Output overvoltage fault                             | PMBUS         | Switching stops, then enters protection mode                                                      | Ignore, hiccup or latch-off; delay                            |

| Output under-voltage fault                           | PMBUS         | Switching stops, then enters protection mode                                                      | Ignore, hiccup or latch-off; delay                            |

| Input overvoltage fault                              | PMBUS         | Switching stops until back in range                                                               | Ignore, resume when back in range, hiccup or latch-off        |

| Input under-voltage                                  | PMBUS         | Switching stops, part is reset                                                                    | no                                                            |

| VCC under-voltage                                    | no            | Switching stops, part is reset                                                                    | no                                                            |

| BOOT under-voltage                                   | no            | HS FET turns off, LS FET turns on regularly to refresh V <sub>BOOT</sub> , until the fault clears | no                                                            |

| Average output current fault                         | PMBUS         | Switching stops, then enters protection mode                                                      | Ignore, hiccup or latch-off; delay                            |

| Peak HS FET current fault                            | PMBUS         | Cycle-by-cycle current limit, enters protection mode after delay                                  | Ignore, hiccup or latch-off; delay                            |

| Peak HS FET current extreme fault                    | PMBUS         | Enters protection mode                                                                            | Ignore, hiccup or latch-off                                   |

| Peak negative LS FET current fault                   | PMBUS         | Cycle-by-cycle current limit                                                                      | no                                                            |

| Switch node fault                                    | no            | Switching stops, then enters protection mode                                                      | Trim option to change to latch off                            |

| Over temperature Fault                               | PMBUS         | Switching stops until back in range                                                               | Ignore, resume when back in range or latch-off                |

| Umbrella Thermal shutdown                            | no            | Switching stops and VCC LDO turns off, until back in range                                        | no                                                            |

| Start-up fault (VOUT UV not met at the end of timer) | PMBUS         | Switching stops, then enters protection mode                                                      | Ignore, hiccup or latch-off                                   |

#### **Telemetry**

The FAN2510xx constantly measures its input voltage, input current, output voltage, output current and die temperature and reports it in dedicated PMBUS registers. Each measured value is refreshed every  $900 \, \mu s$ .

Figure 12. Typical I<sub>OUT</sub> Telemetry Accuracy

### PMBUS General Description

The PMBUS specification can be found at <a href="https://www.pmbus.org">www.pmbus.org</a>. FAN2510xx support both the 100 kHz and

400 kHz bus timing requirements. Communication over the PMBUS interface supports Packet Error Checking (PEC). If the master provides the clock pulses for the PEC byte, PED is used. If the additional clock pulses are not present before a STOP, the PEC is not used. PMBUS has several transaction formats. The formats that are supported in FAN2510xx are listed below:

#### PMBUS Send Byte

The send byte transaction is used to send a simple command to the device. A send byte transaction transfers a command with no data. The CLEAR\_FAULTS command that clears the current fault flags present in the system is an example of such a command. A start bit, followed by the 7-bit slave address and finished by a write bit (0-value) to indicate a write make up the first stage of the transaction. If the slave ACKs the address, then the host sends the 8-bit command followed by a stop condition. The format is given below.

### PMBUS Send Byte

| 1 | 7             | 1  | 1 | 8            | 1 | 1 |

|---|---------------|----|---|--------------|---|---|

| S | SLAVE ADDRESS | WR | Α | COMMAND_CODE | Α | Р |

### PMBUS Write Byte

The write byte transaction is used to send single byte data to the chip. The OPERATION command that configures the operation of the device is an example of this type of transaction. Similar to the send byte transaction above, the series of start bit, 7-bit slave address with write bit (0-value), command byte, and finally the 8-bit data byte. The format is given below.

### PMBUS Write Byte

| 1 | 7             | 1  | 1 | 8            | 1 | 8         | 1 | 1 |

|---|---------------|----|---|--------------|---|-----------|---|---|

| S | SLAVE ADDRESS | WR | Α | COMMAND_CODE | Α | DATA_BYTE | Α | Р |

### PMBUS Write Word

The write word transaction is used to send a single word of data (two bytes) to the chip. The TON\_DELAY command is an example of such a transaction. Similar to the write byte

command, the only difference is that after the third acknowledge (the low data byte) the high byte is sent in addition.

#### PMBUS Write Word

| 1 | 7             | 1  | 1 | 8            | 1 | 8             | 1 | 1              | 1 | 1 |

|---|---------------|----|---|--------------|---|---------------|---|----------------|---|---|

| S | SLAVE ADDRESS | WR | Α | COMMAND_CODE | Α | DATA_BYTE LOW | Α | DATA_BYTE HIGH | Α | Р |

#### PMBUS Read Byte

The read byte starts out like a normal I2C write transaction by sending the address and the write bit. The second byte contains the command code, then a repeated start is sent, and following that is the address and read bit send the signal to the device to return data for the specified command code. The slave responds by transmitting the byte value requested.

### PMBUS Read Byte

| 1 | 7             | 1  | 1 | 8            | 1 | 1  | 7             | 1  | 1 | 8         | 1 | 1 |

|---|---------------|----|---|--------------|---|----|---------------|----|---|-----------|---|---|

| S | SLAVE ADDRESS | WR | Α | COMMAND_CODE | Α | Sr | SLAVE ADDRESS | Rd | Α | DATA BYTE | Ν | Р |

#### PMBUS Read Word

The read word transaction also starts out like a normal I 2C write transaction by sending the address and the write bit. The second byte contains the command code, then a

repeated start is sent, and following that is the address and read bit signaling the device to return data for the specified command code. The slave responds by transmitting the value requested low byte first and high byte last.

#### PMBUS Read Word

| 1 | 7             | 1  | 1 | 8            | 1 | 1  | 7             | 1  | 1 | 8         | 1 | 8              | 1 | 1 |

|---|---------------|----|---|--------------|---|----|---------------|----|---|-----------|---|----------------|---|---|

| S | SLAVE ADDRESS | WR | Α | COMMAND_CODE | Α | Sr | SLAVE ADDRESS | RD | Α | DATA BYTE | Ν | DATA BYTE HIGH | Ν | Р |

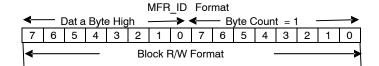

#### PMBUS Block Write

The Block Write begins with a slave address and a write condition. After the command code the host issues a byte count which describes how many more bytes will follow in the message. FAN2510xx allows only 1 byte. The byte count field can only have the value 01, followed by the one byte of data.

#### PMBUS Block Write

| 1 | 7             | 1  | 1 | 8            | 1 | 8              | 1 | 8         | 1 | 1 |

|---|---------------|----|---|--------------|---|----------------|---|-----------|---|---|

| S | SLAVE ADDRESS | WR | Α | COMMAND_CODE | Α | BYTE COUNT = 1 | Α | DATA BYTE | Α | Р |

#### PMBUS Block Read

A Block Read differs from a block write in that the repeated START condition exists to satisfy the requirement for a change in the transfer direction. A NACK immediately

preceding the STOP condition signifies the end of the read transfer.

FAN2510xx allows only 1 byte. The byte count field can only have the value 01, followed by the one byte of data.

#### PMBUS Block Read

| 1 | 7             | 1  | 1 | 8                 | 1 | 1  | 7             | 1  | 1 | 8              | 1 | 8         | 1 | 1 |

|---|---------------|----|---|-------------------|---|----|---------------|----|---|----------------|---|-----------|---|---|

| S | SLAVE ADDRESS | WR | Α | COM-<br>MAND_CODE | Α | Sr | SLAVE ADDRESS | RD | Α | BYTE COUNT = 1 | Α | DATA BYTE | Α | Р |

### Packet Error Checking (PEC)

PEC is optionally implemented in PMBUS devices, but is highly recommended due to the critical nature of data validity in power-management systems. Packet Error Code (also PEC) bytes are generated using the popular CRC-8 algorithm that is based on performing XOR operations on

the input bit stream with a fixed CRC polynomial. The PEC byte is calculated on all bytes in the I2C transaction including device address and read/write. PEC does not include start, stop, ACK/NACK, and repeated start bits.

PMBUS Send byte with PEC:

#### PMBUS Send Byte with PEC

| 1 | 7             | 1  | 1 | 8            | 1 | 8        | 1 | 1 |

|---|---------------|----|---|--------------|---|----------|---|---|

| S | SLAVE ADDRESS | WR | Α | COMMAND_CODE | Α | PEC BYTE | Α | Р |

### PMBUS Write Byte with PEC:

#### PMBUS Write Byte with PEC

| 1 | 7             | 1  | 1 | 8            | 1 | 8         | 1 | 8        | 1 | 1 |

|---|---------------|----|---|--------------|---|-----------|---|----------|---|---|

| S | SLAVE ADDRESS | WR | Α | COMMAND_CODE | Α | DATA_BYTE | Α | PEC BYTE | Α | Р |

### PMBUS Write Word with PEC:

### PMBUS Write Word with PEC

| 1 | 7             | 1  | 1 | 8            | 1 | 8             | 1 | 8              | 1 | 8        | 1 | 1 |

|---|---------------|----|---|--------------|---|---------------|---|----------------|---|----------|---|---|

| S | SLAVE ADDRESS | WR | Α | COMMAND_CODE | Α | DATA_BYTE LOW | Α | DATA_BYTE HIGH | Α | PEC BYTE | Α | Р |

## PMBUS Read Byte with PEC:

### PMBUS Read Byte with PEC

| 1 | 7             | 1  | 1 | 8            | 1 | 1  | 7             | 1  | 1 | 8         | 1 | 8        | 1 | 1 |

|---|---------------|----|---|--------------|---|----|---------------|----|---|-----------|---|----------|---|---|

| S | SLAVE ADDRESS | WR | Α | COMMAND_CODE | Α | Sr | SLAVE ADDRESS | RD | Α | DATA BYTE | Α | PEC BYTE | Α | Р |

### PMBUS Read Word with PEC:

### PMBUS Read Word with PEC

| 1 | 7             | 1  | 1 | 8            | 1 | 1  | 7             | 1  | 1 | 8             | 1 | 8                 | 1 | 8           | 1 | 1 |

|---|---------------|----|---|--------------|---|----|---------------|----|---|---------------|---|-------------------|---|-------------|---|---|

| S | SLAVE ADDRESS | WR | Α | COMMAND_CODE | Α | Sr | SLAVE ADDRESS | RD | Α | DATA BYTE LOW | Α | DATA BYTE<br>HIGH | Α | PEC<br>BYTE | Α | Р |

### PMBUS Block Write with PEC:

### PMBUS Block Write with PEC

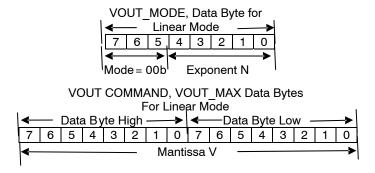

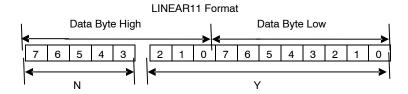

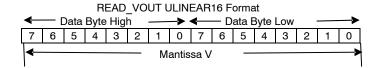

| 1     | 7             | 1  | 1 | 8            | 1 | 8             | 1 | 8         | 1 | 8        | 1 | 1 |