# CMOS Dual 8-Bit Buffered Multiplying DAC

# AD7628

#### FEATURES

On-Chip Latches for Both DACs +12 V to +15 V Operation DACs Matched to 1% Four Quadrant Multiplication TTL/CMOS Compatible from +12 V to +15 V Latch Free (Protection Schottkys not Required)

APPLICATIONS Disk Drives Programmable Filters X-Y Graphics Gain/Attenuation

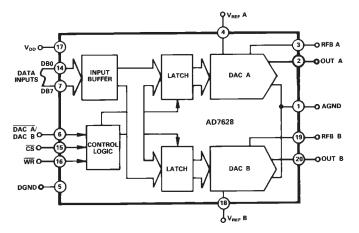

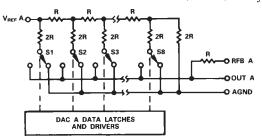

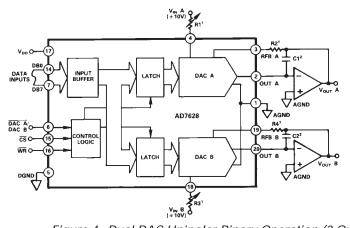

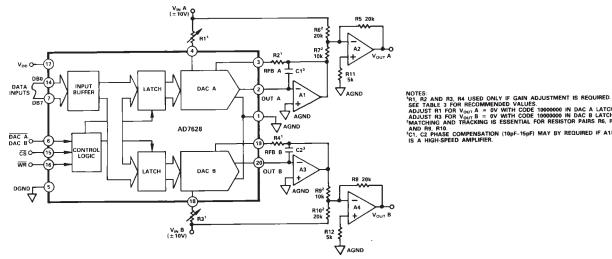

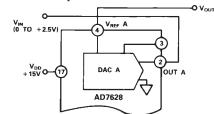

#### FUNCTIONAL BLOCK DIAGRAM

#### **GENERAL DESCRIPTION**

The AD7628 is a monolithic dual 8-bit digital/analog converter featuring excellent DAC-to-DAC matching. It is available in small 0.3" wide 20-pin DIPs and in 20-terminal surface mount packages.

Separate on-chip latches are provided for each DAC to allow easy microprocessor interface.

Data is transferred into either of the two DAC data latches via a common 8-bit TTL/CMOS compatible input port. Control input  $\overline{DAC} A/DAC$  B determines which DAC is to be loaded. The AD7628's load cycle is similar to the write cycle of a random access memory, and the device is bus compatible with most 8-bit microprocessors, including 6502, 6809, 8085, Z80.

The device operates from a +12 V to +15 V power supply and is TTL-compatible over this range. Power dissipation is a low 20 mW.

Both DACs offer excellent four quadrant multiplication characteristics with a separate reference input and feedback resistor for each DAC.

#### **PRODUCT HIGHLIGHTS**

- 1. DAC to DAC matching: since both of the AD7628 DACs are fabricated at the same time on the same chip, precise matching and tracking between DAC A and DAC B is inherent. The AD7628's matched CMOS DACs make a whole new range of applications circuits possible, particularly in the audio, graphics and process control areas.

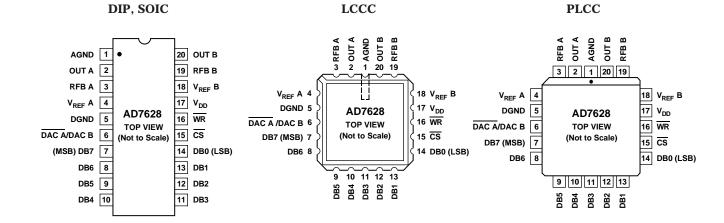

- Small package size: combining the inputs to the on-chip DAC latches into a common data bus and adding a DAC A/ DAC B select line has allowed the AD7628 to be packaged in a small 20-pin 0.3" wide DIP, 20-pin SOIC, 20-terminal PLCC and 20-terminal LCC.

- 3. TTL-Compatibility: All digital inputs are TTL-compatible over a +12 V to +15 V power supply range.

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 World Wide Web Site: http://www.analog.com Fax: 617/326-8703 © Analog Devices, Inc., 1996

# **AD7628–SPECIFICATIONS** ( $V_{DD}$ = +10.8 V to +15.75 V, $V_{REF}$ A = $V_{REF}$ B = +10 V; OUT A = OUT B = 0 V unless otherwise noted)

| Parameter                                                                                                                                                             | $T_A = +25^{\circ}C^1$ | $\begin{array}{l} T_{A}=-40^{\circ}C\\ to \ +85^{\circ}C \end{array}$ | $\begin{array}{l} T_{A}=-55^{\circ}C\\ to \ +125^{\circ}C^{1} \end{array}$ | Units                          | Test Conditions/Comments                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STATIC PERFORMANCE <sup>2</sup><br>Resolution<br>Relative Accuracy<br>Differential Nonlinearity                                                                       | 8<br>±1/2<br>±1        | 8<br>±1/2<br>±1                                                       | 8<br>±1/2<br>±1                                                            | Bits<br>LSB max<br>LSB max     | This is an Endpoint Linearity Specification<br>All Grades Guaranteed Monotonic Over                                                                                                      |

| Gain Error                                                                                                                                                            | ±2                     | ±3                                                                    | ±3                                                                         | LSB max                        | Full Operating Temperature Range<br>Measured Using Internal RFB A and RFB B.<br>Both DAC Latches Loaded with 11111111.<br>Gain Error is Adjustable Using Circuits<br>of Figures 4 and 5. |

| Gain Temperature Coefficient <sup>3</sup><br>∆Gain/∆Temperature<br>Output Leakage Current                                                                             |                        | ±0.0035                                                               | ±0.0035                                                                    | %/°C max                       |                                                                                                                                                                                          |

| OUT A (Pin 2)<br>OUT B (Pin 20)                                                                                                                                       | $\pm 50 \pm 50$        | $\pm 200 \\ \pm 200$                                                  | $\pm 200 \pm 200$                                                          | nA max<br>nA max               | DAC Latches Loaded with 00000000                                                                                                                                                         |

| Input Resistance (V <sub>REF</sub> A, V <sub>REF</sub> B)                                                                                                             | 8<br>15                | 8<br>15                                                               | 8<br>15                                                                    | $k\Omega$ min<br>$k\Omega$ max | Input Resistance TC = $-300 \text{ ppm/}^{\circ}\text{C}$ , Typical<br>Input Resistance is 11 k $\Omega$                                                                                 |

| V <sub>REF</sub> A/V <sub>REF</sub> B Input Resistance<br>Match                                                                                                       | ±1                     | ±1                                                                    | ±1                                                                         | % max                          |                                                                                                                                                                                          |

| DIGITAL INPUTS <sup>4</sup><br>Input High Voltage (V <sub>IH</sub> )<br>Input Low Voltage (V <sub>IL</sub> )<br>Input Current (I <sub>IN</sub> )<br>Input Capacitance | 2.4<br>0.8<br>±1       | 2.4<br>0.8<br>±10                                                     | 2.4<br>0.8<br>±10                                                          | V min<br>V max<br>μA max       | $V_{IN} = 0$ or $V_{DD}$                                                                                                                                                                 |

| $\frac{DB0}{WR} = \frac{DB7}{CS}, \frac{DACA}{DACB}$                                                                                                                  | 10<br>15               | 10<br>15                                                              | 10<br>15                                                                   | pF max<br>pF max               |                                                                                                                                                                                          |

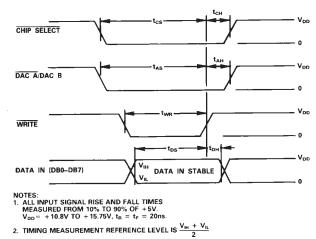

| SWITCHING CHARACTERISTICS <sup>3</sup><br>See Timing Diagram                                                                                                          |                        |                                                                       |                                                                            |                                |                                                                                                                                                                                          |

| Chip Select to Write Set Up Time $(t_{CS})$<br>Chip Select to Write Hold Time $(t_{CH})$<br>DAC Select to Write Set Up Time $(t_{AS})$                                | 160<br>10<br>160       | 160<br>10<br>160                                                      | 210<br>10<br>210                                                           | ns min<br>ns min<br>ns min     |                                                                                                                                                                                          |

| DAC Select to Write Hold Time (t <sub>AH</sub> )                                                                                                                      | 10                     | 10                                                                    | 10                                                                         | ns min                         |                                                                                                                                                                                          |

| Data Valid to Write Set Up Time ( $t_{DS}$ )<br>Data Valid to Write Hold Time ( $t_{DH}$ )                                                                            | 160<br>10              | 160<br>10                                                             | 210<br>10                                                                  | ns min<br>ns min               |                                                                                                                                                                                          |

| Write Pulse Width $(t_{WR})$                                                                                                                                          | 150                    | 170                                                                   | 210                                                                        | ns min                         |                                                                                                                                                                                          |

| POWER SUPPLY<br>I <sub>DD</sub> , K Grade<br>B, T Grades                                                                                                              | 2 2                    | 2<br>2.5                                                              | 2.5                                                                        | mA<br>mA                       | See Figure 3<br>All Digital Inputs $V_{IL}$ or $V_{IH}$<br>All Digital Inputs $V_{IL}$ or $V_{IH}$                                                                                       |

| All Grades                                                                                                                                                            | 100                    | 500                                                                   | 500                                                                        | μA                             | All Digital Inputs 0 V or $V_{DD}$                                                                                                                                                       |

Specifications subject to change without notice.

### AC PERFORMANCE CHARACTERISTICS These characteristics are included for Design Guidance only and are not subject to test. V<sub>DD</sub> = +10.8 V to +15.75 V. (Measured Using Recommended PC Board Layout (Figure 7) and AD644 as Output Amplifiers)

| Parameter                                                                                                                                                                                    | $T_A = +25^{\circ}C^1$ | $\begin{array}{l} T_A = -40^\circ C \\ to \ +85^\circ C^1 \end{array}$ | $\begin{array}{l} T_{A}=-55^{\circ}C\\ to\ +125^{\circ}\pi C^{1} \end{array}$ | Units                                | Test Conditions/Comments                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC SUPPLY REJECTION                                                                                                                                                                          |                        |                                                                        |                                                                               |                                      |                                                                                                                                                                                                                                    |

| $(\Delta GAIN/\Delta V_{DD})$                                                                                                                                                                | 0.01                   | 0.02                                                                   | 0.02                                                                          | % per % max                          | $\Delta V_{DD} = \pm 5\%$                                                                                                                                                                                                          |

| CURRENT SETTLING TIME                                                                                                                                                                        | 350                    | 400                                                                    | 400                                                                           | ns max                               | $ \begin{array}{l} \hline To \ 1/2 \ LSB \ OutA/OutB \ Load = 100 \ \Omega. \\ \hline WR = \overline{CS} = 0 \ V. \\ DB0-DB7 = 0 \ V \ to \ V_{DD} \ or \ V_{DD} \ to \ 0 \ V \end{array} $                                        |

| DIGITAL-TO-ANALOG GLITCH                                                                                                                                                                     |                        |                                                                        |                                                                               |                                      |                                                                                                                                                                                                                                    |

| IMPULSE                                                                                                                                                                                      | 330                    |                                                                        |                                                                               | nV sec typ                           | For Code Transition 00000000 to 11111111                                                                                                                                                                                           |

| $\begin{array}{c} \text{OUTPUT CAPACITANCE} \\ \text{C}_{\text{OUT}}\text{A} \\ \text{C}_{\text{OUT}}\text{B} \\ \text{C}_{\text{OUT}}\text{A} \\ \text{C}_{\text{OUT}}\text{B} \end{array}$ | 25<br>25<br>60<br>60   | 25<br>25<br>60<br>60                                                   | 25<br>25<br>60<br>60                                                          | pF max<br>pF max<br>pF max<br>pF max | DAC Latches Loaded with 00000000<br>DAC Latches Loaded with 11111111                                                                                                                                                               |

| AC FEEDTHROUGH $V_{REF}A$ to OUT A $V_{REF}B$ to OUT B                                                                                                                                       | -70<br>-70             | -65<br>-65                                                             | -65 -65                                                                       | dB max<br>dB max                     | $V_{REF}A$ , $V_{REF}B = 20 V p$ -p Sine Wave<br>@ 10 kHz                                                                                                                                                                          |

| CHANNEL-TO-CHANNEL ISOLATION $V_{REF}A$ to OUT B $V_{REF}B$ to OUTA                                                                                                                          | -80<br>-80             |                                                                        |                                                                               | dB typ<br>dB typ                     | Both DAC Latches Loaded with 11111111.<br>V <sub>REF</sub> A = 20 V p-p Sine Wave @ 10 kHz<br>V <sub>REF</sub> B = 0 V See Figure 6.<br>V <sub>REF</sub> B = 20 V p-p Sine Wave @ 10 kHz<br>V <sub>RFF</sub> A = 0 V See Figure 6. |

| DIGITAL CROSSTALK                                                                                                                                                                            | 60                     |                                                                        |                                                                               | nV sec typ                           | Measured for Code Transition 00000000<br>to 11111111                                                                                                                                                                               |

| HARMONIC DISTORTION                                                                                                                                                                          | -85                    |                                                                        |                                                                               | dB typ                               | V <sub>IN</sub> = 6 V rms @ 1 kHz                                                                                                                                                                                                  |

NOTES <sup>1</sup>Temperature Ranges are K Version; -40°C to +85°C; B Version; -40°C to +85°C; T Version; -55°C to +125°C. <sup>2</sup>Specification applies to both DACs in AD7628. <sup>3</sup>Guaranteed by design but not production tested. <sup>4</sup>Logic inputs are MOS Gates. Typical input current (+25°C) is less than 1 nA.

Specifications subject to change without notice.

#### ABSOLUTE MAXIMUM RATINGS

$(T_A = +25^{\circ}C \text{ unless otherwise noted})$

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                        |

|---------------------------------------------------------------------------------------------|

| Digital Input Voltage to DGND $\dots -0.3 \text{ V}, \text{ V}_{\text{DD}} + 0.3 \text{ V}$ |

| $V_{PIN2}$ , $V_{PIN20}$ to AGND0.3 V, $V_{DD}$ + 0.3 V                                     |

| $V_{REF}$ A, $V_{REF}$ B to AGND ±25 V                                                      |

| $V_{RFB}$ A, $V_{RFB}$ B to AGND ±25 V                                                      |

| Power Dissipation (Any Package) to +75°C 450 mW                                             |

| Derates above +75°C by 6 mW/°C                                                              |

| Operating Temperature Range                                                                 |

| Commercial (K) Grades40°C to +85°C                                                          |

| Industrial (B) Grades40°C to +85°C                                                          |

| Extended (T) Grades                                                                         |

| Storage Temperature                                                                         |

| Lead Temperature (Soldering, 10 sec) +300°C                                                 |

#### **ORDERING GUIDE**

| Model <sup>1</sup>                                                   | Temperature                                                                                                                  | Relative                                                                                                            | Gain                                                     | Package                                        |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------|

|                                                                      | Range                                                                                                                        | Accuracy                                                                                                            | Error                                                    | Option <sup>2</sup>                            |

| AD7628KN<br>AD7628KP<br>AD7628KR<br>AD7628BQ<br>AD7628TQ<br>AD7628TE | -40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C<br>-40°C to +85°C<br>-55°C to +125°C<br>-55°C to +125°C | $\pm 1/2$ LSB<br>$\pm 1/2$ LSB<br>$\pm 1/2$ LSB<br>$\pm 1/2$ LSB<br>$\pm 1/2$ LSB<br>$\pm 1/2$ LSB<br>$\pm 1/2$ LSB | ±2 LSB<br>±2 LSB<br>±2 LSB<br>±2 LSB<br>±2 LSB<br>±2 LSB | N-20<br>P-20A<br>R-20<br>Q-20<br>Q-20<br>E-20A |

NOTES

<sup>1</sup>To order MIL-STD-883, Class B process parts, add /883B to part number. Contact your local sales office for military data sheet.

$^2E$  = Leadless Ceramic Chip Carrier; N = Plastic DIP; P = Plastic Leaded Chip Carrier; Q = Cerdip; R = SOIC.

#### TERMINOLOGY

#### **Relative Accuracy:**

Relative accuracy or endpoint nonlinearity is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. It is measured after adjusting for zero and full-scale, and is normally expressed in LSBs or as a percentage of full-scale reading.

#### **Differential Nonlinearity:**

Differential nonlinearity is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of  $\pm 1$  LSB max over the operating temperature range ensures monotonicity.

#### **Gain Error:**

Gain error is a measure of the output error between an ideal DAC and the actual device output. It is measured with all 1s in the DAC latches after offset error has been adjusted out. Gain error of both DACs is adjustable to zero with external resistance.

#### **Output Capacitance:**

Capacitance from OUT A or OUT B to AGND.

#### **Digital-to-Analog Glitch Impulse:**

The amount of charge injected from the digital inputs to the analog output when the inputs change state. This is normally specified as the area of the glitch in either pA-secs or nV-secs, depending upon whether the glitch is measured as a current or voltage signal. Glitch impulse is measured with  $V_{REF}$  A,  $V_{REF}$  B = AGND.

#### **Channel-to-Channel Isolation:**

The proportion of input signal from one DAC's reference input that appears at the output of the other DAC, expressed as a ratio in dB.

#### **Digital Crosstalk:**

The glitch energy transferred to the output of one converter due to a change in digital input code to the other converter. Specified in nV secs.

**PIN CONFIGURATIONS**

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD7628 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### INTERFACE LOGIC INFORMATION DAC Selection

Both DAC latches share a common 8-bit input port. The control input DAC A/DAC B selects which DAC can accept data from the input port.

#### **Mode Selection**

Inputs  $\overline{CS}$  and  $\overline{WR}$  control the operating mode of the selected DAC. See Mode Selection Table below.

#### Write Mode

When  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  are both low, the selected DAC is in the write mode. The input data latches of the selected DAC are transparent and its analog output responds to activity on DB0–DB7.

#### Hold Mode

The selected DAC latch retains the data that was present on DB0–DB7 just prior to  $\overline{CS}$  or  $\overline{WR}$  assuming a high state. Both analog outputs remain at the values corresponding to the data in their respective latches.

Mode Selection Table

| DAC A/<br>DAC B | CS | WR | DAC A | DAC B |

|-----------------|----|----|-------|-------|

| L               | L  | L  | WRITE | HOLD  |

| Н               | L  | L  | HOLD  | WRITE |

| Х               | Н  | X  | HOLD  | HOLD  |

| Х               | X  | H  | HOLD  | HOLD  |

L = Low State, H = High State, X = Don't Care

#### WRITE CYCLE TIMING DIAGRAM

#### **CIRCUIT INFORMATION-D/A SECTION**

The AD7628 contains two identical 8-bit multiplying D/A converters, DAC A and DAC B. Each DAC consists of a highly stable thin film R-2R ladder and eight N-channel current steering switches. A simplified D/A circuit for DAC A is shown in Figure 1. An inverted R-2R ladder structure is used; that is, binary

Figure 1. Simplified Functional Circuit for DAC A

weighted currents are switched between the DAC output and AGND, thus maintaining fixed currents in each ladder leg independent of switch state.

#### EQUIVALENT CIRCUIT ANALYSIS

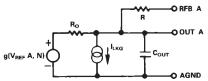

Figure 2 shows an approximate equivalent circuit for one of the AD7628's D/A converters, in this case DAC A. A similar equivalent circuit can be drawn for DAC B. Note that AGND (Pin 1) is common for both DAC A and DAC B.

The current source  $I_{LEAKAGE}$  is composed of surface and junction leakages and, as with most semiconductor devices, approximately doubles every 10°C. The resistor Ro, as shown in Figure 2, is the equivalent output resistance of the device, which varies with input code (excluding all 0s code) from 0.8R to 2R. R is typically 11 k $\Omega$ .  $C_{OUT}$  is the capacitance due to the N-channel switches and varies from about 50 pF to 120 pF, depending on the digital input.  $g(V_{REF} A, N)$  is the Thevenin equivalent voltage generator due to the R-2R ladder.

For further information on CMOS multiplying D/A converters, refer to "CMOS DAC Application Guide, 2ND Edition" available from Analog Devices, Publication Number G872a-15-4/86.

Figure 2. Equivalent Analog Output Circuit of DAC A

#### CIRCUIT INFORMATION-DIGITAL SECTION

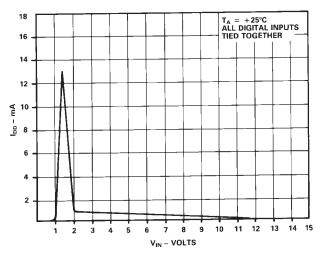

The input buffers are simple CMOS level-shifters designed so that when the AD7628 is operated with  $V_{\rm DD}$  from 10.8 V to 15.75 V, the buffer converts TTL input levels (2.4 V and 0.8 V) into CMOS logic levels. When  $V_{\rm IN}$  is in the region of 1.0 volt to 2.0 volts, the input buffers operate in their linear region and pass a quiescent current (see Figure 3). To minimize power supply currents, it is recommended that the digital input voltages be as close to the supply rails (V\_{\rm DD} and DGND) as practicably possible.

The AD7628 may be operated with any supply voltage in the range  $10.8 \le V_{DD} \le 15.75$  volts.

Figure 3. Typical Plot of Supply Current,  $I_{DD}$  vs. Logic Input Voltage  $V_{IN}$  to  $V_{DD}$  = +15 V

NOTES: "R1, R2, AND R3, R4 USED ONLY IF GAIN ADJUSTMENT IS REQUIRED SEE TABLE 3 FOR RECOMMENDED VALUES. "C1, C2 PHASE COMPENSATION (10p--15pF) IS REQUIRED WHEN USING HIGH SPEED AMPLIFIERS TO PREVENT RINGING OR OSCILLATION.

Figure 4. Dual DAC Unipolar Binary Operation (2 Quadrant Multiplication). See Table I.

Figure 5. Dual DAC Bipolar Operation (4 Quadrant Multiplication). See Table II.

Table II. Bipolar (Offset Binary) Code Table

| DAC Latch Contents<br>MSB LSB | Analog Output<br>(DAC A or DAC B)                         | DAC Latch Contents<br>MSB LSB | Analog Output<br>(DAC A or DAC B)     |

|-------------------------------|-----------------------------------------------------------|-------------------------------|---------------------------------------|

| 11111111                      | $-V_{IN}\left(rac{255}{256} ight)$                       |                               | $+V_{IN}\left(\frac{127}{128}\right)$ |

| 1 0 0 0 0 0 0 1               | $-V_{IN}\left(rac{129}{256} ight)$                       | 1 0 0 0 0 0 0 1               | $+V_{IN}\left(\frac{1}{128}\right)$   |

| 1 0 0 0 0 0 0 0 0             | $-V_{IN}\left(\frac{128}{256}\right) = -\frac{V_{IN}}{2}$ | 1 0 0 0 0 0 0 0 0             | 0                                     |

| 01111111                      | $-V_{IN}\left(rac{127}{256} ight)$                       | 0 1 1 1 1 1 1 1               | $-V_{IN}\left(\frac{1}{128}\right)$   |

| 0 0 0 0 0 0 0 1               | $-V_{IN}\left(rac{1}{256} ight)$                         | 0 0 0 0 0 0 0 0 1             | $-V_{IN}\left(\frac{127}{128}\right)$ |

| 0 0 0 0 0 0 0 0 0             | $-V_{IN}\left(\frac{0}{256}\right)=0$                     | 0 0 0 0 0 0 0 0 0             | $-V_{IN}\left(rac{128}{128} ight)$   |

NOTE: 1 LSB =  $(2^{-8})(V_{IN}) = \frac{1}{256}(V_{IN})$

NOTE: 1 LSB =  $(2^{-7})(V_{IN}) = \frac{1}{128} (V_{IN})$

**Table III. Recommended Trim Resistor Values**

| Trim<br>Resistor | K/B/T |

|------------------|-------|

| R1; R3           | 500   |

| R2; R4           | 150   |

#### APPLICATIONS INFORMATION Application Hints

To ensure system performance consistent with AD7628 specifications, careful attention must be given to the following points:

- 1. GENERAL GROUND MANAGEMENT: AC or transient voltages between the AD7628 AGND and DGND can cause noise injection into the analog output. The simplest method of ensuring that voltages at AGND and DGND are equal is to tie AGND and DGND together at the AD7628. In more omplex systems where the AGND-DGND intertie is on the backplane, it is recommended that diodes be connected in inverse parallel between the AD7628 AGND and DGND pins (1N914 or equivalent).

- 2. OUTPUT AMPLIFIER OFFSET: CMOS DACs exhibit a code-dependent output resistance which, in turn, causes a code-dependent amplifier noise gain. The effect is a code-dependent differential nonlinearity term at the amplifier output that depends on  $V_{\rm OS}$  ( $V_{\rm OS}$  is amplifier input offset voltage). This differential nonlinearity term adds to the R/2R differential nonlinearity. To maintain monotonic operation, it is recommended that amplifier  $V_{\rm OS}$  be no greater than 10% of 1 LSB over the temperature range of interest.

- 3. HIGH FREQUENCY CONSIDERATIONS: The output capacitance of a CMOS DAC works in conjunction with the amplifier feedback resistance to add a pole to the open loop response. This can cause ringing or oscillation. Stability can be restored by adding a phase compensation capacitor in parallel with the feedback resistor.

#### **DYNAMIC PERFORMANCE**

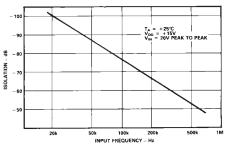

The dynamic performance of the two DACs in the AD7628 will depend on the gain and phase characteristics of the output amplifiers, together with the optimum choice of the PC board layout and decoupling components. Figure 6 shows the relationship between input frequency and channel-to-channel isolation.

Figure 6. Channel-to-Channel Isolation

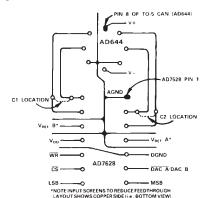

Figure 7. Suggested PC Board Layout for AD7628 with AD644 Dual Op Amp

Figure 7 shows a printed circuit layout for the AD7628 and the AD644 dual op amp, which minimizes feedthrough and crosstalk.

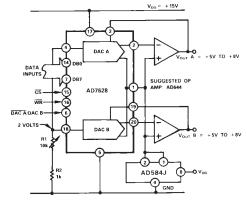

### SINGLE SUPPLY APPLICATIONS

The AD7628 DAC R-2R ladder termination resistors are connected to AGND within the device. This arrangement is particularly convenient for single supply operation because AGND may be biased at any voltage between DGND and  $V_{DD}$ . Figure 8 shows a circuit that provides two +5 V to +8 V analog outputs by biasing AGND +5 V up from DGND. The two DAC reference inputs are tied together and a reference input voltage is obtained without a buffer amplifier by making use of the constant and matched impedances of the DAC A and DAC B reference inputs. Current flows through the two DAC R-2R ladders into R1, and R1 is adjusted until the  $V_{REF}$  A and  $V_{REF}$  B inputs are at +2 V. The two analog output voltages range from +5 V to +8 V for DAC codes 00000000 to 11111111.

Figure 8. AD7628 Single Supply Operation

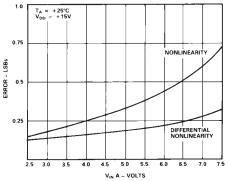

Figure 9 shows DAC A of the AD7628 connected in a positive reference, voltage switching mode. This configuration is useful because  $V_{\rm OUT}$  is the same polarity as  $V_{\rm IN}$ , allowing single supply operation. However, to retain specified linearity,  $V_{\rm IN}$  must be in the range 0 V to +2.5 V and the output buffered or loaded with a high impedance (see Figure 10). Note that the input voltage is connected to the DAC OUT A, and the output voltage is taken from the DAC  $V_{\rm REF}$  A pin.

Figure 10. Typical AD7628 Performance in Single Supply Voltage Switching Mode

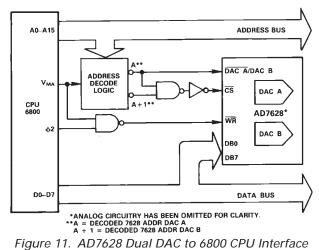

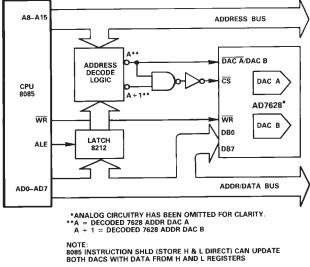

#### MICROPROCESSOR INTERFACE

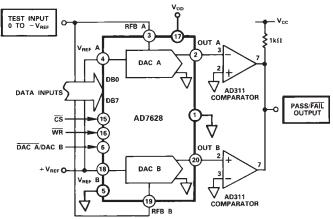

Figure 13. Digitally Programmable Window Comparator (Upper and Lower Limit Detector)

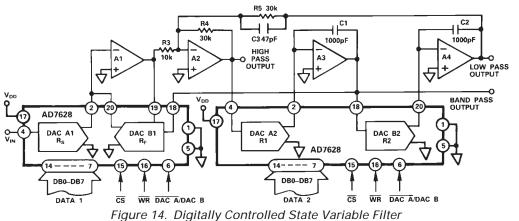

#### PROGRAMMABLE STATE VARIABLE FILTER

Figure 12. AD7628 Dual DAC to 8085 CPU Interface

In the circuit of Figure 13, the AD7628 is used to implement a programmable window comparator. DACs A and B are loaded with the required upper and lower voltage limits for the test, respectively. If the test input is not within the programmed limits, the pass/fail output will indicate a fail (logic zero).

#### **CIRCUIT EQUATIONS**

$$C_{1} = C_{2}, R_{1} = R_{2}, R_{4} = R_{5}$$

$$f_{C} = \frac{1}{2\pi R_{1} C_{1}}$$

$$Q = \frac{R_{3}}{R_{4}} \cdot \frac{R_{F}}{R_{FBB1}}$$

$$A_{O} = -\frac{R_{F}}{R_{S}}$$

NOTE

DAC equivalent resistance equals

$$\frac{256 \times (DAC \ Ladder \ resistance)}{DAC \ Digital \ Code}$$

In this state, variable or universal filter configuration (Figure 14) for DACs A1 and B1 control the gain and Q of the filter characteristic, while DACs A2 and B2 control the cutoff frequency,  $f_C$ . DACs A2 and B2 must track accurately for the simple expression for  $f_C$  to hold. This is readily accomplished by the AD7628. Op amps are  $2 \times AD644$ . C3 compensates for the effects of op amp gain-bandwidth limitations.

The filter provides low pass, high pass and band pass outputs and is ideally suited for applications where microprocessor control of filter parameters is required, e.g., equalizer, tone controls, etc.

Programmable range for component values shown is  $f_{\rm C}$  = 0 kHz to 15 kHz and Q = 0.3 to 4.5.

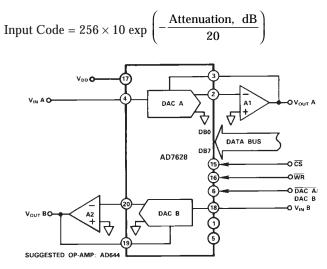

#### DIGITALLY CONTROLLED DUAL TELEPHONE ATTENUATOR

In this configuration, the AD7628 functions as a 2-channel digitally controlled attenuator; ideal for stereo audio and telephone signal level control applications. Table IV gives input codes vs. attenuation for a 0 dB to 15.5 dB range.

Figure 15. Digitally Controlled Dual Telephone Attenuator

| Table IV. Attenuation vs. DAC A, DAC B Code for the |

|-----------------------------------------------------|

| Circuit of Figure 15                                |

| Attn. dB | DAC Input<br>Code | Code in<br>Decimal | Attn. dB | DAC Input<br>Code | Code in<br>Decimal |

|----------|-------------------|--------------------|----------|-------------------|--------------------|

| 0        | 111111111         | 255                | 8.0      | 01100110          | 102                |

| 0.5      | 11110010          | 242                | 8.5      | 01100000          | 96                 |

| 1.0      | 11100100          | 228                | 9.0      | 01011011          | 91                 |

| 1.5      | 11010111          | 215                | 9.5      | 01010110          | 86                 |

| 2.0      | 11001011          | 203                | 10.0     | 01010001          | 81                 |

| 2.5      | 11000000          | 192                | 10.5     | 01001100          | 76                 |

| 3.0      | 10110101          | 181                | 11.0     | 01001000          | 72                 |

| 3.5      | 10101011          | 171                | 11.5     | 01000100          | 68                 |

| 4.0      | 10100010          | 162                | 12.0     | 01000000          | 64                 |

| 4.5      | 10011000          | 152                | 12.5     | 00111101          | 61                 |

| 5.0      | 10010000          | 144                | 13.0     | 00111001          | 57                 |

| 5.5      | 10001000          | 136                | 13.5     | 00110110          | 54                 |

| 6.0      | 10000000          | 128                | 14.0     | 0011001           | 51                 |

| 6.5      | 0111001           | 121                | 14.5     | 00110000          | 48                 |

| 7.0      | 01110010          | 114                | 15.0     | 00101110          | 46                 |

| 7.5      | 01101100          | 108                | 15.5     | 00101011          | 43                 |

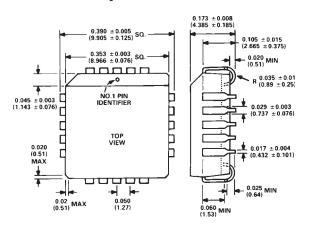

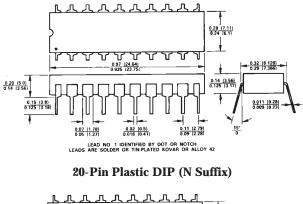

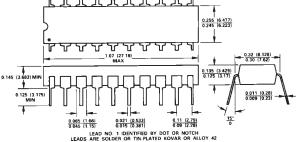

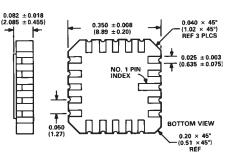

#### **MECHANICAL INFORMATION**

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### 20-Terminal Leadless Chip Carrier (E Suffix)

#### 20-Terminal Plastic Leaded Chip Carrier (P Suffix)