Is Now Part of

# **ON Semiconductor**®

# To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="https://www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to <a href="https://www.onsemi.com">Fairchild\_questions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized applications, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an equif prese

February 2013

# FAN6920MR mWSaver<sup>™</sup> Technology Integrated Critical-Mode PFC and Quasi-Resonant Current-Mode PWM Controller

### **Features**

- mWSaver™ Technology Provides Industry's Bestin-Class Standby Power

- Internal High-Voltage JFET Startup

- Adaptive Off-Time Modulation of t<sub>OFF-MIN</sub> for QR PWM Stage, Improved Light-Load Efficiency

- PFC Burst or Shutdown at Light-Load Condition

- Optimized for Dual Switch Flyback Design to Achieve > 90% Efficiency While Meeting 2013 ErP lot 6 Standby Power Requirement

- Integrated PFC and Flyback Controller

- Critical-Mode PFC Controller

- Zero-Current Detection for PFC Stage

- Quasi-Resonant Operation for PWM Stage

- Internal 5 ms Soft-Start for PWM

- Brownout Protection

- High / Low Line Over-Power Compensation

- Auto-Recovery Over-Current Protection

- Auto-Recovery Open-Loop Protection

- Externally Auto-Recovery Triggering (RT Pin)

- Adjustable Over-Temperature Protection

- VDD Pin and Output Voltage OVP (Auto-Recovery)

- Internal Over-Temperature Shutdown (140°C)

## Applications

- AC/DC NB Adapters

- Open-Frame SMPS

**Ordering Information**

Battery Charger

# Description

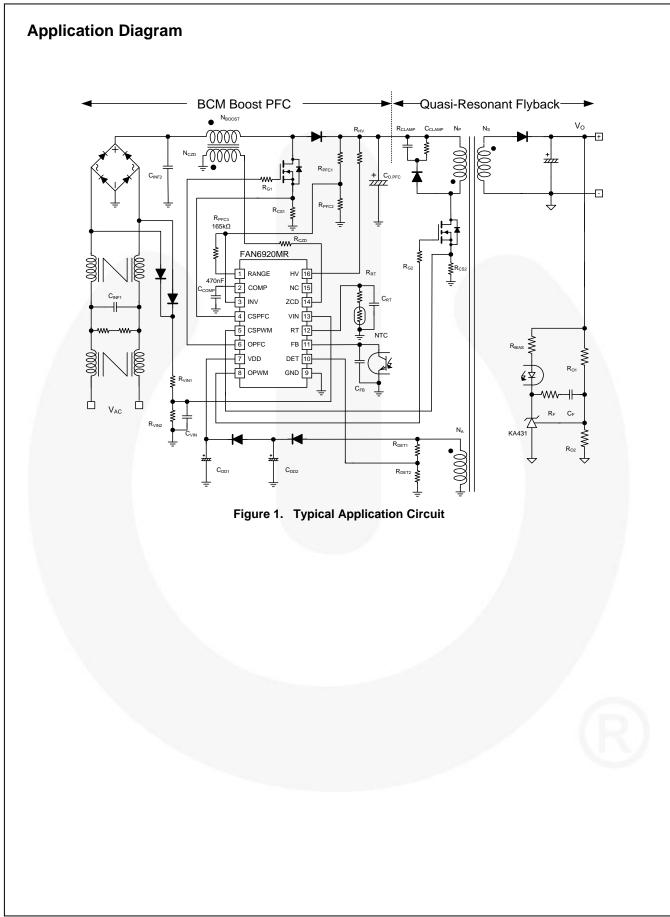

The highly integrated FAN6920MR combines Power Factor Correction (PFC) controller and quasi-resonant PWM controller. Integration provides cost-effective design and reduces external components.

For PFC, FAN6920MR uses a controlled on-time technique to provide a regulated DC output voltage and to perform natural power-factor correction. With an innovative THD optimizer, FAN6920MR can reduce input current distortion at zero-crossing duration to improve THD performance.

For PWM, FAN6920MR provides several functions to enhance the power system performance: valley detection, green-mode operation, and high / low line over-power compensation. Protection functions include secondaryside open-loop and over-current with auto-recovery protection; external auto-recovery triggering; adjustable over-temperature protection by the RT pin; and external NTC resistor, internal over-temperature shutdown, V<sub>DD</sub> pin OVP, and the DET pin over-voltage for output OVP, and brown-in / out for AC input voltage UVP.

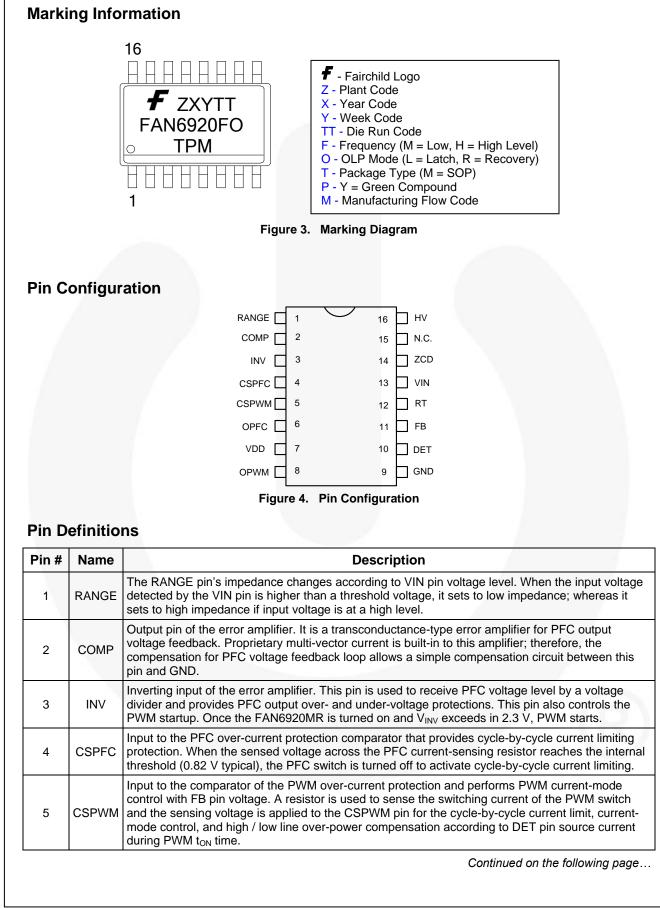

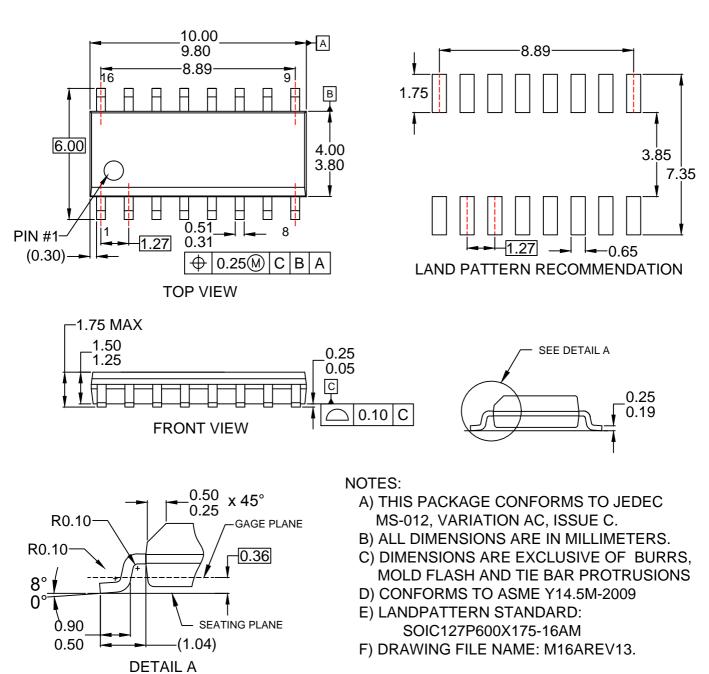

The FAN6920MR controller is available in a 16-pin small-outline package (SOP).

### **Related Resources**

Evaluation Board: FEBFAN6920MR\_T02U120A

| Part Number | OLP Mode | Operating<br>Temperature Range | Package                            | Packing<br>Method |

|-------------|----------|--------------------------------|------------------------------------|-------------------|

| FAN6920MRMY | Recovery | -40°C to +105°C                | 16-Pin Small Outline Package (SOP) | Tape & Reel       |

# Pin Definitions (Continued)

| in # | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6    | OPFC | Totem-pole driver output to drive the external power MOSFET. The clamped gate output voltage is 15.5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

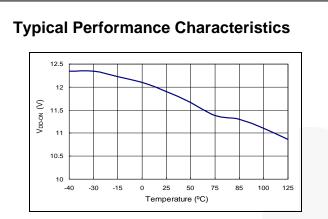

| 7    | VDD  | Power supply. The threshold voltages for startup and turn-off are 12 V and 7 V, respectively. The startup current is less than 30 $\mu$ A and the operating current is lower than 10 mA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8    | OPWM | Totem-pole output generates the PWM signal to drive the external power MOSFET. The clamped gate output voltage is 17.5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9    | GND  | The power ground and signal ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10   | DET  | <ul> <li>This pin is connected to an auxiliary winding of the PWM transformer through a resistor divider for the following purposes:</li> <li>Producing an offset voltage to compensate the threshold voltage of PWM current limit for overpower compensation. The offset is generated in accordance with the input voltage when the PWM switch is on.</li> <li>Detecting the valley voltage signal of drain voltage of the PWM switch to achieve the valley voltage switching and minimize the switching loss on the PWM switch.</li> <li>Providing output over-voltage protection. A voltage comparator is built in to the DET pin. The DET pin detects the flat voltage through a voltage divider paralleled with auxiliary winding. This flat voltage is reflected to the secondary winding DWM inductor discharge time. If output over-woltage near bicker the near the near the near three of DVM.</li> </ul> |

|      |      | over voltage and this flat voltage are higher than 2.5 V, the controller stops all PFC and PWM switching operation. The protection mode is auto-recovery.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

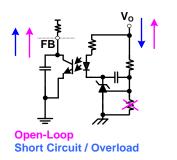

| 11   | FB   | Feedback voltage pin used to receive the output voltage level signal to determine PWM gate duty for regulating output voltage. The FB pin voltage can also activate open-loop, overload protection and output-short circuit protection if the FB pin voltage is higher than a threshold of around 4.2 V for more than 50 ms. The input impedance of this pin is a 5 k $\Omega$ equivalent resistance. A 1/3 attenuator is connected between the FB pin and the input of the CSPWM/FB comparator.                                                                                                                                                                                                                                                                                                                                                                                                                    |

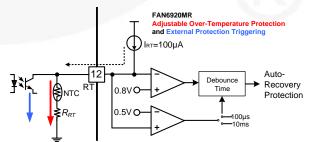

| 12   | RT   | Adjustable over-temperature protection and external protection triggering. A constant current flows out from the RT pin. When RT pin voltage is lower than 0.8 V (typical), protection is activated and stops PFC and PWM switching operation. This protection is auto-recovery.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 13   | VIN  | Line-voltage detection for brownin / out protections. This pin can receive the AC input voltage level through a voltage divider. The voltage level of the VIN pin is not only used to control RANGE pin's status, but it can also perform brownin / out protection for AC input voltage UVP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 14   | ZCD  | Zero-current detection for the PFC stage. This pin is connected to an auxiliary winding coupled to PFC inductor winding to detect the ZCD voltage signal once the PFC inductor current discharges to zero. When the ZCD voltage signal is detected, the controller starts a new PFC switching cycle. When the ZCD pin voltage is pulled to under 0.2 V (typical), it disables the PFC stage and the controller stops PFC switching. This can be realized with an external circuit if disabling the PFC stage is desired.                                                                                                                                                                                                                                                                                                                                                                                            |

| 15   | NC   | No connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6    | ΗV   | High-voltage startup pin is connected to the AC line voltage through a resistor (100 k $\Omega$ typical) for providing a high charging current to V <sub>DD</sub> capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                                                                 | Min. | Max. | Unit |

|------------------|---------------------------------------------------------------------------|------|------|------|

| V <sub>DD</sub>  | DC Supply Voltage                                                         |      | 30   | V    |

| $V_{HV}$         | HV                                                                        |      | 500  | V    |

| V <sub>H</sub>   | OPFC, OPWM                                                                | -0.3 | 25.0 | V    |

| VL               | INV, COMP, CSPFC, DET, FB, CSPWM, RT, VIN, RANGE                          | -0.3 | 7.0  | V    |

| V <sub>ZCD</sub> | Input Voltage to ZCD Pin                                                  | -0.3 | 12.0 | V    |

| PD               | Power Dissipation                                                         |      | 800  | mW   |

| heta ja          | Thermal Resistance (Junction-to-Air)                                      |      | 104  | °C/W |

| heta JC          | Thermal Resistance (Junction-to-Case)                                     |      | 41   | °C/W |

| TJ               | Operating Junction Temperature                                            | -40  | +150 | °C   |

| T <sub>STG</sub> | Storage Temperature Range                                                 | -55  | +150 | °C   |

| TL               | Lead Temperature (Soldering, 10 Seconds)                                  |      | +260 | °C   |

| FOD              | Human Body Model, JESD22-A114 (All Pins Except HV Pin) <sup>(3)</sup>     |      | 4500 | V    |

| ESD              | Charged Device Model, JESD22-C101 (All Pins Except HV Pin) <sup>(3)</sup> |      | 1250 | V    |

Notes:

1. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

2. All voltage values, except differential voltages, are given with respect to the GND pin.

3. All pins including HV pin: CDM=750 V, HBM 1000 V.

# **Electrical Characteristics**

| Symbol                                           | Parameter                                                                | Conditions                                                                                     | Min.                            | Тур.                            | Max.                            | Unit |

|--------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|---------------------------------|------|

| / <sub>DD</sub> Section                          | 1                                                                        |                                                                                                | 1                               |                                 | 11                              |      |

| V <sub>OP</sub>                                  | Continuously Operating Voltage                                           |                                                                                                |                                 |                                 | 25                              | V    |

| $V_{\text{DD-ON}}$                               | Turn-On Threshold Voltage                                                |                                                                                                | 10.5                            | 12.0                            | 13.5                            | V    |

| V <sub>DD-PWM-OFF</sub>                          | PWM Off Threshold Voltage                                                |                                                                                                | 6                               | 7                               | 8                               | V    |

| $V_{\text{DD-OFF}}$                              | Turn-Off Threshold Voltage                                               |                                                                                                | 4                               | 5                               | 6                               | V    |

| I <sub>DD-ST</sub>                               | Startup Current                                                          | V <sub>DD</sub> =V <sub>DD-ON</sub> - 0.16 V,<br>Gate Open                                     |                                 | 20                              | 30                              | μA   |

| I <sub>DD-OP</sub>                               | Operating Current                                                        | V <sub>DD</sub> =15 V, OPFC,<br>OPWM=100 kHz,<br>C <sub>L-PFC</sub> , C <sub>L-PWM</sub> =2 nF |                                 |                                 | 10                              | mA   |

| IDD-GREEN                                        | Green-Mode Operating Supply Current (Average)                            | V <sub>DD</sub> =15 V,<br>OPWM=450 Hz,<br>C <sub>L-PWM</sub> =2 nF                             |                                 | 5.5                             |                                 | mA   |

| IDD-PWM-OFF                                      | Operating Current at PWM-Off Phase                                       | V <sub>DD</sub> =V <sub>DD-PWM-OFF</sub> -<br>0.5 V                                            | 70                              | 120                             | 170                             | μA   |

| V <sub>DD-OVP</sub>                              | V <sub>DD</sub> Over-Voltage Protection<br>(Auto-Recovery)               |                                                                                                | 26.5                            | 27.5                            | 28.5                            | V    |

| t <sub>VDD-OVP</sub>                             | V <sub>DD</sub> OVP Debounce Time                                        |                                                                                                | 100                             | 150                             | 200                             | μs   |

| / Startup C                                      | urrent Source Section                                                    |                                                                                                |                                 |                                 |                                 |      |

| I <sub>HV</sub> Supply Current Drawn from HV Pin | V <sub>AC</sub> =90 V,<br>(V <sub>DC</sub> =120 V), V <sub>DD</sub> =0 V | 1.3                                                                                            |                                 |                                 | mA                              |      |

| ·nv                                              |                                                                          | HV=500 V,<br>V <sub>DD</sub> =V <sub>DD-OFF</sub> +1 V                                         |                                 | 1.0                             |                                 | μA   |

| N and RAN                                        | IGE Section                                                              |                                                                                                |                                 |                                 |                                 |      |

| $V_{\text{VIN-UVP}}$                             | Threshold Voltage for AC Input Under-<br>Voltage Protection              |                                                                                                | 0.95                            | 1.00                            | 1.05                            | V    |

| V <sub>VIN-RE-UVP</sub>                          | Under-Voltage Protection Reset<br>Voltage                                |                                                                                                | V <sub>VIN-UVP</sub><br>+0.15 V | V <sub>VIN-UVP</sub><br>+0.20 V | V <sub>VIN-UVP</sub><br>+0.25 V | V    |

| t <sub>vin-uvp</sub>                             | Under-Voltage Protection Debounce<br>Time                                |                                                                                                | 70                              | 100                             | 130                             | ms   |

| V <sub>VIN-RANGE-H</sub>                         | High V <sub>VIN</sub> Threshold for RANGE<br>Comparator                  |                                                                                                | 2.40                            | 2.45                            | 2.50                            | V    |

| Vvin-range-l                                     | Low V <sub>VIN</sub> Threshold for RANGE<br>Comparator                   |                                                                                                | 2.20                            | 2.25                            | 2.30                            | V    |

| t <sub>RANGE</sub>                               | Range-Enable / Disable Debounce<br>Time                                  |                                                                                                | 60                              | 90                              | 120                             | ms   |

| V <sub>RANGE-OL</sub>                            | Output Low Voltage of RANGE Pin                                          | I <sub>O</sub> =1 mA                                                                           |                                 |                                 | 0.5                             | V    |

| I <sub>RANGE-OH</sub>                            | Output High Leakage Current of<br>RANGE Pin                              | RANGE=5 V                                                                                      |                                 |                                 | 50                              | nA   |

| t <sub>ON-MAX-PFC</sub>                          | PFC Maximum On Time                                                      | R <sub>MOT</sub> =24 kΩ                                                                        | 22                              | 25                              | 28                              | μs   |

| Symbol               | Parameter                                              | Conditions                                                           | Min.                               | Тур.                               | Max.                               | Unit |

|----------------------|--------------------------------------------------------|----------------------------------------------------------------------|------------------------------------|------------------------------------|------------------------------------|------|

| PFC STAGE            |                                                        |                                                                      |                                    |                                    |                                    |      |

| /oltage Erro         | or Amplifier Section                                   |                                                                      |                                    |                                    |                                    |      |

| Gm                   | Transconductance <sup>(4)</sup>                        |                                                                      | 100                                | 125                                | 150                                | µmho |

| V <sub>REF</sub>     | Feedback Comparator Reference<br>Voltage               |                                                                      | 2.465                              | 2.500                              | 2.535                              | V    |

| .,                   |                                                        | RANGE=Open                                                           | 2.70                               | 2.75                               | 2.80                               | .,   |

| V <sub>INV-H</sub>   | Clamp High Feedback Voltage                            | RANGE=Ground                                                         | 2.60                               | 2.65                               | 2.70                               | V    |

| Vratio               | Clamp High Output Voltage Ratio <sup>(4)</sup>         | V <sub>INV-H</sub> / V <sub>REF</sub> ,<br>RANGE=Open                | 1.06                               |                                    | 1.14                               | V/V  |

| V RATIO              |                                                        | V <sub>INV-H</sub> / V <sub>REF</sub> ,<br>RANGE=Ground              | 1.04                               |                                    | 1.08                               | V/V  |

| V <sub>INV-L</sub>   | Clamp Low Feedback Voltage                             |                                                                      | 2.25                               | 2.35                               | 2.45                               | V    |

| V <sub>INV-OVP</sub> | Over-Voltage Protection for INV Inpu                   | RANGE=Open                                                           |                                    | 2.90                               | 2.95                               | v    |

|                      |                                                        | RANGE=Ground                                                         |                                    | 2.75                               | 2.80                               |      |

| t <sub>INV-OVP</sub> | Over-Voltage Protection Debounce                       |                                                                      | 50                                 | 70                                 | 90                                 | μs   |

| V <sub>INV-UVP</sub> | Under-Voltage Protection for INV Inp                   | put                                                                  | 0.35                               | 0.45                               | 0.55                               | V    |

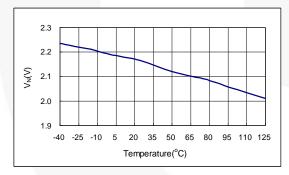

| VINV-PWMON           | PWM ON Threshold Voltage on INV                        | Pin                                                                  | 2.2                                | 2.3                                | 2.4                                | V    |

| VHYST-PWMON          | Hysteresis for PWM ON Threshold<br>Voltage on INV Pin  |                                                                      | V <sub>INV-</sub><br>PWMON<br>-1.6 | V <sub>INV-</sub><br>pwmon<br>-1.5 | V <sub>INV-</sub><br>PWMON<br>-1.4 | v    |

| t <sub>INV-UVP</sub> | Under-Voltage Protection Debounce<br>Time              |                                                                      | 50                                 | 70                                 | 90                                 | μs   |

| V <sub>INV-BO</sub>  | PWM and PFC Off Threshold for<br>Brownout Protection   |                                                                      | 1.15                               | 1.20                               | 1.25                               | V    |

| V <sub>COMP-BO</sub> | Limited Voltage on COMP Pin for<br>Brownout Protection |                                                                      | 1.55                               | 1.60                               | 1.65                               | V    |

| COMP-BURST           | Internal Bias Current for PFC Burst                    | Node                                                                 | 120                                | 150                                | 180                                | μA   |

|                      | Comparator Output High Voltage                         |                                                                      | 4.80                               | 0                                  | 5.20                               |      |

| V <sub>сомр-н</sub>  |                                                        | V <sub>FB</sub> =1.3 V, V <sub>VIN</sub> =1.2 V                      | 2.20                               | 2.30                               | 2.40                               | v    |

| V COMP-H             | Comparator Output High Voltage at Burst Mode           | V <sub>FB</sub> =1.3 V, V <sub>VIN</sub> =1.6 V                      | 2.00                               | 2.10                               | 2.20                               | v    |

|                      |                                                        | $V_{FB}$ =1.3 V, $V_{VIN}$ =2 V                                      | 1.80                               | 1.90                               | 2.00                               |      |

| V <sub>COMP-L</sub>  | Comparator Output Low Voltage at F<br>Burst Mode       | PFC RANGE=Open,<br>V <sub>FB</sub> =1.3 V                            | 0.9                                | 1.0                                | 1.1                                | V    |

| V <sub>oz</sub>      | Zero Duty Cycle Voltage on COMP F                      | Pin                                                                  | 1.10                               | 1.25                               | 1.40                               | V    |

|                      | Comparator Output Source Current                       | V <sub>INV</sub> =2.3 V,<br>V <sub>COMP</sub> =1.5 V                 | 15                                 | 30                                 | 45                                 | μA   |

|                      |                                                        | V <sub>INV</sub> =1.5 V                                              | 0.50                               | 0.75                               | 1.00                               | mA   |

| I <sub>COMP</sub>    |                                                        | RANGE=Open,<br>V <sub>INV</sub> =2.75 V,<br>V <sub>COMP</sub> =5 V   | 20                                 | 30                                 | 40                                 |      |

|                      | Comparator Output Sink Current                         | RANGE=Ground,<br>V <sub>INV</sub> =2.65 V,<br>V <sub>COMP</sub> =5 V | 20                                 | 30                                 | 40                                 | - μΑ |

|                      |                                                        |                                                                      | Contin                             | ued on the                         | following                          | page |

| Symbol               | Parameter                                                  | Conditions                                             | Min. | Тур.        | Max. | Unit |

|----------------------|------------------------------------------------------------|--------------------------------------------------------|------|-------------|------|------|

| C Current            | -Sense Section                                             |                                                        |      |             |      |      |

| V <sub>CSPFC</sub>   | Threshold Voltage for Peak Current<br>Cycle-by-Cycle Limit | V <sub>COMP</sub> =5 V                                 | 0.77 | 0.82        | 0.87 | V    |

| t <sub>PD</sub>      | Propagation Delay                                          |                                                        |      | 110         | 200  | ns   |

| t <sub>BNK</sub>     | Leading-Edge Blanking Time                                 |                                                        | 110  | 180         | 250  | ns   |

| Av                   | CSPFC Compensation Ratio for THD                           |                                                        | 0.90 | 0.95        | 1.00 | V/V  |

| C Output             | Section                                                    |                                                        |      |             |      |      |

| Vz                   | PFC Gate Output Clamping Voltage                           | V <sub>DD</sub> =25 V                                  | 14.0 | 15.5        | 17.0 | V    |

| V <sub>OL</sub>      | PFC Gate Output Voltage Low                                | V <sub>DD</sub> =15 V,<br>I <sub>O</sub> =100 mA       | 1    |             | 1.5  | V    |

| V <sub>он</sub>      | PFC Gate Output Voltage High                               | V <sub>DD</sub> =15 V,<br>I <sub>O</sub> =100 mA       | 8    |             |      | V    |

| t <sub>R</sub>       | PFC Gate Output Rising Time                                | V <sub>DD</sub> =12 V, C <sub>L</sub> =3 nF, 20~80%    | 30   | 65          | 100  | ns   |

| t <sub>F</sub>       | PFC Gate Output Falling Time                               | V <sub>DD</sub> =12 V, C <sub>L</sub> =3 nF,<br>80~20% | 30   | 50          | 70   | ns   |

| C Zero-Cu            | urrent Detection Section                                   |                                                        |      |             |      |      |

| V <sub>ZCD</sub>     | Input Threshold Voltage Rising Edge                        | V <sub>ZCD</sub> Increasing                            | 1.9  | 2.1         | 2.3  | V    |

| ZCD-HYST             | Threshold Voltage Hysteresis                               | V <sub>ZCD</sub> Decreasing                            | 0.25 | 0.35        | 0.45 | V    |

| ZCD-HIGH             | Upper Clamp Voltage                                        | I <sub>ZCD</sub> =3 mA                                 | 8    | 10          |      | V    |

| ZCD-LOW              | Lower Clamp Voltage                                        |                                                        | 0.35 | 0.45        | 0.55 | V    |

| ZCD-SSC              | Starting Source Current Threshold Voltage                  |                                                        | 0.70 | 0.90        | 1.10 | V    |

| t <sub>DELAY</sub>   | Maximum Delay from ZCD to Output<br>Turn-On                | V <sub>COMP</sub> =5 V,<br>f <sub>S</sub> =60 kHz      | 100  |             | 200  | ns   |

| START-PFC            | Restart Time                                               |                                                        | 300  | 500         | 700  | μs   |

| t <sub>INHIB</sub>   | Inhibit Time (Maximum Switching<br>Frequency Limit)        | V <sub>COMP</sub> =5 V                                 | 1.5  | 2.5         | 3.5  | μs   |

| ZCD-DIS              | PFC Enable / Disable Function<br>Threshold Voltage         |                                                        | 0.15 | 0.20        | 0.25 | V    |

| t <sub>ZCD-DIS</sub> | PFC Enable / Disable Function<br>Debounce Time             | V <sub>ZCD</sub> =100 mV                               | 100  | 150         | 200  | μs   |

|                      |                                                            |                                                        |      | inued on ti |      |      |

|                         | Parameter                                                                                                     | Conditions                                                    | Min.   | Тур.         | Max.   | Unit |

|-------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------|--------------|--------|------|

| WM STAG                 | È                                                                                                             |                                                               |        |              |        |      |

| Feedback In             | put Section                                                                                                   |                                                               |        |              |        |      |

| Av                      | Input-Voltage to Current Sense<br>Attenuation <sup>(4)</sup>                                                  | $A_V = \Delta V_{CS} / \Delta V_{FB}$ ,<br>0 < $V_{CS}$ < 0.9 | 1/2.75 | 1/3.00       | 1/3.25 | V/V  |

| Z <sub>FB</sub>         | Input Impedance <sup>(4)</sup>                                                                                | $V_{FB} > V_G$                                                | 3      | 5            | 7      | kΩ   |

| loz                     | Bias Current                                                                                                  | V <sub>FB</sub> =V <sub>OZ</sub>                              |        | 1.2          | 2.0    | mA   |

| V <sub>oz</sub>         | Zero Duty Cycle Input Voltage                                                                                 |                                                               | 0.7    | 0.9          | 1.1    | V    |

| V <sub>FB-OLP</sub>     | Open-Loop Protection Threshold<br>Voltage                                                                     |                                                               | 3.9    | 4.2          | 4.5    | V    |

| t <sub>FB-OLP</sub>     | The Debounce Time for Open-Loop<br>Protection                                                                 |                                                               | 40     | 50           | 60     | ms   |

| t <sub>FB-SS</sub>      | Internal Soft-Start Time <sup>(4)</sup>                                                                       | V <sub>FB</sub> =0 V~3.6 V                                    | 4      | 5            | 6      | ms   |

| DET Pin OV              | and Valley Detection Section                                                                                  |                                                               |        |              |        |      |

| V <sub>DET-OVP</sub>    | Comparator Reference Voltage                                                                                  |                                                               | 2.45   | 2.50         | 2.55   | V    |

| Av                      | Open-Loop Gain <sup>(4)</sup>                                                                                 |                                                               |        | 60           |        | dB   |

| BW                      | Gain Bandwidth <sup>(4)</sup>                                                                                 |                                                               |        | 1            |        | MHz  |

| t <sub>DET-OVP</sub>    | Output OVP (Auto-Recovery) Debounce<br>Time                                                                   |                                                               | 100    | 150          | 200    | μs   |

| I <sub>DET-SOURCE</sub> | Maximum Source Current                                                                                        | V <sub>DET</sub> =0 V                                         |        |              | 1      | mA   |

| $V_{\text{DET-LOW}}$    | Lower Clamp Voltage                                                                                           | I <sub>DET</sub> =1 mA                                        | 0.15   | 0.25         | 0.35   | V    |

| VALLEY-DELAY            | Delay Time from Valley Signal Detected to Output Turn-On <sup>(4)</sup>                                       |                                                               | 150    | 200          | 250    | ns   |

| toff-bnk                | Leading-Edge Blanking Time for DET-<br>OVP (2.5 V) and Valley Signal when<br>PWM MOS Turns Off <sup>(4)</sup> |                                                               |        | 2.5          |        | μs   |

| t <sub>TIME-OUT</sub>   | Time-Out After t <sub>OFF-MIN</sub> <sup>(4)</sup>                                                            |                                                               | 8      | 9            | 10     | μs   |

| WM Oscilla              | tor Section                                                                                                   |                                                               |        |              |        |      |

| t <sub>on-max-pwm</sub> | Maximum On-Time                                                                                               |                                                               | 38     | 45           | 52     | μs   |

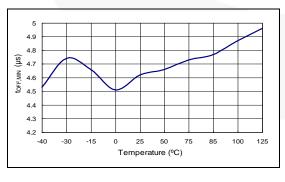

| t <sub>OFF-MIN</sub>    | Minimum Off-Time                                                                                              | $V_{FB} \geqq V_{N}\text{, } T_{A}\text{=}25^{\circ}\text{C}$ |        | 5            |        | μs   |

| V <sub>N</sub>          | Beginning of Green-On Mode at FB                                                                              | V <sub>FB</sub> =V <sub>G</sub>                               | 1.95   | 20.5<br>2.10 | 2.25   | V    |

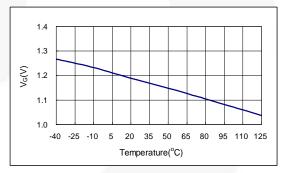

| V <sub>G</sub>          | Voltage Level<br>Beginning of Green-Off Mode at FB<br>Voltage Level                                           |                                                               | 1.00   | 1.15         | 1.30   | V    |

|                         | Hysteresis for Beginning of Green-Off<br>Mode at FB Voltage Level <sup>(4)</sup>                              |                                                               |        | 0.1          | - (    | V    |

| Symbol              | Parameter                                                     | Conditions                                                                                                | Min. | Тур.       | Max.        | Unit     |

|---------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------|------------|-------------|----------|

| TRL-PFC-BM          | Threshold Voltage on FB Pin for PFC                           | RANGE Pin<br>Internally Open                                                                              | 1.65 | 1.70       | 1.75        | v        |

| TRL-PFC-BM          | Burst Mode                                                    | RANGE Pin<br>Internally Ground                                                                            | 1.60 | 1.65       | 1.70        | v        |

| TRL-PFC-ON          | Threshold Voltage on FB Pin for PFC Normal operating          |                                                                                                           | 1.75 | 1.80       | 1.85        | V        |

| t <sub>PFC-BM</sub> | Debounce Time for PFC Burst Mode                              | PFC Normal<br>Operating → Burst<br>Mode                                                                   |      | 100        |             | ms       |

| t <sub>PFC-ON</sub> | Debounce Time for PFC Recovery to Normal Operating            | PFC Burst Mode→<br>Normal Operating                                                                       |      | 200        |             | μs       |

|                     |                                                               | $V_{FB} < V_G,  T_A {=} 25^\circ C$                                                                       | 1.85 | 2.25       | 2.65        | ms       |

| ARTER-PWM           | Start Timer (Time-Out Timer)                                  | $\label{eq:VFB} \begin{split} V_{FB} &> V_{FB\text{-}OLP}, \\ T_A &= 25^{\circ}C \end{split}$             | 22   | 28         | 34          | μs       |

| /M Output           | Section                                                       |                                                                                                           |      | _          |             |          |

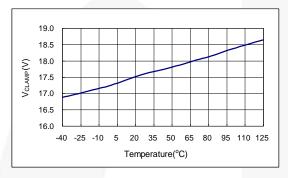

| V <sub>CLAMP</sub>  | PWM Gate Output Clamping Voltage                              | V <sub>DD</sub> =25 V                                                                                     | 16.0 | 17.5       | 19.0        | V        |

| V <sub>OL</sub>     | PWM Gate Output Voltage Low                                   | V <sub>DD</sub> =15 V,<br>I <sub>O</sub> =100 mA                                                          |      |            | 1.5         | V        |

| V <sub>OH</sub>     | PWM Gate Output Voltage High                                  | V <sub>DD</sub> =15 V,<br>I <sub>O</sub> =100 mA                                                          | 8    |            |             | V        |

| t <sub>R</sub>      | PWM Gate Output Rising Time                                   | C <sub>L</sub> =3 nF,<br>V <sub>DD</sub> =12 V, 20~80%                                                    |      | 80         | 110         | ns       |

| t <sub>F</sub>      | PWM Gate Output Falling Time                                  | C <sub>L</sub> =3 nF, V <sub>DD</sub> =12 V, 20~80%                                                       |      | 40         | 70          | ns       |

| rrent Sens          | se Section                                                    |                                                                                                           |      |            |             |          |

| t <sub>PD</sub>     | Delay to Output                                               |                                                                                                           |      | 150        | 200         | ns       |

|                     |                                                               | $\begin{array}{l} I_{DET} < 75 \; \mu \text{A}, \\ T_{\text{A}} \mbox{=} 25^{\circ} \mbox{C} \end{array}$ | 0.81 | 0.84       | 0.87        | v        |

| V <sub>LIMIT</sub>  | Limit Voltage on CSPWM Pin for Over-                          | I <sub>DET</sub> =185 μA,<br>T <sub>A</sub> =25°C                                                         | 0.69 | 0.72       | 0.75        |          |

|                     | Power Compensation                                            | I <sub>DET</sub> =350 μA,<br>T <sub>A</sub> =25°C                                                         | 0.55 | 0.58       | 0.61        |          |

|                     |                                                               | I <sub>DET</sub> =550 μA,<br>T <sub>A</sub> =25°C                                                         | 0.37 | 0.40       | 0.43        |          |

| V <sub>SLOPE</sub>  | Slope Compensation <sup>(4)</sup>                             | t <sub>on</sub> =45 μs,<br>RANGE=Open                                                                     | 0.25 | 0.30       | 0.35        | v        |

|                     |                                                               | t <sub>ON</sub> =0 μs                                                                                     | 0.05 | 0.10       | 0.15        |          |

| t <sub>on-вnк</sub> | Leading-Edge Blanking Time                                    |                                                                                                           |      | 300        | _           | ns       |

| S-FLOATING          | CSPWM Pin Floating V <sub>CSPWM</sub> Clamped<br>High Voltage | CSPWM Pin<br>Floating                                                                                     | 4.5  |            | 5.0         | V        |

| t <sub>CS-H</sub>   | Delay Time, CS Pin Floating                                   | CSPWM Pin<br>Floating                                                                                     |      | 150        |             | μs       |

|                     |                                                               |                                                                                                           | Cont | inued on t | he followir | ng page. |

$V_{\text{DD}}\text{=}15$  V and  $T_{\text{A}}\text{=}25^{\circ}\text{C}$  unless otherwise noted.

| Symbol                    | Parameter                                              | Conditions                                  | Min. | Тур. | Max. | Unit |

|---------------------------|--------------------------------------------------------|---------------------------------------------|------|------|------|------|

| RT Pin Over-              | Temperature Protection Section                         |                                             | •    |      |      |      |

| T <sub>OTP</sub>          | Internal Threshold Temperature for OTP <sup>(4)</sup>  |                                             | 125  | 140  | 155  | °C   |

| T <sub>OTP-HYST</sub>     | Hysteresis Temperature for Internal OTP <sup>(4)</sup> |                                             |      | 30   |      | °C   |

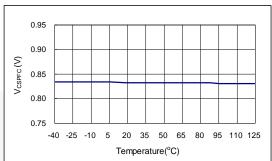

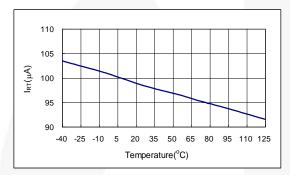

| I <sub>RT</sub>           | Internal Source Current of RT Pin                      |                                             | 90   | 100  | 110  | μA   |

| $V_{RT-AR}$               | Protection Triggering Voltage                          |                                             | 0.75 | 0.80 | 0.85 | V    |

| V <sub>RT-OTP-LEVEL</sub> | Threshold Voltage for Two-Level<br>Debounce Time       |                                             | 0.45 | 0.50 | 0.55 | V    |

| t <sub>RT-ОТР-Н</sub>     | Debounce Time for OTP                                  |                                             |      | 10   |      | ms   |

| t <sub>RT-OTP-L</sub>     | Debounce Time for Externally Triggering                | V <sub>RT</sub> < V <sub>RT-OTP-LEVEL</sub> | 70   | 110  | 150  | μs   |

Note:

4. Guaranteed by design.

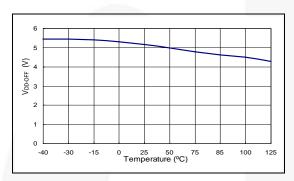

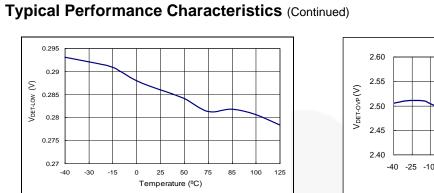

Figure 5. Turn-On Threshold Voltage

Figure 7. Turn-Off Threshold Voltage

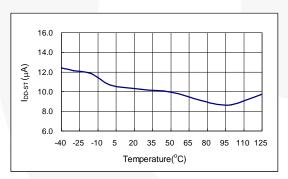

Figure 9. Startup Current

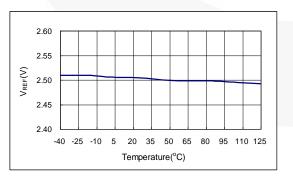

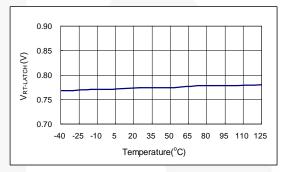

Figure 11. PFC Output Feedback Reference Voltage

Figure 6. PWM-Off Threshold Voltage

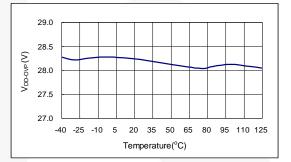

Figure 8. V<sub>DD</sub> Over-Voltage Protection Threshold

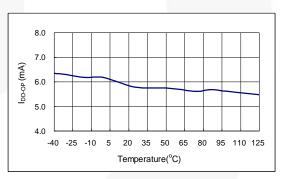

Figure 10. Operating Current

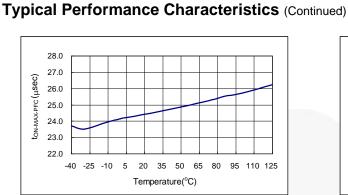

Figure 13. PFC Maximum On-Time

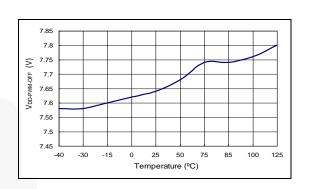

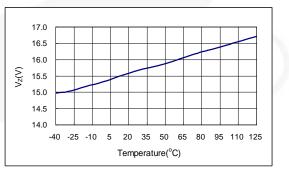

Figure 15. PWM Gate Output Clamping Voltage

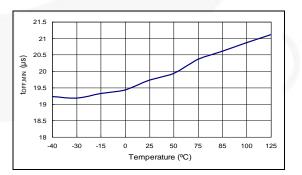

Figure 17. Beginning of Green-On Mode at V<sub>FB</sub>

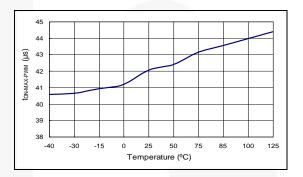

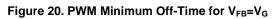

Figure 19. PWM Minimum Off-Time for  $V_{FB} > V_N$

Figure 14. PFC Peak Current Limit Voltage

Figure 16. PWM Maximum On-Time

Figure 18. Beginning of Green-Off Mode at  $V_{\mbox{\scriptsize FB}}$

Figure 21. Lower Clamp Voltage of DET Pin

2.60 2.55 2.50 2.45 2.40 -40 -25 -10 5 20 35 50 65 80 95 110 125 Temperature(°C)

Figure 22. Reference Voltage for Output Over-Voltage Protection of DET Pin

Figure 24. Over-Temperature Protection Threshold Voltage of RT Pin

### **Functional Description**

#### **PFC Stage**

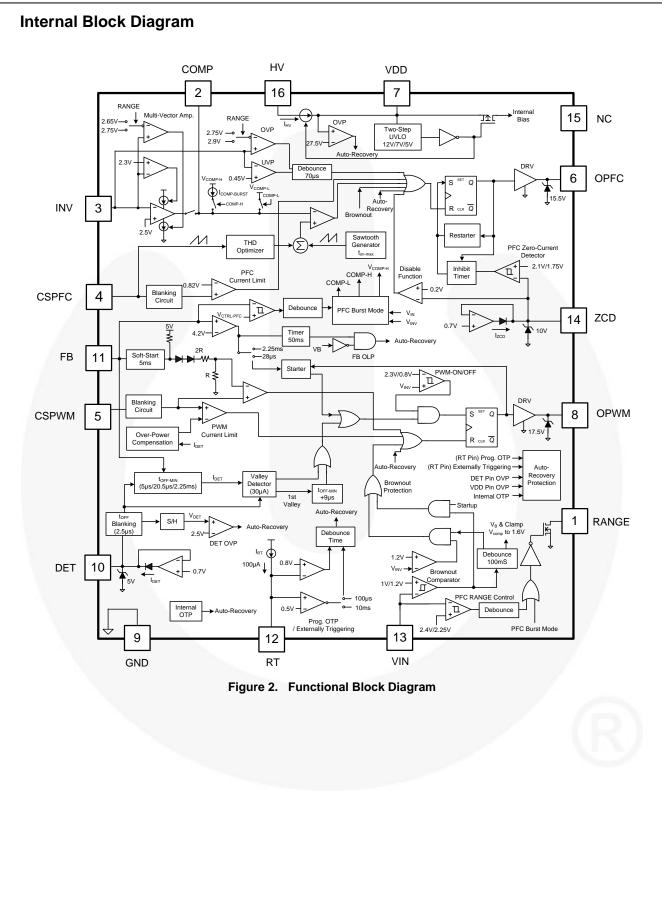

#### Multi-Vector Error Amplifier and THD Optimizer

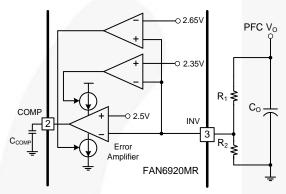

For better dynamic performance, faster transient response, and precise clamping on the PFC output, FAN6920MR uses a transconductance type amplifier with proprietary innovative multi-vector error amplifier. The schematic diagram of this amplifier is shown in Figure 25. The PFC output voltage is detected from the INV pin by an external resistor divider circuit that consists of  $R_1$  and  $R_2$ . When PFC output variation voltage reaches 6% over or under the reference voltage of 2.5 V, the multi-vector error amplifier adjusts its output sink or source current to increase the loop response to simplify the compensated circuit.

Figure 25. Multi-Vector Error Amplifier

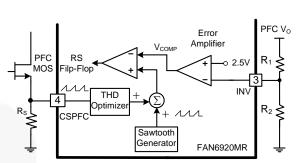

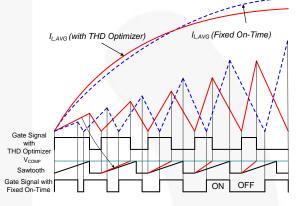

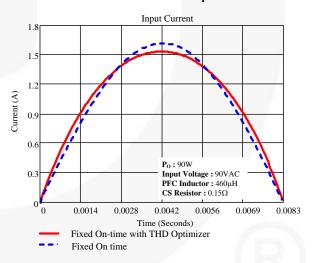

The feedback voltage signal on the INV pin is compared with reference voltage 2.5 V, which makes the error amplifier source or sink current to charge or discharge its output capacitor C<sub>COMP</sub>. The COMP voltage is compared with the internally generated sawtooth waveform to determine the on-time of PFC gate. Normally, with lower feedback loop bandwidth, the variation of the PFC gate on-time should be very small and almost constant within one input AC cycle. However, the power factor correction circuit operating at light-load condition has a defect, zero crossing distortion; which distorts input current and makes the system's Total Harmonic Distortion (THD) worse. To improve the result of THD at light-load condition. especially at high input voltage, an innovative THD optimizer is inserted by sampling the voltage across the current-sense resistor. This sampling voltage on current-sense resistor is added into the sawtooth waveform to modulate the on-time of PFC gate, so it is not constant on-time within a half AC cycle. The method of operation block between THD optimizer and PWM is shown in Figure 26. After THD optimizer processes, around the valley of AC input voltage, the compensated on-time becomes wider than the original. The PFC ontime, which is around the peak voltage, is narrowed by the THD optimizer. The timing sequences of the PFC MOS and the shape of the inductor current are shown in Figure 27. Figure 28 shows the difference between calculated fixed on-time mechanism and fixed on-time with THD optimizer during a half AC cycle.

Figure 27. Operation Waveforms of Fixed On-Time with and without THD Optimizer

#### Figure 28. Calculated Waveforms of Fixed On-Time with and without THD Optimizer During a Half AC Cycle

#### **RANGE Pin**

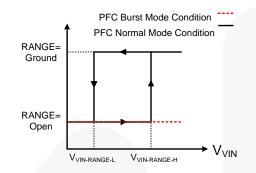

A built-in low-voltage MOSFET can be turned on or off according to  $V_{VIN}$  voltage level and PFC status. The drain pin of this internal MOSFET is connected to the RANGE pin. Figure 29 shows the status curve of  $V_{VIN}$  voltage level and RANGE impedance (open or ground).

#### Figure 29. Hysteresis Behavior between RANGE Pin and VIN Pin Voltage

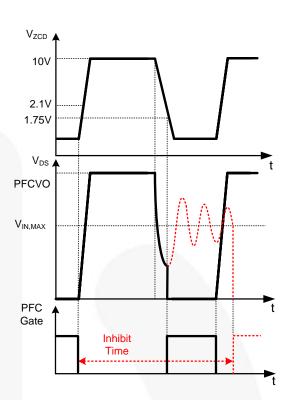

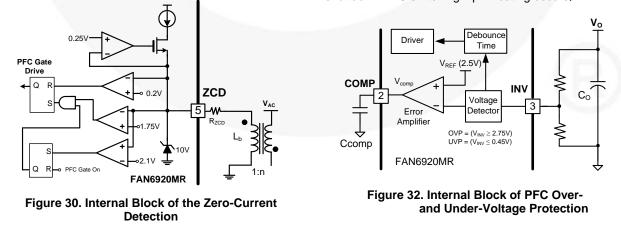

#### Zero-Current Detection (ZCD Pin)

Figure 30 shows the internal block of zero-current detection. The detection function is performed by sensing the information on an auxiliary winding of the PFC inductor. Referring to Figure 31, when PFC MOS is off, the stored energy of the PFC inductor starts to release to the output load. Then the drain voltage of PFC MOS starts to decrease since the PFC inductor resonates with parasitic capacitance. Once the ZCD pin voltage is lower than the triggering voltage (1.75 V typical), the PFC gate signal is sent again to start a new switching cycle.

If PFC operation needs to be shut down due to abnormal condition, pull the ZCD pin LOW, voltage under 0.2 V (typical), to activate the PFC disable function to stop PFC switching operation.

For preventing excessive high switching frequency at light load, a built-in inhibit timer is used to limit the minimum  $t_{OFF}$  time. Even if the ZCD signal has been detected, the PFC gate signal is not sent during the inhibit time (2.5 µs typical).

Figure 31. Operation Waveforms of PFC Zero-Current Detection

#### **Protection for PFC Stage**

#### PFC Output Voltage UVP and OVP (INV Pin)

FAN6920MR provides several kinds of protection for PFC stage. PFC output over- and under-voltage are essential for PFC stage. Both are detected and determined by INV pin voltage, as shown in Figure 32. When INV pin voltage is over 2.75 V or under 0.45 V, due to overshoot or abnormal conditions, and lasts for a de-bounce time around 70  $\mu$ s; the OVP or UVP circuit is activated to stop PFC switching operation immediately.

The INV pin is not only used to receive and regulate PFC output voltage; it can also perform PFC output OVP/ UVP protection. For failure-mode test, this pin can shut down PFC switching if pin floating occurs.

17

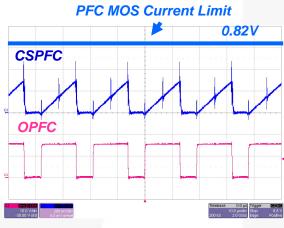

#### PFC Peak Current Limiting (CSPFC Pin)

During PFC stage switching operation, the PFC switch current is detected by the current-sense resistor on the CSPFC pin and the detected voltage on this resistor is delivered to the input terminal of a comparator and compared with a threshold voltage 0.82 V (typical). Once the CSPFC pin voltage is higher than the threshold voltage, the PFC gate is turned off immediately.

The PFC peak switching current is adjustable by the current-sense resistor. Figure 33 shows the measured waveform of PFC gate and CSPFC pin voltage.

Figure 33. Cycle-by-Cycle Current Limiting

#### **Brownout Protection (VIN Pin)**

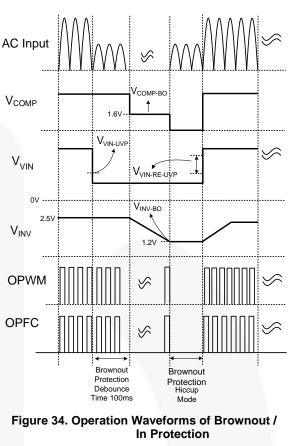

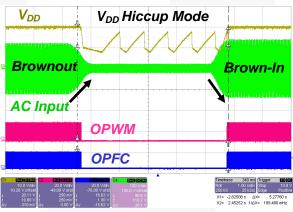

With AC voltage detection, FAN6920MR can perform brownout / in protection (AC voltage UVP). Figure 34 shows the key operation waveforms of brownout / in protection. Both use the VIN pin to detect AC input voltage level and the VIN pin is connected to AC input by a resistor divider (refer to Figure 1); therefore, the V<sub>VIN</sub> voltage is proportional to the AC input voltage. When the AC voltage drops and V<sub>VIN</sub> voltage is lower than 1 V for 100 ms, the UVP protection is activated and the COMP pin voltage is clamped to around 1.6 V. Because PFC gate duty is determined by comparing the sawtooth waveform and COMP pin voltage, lower COMP voltage results in narrow PFC on-time, so that the energy converged is limited and the PFC output voltage decreases. When INV pin voltage is lower than 1.2 V, FAN6920MR stops all PFC and PWM switching operation immediately until V<sub>DD</sub> voltage drops to turn-off voltage then rises to turn-on voltage again (UVLO).

When the brownout protection is activated, all switching operation is turned off and  $V_{\text{DD}}$  voltage enters Hiccup Mode up and down continuously. Once  $V_{\text{VIN}}$  voltage is higher than 1.3 V (typical) and  $V_{\text{DD}}$  reaches turn-on voltage again, the PWM and PFC gate is sent.

The measured waveforms of brownout / in protection are shown in Figure 35.

Figure 35. Measured Waveform of Brownout / In Protection (Adapter Application)

#### **PFC Burst Mode**

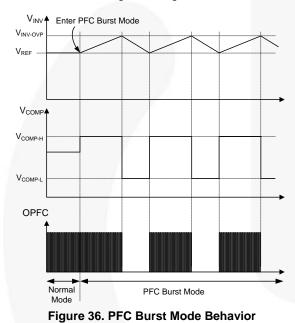

To minimize the power dissipation at light-load condition, the FAN6920MR PFC control enters burstmode operation. As the load decreases, the PWM feedback voltage (V<sub>FB</sub>) decreases. When V<sub>FB</sub> < V<sub>CTRL-</sub> PFC-BM for 100 ms, the device enters PFC burst mode, the V<sub>COMP</sub> pulls high to V<sub>COMP-H</sub>, and PFC output voltage increases. When the PFC feedback voltage on INV pin (V<sub>INV</sub>) triggers the OVP threshold voltage (V<sub>INV-OVP</sub>), V<sub>COMP</sub> pulls low to V<sub>COMP-L</sub>, the OPFC pin switching stops and the PFC output voltages start to drop. Once the V<sub>INV</sub> drops below the feedback comparator reference voltage (V<sub>REF</sub>), V<sub>COMP</sub> pulls high to V<sub>COMP-H</sub> and OPFC starts switching again. Burst-mode operation alternately enables and disables switching of the power MOSFET to reduce the switching loss at light-load condition.

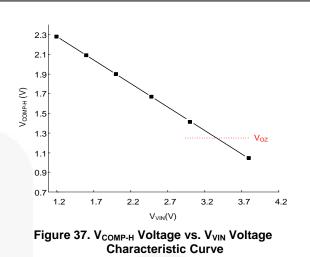

The V<sub>COMP-H</sub> is adjusted by the VIN pin voltage, as shown in Figure 37. Since the VIN pin is connected to rectified AC input line voltage through the resistive divider, a higher line voltage generates a higher VIN pin voltage. The V<sub>COMP-H</sub> decreases as VIN pin voltage increases, limiting the PFC choke current at a higher input voltage to reduce acoustic noise. If the V<sub>COMP-H</sub> is below the PFC V<sub>OZ</sub>, the PFC automatically shuts down at light load with high line voltage input condition.

#### PWM Stage

#### HV Startup and Operating Current (HV Pin)

The HV pin is connected to the AC line through a resistor (refer to Figure 1). With a built-in high-voltage startup circuit, when AC voltage is applied to the power system, FAN6920MR provides a high current to charge the external  $V_{DD}$  capacitor to speed up controller's startup time and build up normal rated output voltage within three seconds. To save power consumption, after  $V_{DD}$  voltage exceeds turn-on voltage and enters normal operation; this high-voltage startup resistor.

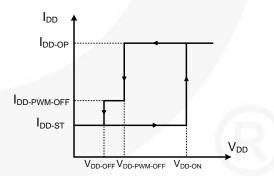

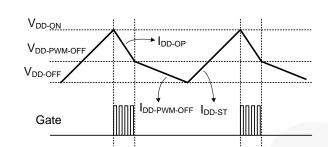

Figure 38 shows the characteristic curve of V<sub>DD</sub> voltage and operating current I<sub>DD</sub>. When V<sub>DD</sub> voltage is lower than V<sub>DD-PWM-OFF</sub>, FAN6920MR stops all switching operation and turns off unnecessary internal circuits to reduce operating current. By doing so, the period from V<sub>DD-PWM-OFF</sub> to V<sub>DD-OFF</sub> can be extended and the hiccup mode frequency can be decreased to reduce the input power in case of output short circuit. Figure 39 shows the typical waveforms of V<sub>DD</sub> voltage and gate signal with hiccup mode operation.

Figure 38. V<sub>DD</sub> vs. I<sub>DD-OP</sub> Characteristic Curve

#### Figure 39. Typical Waveform of V<sub>DD</sub> Voltage and Gate Signal at Hiccup Mode Operation

# Green-Mode Operation and PFC-ON / OFF Control (FB Pin)

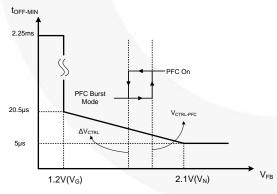

Green mode further reduces power loss in the system (e.g. switching loss). Through off-time modulation to regulate switching frequency according to FB pin voltage. When output loading decreases, FB voltage lowers due to secondary feedback movement and the t<sub>OFF-MIN</sub> is extended. After t<sub>OFF-MIN</sub> (determined by FB voltage), the internal valley-detection circuit is activated to detect the valley on the drain voltage of the PWM switch. When the valley signal is detected, FAN6920MR outputs a PWM gate signal to turn on the switch and begin a new switching cycle.

With green mode operation and valley detection, at light-load condition; the power system can perform extended valley switching a DCM operation and can further reduce switching loss for better conversion efficiency. The FB pin voltage versus  $t_{OFF-MIN}$  time characteristic curve is shown in Figure 40. As Figure 40 shows, FAN6920MR can narrow down to 2.25 ms  $t_{OFF}$  time, which is around 440 Hz switching frequency.

Referring to Figure 1 and Figure 2, FB pin voltage is not only used to receive secondary feedback signal to determine gate on-time, but also determines PFC stage operating mode.

Figure 40. V<sub>FB</sub> Voltage vs. t<sub>OFF-MIN</sub> Time Characteristic Curve

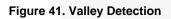

#### Valley Detection (DET Pin)

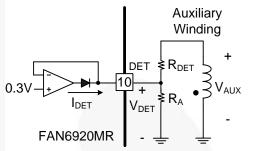

When FAN6920MR operates in Green Mode,  $t_{OFF-MIN}$  is determined by the Green Mode circuit, according to the FB pin voltage level. After  $t_{OFF-MIN}$ , the internal valley-detection circuit is activated. During  $t_{OFF}$  of the PWM switch, when transformer inductor current discharges to zero, the transformer inductor and parasitic capacitor of

PWM switch start to resonate concurrently. When the drain voltage on the PWM switch falls, the voltage across on auxiliary winding  $V_{AUX}$  also decreases since the auxiliary winding is coupled to the primary winding. Once the  $V_{AUX}$  voltage resonates and falls to negative,  $V_{DET}$  voltage is clamped by the DET pin (*refer to Figure 41*) and FAN6920MR is forced to flow out a current I<sub>DET</sub>. FAN6920MR reflects and compares this I<sub>DET</sub> current. If this source current rises to a threshold current, the PWM gate signal is sent out after a fixed delay time (200 ns typical).

Figure 42. Measured Waveform of Valley Detection

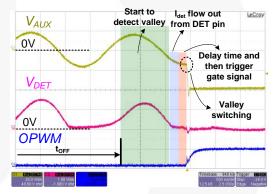

### High / Low Line Over-Power Compensation (DET Pin)

Generally, when the power switch turns off, there is a delay from gate signal falling edge to power switch off. This delay is produced by an internal propagation delay of the controller and the turn-off delay of the PWM switch due to gate resistor and gate-source capacitor CISS. At different AC input voltages, this delay produces different maximum output power with the same PWM current limit level. Higher input voltage generates higher maximum output power because applied voltage on primary winding is higher and causes higher rising slope inductor current. It results in higher peak inductor current at the same delay. Furthermore, under the same output wattage, the peak switching current at high line is lower than that at low line. Therefore, to make the maximum output power close at different input voltages, the controller needs to regulate VLIMIT voltage of the CSPWM pin to control the PWM switch current.

Referring to Figure 43, during  $t_{ON}$  of the PWM switch, the input voltage is applied to primary winding and the voltage across on auxiliary winding  $V_{AUX}$  is proportional to primary winding voltage. As the input voltage increases, the reflected voltage on auxiliary winding

$V_{\text{AUX}}$  becomes higher as well. FAN6920MR also clamps the DET pin voltage and flows out current  $I_{\text{DET}}$ . Since the current  $I_{\text{DET}}$  is in accordance with  $V_{\text{AUX}}$  voltage, FAN6920MR depends on this current during  $t_{\text{ON}}$  to regulate the current limit level of the PWM switch to perform high / low line over-power compensation.

As the input voltage increases, the reflected voltage on the auxiliary winding  $V_{\text{AUX}}$  becomes higher as well as the current  $I_{\text{DET}}$  and the controller regulates the  $V_{\text{LIMIT}}$  to a lower level.

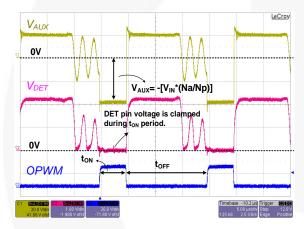

The R<sub>DET</sub> resistor is connected from auxiliary winding to the DET pin. Engineers can adjust this R<sub>DET</sub> resistor to get proper V<sub>LIMIT</sub> voltage to fit the specification of overpower or over-current protection. The characteristic curve of I<sub>DET</sub> current vs. V<sub>LIMIT</sub> voltage on CSPWM pin is shown in Figure 44.

$$I_{DET} = \left[ V_{IN} \times \left( N_A / N_P \right) \right] / R_{DET}$$

<sup>(1)</sup>

where  $V_{\text{IN}}$  is input voltage;  $N_{\text{A}}$  is turn number of auxiliary winding; and  $N_{\text{P}}$  is turn number of primary winding.

#### Figure 43. Relationship between VAUX and VIN

#### Leading-Edge Blanking (LEB)

When the PFC or PWM switches are turned on, a voltage spike is induced on the current-sense resistor due to the reciprocal effect by reverse-recovery energy of the output diode and  $C_{OSS}$  of power MOSFET. To prevent this spike, a leading-edge blanking time is built-in and a small RC filter (e.g. 100  $\Omega$ , 470 pF) is recommended between the CSPWM pin and GND.

#### Protection for PWM Stage

#### VDD Pin Over-Voltage Protection (OVP)

$V_{\text{DD}}$  over-voltage protection prevents device damage once  $V_{\text{DD}}$  voltage is higher than device stress rating voltage. In the case of  $V_{\text{DD}}$  OVP, the controller stops all switching operation immediately and enters autorecovery protection.

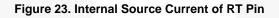

#### Adjustable Over-Temperature Protection and Externally Protection Triggering (RT Pin)

Figure 45 is a typical application circuit with an internal block of RT pin. As shown, a constant current  $I_{RT}$  flows out from the RT pin, so the voltage  $V_{RT}$  on the RT pin can be obtained as  $I_{RT}$  current multiplied by the resistor, which consists of NTC resistor and  $R_A$  resistor. If the RT pin voltage is lower than 0.8 V and lasts for a debounce time, auto-recovery protection is activated and stops all PFC and PWM switching.

RT pin is usually used to achieve over-temperature protection with a NTC resistor and provide external protection triggering for additional protection. Engineers can use an external triggering circuit (e.g. transistor) to pull the RT pin low and activate controller auto-recovery protection.

Generally, the external protection triggering needs to activate rapidly since it is usually used to protect the power system from abnormal conditions. Therefore, the protection debounce time of the RT pin is set to around 110  $\mu$ s once the RT pin voltage is lower than 0.5 V.

For over-temperature protection, because the temperature does not change immediately; the RT pin voltage is reduced slowly as well. The debounce time for adjustable OTP should not need a fast reaction. To prevent improper protection triggering on the RT pin due to exacting test condition (e.g. lightning test); when the RT pin triggering voltage is higher than 0.5 V, the protection debounce time is set to around 10 ms. To avoid improper triggering on the RT pin, add a small value capacitor (e.g. 1000 pF) paralleled with NTC and the  $R_A$  resistor.

Figure 45. Adjustable Over-Temperature Protection

#### Output Over-Voltage Protection (DET Pin)

Referring to Figure 46, during the discharge time of PWM transformer inductor; the voltage across on auxiliary winding is reflected from secondary winding and therefore the flat voltage on the DET pin is proportional to the output voltage. FAN6920MR can sample this flat voltage level after a  $t_{OFF}$  blanking time to perform output over-voltage protection. This  $t_{OFF}$  blanking time is used to ignore the voltage ringing from leakage inductance of PWM transformer. The sampling flat voltage level is compared with internal threshold voltage 2.5 V and, once the protection.

The controller can protect rapidly by this kind of cycleby-cycle sampling method in the case of output over voltage. The protection voltage level can be determined by the ratio of external resistor divider  $R_A$  and  $R_{DET}$ . The flat voltage on DET pin can be expressed by the following equation:

$$V_{DET} = \left(N_A / N_S\right) \times V_O \times \frac{R_A}{R_{DET} + R_A}$$

(2)

PWM Gate  $V_o$  · V<sub>AUX</sub>  $PFC_V_o$ N<sub>P</sub> R Sampling  $R_{DET} + R$  $V_{DE}$ Here t<sub>OFF</sub> Blanking 0.3V Figure 46. Operation Waveform of Output **Over-Voltage Detection**

Open-Loop, Short-Circuit, and Overload Protection (FB Pin)

#### Figure 47. FB Pin Open-Loop, Short Circuit, and Overload Protection

Referring to Figure 47; outside of FAN6920MR, the FB pin is connected to the collector of transistor of an optocoupler. Inside, the FB pin is connected to an internal voltage bias through a resistor of around 5 k $\Omega$ .