19-1054; Rev 0; 1/08

EVALUATION KIT AVAILABLE

## Programmable Switch-Mode LED Driver with Analog-Controlled PWM Dimming

### **General Description**

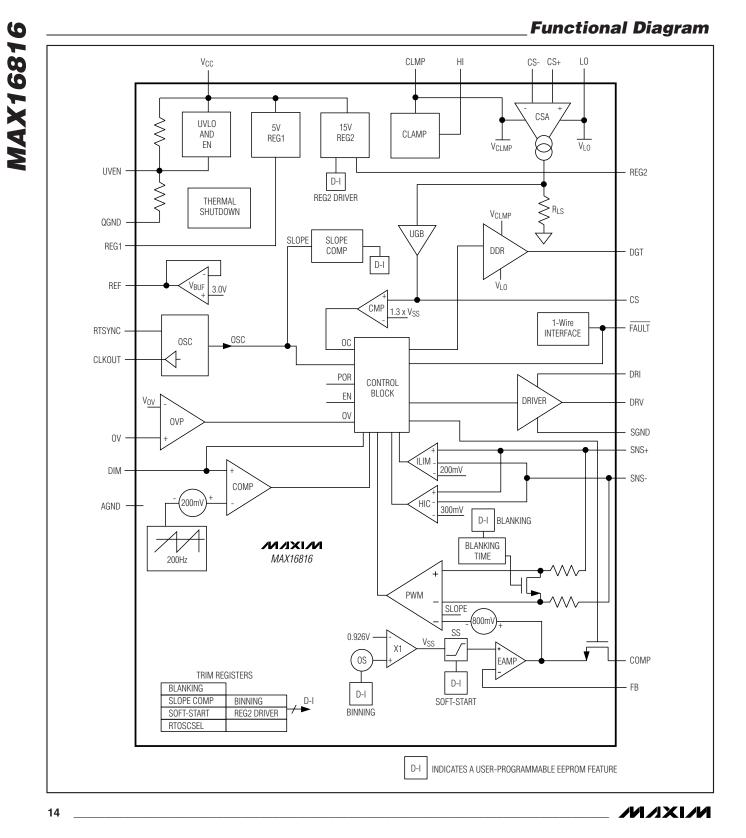

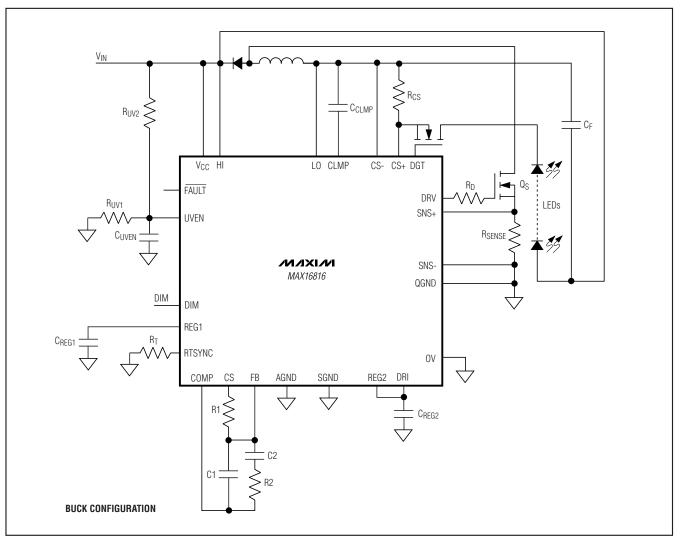

The MAX16816 is a current-mode, high-brightness LED (HB LED) driver designed to control two external n-channel MOSFETs for single-string LED current regulation. The MAX16816 integrates all the building blocks necessary to implement fixed-frequency HB LED drivers with wide-range dimming control and EEPROM-programmable LED current binning with a factor of up to 1.6. This device is configurable to operate as a step-down (buck), step-up (boost), or step-up/step-down (buck-boost) current regulator.

Current-mode control with adjustable leading-edge blanking simplifies control-loop design. Adjustable slope compensation stabilizes the current loop when operating at duty cycles above 50%. The MAX16816 operates over a wide input voltage range and is capable of withstanding automotive load-dump events. Multiple MAX16816 devices can be synchronized to each other or to an external clock. The MAX16816 includes a floating dimming driver for brightness control with an external n-channel MOSFET in series with the LED string.

HB LEDs using the MAX16816 can achieve efficiencies of over 90% in automotive applications. The MAX16816 also includes a 1.4A source and 2A sink gate driver for driving switching MOSFETs in high-power LED driver applications, such as front light assemblies. Dimming control allows for wide PWM dimming range at frequencies up to 5kHz. Higher dimming ratios (up to 1000:1) are achievable at lower dimming frequencies.

The MAX16816 provides user-programmable features through on-chip nonvolatile EEPROM registers. Adjustable features include a programmable soft-start, LED current (binning), external MOSFET gate driver supply voltage, slope compensation, leading-edge blanking time, and disabling/enabling of the RT oscillator.

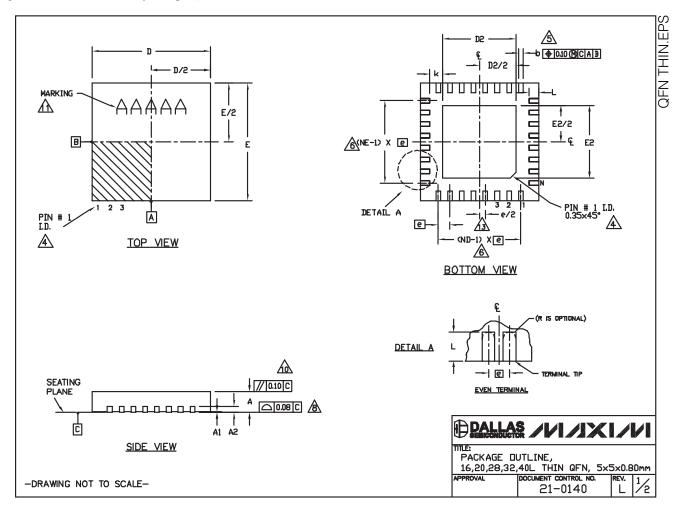

The MAX16816 is available in a 32-pin TQFN package with exposed pad and operates over the -40°C to  $+125^{\circ}$ C automotive temperature range.

### **Applications**

Automotive Exterior: Rear Combination Lights (RCL), Daytime Running Lights (DRL), Fog and Front Lighting, High-Beam/Low-Beam/Turn Lights

General Illumination

Navigation and Marine Indicators

Neon Replacement, Emergency Lighting Signage and Beacons

### \_Features

- ♦ EEPROM-Programmable LED Current Binning

- ♦ Wide Input Range: 5.9V to 76V with Cold Start Operation to 5.4V

- Integrated Floating Differential LED Current-Sense Amplifier

- Floating Dimming Driver Capable of Driving an n-Channel MOSFET

- 5% or Better LED Current Accuracy

- Multiple Topologies: Buck, Boost, Buck-Boost, SEPIC

- Resistor-Programmable Switching Frequency (125kHz to 500kHz) and Synchronization Capability

- 200Hz On-Board Ramp Allows Analog-Controlled PWM Dimming and External PWM Dimming

- Output Overvoltage, Overcurrent, and LED Short Protection

- ♦ Enable/Shutdown Input with Shutdown Current Below 45µA

### **Ordering Information**

|   | PART         | TEMP RANGE      | PIN-<br>PACKAGE | PKG<br>CODE |

|---|--------------|-----------------|-----------------|-------------|

| N | IAX16816ATJ+ | -40°C to +125°C | 32 TQFN-EP*     | T3255M-4    |

+Denotes a lead-free package.

\*EP = Exposed pad.

Pin Configuration appears at end of data sheet.

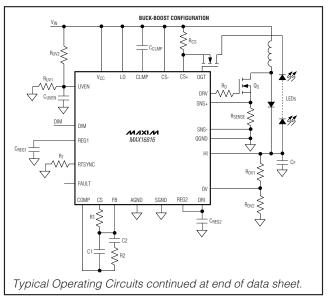

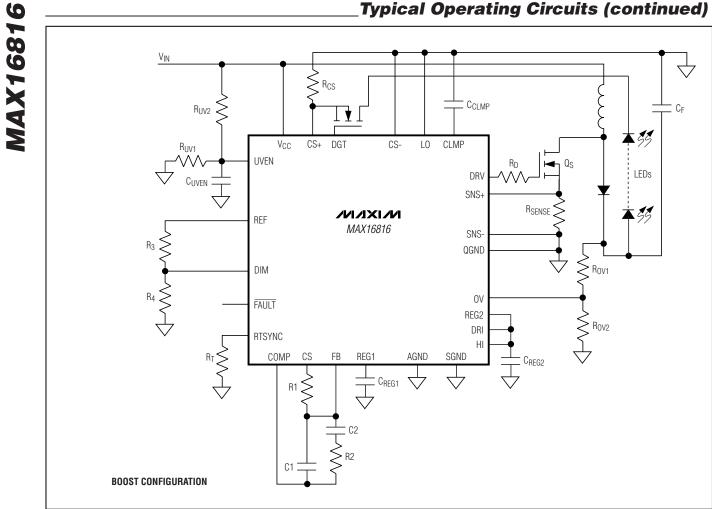

### \_Typical Operating Circuits

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> , HI, LO, CLMP to QGND<br>CS+, CS-, DGT, UVEN, FAULT to QGND |                                   |

|------------------------------------------------------------------------------|-----------------------------------|

| UVEN to QGND                                                                 | -0.3V to (V <sub>CC</sub> + 0.3V) |

| DRV to SGND                                                                  | 0.3V to +18V                      |

| DRI, REG2, DIM to AGND                                                       | 0.3V to +18V                      |

| QGND, SGND to AGND                                                           | 0.3V to +0.3V                     |

| SNS+ to SNS                                                                  | 0.3V to +6V                       |

| CS, FB, COMP, SNS+, SNS-, OV, REF,                                           |                                   |

| RTSYNC to AGND                                                               | 0.3V to +6V                       |

| REG1, CLKOUT to AGND                                                         | 0.3V to +6V                       |

| CS+ to CS                                                                    | 0.3V to +12V                      |

| HI to LO                                                                     | 0.3V to +36V                      |

| CS+, CS-, DGT, CLMP to LO                                                    | 0.3V to +12V                      |

| CS+, CS-, DGT, CLMP to LO0.3V to (HI + 0.3V)<br>HI to CLMP0.3V to +28V |  |

|------------------------------------------------------------------------|--|

| Continuous Power Dissipation* ( $T_A = +70^{\circ}C$ )                 |  |

| 32-Pin TQFN (derate 34.5mW/°C above +70°C)2758mW                       |  |

| Thermal Resistance                                                     |  |

| θJA                                                                    |  |

| θ.JC1.7°C/W                                                            |  |

| Operating Temperature Range40°C to +125°C                              |  |

| Maximum Junction Temperature+150°C                                     |  |

| Storage Temperature Range60°C to +150°C                                |  |

| Lead Temperature (soldering, 10s)+300°C                                |  |

|                                                                        |  |

|                                                                        |  |

\*As per JEDEC 51 standard, Multilayer Board (PCB).

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = V_{UVEN} = 14V, C_{REG1} = 1\mu F, C_{REG2} = 1\mu F, C_{CLMP} = 0.1\mu F, R_T = 25k\Omega, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical specifications are at T<sub>A</sub> = +25°C.)

| PARAMETER                            | SYMBOL                | CONDITIONS                                                                            | MIN  | ТҮР   | MAX  | UNITS |

|--------------------------------------|-----------------------|---------------------------------------------------------------------------------------|------|-------|------|-------|

| Input Voltage Range                  | V <sub>CC</sub>       |                                                                                       | 5.5  |       | 76   | V     |

| Supply Current to V <sub>CC</sub>    | IQ_VCC                | Exclude current to the gate driver, IREG2                                             |      | 2.7   | 4.5  | mA    |

| Supply Current to HI                 | I <sub>Q_HI</sub>     | $V_{HI} = 14V$                                                                        |      | 0.5   | 1.0  | mA    |

| Shutdown Current to V <sub>CC</sub>  | ISHDN_VCC             | V <sub>UVEN</sub> ≤ 300mV                                                             |      | 25    | 45   | μA    |

| Shutdown Current to HI               | ISHDN_HI              | V <sub>UVEN</sub> ≤ 300mV                                                             |      | 1     | 10   | μA    |

| UVEN                                 |                       |                                                                                       |      |       |      |       |

|                                      | VCC_R                 | V <sub>CC</sub> rising                                                                | 5.5  |       | 6.0  | V     |

| V <sub>CC</sub> UVLO Threshold       | V <sub>CC_F</sub>     | V <sub>CC</sub> falling                                                               | 5.0  |       | 5.5  | V     |

| V <sub>CC</sub> Threshold Hysteresis | VCC_HYS               |                                                                                       |      | 0.4   |      | V     |

| UVEN Threshold                       | Vuvr                  | V <sub>UVEN</sub> rising                                                              | 1.10 | 1.244 | 1.36 | V     |

|                                      | VUVF                  | V <sub>UVEN</sub> falling                                                             | 1.00 | 1.145 | 1.26 |       |

| UVEN Input Current                   | IUVEN                 | $(V_{UVEN} = 0V \text{ and } V_{CC} = 14V) (V_{UVEN} = 76V)$<br>and $V_{CC} = 77V)$   | -0.2 |       | +0.2 | μA    |

| REGULATORS                           | ·                     |                                                                                       |      |       |      |       |

|                                      |                       | 0 < I <sub>REG1</sub> < 2mA, 7.5V < V <sub>CC</sub> < 76V                             | 4.75 | 5.00  | 5.25 | V     |

| REG1 Regulator Output                | VREG1                 | $I_{REG1} = 2mA, V_{CC} = 5.7V$                                                       | 4.00 | 4.50  | 5.25 | V     |

| REG1 Dropout Voltage                 |                       | I <sub>REG1</sub> = 2mA (Note 1)                                                      |      | 0.5   | 1.0  | V     |

| REG1 Load Regulation                 | $\Delta V / \Delta I$ | $V_{CC} = 7.5V$ , $I_{REG1} = 0$ to 2mA                                               |      |       | 25   | Ω     |

| REG2 Dropout Voltage                 |                       | $V_{CC} \ge 9.5V$ , REG2 control register is '0011',<br>IREG2 = 20mA (Note 1)         |      | 0.5   | 1.0  | V     |

| REG2 Load Regulation                 | ΔV/ΔΙ                 | $V_{CC} \ge 9.5V$ , REG2 control register is '0011',<br>I <sub>REG2</sub> = 0 to 20mA |      |       | 25   | Ω     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = V_{UVEN} = 14V, C_{REG1} = 1\mu F, C_{REG2} = 1\mu F, C_{CLMP} = 0.1\mu F, R_T = 25k\Omega, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical specifications are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                           | SYMBOL                              | CONDITIONS                                                                                | MIN                                           | ТҮР  | МАХ             | UNITS |

|-------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------|------|-----------------|-------|

|                                     |                                     | REG2 control register is '0000',<br>V <sub>CC</sub> $\ge$ 7.5V, I <sub>REG2</sub> = 1mA   | 4.75                                          | 5    | 5.25            |       |

|                                     |                                     | REG2 control register is '0011',<br>V <sub>CC</sub> $\ge$ 9.5V, I <sub>REG2</sub> = 1mA   | 6.65                                          | 7.0  | 7.35            |       |

|                                     |                                     | REG2 control register is '1111',<br>V <sub>CC</sub> $\geq$ 17.5V, I <sub>REG2</sub> = 1mA | 13.5                                          | 15   | 16.5            | N/    |

| REG2 Regulation Voltage             |                                     | REG2 control register is '0000',<br>V <sub>CC</sub> = 5.7V, $0 \le I_{REG2} \le 20mA$     | 4                                             | 4.5  | 5.25            | V     |

|                                     |                                     | REG2 control register is '0000',<br>V <sub>CC</sub> = 7.5V, $0 \le I_{REG2} \le 20mA$     | 4.75                                          | 5    | 5.25            |       |

|                                     |                                     | REG2 control register is '1111',<br>V <sub>CC</sub> = 17.5V, $0 \le I_{REG2} \le 20$ mA   | 13.5                                          | 15   | 16.5            |       |

| HIGH-SIDE REGULATOR (C              | LMP) (All voltag                    | es referred to V <sub>LO</sub> ) (Note 2)                                                 | •                                             |      |                 |       |

| CLMP UVLO Threshold                 | VCLMP_TH                            | V <sub>CLMP</sub> rising                                                                  | 2.0                                           | 2.5  | 3.0             | V     |

| CLMP UVLO Threshold<br>Hysteresis   | VCLMP_HYS                           |                                                                                           |                                               | 0.22 |                 | V     |

|                                     |                                     | $8.7V \le (V_{HI} - V_{LO}) \le 36V, I_{CLMP} = 1mA$                                      | 5.5                                           | 8.0  | 10.0            |       |

| CLMP Regulator Output<br>Voltage    | VCLMP                               | $5.0V \le (V_{HI} - V_{LO}) \le 8.7V, I_{CLMP} = 250\mu A$                                | (V <sub>HI</sub> - V <sub>LO</sub> )<br>- 0.7 |      | V               |       |

| CURRENT-SENSE AMPLIFI               | ER (CSA)                            | •                                                                                         |                                               |      |                 |       |

| Differential Input Voltage<br>Range | V <sub>CS+</sub> - V <sub>CS-</sub> |                                                                                           | 0                                             |      | 0.3             | V     |

| Common-Mode Range                   |                                     | $V_{CC} \le 68V$                                                                          | 0                                             |      | V <sub>CC</sub> | V     |

| CS+ Input Bias Current              | I <sub>CS+</sub>                    | $V_{CS+} = 0.3V, V_{CS-} = 0V$                                                            | -250                                          |      | +250            | nA    |

| CS- Input Bias Current              | I <sub>CS-</sub>                    | $V_{CS+} = 0.3V, V_{CS-} = 0V$                                                            |                                               |      | 400             | μA    |

| Unity-Gain Bandwidth                |                                     | From (CS+ to CS-) to CS                                                                   |                                               | 1.0  |                 | MHz   |

| REF OUTPUT BUFFER                   |                                     |                                                                                           |                                               |      |                 |       |

| REF Output Voltage                  | VREF                                | $-100\mu A \le I_L \le +100\mu A$                                                         | 2.85                                          | 3.0  | 3.15            | V     |

| DIM DRIVER                          |                                     |                                                                                           |                                               |      |                 |       |

| Minimal Pulse Width                 |                                     | f <sub>DIM</sub> = 200Hz (Note 3)                                                         |                                               | 20   | 40              | μs    |

| Source Current                      |                                     | $V_{CLMP} - V_{LO} = 4V$                                                                  | 5                                             | 20   |                 | mA    |

|                                     |                                     | $V_{CLMP} - V_{LO} = 8V$                                                                  | 30                                            | 67   |                 | 110.0 |

| Sink Current                        |                                     | $V_{CLMP} - V_{LO} = 4V$                                                                  | 10                                            | 22   |                 | mA    |

|                                     |                                     | $V_{CLMP} - V_{LO} = 8V$                                                                  | 40                                            | 76   |                 |       |

| GATE DRIVER                         |                                     |                                                                                           |                                               |      |                 | 1     |

| DRI Voltage Range                   | VDRI                                | V <sub>CC</sub> ≥ 2.5V above V <sub>DRI</sub>                                             | 5                                             |      | 15              | V     |

| DRI UVLO Threshold                  | VUVLO_TH                            |                                                                                           | 4.0                                           | 4.2  | 4.4             | V     |

| DRI UVLO Threshold<br>Hysteresis    | VUVLO_HYST                          |                                                                                           |                                               | 0.3  |                 | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = V_{UVEN} = 14V, C_{REG1} = 1\mu F, C_{REG2} = 1\mu F, C_{CLMP} = 0.1\mu F, R_T = 25k\Omega, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical specifications are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                                                          | SYMBOL             | CONDITIONS                                                  | MIN  | ТҮР | MAX  | UNITS |

|------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------|------|-----|------|-------|

|                                                                                    | Z <sub>OUT_L</sub> | V <sub>DRI</sub> = 7.0V, DRV sinking 250mA                  |      | 2.8 | 4    | 0     |

| Driver Output Impedance                                                            | Zout_h             | V <sub>DRI</sub> = 7.0V, DRV sourcing 250mA                 |      | 5.0 | 8    | Ω     |

| Peak Sink Current                                                                  | I <sub>SK</sub>    | $V_{DRI} = 7.0V$                                            |      | 2.5 |      | А     |

| Peak Source Current                                                                | ISR                | $V_{DRI} = 7.0V$                                            |      | 1.4 |      | А     |

| PWM, ILIM, AND HICCUP COM                                                          | IPARATOR           |                                                             |      |     |      |       |

| PWM Comparator Offset<br>Voltage                                                   |                    | VCOMP - (VSNS+ -VSNS-)                                      |      | 0.8 |      | V     |

| Peak Current-Limit<br>Comparator Trip Threshold                                    |                    |                                                             | 160  | 200 | 245  | mV    |

| Peak Current-Limit<br>Comparator Propagation<br>Delay (Excluding Blanking<br>Time) |                    | 50mV overdrive                                              |      | 40  |      | ns    |

| HICCUP Comparator Trip<br>Threshold                                                |                    |                                                             | 235  | 300 | 385  | mV    |

| SNS+ Input Bias Current                                                            |                    | $V_{SNS+} = 0V, V_{SNS-} = 0V$                              | -100 | -65 |      | μA    |

| SNS- Input Bias Current                                                            |                    | $V_{SNS+} = 0V, V_{SNS-} = 0V$                              | -100 | -65 |      | μA    |

| BLANKING TIME                                                                      |                    |                                                             |      |     |      |       |

|                                                                                    |                    | Blanking Time Control Register is '00'                      |      | 150 |      |       |

| Dia akia a Tina a                                                                  |                    | Blanking Time Control Register is '01'                      |      | 125 |      |       |

| Blanking Time                                                                      |                    | Blanking Time Control Register is '10'                      |      | 100 |      | ns    |

|                                                                                    |                    | Blanking Time Control Register is '11'                      |      | 75  |      |       |

| ERROR AMPLIFIER                                                                    |                    | ·                                                           |      |     |      |       |

| FB Input Bias Current                                                              |                    | $V_{FB} = 1V$                                               | -100 |     | +100 | nA    |

| EAMP Output Sink Current                                                           |                    | V <sub>FB</sub> = 1.735V, V <sub>COMP</sub> = 1V            | 3    | 7   |      | mA    |

| EAMP Output Source Current                                                         |                    | V <sub>FB</sub> = 0.735V, V <sub>COMP</sub> = 1V            | 2    | 7   |      | mA    |

| EAMP Input Common-Mode<br>Voltage                                                  | V <sub>COM</sub>   | (Note 5)                                                    | 0    |     | 1.6  | V     |

| EAMP Output Clamp Voltage                                                          |                    |                                                             | 1.3  | 2.0 | 2.7  | V     |

| Voltage Gain                                                                       | Av                 | $R_{COMP} = 100k\Omega$ to AGND                             |      | 80  |      | dB    |

| Unity-Gain Bandwidth                                                               | GBW                | $R_{COMP} = 100k\Omega$ to AGND, $C_{COMP} = 100pF$ to AGND |      | 0.5 |      | MHz   |

| OSCILLATOR, OSC SYNC, CL                                                           | K, AND CLKO        | тис                                                         |      |     |      |       |

|                                                                                    | fsw_MIN            |                                                             |      |     | 125  |       |

| SYNC Frequency Range                                                               | fsw_max            |                                                             | 500  |     |      | kHz   |

|                                                                                    |                    | RTOF bit set to '0', $R_T = 100k\Omega$                     | 106  | 125 | 143  | kHz   |

| RTSYNC Oscillator Frequency                                                        |                    | RTOF bit set to '0', $R_T = 25k\Omega$                      | 475  | 500 | 525  |       |

| SYNC High-Level Voltage                                                            | VSIHL              |                                                             | 2.8  |     |      | V     |

| SYNC Low-Level Voltage                                                             | VSILL              |                                                             | 1    |     | 0.4  | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = V_{UVEN} = 14V, C_{REG1} = 1\mu F, C_{REG2} = 1\mu F, C_{CLMP} = 0.1\mu F, R_T = 25k\Omega, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical specifications are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                | SYMBOL               | CONDITIONS                                    | MIN  | TYP    | MAX  | UNITS |

|------------------------------------------|----------------------|-----------------------------------------------|------|--------|------|-------|

| CLKOUT High Level                        |                      | I <sub>SINK</sub> = 0.8mA                     | 2.8  |        |      | V     |

| CLKOUT Low Level                         |                      | ISOURCE = 1.6mA                               |      |        | 0.4  | V     |

| CLKOUT Maximum Load<br>Capacitance       | Cclk_cap             | f <sub>SW</sub> = 500kHz                      |      |        | 500  | pF    |

| DIM SYNC, DIM RAMP, AND D                | IM PWM GEN           | I                                             |      |        |      |       |

| Internal RAMP Frequency                  | <b>f</b> RAMP        |                                               | 160  | 200    | 240  | Hz    |

| External Sync Frequency<br>Range         | fdim                 |                                               | 80   |        | 2000 | Hz    |

| External Sync Low-Level<br>Voltage       | VLTH                 |                                               |      |        | 0.4  | V     |

| External Sync High-Level<br>Voltage      | V <sub>HTH</sub>     |                                               | 3.2  |        |      | V     |

| DIM Comparator Offset                    | VDIMOS               |                                               | 170  | 200    | 300  | mV    |

| DIGITAL SOFT-START AND B                 |                      | •                                             | •    |        |      | •     |

|                                          |                      | Digital Soft-Start Duration register is '000' |      | 4096   |      |       |

|                                          |                      | Digital Soft-Start Duration register is '001' |      | 2048   |      |       |

|                                          |                      | Digital Soft-Start Duration register is '010' |      | 1536   |      |       |

| Soft-Start Duration                      | tss                  | Digital Soft-Start Duration register is '011' |      | 1024   |      |       |

| Solt-Start Duration                      |                      | Digital Soft-Start Duration register is '100' | 768  |        |      | μs    |

|                                          |                      | Digital Soft-Start Duration register is '101' |      | 512    |      |       |

|                                          |                      | Digital Soft-Start Duration register is '110' |      | 256    |      |       |

|                                          |                      | Digital Soft-Start Duration register is '111' |      | 0      |      |       |

|                                          |                      | Binning Adjustment register is '0000'         |      | 100.00 |      |       |

|                                          |                      | Binning Adjustment register is '0001'         |      | 106.67 |      |       |

|                                          |                      | Binning Adjustment register is '0010'         |      | 113.33 |      |       |

|                                          |                      | Binning Adjustment register is '0011'         |      | 120.00 |      |       |

|                                          |                      | Binning Adjustment register is '0100'         |      | 126.67 |      |       |

| Binning Range                            |                      | Binning Adjustment register is '0101'         |      | 133.33 |      | mV    |

|                                          |                      | Binning Adjustment register is '0110'         |      | 140.00 |      |       |

|                                          |                      | Binning Adjustment register is '0111'         |      | 146.67 |      |       |

|                                          |                      | Binning Adjustment register is '1000'         |      | 153.33 |      |       |

|                                          |                      | Binning Adjustment register is '1001'         |      | 160.00 |      |       |

|                                          |                      | Binning Adjustment register is '1010'         |      | 166.67 |      |       |

| OVERVOLTAGE COMPARATO                    | OR, LOAD OV          | ERCURRENT COMPARATOR                          |      |        |      | ·     |

| OVP Overvoltage Comparator<br>Threshold  | V <sub>OV</sub>      | V <sub>OV</sub> rising                        | 1.20 | 1.235  | 1.27 | V     |

| OVP Overvoltage Comparator<br>Hysteresis | V <sub>OV_HYST</sub> |                                               |      | 63.5   |      | mV    |

5

MAX16816

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = V_{UVEN} = 14V, C_{REG1} = 1\mu F, C_{REG2} = 1\mu F, C_{CLMP} = 0.1\mu F, R_T = 25k\Omega, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical specifications are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                   | SYMBOL | CONDITIONS                                                            | MIN | ТҮР                                                               | МАХ | UNITS |  |  |  |

|-----------------------------|--------|-----------------------------------------------------------------------|-----|-------------------------------------------------------------------|-----|-------|--|--|--|

| SLOPE COMPENSATION          |        | •                                                                     |     |                                                                   |     |       |  |  |  |

|                             |        | Slope Compensation register is '0000', clock generated by $R_{T}$     |     | 0                                                                 |     |       |  |  |  |

|                             |        |                                                                       |     | Slope Compensation register is '0001', clock generated by $R_{T}$ |     | 20    |  |  |  |

|                             |        | Slope Compensation register is '0010', clock generated by $R_{T}$     |     | 40                                                                |     |       |  |  |  |

|                             |        | Slope Compensation register is '0011', clock generated by $R_T$       |     | 60                                                                |     |       |  |  |  |

|                             |        | Slope Compensation register is '0100', clock generated by $R_T$       |     | 80                                                                |     |       |  |  |  |

|                             |        | Slope Compensation register is '0101', clock generated by $R_{\rm T}$ |     | 100                                                               |     |       |  |  |  |

|                             |        | Slope Compensation register is '0110', clock generated by $R_T$       |     | 120                                                               |     |       |  |  |  |

| Slope Compensation Peak-to- |        | Slope Compensation register is '0111', clock generated by $R_{T}$     |     | 140                                                               |     | mV/   |  |  |  |

| Peak Voltage Per Cycle      |        | Slope Compensation register is '1000', clock generated by $R_T$       |     | 160                                                               |     | cycle |  |  |  |

|                             |        | Slope Compensation register is '1001', clock generated by $R_T$       |     | 180                                                               |     |       |  |  |  |

|                             |        | Slope Compensation register is '1010', clock generated by $R_T$       |     | 200                                                               |     |       |  |  |  |

|                             |        | Slope Compensation register is '1011', clock generated by $R_T$       |     | 220                                                               |     |       |  |  |  |

|                             |        | Slope Compensation register is '1100', clock generated by $R_T$       |     | 240                                                               |     |       |  |  |  |

|                             |        | Slope Compensation register is '1101', clock generated by $R_T$       |     | 260                                                               |     |       |  |  |  |

|                             |        | Slope Compensation register is '1110', clock generated by $R_{\rm T}$ |     | 280                                                               |     |       |  |  |  |

|                             |        | Slope Compensation register is '1111', clock generated by $R_{\rm T}$ |     | 300                                                               |     |       |  |  |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = V_{UVEN} = 14V, C_{REG1} = 1\mu F, C_{REG2} = 1\mu F, C_{CLMP} = 0.1\mu F, R_T = 25k\Omega, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical specifications are at T<sub>A</sub> = +25°C.)

| PARAMETER          | SYMBOL | CONDITIONS                                                                 | MIN | ТҮР | МАХ | UNITS   |

|--------------------|--------|----------------------------------------------------------------------------|-----|-----|-----|---------|

|                    |        | Slope Compensation register is '0000',<br>external clock applied to RTSYNC |     | 0   |     |         |

|                    |        | Slope Compensation register is '0001',<br>external clock applied to RTSYNC |     | 2   |     |         |

|                    |        | Slope Compensation register is '0010',<br>external clock applied to RTSYNC |     | 4   |     |         |

|                    |        | Slope Compensation register is '0011', external clock applied to RTSYNC    |     | 6   |     |         |

|                    |        | Slope Compensation register is '0100',<br>external clock applied to RTSYNC |     | 8   |     |         |

|                    |        | Slope Compensation register is '0101', external clock applied to RTSYNC    |     | 10  |     |         |

|                    |        | Slope Compensation register is '0110',<br>external clock applied to RTSYNC |     | 12  |     | – mV/µs |

|                    |        | Slope Compensation register is '0111', external clock applied to RTSYNC    |     | 14  |     |         |

| Slope Compensation |        | Slope Compensation register is '1000',<br>external clock applied to RTSYNC |     | 16  |     |         |

|                    |        | Slope Compensation register is '1001',<br>external clock applied to RTSYNC |     | 18  |     |         |

|                    |        | Slope Compensation register is '1010',<br>external clock applied to RTSYNC |     | 20  |     |         |

|                    |        | Slope Compensation register is '1011',<br>external clock applied to RTSYNC |     | 22  |     |         |

|                    |        | Slope Compensation register is '1100',<br>external clock applied to RTSYNC |     | 24  |     |         |

|                    |        | Slope Compensation register is '1101',<br>external clock applied to RTSYNC |     | 26  |     |         |

|                    |        | Slope Compensation register is '1110',<br>external clock applied to RTSYNC |     | 28  |     |         |

|                    |        | Slope Compensation register is '1111',<br>external clock applied to RTSYNC |     | 30  |     |         |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = V_{UVEN} = 14V, C_{REG1} = 1\mu F, C_{REG2} = 1\mu F, C_{CLMP} = 0.1\mu F, R_T = 25k\Omega, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical specifications are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                         | SYMBOL              | CONDITIONS                                       | MIN | ТҮР  | MAX | UNITS  |

|-----------------------------------|---------------------|--------------------------------------------------|-----|------|-----|--------|

| FAULT I/O                         |                     |                                                  |     |      |     |        |

| FAULT Leakage Current             |                     | $5.5V < V_{FAULT} < 76V$                         | -1  |      | +1  | μΑ     |

| FAULT Input Low Current           |                     | $V_{FAULT} = 0V$                                 |     | 500  |     | μΑ     |

| FAULT Pulldown Current            |                     | $V_{FAULT} = 2V$                                 | 0.7 | 1.2  | 1.8 | mA     |

| FAULT Pulldown Input<br>Logic-Low | VIL                 |                                                  |     |      | 0.4 | V      |

| FAULT Output Logic-High           |                     | Sourcing 10µA                                    | 2.8 |      |     | V      |

| FAULT Output Logic-Low            |                     | Sinking 10µA                                     |     |      | 0.4 | V      |

| Programming Slot at Power-Up      |                     | $V_{UVEN} > 1.244V$ and $V_{CC} > 5.9V$ (Note 4) | 6.4 | 8.0  |     | ms     |

| THERMAL SHUTDOWN                  |                     |                                                  |     |      |     | -      |

| Thermal Shutdown<br>Temperature   | TJ_SHDN             |                                                  |     | +165 |     | °C     |

| Thermal Shutdown Hysteresis       | $\Delta T_{J_SHDN}$ |                                                  |     | 20   |     | °C     |

| EEPROM                            |                     |                                                  |     |      |     |        |

| Data Retention                    | tDR                 | $T_{A} = +125^{\circ}C$ (Note 5)                 | 10  |      |     | years  |

| EEPROM Write Time                 | twra                | (Note 5)                                         |     |      | 14  | ms     |

| Endurance                         |                     | $T_A = +85^{\circ}C$ , read and write (Note 5)   | 50k |      |     | cycles |

### ELECTRICAL CHARACTERISTICS – 1-Wire<sup>®</sup> System

$(C_{REG1} = 1\mu F, C_{REG2} = 1\mu F, T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical specifications are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                   | SYMBOL           | CONDITIONS | MIN | ТҮР | MAX | UNITS |

|-----------------------------|------------------|------------|-----|-----|-----|-------|

| I/O GENERAL DATA            |                  |            | ·   |     |     |       |

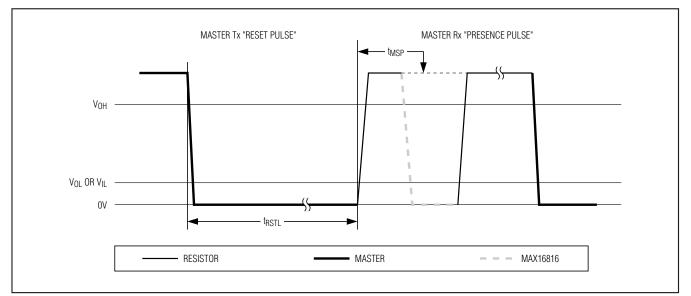

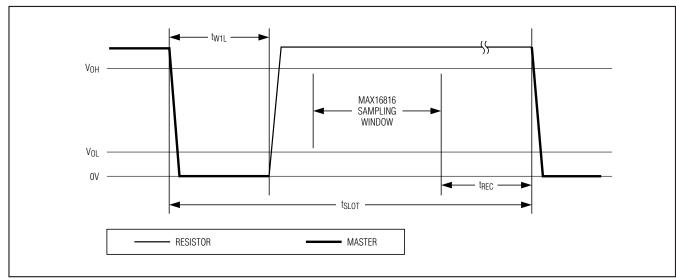

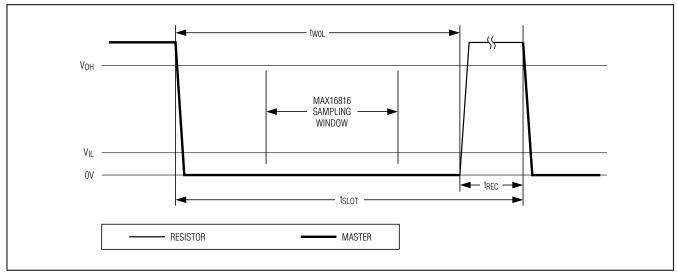

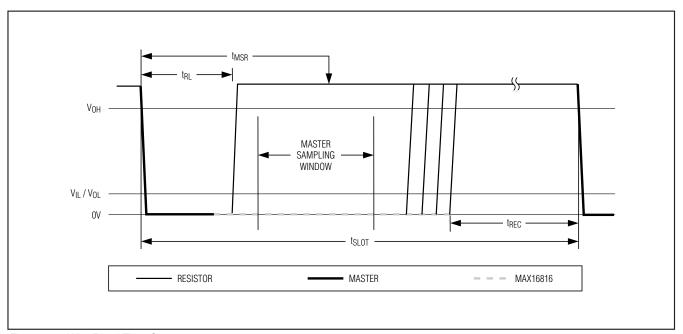

| 1-Wire Time Slot Duration   | <b>t</b> SLOT    |            | 65  |     |     | μs    |

| Recovery Time               | t <sub>REC</sub> | (Note 6)   | 5   |     |     | μs    |

| I/O, 1-Wire RESET, PRESENCI | E DETECT CY      | CLE        |     |     |     |       |

| Reset Low Time              | <b>t</b> RSTL    |            | 480 |     | 640 | μs    |

| Presence Detect Sample Time | tMSP             |            | 65  |     | 75  | μs    |

| I/O, 1-Wire WRITE           |                  |            |     |     |     |       |

| Write-0 Low Time            | t <sub>WOL</sub> |            | 60  |     |     | μs    |

| Write-1 Low Time            | tw1L             |            | 5   |     | 15  | μs    |

| I/O, 1-Wire READ            |                  |            |     |     |     |       |

| Read Low Time               | t <sub>RL</sub>  |            | 5   |     | 10  | μs    |

| Read Sample Time            | t <sub>MSR</sub> |            | 12  |     | 15  | μs    |

|                             |                  |            |     |     |     |       |

1-Wire is a registered trademark of Dallas Semiconductor Corp., a wholly owned subsidiary of Maxim Integrated Products, Inc.

M/IXI/N

### **ELECTRICAL CHARACTERISTICS**

- Note 1: Dropout voltage is defined as the input to output differential voltage at which the output voltage drops 100mV below its nominal value measured at output.

- Note 2: V<sub>CLMP\_TH</sub> determines the voltage necessary to operate the current-sense amplifier. The DIM driver requires 2.5V for (V<sub>CLMP</sub> V<sub>LO</sub>) to drive a FET. V<sub>HI</sub> is typically one diode drop above V<sub>CLMP</sub>. A large capacitor connected to V<sub>CLMP</sub> slows the response of the LED current-sense circuitry, resulting in current overshoot. To ensure proper operation, connect a 0.1µF capacitor from CLMP to LO.

- Note 3: Minimum pulse width required to guarantee proper dimming operation.

- **Note 4:** FAULT multiplexes a programming interface and fault indication functionality. At power-up initialization, an internal timer enables FAULT and two programming passcodes must be entered within the programming slot to enter programming mode. If the programming passcodes are not received correctly within the programming slot, FAULT goes back towards fault indication. Cycling power to the device is required to re-attempt entry into programming mode.

- Note 5: Not production tested. Guaranteed by design.

- **Note 6:** Recovery time is the time required for  $\overline{FAULT}$  to be pulled high by the internal 10k $\Omega$  resistor.

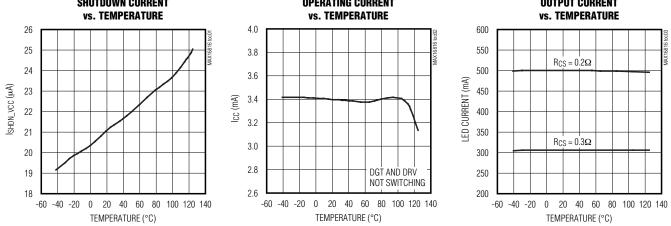

### **Typical Operating Characteristics**

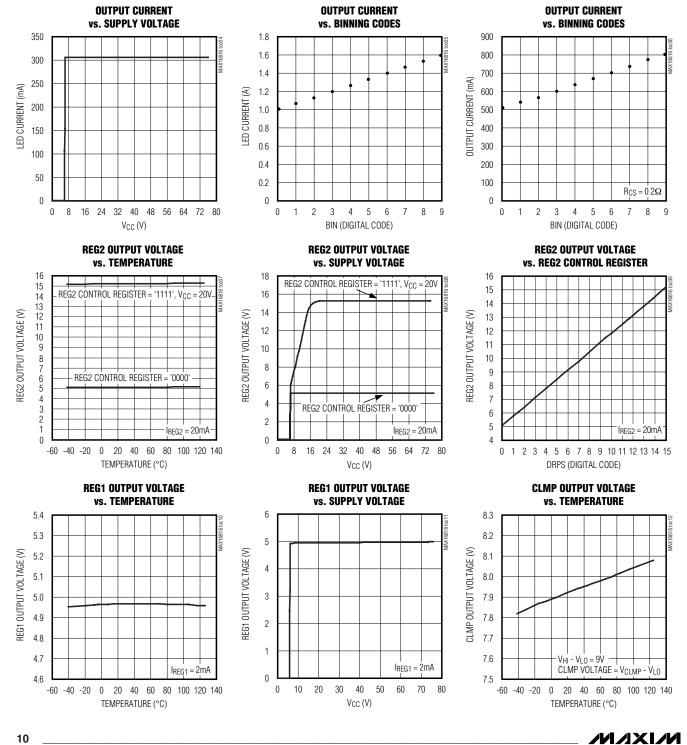

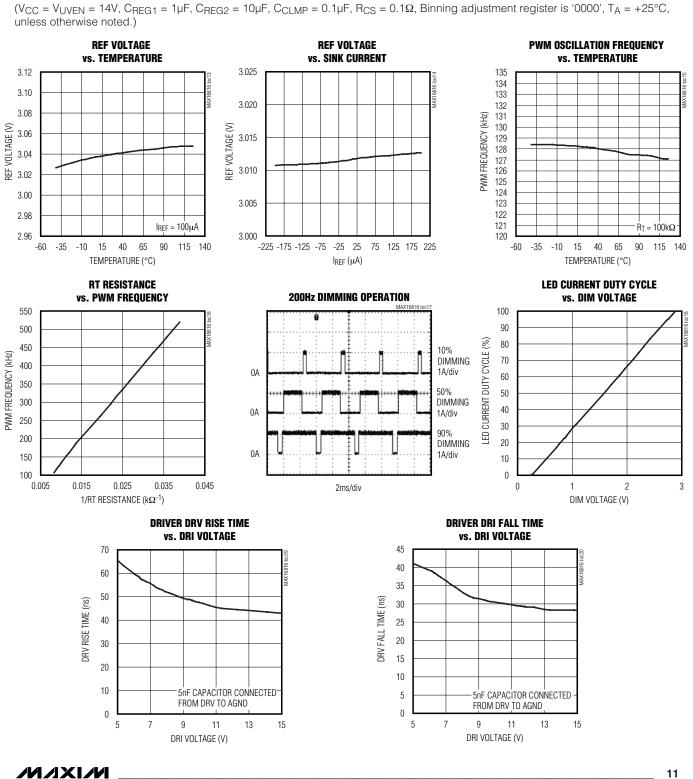

### \_Typical Operating Characteristics (continued)

$(V_{CC} = V_{UVEN} = 14V, C_{REG1} = 1\mu$ F,  $C_{REG2} = 10\mu$ F,  $C_{CLMP} = 0.1\mu$ F,  $R_{CS} = 0.1\Omega$ , Binning adjustment register is '0000',  $T_A = +25^{\circ}$ C, unless otherwise noted.)

**Typical Operating Characteristics (continued)**

MAX16816

Downloaded from Elcodis.com electronic components distributor

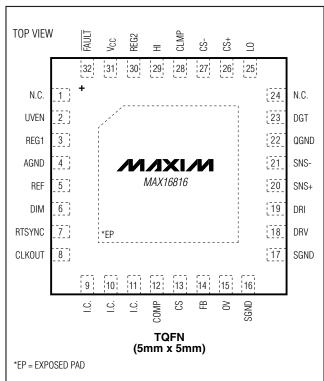

### **Pin Description**

| PIN       | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 24     | N.C.   | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2         | UVEN   | Undervoltage Lockout (UVLO) Threshold/Enable Input. UVEN is a dual-function adjustable UVLO threshold input with an enable feature. Connect UVEN to $V_{CC}$ through a resistive voltage-divider to program the UVLO threshold. Connect UVEN directly to $V_{CC}$ to use the 5.9V (max) default UVLO threshold. Apply a voltage greater than 1.244V to UVEN to enable the device.                                                                                                                                                           |

| 3         | REG1   | 5V Regulator Output. REG1 is an internal low-dropout voltage regulator that generates a 5V ( $V_{CC}$ > 6V) output voltage and supplies power to internal circuitry. Bypass REG1 to AGND through a 1µF ceramic capacitor.                                                                                                                                                                                                                                                                                                                   |

| 4         | AGND   | Analog Ground. Use proper single-point ground design and decoupling to avoid ground impedance loop errors.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5         | REF    | Accurate 3V Buffered Reference Output. Connect REF to DIM through a resistive voltage-divider to apply a DC voltage for analog-controlled dimming functionality. Leave REF unconnected if unused.                                                                                                                                                                                                                                                                                                                                           |

| 6         | DIM    | Dimming Control Input. Connect DIM to an external PWM signal for PWM dimming. For analog-controlled dimming, connect DIM to REF through a resistive voltage-divider. The dimming frequency is 200Hz under these conditions. Connect DIM to AGND to turn off the LEDs.                                                                                                                                                                                                                                                                       |

| 7         | RTSYNC | Sync Input/Output. The internal PWM clock is selectable through the RTOF EEPROM bit. Connect an external resistor to RTSYNC and set the RTOF register to '0' to select a clock frequency between 125kHz and 500kHz. Set RTOF register to '0' and connect RTSYNC to an external clock to synchronize the device with external clock. Set RTOF register to '1' to use the fixed 125kHz oscillator. Under these conditions, RTSYNC is powered off and may be left in any state. See the <i>Oscillator, Clock, and Synchronization</i> section. |

| 8         | CLKOUT | Clock Output. CLKOUT buffers the oscillator/clock. Connect CLKOUT to the SYNC input of another device to operate the MAX16816 in a multichannel configuration. CLKOUT is a logic output.                                                                                                                                                                                                                                                                                                                                                    |

| 9, 10, 11 | I.C.   | Internally Connected. Must be connected to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12        | COMP   | Error-Amplifier Output. Connect the compensation network from COMP to FB for stable closed-loop control. Use low-leakage ceramic capacitors in the feedback network.                                                                                                                                                                                                                                                                                                                                                                        |

| 13        | CS     | Current-Sense Voltage Output. CS outputs a voltage proportional to the current sensed through the current-<br>sense amplifier. Connect CS through a passive network to FB as dictated by the chosen compensation<br>scheme.                                                                                                                                                                                                                                                                                                                 |

| 14        | FB     | Error-Amplifier Inverting Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 15        | OV     | Overvoltage Protection Input. Connect OV to HI through a resistive voltage-divider to set the overvoltage limit for the load. When the voltage at OV exceeds the 1.235V (typ) threshold, an overvoltage fault is generated and the switching MOSFET turns off. The MOSFET is turned on again when the voltage at OV drops below 1.17V (typ).                                                                                                                                                                                                |

| 16, 17    | SGND   | Switching Ground. SGND is the ground for non-analog and high-current gate-driver circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 18        | DRV    | Gate-Driver Output. Connect DRV through a series resistor to the gate of an external n-channel MOSFET to reduce EMI. DRV can sink 1A or source 0.5A.                                                                                                                                                                                                                                                                                                                                                                                        |

| 19        | DRI    | Gate-Driver Supply Input. Connect DRI to REG2 to power the primary switching MOSFET driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 20        | SNS+   | Positive Peak Current-Sense Input. Connect SNS+ to the positive side of the switch current-sense resistor, RSENSE.                                                                                                                                                                                                                                                                                                                                                                                                                          |

## **Pin Description (continued)**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21  | SNS-            | Negative Peak Current-Sense Input. Connect SNS- to the negative side of the switch current-sense resistor, RSENSE.                                                                                                                                                                                                                                                                                                                                            |

| 22  | QGND            | Analog Ground. Ensure a low-impedance connection between QGND and AGND.                                                                                                                                                                                                                                                                                                                                                                                       |

| 23  | DGT             | Dimming Gate-Driver Output. Connect DGT to the gate of an external n-channel MOSFET for dimming. DGT is powered by the internal regulator, CLAMP, and is referenced to LO.                                                                                                                                                                                                                                                                                    |

| 25  | LO              | Low-Voltage Input. LO is the return point for the LED current. When using the MAX16816 in a buck-boost configuration, connect LO to $V_{CC}$ . When using the device in a boost configuration only, connect LO to AGND. Connect LO to the junction of the inductor and LED current-sense resistor, $R_{CS}$ , when using a buck configuration.                                                                                                                |

| 26  | CS+             | Noninverting Current-Sense Amplifier Input. Connect $CS+$ to the positive side of an external sense resistor, $R_{CS}$ , connected in series with the load (LEDs).                                                                                                                                                                                                                                                                                            |

| 27  | CS-             | Inverting Current-Sense Amplifier Input. Connect CS- to the negative side of an external sense resistor, R <sub>CS</sub> , connected in series with the load (LEDs).                                                                                                                                                                                                                                                                                          |

| 28  | CLMP            | Internal CLAMP Regulator Bypass. CLAMP supplies an 8V (typ) output when $V_{HI} \ge 9V$ . If $V_{HI}$ is lower than 9V, $V_{CLMP}$ is one diode drop below $V_{HI}$ . The CLAMP regulator powers the current-sense amplifier and provides the high reference for the dimming driver. $V_{CLMP}$ must be at least 2.5V higher than $V_{LO}$ to enable the current-sense amplifier and dimming MOSFET driver. Bypass CLMP to LO with a 0.1µF ceramic capacitor. |

| 29  | Н               | High-Voltage Input. HI is referred to LO. HI supplies power to the current-sense amplifier and dimming MOSFET gate driver through the CLMP regulator.                                                                                                                                                                                                                                                                                                         |

| 30  | REG2            | Internal Regulator Output. REG2 is an internal voltage regulator that generates EEPROM-programmable (5V to 15V) output and supplies power to internal circuitry. Connect REG2 to DRI to power the switching MOSFET driver during normal operation. Bypass REG2 to AGND with a 10µF ceramic capacitor.                                                                                                                                                         |

| 31  | V <sub>CC</sub> | Supply Voltage Input                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 32  | FAULT           | FAULT Input/Output. FAULT is a bidirectional high-voltage logic input/output. FAULT multiplexes a 1-Wire programming interface with a fault indicator. FAULT is internally pulled up to 5V through a $10k\Omega$ resistor and a 1.8mA (max) current pulldown to ground.                                                                                                                                                                                       |

| EP  | EP              | Exposed Pad. Connect EP to AGND. EP also functions as a heatsink to maximize thermal dissipation. Do not use as the main ground connection.                                                                                                                                                                                                                                                                                                                   |

Downloaded from <u>Elcodis.com</u> electronic components distributor

### **Detailed Description**

The MAX16816 is a current-mode PWM LED driver for use in driving HB LEDs. An output current accuracy of 5% is achievable using two current regulation loops: one current regulation loop controls the external switching MOSFET peak current through a sense resistor, R<sub>SENSE</sub>, from SNS+ to SNS- while the other current regulation loop controls the average LED string current through the sense resistor, R<sub>CS</sub>, in series with the LEDs. The wide operating supply range of 5.9V/5.4V (ON/OFF) to 76V makes the MAX16816 ideal in automotive applications.

The MAX16816 provides LED binning through one programmable on-chip nonvolatile EEPROM. The LED current can be scaled up to a factor of 1.6. This feature is used to offset factory LED luminance variations and allows the system to achieve overall luminance accuracy.

A programmable undervoltage lockout (UVEN) ensures predictable operation during brownout conditions. The UVEN input circuitry monitors the supply voltage, V<sub>CC</sub>, and turns the driver off when V<sub>CC</sub> drops below the UVLO threshold. Connect UVEN to V<sub>CC</sub> to use the 5.7V (typ) default UVLO threshold. The MAX16816 includes a cycle-by-cycle current limit that turns off the gate drive to the external switching MOSFET (Qs) during an overcurrent condition and a programmable oscillator that simplifies and optimizes the design of external magnetics.

The MAX16816 is capable of synchronizing to an external clock or operating in a stand-alone mode. A single resistor,  $R_T$ , can be used to adjust the switching frequency from 125kHz to 500kHz for stand-alone operation. To synchronize the device with an external clock, apply a clock signal directly to the RTSYNC input. A buffered clock output, CLKOUT, is available to configure the MAX16816 for multichannel applications. The external RT oscillator can be disabled by setting EEPROM register RTOF to '1'.

The MAX16816 provides wide contrast pulsed dimming (up to 1000:1) utilizing a separate dimming input. Apply either a DC level voltage or low-frequency PWM signal to the dimming input. DC level input results in a 200Hz fixed dimming frequency.

The MAX16816 provides configurable on-chip nonvolatile EEPROM features including a programmable soft-start, load current, external MOSFET gate-driver supply voltage, blanking time, and slope compensation.

Protection features include peak current limiting, HICCUP mode current limiting, output overvoltage protection, short-circuit protection, and thermal shutdown. The HICCUP current-limit circuitry reduces the power deliv-

ered to the load during severe fault conditions. A nonlatching overvoltage protection limits the voltage on the external switching MOSFET (Qs) under open-circuit conditions in the LED string. During continuous operation at high input voltages, the power dissipation of the MAX16816 could exceed the maximum rating and the internal thermal shutdown circuitry safely turns off the MAX16816 when the device junction temperature exceeds +165°C. When the junction temperature drops below the hysteresis temperature, the MAX16816 automatically reinitiates startup.

#### Undervoltage Lockout/Enable (UVEN)

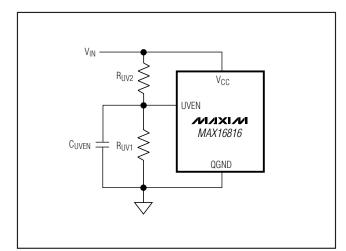

The MAX16816 features a dual-purpose adjustable undervoltage lockout input and enable function (UVEN). Connect UVEN to V<sub>CC</sub> through a resistive voltage-divider to set the undervoltage lockout (UVLO) threshold. The device is enabled when the voltage at UVEN exceeds the 1.244V (typ) threshold. Drive UVEN to ground to disable the output.

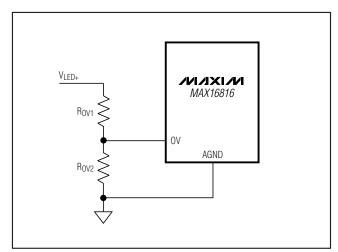

#### Setting the UVLO Threshold

Connect UVEN directly to V<sub>CC</sub> to select the default 5.7V (typ) UVLO threshold. Connect UVEN to V<sub>CC</sub> through a resistive voltage-divider to select a UVLO threshold (Figure 1). Select the desired UVLO threshold voltage, V<sub>UVLO</sub>, and calculate resistor values using the following equation:

$$R_{UV1} = R_{UV2} \times \left(\frac{V_{UVEN}}{V_{UVLO} - V_{UVEN}}\right)$$

where R<sub>UV1</sub> + R<sub>UV2</sub>  $\leq$  270k $\Omega$ . V<sub>UVEN</sub> is the 1.244V (typ) UVEN threshold voltage.

Figure 1. Setting the UVLO Threshold

The capacitor C<sub>UVEN</sub> is required to prevent chattering at the UVLO threshold due to line impedance drops during power-up and dimming. If the undervoltage setting is very close to the required minimum operating voltage, there can be large jumps in the voltage at V<sub>CC</sub> during dimming, which may cause the MAX16816 to turn on and off when the dimming signal transitions from low to high. The capacitor C<sub>UVEN</sub> should be large enough to limit the ripple on UVEN to less than the 100mV (min) UVEN hysteresis so that the device does not turn off under these circumstances.

#### Soft-Start

The MAX16816 features a digitally programmable softstart delay that allows the load current to ramp up in a controlled manner, minimizing output overshoot. Softstart begins once the device is enabled and V<sub>CC</sub> exceeds the UVLO threshold. Soft-start circuitry slowly increases the internal soft-start voltage, V<sub>SS</sub>, resulting in a controlled rise of the load current. Signals applied to DIM are ignored until the soft-start duration is complete and a successive delay of 200µs has elapsed. Use the Digital Soft-Start Duration register in the EEPROM to select a soft-start duration from 0 (no delay) to 4.096ms. See the *EEPROM and Programming* section for more information on using the Digital Soft-Start Duration register.

#### Regulators (REG1, REG2, CLAMP)

The MAX16816 includes a fixed 5V voltage regulator, REG1; an EEPROM-adjustable regulator, REG2; and an internal 8V regulator, CLAMP. REG1 and REG2 power up when V<sub>CC</sub> exceeds the UVLO threshold. REG1 supplies power to internal circuitry and remains on during PWM dimming. REG1 is capable of driving external loads up to 2mA.

Use the REG2 Control Register in the EEPROM to select an output voltage from 5V to 15V for REG2. Connect REG2 to DRI to generate the supply voltage for the primary switching MOSFET driver, DRV. REG2 is capable of delivering up to 20mA of current. See the *EEPROM and Programming* section for more information on configuring the REG2 output voltage.

CLAMP is powered by HI and supplies power to the current-sense amplifier (CSA). CSA is enabled when V<sub>CLMP</sub> goes 2.5V above V<sub>LO</sub> and is disabled when (V<sub>CLMP</sub> - V<sub>LO</sub>) falls below 2.28V. The CLAMP regulator also provides power to the dimming MOSFET control circuitry. CLMP is the output of the CLAMP regulator. Do not use CLMP to power external circuitry. Bypass CLMP to LO with a 0.1 $\mu$ F ceramic capacitor. A larger capacitor will result in overshoot of the load current.

#### **Reference Voltage Output (REF)**

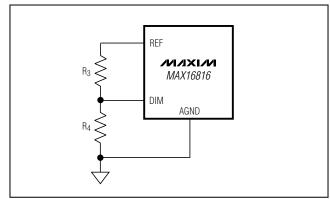

The MAX16816 includes a 5% accurate, 3V (typ) buffered reference output, REF. REF is a push-pull output capable of sourcing/sinking up to 200µA of current and can drive a maximum load capacitance of 100pF. Connect REF to DIM through a resistive voltage-divider to supply an analog signal for dimming. See the *Dimming Input (DIM)* section for more information.

#### **Dimming MOSFET Driver (DDR)**

The MAX16816 requires an external n-channel MOSFET for PWM dimming. Connect the MOSFET to the output of the DDR dimming driver, DGT, for normal operation. V<sub>DGT</sub> swings between V<sub>LO</sub> and V<sub>CLMP</sub>. The DDR dimming driver is capable of sinking or sourcing up to 20mA of current. The average current required to drive the dimming MOSFET (I<sub>DRIVE\_DIM</sub>) depends on the MOSFET's total gate charge (Q<sub>G\_DIM</sub>) and the dimming frequency of the converter, f<sub>DIM</sub>. Use the following equation to calculate the supply current for the n-channel dimming FET driver.

### $I_{DRIVE_DIM} = Q_{G_DIM} \times f_{DIM}$

n-Channel MOSFET Switch Driver (DRV) The MAX16816 drives an external n-channel MOSFET for switching. Use an external supply or connect REG2 to DRI to power the MOSFET driver. The driver output, VDRV, swings between ground and VDRI. Ensure that VDRI remains below the absolute maximum VGS rating of the external MOSFET. DRV is capable of sinking 2A or sourcing 1.4A of peak current, allowing the MAX16816 to switch MOSFETs in high-power applications. The average current sourced to drive the external MOSFET depends on the total gate charge (QG) and operating frequency of the converter, f<sub>SW</sub>. The power dissipation in the MAX16816 is a function of the average output drive current (IDRIVE). Use the following equations to calculate the power dissipation in the gate-driver section of the MAX16816 due to IDRIVE:

#### $I_{DRIVE} = Q_G \times f_{SW}$

Pd = Idrive x Vdri

where V<sub>DRI</sub> is the supply voltage to the gate driver.

#### **Dimming Input (DIM)**

M/IXI/M

The dimming input, DIM, functions with either analog or PWM control signals. Once the internal pulse detector detects three successive edges of a PWM signal with a frequency between 80Hz and 2kHz, the MAX16816 synchronizes to the external signal and pulse-width modulates the LED current at the external DIM input frequency with the same duty cycle as the DIM input. If

an analog control signal is applied to DIM, the MAX16816 compares the DC input to an internally generated 200Hz ramp to pulse-width modulate the LED current ( $f_{DIM} = 200$ Hz). The output current duty cycle is linearly adjustable from 0 to 100% (0.2V < V<sub>DIM</sub> < 2.8V).

Use the following formula to calculate voltage,  $V_{\text{DIM},}$  necessary for a given output current duty cycle, D:

$$V_{DIM} = (D \times 2.6) + 0.2V$$

where  $V_{\text{DIM}}$  is the voltage applied to DIM in volts.

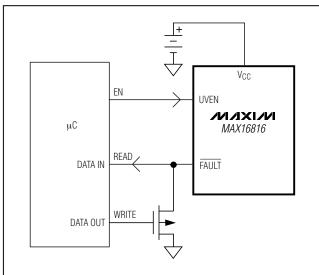

Connect DIM to REF through a resistive voltage-divider to apply a DC DIM control signal (Figure 2). Use the required dimming input voltage,  $V_{DIM}$ , calculated above and select appropriate resistor values using the following equation:

$R_4 = R_3 \times V_{DIM} / (V_{REF} - V_{DIM})$

where V<sub>REF</sub> is the 3V reference output voltage and  $15k\Omega \le R_3 + R_4 \le 150k\Omega$ .

A minimum 20µs pulse width is necessary for proper operation during dimming.

**Oscillator, Clock, and Synchronization**

The MAX16816 is capable of stand-alone operation, of synchronizing to an external clock, and of driving external devices in SYNC mode. For stand-alone operation, set the EEPROM Oscillator Enable/Disable (RTOF) bit to '1' to use the fixed internal 125kHz oscillator or set RTOF to '0' and program the switching frequency by connecting a single external resistor, RT, between RTSYNC and ground. Select a switching frequency, fsw, between 125kHz and 500kHz and calculate RT using the following formula:

$$R_{T} = \frac{500 \text{kHz}}{\text{f}_{SW}} \times 25 \text{k}\Omega$$

where the switching frequency is in kHz and RT is in  $k\Omega.$

Figure 2. Creating DIM Input Signal from REF

M/IXI/M

To synchronize the MAX16816 with an external clock signal ranging from 125kHz to 500kHz, set the RTOF bit to '0' and connect the clock signal to the RTSYNC input. The MAX16816 synchronizes to the clock signal after the detection of 5 successive clock edges at RTSYNC.

A buffered clock output, CLKOUT, can drive the RTSYNC input of an external PWM controller for multichannel applications. CLKOUT can drive capacitive loads up to 500pF.

If the PWM switching frequency is set to 125kHz, the RTSYNC oscillator can be temporarily disabled by setting the EEPROM RTOF bit to '1'. In this case, the internal 125kHz frequency-fixed oscillator drives the PWM. See the *EEPROM and Programming* section for more information on setting the Oscillator Enable/Disable bit in the EEPROM.

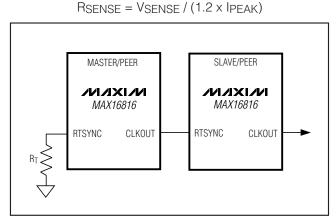

#### **Multichannel Configuration**

The MAX16816 is capable of multichannel operation and is configurable as a master or slave in a Master-Slave configuration, or in a Peer-to-Peer configuration. Connect CLKOUT to the SYNC input of an external device to use the MAX16816 as a master clock signal. Connect an external clock signal to RTSYNC to configure the MAX16816 as a slave. To setup two MAX16816 devices in a daisy-chain configuration, drive the RTSYNC input of one MAX16816 with the CLKOUT buffer of another (Figure 3).

#### **ILIM and HICCUP Comparator**

RSENSE sets the peak current through the inductor for switching. The differential voltage across R<sub>SENSE</sub> is compared to the 200mV voltage-trip limit of the currentlimit comparator, ILIM. Set the current limit 20% higher than the peak switch current at the rated output power and minimum voltage. Use the following equation to calculate R<sub>SENSE</sub>:

Figure 3. Master-Slave/Peer-Peer Clock Configuration

where  $V_{SENSE}$  is the 200mV maximum differential voltage between SNS+ and SNS- and IPEAK is the peak inductor current at full load and minimum input voltage.

When the voltage drop across R<sub>SENSE</sub> exceeds the ILIM threshold, the MOSFET driver (DRV) terminates the on-cycle and turns the switch off, reducing the current through the inductor. The FET is turned back on at the beginning of the next switching cycle.

When the voltage across R<sub>SENSE</sub> exceeds the 300mV (typ) HICCUP threshold, the HIC comparator terminates the on-cycle of the device, turning the switching MOS-FET off. Following a startup delay of 8ms (typ), the MAX16816 reinitiates soft-start. The device will continue to operate in HICCUP mode until the overcurrent condition is removed.

A programmable built-in leading-edge blanking circuit of the current-sense signal prevents these comparators from prematurely terminating the on-cycle of the external switching MOSFET ( $Q_S$ ). Select a blanking time from 75ns to 150ns by configuring the Blanking Time register in the EEPROM. In some cases, the maximum blanking time may not be adequate and an additional RC filter may be required to prevent spurious turn-off.

#### **Load Current Sense**

The load sense resistor, R<sub>CS</sub>, monitors the current through the LEDs. The internal floating current-sense amplifier, CSA, measures the differential voltage across R<sub>CS</sub>, and generates a voltage proportional to the load current through R<sub>CS</sub> at CS. This voltage on CS is referred to AGND. The closed-loop regulates the load current to a value,  $I_{LED}$ , given by the following equation:

#### $I_{LED} = V_{SS} / R_{CS}$

where V<sub>SS</sub> is the binning adjustment voltage. Set the value of V<sub>SS</sub> in the Binning Adjustment register in the EEPROM between 100mV and 166mV. See the *EEPROM and Programming* section for more information on adjusting the binning voltage.

#### **Slope Compensation**

The amount of slope compensation required is largely dependent on the down-slope of the inductor current when the switching MOSFET, QS, is off. The inductor down-slope depends on the input-to-output voltage differential of the converter, the inductor value, and the switching frequency. For stability, the compensation slope should be equal to or greater than half of the inductor current down-slope multiplied by the current-sense resistance (RSENSE).

See the *EEPROM and Programming* section for more information on the ESLP register.

#### Internal Voltage-Error Amplifier (EAMP)

The MAX16816 includes a built-in voltage amplifier, with three-state output, which can be used to close the feedback loop. The buffered output current-sense signal appears at CS, which is connected to the inverting input, FB, of the error amplifier through resistor R<sub>1</sub>. The noninverting input is connected to an internally trimmed current reference.

The output of the error amplifier is controlled by the signal applied to DIM. When DIM is high, the output of the amplifier is connected to COMP. The amplifier output is open when DIM is low. This enables the integrating capacitor to hold the charge when the DIM signal has turned off the gate drive. When DIM is high again, the voltage on the compensation capacitors,  $C_1$  and  $C_2$ , forces the converter into steady state almost instantaneously.

#### **PWM Dimming**

PWM dimming is achieved by driving DIM with either a PWM signal or a DC signal. The PWM signal is connected internally to the error amplifier, the dimming MOSFET gate driver, and the switching MOSFET gate driver. When the DIM signal is high, the dimming MOSFET and the switching MOSFET drivers are enabled and the output of the voltage-error amplifier is connected to the external compensation network. Also, the buffered current-sense signal is connected to CS. Preventing discharge of the compensation capacitor when the DIM signal is low allows the control loop to return the LED current to its original value almost instantaneously.