# Autonomous USB Type-C Controller with Configurable I<sup>2</sup>C Address

### Description

The FUSB301A is a fully autonomous Type-C controller optimized for < 15 W applications. The FUSB301A offers CC logic detection for Source Mode, Sink Mode, DRP, accessory detection support, and dead battery support. The FUSB301A features configurable I<sup>2</sup>C address to support multiple ports per system. The FUSB301A features an extremely low power disable mode as well as low power during normal operation. It is available in an ultra thin, 12-Lead TMLP Package.

#### **Features**

- Fully Autonomous Type-C Controller Supports Type-C Versions 1.1 and 1.0

- V<sub>DD</sub> Operating Range, 3.0 V 5.5 V

- Low Disable Power: I<sub>CC</sub> = 2.0 μA (Max.)

- Low Standby Power:  $I_{CC} = 7.0 \,\mu\text{A}$  (Max.)

- DRP Mode with Optional Accessory Support

- Configurable I<sup>2</sup>C Address

- Capable of Supporting Try.SNK and Try.SRC

- Dead Battery Support (SINK Support when No Power Applied)

- 2 kV HBM ESD Protection

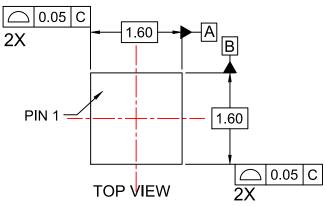

- Small Packaging, 12 Lead TMLP (1.6 mm × 1.6 mm × 0.375 mm)

### **Applications**

- Smartphones

- Tablets

.....)

Notebooks

• Ultra Portable Applications

# ON Semiconductor®

www.onsemi.com

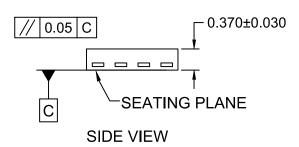

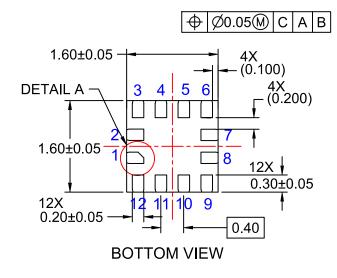

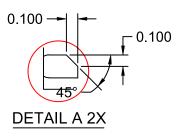

**Bottom View**

X2QFN12 1.6x1.6, 0.4P CASE 722AD

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 2 of this data sheet.

### **ORDERING INFORMATION**

| Part Number | Top Mark | Operating<br>Temperature Range | Package                                                                        | Packing Method <sup>†</sup> |

|-------------|----------|--------------------------------|--------------------------------------------------------------------------------|-----------------------------|

| FUSB301A    | NX       | -40 to 85°C                    | 12-Lead Ultra-thin Molded<br>Leadless Package (TMLP)<br>1.6 mm×1.6 mm×0.375 mm | Tape and Reel               |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

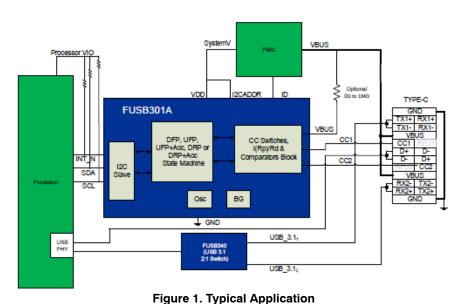

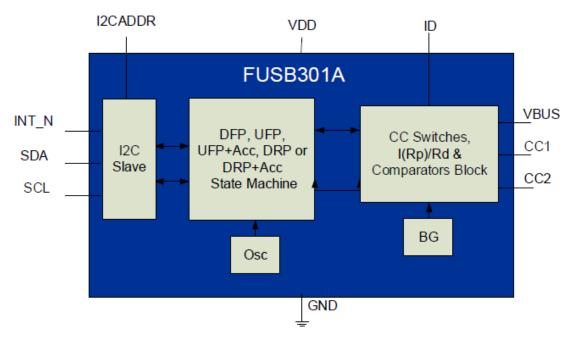

### **BLOCK DIAGRAM**

Figure 2. Block Diagram

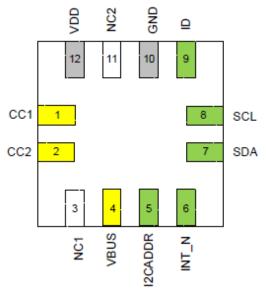

# **PIN CONFIGURATION**

Figure 3. Pin Assignment (Top Through View)

#### **PIN DESCRIPTIONS**

| Pin #            | Name            | Туре                 | Description                                                                                                                      |

|------------------|-----------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------|

| USB Type-C Conn  | ector Interface |                      |                                                                                                                                  |

| 1, 2             | CC1, CC2        | I/O                  | Type-C Configuration Channel                                                                                                     |

| 4                | VBUS            | Input                | VBUS input pin for attach and detach detection                                                                                   |

| 10               | GND             | Ground               | Ground                                                                                                                           |

| Power Interface  |                 |                      |                                                                                                                                  |

| 12               | VDD             | Power                | Input Supply Voltage                                                                                                             |

| Signal Interface |                 |                      |                                                                                                                                  |

| 8                | SCL             | Input                | I <sup>2</sup> C serial clock signal to be connected to the I <sup>2</sup> C master                                              |

| 7                | SDA             | Open-Drain<br>I/O    | I <sup>2</sup> C serial data signal to be connected to the I <sup>2</sup> C master                                               |

| 6                | INT_N           | Open-Drain<br>Output | Active LOW open drain interrupt output used to prompt the processor to read the I <sup>2</sup> C register bits                   |

| 9                | ID              | Open-Drain<br>Output | Used to Identify if connected device is Source or Sink. The ID Pin can be used to interface with USB 2.0 Input on the processor. |

| 5                | I2CADDR         | Input                | Used to change bit 3 of the I2C address so that multiple addresses can be used in a system where two device addresses conflict   |

| 3                | NC1             | NC                   | No Connect – Tie to Ground or Float                                                                                              |

| 11               | NC2             | NC                   | No Connect - Tie to Ground or Float                                                                                              |

### **Dead Battery**

If power is not applied to FUSB301A and it is attached to a Source device, then the Source would pull up the CC line connected through the cable. The FUSB301A in response would turn on the pull-down that will bring the CC voltage to a range that the Source can detect an attach and turn on VBUS.

## Power Up, Initialization and Reset, Interrupt Operation

When power is first applied, the FUSB301A will power up in Sink mode with all interrupts masked. The local processor must configure the FUSB301A to the desired mode and clear the global interrupt mask bit, INT\_MASK. The INT\_N pin is an active low, open drain output. This pin indicates to the host processor that an interrupt has occurred in the FUSB301A which needs attention. The INT\_N pin is

in a high impedance state by default after power-up or device reset, and the global interrupt mask (INT\_MASK in Control register) is set. After INT\_MASK bit is cleared by the local processor, the INT\_N pin stays high impedance in preparation of future interrupts. When an interruptible event occurs, INT\_N is driven LOW and is in a high impedance state again when the processor clears the interrupt by reading the interrupt registers. Subsequent to the initial power up or reset; if the processor writes a "1" to global interrupt mask bit when the system is already powered up, the INT\_N pin stays in a high impedance state and ignores all interrupts until the global interrupt mask bit is cleared. If an event happens that would ordinarily cause an interrupt when the global interrupt mask bit is set, the INT\_N pin goes LOW when the global interrupt mask is cleared.

**Table 1. ID PIN TRUTH TABLE**

| Type Register (h12, bit 4) | Description       | ID             |

|----------------------------|-------------------|----------------|

| SINK = b0                  | SINK Not Detected | Hi-Z (default) |

| SINK = b1                  | SINK Detected     | Low            |

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                | Parameter                                                 | Min. | Max. | Unit |

|-----------------------|-----------------------------------------------------------|------|------|------|

| $V_{DD}$              | Supply Voltage from V <sub>DD</sub>                       | -0.5 | 6.0  | V    |

| V <sub>BUS</sub>      | VBUS Supply Voltage                                       | -0.5 | 28   | V    |

| V <sub>CC_HDDRP</sub> | CC pins when configured as Host, Device or Dual Role Port | -0.5 | 6.0  | V    |

| T <sub>STORAGE</sub>  | Storage Temperature Range                                 | -65  | +150 | °C   |

### **ABSOLUTE MAXIMUM RATINGS** (continued)

| Symbol | Parameter                                  |                                                               |         | Min. | Max. | Unit |

|--------|--------------------------------------------|---------------------------------------------------------------|---------|------|------|------|

| TJ     | Maximum Junction Temperature               |                                                               |         |      | +150 | °C   |

| TL     | Lead Temperature (Soldering, 10 seconds)   |                                                               |         |      | +260 | °C   |

| ESD    | IEC 6100-4-2 System ESD                    | 100-4-2 System ESD Connector Pins (VBUS, CC1 and CC2) Contact | 15      |      | kV   |      |

|        |                                            |                                                               | Contact | 8    | +150 |      |

|        | Human Body Model, JEDEC JESD22-A114        | Connector Pins<br>CC1 and C                                   |         | 4    |      |      |

|        |                                            | Others                                                        | 3       | 2    |      |      |

|        | Charged Device Model, JEDEC<br>LESD22-C101 | All Pins                                                      | 6       | 1    |      |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

### **RECOMMENDED OPERAING CONDITIONS**

| Symbol           | Parameter             | Min.    | Тур. | Max. | Unit |

|------------------|-----------------------|---------|------|------|------|

| V <sub>BUS</sub> | VBUS Supply Voltage   | 3.7     | 5.0  | 21   | V    |

| V <sub>DD</sub>  | Supply Voltage        | 2.8 (1) | 3.3  | 5.5  | V    |

| T <sub>A</sub>   | Operating Temperature | -40     |      | +85  | °C   |

<sup>1.</sup> This is for functional operation only and isn't the lowest limit for all subsequent electrical specifications below. All electrical parameters have a minimum of 3 V operation.

### DC AND TRANSIENT CHARACTERISTICS

Unless otherwise specified: Recommended  $T_A$  and  $T_J$  temperature ranges. All typical values are at  $T_A = 25$ °C and  $V_{DD} = 3.3$  V unless otherwise specified.

|                       |                                                                          |      | = -40 to +85<br>= -40 to +12 |      |      |

|-----------------------|--------------------------------------------------------------------------|------|------------------------------|------|------|

| Symbol                | Parameter                                                                | Min. | Тур.                         | Max. | Unit |

| Type C Specific       | Parameters                                                               | •    |                              | •    | •    |

| I <sub>80</sub> _ccx  | Source 80 μA CC Current (Default) HOST_CUR1 = 0, HOST_CUR0 = 1           | 64   | 80                           | 96   | μΑ   |

| I <sub>180_CCX</sub>  | Source 180 μA CC Current (1.5 A) HOST_CUR1 = 1,<br>HOST_CUR0 = 0         | 166  | 180                          | 194  | μΑ   |

| I <sub>330</sub> _CCX | Source 330 μA CC Current (3 A) HOST_CUR1 = 1,<br>HOST_CUR0 = 1           | 304  | 330                          | 356  | μΑ   |

| V <sub>SNKDB</sub>    | Sink Pull-Down Voltage in Dead Battery Under all Pull-up SOURCE Loads    |      |                              | 2.18 | V    |

| R <sub>DEVICE</sub>   | Sink Pull–Down Resistance when V <sub>DD</sub> is within Operating Range | 4.6  | 5.1                          | 5.6  | kΩ   |

| zOPEN                 | CC Resistance for Disabled State                                         | 126  |                              |      | kΩ   |

| vRa-SRCdef            | Ra Detection Threshold for CC Pin for Source for Default Current on VBUS | 0.15 | 0.20                         | 0.25 | V    |

| vRa-SRC1.5A           | Ra Detection Threshold for CC Pin for Source for 1.5 A Current on VBUS   | 0.35 | 0.40                         | 0.45 | V    |

| vRa-SRC3A             | Ra Detection Threshold for CC Pin for Source for 3 A Current on VBUS     | 0.75 | 0.80                         | 0.85 | ٧    |

| vRd-SRCdef            | Rd Detection Threshold for Source for Default Current (HOST_CUR1/0 = 01) | 1.50 | 1.60                         | 1.65 | ٧    |

| vRd-SRC1.5A           | Rd Detection Threshold for Source for 1.5 A Current (HOST_CUR1/0 = 10)   | 1.50 | 1.60                         | 1.65 | ٧    |

# DC AND TRANSIENT CHARACTERISTICS

Unless otherwise specified: Recommended  $T_A$  and  $T_J$  temperature ranges. All typical values are at  $T_A = 25$ °C and  $V_{DD} = 3.3$  V unless otherwise specified. (continued)

|           |                                                                      | $T_{A} = -40 \text{ to } +85^{\circ}\text{C}$ $T_{J} = -40 \text{ to } +125^{\circ}\text{C}$ $Min. \qquad Typ. \qquad Max.$ $2.45 \qquad 2.60 \qquad 2.75$ $0.15 \qquad 0.20 \qquad 0.25$ $0.61 \qquad 0.66 \qquad 0.70$ |      |      |      |

|-----------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| Symbol    | Parameter                                                            | Min.                                                                                                                                                                                                                     | Тур. | Max. | Unit |

| vRd-SRC3A | Rd Detection Threshold for Source for 3 A Current (HOST_CUR1/0 = 11) | 2.45                                                                                                                                                                                                                     | 2.60 | 2.75 | V    |

| vRa-SNK   | Ra Detection Threshold for CC Pin for Sink                           | 0.15                                                                                                                                                                                                                     | 0.20 | 0.25 | V    |

| vRd-def   | Rd Default Current Detection Threshold for Sink                      | 0.61                                                                                                                                                                                                                     | 0.66 | 0.70 | V    |

| vRd-1.5A  | Rd 1.5 A Current Detection Threshold for Sink                        | 1.16                                                                                                                                                                                                                     | 1.23 | 1.31 | V    |

| vRd-3.0A  | Rd 3 A Current Detection Threshold for Sink                          | 2.04                                                                                                                                                                                                                     | 2.11 | 2.18 | V    |

| vVBUSthr  | VBUS Threshold at which I_VBUSOK Interrupt is Triggered              |                                                                                                                                                                                                                          |      | 3.7  | V    |

### **CURRENT CONSUMPTION**

|          |                                                |                     |                                       |      | -40 to +8<br>-40 to +1 |      | Unit |

|----------|------------------------------------------------|---------------------|---------------------------------------|------|------------------------|------|------|

| Symbol   | Parameter                                      | V <sub>DD</sub> (V) | Conditions                            | Min. | Тур.                   | Max. | Unit |

| Idisable | Disabled Current                               | 3.0 to 5.5          | Disabled State                        |      | 0.35                   | 2.0  | μΑ   |

| Istby    | Unattached Sink                                | 3.0 to 5.5          | Nothing attached                      |      | 3.5                    | 7.0  | μΑ   |

|          | Unattached Sink + Acc,<br>Source + Acc, or DRP |                     | Nothing attached, Internally Toggling |      | 5                      | 20   | μΑ   |

| lattach  | Attach Current (Less Host                      | 3.0 to 5.5          | Attached as a Sink                    |      | 5                      | 15   | μΑ   |

|          | Current)                                       |                     | Attached as a Source                  |      | 10                     | 15   | μΑ   |

### **TIMING PARAMETERS**

|                             |                                                                                          |                                     |       | -40 to +8<br>-40 to +1 |       | Unit |

|-----------------------------|------------------------------------------------------------------------------------------|-------------------------------------|-------|------------------------|-------|------|

| Symbol                      | Parameter                                                                                |                                     | Min.  | Тур.                   | Max.  | Unit |

| tCCDebounce                 | CDebounce Debounce Time for CC (Source or Accessory)                                     |                                     | 100   | 150                    | 200   | ms   |

| Debounce Time for CC (Sink) |                                                                                          |                                     | 63    | 75                     | 87    | ms   |

| tPDDebounce                 | Debounce Time for CC Detach Detection                                                    | oounce Time for CC Detach Detection |       | 15                     | 20    | ms   |

| tAccDetect                  | Debounce Time to Detect AudioAccessory, or DebugAccessory is Atached                     |                                     | 50    | 100                    | 200   | ms   |

| tErrorRecovery              | Time staying in the ErrorRecovery State if sent th ERROR_REC bit or by a change of Modes | ere via the                         | 25    | 50 100                 |       | ms   |

| tVBUSondeb                  | Debounce Time of VBUS Detection when acting a is present                                 | as a Sink to Signal VBUS            | 0.167 | 0.200                  | 0.375 | ms   |

| tVBUSoffdeb                 | Debounce Time of VBUS Detection when acting a has been removed                           | as a Sink to Signal VBUS            | 10    | 15                     | 20    | ms   |

| tDRPToggle1                 | For DRP Operation, Time Spent in Unat-                                                   | DRPROGGLE = 00                      | 35    |                        | 70    | ms   |

|                             | tached.Sink before going to Unattached.Source State                                      | DRPROGGLE = 01                      | 30    |                        | 60    |      |

|                             |                                                                                          | DRPROGGLE = 10                      | 25    |                        | 50    |      |

|                             |                                                                                          | DRPROGGLE = 11                      | 20    |                        | 40    |      |

### **TIMING PARAMETERS**

|             |                                                     |                |      | = -40 to +8<br>-40 to +1 |      | Unit |

|-------------|-----------------------------------------------------|----------------|------|--------------------------|------|------|

| Symbol      | Parameter                                           |                | Min. | Тур.                     | Max. | Unit |

| tDRPToggle2 | tached.Source before going to Unattached.Sink State | DRPROGGLE = 00 | 15   |                          | 30   | ms   |

|             |                                                     | DRPROGGLE = 01 | 20   |                          | 40   |      |

|             |                                                     | DRPROGGLE = 10 | 25   |                          | 50   |      |

|             |                                                     | DRPROGGLE = 11 | 30   |                          | 60   |      |

# **IO SPECIFICATIONS**

|                               |                                                               |                     |                                | T <sub>A</sub> :   | Unit |                    |      |

|-------------------------------|---------------------------------------------------------------|---------------------|--------------------------------|--------------------|------|--------------------|------|

| Symbol                        | Parameter                                                     | V <sub>DD</sub> (V) | Conditions                     | Min.               | Тур. | Max.               | Unit |

| Host Interface                | Pins (ID)                                                     | •                   |                                | •                  |      | •                  |      |

| V <sub>OLID</sub>             | Output Low Voltage                                            | 3.0 to 5.5          | I <sub>OL</sub> = 4 mA         |                    |      | 0.4                | V    |

| Host Interface                | Pins (I2CADDR)                                                | •                   |                                | •                  |      | •                  | •    |

| V <sub>ILADDR</sub>           | Low-Level Input Voltage                                       | 3.0 to 5.5          |                                |                    |      | 0.3V <sub>DD</sub> | V    |

| V <sub>IHADDR</sub>           | High-Level Input Voltage                                      | 3.0 to 5.5          |                                | 0.7V <sub>DD</sub> |      |                    | V    |

| Host Interface                | Pins (INT_N)                                                  |                     |                                | •                  |      |                    |      |

| V <sub>OLINTN</sub>           | Output Low Voltage                                            | 3.0 to 5.5          | I <sub>OL</sub> = 4 mA         |                    |      | 0.4                | V    |

| I <sup>2</sup> C Interface Pi | ins – Fast Mode SDA, SCL                                      |                     |                                | •                  |      |                    |      |

| V <sub>ILI2C</sub>            | Low-Level Input Voltage                                       | 3.0 to 5.5          |                                |                    |      | 0.4                | V    |

| V <sub>IHI2C</sub>            | High-Level Input Voltage                                      | 3.0 to 5.5          |                                | 1.2                |      |                    | V    |

| V <sub>HYS</sub>              | Hysteresis of Schmitt Trigger Inputs                          | 3.0 to 5.5          |                                | 0.2                |      |                    | V    |

| I <sub>I2C</sub>              | Input Current of SDA and SCL Pins                             | 3.0 to 5.5          | Input Voltage<br>0.26 V to 2 V | -10                |      | 10                 | μΑ   |

| I <sub>CCTI2C</sub>           | VDD Current when SDA and SCL are HIGH                         | 3.0 to 5.5          | Input Voltage<br>1.8 V         |                    |      | 10                 | μΑ   |

| V <sub>OLSDA</sub>            | Low-Level Output Voltage at 3 mA<br>Sink Current (Open-Drain) | 3.0 to 5.5          |                                | 0                  |      | 0.3                | V    |

| C <sub>I</sub>                | Capacitance for Each I/O Pin (2)                              | 3.0 to 5.5          |                                |                    |      | 10                 | pF   |

<sup>2.</sup> Guaranteed by characterization. Not production tested.

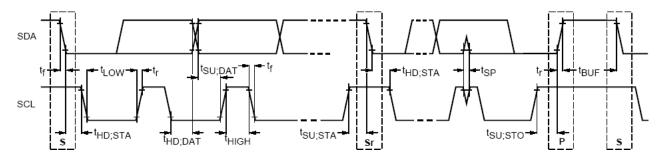

# FAST MODE I<sup>2</sup>C SPECIFICATIONS (Note 3)(see Figure 4)

|                     |                                          | Fast I   |                            |      |    |

|---------------------|------------------------------------------|----------|----------------------------|------|----|

| Symbol              | Parameter                                | Min.     | Max.                       | Unit |    |

| f <sub>SCL</sub>    | I2C_SCL Clock Frequency                  | 0        | 400                        | kHz  |    |

| t <sub>HD;STA</sub> | Hold Time (Repeated) START Condition     | 0.6      |                            | μs   |    |

| t <sub>LOW</sub>    | LOW Period of I2C_SCL Clock              | 1.3      |                            | μs   |    |

| t <sub>HIGH</sub>   | HIGH Period of I2C_SCL Clock             |          | 0.6                        |      | μs |

| t <sub>SU;STA</sub> | Set-up Time for Repeated START Condition |          | 0.6                        |      | μs |

| t <sub>HD;DAT</sub> | Data Hold Time                           |          | 0                          | 0.9  | μs |

| t <sub>SU;DAT</sub> | Data Set-up Time                         | (Note 4) | 100                        |      | ns |

| t <sub>r</sub>      | Rise Time of I2C_SDA and I2C_SCL Signals | (Note 5) | 20*(V <sub>DD</sub> /5.5V) | 250  | ns |

| t <sub>f</sub>      | Fall Time of I2C_SDA and I2C_SCL Signals | (Note 5) | 20*(V <sub>DD</sub> /5.5V) | 250  | ns |

FAST MODE I2C SPECIFICATIONS (Note 3) (see Figure 4) (continued)

|                     |                                                                   | Fast I |      |      |

|---------------------|-------------------------------------------------------------------|--------|------|------|

| Symbol              | Parameter                                                         | Min.   | Max. | Unit |

| t <sub>SU;STO</sub> | Set-up Time for STOP Condition                                    | 0.6    |      | μs   |

| t <sub>BUF</sub>    | BUS-Free Time between STOP and START Conditions                   | 1.3    |      | μs   |

| t <sub>SP</sub>     | Pulse Width of Spikes that Must Be Suppressed by the Input Filter | 0      | 50   | ns   |

- 3. Guaranteed by characterization. Not production tested.

- 4. A fast-mode I<sup>2</sup>C bus device can be used in a standard-mode I<sup>2</sup>C bus system, but the requirement t<sub>SU;DAT</sub> ≥ 250 ns must be met. This is automatically the case of the device does not stretch the LOW period of the I2C\_SCL signal. If such a device does stretch the LOW period I2C\_SCL signal, it must output the next data bit to the I2C\_SDA line tr\_max + t<sub>SU;DAT</sub> = 1000 + 250 = 1250 ns (according to the standard-mode I<sup>2</sup>C bus specification) before the I2C\_SCL line is released.

- Cb equals the total capacitance of one bus line in pF. If mixed with high-speed devices, faster fall times are allowed according to the I<sup>2</sup>C specification.

Figure 4. Definition of Timing for Full-Speed Mode Devices on the I<sup>2</sup>C Bus

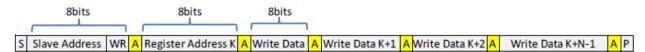

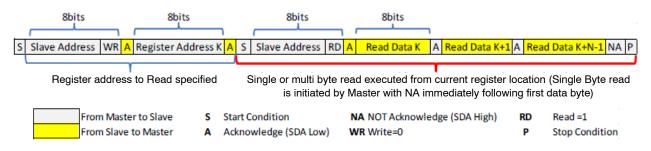

### **I<sup>2</sup>C INTERFACE**

The FUSB301A includes a full I<sup>2</sup>C slave controller. The I<sup>2</sup>C slave fully complies with the I<sup>2</sup>C specification version 6

requirements. This block is designed for fast mode. Examples of an I<sup>2</sup>C write and read sequence are shown Figure 5 and Figure 6 respectively.

NOTE: Single Byte read is initiated by Master with P immediately following first data byte.

Figure 5. I<sup>2</sup>C Write Example

NOTE: If Register is not specified Master will begin read from current register. In this case only sequence showing in Red bracket is needed.

Figure 6. I<sup>2</sup>C Read Example

# I<sup>2</sup>C ADDRESS

The I2CADDR bit high or low is indicated in bit3 of the slave address shown in Table 2.

Table 2. FUSB301A I<sup>2</sup>C SLAVE ADDRESS

| Name          | Size (Bits) | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 |

|---------------|-------------|-------|-------|-------|-------|---------|-------|-------|-------|

| Slave Address | 8           | 0     | 1     | 0     | 0     | I2CADDR | 0     | 1     | R/W   |

# **REGISTER DEFINITIONS**

### **Table 3. REGISTER MAP**

| Address   | Register<br>Name | Туре | RST<br>Val | Bit 7 | Bit 6      | Bit 5       | Bit 4   | Bit 3             | Bit 2     | Bit 1      | Bit 0     |

|-----------|------------------|------|------------|-------|------------|-------------|---------|-------------------|-----------|------------|-----------|

| 0×01      | Device ID        | RO   | 12         |       | Version    | on ID [3:0] |         | Revision ID [3:0] |           |            |           |

| 0×02      | Modes            | R/W  | 04         |       |            | DRP+ACC     | DRP     | Sink+ACC          | Sink      | Source+ACC | Source    |

| 0×03      | Control          | R/W  | 03         |       |            | DRPTO       | GGLE    |                   | HOST_CUR1 | HOST_CUR0  | INT_MASK  |

| 0×04      | Manual           | W/C  | 00         |       |            |             |         | UNATT_SNK         | UNATT_SRC | DISABLED   | ERROR_REC |

| 0×05      | Reset            | W/C  | 00         |       |            |             |         |                   |           |            | SW_RES    |

| 0×06-0×0F | Reserved         | Х    | xx         |       |            |             |         | Do Not Use        |           |            |           |

| 0×10      | Mask             | R/W  | 00         |       |            |             |         | M_ACC_CH          | M_BC_LVL  | M_DETACH   | M_ATTACH  |

| 0×11      | Status           | RO   | 00         |       |            | ORIENT1     | ORIENT0 | VBUSOK            | BC_LVL1   | BC_LVL0    | ATTACH    |

| 0×12      | Туре             | RO   | 00         |       |            |             | Sink    | Source            |           | DEBUGACC   | AUDIOACC  |

| 0×13      | Interrupt        | R/C  | 00         |       |            |             |         | I_ACC_CH          | I_BC_LVL  | I_DETACH   | I_ATTACH  |

| 0×14-0×1F | Reserved         | Х    | xx         |       | Do Not Use |             |         |                   |           |            |           |

6. Do not use registers that are blank.7. Values read from undefined register bits are invalid. Do not write to undefined registers.

### Table 4. DEVICE ID

Address: 01h

Reset Value: 0×0001\_0010

Type: Read Only

| Bit # | Name        | Size (Bits) | Description                                                          |

|-------|-------------|-------------|----------------------------------------------------------------------|

| 7:4   | Version ID  | 4           | Device version ID by Trim or etc. A_[Version ID]: 0001 (FUSB301ATMX) |

| 3:0   | Revision ID | 4           | Revision History of each version [Revision ID]_revC: 0010            |

### **Table 5. MODES**

Address: 02h

Reset Value: 0×0000\_0100 Type: Read/Write

| Bit # | Name       | Size (Bits) | Description                                                             |

|-------|------------|-------------|-------------------------------------------------------------------------|

| 7:6   | Reserved   | 2           | Do Not Use                                                              |

| 5     | DRP+ACC    | 1           | 1: Configure device as a Dual Role Port (DRP) with accessory support    |

| 4     | DRP        | 1           | 1: Configure device as a Dual Role Port (DRP) without accessory support |

| 3     | Sink+ACC   | 1           | 1: Configure device as a Sink with accessory support                    |

| 2     | Sink       | 1           | 1: Configure device as a Sink without accessory support                 |

| 1     | Source+ACC | 1           | 1: Configure device as a Source with accessory support                  |

| 0     | Source     | 1           | 1: Configure device as a Source without accessory support               |

### **Table 6. CONTROL**

Address: 03h

Reset Value: 0×XX00\_X011

Type: Read/Write

| Bit # | Name              | Size (Bits) | Description                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|-------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6   | Reserved          | 2           | Do Not Use                                                                                                                                                                                                                                                                                                                                                                                               |

| 5:4   | DRPTOGGLE         | 2           | Selects different timing for Dual Role Port Toggle between Unattached. Sink State and Unattached.SOURCE State.  00: 35 ms min. in Unattached.Sink and 15 ms min. In Unattached SOURCE  01: 30 ms min. In Unattached.Sink and 20 ms min. In Unattached.SOURCE 10: 25 ms min. In Unattached.Sink and 25 ms min. In Unattached.SOURCE 11: 20 ms min. In Unattached.Sink and 30 ms min. In Unattached.SOURCE |

| 3     | Reserved          | 1           | Do Not Use                                                                                                                                                                                                                                                                                                                                                                                               |

| 2:1   | HOST_CUR<br>[1:0] | 2           | 1: Controls the pull-up current when device enabled as a Source 00: No Current 01: 80 μA - Default USB Power 10: 180 μA - Medium Current Mode: 1.5 A 11: 330 μA - High Current Mode: 3 A                                                                                                                                                                                                                 |

| 0     | INT_MASK          | 1           | 1: Global interrupt mask to mask all interrupts                                                                                                                                                                                                                                                                                                                                                          |

### Table 7. MANUAL(Note 8)

Address: 04h

Reset Value: 0×XXXX\_0000

Type: Write/Clear

| Bit # | Name                   | Size (Bits) | Description                                                            |

|-------|------------------------|-------------|------------------------------------------------------------------------|

| 7:4   | Reserved               | 4           | Do Not Use                                                             |

| 3     | UNATT_SINK<br>(Note 9) | 1           | 1: Put device in Unattached.Sink state as defined in the Type C spec   |

| 2     | UNATT_SOURCE           | 1           | 1: Put device in Unattached.Source state as defined in the Type C spec |

| 1     | DISABLED<br>(Note 10)  | 1           | 1: Put device in Disabled state as defined in the Type C spec          |

| 0     | ERROR_REC              | 1           | 1: Put device in ErrorRecovery state as defined in the Type C spec     |

<sup>8.</sup> If more than one bit is set to "b1" simultaneously then an order of priority will be used. 1st priority is DISABLED, 2nd is ERROR\_REC, 3rd is UNATT\_SOURCE, last is UNATT\_SINK. The highest priority bit will take precedence and all other bits will be cleared automatically.

#### **Table 8. RESET**

Address: 05h

Reset Value: 0×XXXX\_XXX0

Type: Write/Clear

| Bit # | Name     | Size (Bits) | Description                           |

|-------|----------|-------------|---------------------------------------|

| 7:6   | Reserved | 7           | Do Not Use                            |

| 0     | SW_RES   | 1           | 1: Reset the system and I2C Register. |

#### Table 9. MASK

Address: 10h

Reset Value: 0×XXXX\_0000

Type: Read/Write

| Bit # | Name     | Size (Bits) | Description                                                   |

|-------|----------|-------------|---------------------------------------------------------------|

| 7:4   | Reserved | 4           | Do Not Use                                                    |

| 3     | M_ACC_CH | 1           | 1: Mask a change from Accessory Present to Attached Accessory |

<sup>9.</sup> Wait 2 ms between Modes = Sink and Manual = UNATT\_SINK writes.

<sup>10.</sup> The DISABLED bit must be manually cleared.

Table 9. MASK (continued)

Address: 10h

Reset Value: 0×XXXX\_0000

Type: Read/Write

| Bit # | Name     | Size (Bits) | Description                                    |

|-------|----------|-------------|------------------------------------------------|

| 2     | M_BC_LVL | 1           | 1: Mask a change in I_BC_LVL interrupt bit     |

| 1     | M_DETACH | 1           | 1: Mask the I_DETACH interrupt bit             |

| 0     | M_ATTACH | 1           | 1: Mask a change in the I_ATTACH interrupt bit |

### Table 10. STATUS

Address: 11h

Reset Value: 0×XX00\_0000

Type: Read

| Bit # | Name        | Size (Bits) | Description                                                                                                                                                                                                                                                         |

|-------|-------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6   | Reserved    | 2           | Do Not Use                                                                                                                                                                                                                                                          |

| 5:4   | ORIENT[1:0] | 2           | Status to indicate which CCx pins has the CC cable connection 11: A fault has occurred during the detection 10: Cable CC is connected through the CC2 pin 01: Cable CC is connected through the CC1 pin 00: No or unresolved connection detected.                   |

| 3     | VBUSOK      | 1           | 1: Status to indicate VBUS is in the valid range                                                                                                                                                                                                                    |

| 2:1   | BC_LVL[1:0] | 2           | Thresholds that allow detection of current advertisement on CC line  00: Ra or unattached Sink  01: Rd threshold for Sink default current advertisement  10: RD threshold for Sink 1.5 A current advertisement  11: RD threshold for Sink 3 A current advertisement |

| 0     | ATTACH      | 1           | 1: Attached to a device or accessory of a type shown in the Type register                                                                                                                                                                                           |

# Table 11. TYPE

Address: 12h

Reset Value: 0×XXX0\_0X00

Type: Read

| Bit # | Name     | Size (Bits) | Description                                      |

|-------|----------|-------------|--------------------------------------------------|

| 7:5   | Reserved | 3           | Do Not Use                                       |

| 4     | Sink     | 1           | 1: Indicates a Sink has been detected            |

| 3     | Source   | 1           | 1: Indicates a Source has been detected          |

| 2     | Reserved | 1           | Do Not Use                                       |

| 1     | DEBUGACC | 1           | 1: Indicates a Debug Accessory has been detected |

| 0     | AUDIOACC | 1           | 1: Indicates a Audio Accessory has been detected |

## Table 12. INTERRUPTO

Address: 13h

Reset Value: 0×XXXX\_X000

Type: Write/Clear

| Bit # | Name     | Size (Bits) | Description                                                                                          |

|-------|----------|-------------|------------------------------------------------------------------------------------------------------|

| 7:4   | Reserved | 4           | Do Not Use                                                                                           |

| 3     | I_ACC_CH | 1           | Interrupt flagged when a change from Accessory Present to Audio Accessory or Debug Accessory occurs. |

| 2     | I_BC_LVL | 1           | I: Interrupt flagged when a change in BC_LVL advertised current level has occurred                   |

# Table 12. INTERRUPT0 (continued)

Address: 13h

Reset Value: 0×XXXX\_X000

Type: Write/Clear

| Bit # | Name     | Size (Bits) | Description                                                                                           |

|-------|----------|-------------|-------------------------------------------------------------------------------------------------------|

| 1     | I_DETACH | 1           | 1: Interrupt flagged when a device or accessory has been detached                                     |

| 0     | I_ATTACH | 1           | Interrupt flagged when a device or accessory of type indicated in the Type register has been attached |

ON Semiconductor is licensed by the Philips Corporation to carry the  $I^2C$  bus protocol.

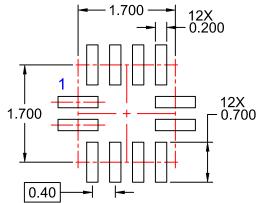

### X2QFN12 1.6x1.6, 0.4P CASE 722AD ISSUE O

**DATE 31 OCT 2016**

LAND PATTERN RECOMMENDATION

### NOTES:

- A. NO JEDEC REGISTRATION APPLIES.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCE PER ASME Y14.5M, 2009.

- D. PACKAGE NOMINAL HEIGHT IS 370 MICRONS.

| DOCUMENT NUMBER: | 98AON13693G           | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | X2QFN12 1.6x1.6, 0.4P |                                                                                                                                                                                     | PAGE 1 OF 1 |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

**TECHNICAL SUPPORT** North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada

Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

onsemi

FUSB301ATMX